#### Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# H8/3827R Group, H8/3827S Group, H8/38327 Group, H8/38427 Group

# Hardware Manual

**Renesas 8-Bit Single-Chip Microcomputer** H8 Family/H8/300L Super Low Power Series H8/38327 Group H8/38322 H8/3827R Group H8/3822R H8/3823R H8/38323 H8/3824R H8/38324 H8/3825R H8/38325 H8/3826R H8/38326 H8/3827R H8/38327 H8/3827S Group H8/3824S H8/38427 Group H8/38422 H8/3825S H8/38423 H8/3826S H8/38424 H8/3827S H8/38425 H8/38426

Renesas Electronics

Rev.6.00 2006.08

H8/38427

- These materials are intended as a reference to assist our customers in the selection of the F Technology Corp. product best suited to the customer's application; they do not convey any under any intellectual property rights, or any other rights, belonging to Renesas Technology a third party.

- Renesas Technology Corp. assumes no responsibility for any damage, or infringement of ar party's rights, originating in the use of any product data, diagrams, charts, programs, algorith circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, progra algorithms represents information on products at the time of publication of these materials, a subject to change by Renesas Technology Corp. without notice due to product improvemen other reasons. It is therefore recommended that customers contact Renesas Technology C orp. product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.cc

- 4. When using any or all of the information contained in these materials, including product data diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a system before making a final decision on the applicability of the information and products. F Technology Corp. assumes no responsibility for any damage, liability or other loss resulting information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a c system that is used under circumstances in which human life is potentially at stake. Please Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor considering the use of a product contained herein for any specific purposes, such as appara systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use

- The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, the be exported under a license from the Japanese government and cannot be imported into a cother than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/o country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the producontained therein.

Rev. 6.00 Aug 04, 2006 page ii of xxxiv

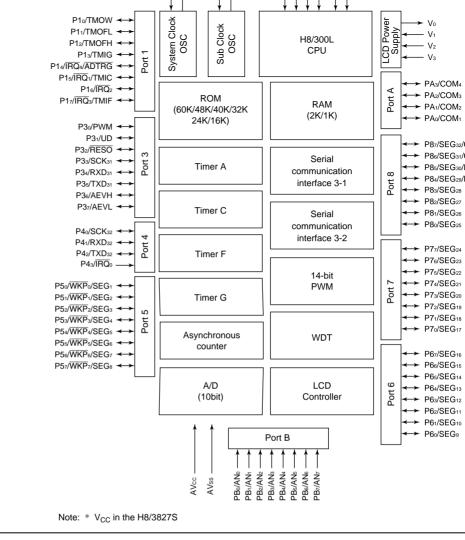

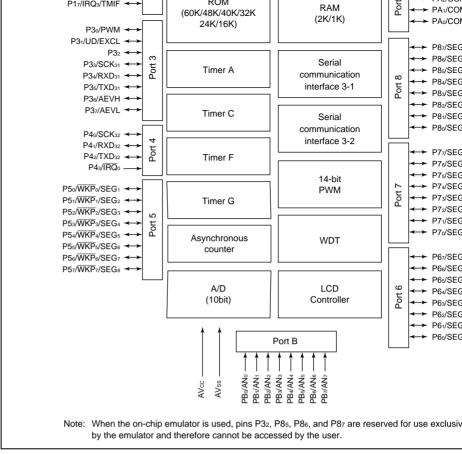

an ideal configuration as a microcomputer for embedding in sophisticated control syst (ZTAT<sup>TM\*1</sup>), flash memory (F-ZTAT<sup>TM\*2</sup>), and mask ROM are available as on-chip F enabling users to respond quickly and flexibly to changing application specifications a demands of the transition from initial to full-fledged volume production.

Notes: 1. ZTAT is a trademark of Renesas Technology Corp.

- 2. F-ZTAT is a trademark of Renesas Technology Corp.

- Intended Readership: This manual is intended for users undertaking the design of an a system using the H8/3827R Group, H8/3827S Group, H8/38327 H8/38427 Group. Readers using this manual require a basic know electrical circuits, logic circuits, and microcomputers.

- Purpose: The purpose of this manual is to give users an understanding of the functions and electrical characteristics of the H8/3827R Group, I Group, H8/38327 Group, and H8/38427 Group. Details of executions the found in the H8/300L Series Programming M which should be read in conjunction with the present manual.

Using this Manual:

For an overall understanding of the H8/3827R Group, H8/3827S Group, H8/38327 H8/38427 Group's functions

Follow the Table of Contents. This manual is broadly divided into sections on the

control functions, peripheral functions, and electrical characteristics.

For a detailed understanding of CPU functions Refer to the separate publication H8/300L Series Programming Manual. Note on bit notation: Bits are shown in high-to-low order from left to right.

Rev. 6.00 Aug 04, 2006 pa

### Renesas

- 4. The address area from H'F300 to H'F6FF must not be accessed under any circumstances.

- 5. When the on-chip emulator is used, pin P3<sub>2</sub> functions as an I/O pin, pins P8<sub>3</sub> function as input pins, and pin P8<sub>7</sub> functions as an output pin.

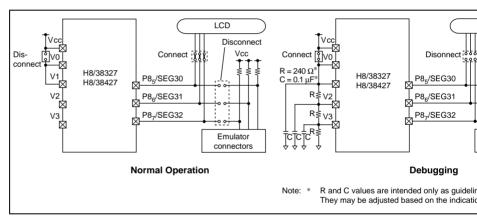

- 6. It is necessary to change the user board for LCD display debugging. This ite apply if LCD display is not used or if the emulator is not operated in writer

User Board Changes

The following changes are necessary.

- Connect pin V1 to the V<sub>CC</sub> power supply. Also connect capacitors and repins V1, V2, and V3. Connect a capacitor and a resistor to pins V1, V2, a

- No SEG signals are output from pins P8<sub>5</sub>/SEG30, P8<sub>6</sub>/SEG31, and P8<sub>7</sub>/S the display is unstable. In addition, a DC voltage is applied. If damage to a concern, disconnect the above three pins from the LCD.

A connection example is shown below. Refer to the emulator user's manual information on other settings.

Rev. 6.00 Aug 04, 2006 page iv of xxxiv

|                                                                                   | Docume   |

|-----------------------------------------------------------------------------------|----------|

| H8/3827R Group, H8/3827S Group, H8/38327 Group, H8/38427 Group<br>Hardware Manual | This man |

| H8/300L Series Programming Manual                                                 | REJ09B0  |

User's manuals for development tools:

| Manual Title                                                                                                 | Docume  |

|--------------------------------------------------------------------------------------------------------------|---------|

| C/C++ Compiler, Assembler, Optimizing Linkage Editor User's Manual                                           | REJ10B0 |

| H8S, H8/300 Series Simulator/Debugger User's Manual                                                          | REJ10B0 |

| High-Performance Embedded Workshop User's Manual                                                             | ADE-702 |

| H8S, H8/300 Series High-Performance Embedded Workshop,<br>High-Performance Debugging Interface User's Manual | ADE-702 |

Application Note:

| Manual Title                    | Documei |

|---------------------------------|---------|

| H8/300L Series Application Note | ADE-502 |

Rev. 6.00 Aug 04, 2006 pa

# Renesas

Rev. 6.00 Aug 04, 2006 page vi of xxxiv

or if the emulator is not operated in writer mode.

User Board Changes

The following changes are necessary.

Connect pin V1 to the V<sub>CC</sub> power supply. Also capacitors and resistors to pins V1, V2, and V3. capacitor and a resistor to pins V1, V2, and V3.

During a break, the watchdog timer continues to c Therefore, an internal reset is generated if an ove during the break.

|                     |     |                              | •                                     |                                    |                                  |                             |                                                                                              |

|---------------------|-----|------------------------------|---------------------------------------|------------------------------------|----------------------------------|-----------------------------|----------------------------------------------------------------------------------------------|

| 1.3.2 Pin Functions | 28  | Table a                      | amended                               |                                    |                                  |                             |                                                                                              |

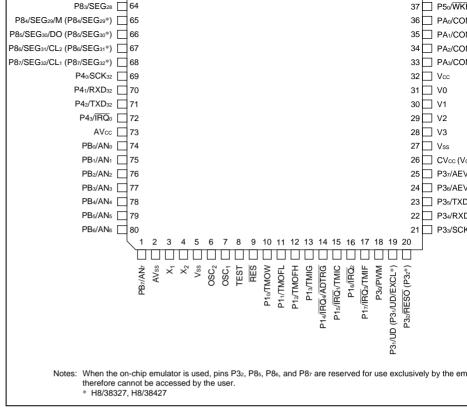

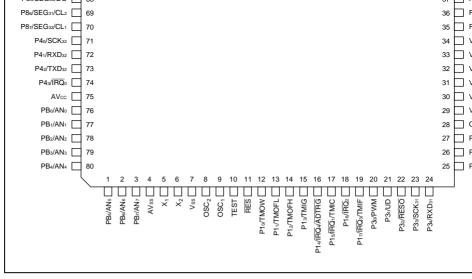

| Table 1.6 Pin       |     |                              |                                       | Pir                                | n No.                            | _                           |                                                                                              |

| Functions           |     | Туре                         | Symbol                                | FP-80A<br>TFP-80C                  | FP-80B                           |                             | Name and Functions                                                                           |

|                     |     | System control               | TEST                                  | 8                                  | 10                               | Input                       | Test pin: This pin is recannot be used. It sho to $V_{SS}$ .                                 |

| 8.3.1 Overview      | 203 | Descrip                      | otion ame                             | nded                               |                                  |                             |                                                                                              |

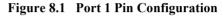

|                     |     | Port 3 i                     | is a 8-bit l                          | I/O port,                          | configu                          | ured a                      | s shown in figure                                                                            |

|                     |     | during<br>after th<br>connec | the reset<br>e reset is<br>tions to e | period. I<br>cleared<br>external o | t turns<br>. This s<br>circuitry | off an<br>should<br>/. Note | III-up MOS for pi<br>d normal operati<br>be considered v<br>that in the mas<br>ate normally. |

|                     |     |                              |                                       |                                    |                                  |                             |                                                                                              |

Rev. 6.00 Aug 04, 2006 pag

|                                                                                                                                                                                |     | P3 <sub>2</sub> <sup>+3</sup> High-<br>P3 <sub>3</sub> /UD <sup>*2</sup> impedance<br>P3/UD/EXCL <sup>+3*4</sup><br>P3/PWM<br>Notes: 1. A high-level signal is output when the MOS pull-up is in the on state.<br>2. Applies to H8/3827R Group and H8/3827S Group.<br>3. Applies to the mask ROM version of the H8/38327 Group and H8/38427<br>4. Applies to the F-ZTAT version of the H8/38327 Group and H8/38427 Group and H8/3842 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.12.1 The<br>Management of the<br>Un-Use Terminal                                                                                                                             | 236 | <ul> <li>Description amended</li> <li>If an unused pin is an output pin, handle it in one of following ways:</li> <li>Set the output of the unused pin to high and pul Vcc with an external resistor of approximately 1</li> <li>Set the output of the unused pin to low and pull Vss with an external resistor of approximately 1</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

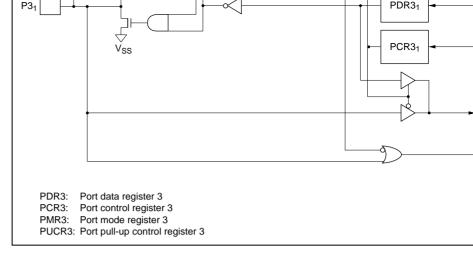

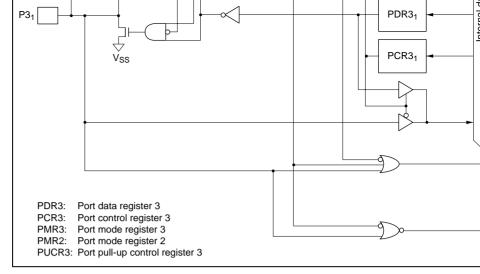

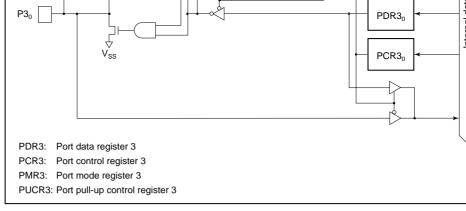

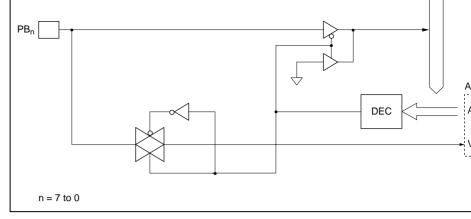

| C.2 Block Diagrams<br>of Port 3<br>Figure C.2 (e-2)<br>Port 3 Block Diagram<br>(Pin P3 <sub>2</sub> in the Mask<br>ROM Version of the<br>H8/38327 Group and<br>H8/38427 Group) | 593 | Figure title amended                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Figure C.2 (e-3)<br>Port 3 Block Diagram<br>(Pin P $_2$ in the F-ZTAT<br>Version of the<br>H8/38327 Group and<br>H8/38427 Group)                                               | 594 | Newly added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Rev. 6.00 Aug 04, 2006 page viii of xxxiv

Rev. 6.00 Aug 04, 2006 pa

Rev. 6.00 Aug 04, 2006 page x of xxxiv

|       | 1.3.2   | Pin Functions                        |

|-------|---------|--------------------------------------|

| Secti | ion 2   | CPU                                  |

| 2.1   | Overvi  | ew                                   |

|       | 2.1.1   | Features                             |

|       | 2.1.2   | Address Space                        |

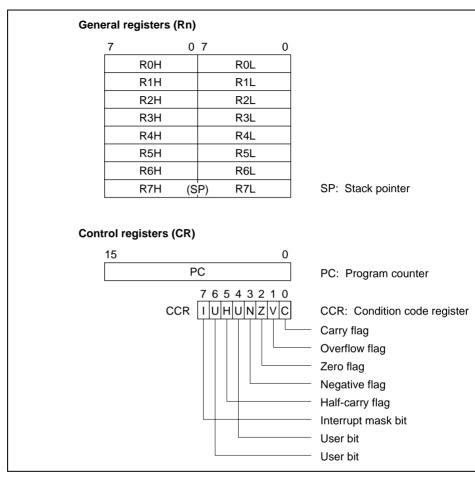

|       | 2.1.3   | Register Configuration               |

| 2.2   | Registe | er Descriptions                      |

|       | 2.2.1   | General Registers                    |

|       | 2.2.2   |                                      |

|       | 2.2.3   | Initial Register Values              |

| 2.3   | Data F  | ormats                               |

|       | 2.3.1   | Data Formats in General Registers    |

|       | 2.3.2   | Memory Data Formats                  |

| 2.4   | Addres  | sing Modes                           |

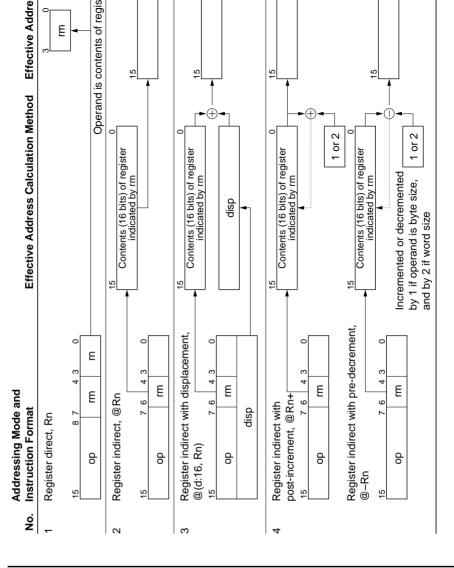

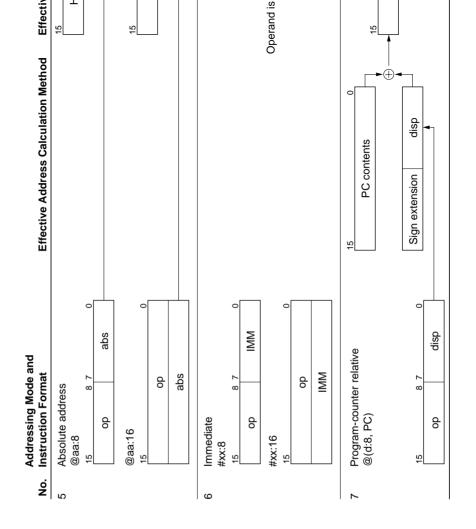

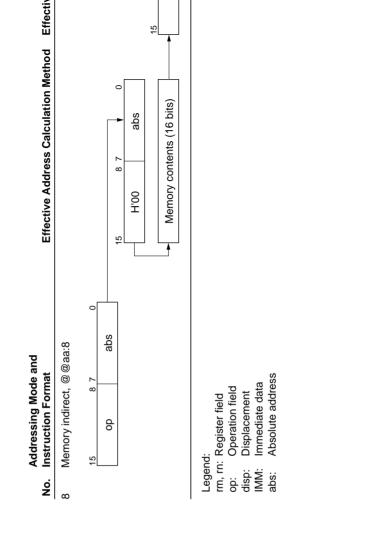

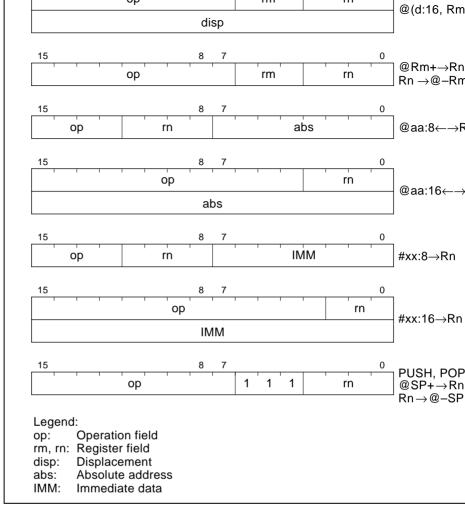

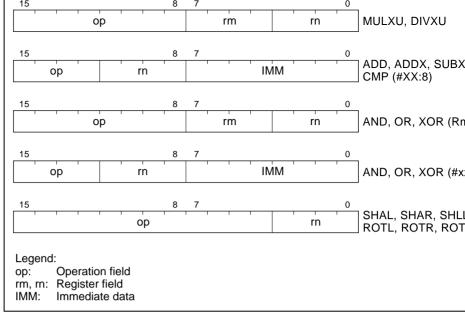

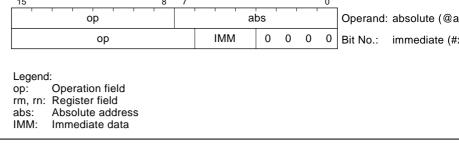

|       | 2.4.1   | Addressing Modes                     |

|       | 2.4.2   | Effective Address Calculation        |

| 2.5   | Instruc | tion Set                             |

|       | 2.5.1   | Data Transfer Instructions           |

|       | 2.5.2   | Arithmetic Operations                |

|       | 2.5.3   | Logic Operations                     |

|       | 2.5.4   | Shift Operations                     |

|       | 2.5.5   | Bit Manipulations                    |

|       | 2.5.6   | Branching Instructions               |

|       | 2.5.7   | System Control Instructions          |

|       | 2.5.8   | Block Data Transfer Instruction      |

| 2.6   | Basic ( | Dperational Timing                   |

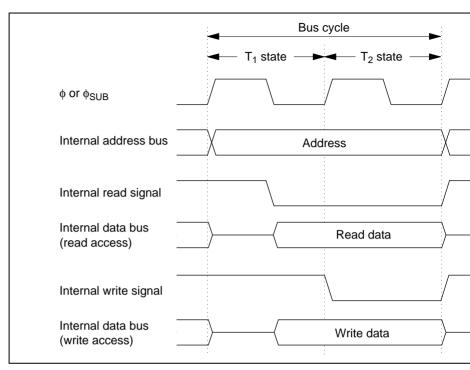

|       | 2.6.1   | Access to On-Chip Memory (RAM, ROM)  |

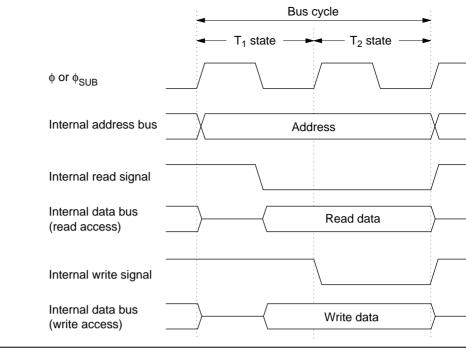

|       | 2.6.2   | Access to On-Chip Peripheral Modules |

| 2.7   | CPU S   | tates                                |

|       | 2.7.1   | Overview                             |

|       | 2.7.2   | Program Execution State              |

Rev. 6.00 Aug 04, 2006 pa

| Sect       | ion 3  | Exception Handling                                                    |

|------------|--------|-----------------------------------------------------------------------|

| 3.1        |        | riew                                                                  |

| 3.2        | Reset  |                                                                       |

|            | 3.2.1  | Overview                                                              |

|            | 3.2.2  | Reset Sequence                                                        |

|            | 3.2.3  | Interrupt Immediately after Reset                                     |

| 3.3        | Interr | upts                                                                  |

|            | 3.3.1  | Overview                                                              |

|            | 3.3.2  | Interrupt Control Registers                                           |

|            | 3.3.3  | External Interrupts                                                   |

|            | 3.3.4  | Internal Interrupts                                                   |

|            | 3.3.5  | Interrupt Operations                                                  |

|            | 3.3.6  | Interrupt Response Time                                               |

| 3.4        | Appli  | cation Notes                                                          |

|            | 3.4.1  | Notes on Stack Area Use                                               |

|            | 3.4.2  | Notes on Rewriting Port Mode Registers                                |

|            | 3.4.3  | Method for Clearing Interrupt Request Flags                           |

| <b>C</b> 4 | : 1    | Clash Dalas Concertant                                                |

|            |        | Clock Pulse Generators                                                |

| 4.1        |        | iew                                                                   |

|            |        | Block Diagram                                                         |

|            | 4.1.2  | System Clock and Subclock                                             |

| 4.2        | -      | n Clock Generator                                                     |

| 4.3        |        | ock Generator                                                         |

| 4.4        |        | alers                                                                 |

| 4.5        | Note   | on Oscillators                                                        |

|            | 4.5.1  | Definition of Oscillation Stabilization Wait Time                     |

|            | 4.5.2  | Notes on Use of Crystal Oscillator Element (Excluding Ceramic Oscilla |

|            |        | Element)                                                              |

Rev. 6.00 Aug 04, 2006 page xii of xxxiv

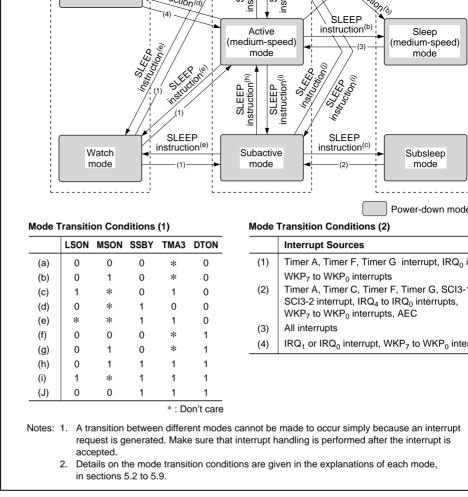

|      | 3.3.1  | Transition to Standby Mode                                            |

|------|--------|-----------------------------------------------------------------------|

|      | 5.3.2  | Clearing Standby Mode                                                 |

|      | 5.3.3  | Oscillator Settling Time after Standby Mode is Cleared                |

|      | 5.3.4  | Standby Mode Transition and Pin States                                |

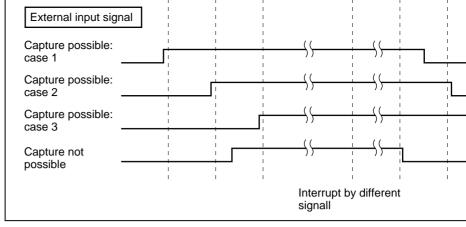

|      | 5.3.5  | Notes on External Input Signal Changes before/after Standby Mode      |

| 5.4  | Watch  | Mode                                                                  |

|      | 5.4.1  | Transition to Watch Mode                                              |

|      | 5.4.2  | Clearing Watch Mode                                                   |

|      | 5.4.3  | Oscillator Settling Time after Watch Mode is Cleared                  |

|      | 5.4.4  | Notes on External Input Signal Changes before/after Watch Mode        |

| 5.5  | Subsle | ep Mode                                                               |

|      | 5.5.1  | Transition to Subsleep Mode                                           |

|      | 5.5.2  | Clearing Subsleep Mode                                                |

| 5.6  | Subact | ive Mode                                                              |

|      | 5.6.1  | Transition to Subactive Mode                                          |

|      | 5.6.2  | Clearing Subactive Mode                                               |

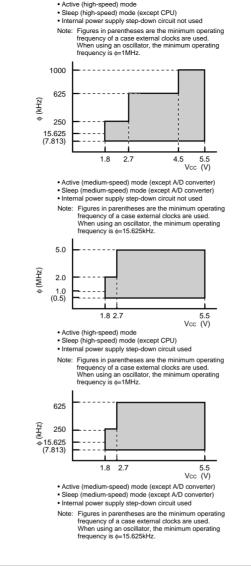

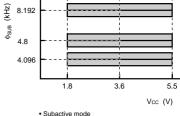

|      | 5.6.3  | Operating Frequency in Subactive Mode                                 |

| 5.7  | Active | (Medium-Speed) Mode                                                   |

|      | 5.7.1  | Transition to Active (Medium-Speed) Mode                              |

|      | 5.7.2  | Clearing Active (Medium-Speed) Mode                                   |

|      | 5.7.3  | Operating Frequency in Active (Medium-Speed) Mode                     |

| 5.8  | Direct | Transfer                                                              |

|      | 5.8.1  | Overview of Direct Transfer                                           |

|      | 5.8.2  | Direct Transition Times                                               |

|      | 5.8.3  | Notes on External Input Signal Changes before/after Direct Transition |

| 5.9  | Modul  | e Standby Mode                                                        |

|      | 5.9.1  | Setting Module Standby Mode                                           |

|      | 5.9.2  | Clearing Module Standby Mode                                          |

|      | 5.9.3  | Usage Note                                                            |

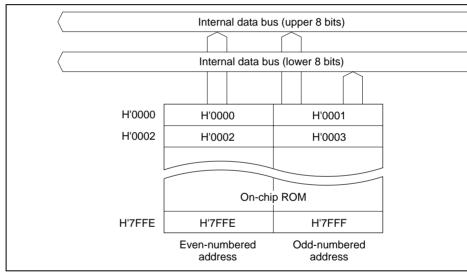

| Sect | ion 6  | ROM                                                                   |

| 6.1  | Overv  | iew                                                                   |

|      |        |                                                                       |

Rev. 6.00 Aug 04, 2006 pag

| 0.3  | riash n |                                                          |

|------|---------|----------------------------------------------------------|

|      | 6.5.1   | Features                                                 |

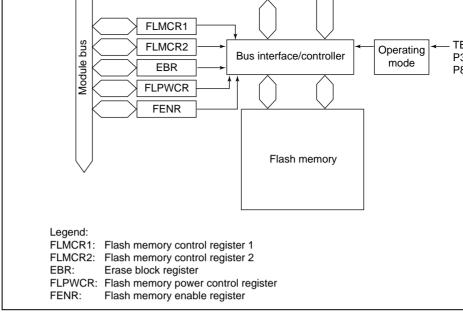

|      | 6.5.2   | Block Diagram                                            |

|      | 6.5.3   | Block Configuration                                      |

|      | 6.5.4   | Register Configuration                                   |

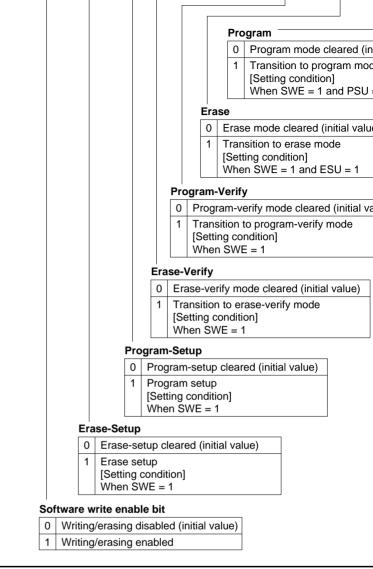

| 6.6  | Descrip | ptions of Registers of the Flash Memory                  |

|      | 6.6.1   | Flash Memory Control Register 1 (FLMCR1)                 |

|      | 6.6.2   | Flash Memory Control Register 2 (FLMCR2)                 |

|      | 6.6.3   | Erase Block Register (EBR)                               |

|      | 6.6.4   | Flash Memory Power Control Register (FLPWCR)             |

|      | 6.6.5   | Flash Memory Enable Register (FENR)                      |

| 6.7  | On-Boa  | ard Programming Modes                                    |

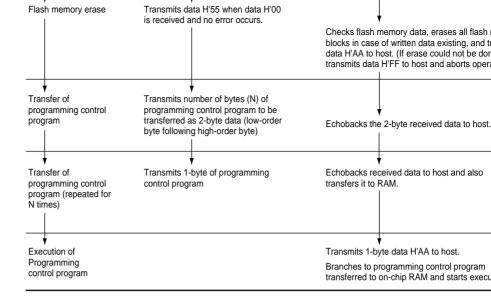

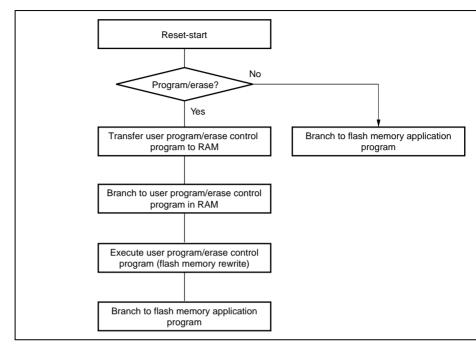

|      | 6.7.1   | Boot Mode                                                |

|      | 6.7.2   | Programming/Erasing in User Program Mode                 |

| 6.8  | Flash N | Aemory Programming/Erasing                               |

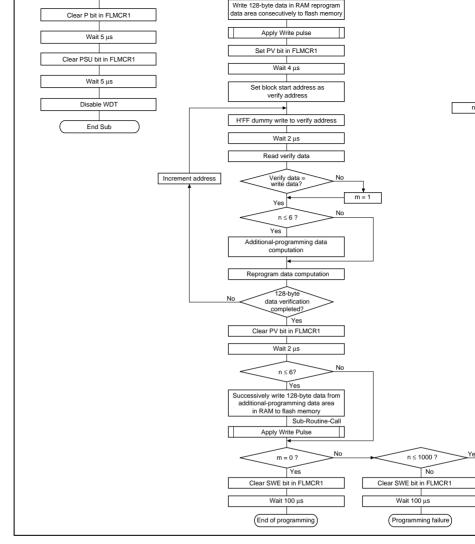

|      | 6.8.1   | Program/Program-Verify                                   |

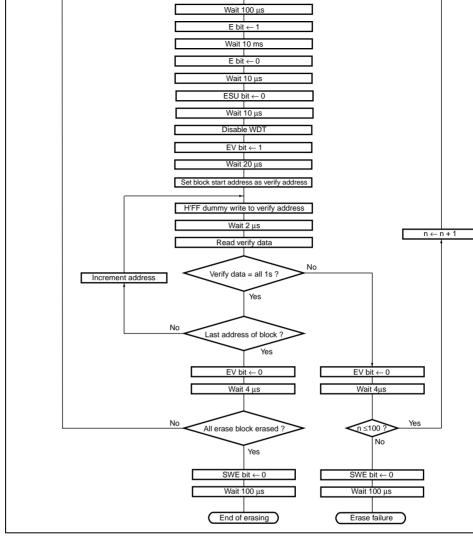

|      | 6.8.2   | Erase/Erase-Verify                                       |

|      | 6.8.3   | Interrupt Handling when Programming/Erasing Flash Memory |

| 6.9  | Program | n/Erase Protection                                       |

|      | 6.9.1   | Hardware Protection                                      |

|      | 6.9.2   | Software Protection                                      |

|      | 6.9.3   | Error Protection                                         |

| 6.10 | Program | nmer Mode                                                |

|      | 6.10.1  | Socket Adapter                                           |

|      | 6.10.2  | Programmer Mode Commands                                 |

|      | 6.10.3  | Memory Read Mode                                         |

|      | 6.10.4  | Auto-Program Mode                                        |

|      | 6.10.5  | Auto-Erase Mode                                          |

|      | 6.10.6  | Status Read Mode                                         |

|      | 6.10.7  | Status Polling                                           |

|      | 6.10.8  | Programmer Mode Transition Time                          |

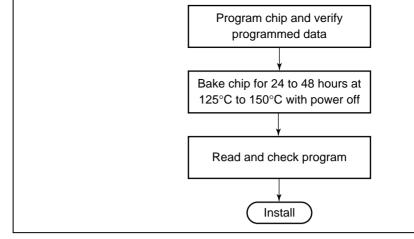

|      | 6.10.9  | Notes on Memory Programming                              |

|      |         |                                                          |

Rev. 6.00 Aug 04, 2006 page xiv of xxxiv

| 0.2 | ron i.  |                                        |

|-----|---------|----------------------------------------|

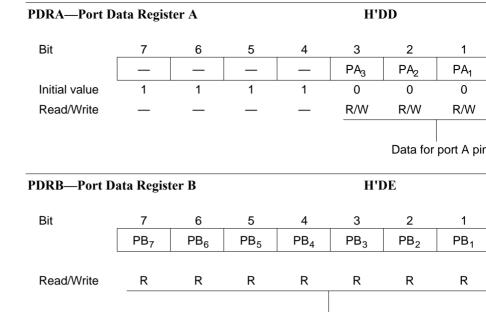

|     | 8.2.1   | Overview                               |

|     | 8.2.2   | Register Configuration and Description |

|     | 8.2.3   | Pin Functions                          |

|     | 8.2.4   | Pin States                             |

|     | 8.2.5   | MOS Input Pull-Up                      |

| 8.3 | Port 3. | 1 1                                    |

|     | 8.3.1   | Overview                               |

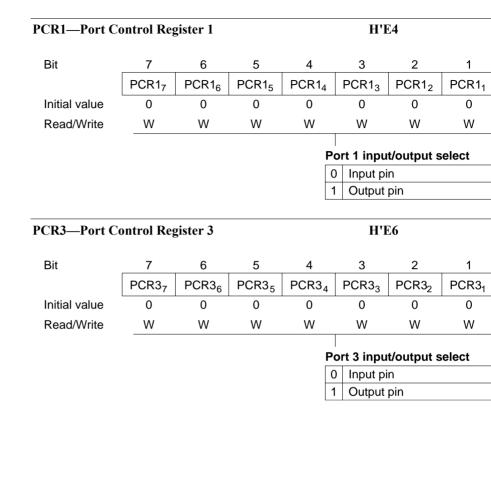

|     | 8.3.2   | Register Configuration and Description |

|     | 8.3.3   | Pin Functions                          |

|     | 8.3.4   | Pin States                             |

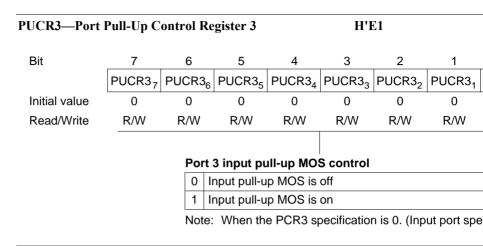

|     | 8.3.5   | MOS Input Pull-Up                      |

| 8.4 |         |                                        |

|     | 8.4.1   | Overview                               |

|     | 8.4.2   | Register Configuration and Description |

|     | 8.4.3   | Pin Functions                          |

|     | 8.4.4   | Pin States                             |

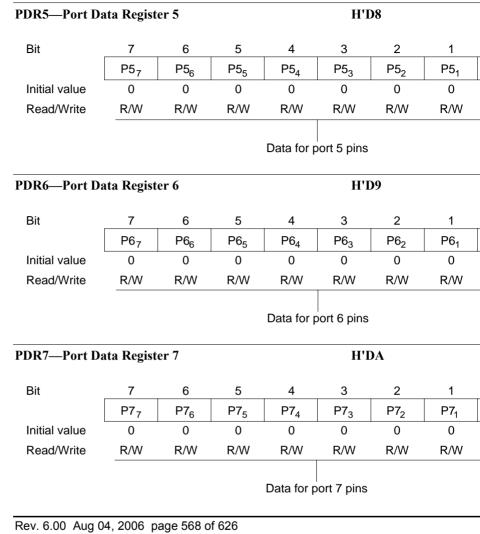

| 8.5 | Port 5. |                                        |

|     | 8.5.1   | Overview                               |

|     | 8.5.2   | Register Configuration and Description |

|     | 8.5.3   | Pin Functions                          |

|     | 8.5.4   | Pin States                             |

|     | 8.5.5   | MOS Input Pull-Up                      |

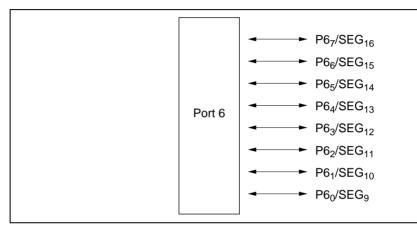

| 8.6 | Port 6. |                                        |

|     | 8.6.1   | Overview                               |

|     | 8.6.2   | Register Configuration and Description |

|     | 8.6.3   | Pin Functions                          |

|     | 8.6.4   | Pin States                             |

|     | 8.6.5   | MOS Input Pull-Up                      |

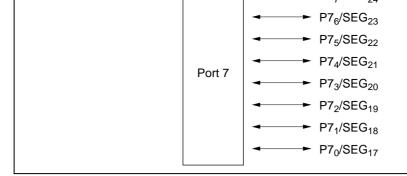

| 8.7 |         |                                        |

|     | 8.7.1   | Overview                               |

|     | 8.7.2   | Register Configuration and Description |

|     |         | 0 0 ···· · · · ·                       |

Rev. 6.00 Aug 04, 2006 pag

|       | 0.9.1   | Overview                                             |

|-------|---------|------------------------------------------------------|

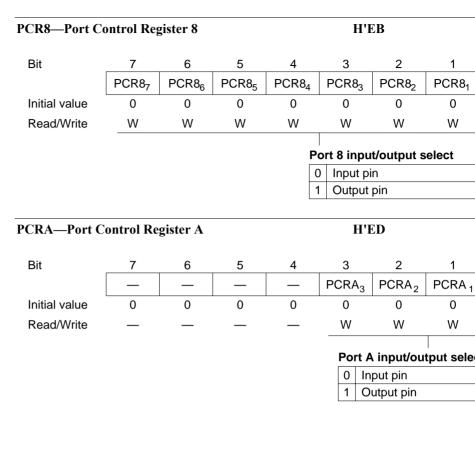

|       | 8.9.2   | Register Configuration and Description               |

|       | 8.9.3   | Pin Functions                                        |

|       | 8.9.4   | Pin States                                           |

| 8.10  | Port B. |                                                      |

|       |         | Overview                                             |

|       |         | Register Configuration and Description               |

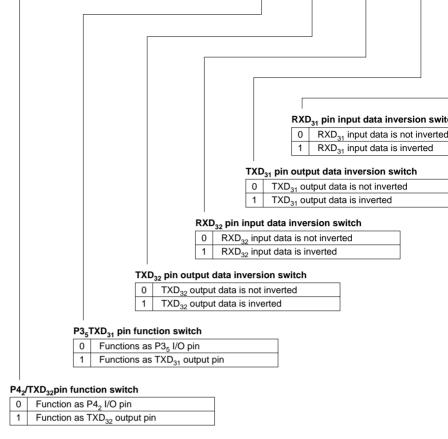

| 8.11  |         | Dutput Data Inversion Function                       |

|       |         | Överview                                             |

|       | 8.11.2  |                                                      |

|       | 8.11.3  | Note on Modification of Serial Port Control Register |

| 8.12  |         | ation Note                                           |

|       | 8.12.1  | The Management of the Un-Use Terminal                |

|       |         | C C                                                  |

| Secti | on 9    | Timers                                               |

| 9.1   | Overvi  | ew                                                   |

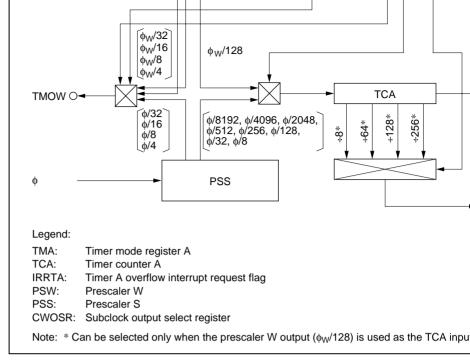

| 9.2   | Timer A | Α                                                    |

|       | 9.2.1   | Overview                                             |

|       | 9.2.2   | Register Descriptions                                |

|       | 9.2.3   | Timer Operation                                      |

|       | 9.2.4   | Timer A Operation States                             |

|       | 9.2.5   | Application Note                                     |

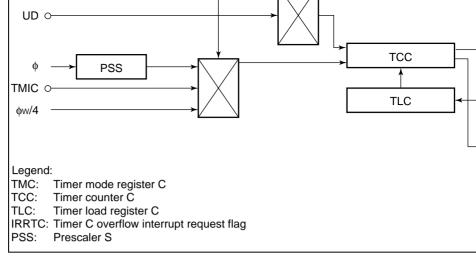

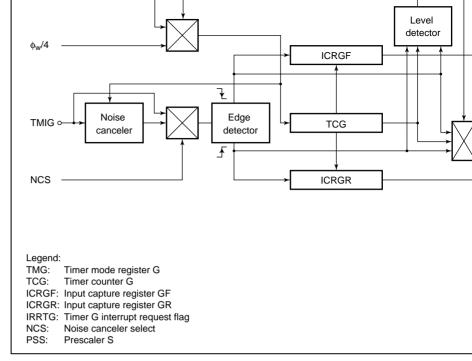

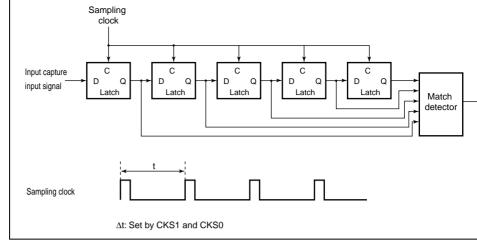

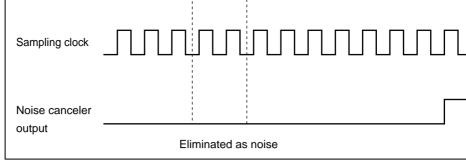

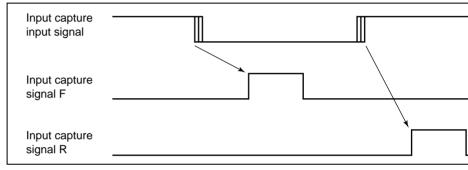

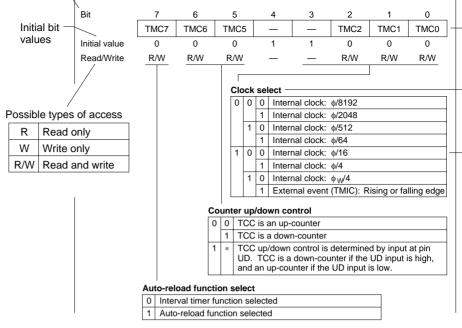

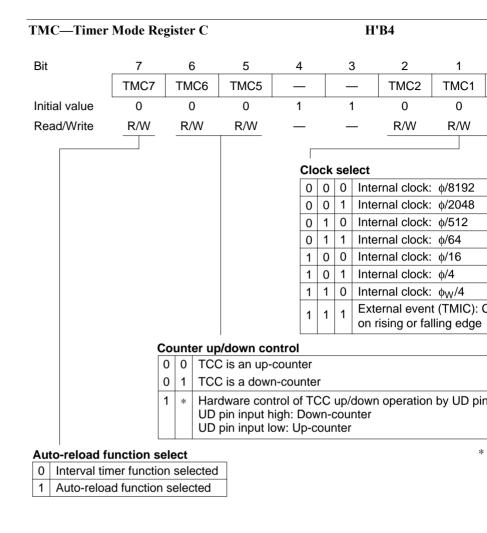

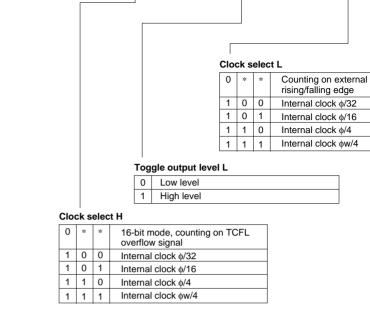

| 9.3   | Timer ( | g                                                    |

|       | 9.3.1   | Overview                                             |

|       | 9.3.2   | Register Descriptions                                |

|       | 9.3.3   | Timer Operation                                      |

|       | 9.3.4   | Timer C Operation States                             |

|       | 9.3.5   | Usage Note                                           |

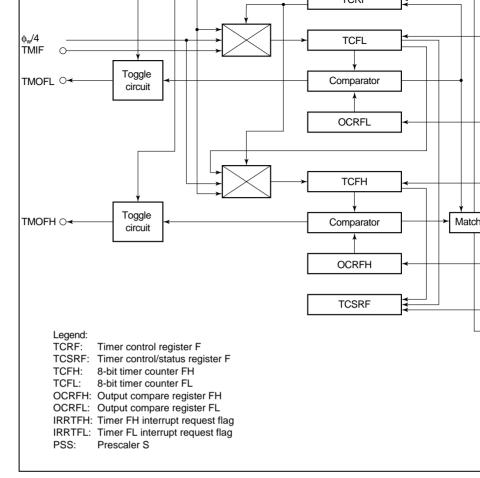

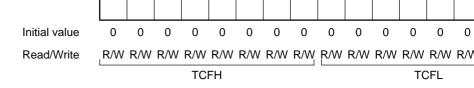

| 9.4   | Timer l | F                                                    |

|       | 9.4.1   | Overview                                             |

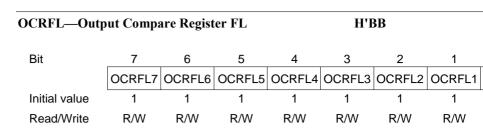

|       | 9.4.2   | Register Descriptions                                |

|       | 9.4.3   | CPU Interface                                        |

|       |         |                                                      |

Rev. 6.00 Aug 04, 2006 page xvi of xxxiv

|       | 9.3.0   | I liner & Application Example              |

|-------|---------|--------------------------------------------|

| 9.6   | Watche  | log Timer                                  |

|       | 9.6.1   | Overview                                   |

|       | 9.6.2   | Register Descriptions                      |

|       | 9.6.3   | Timer Operation                            |

|       | 9.6.4   | Watchdog Timer Operation States            |

| 9.7   | Asynch  | nronous Event Counter (AEC)                |

|       | 9.7.1   | Overview                                   |

|       | 9.7.2   | Register Descriptions                      |

|       | 9.7.3   | Operation                                  |

|       | 9.7.4   | Asynchronous Event Counter Operation Modes |

|       | 9.7.5   | Application Notes                          |

|       |         |                                            |

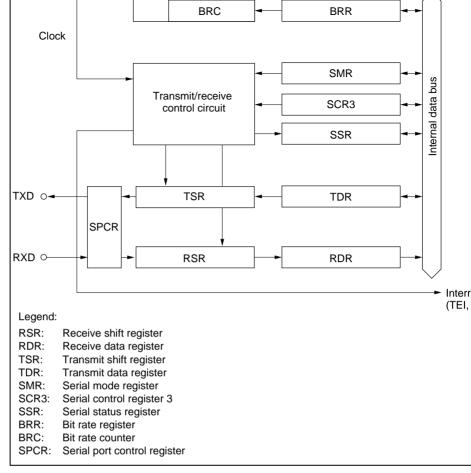

| Secti | ion 10  | Serial Communication Interface             |

| 10.1  | Overvi  | ew                                         |

|       | 10.1.1  | Features                                   |

|       | 10.1.2  | Block Diagram                              |

|       | 10.1.3  | Pin Configuration                          |

|       |         | Register Configuration                     |

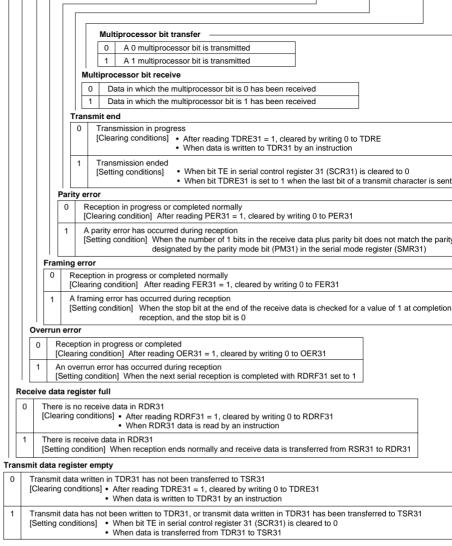

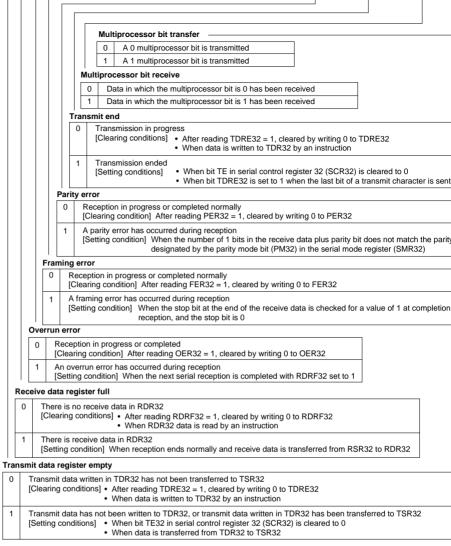

| 10.2  |         | r Descriptions                             |

|       |         | Receive Shift Register (RSR)               |

|       | 10.2.2  | Receive Data Register (RDR)                |

|       | 10.2.3  | Transmit Shift Register (TSR)              |

|       | 10.2.4  | $\mathcal{O}$                              |

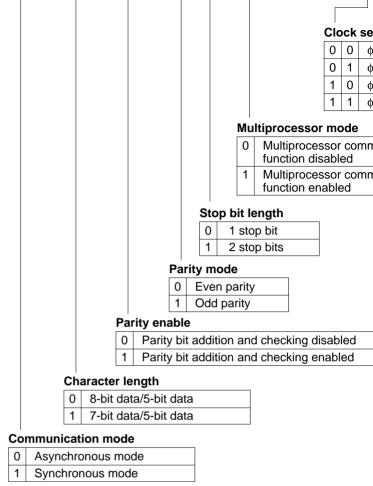

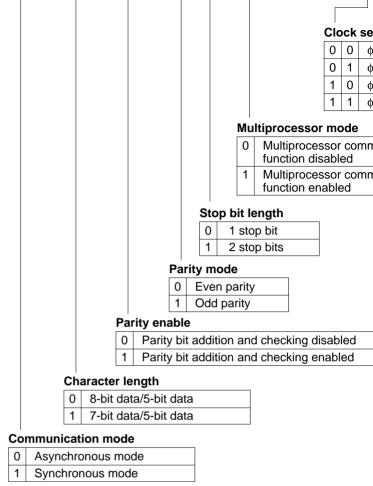

|       | 10.2.5  | Serial Mode Register (SMR)                 |

|       | 10.2.6  | 8                                          |

|       | 10.2.7  | e ( )                                      |

|       | 10.2.8  | 8                                          |

|       | 10.2.9  |                                            |

|       | 10.2.10 | Serial Port Control Register (SPCR)        |

| 10.3  | -       | ion                                        |

|       | 10.3.1  | Overview                                   |

Rev. 6.00 Aug 04, 2006 pag

|                        | 11.1.1  | reatures                                          |

|------------------------|---------|---------------------------------------------------|

|                        | 11.1.2  | Block Diagram                                     |

|                        | 11.1.3  | Pin Configuration                                 |

|                        |         | Register Configuration                            |

| 11.2                   |         | er Descriptions                                   |

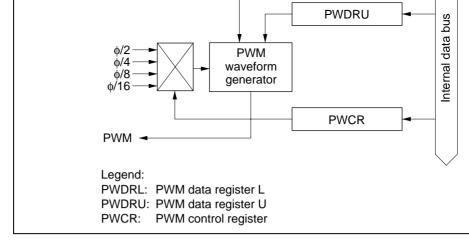

|                        | 11.2.1  | PWM Control Register (PWCR)                       |

|                        |         | PWM Data Registers U and L (PWDRU, PWDRL)         |

|                        |         | Clock Stop Register 2 (CKSTPR2)                   |

| 11.3                   | Operati | ion                                               |

|                        | 11.3.1  | Operation                                         |

|                        |         | PWM Operation Modes                               |

|                        |         |                                                   |

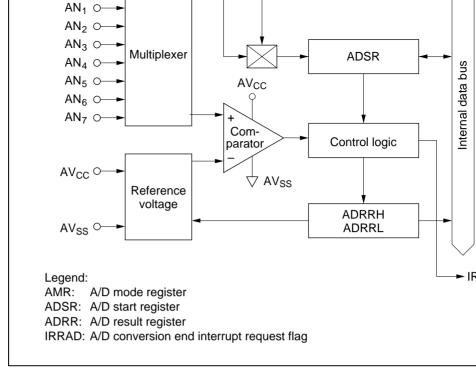

| Sect                   | ion 12  | A/D Converter                                     |

| 12.1                   | Overvie | ew                                                |

|                        | 12.1.1  | Features                                          |

|                        | 12.1.2  | Block Diagram                                     |

|                        | 12.1.3  | Pin Configuration                                 |

|                        | 12.1.4  | Register Configuration                            |

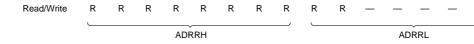

| 12.2                   | Registe | er Descriptions                                   |

|                        |         | A/D Result Registers (ADRRH, ADRRL)               |

|                        | 12.2.2  | A/D Mode Register (AMR)                           |

|                        | 12.2.3  | A/D Start Register (ADSR)                         |

|                        | 12.2.4  | Clock Stop Register 1 (CKSTPR1)                   |

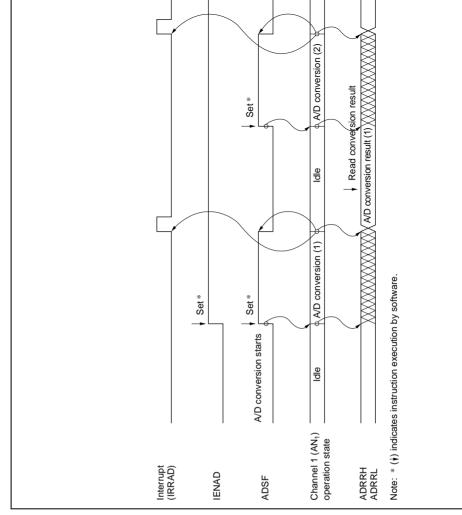

| 12.3                   |         | ion                                               |

|                        | 12.3.1  | A/D Conversion Operation                          |

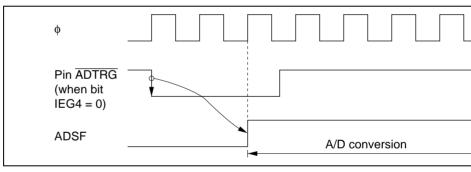

|                        | 12.3.2  | Start of A/D Conversion by External Trigger Input |

|                        |         | A/D Converter Operation Modes                     |

| 12.4                   | Interru | pts                                               |

| 12.5                   | Typical | l Use                                             |

| 12.6 Application Notes |         |                                                   |

|                        | 12.6.1  | Application Notes                                 |

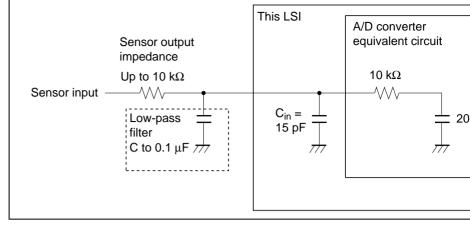

|                        | 12.6.2  | Permissible Signal Source Impedance               |

|                        |         |                                                   |

Rev. 6.00 Aug 04, 2006 page xviii of xxxiv

|            | 13.2  | Registe                                              |                                                                |  |  |  |  |

|------------|-------|------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

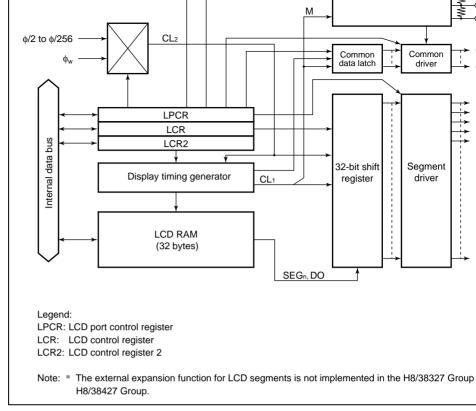

|            |       | 13.2.1                                               | LCD Port Control Register (LPCR)                               |  |  |  |  |

|            |       | 13.2.2                                               | LCD Control Register (LCR)                                     |  |  |  |  |

|            |       | 13.2.3                                               | LCD Control Register 2 (LCR2)                                  |  |  |  |  |

|            |       |                                                      | Clock Stop Register 2 (CKSTPR2)                                |  |  |  |  |

|            | 13.3  | Operati                                              | on                                                             |  |  |  |  |

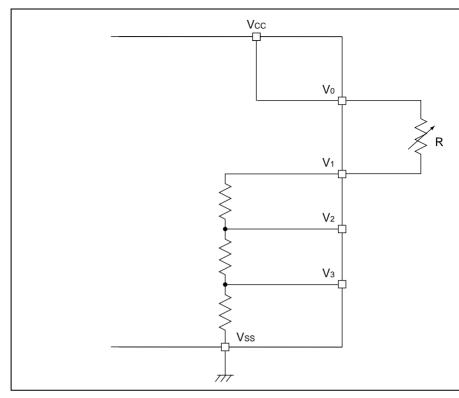

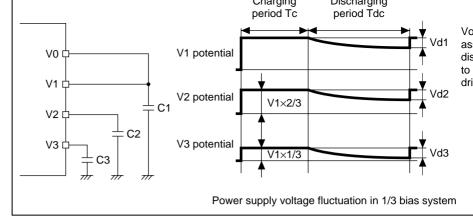

|            |       | 13.3.1                                               | Settings Up to LCD Display                                     |  |  |  |  |

|            |       | 13.3.2                                               | Relationship between LCD RAM and Display                       |  |  |  |  |

|            |       | 13.3.3                                               | Luminance Adjustment Function (V <sub>0</sub> Pin)             |  |  |  |  |

|            |       | 13.3.4                                               | Low-Power-Consumption LCD Drive System                         |  |  |  |  |

|            |       | 13.3.5                                               | Operation in Power-Down Modes                                  |  |  |  |  |

|            |       | 13.3.6                                               | Boosting the LCD Drive Power Supply                            |  |  |  |  |

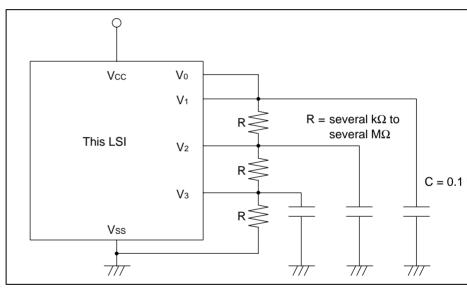

|            |       | 13.3.7                                               | Connection to HD66100                                          |  |  |  |  |

|            |       |                                                      |                                                                |  |  |  |  |

| Section 14 |       | on 14                                                | Power Supply Circuit                                           |  |  |  |  |

|            | 14.1  | 4.1 Overview                                         |                                                                |  |  |  |  |

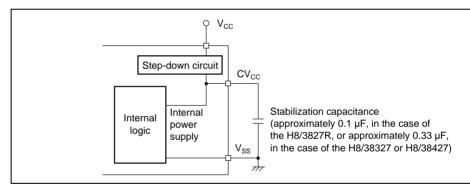

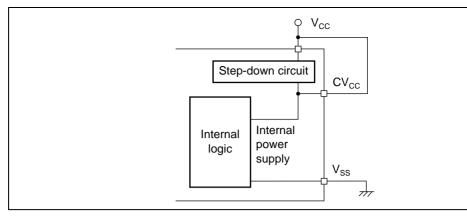

|            | 14.2  | 2 When Using Internal Power Supply Step-Down Circuit |                                                                |  |  |  |  |

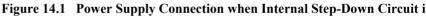

|            | 14.3  | When I                                               | Not Using Internal Power Supply Step-Down Circuit              |  |  |  |  |

|            | 14.4  |                                                      | 7S Group                                                       |  |  |  |  |

| 14.5 Notes |       | Notes of                                             | on Switching from the H8/3827R to the H8/38327 or H8/38427     |  |  |  |  |

|            |       |                                                      |                                                                |  |  |  |  |

|            | Secti |                                                      | Electrical Characteristics                                     |  |  |  |  |

|            | 15.1  |                                                      | 7R Group Absolute Maximum Ratings (Regular Specifications)     |  |  |  |  |

|            | 15.2  |                                                      | 7R Group Electrical Characteristics (Regular Specifications)   |  |  |  |  |

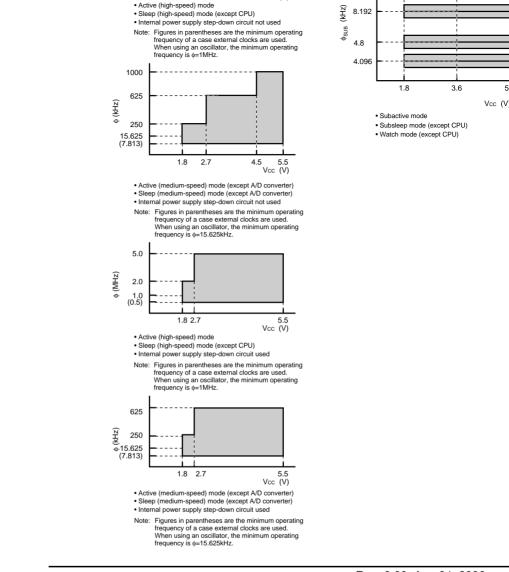

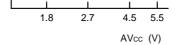

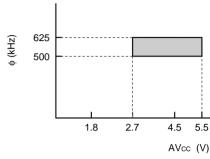

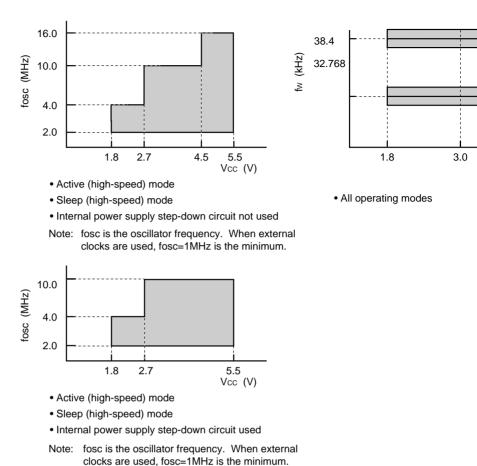

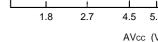

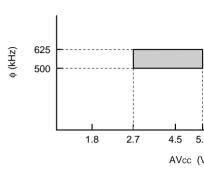

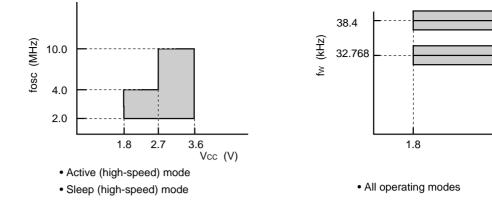

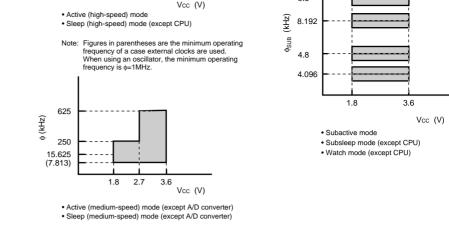

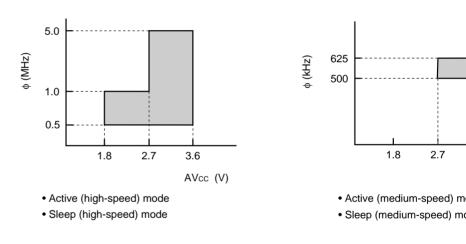

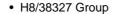

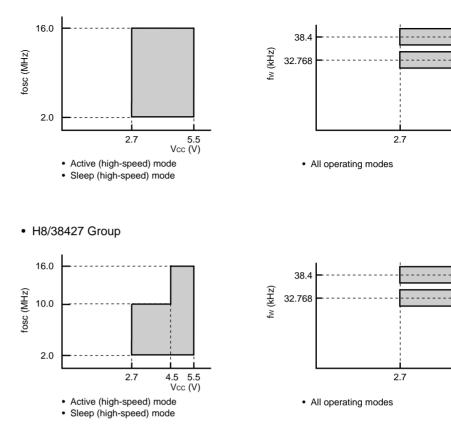

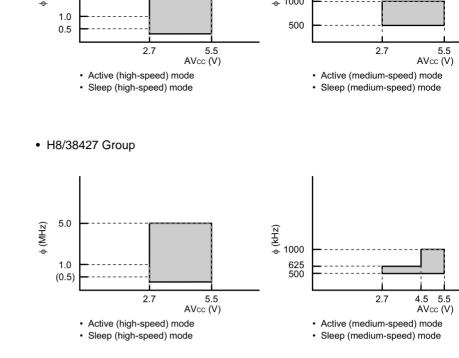

|            |       |                                                      | Power Supply Voltage and Operating Range                       |  |  |  |  |

|            |       |                                                      | DC Characteristics                                             |  |  |  |  |

|            |       |                                                      | AC Characteristics                                             |  |  |  |  |

| 15.2.4     |       |                                                      | A/D Converter Characteristics                                  |  |  |  |  |

|            |       |                                                      | LCD Characteristics                                            |  |  |  |  |

|            | 15.3  |                                                      | 7R Group Absolute Maximum Ratings (Wide-Range Specification)   |  |  |  |  |

|            | 15.4  |                                                      | 7R Group Electrical Characteristics (Wide-Range Specification) |  |  |  |  |

|            |       | 15.4.1                                               | Power Supply Voltage and Operating Range                       |  |  |  |  |

|            |       |                                                      |                                                                |  |  |  |  |

Rev. 6.00 Aug 04, 2006 pag

|       | 13.0.3                                                        |                                                          |  |  |  |  |

|-------|---------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

|       | 15.6.4                                                        | A/D Converter Characteristics                            |  |  |  |  |

|       | 15.6.5                                                        | LCD Characteristics                                      |  |  |  |  |

| 15.7  | Absolute Maximum Ratings of H8/38327 Group and H8/38427 Group |                                                          |  |  |  |  |

| 15.8  |                                                               | cal Characteristics of H8/38327 Group and H8/38427 Group |  |  |  |  |

|       |                                                               | Power Supply Voltage and Operating Ranges                |  |  |  |  |

|       |                                                               | DC Characteristics                                       |  |  |  |  |

|       |                                                               | AC Characteristics                                       |  |  |  |  |

|       |                                                               | A/D Converter Characteristics                            |  |  |  |  |

|       |                                                               | LCD Characteristics                                      |  |  |  |  |

|       |                                                               | Flash Memory Characteristics                             |  |  |  |  |

| 15.9  |                                                               | on Timing                                                |  |  |  |  |

| 15.10 |                                                               | Load Circuit                                             |  |  |  |  |

|       |                                                               | tor                                                      |  |  |  |  |

|       |                                                               | Note                                                     |  |  |  |  |

|       | •                                                             |                                                          |  |  |  |  |

| Appe  | endix A                                                       | CPU Instruction Set                                      |  |  |  |  |

| A.1   |                                                               | tions                                                    |  |  |  |  |

| A.2   | Operati                                                       | on Code Map                                              |  |  |  |  |

| A.3   | Numbe                                                         | r of Execution States                                    |  |  |  |  |

|       |                                                               |                                                          |  |  |  |  |

| Appe  | endix E                                                       | Internal I/O Registers                                   |  |  |  |  |

| B.1   |                                                               | ses                                                      |  |  |  |  |

| B.2   |                                                               | ns                                                       |  |  |  |  |

|       |                                                               |                                                          |  |  |  |  |

| Appe  | endix C                                                       | I/O Port Block Diagrams                                  |  |  |  |  |

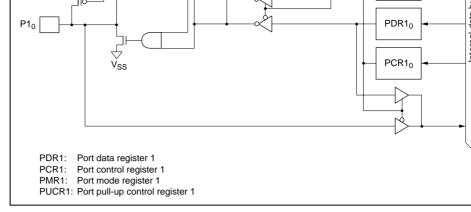

| C.1   | Block I                                                       | Diagrams of Port 1                                       |  |  |  |  |

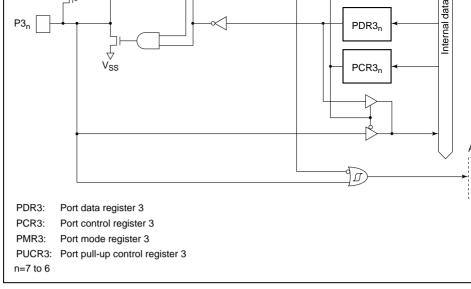

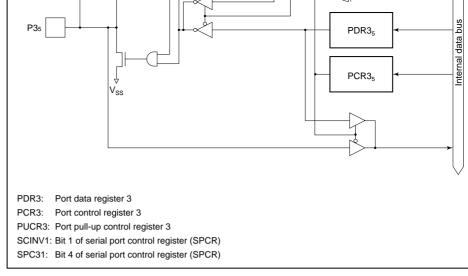

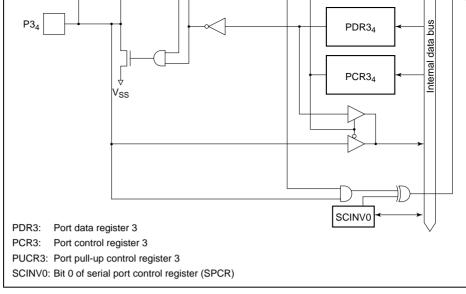

| C.2   |                                                               | Diagrams of Port 3                                       |  |  |  |  |

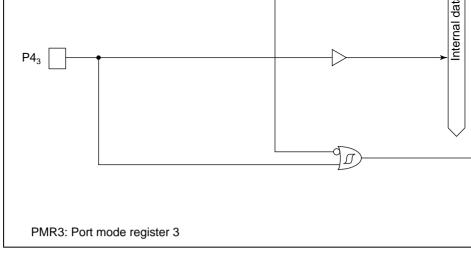

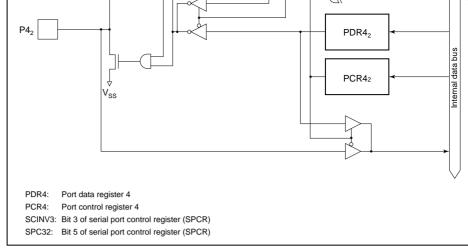

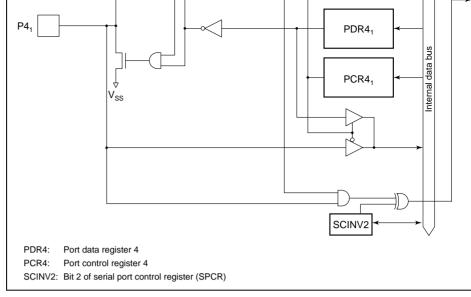

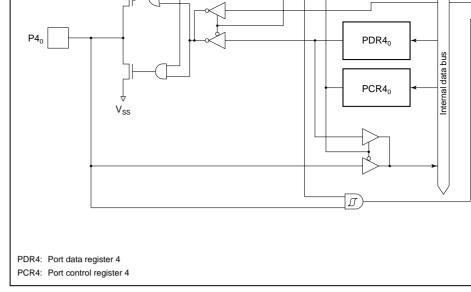

| C.3   | Block I                                                       | Diagrams of Port 4                                       |  |  |  |  |

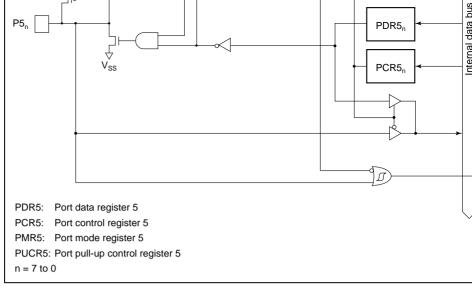

| C.4   |                                                               | Diagram of Port 5                                        |  |  |  |  |

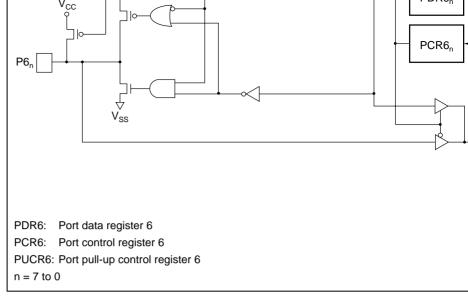

| C.5   |                                                               | Diagram of Port 6                                        |  |  |  |  |

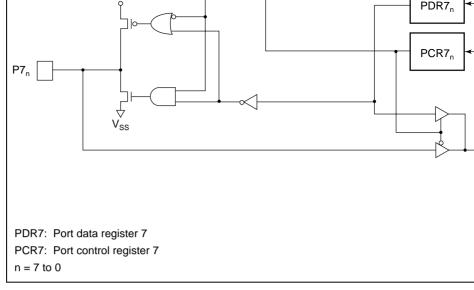

| C.6   |                                                               | Diagram of Port 7                                        |  |  |  |  |

| •     |                                                               | 6                                                        |  |  |  |  |

Rev. 6.00 Aug 04, 2006 page xx of xxxiv

| Appendix F | rackage Dimensions          |

|------------|-----------------------------|

| Appendix G | Specifications of Chip Form |

| Annendix H | Form of Bonding Pads        |

|            | Torin of Boliding Lads      |

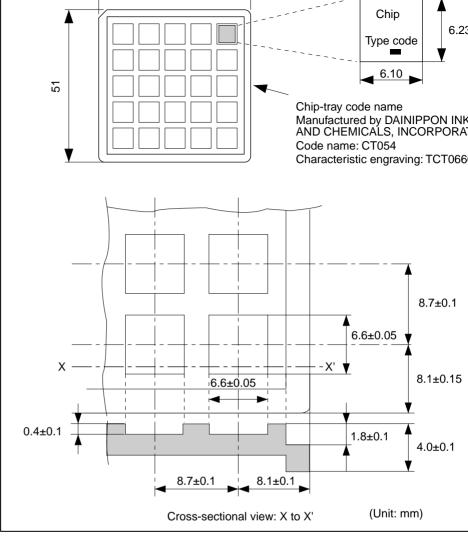

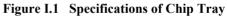

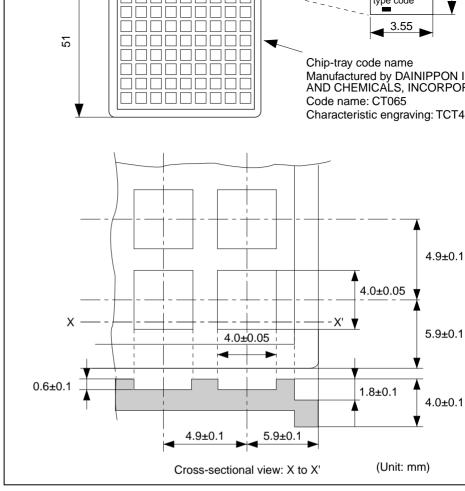

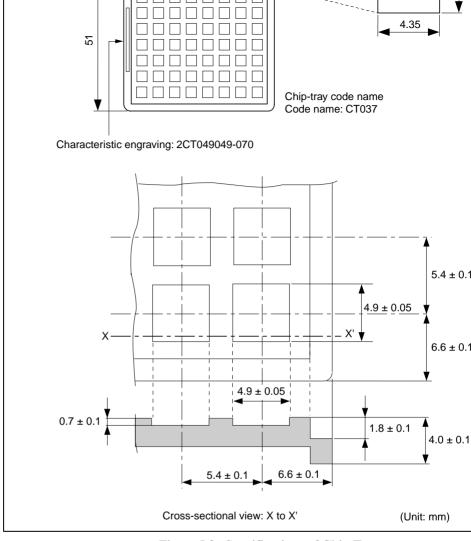

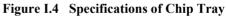

| Appendix I | Specifications of Chip Tray |

Rev. 6.00 Aug 04, 2006 pag

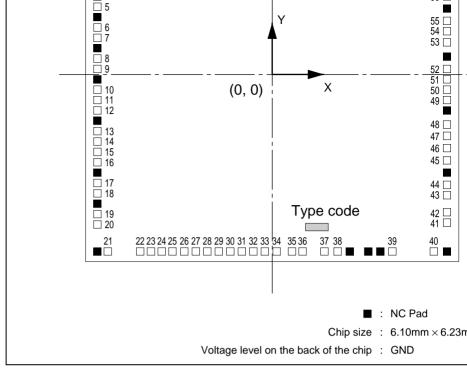

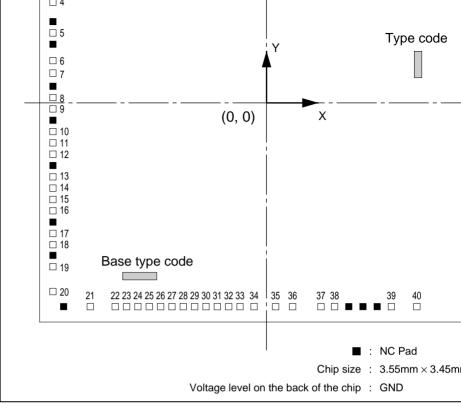

| Figure 1.4 | Bonding Pad Location Diagram of H8/3827R Group (Mask ROM Vers |

|------------|---------------------------------------------------------------|

|            | (Top View)                                                    |

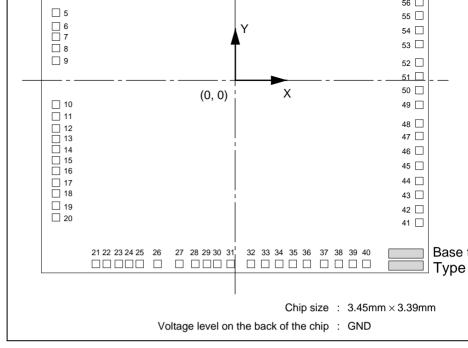

| Figure 1.5 | Bonding Pad Location Diagram of H8/3827S Group (Mask ROM Vers |

|            | (Top View)                                                    |

| Figure 1.6 | Bonding Pad Location Diagram of HCD64F38327 and HCD64F38427   |

|            | (Top View)                                                    |

| Figure 1.7 | Bonding Pad Location Diagram of H8/38327 Group (Mask ROM Vers |

|            | and H8/38427 Group (Mask ROM Version) (Top View)              |

|            |                                                               |

#### Section 2 CPU

| Figure 2.1     | CPU Registers                                           |

|----------------|---------------------------------------------------------|

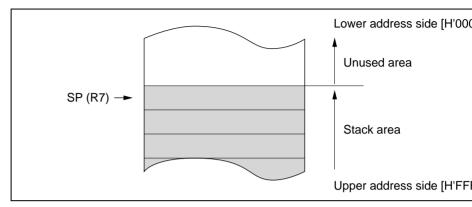

| Figure 2.2     | Stack Pointer                                           |

| Figure 2.3     | Register Data Formats                                   |

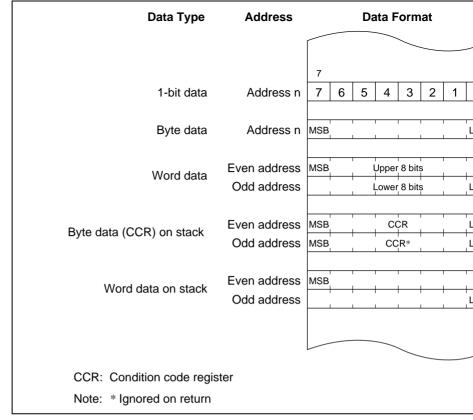

| Figure 2.4     | Memory Data Formats                                     |

| Figure 2.5     | Data Transfer Instruction Codes                         |

| Figure 2.6     | Arithmetic, Logic, and Shift Instruction Codes          |

| Figure 2.7     | Bit Manipulation Instruction Codes                      |

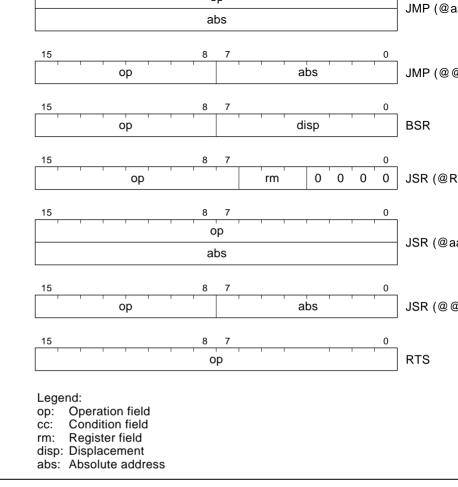

| Figure 2.8     | Branching Instruction Codes                             |

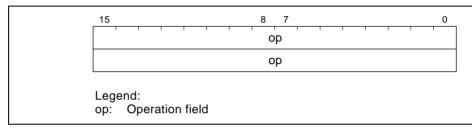

| Figure 2.9     | System Control Instruction Codes                        |

| Figure 2.10    | Block Data Transfer Instruction Code                    |

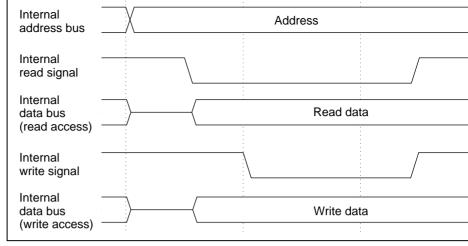

| Figure 2.11    | On-Chip Memory Access Cycle                             |

| Figure 2.12    | On-Chip Peripheral Module Access Cycle (2-State Access) |

| Figure 2.13    | On-Chip Peripheral Module Access Cycle (3-State Access) |

| Figure 2.14    | CPU Operation States                                    |

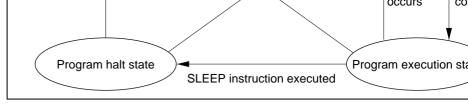

| Figure 2.15    | State Transitions                                       |

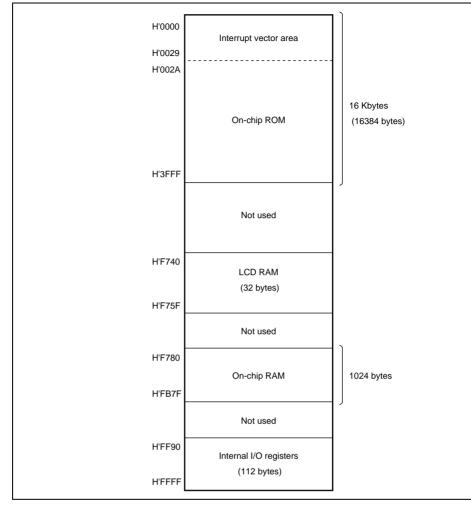

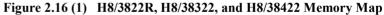

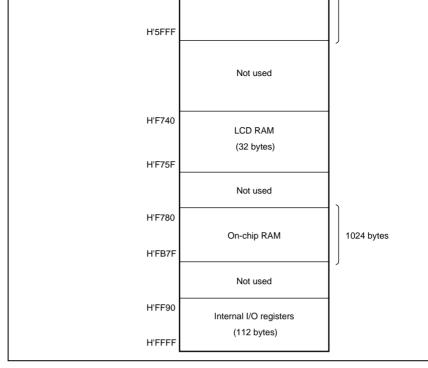

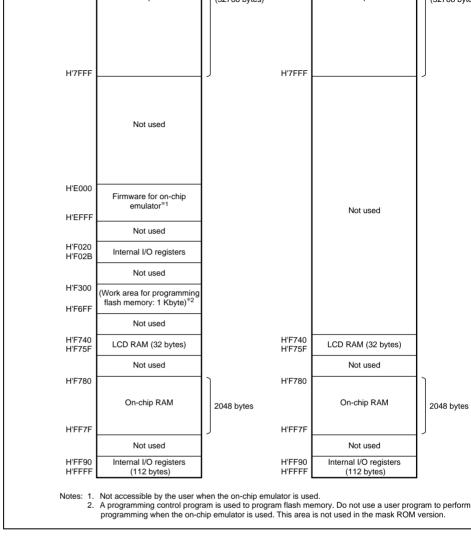

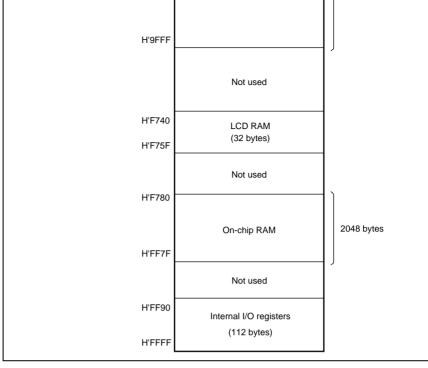

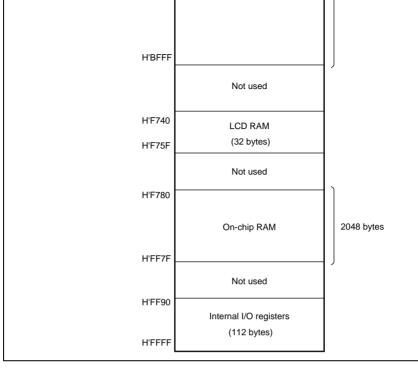

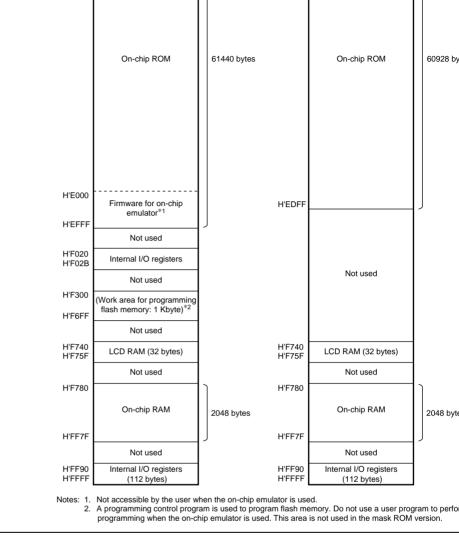

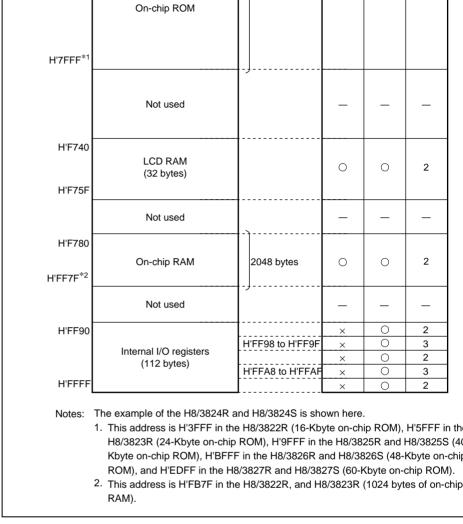

| Figure 2.16(1) | H8/3822R, H8/38322, and H8/38422 Memory Map             |

| Figure 2.16(2) | H8/3823R, H8/38323, and H8/38423 Memory Map             |

| Figure 2.16(3) | H8/3824R, H8/3824S, H8/38324, and H8/38424 Memory Map   |

| Figure 2.16(4) | H8/3825R, H8/3825S, H8/38325, and H8/38425 Memory Map   |

| Figure 2.16(5) | H8/3826R, H8/3826S, H8/38326, and H8/38426 Memory Map   |

| Figure 2.16(6) | H8/3827R, H8/3827S, H8/38327, and H8/38427 Memory Map   |

|                |                                                         |

Rev. 6.00 Aug 04, 2006 page xxii of xxxiv

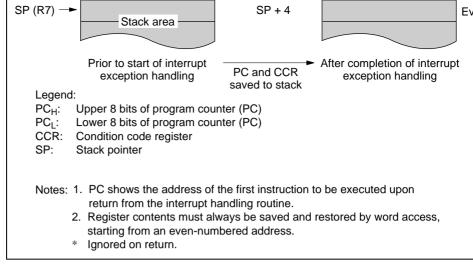

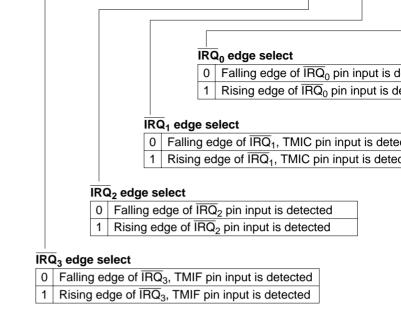

| Figure 5.4     | Stack State after Completion of Interrupt Exception Handling       |  |  |  |  |

|----------------|--------------------------------------------------------------------|--|--|--|--|

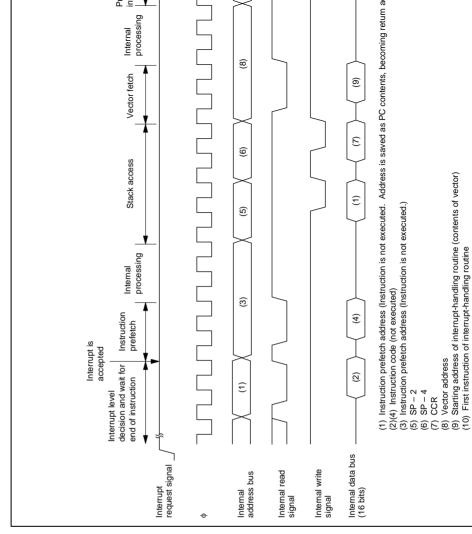

| Figure 3.5     | Interrupt Sequence                                                 |  |  |  |  |

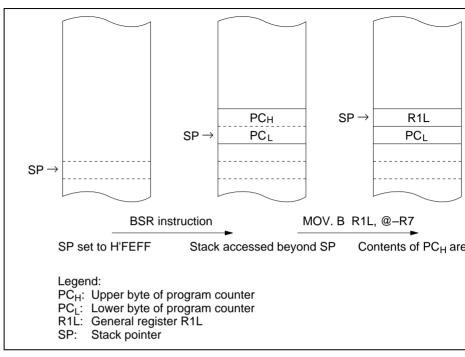

| Figure 3.6     | Operation when Odd Address is Set in SP                            |  |  |  |  |

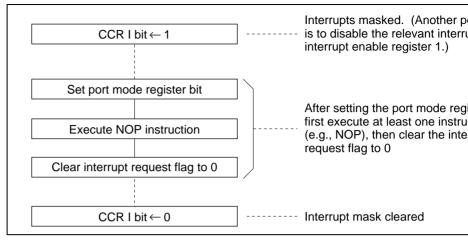

| Figure 3.7     | Port Mode Register Setting and Interrupt Request Flag Clearing Pro |  |  |  |  |

|                |                                                                    |  |  |  |  |

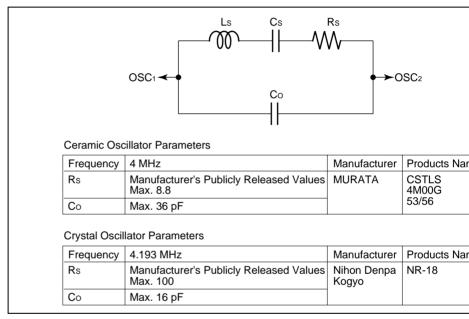

| Section 4 Clo  | ock Pulse Generators                                               |  |  |  |  |

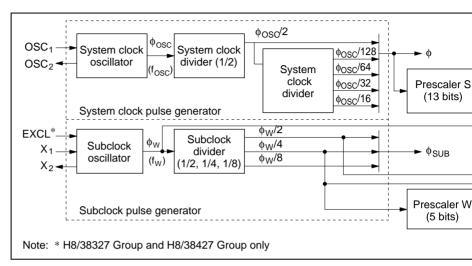

| Figure 4.1     | Block Diagram of Clock Pulse Generators                            |  |  |  |  |

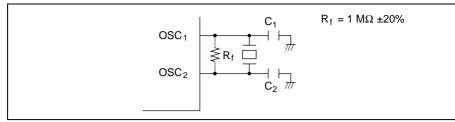

| Figure 4.2     | Typical Connection to Crystal Oscillator                           |  |  |  |  |

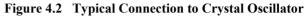

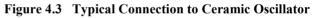

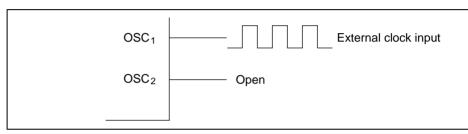

| Figure 4.3     | Typical Connection to Ceramic Oscillator                           |  |  |  |  |

| Figure 4.4     | Board Design of Oscillator Circuit                                 |  |  |  |  |

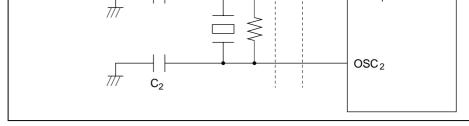

| Figure 4.5     | External Clock Input (Example)                                     |  |  |  |  |

| Figure 4.6     | Typical Connection to 32.768 kHz/38.4 kHz Crystal Oscillator (Subc |  |  |  |  |

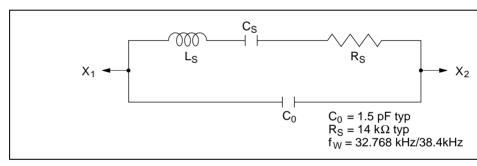

| Figure 4.7     | Equivalent Circuit of 32.768 kHz/38.4 kHz Crystal Oscillator       |  |  |  |  |

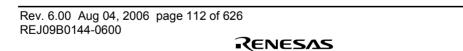

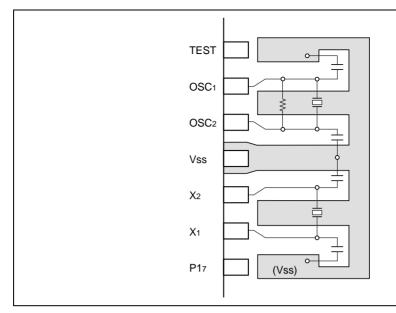

| Figure 4.8     | Pin Connection when not Using Subclock                             |  |  |  |  |

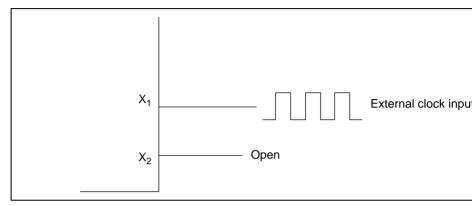

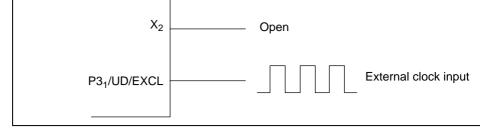

| Figure 4.9 (a) | Pin Connection when Inputting External Clock                       |  |  |  |  |

|                |                                                                    |  |  |  |  |

| 0              | 1 0                                                                 |

|----------------|---------------------------------------------------------------------|

| Figure 4.9 (b) | Pin Connection when Inputting External Clock                        |

|                | (H8/38327 Group and H8/38427 Group)                                 |

| Figure 4.10    | Example of Crystal and Ceramic Oscillator Element Arrangement       |

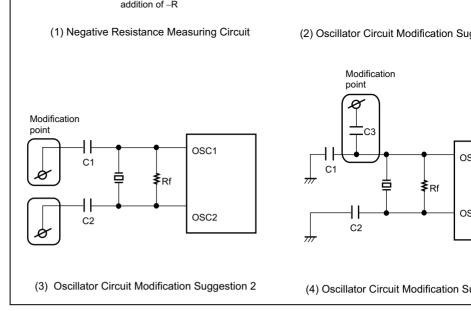

| Figure 4.11    | Negative Resistance Measurement and Circuit Modification Suggestion |

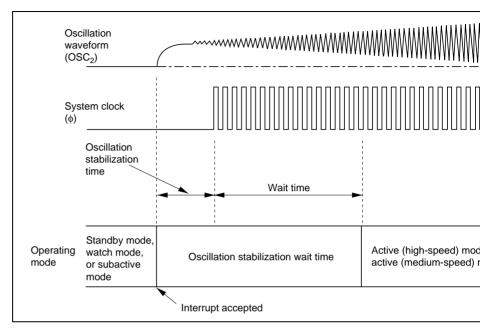

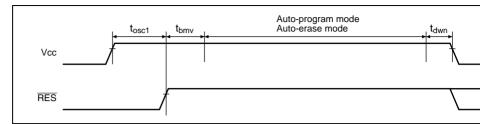

Figure 4.12 Oscillation Stabilization Wait Time.....

#### Section 5 Power-Down Modes

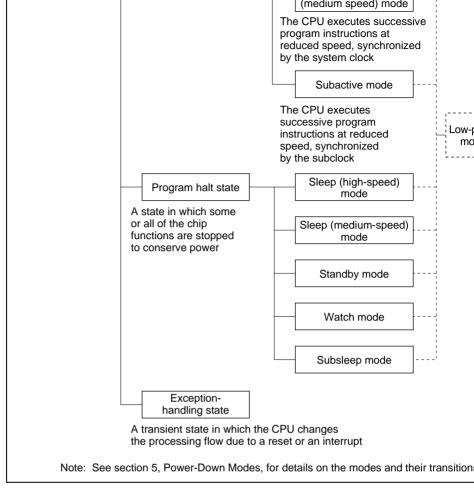

| Figure 5.1 | Mode Transition Diagram                                        |

|------------|----------------------------------------------------------------|

| e          | Standby Mode Transition and Pin States                         |

| Figure 5.3 | External Input Signal Capture when Signal Changes before/after |

| -          | Standby Mode or Watch Mode                                     |

#### Section 6 ROM

| Figure 6.1 | ROM Block Diagram (H8/3824R, H8/3824S, H8/38324, and H8/384 |

|------------|-------------------------------------------------------------|

| Figure 6.2 | Socket Adapter Pin Correspondence (with HN27C101)           |

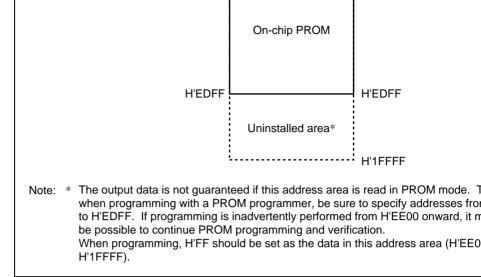

| Figure 6.3 | H8/3827R Memory Map in PROM Mode                            |

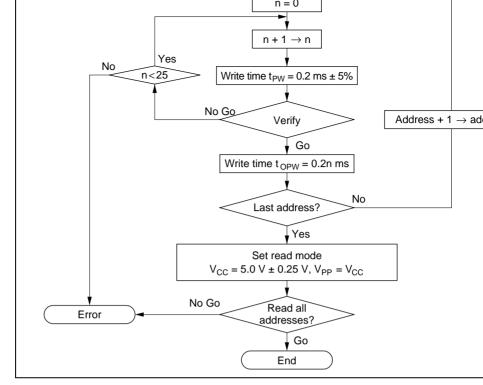

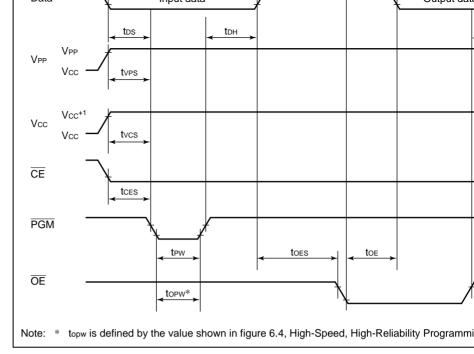

| Figure 6.4 | High-Speed, High-Reliability Programming Flow Chart         |

Rev. 6.00 Aug 04, 2006 page

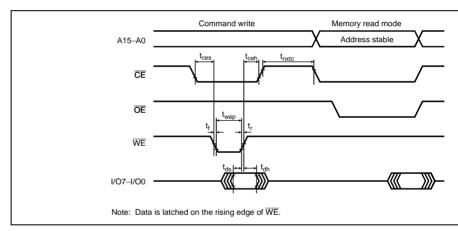

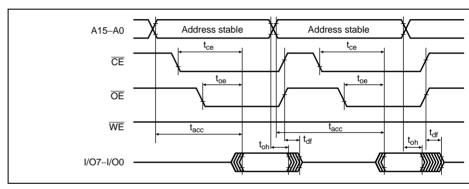

| rigule 0.15 | Timing waveforms for Memory Read after Memory write                                  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------|--|--|--|--|

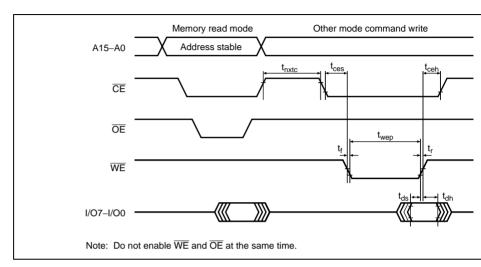

| Figure 6.14 | Timing Waveforms in Transition from Memory Read Mode to Anothe                       |  |  |  |  |

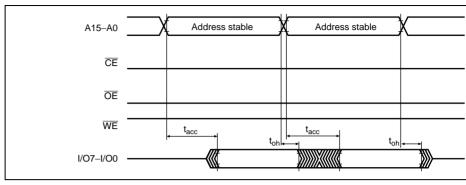

| Figure 6.15 | $\overline{\text{CE}}$ and $\overline{\text{OE}}$ Enable State Read Timing Waveforms |  |  |  |  |

| Figure 6.16 | $\overline{\text{CE}}$ and $\overline{\text{OE}}$ Clock System Read Timing Waveforms |  |  |  |  |

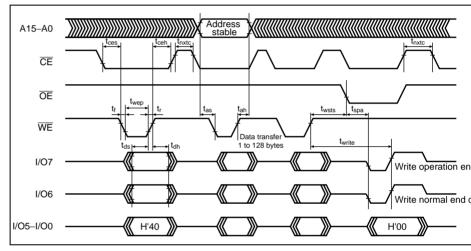

| Figure 6.17 | Auto-Program Mode Timing Waveforms                                                   |  |  |  |  |

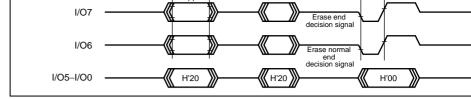

| Figure 6.18 | Auto-Erase Mode Timing Waveforms                                                     |  |  |  |  |

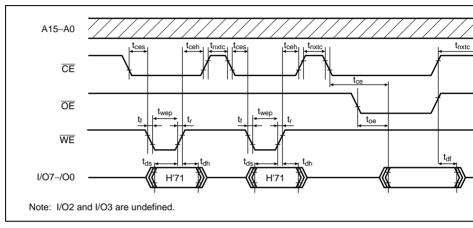

| Figure 6.19 | Status Read Mode Timing Waveforms                                                    |  |  |  |  |

| Figure 6.20 | Oscillation Stabilization Time, Boot Program Transfer Time,                          |  |  |  |  |

|             | and Power-Down Sequence                                                              |  |  |  |  |

|             |                                                                                      |  |  |  |  |

#### Section 7 RAM

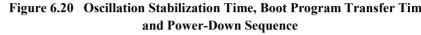

| Figure 7.1 | RAM Block Diagram ( | H8/3824R, | H8/3824S, | H8/38324, | and H8/38424 |

|------------|---------------------|-----------|-----------|-----------|--------------|

|            |                     |           |           |           |              |

#### Section 8 I/O Ports

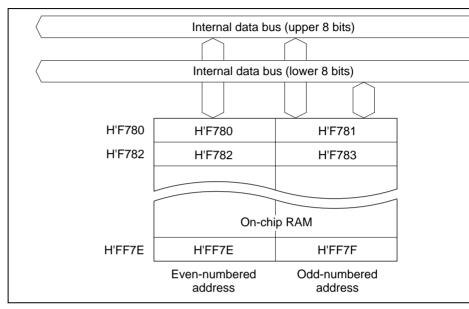

| Figure 8.1  | Port 1 Pin Configuration             |

|-------------|--------------------------------------|

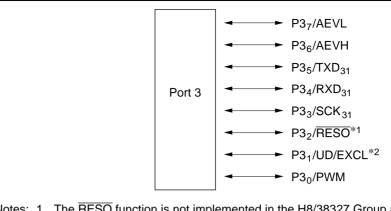

| Figure 8.2  | Port 3 Pin Configuration             |

| Figure 8.3  | Port 4 Pin Configuration             |

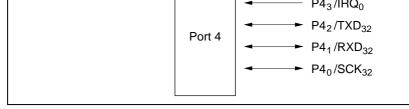

| Figure 8.4  | Port 5 Pin Configuration             |

| Figure 8.5  | Port 6 Pin Configuration             |

| Figure 8.6  | Port 7 Pin Configuration             |

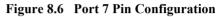

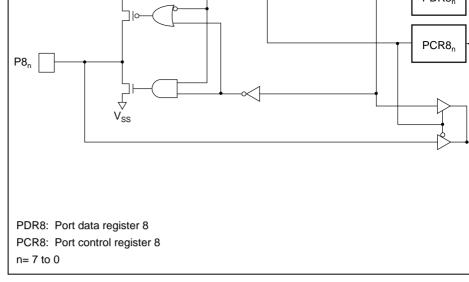

| Figure 8.7  | Port 8 Pin Configuration             |

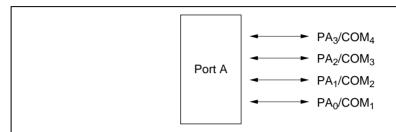

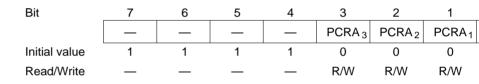

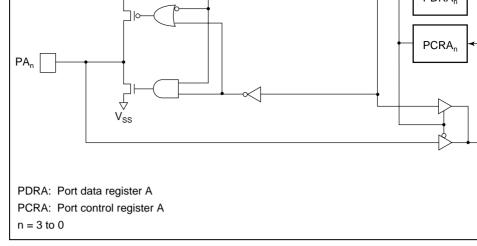

| Figure 8.8  | Port A Pin Configuration             |

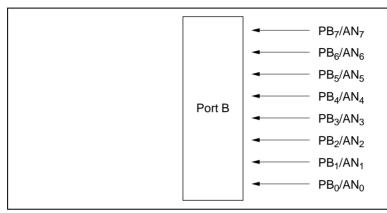

| Figure 8.9  | Port B Pin Configuration             |

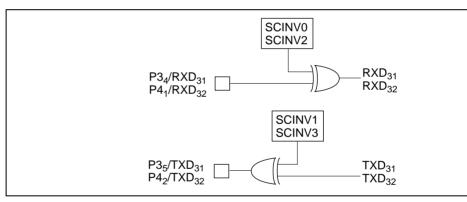

| Figure 8.10 | Input/Output Data Inversion Function |

| 0           | 1 1                                  |

#### Section 9 Timers

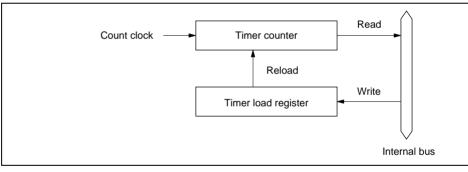

| Figure 9.1 | Block Diagram of Timer A                    |

|------------|---------------------------------------------|

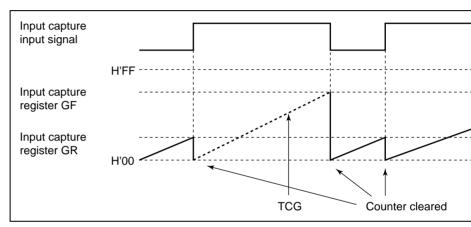

| Figure 9.2 | Block Diagram of Timer C                    |

| Figure 9.3 | Block Diagram of Timer F                    |

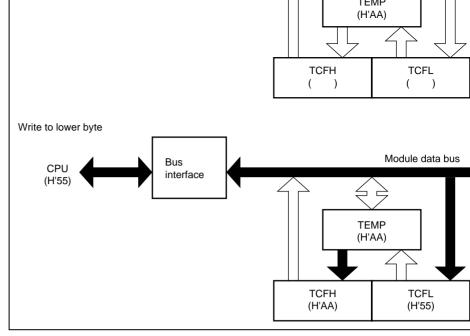

| Figure 9.4 | Write Access to TCR (CPU $\rightarrow$ TCF) |

| Figure 9.5 | Read Access to TCF (TCF $\rightarrow$ CPU)  |

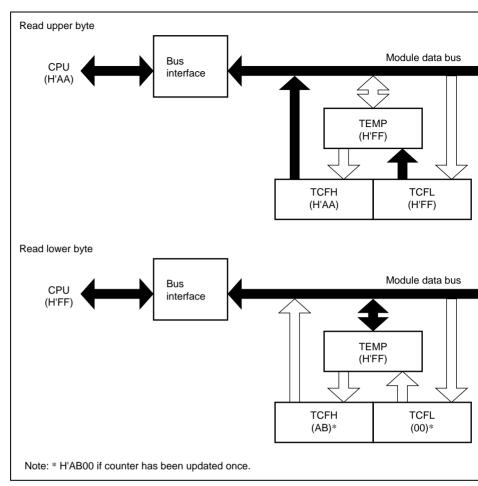

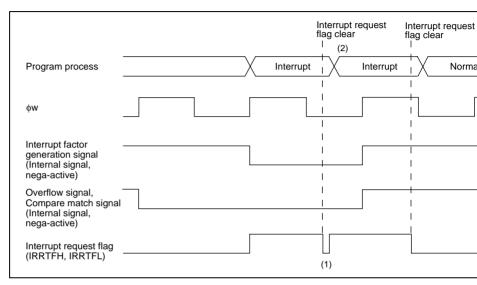

| e          | TMOFH/TMOFL Output Timing                   |

|            | 8                                           |

Rev. 6.00 Aug 04, 2006 page xxiv of xxxiv

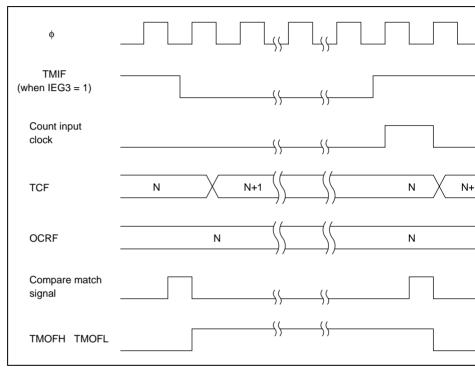

| Port Mode Register Manipulation and Interrupt Enable Flag Clearing |

|--------------------------------------------------------------------|

| Procedure                                                          |

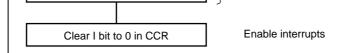

| Timer G Application Example                                        |

| Block Diagram of Watchdog Timer                                    |

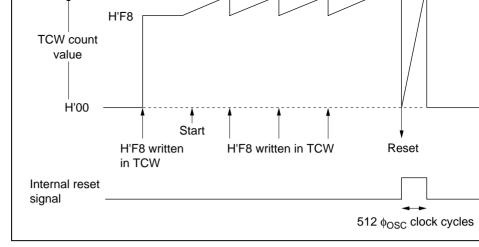

| Typical Watchdog Timer Operations (Example)                        |

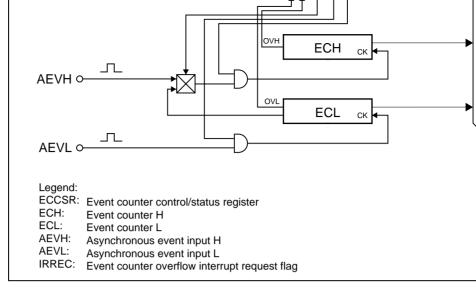

| Block Diagram of Asynchronous Event Counter                        |

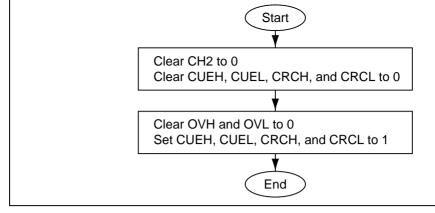

| Example of Software Processing when Using ECH and ECL as 16-Bi     |

| Counter                                                            |

| Example of Software Processing when Using ECH and ECL as 8-Bit     |

| Counters                                                           |

|                                                                    |

#### Section 10 Serial Communication Interface

| Figure 10.1     | SCI3 Block Diagram                                          |

|-----------------|-------------------------------------------------------------|

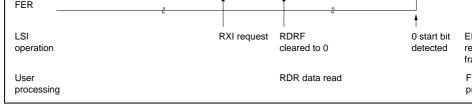

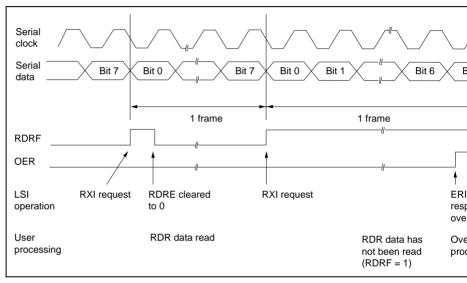

| Figure 10.2 (a) | RDRF Setting and RXI Interrupt                              |

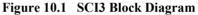

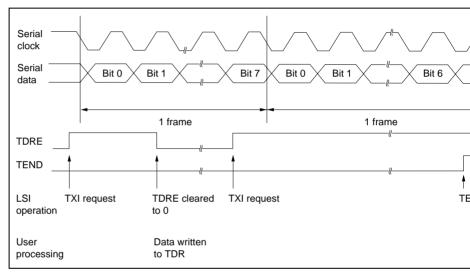

| Figure 10.2 (b) | TDRE Setting and TXI Interrupt                              |

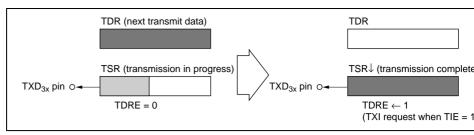

| Figure 10.2 (c) | TEND Setting and TEI Interrupt                              |

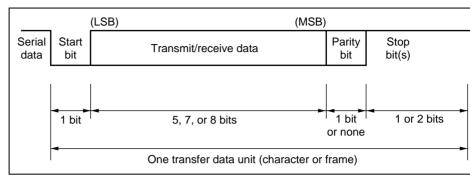

| Figure 10.3     | Data Format in Asynchronous Communication                   |

| Figure 10.4     | Phase Relationship between Output Clock and Transfer Data   |

|                 | (Asynchronous Mode) (8-bit data, parity, 2 stop bits)       |

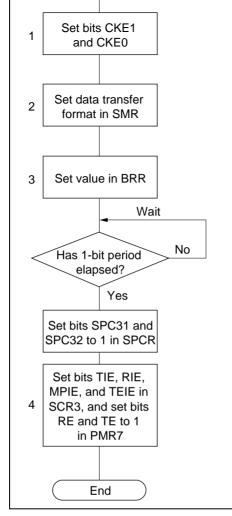

| Figure 10.5     | Example of SCI3 Initialization Flowchart                    |

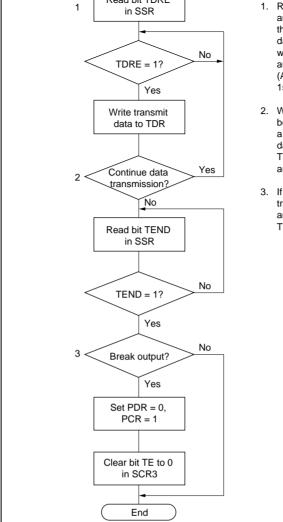

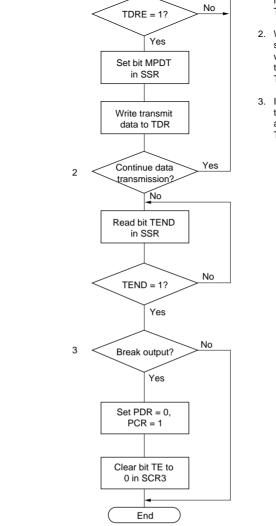

| Figure 10.6     | Example of Data Transmission Flowchart (Asynchronous Mode)  |

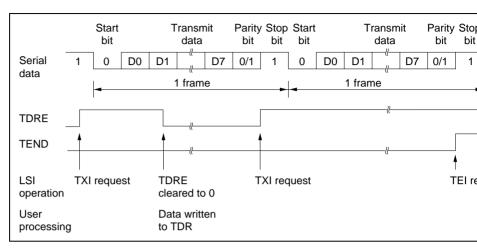

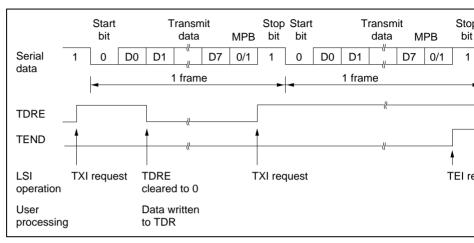

| Figure 10.7     | Example of Operation when Transmitting in Asynchronous Mode |

|                 | (8-bit data, parity, 1 stop bit)                            |

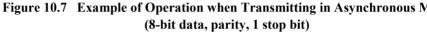

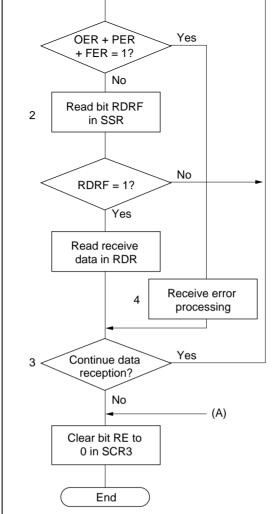

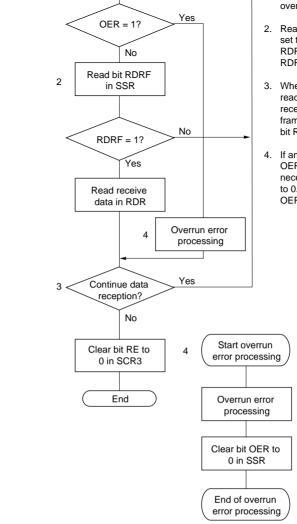

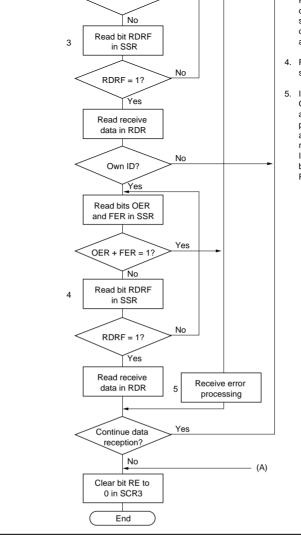

| Figure 10.8     | Example of Data Reception Flowchart (Asynchronous Mode)     |

| Figure 10.9     | Example of Operation when Receiving in Asynchronous Mode    |

|                 | (8-bit data, parity, 1 stop bit)                            |

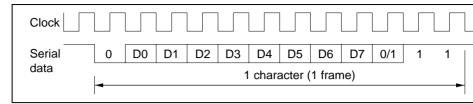

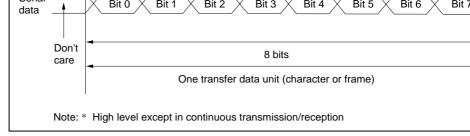

| Figure 10.10    | Data Format in Synchronous Communication                    |

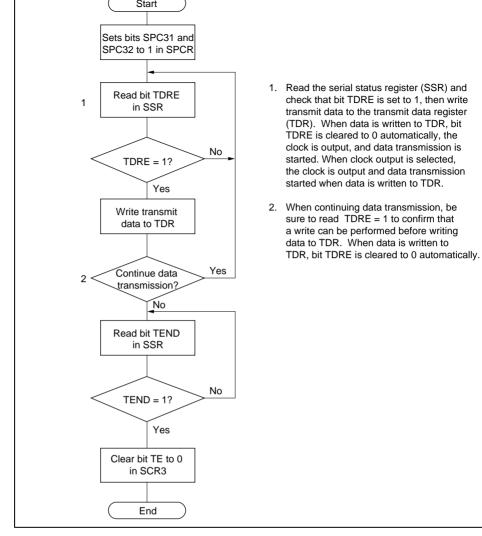

| Figure 10.11    | Example of Data Transmission Flowchart (Synchronous Mode)   |

| Figure 10.12    | Example of Operation when Transmitting in Synchronous Mode  |

| Figure 10.13    | Example of Data Reception Flowchart (Synchronous Mode)      |

| Figure 10.14    | Example of Operation when Receiving in Synchronous Mode     |

Rev. 6.00 Aug 04, 2006 page

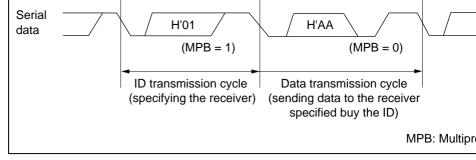

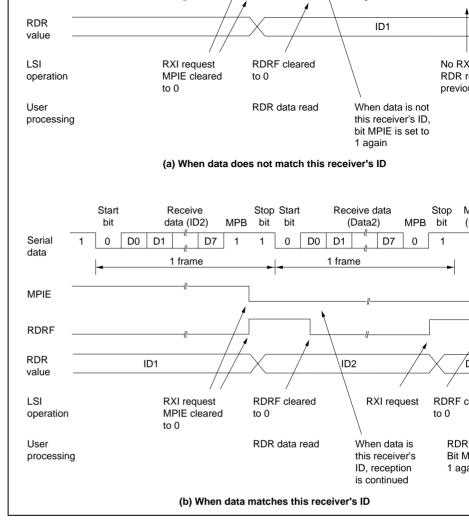

| Figure 10.20 | Example of Operation when Receiving Using Multiprocessor Format |

|--------------|-----------------------------------------------------------------|

|              | (8-bit data, multiprocessor bit, 1 stop bit)                    |

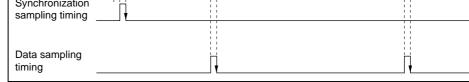

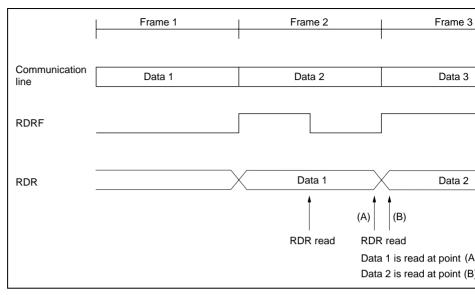

| Figure 10.21 | Receive Data Sampling Timing in Asynchronous Mode               |

| Figure 10.22 | Relation between RDR Read Timing and Data                       |

| e            |                                                                 |

#### Section 11 14-Bit PWM

| Figure 11.1 | Block Diagram of the 14 Bit PWM |

|-------------|---------------------------------|

| Figure 11.2 | PWM Output Waveform             |

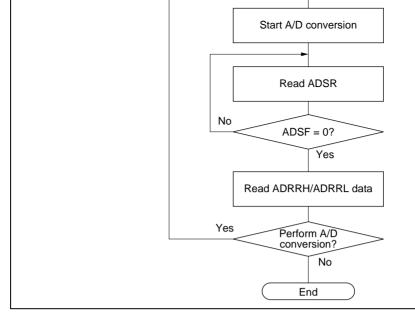

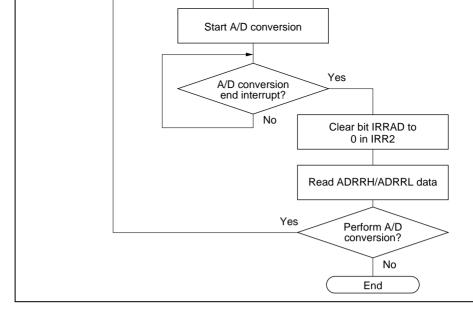

#### Section 12 A/D Converter

| / Softwar |

|-----------|

| Used)     |

|           |

| ,         |

#### Section 13 LCD Controller/Driver

| Figure 13.1  | Block Diagram of LCD Controller/Driver                        |

|--------------|---------------------------------------------------------------|

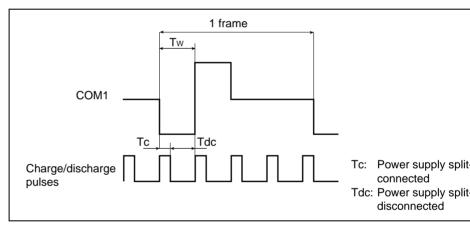

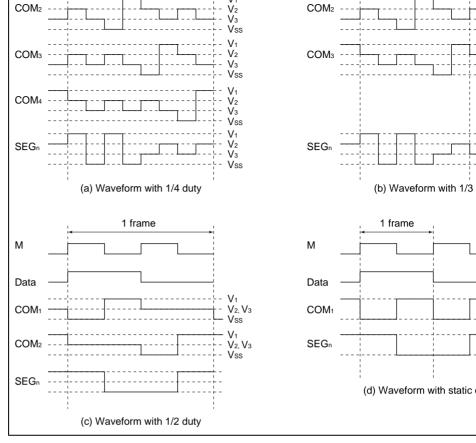

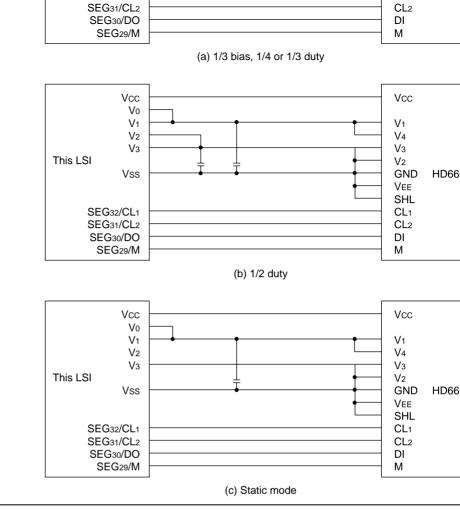

| Figure 13.2  | Example of A Waveform with 1/2 Duty and 1/2 Bias              |

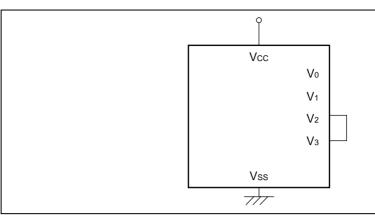

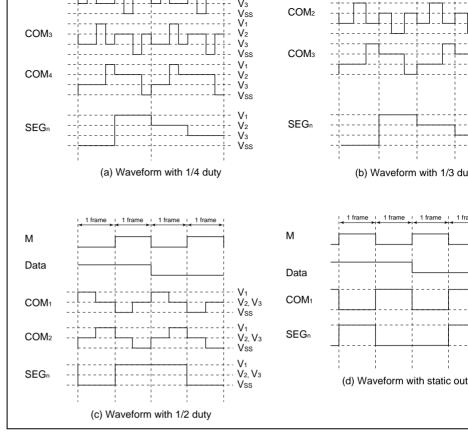

| Figure 13.3  | Handling of LCD Drive Power Supply when Using 1/2 Duty        |

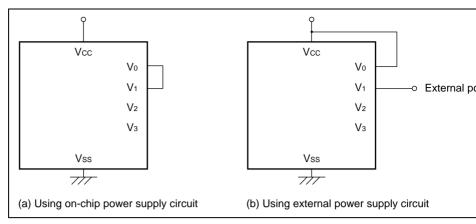

| Figure 13.4  | Examples of LCD Power Supply Pin Connections                  |

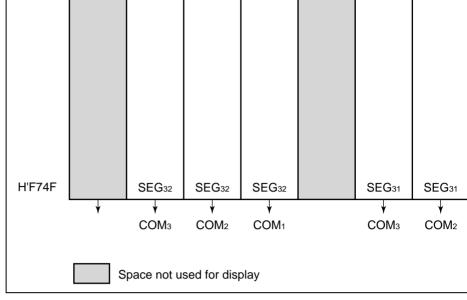

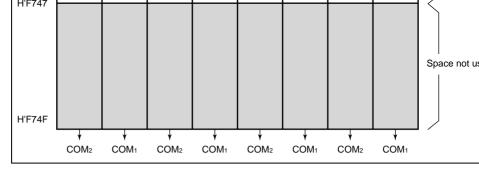

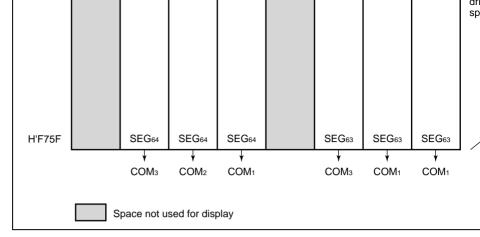

| Figure 13.5  | LCD RAM Map when Not Using Segment External Expansion (1/4 Du |

| Figure 13.6  | LCD RAM Map when Not Using Segment External Expansion (1/3 Du |

| Figure 13.7  | LCD RAM Map when Not Using Segment External Expansion (1/2 Du |

| Figure 13.8  | LCD RAM Map when Not Using Segment External Expansion (Static |

| Figure 13.9  | LCD RAM Map when Using Segment External Expansion             |

|              | (SGX = "1", SGS3 to SGS0 = "0000" 1/4 Duty)                   |

| Figure 13.10 | LCD RAM Map when Using Segment External Expansion             |

|              | (SGX = "1", SGS3 to SGS0 = "0000" 1/3 Duty)                   |

| Figure 13.11 | LCD RAM Map when Using Segment External Expansion             |

|              | (SGX = "1", SGS3 to SGS0 = "0000" 1/2 Duty)                   |

|              |                                                               |

Rev. 6.00 Aug 04, 2006 page xxvi of xxxiv

#### Section 14 Power Supply Circuit

| Figure 14.1 | Power Supply Connection when Internal Step-Down Circuit is Used. |

|-------------|------------------------------------------------------------------|

| Figure 14.2 | Power Supply Connection when Internal Step-Down Circuit is Not U |

#### Section 15 Electrical Characteristics

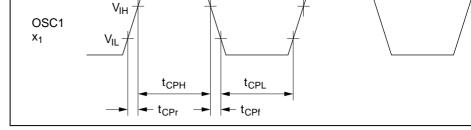

| Figure 15.1  | Clock Input Timing                        |

|--------------|-------------------------------------------|

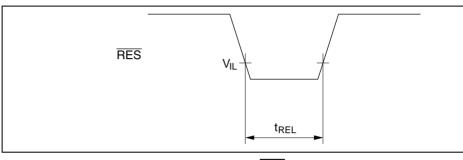

| Figure 15.2  | RES Low Width                             |

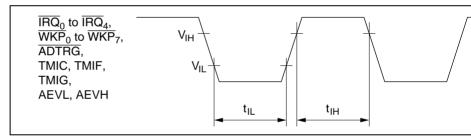

| Figure 15.3  | Input Timing                              |

| Figure 15.4  | UD Pin Minimum Modulation Width Timing    |

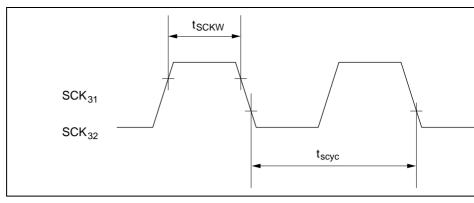

| Figure 15.5  | SCK3 Input Clock Timing                   |

| Figure 15.6  | SCI3 Synchronous Mode Input/Output Timing |

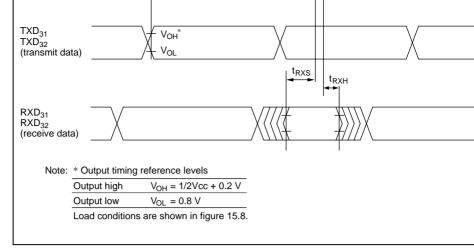

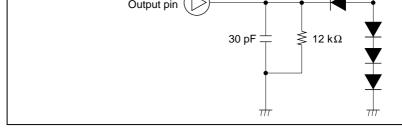

| Figure 15.7  | Segment Expansion Signal Timing           |

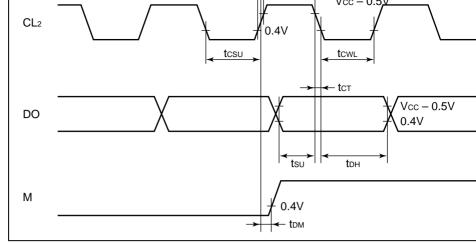

| Figure 15.8  | Output Load Condition                     |

| Figure 15.9  | Resonator Equivalent Circuit              |

| Figure 15.10 | Resonator Equivalent Circuit              |

#### Appendix C I/O Port Block Diagrams

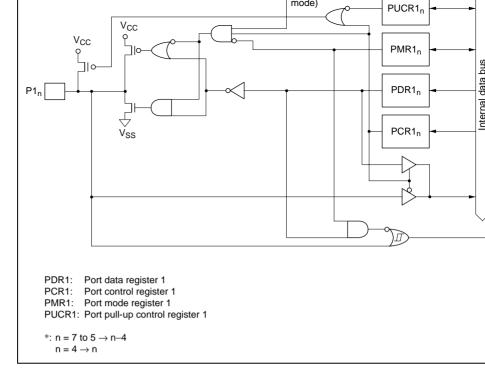

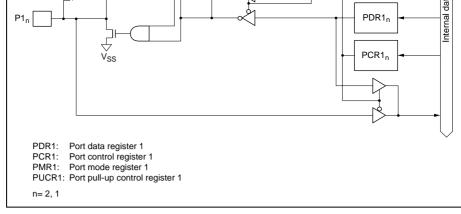

| Figure C.1 (a)   | Port 1 Block Diagram (Pins P1 <sub>7</sub> to P1 <sub>4</sub> )                |

|------------------|--------------------------------------------------------------------------------|

|                  | Port 1 Block Diagram (Pin P1 <sub>3</sub> )                                    |

|                  | Port 1 Block Diagram (Pin P1 <sub>2</sub> , P1 <sub>1</sub> )                  |

|                  | Port 1 Block Diagram (Pin P1 <sub>0</sub> )                                    |

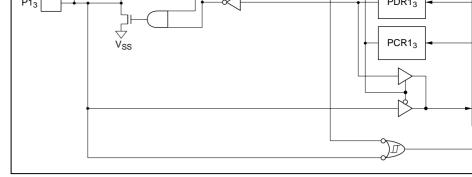

|                  | Port 3 Block Diagram (Pin P37 to P36)                                          |

|                  | Port 3 Block Diagram (Pin P3 <sub>5</sub> )                                    |

|                  | Port 3 Block Diagram (Pin P3 <sub>4</sub> )                                    |

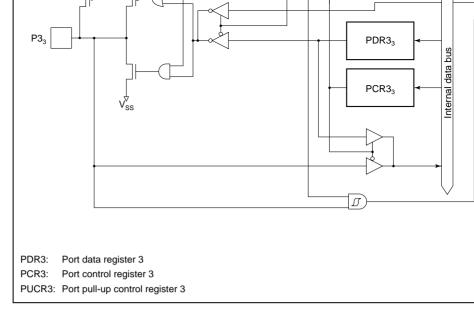

|                  | Port 3 Block Diagram (Pin P3 <sub>3</sub> )                                    |

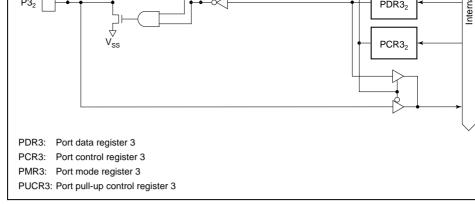

|                  | )Port 3 Block Diagram (Pin P32, H8/3827R Group and H8/3827S Group              |

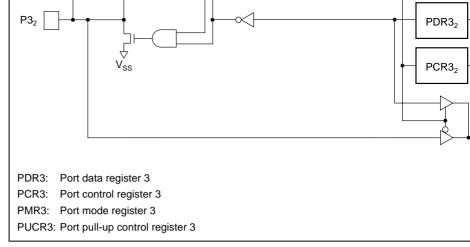

|                  | )Port 3 Block Diagram (Pin P3 <sub>2</sub> in the Mask ROM Version of the H8/3 |

| C X              | and H8/38427 Group)                                                            |

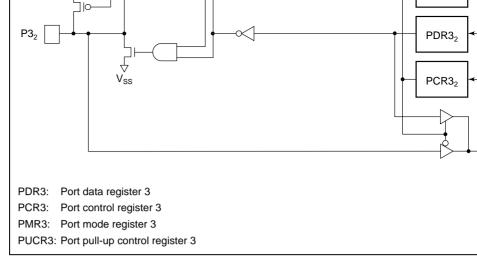

| Figure C.2 (e-3  | )Port 3 Block Diagram (Pin P3 <sub>2</sub> in the F-ZTAT Version of the H8/383 |

| -                | and H8/38427 Group)                                                            |

| Figure C.2 (f-1) | ) Port 3 Block Diagram (Pin P3 <sub>1</sub> , H8/3827R Group and H8/3827S Grou |

Rev. 6.00 Aug 04, 2006 page

| Figure C.0 | Fort / Block Diagram        |

|------------|-----------------------------|

| Figure C.7 | Port 8 Block Diagram        |

| Figure C.8 | Port A Block Diagram        |

| Figure C.9 | Port B Block Diagram        |

|            |                             |

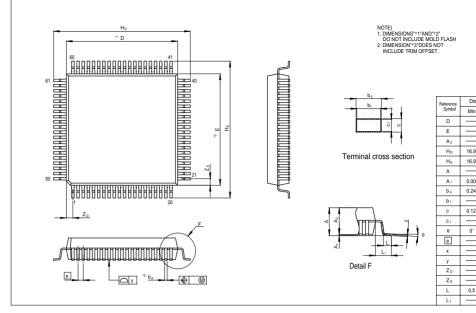

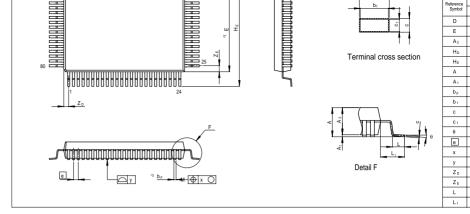

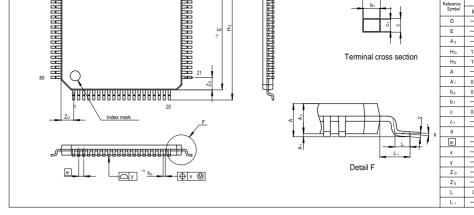

| Appendix F | Package Dimensions          |

| Figure F.1 | FP-80A Package Dimensions   |

| Figure F.2 | FP-80B Package Dimensions   |

| Figure F.3 | TFP-80C Package Dimensions  |

|            |                             |

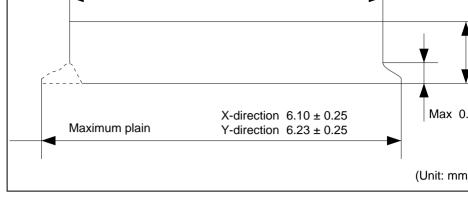

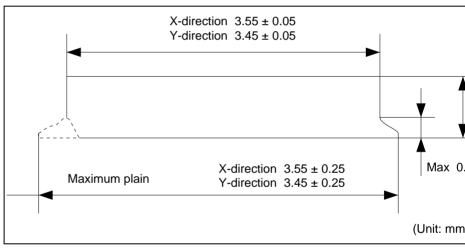

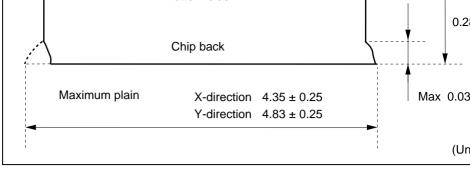

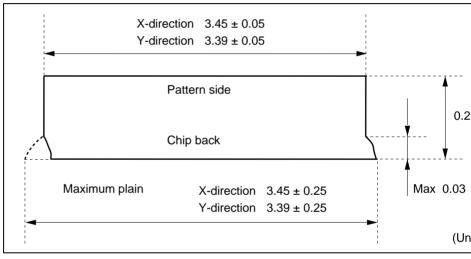

| Appendix G | Specifications of Chip Form |

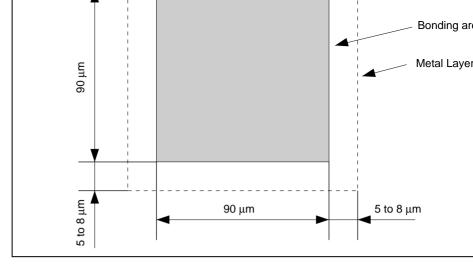

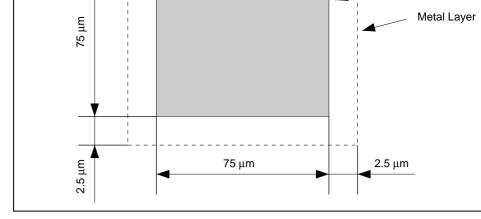

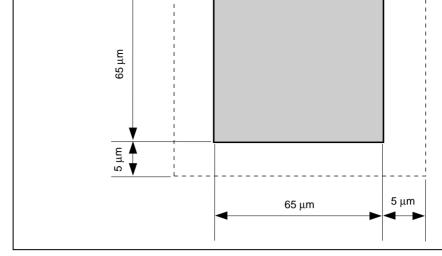

| Figure G.1 | Chip Sectional Figure       |

| Figure G.2 | Chip Sectional Figure       |

| Figure G.3 | Chip Sectional Figure       |

| Figure G.4 | Chip Sectional Figure       |

|            |                             |

| Appendix H | Form of Bonding Pads        |

| Figure H.1 | Bonding Pad Form            |

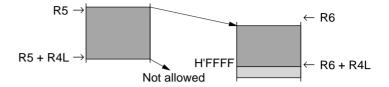

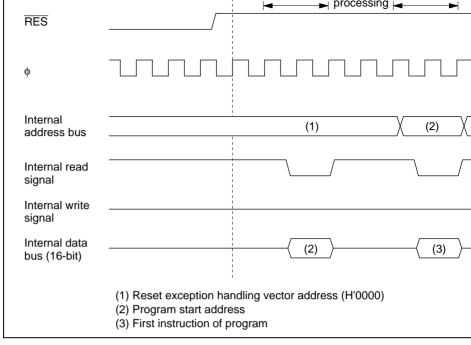

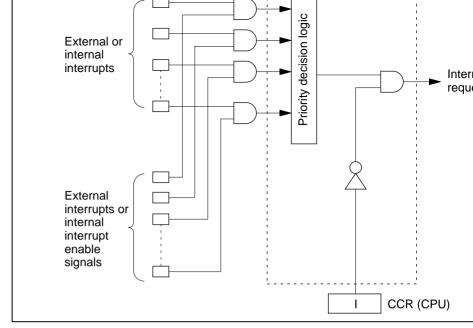

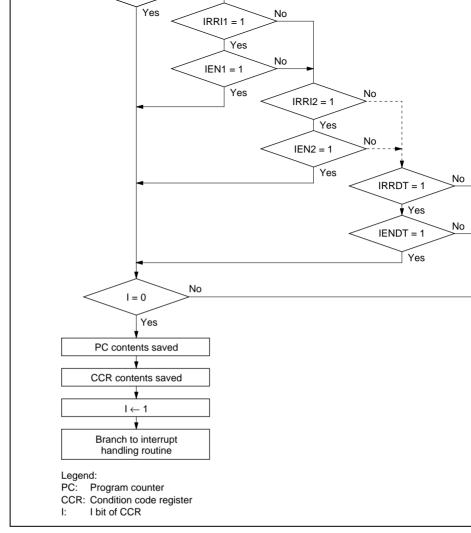

| Figure H.2 | Bonding Pad Form            |