# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

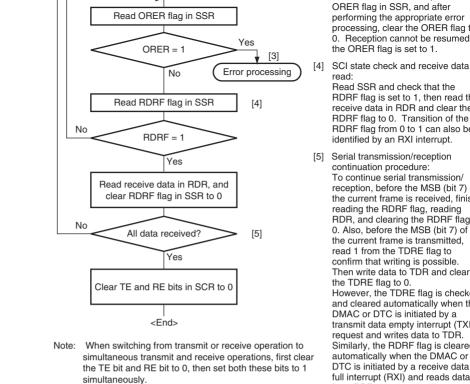

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

## Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

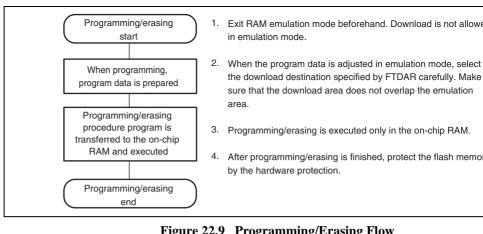

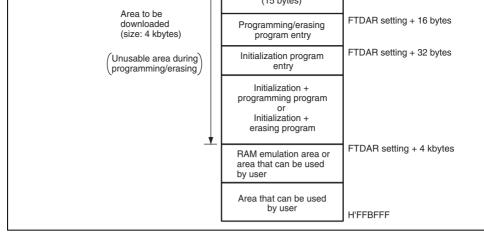

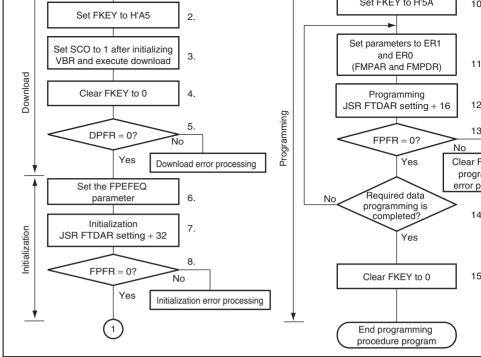

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# H8SX/1638 Group, H8SX/1638L Group

Hardware Manual

Renesas 32-Bit CISC Microcomputer H8SX Family / H8SX/1600 Series

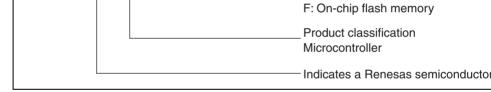

H8SX/1638 R5F61638 H8SX/1634 R5F61634 H8SX/1632 R5F61632 H8SX/1638L R5F61638L H8SX/1634L R5F61634L H8SX/1632L R5F61632L

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Rev. 2.00 Sep. 10, 2008 Page ii of xxviii

document, please confirm the latest product information with a Renesas sales office. Also, please pa and careful attention to additional and different information to be disclosed by Renesas such as that through our website. (http://www.renesas.com) 5. Renesas has used reasonable care in compiling the information included in this document, but Rene

assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the in-

characteristics, installation and other product characteristics. Renesas shall have no liability for malfu

10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have s characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design hardware and software including but not limited to redundancy, fire control and malfunction prevention appropriate treatment for aging degradation or any other applicable measures. Among others, since evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final pro

11. In case Renesas products listed in this document are detached from the products to which the Renes products are attached or affixed, the risk of accident such as swallowing by infants and small children high. You should implement safety measures so that Renesas products may not be easily detached

6. When using or otherwise relying on the information in this document, you should evaluate the information in this document, you should evaluate the information in this document. light of the total system before deciding about the applicability of such information to the intended applicability of such information to the information to the intended applicability of such information to the inf Renesas makes no representations, warranties or quaranties regarding the suitability of its products particular application and specifically disclaims any liability arising out of the application and use of the

information in this document or Renesas products. 7. With the exception of products specified by Renesas as suitable for automobile applications. Renesa products are not designed, manufactured or tested for applications or otherwise in systems the failure malfunction of which may cause a direct threat to human life or create a risk of human injury or which

included in this document.

- especially high quality and reliability such as safety systems, or equipment or systems for transportat traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea comi transmission. If you are considering the use of our products for such purposes, please contact a Ren sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes lis (1) artificial life support devices or systems (2) surgical implantations (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life Renesas shall have no liability for damages arising out of the uses set forth in the above and purchas

damages arising out of the use of Renesas products beyond such specified ranges.

products. Renesas shall have no liability for damages arising out of such detachment.

elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Technology Corp., its affiliated companies and their officers, directors, and employees against any ar damages arising out of such applications. You should use the products described herein within the range specified by Renesas, especially with to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation

12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior w approval from Renesas. 13. Please contact a Renesas sales office if you have any questions regarding the information contained document, Renesas semiconductor products, or if you have any other inquiries.

system manufactured by you.

Rev. 2.00 Sep. 10, 2008 Pa

vicinity of LSI, all associated shoot-through current nows internally, and mailunct due to the false recognition of the pin state as an input signal become possible. pins should be handled as described under Handling of Unused Pins in the manu 2. Processing at Power-on

- The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of regist

- settings and pins are undefined at the moment when power is supplied. In a finished product where the reset signal is applied to the external reset pin, the of pins are not guaranteed from the moment when power is supplied until the res

- process is completed. In a similar way, the states of pins in a product that is reset by an on-chip powerfunction are not guaranteed from the moment when power is supplied until the po

- reaches the level at which resetting has been specified. Prohibition of Access to Reserved Addresses Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of function not access these addresses; the correct operation of LSI is not guaranteed if the accessed. 4. Clock Signals

- signal has stabilized.

- After applying a reset, only release the reset line after the operating clock signal has stable. When switching the clock signal during program execution, wait until the targ — When the clock signal is generated with an external resonator (or from an extern

- oscillator) during a reset, ensure that the reset line is only released after full stab the clock signal. Moreover, when switching to a clock signal produced with an ex

- resonator (or by an external oscillator) while program execution is in progress, we the target clock signal is stable. 5. Differences between Products

Before changing from one product to another, i.e. to one with a different part number that the change will not lead to problems.

- The characteristics of MPU/MCU in the same group but having different part num differ because of the differences in internal memory capacity and layout pattern.

- each of the products.

changing to products of different part numbers, implement a system-evaluation to

RENESAS

Rev. 2.00 Sep. 10, 2008 Page iv of xxviii

When designing an application system that includes this LSI, take all points to note account. Points to note are given in their contexts and at the final part of each sect in the section giving usage notes.

The list of revisions is a summary of major points of revision or addition for earlier It does not cover all revised items. For details on the revised points, see the actual in the manual.

The following documents have been prepared for the H8SX/1638, H8SX/1638L Grousing any of the documents, please visit our web site to verify that you have the most date available version of the document.

| Document Type               | Contents                                                                                                                                                       | Document Title                                 | Docu      |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------|

| Data Sheet                  | Overview of hardware and electrical characteristics                                                                                                            | _                                              |           |

| Hardware Manual             | Hardware specifications (pin assignments, memory maps, peripheral specifications, electrical characteristics, and timing charts) and descriptions of operation | H8SX/1638, H8SX/1638L<br>Group Hardware Manual | This r    |

| Software Manual             | Detailed descriptions of the CPU and instruction set                                                                                                           | H8SX Family Software<br>Manual                 | REJ0      |

| Application Note            | Examples of applications and sample programs                                                                                                                   | The latest versions are available web site.    | ailable f |

| Renesas Technical<br>Update | Preliminary report on the specifications of a product, document, etc.                                                                                          | _                                              |           |

Rev. 2.00 Sep. 10, 2008 Pa

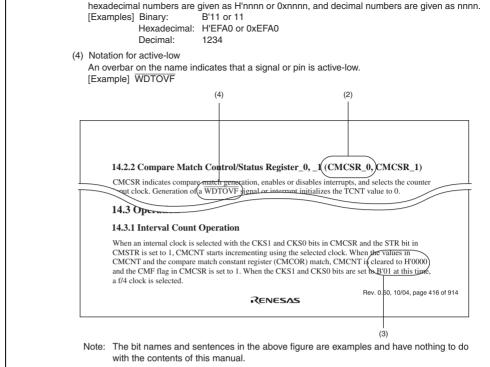

Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary).

Rev. 2.00 Sep. 10, 2008 Page vi of xxviii

| Bit     | Bit Name                   | Initial Value R/   | R/W Description                                                     |

|---------|----------------------------|--------------------|---------------------------------------------------------------------|

| 15      | -                          | ф R                | Reserved These bits are always read as 0.                           |

| 13 to 1 | 1 ASID2 to<br>ASID0        | All O R/           | W Address Identifier These bits enable or disable the pin function. |

| 10      | -                          | 0 R                | Reserved This bit is always read as 0.                              |

| 9       | -                          | 1 R                | R Reserved This bit is always read as 1.                            |

|         | -                          | 0                  |                                                                     |

|         | he bit names an<br>nanual. | nd sentences in th | he above figure are examples, and have nothing to do with the cor   |

(1) Bit

Indicates the bit number or numbers.

In the case of a 32-bit register, the bits are arranged in order from 31 to 0. In the case

of a 16-bit register, the bits are arranged in order from 15 to 0.

Indicates the name of the bit or bit field.

When the number of bits has to be clearly indicated in the field, appropriate notation is included (e.g., ASID[3:0]). A reserved bit is indicated by "-".

Certain kinds of bits, such as those of timer counters, are not assigned bit names. In such

cases, the entry under Bit Name is blank.

Indicates the value of each bit immediately after a power-on reset, i.e., the initial value.

0: The initial value is 0 1: The initial value is 1

-: The initial value is undefined

(4) R/W For each bit and bit field, this entry indicates whether the bit or field is readable or writable

or both writing to and reading from the bit or field are impossible. The notation is as follows:

R/W: The bit or field is readable and writable.

R/(W): The bit or field is readable and writable.

However, writing is only performed to flag clearing.

The bit or field is readable.

"R" is indicated for all reserved bits. When writing to the register, write

the value under Initial Value in the bit chart to reserved bits or fields. The bit or field is writable.

W: (5) Description

Describes the function of the bit or field and specifies the values for writing.

RENESAS

Rev. 2.00 Sep. 10, 2008 Pag

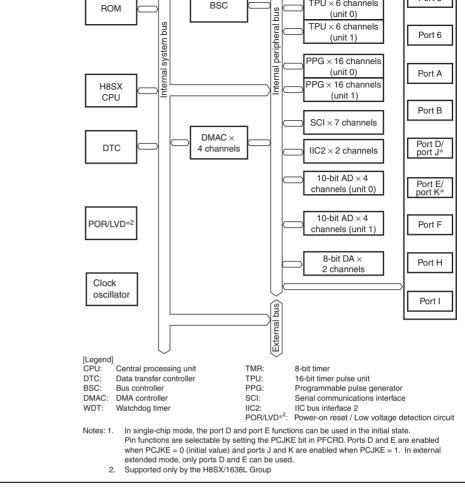

| TMR     | 8-bit timer                          |  |

|---------|--------------------------------------|--|

| TPU     | 16-bit timer pulse unit              |  |

| WDT     | Watchdog timer                       |  |

| . A h h | intions otherwhen these listed shows |  |

Serial communication interface

Abbreviations other than those listed above

Description

SCI

**Abbreviation**

VCO

| ACIA  | Asynchronous communication interface adapter                      |

|-------|-------------------------------------------------------------------|

| bps   | Bits per second                                                   |

| CRC   | Cyclic redundancy check                                           |

| DMA   | Direct memory access                                              |

| DMAC  | Direct memory access controller                                   |

| GSM   | Global System for Mobile Communications                           |

| Hi-Z  | High impedance                                                    |

| IEBus | Inter Equipment Bus (IEBus is a trademark of NEC Electronics Corp |

| I/O   | Input/output                                                      |

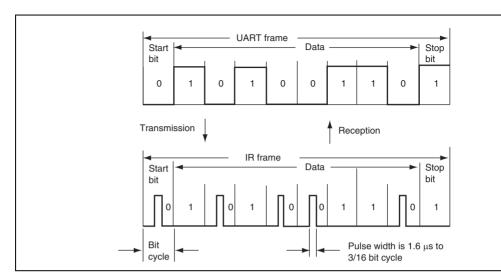

| IrDA  | Infrared Data Association                                         |

| LSB   | Least significant bit                                             |

| MSB   | Most significant bit                                              |

| NC    | No connection                                                     |

| PLL   | Phase-locked loop                                                 |

| PWM   | Pulse width modulation                                            |

| SFR   | Special function register                                         |

| SIM   | Subscriber Identity Module                                        |

| UART  | Universal asynchronous receiver/transmitter                       |

All trademarks and registered trademarks are the property of their respective owners.

Rev. 2.00 Sep. 10, 2008 Page viii of xxviii

Voltage-controlled oscillator

|       |          | 8                                                            |

|-------|----------|--------------------------------------------------------------|

|       | 1.4.2    | Correspondence between Pin Configuration and Operating Modes |

|       | 1.4.3    | Pin Functions                                                |

|       |          |                                                              |

| Secti | ion 2 C  | CPU                                                          |

| 2.1   | Feature  | PS                                                           |

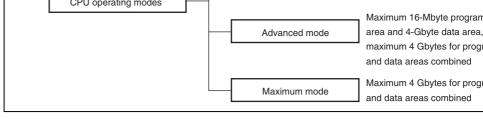

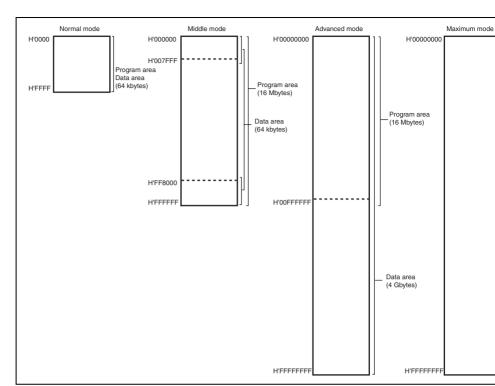

| 2.2   | CPU O    | perating Modes                                               |

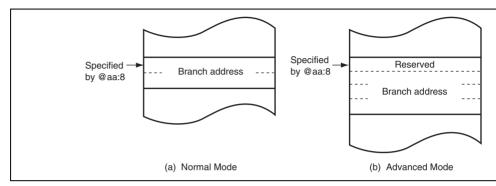

|       | 2.2.1    | Normal Mode                                                  |

|       | 2.2.2    | Middle Mode                                                  |

|       | 2.2.3    | Advanced Mode                                                |

|       | 2.2.4    | Maximum Mode                                                 |

| 2.3   | Instruct | tion Fetch                                                   |

| 2.4   | Addres   | s Space                                                      |

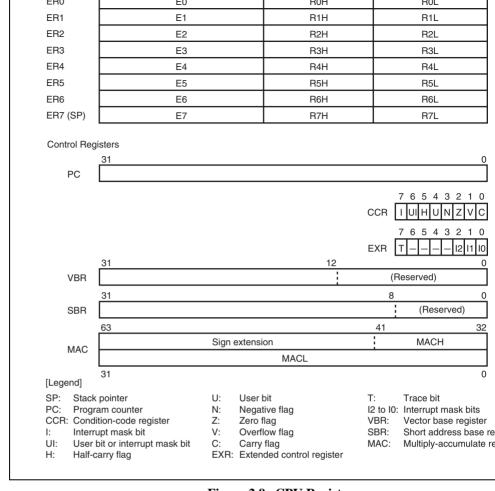

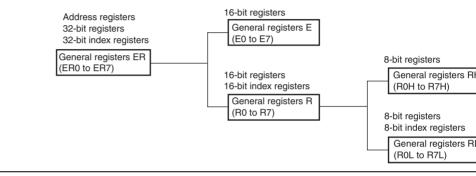

| 2.5   |          | ers                                                          |

|       | 2.5.1    | General Registers                                            |

|       | 2.5.2    | Program Counter (PC)                                         |

|       | 2.5.3    | Condition-Code Register (CCR)                                |

|       | 2.5.4    | Extended Control Register (EXR)                              |

|       | 2.5.5    | Vector Base Register (VBR)                                   |

|       | 2.5.6    | Short Address Base Register (SBR)                            |

|       | 2.5.7    | Multiply-Accumulate Register (MAC)                           |

|       | 2.5.8    | Initial Values of CPU Registers                              |

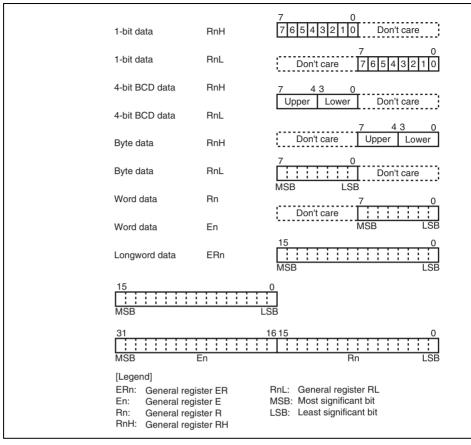

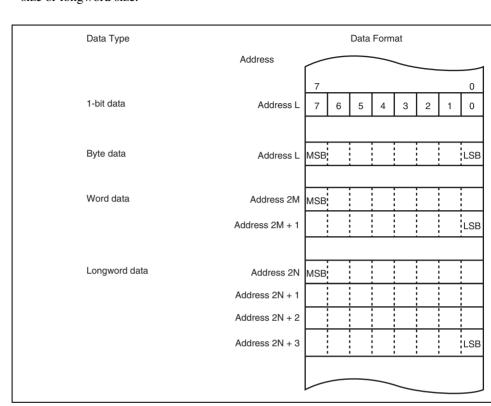

| 2.6   | Data Fo  | ormats                                                       |

|       | 2.6.1    | General Register Data Formats                                |

|       | 2.6.2    | Memory Data Formats                                          |

| 2.7   | Instruct | tion Set                                                     |

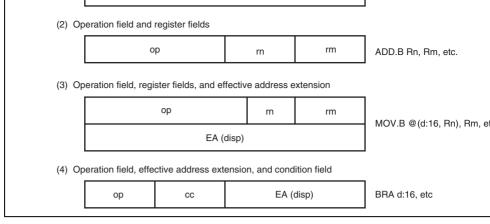

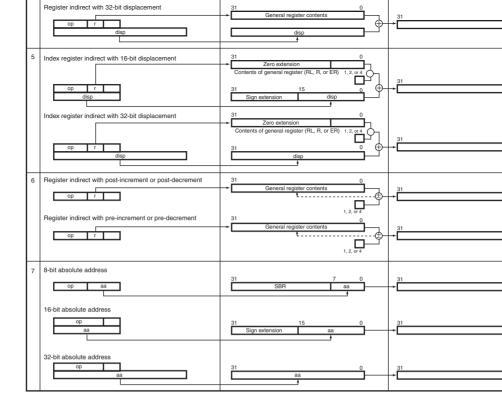

|       | 2.7.1    | Instructions and Addressing Modes                            |

|       |          |                                                              |

1.4.1

2.7.2

2.7.3

Table of Instructions Classified by Function .....

Basic Instruction Formats

Rev. 2.00 Sep. 10, 2008 Pa

|       | 2.8.12    | Effective Address Calculation   |

|-------|-----------|---------------------------------|

|       | 2.8.13    | MOVA Instruction                |

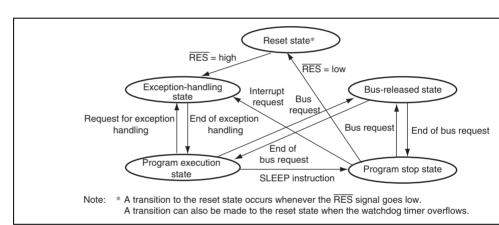

| 2.9   | Process   | ing States                      |

| Secti | ion 3 M   | ICU Operating Modes             |

| 3.1   |           | ng Mode Selection               |

| 3.2   | Register  | r Descriptions                  |

|       | 3.2.1     | Mode Control Register (MDCR)    |

|       | 3.2.2     | System Control Register (SYSCR) |

| 3.3   | Operation | ng Mode Descriptions            |

|       | 3.3.1     | Mode 1                          |

|       | 3.3.2     | Mode 2                          |

|       | 3.3.3     | Mode 3                          |

|       | 3.3.4     | Mode 4                          |

|       | 3.3.5     | Mode 5                          |

|       | 3.3.6     | Mode 6                          |

|       | 3.3.7     | Mode 7                          |

|       | 3.3.8     | Pin Functions                   |

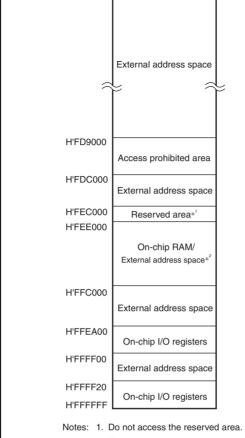

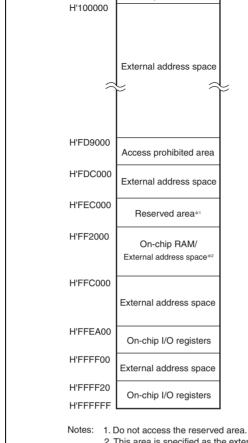

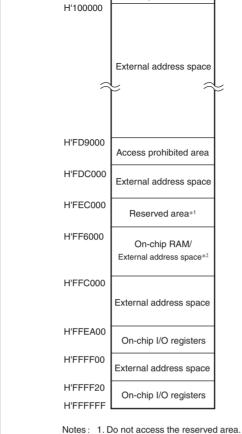

| 3.4   | Address   | s Map                           |

|       | 3.4.1     | Address Map                     |

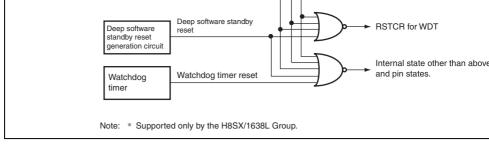

| Secti | ion 4 R   | esets                           |

| 4.1   |           | f Resets                        |

|       | T         | utput Pin                       |

Program-Counter Relative—@(d:8, PC) or @(d:16, PC) .....

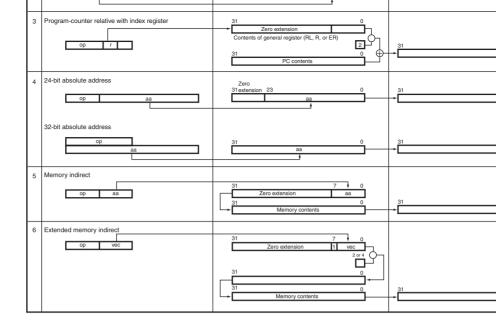

Memory Indirect—@@aa:8.... Extended Memory Indirect—@@vec:7....

Program-Counter Relative with Index Register—@(RnL.B, PC), @(Rn.W, PC), or @(ERn.L, PC).....

2.8.8

2.8.9

2.8.10

2.8.11

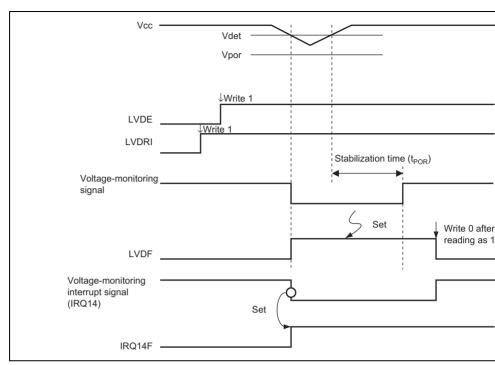

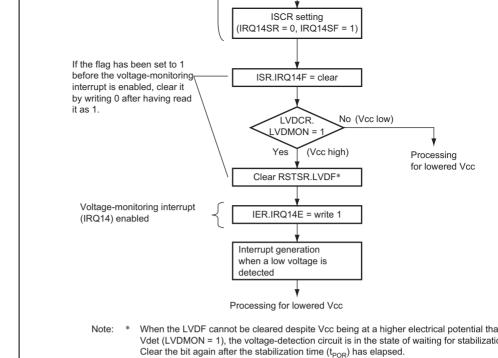

|      | 5.2.1    | Voltage Detection Control Register (LVDCR)                      |

|------|----------|-----------------------------------------------------------------|

|      | 5.2.2    | Reset Status Register (RSTSR)                                   |

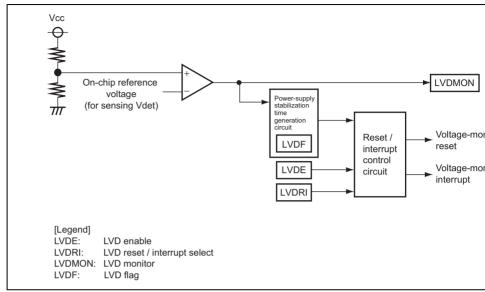

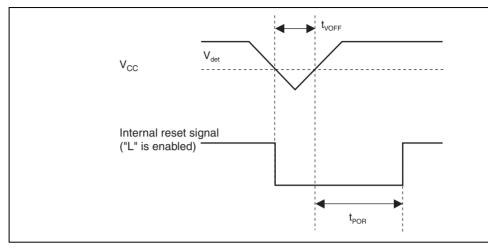

| 5.3  | Voltage  | e Detection Circuit                                             |

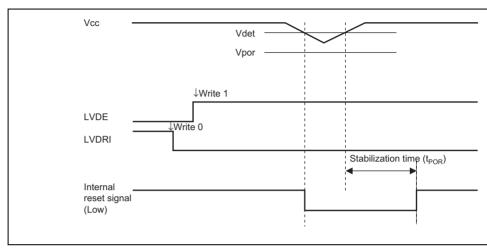

|      | 5.3.1    | Voltage Monitoring Reset                                        |

|      | 5.3.2    | Voltage Monitoring Interrupt                                    |

|      | 5.3.3    | Release from Deep Software Standby Mode by the Voltage-Detectio |

|      |          | Circuit                                                         |

|      | 5.3.4    | Voltage Monitor                                                 |

|      |          |                                                                 |

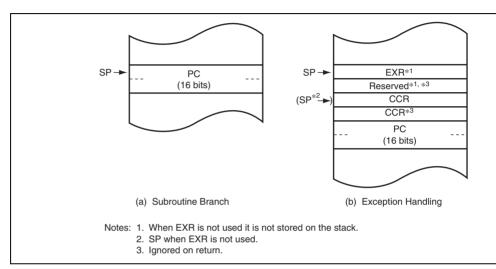

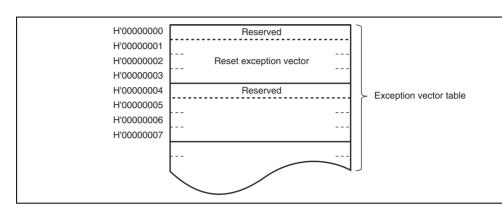

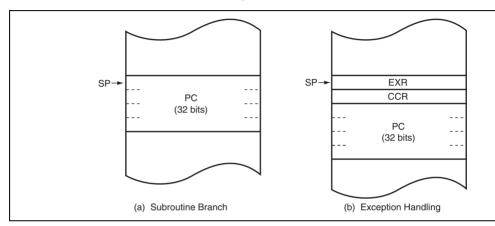

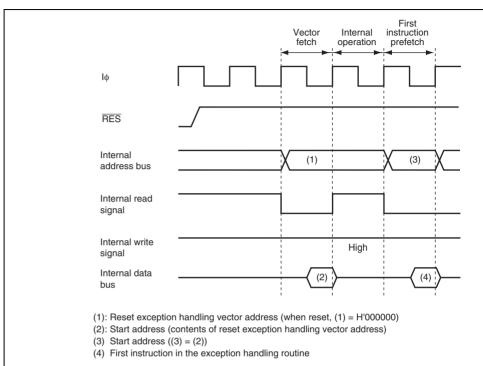

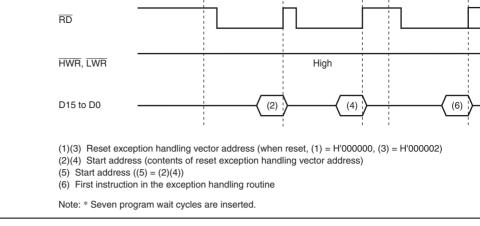

| Sect | ion 6 E  | Exception Handling                                              |

| 6.1  | Except   | ion Handling Types and Priority                                 |

| 6.2  | Except   | ion Sources and Exception Handling Vector Table                 |

| 6.3  | Reset    |                                                                 |

|      | 6.3.1    | Reset Exception Handling                                        |

|      | 6.3.2    | Interrupts after Reset                                          |

|      | 6.3.3    | On-Chip Peripheral Functions after Reset Release                |

| 6.4  | Traces.  |                                                                 |

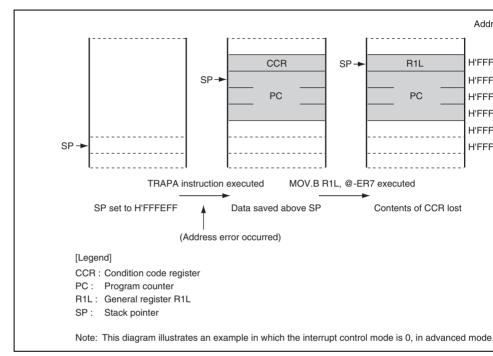

| 6.5  | Addres   | s Error                                                         |

|      | 6.5.1    | Address Error Source                                            |

|      | 6.5.2    | Address Error Exception Handling                                |

| 6.6  | Interruj | pts                                                             |

|      | 6.6.1    | Interrupt Sources                                               |

|      | 6.6.2    | Interrupt Exception Handling                                    |

| 6.7  | Instruc  | tion Exception Handling                                         |

|      | 6.7.1    | Trap Instruction                                                |

|      | 6.7.2    | Sleep Instruction Exception Handling                            |

Features....

Register Descriptions

5.1

5.2

6.7.3

Exception Handling by Illegal Instruction.....

Rev. 2.00 Sep. 10, 2008 Page

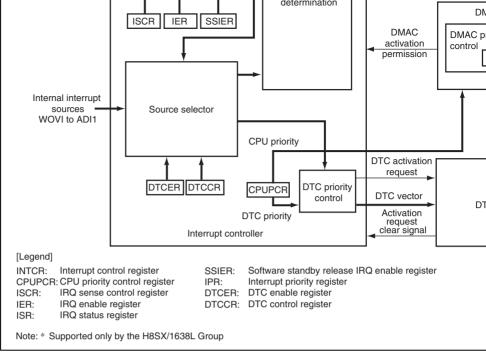

|        | 7.3.7                  | Software Standby Release IRQ Enable Register (SSIER)        |

|--------|------------------------|-------------------------------------------------------------|

| 7.4    | Interru                | ot Sources                                                  |

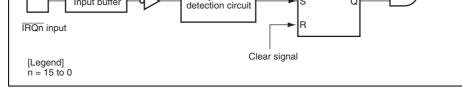

|        | 7.4.1                  | External Interrupts                                         |

|        | 7.4.2                  | Internal Interrupts                                         |

| 7.5    | Interru                | ot Exception Handling Vector Table                          |

| 7.6    | Interru                | ot Control Modes and Interrupt Operation                    |

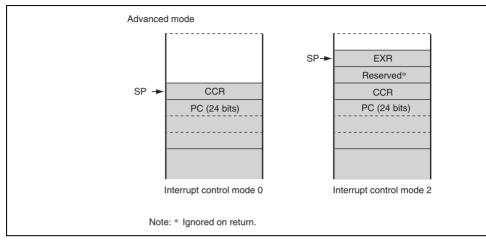

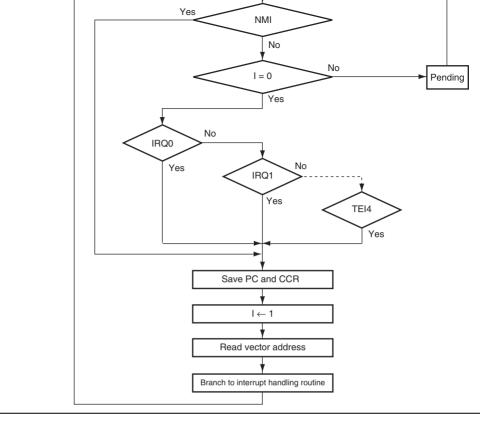

|        | 7.6.1                  | Interrupt Control Mode 0                                    |

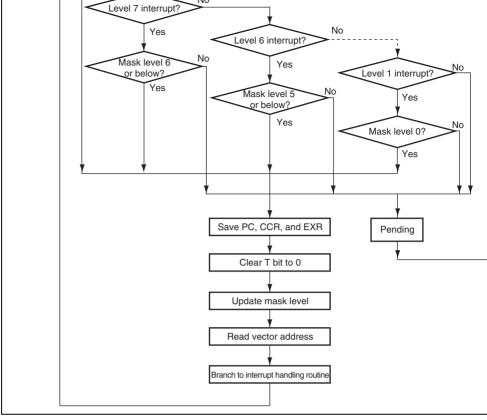

|        | 7.6.2                  | Interrupt Control Mode 2                                    |

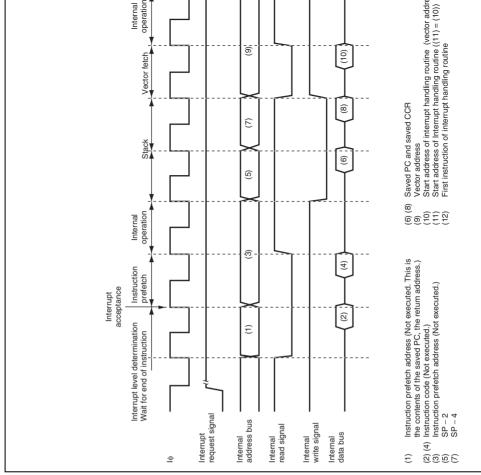

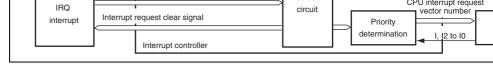

|        | 7.6.3                  | Interrupt Exception Handling Sequence                       |

|        | 7.6.4                  | Interrupt Response Times                                    |

|        | 7.6.5                  | DTC and DMAC Activation by Interrupt                        |

| 7.7    | CPU Pi                 | riority Control Function Over DTC and DMAC                  |

| 7.8    | Usage 1                | Notes                                                       |

|        | 7.8.1                  | Conflict between Interrupt Generation and Disabling         |

|        | 7.8.2                  | Instructions that Disable Interrupts                        |

|        | 7.8.3                  | Times when Interrupts are Disabled                          |

|        | 7.8.4                  | Interrupts during Execution of EEPMOV Instruction           |

|        | 7.8.5                  | Interrupts during Execution of MOVMD and MOVSD Instructions |

|        | 7.8.6                  | Interrupts of Peripheral Modules                            |

| Sect   | tion 8 U               | Jser Break Controller (UBC)                                 |

| 8.1    |                        | S                                                           |

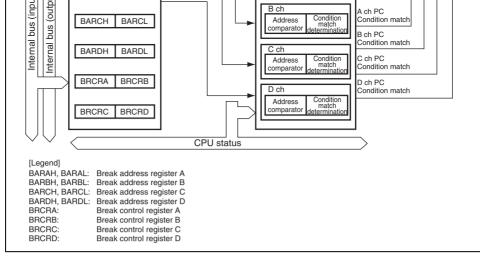

| 8.2    | Block I                | Diagram                                                     |

| 8.3    | Registe                | r Descriptions                                              |

|        | 8.3.1                  | Break Address Register n (BARA, BARB, BARC, BARD)           |

|        | 8.3.2                  | Break Address Mask Register n (BAMRA, BAMRB, BAMRC, BAMR    |

| Rev. 2 | 2.00 Sep. <sup>-</sup> | 10, 2008 Page xii of xxviii                                 |

|        |                        | RENESAS                                                     |

IRQ Enable Register (IER).....

IRQ Sense Control Registers H and L (ISCRH, ISCRL).....

IRQ Status Register (ISR).....

7.3.4

7.3.5

7.3.6

|    | 0.0.4       | P. 10. 1 Till C. 1 P. 1 (P.D.)                        |

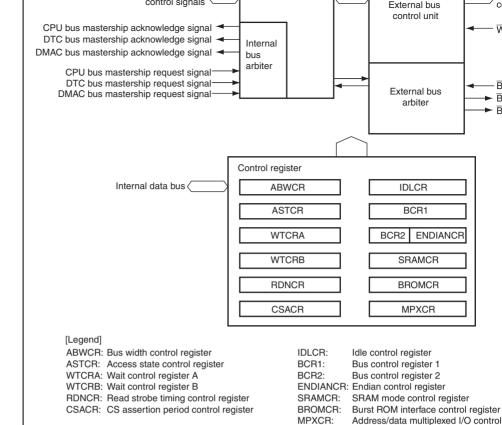

|----|-------------|-------------------------------------------------------|

|    | 9.2.4       | Read Strobe Timing Control Register (RDNCR)           |

|    | 9.2.5       | CS Assertion Period Control Registers (CSACR)         |

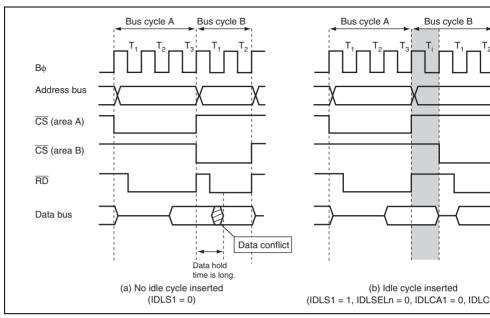

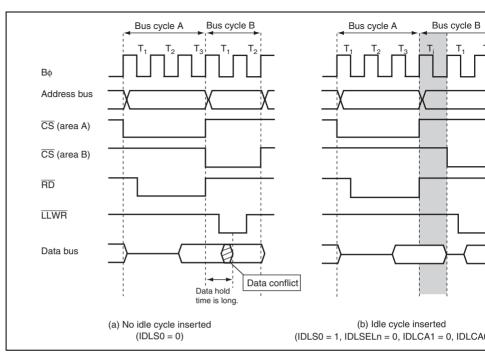

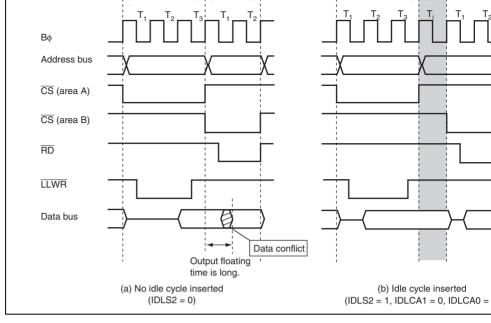

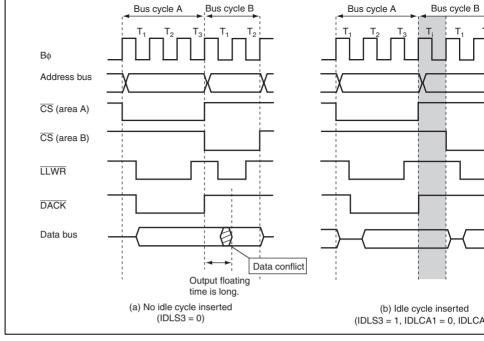

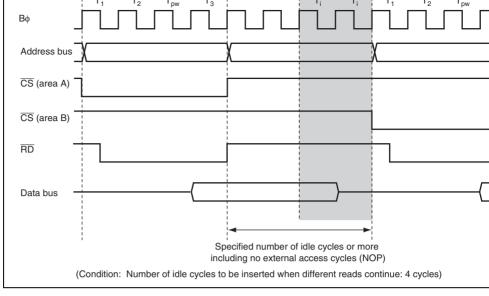

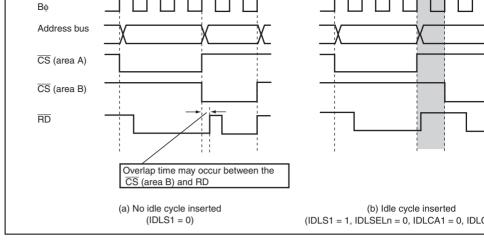

|    | 9.2.6       | Idle Control Register (IDLCR)                         |

|    | 9.2.7       | Bus Control Register 1 (BCR1)                         |

|    | 9.2.8       | Bus Control Register 2 (BCR2)                         |

|    | 9.2.9       | Endian Control Register (ENDIANCR)                    |

|    | 9.2.10      | SRAM Mode Control Register (SRAMCR)                   |

|    | 9.2.11      | Burst ROM Interface Control Register (BROMCR)         |

|    | 9.2.12      | Address/Data Multiplexed I/O Control Register (MPXCR) |

| 9. | .3 Bus Cor  | nfiguration                                           |

| 9. | .4 Multi-C  | lock Function and Number of Access Cycles             |

| 9. | .5 External | Bus                                                   |

|    | 9.5.1       | Input/Output Pins                                     |

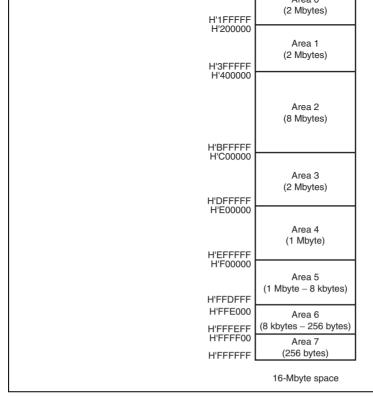

|    | 9.5.2       | Area Division                                         |

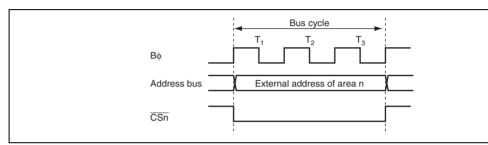

|    | 9.5.3       | Chip Select Signals                                   |

|    | 9.5.4       | External Bus Interface                                |

|    | 9.5.5       | Area and External Bus Interface                       |

|    | 9.5.6       | Endian and Data Alignment                             |

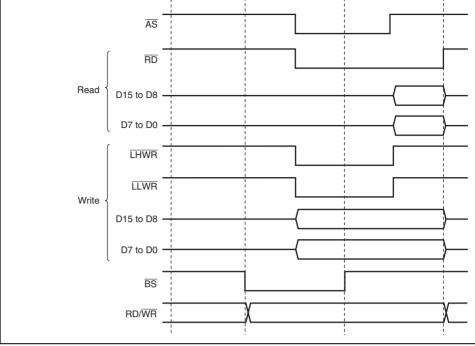

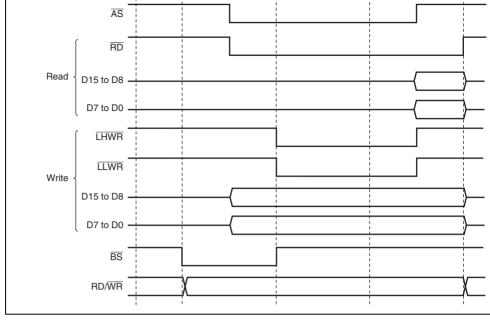

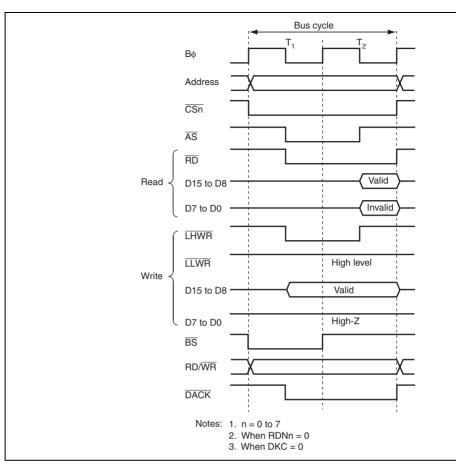

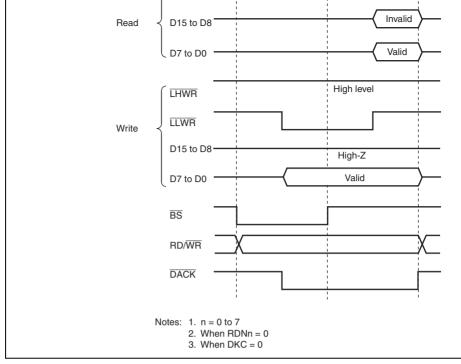

| 9. | .6 Basic Br | us Interface                                          |

|    | 9.6.1       | Data Bus                                              |

|    | 9.6.2       | I/O Pins Used for Basic Bus Interface                 |

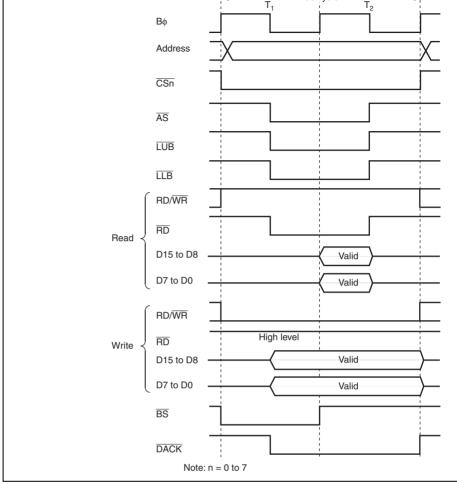

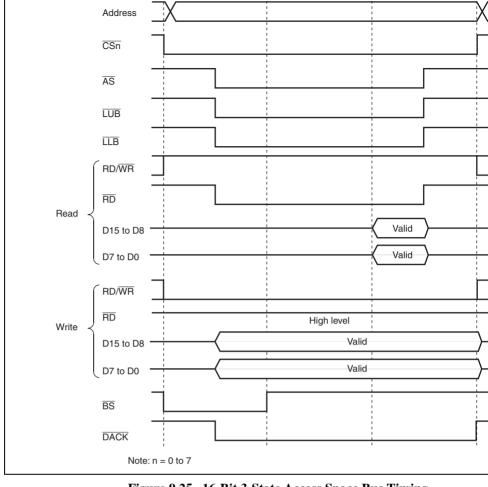

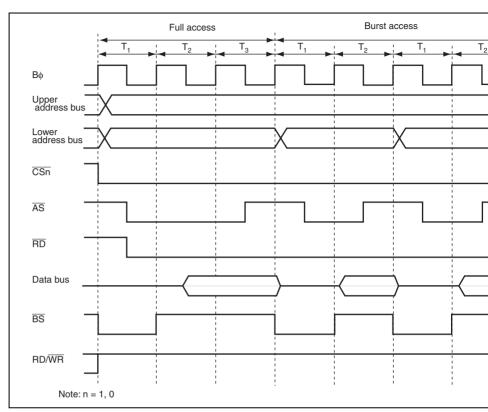

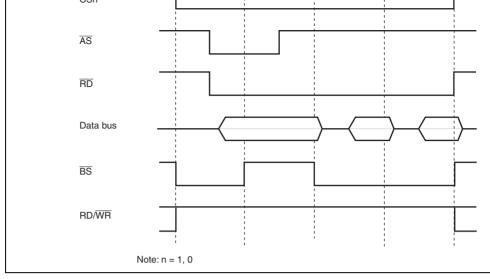

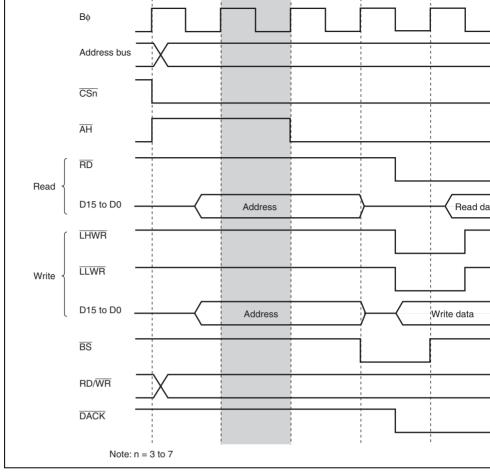

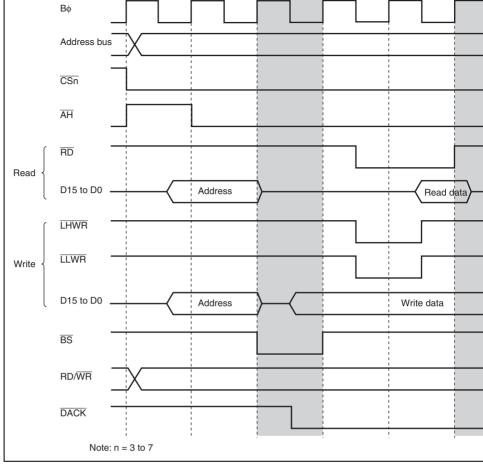

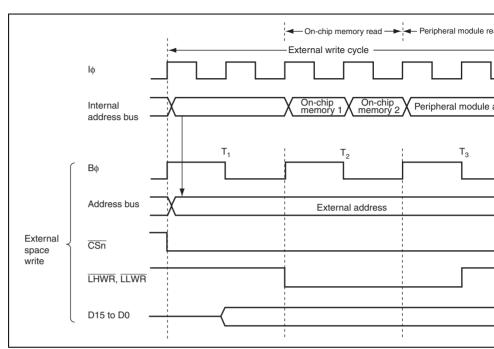

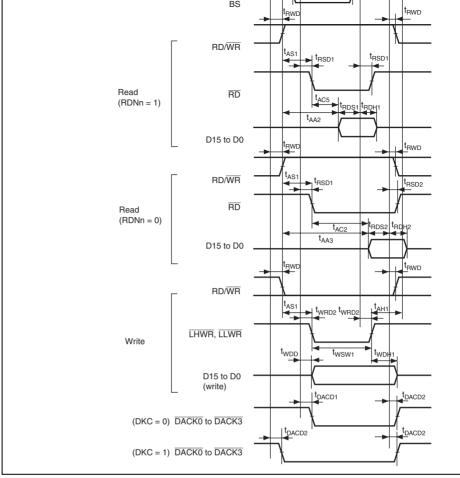

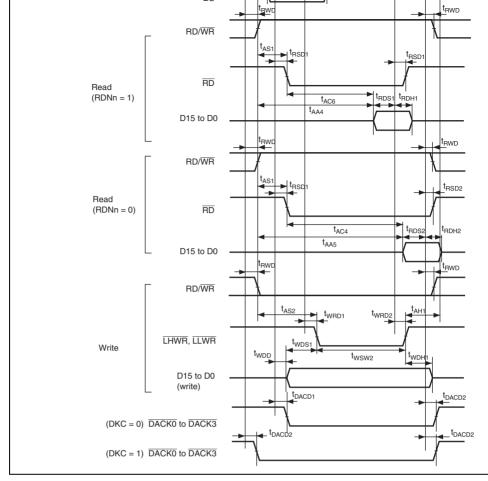

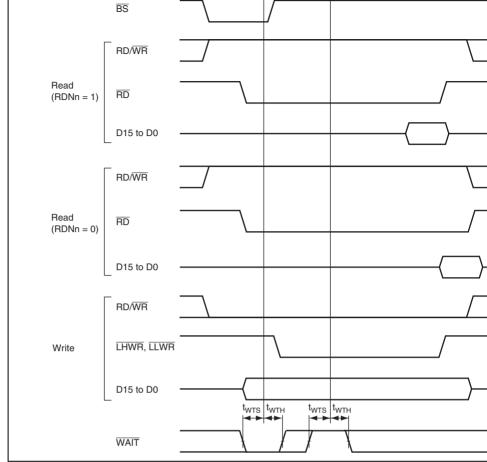

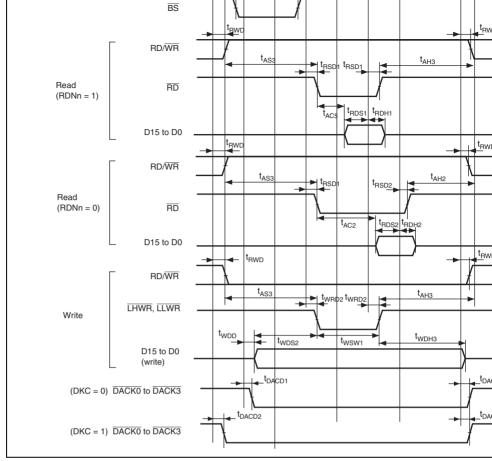

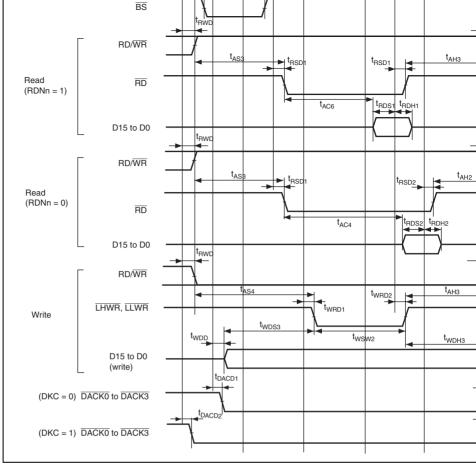

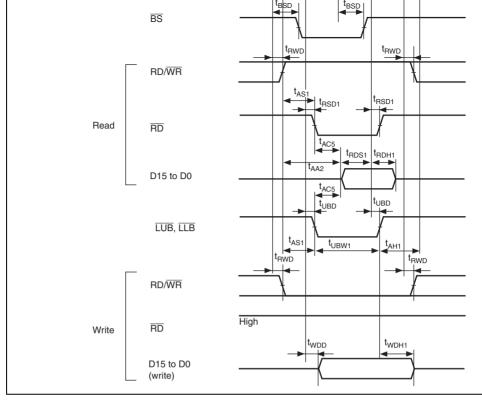

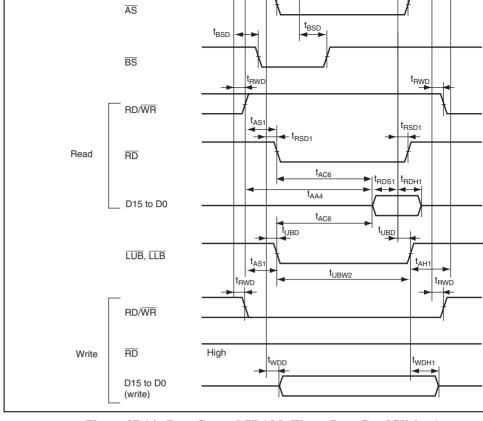

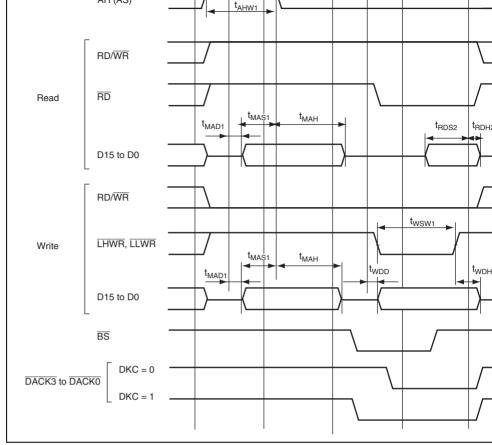

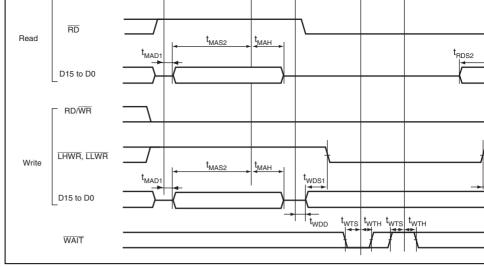

|    | 9.6.3       | Basic Timing                                          |

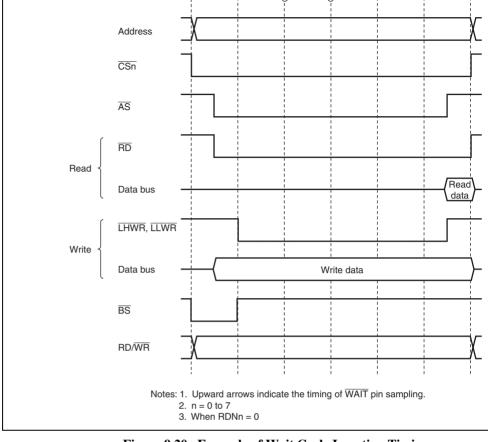

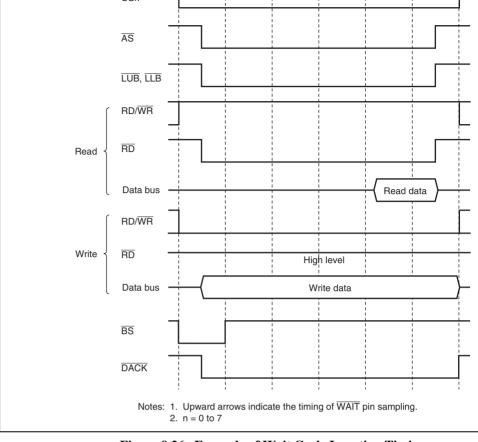

|    | 9.6.4       | Wait Control                                          |

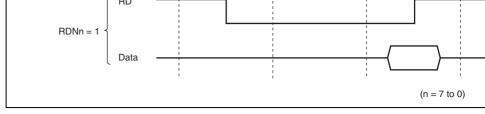

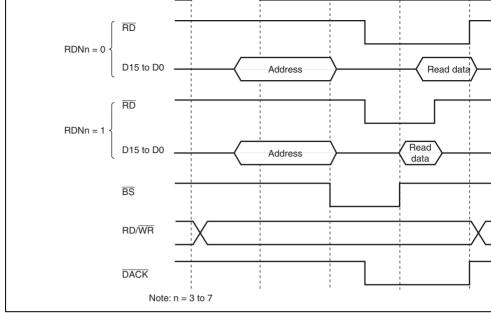

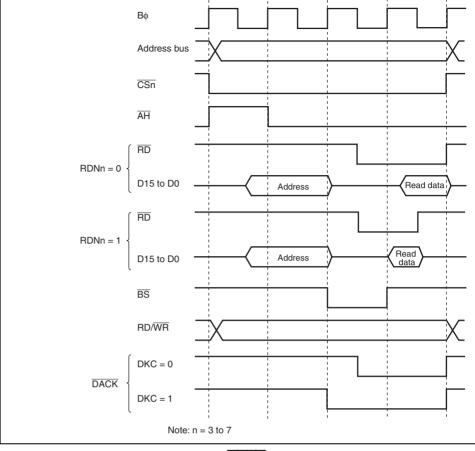

|    | 9.6.5       | Read Strobe (RD) Timing                               |

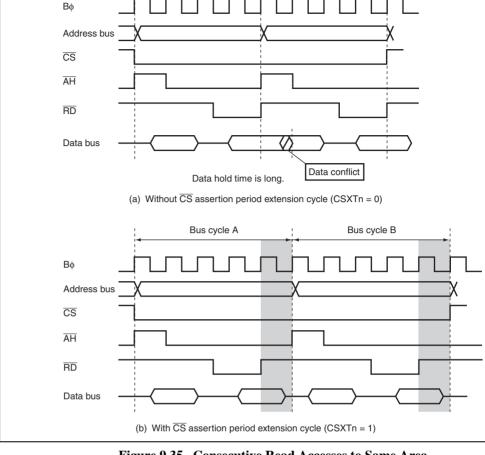

|    | 9.6.6       | Extension of Chip Select (CS) Assertion Period        |

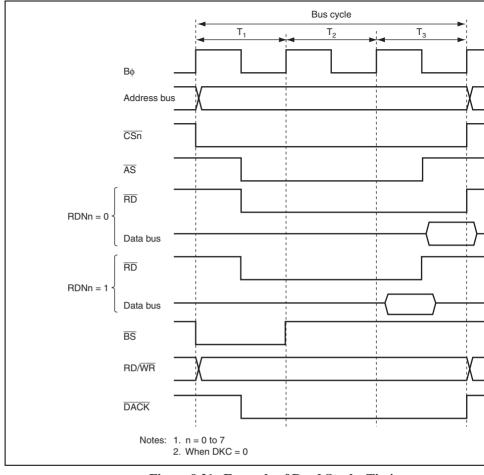

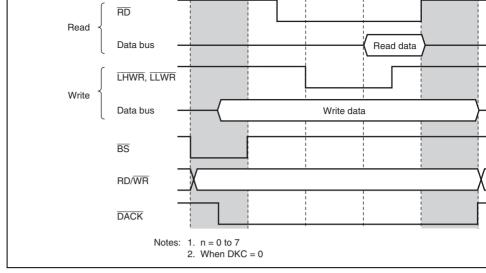

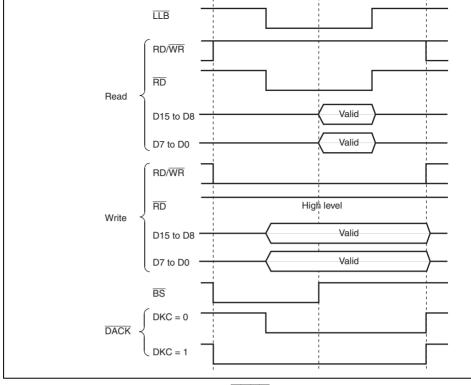

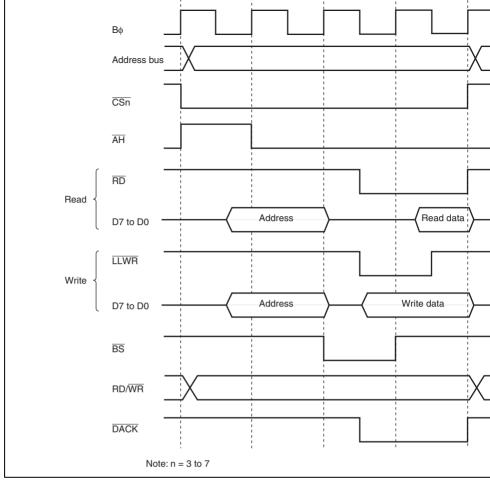

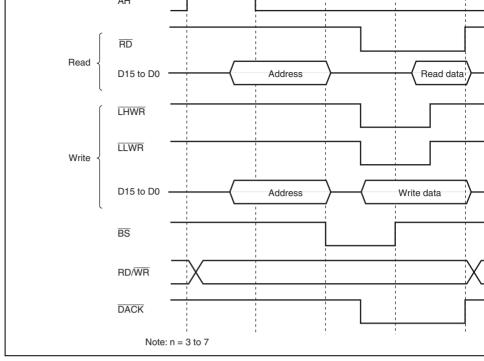

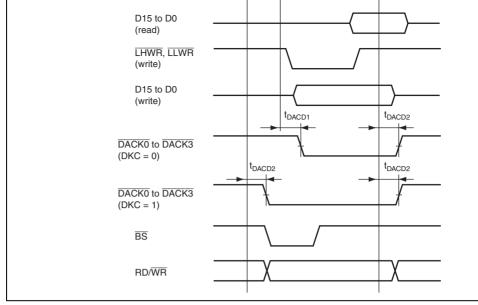

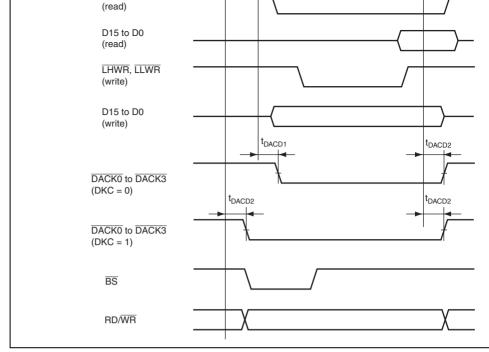

|    | 9.6.7       | DACK Signal Output Timing                             |

| 9. | .7 Byte Co  | ntrol SRAM Interface                                  |

|    | ,           |                                                       |

|    |             | Pay 2.00 Can 10 0000 Pag                              |

|    |             | Rev. 2.00 Sep. 10, 2008 Pag                           |

|    |             |                                                       |

Access State Control Register (ASTCR)

Wait Control Registers A and B (WTCRA, WTCRB) .....

9.2.2

9.2.3

|      | 9.9.3    | Data Bus                                                 |

|------|----------|----------------------------------------------------------|

|      | 9.9.4    | I/O Pins Used for Address/Data Multiplexed I/O Interface |

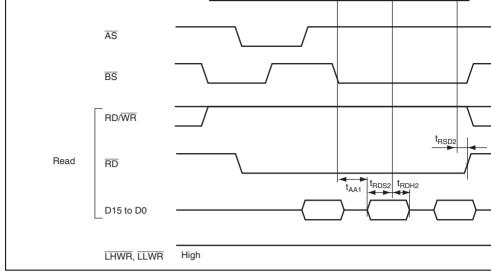

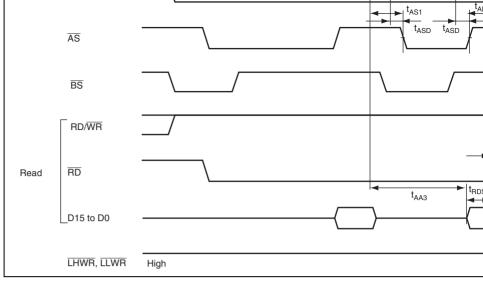

|      | 9.9.5    | Basic Timing                                             |

|      | 9.9.6    | Address Cycle Control                                    |

|      | 9.9.7    | Wait Control                                             |

|      | 9.9.8    | Read Strobe (RD) Timing                                  |

|      | 9.9.9    | Extension of Chip Select (CS) Assertion Period           |

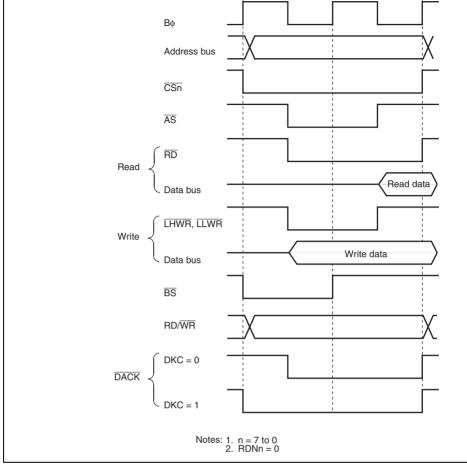

|      | 9.9.10   | DACK Signal Output Timing                                |

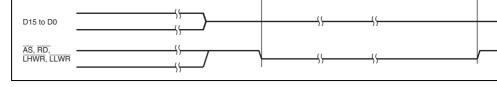

| 9.10 | Idle Cyc | cle                                                      |

|      | 9.10.1   | Operation                                                |

|      | 9.10.2   | Pin States in Idle Cycle                                 |

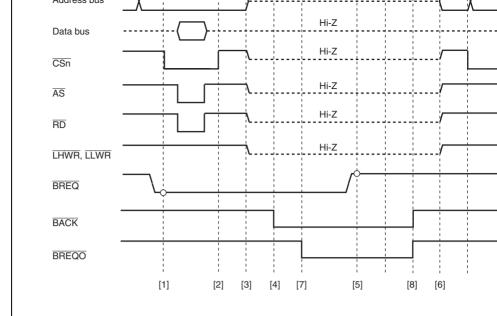

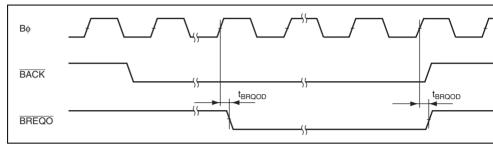

| 9.11 | Bus Rel  | ease                                                     |

|      | 9.11.1   | Operation                                                |

|      | 9.11.2   | Pin States in External Bus Released State                |

|      | 9.11.3   | Transition Timing                                        |

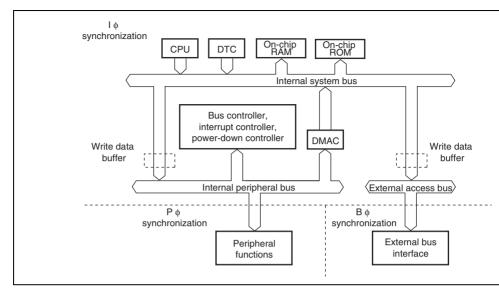

| 9.12 | Internal | Bus                                                      |

|      | 9.12.1   | Access to Internal Address Space                         |

| 9.13 | Write D  | ata Buffer Function                                      |

|      | 9.13.1   | Write Data Buffer Function for External Data Bus         |

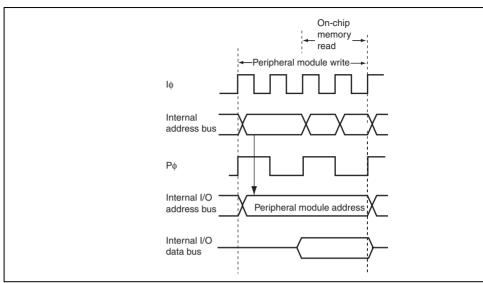

|      | 9.13.2   | Write Data Buffer Function for Peripheral Modules        |

|      | D A .1   | pitration                                                |

I/O Pins Used for Burst ROM Interface.....

Basic Timing.....

Wait Control

Read Strobe  $(\overline{RD})$  Timing Extension of Chip Select (CS) Assertion Period.....

Address/Data Multiplexed I/O Space Setting .....

Address/Data Multiplex .....

Address/Data Multiplexed I/O Interface.....

RENESAS

9.8.3

9.8.4

9.8.5

9.8.6

9.8.7

9.9.1 9.9.2

003

9.9

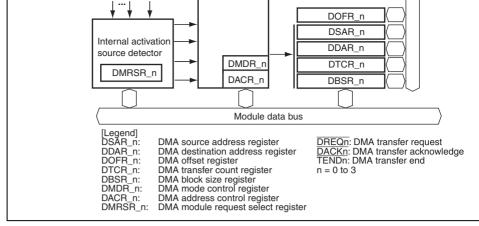

|     | 10.3.6      | DMA Mode Control Register (DMDR)                 |

|-----|-------------|--------------------------------------------------|

|     | 10.3.7      | DMA Address Control Register (DACR)              |

|     | 10.3.8      | DMA Module Request Select Register (DMRSR)       |

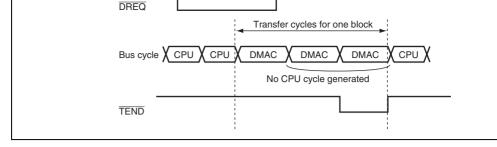

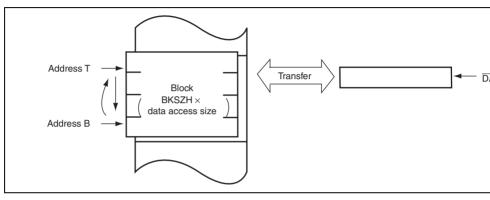

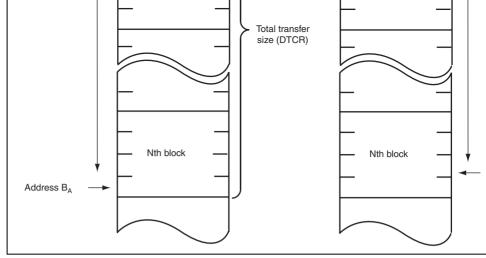

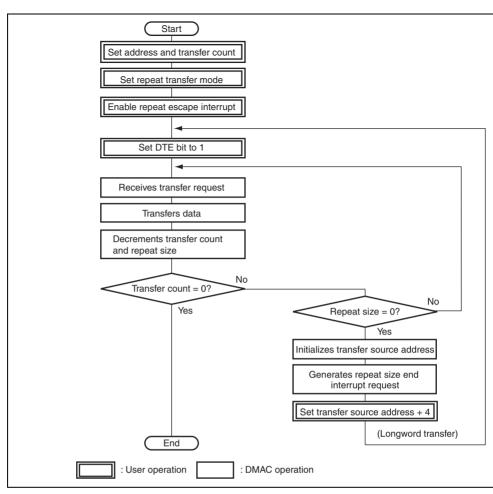

| 10. | .4 Transfe  | r Modes                                          |

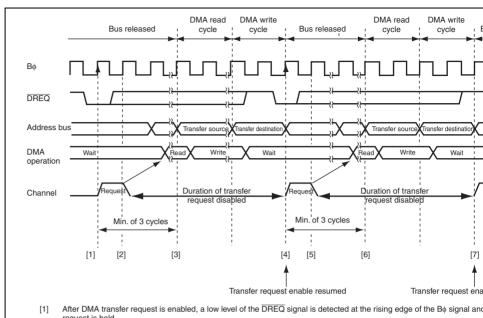

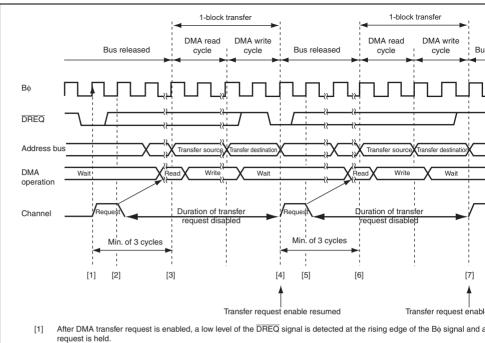

| 10. | .5 Operati  | ons                                              |

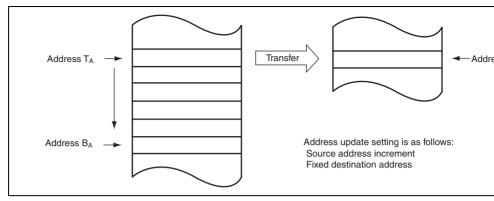

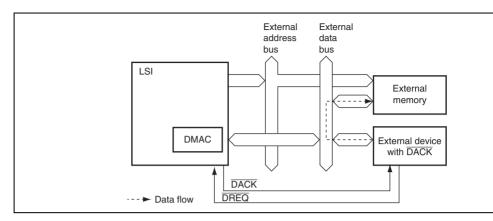

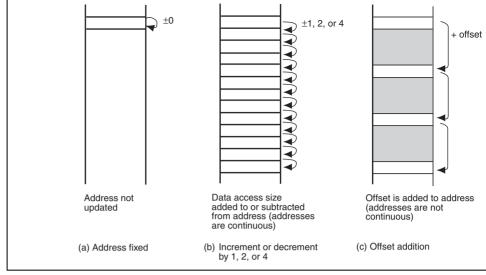

|     | 10.5.1      | Address Modes                                    |

|     | 10.5.2      | Transfer Modes                                   |

|     | 10.5.3      | Activation Sources                               |

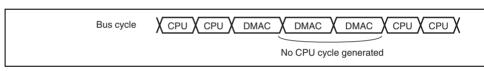

|     | 10.5.4      | Bus Access Modes                                 |

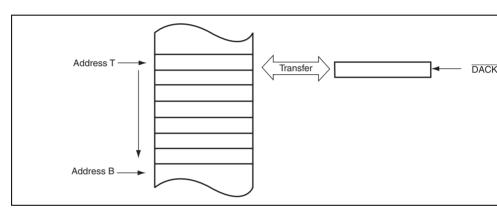

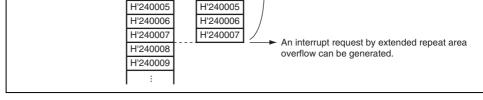

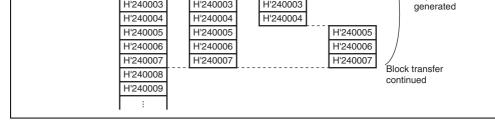

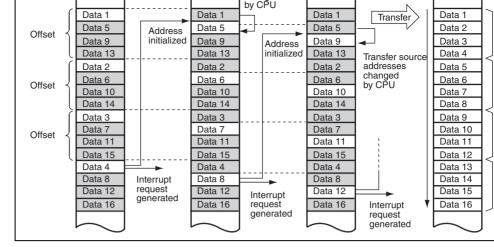

|     | 10.5.5      | Extended Repeat Area Function                    |

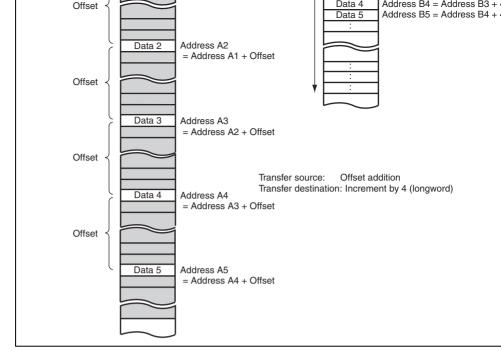

|     | 10.5.6      | Address Update Function using Offset             |

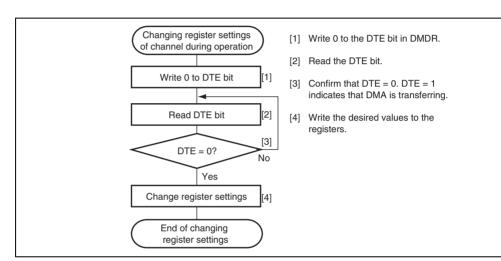

|     | 10.5.7      | Register during DMA Transfer                     |

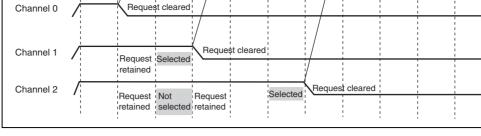

|     | 10.5.8      | Priority of Channels                             |

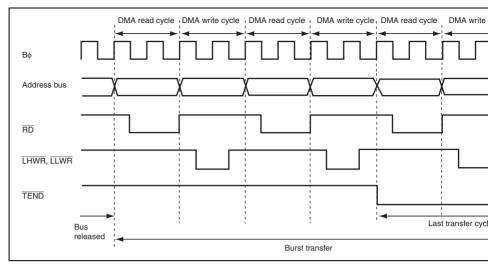

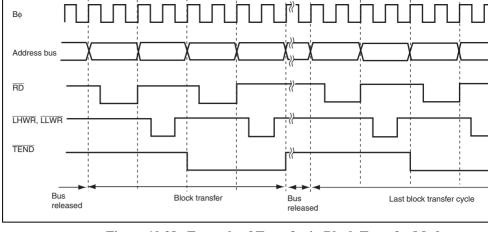

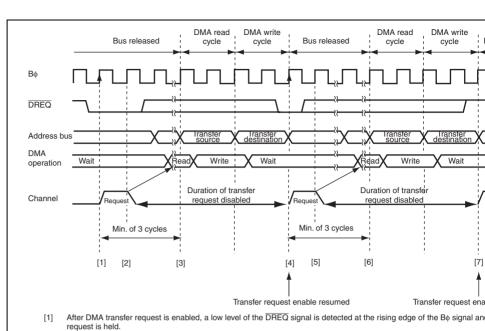

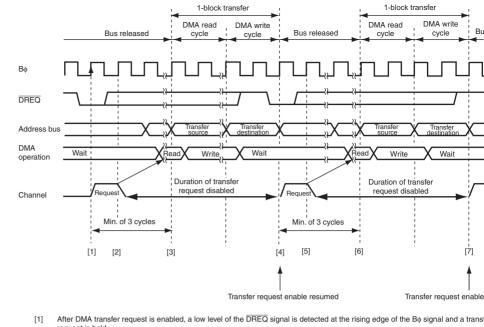

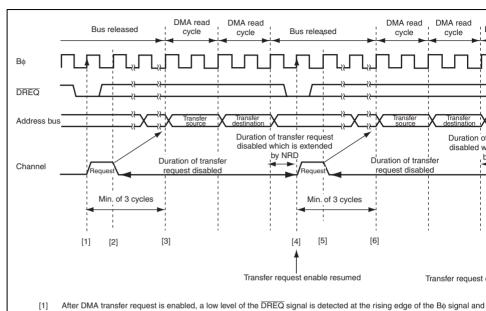

|     | 10.5.9      | DMA Basic Bus Cycle                              |

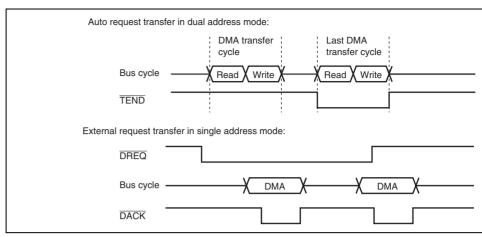

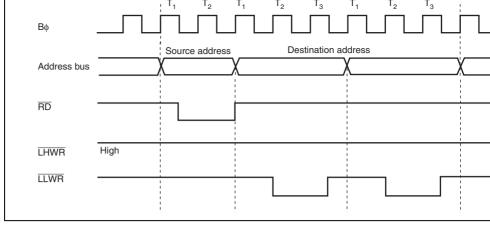

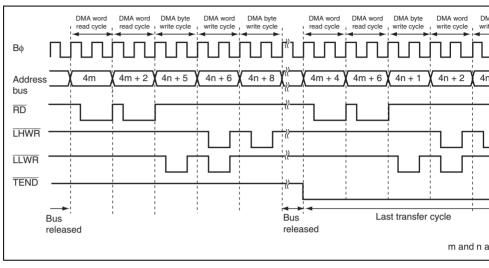

|     | 10.5.10     | Bus Cycles in Dual Address Mode                  |

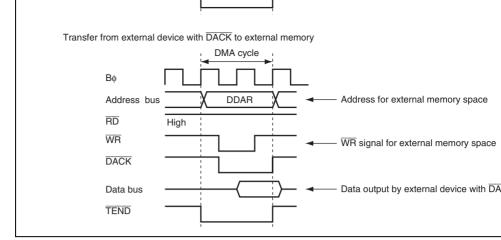

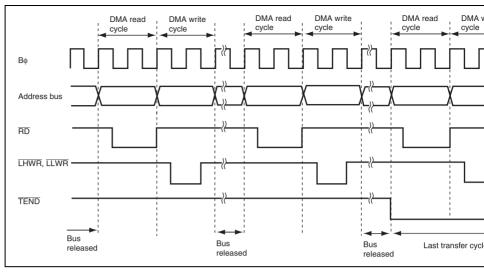

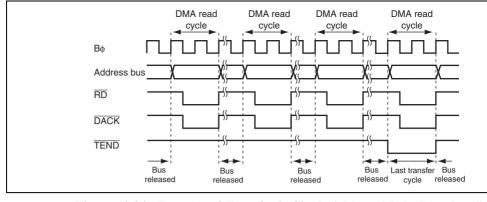

|     | 10.5.11     | Bus Cycles in Single Address Mode                |

| 10. | .6 DMA T    | ransfer End                                      |

| 10. | .7 Relation | nship among DMAC and Other Bus Masters           |

|     | 10.7.1      | CPU Priority Control Function Over DMAC          |

|     | 10.7.2      | Bus Arbitration among DMAC and Other Bus Masters |

| 10. | .8 Interrup | ot Sources                                       |

| 10. | -           | Notes                                            |

|     |             |                                                  |

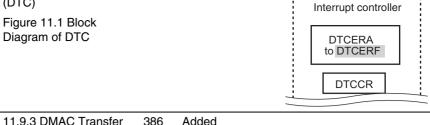

| Se  | ection 11   | Data Transfer Controller (DTC)                   |

| 11. |             | S                                                |

| 11. | .2 Registe  | r Descriptions                                   |

|     | C           |                                                  |

|     |             | Rev. 2.00 Sep. 10, 2008 Pa                       |

|     |             | RENESAS                                          |

|     |             | - (                                              |

|     |             |                                                  |

|     |             |                                                  |

|     |             |                                                  |

DMA Offset Register (DOFR)......

DMA Transfer Count Register (DTCR) ......

DMA Block Size Register (DBSR) .....

10.3.3

10.3.4

10.3.5

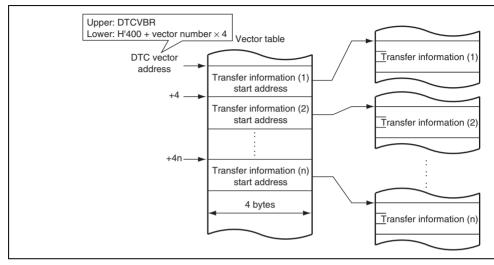

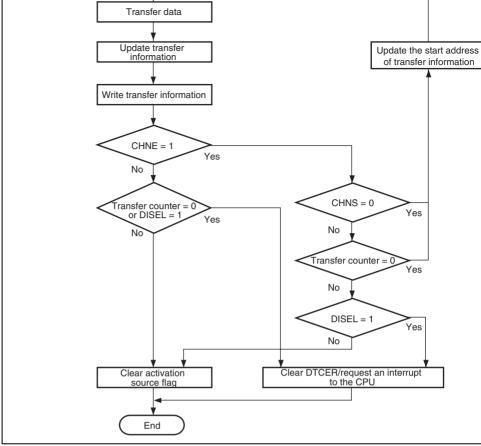

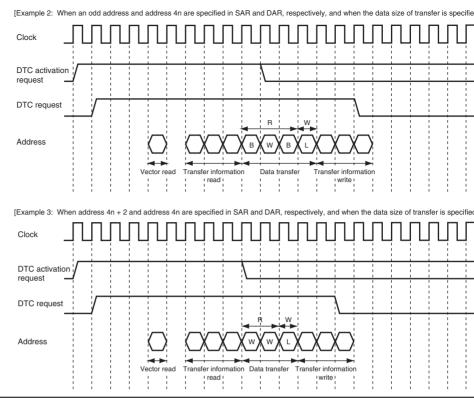

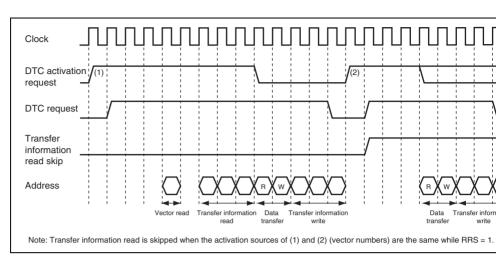

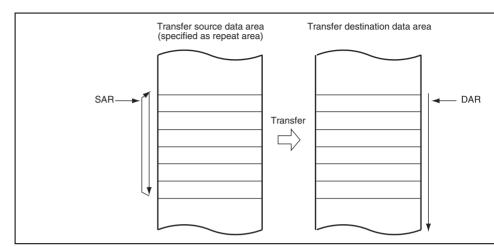

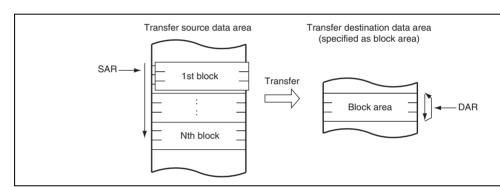

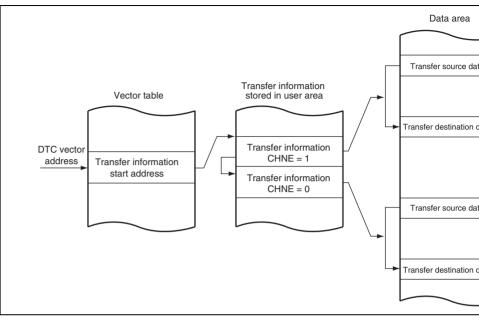

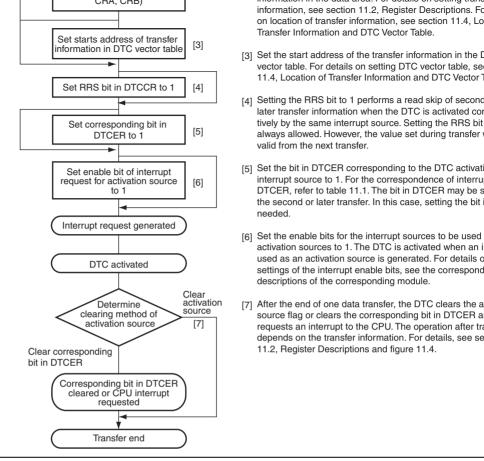

| Repeat Transfer Mode  Block Transfer Mode  Chain Transfer  Operation Timing  Number of DTC Execution Cycles  DTC Bus Release Timing  DTC Priority Level Control to the CPU  vation by Interrupt.  of Use of the DTC  Normal Transfer Mode  Chain Transfer  Chain Transfer when Counter = 0.  Sources  Module Stop State Setting |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chain Transfer Operation Timing Number of DTC Execution Cycles DTC Bus Release Timing DTC Priority Level Control to the CPU vation by Interrupt of Use of the DTC Normal Transfer Mode Chain Transfer Chain Transfer when Counter = 0.                                                                                          |

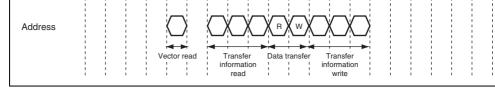

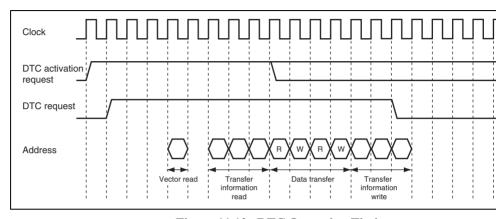

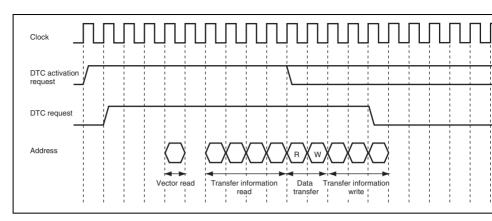

| Operation Timing                                                                                                                                                                                                                                                                                                                |

| Number of DTC Execution Cycles DTC Bus Release Timing DTC Priority Level Control to the CPU vation by Interrupt                                                                                                                                                                                                                 |

| DTC Bus Release Timing                                                                                                                                                                                                                                                                                                          |

| DTC Priority Level Control to the CPU vation by Interrupt                                                                                                                                                                                                                                                                       |

| DTC Priority Level Control to the CPU vation by Interrupt                                                                                                                                                                                                                                                                       |

| of Use of the DTC                                                                                                                                                                                                                                                                                                               |

| Normal Transfer Mode                                                                                                                                                                                                                                                                                                            |

| Chain Transfer                                                                                                                                                                                                                                                                                                                  |

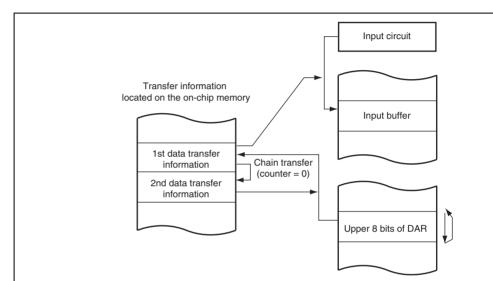

| Chain Transfer when Counter = 0                                                                                                                                                                                                                                                                                                 |

| Sourceses                                                                                                                                                                                                                                                                                                                       |

| res                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                 |

| Module Stop State Setting                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                 |

| On-Chip RAM                                                                                                                                                                                                                                                                                                                     |

| DMAC Transfer End Interrupt                                                                                                                                                                                                                                                                                                     |

| DTCE Bit Setting                                                                                                                                                                                                                                                                                                                |

| Chain Transfer                                                                                                                                                                                                                                                                                                                  |

| Transfer Information Start Address, Source Address, and Destination                                                                                                                                                                                                                                                             |

| Address                                                                                                                                                                                                                                                                                                                         |

| Transfer Information Modification                                                                                                                                                                                                                                                                                               |

| Endian Format                                                                                                                                                                                                                                                                                                                   |

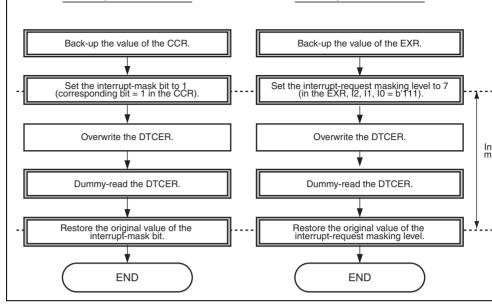

| Points for Caution when Overwriting DTCER                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                 |

11.5

11.5.1

11.5.2 11.5.3

Operation .....

Transfer Information Writeback Skip Function.....

|      | 12.2.7    | Port B                                                  |

|------|-----------|---------------------------------------------------------|

|      | 12.2.8    | Port D                                                  |

|      | 12.2.9    | Port E                                                  |

|      | 12.2.10   | Port F                                                  |

|      | 12.2.11   | Port H                                                  |

|      | 12.2.12   | Port I                                                  |

|      | 12.2.13   | Port J                                                  |

|      | 12.2.14   | Port K                                                  |

| 12.3 | Port Fund | ction Controller                                        |

|      | 12.3.1    | Port Function Control Register 0 (PFCR0)                |

|      | 12.3.2    | Port Function Control Register 1 (PFCR1)                |

|      | 12.3.3    | Port Function Control Register 2 (PFCR2)                |

|      | 12.3.4    | Port Function Control Register 4 (PFCR4)                |

|      | 12.3.5    | Port Function Control Register 6 (PFCR6)                |

|      | 12.3.6    | Port Function Control Register 7 (PFCR7)                |

|      | 12.3.7    | Port Function Control Register 9 (PFCR9)                |

|      | 12.3.8    | Port Function Control Register A (PFCRA)                |

|      | 12.3.9    | Port Function Control Register B (PFCRB)                |

|      | 12.3.10   | Port Function Control Register C (PFCRC)                |

|      | 12.3.11   | Port Function Control Register D (PFCRD)                |

| 12.4 | Usage No  | otes                                                    |

|      | 12.4.1    | Notes on Input Buffer Control Register (ICR) Setting    |

|      | 12.4.2    | Notes on Port Function Control Register (PFCR) Settings |

|      |           |                                                         |

|      |           |                                                         |

|      |           | Rev. 2.00 Sep. 10, 2008 Page                            |

|      |           | RENESAS                                                 |

|      |           | `                                                       |

|      |           |                                                         |

|      |           |                                                         |

Port 2

Port 3.....

Port 5.....

Port 6.....

Port A.....

12.2.2

12.2.3

12.2.4

12.2.5

12.2.6

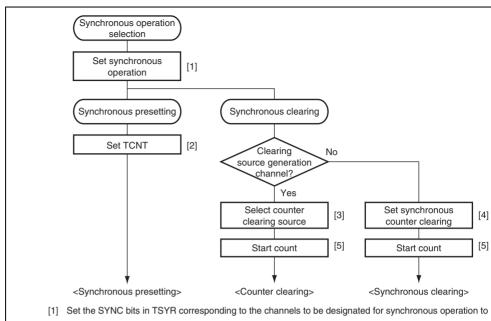

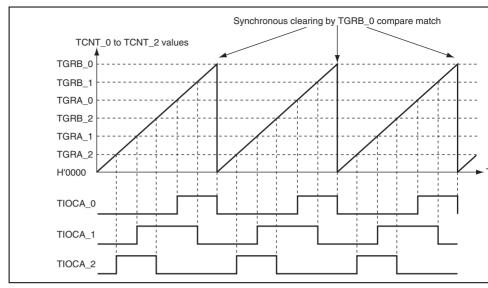

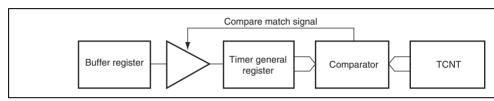

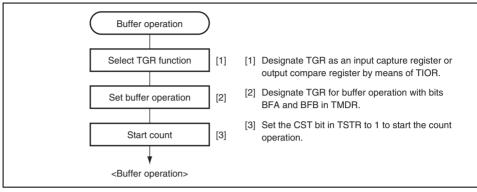

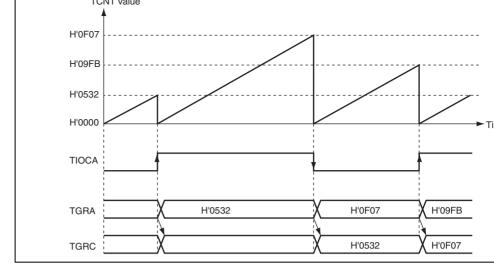

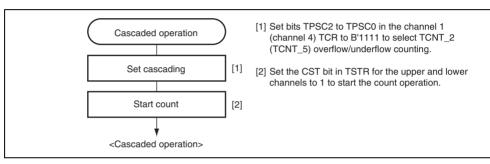

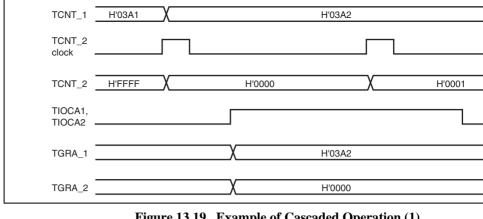

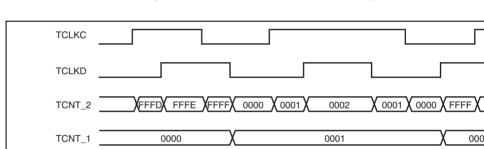

|       | 13.4.3    | Buffer Operation                                         |

|-------|-----------|----------------------------------------------------------|

|       | 13.4.4    | Cascaded Operation                                       |

|       | 13.4.5    | PWM Modes                                                |

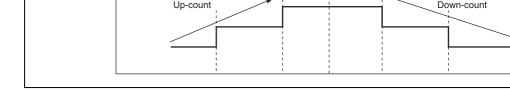

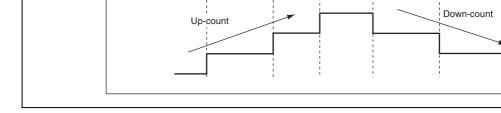

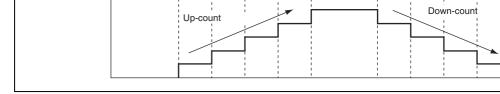

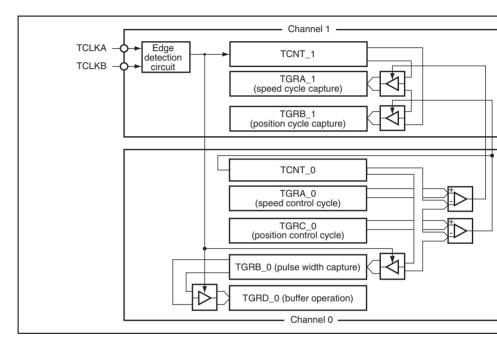

|       | 13.4.6    | Phase Counting Mode                                      |

| 13.5  | Interrupt | Sources                                                  |

| 13.6  | DTC Act   | ivation                                                  |

| 13.7  | DMAC A    | activation                                               |

| 13.8  | A/D Con   | verter Activation                                        |

| 13.9  | Operation | ı Timing                                                 |

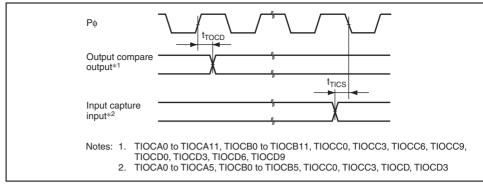

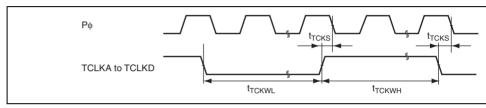

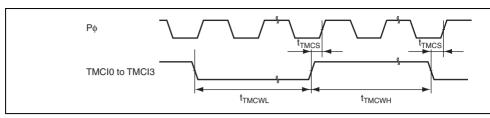

|       | 13.9.1    | Input/Output Timing                                      |

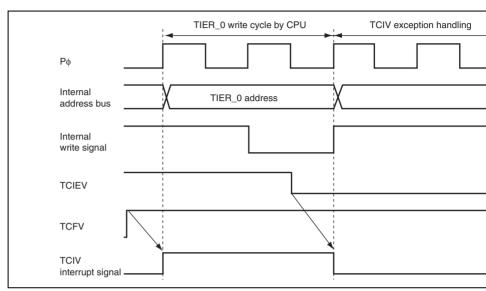

|       | 13.9.2    | Interrupt Signal Timing                                  |

| 13.10 | Usage No  | otes                                                     |

|       | 13.10.1   | Module Stop Function Setting                             |

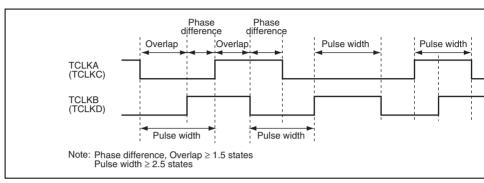

|       | 13.10.2   | Input Clock Restrictions                                 |

|       | 13.10.3   | Caution on Cycle Setting                                 |

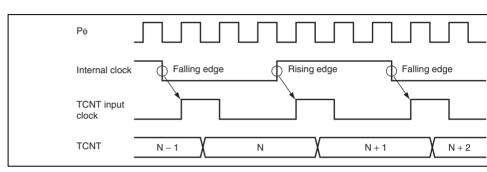

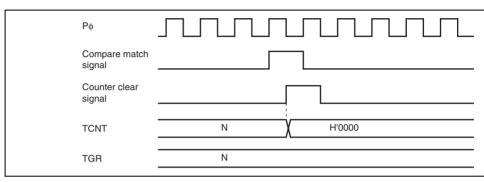

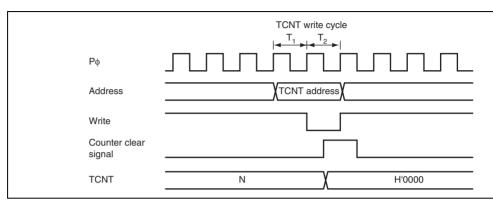

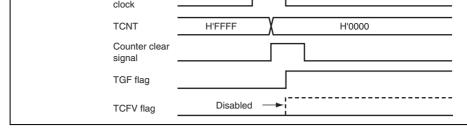

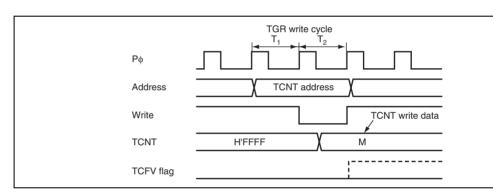

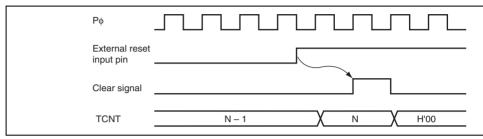

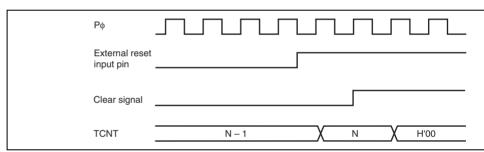

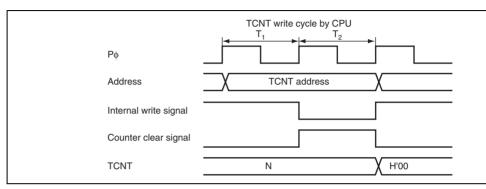

|       | 13.10.4   | Conflict between TCNT Write and Clear Operations         |

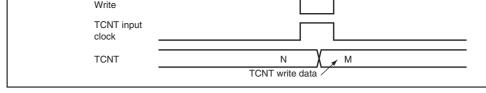

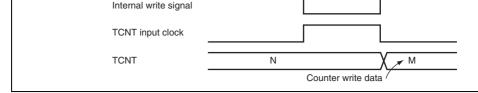

|       | 13.10.5   | Conflict between TCNT Write and Increment Operations     |

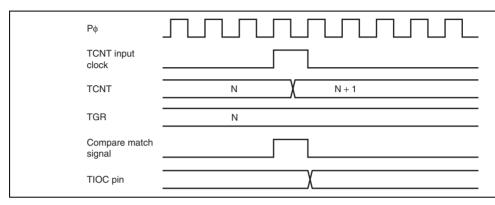

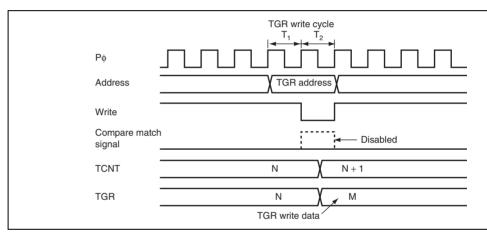

|       | 13.10.6   | Conflict between TGR Write and Compare Match             |

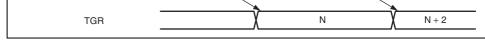

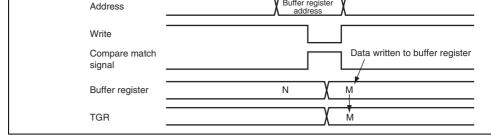

|       | 13.10.7   | Conflict between Buffer Register Write and Compare Match |

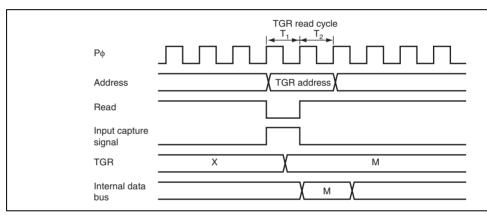

|       | 13.10.8   | Conflict between TGR Read and Input Capture              |

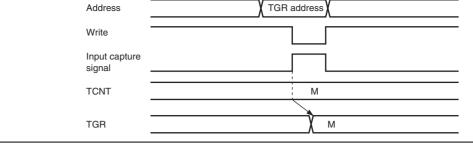

|       | 13.10.9   | Conflict between TGR Write and Input Capture             |

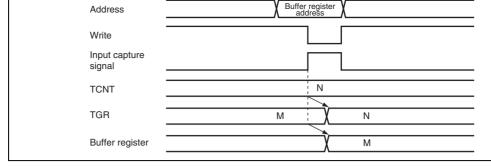

|       |           | Conflict between Buffer Register Write and Input Capture |

|       |           | Conflict between Overflow/Underflow and Counter Clearing |

|       | 13.10.12  | Conflict between TCNT Write and Overflow/Underflow       |

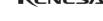

Timer Start Register (TSTR) .....

Timer Synchronous Register (TSYR).....

Operation .....

13.3.813.3.9

13.4.1

13.4.2

13.4

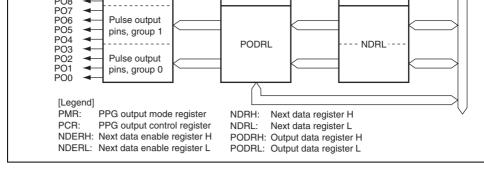

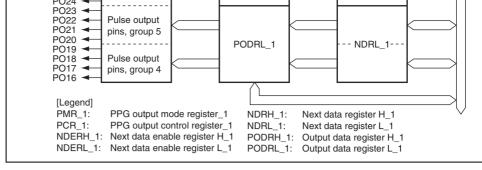

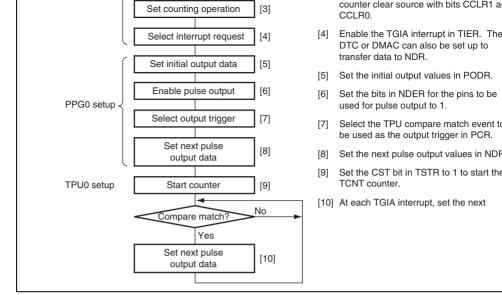

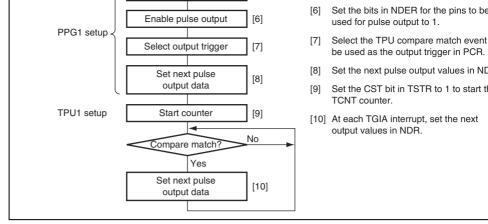

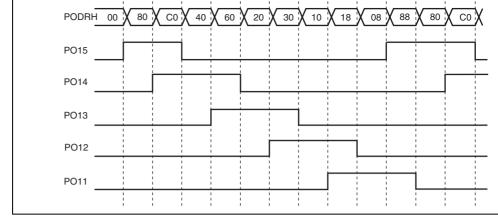

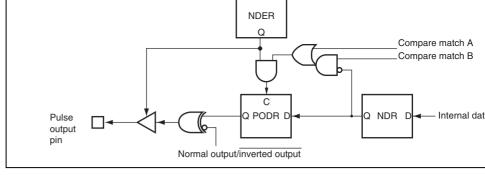

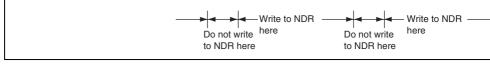

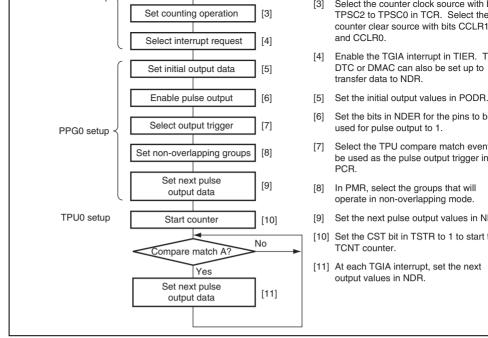

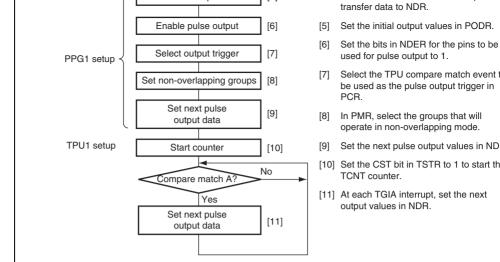

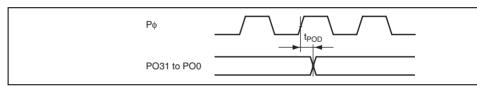

| 14.4.1    | Output Timing                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14.4.2    | Sample Setup Procedure for Normal Pulse Output                                                                                                                                                              |

| 14.4.3    | Example of Normal Pulse Output (Example of 5-Phase Pulse Output)                                                                                                                                            |

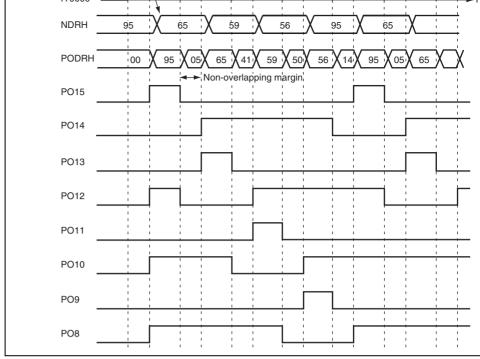

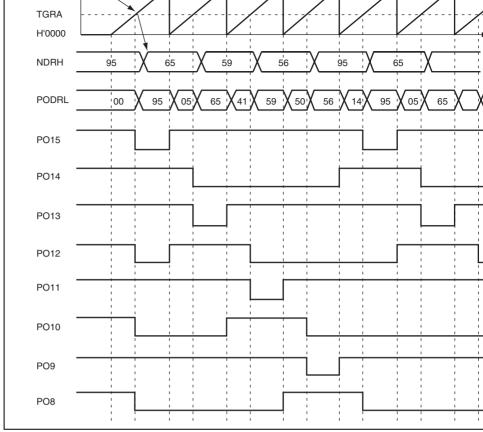

| 14.4.4    | Non-Overlapping Pulse Output                                                                                                                                                                                |

| 14.4.5    | Sample Setup Procedure for Non-Overlapping Pulse Output                                                                                                                                                     |

| 14.4.6    | Example of Non-Overlapping Pulse Output                                                                                                                                                                     |

|           | (Example of 4-Phase Complementary Non-Overlapping Pulse Output)                                                                                                                                             |

| 14.4.7    | Inverted Pulse Output                                                                                                                                                                                       |

| 14.4.8    | Pulse Output Triggered by Input Capture                                                                                                                                                                     |

| Usage N   | Notes                                                                                                                                                                                                       |

| 14.5.1    | Module Stop State Setting                                                                                                                                                                                   |

| 14.5.2    | Operation of Pulse Output Pins                                                                                                                                                                              |

| 14.5.3    | TPU Setting when PPG1 is in Use                                                                                                                                                                             |

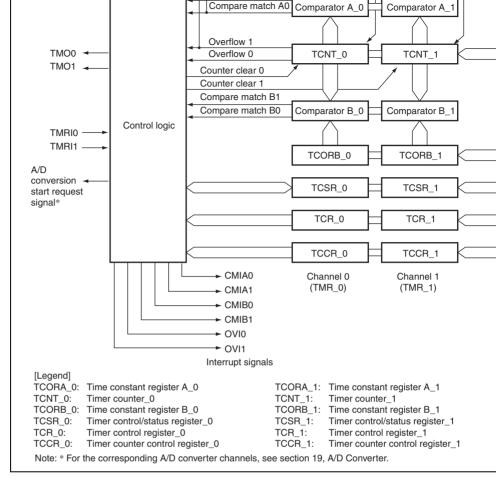

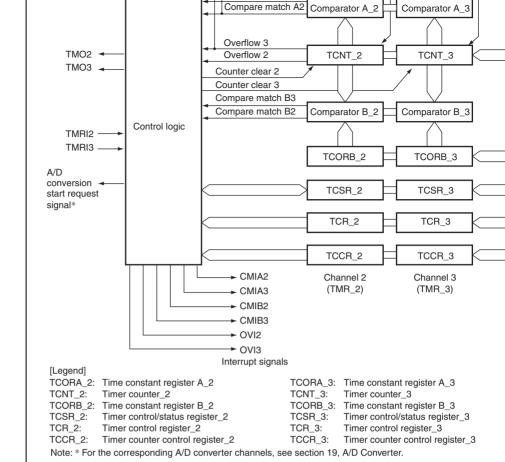

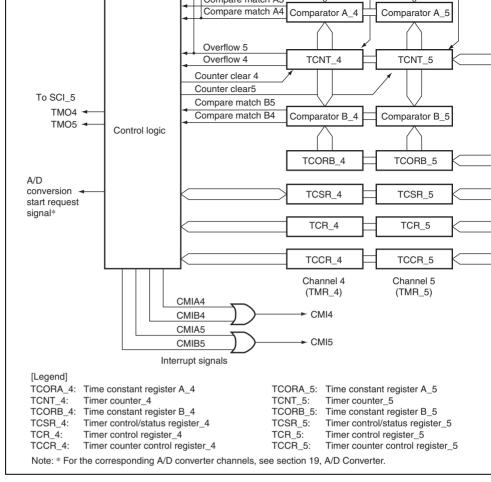

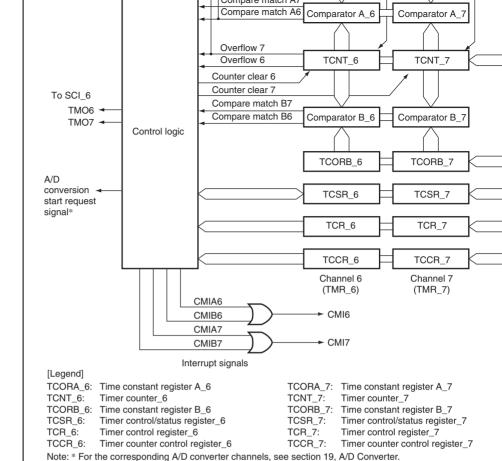

| Features  | 8-Bit Timers (TMR)<br>sutput Pins                                                                                                                                                                           |

| Register  | Descriptions                                                                                                                                                                                                |

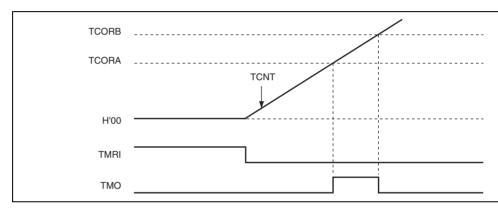

| 15.3.1    | Timer Counter (TCNT)                                                                                                                                                                                        |

| 15.3.2    | Time Constant Register A (TCORA)                                                                                                                                                                            |

| 15.3.3    | Time Constant Register B (TCORB)                                                                                                                                                                            |

| 15.3.4    | Timer Control Register (TCR)                                                                                                                                                                                |

| 15.3.5    | Timer Counter Control Register (TCCR)                                                                                                                                                                       |

| 15.3.6    | Timer Control/Status Register (TCSR)                                                                                                                                                                        |

| Operation | on                                                                                                                                                                                                          |

| 15 / 1    | Dulca Output                                                                                                                                                                                                |

| 15.4.1    | Pulse Output                                                                                                                                                                                                |

|           | 14.4.3<br>14.4.4<br>14.4.5<br>14.4.6<br>14.4.7<br>14.4.8<br>Usage N<br>14.5.1<br>14.5.2<br>14.5.3<br>on 15 S<br>Features<br>Input/O<br>Register<br>15.3.1<br>15.3.2<br>15.3.3<br>15.3.4<br>15.3.5<br>15.3.6 |

PPG Output Control Register (PCR)

PPG Output Mode Register (PMR) .....

Operation .....

14.3.4

14.3.5

14.4

| 15.8          | Usage N                                | otes                                                                                                          |

|---------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------|

|               | 15.8.1                                 | Notes on Setting Cycle                                                                                        |

|               | 15.8.2                                 | Conflict between TCNT Write and Counter Clear                                                                 |

|               | 15.8.3                                 | Conflict between TCNT Write and Increment                                                                     |

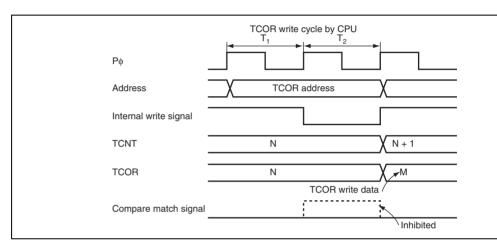

|               | 15.8.4                                 | Conflict between TCOR Write and Compare Match                                                                 |

|               | 15.8.5                                 | Conflict between Compare Matches A and B                                                                      |

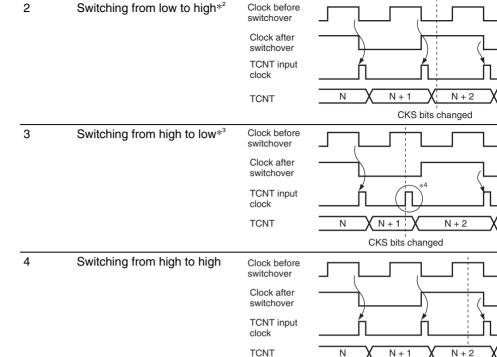

|               | 15.8.6                                 | Switching of Internal Clocks and TCNT Operation                                                               |

|               | 15.8.7                                 | Mode Setting with Cascaded Connection                                                                         |

|               | 15.8.8                                 | Module Stop State Setting                                                                                     |

|               | 15.8.9                                 | Interrupts in Module Stop State                                                                               |

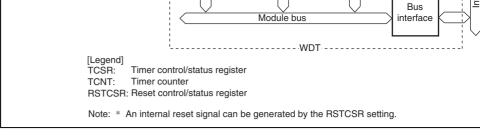

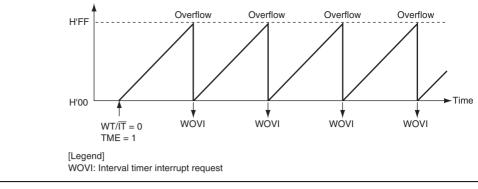

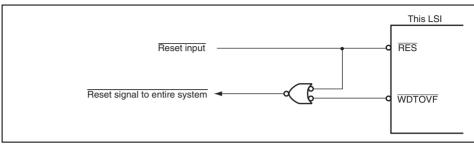

| Secti<br>16.1 |                                        | Watchdog Timer (WDT)                                                                                          |

| 16.2          |                                        |                                                                                                               |

| 1.0           | Input/Ou                               |                                                                                                               |

| 16.3          | _                                      | ıtput Pin                                                                                                     |

| 16.3          | _                                      | Descriptions                                                                                                  |

| 16.3          | Register                               | Descriptions                                                                                                  |

| 16.3          | Register 16.3.1                        | Descriptions                                                                                                  |

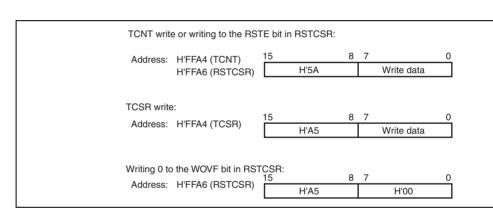

| 16.3          | Register<br>16.3.1<br>16.3.2<br>16.3.3 | Descriptions Timer Counter (TCNT) Timer Control/Status Register (TCSR) Reset Control/Status Register (RSTCSR) |

|               | Register<br>16.3.1<br>16.3.2<br>16.3.3 | Descriptions                                                                                                  |

Interrupt Source.....

Usage Notes.....

RENESAS

Notes on Register Access .....

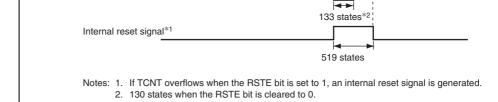

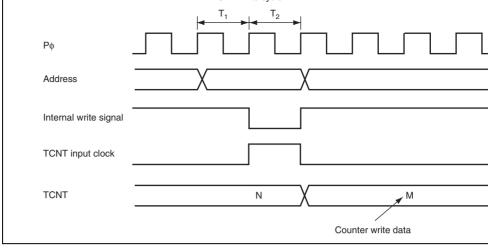

Conflict between Timer Counter (TCNT) Write and Increment.....

Changing Values of Bits CKS2 to CKS0.....

Interrupt Sources.....

15.7

16.5

16.6

16.6.1

16.6.2

16.6.3

Rev. 2.00 Sep. 10, 2008 Page xx of xxviii

15.7.1

15.7.2

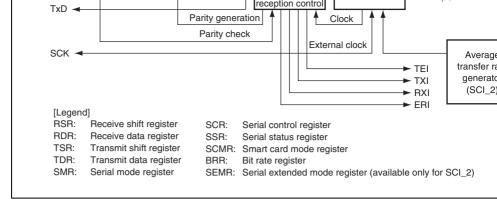

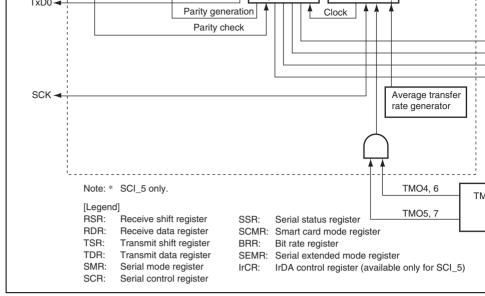

|      | 17.3.4   | Transmit Shift Register (TSR)                                    |

|------|----------|------------------------------------------------------------------|

|      | 17.3.5   | Serial Mode Register (SMR)                                       |

|      | 17.3.6   | Serial Control Register (SCR)                                    |

|      | 17.3.7   | Serial Status Register (SSR)                                     |

|      | 17.3.8   | Smart Card Mode Register (SCMR)                                  |

|      | 17.3.9   | Bit Rate Register (BRR)                                          |

|      | 17.3.10  | Serial Extended Mode Register (SEMR_2)                           |

|      | 17.3.11  | Serial Extended Mode Register 5 and 6 (SEMR_5 and SEMR_6)        |

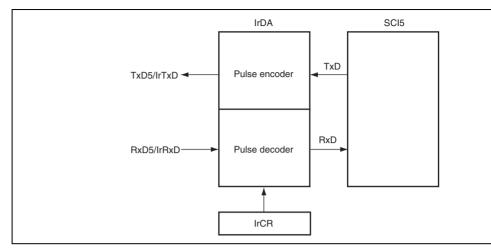

|      | 17.3.12  | IrDA Control Register (IrCR)                                     |

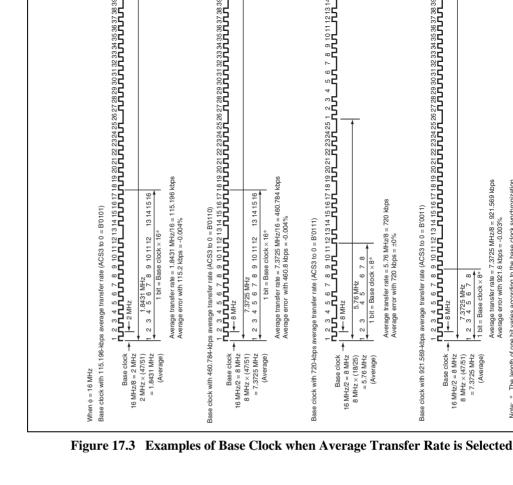

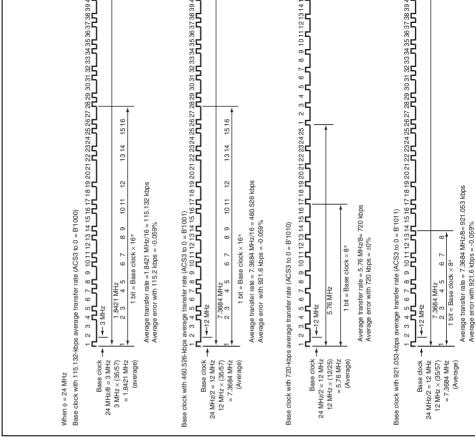

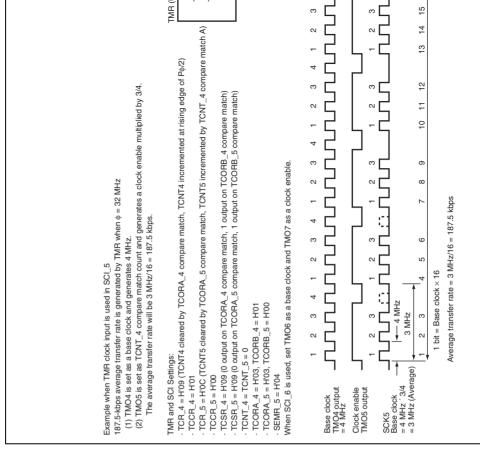

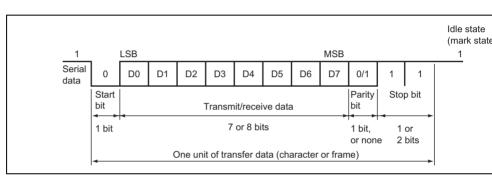

| 17.4 | Operatio | n in Asynchronous Mode                                           |

|      | 17.4.1   | Data Transfer Format                                             |

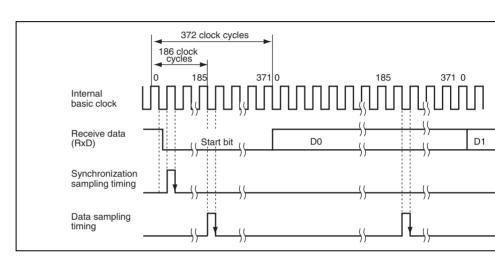

|      | 17.4.2   | Receive Data Sampling Timing and Reception Margin in Asynchronou |

|      |          | Mode                                                             |

|      | 17.4.3   | Clock                                                            |

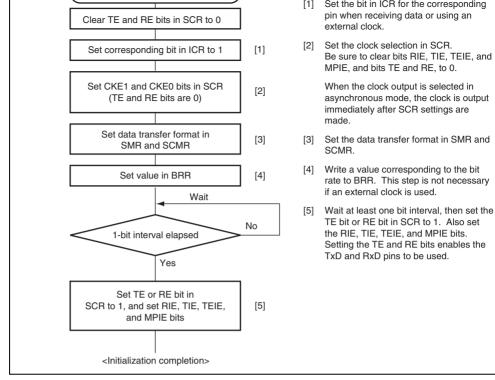

|      | 17.4.4   | SCI Initialization (Asynchronous Mode)                           |

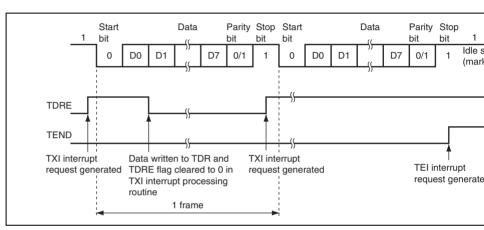

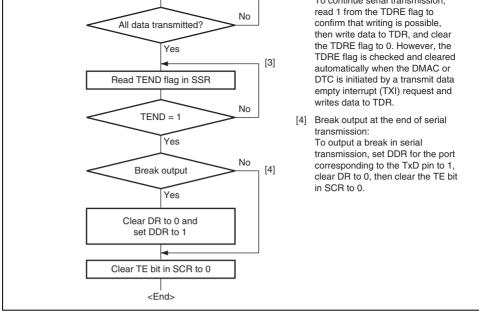

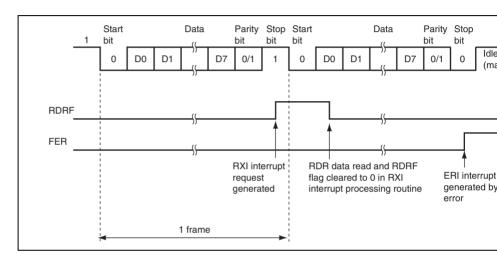

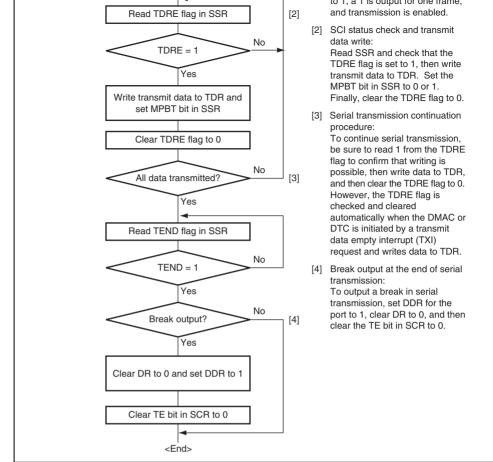

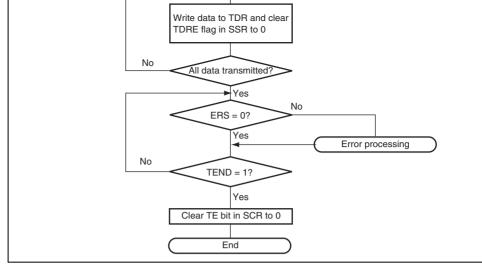

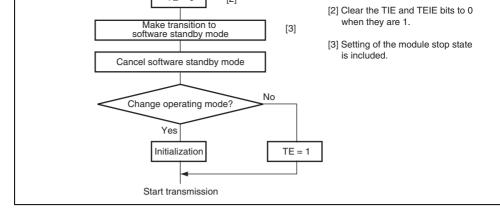

|      | 17.4.5   | Serial Data Transmission (Asynchronous Mode)                     |

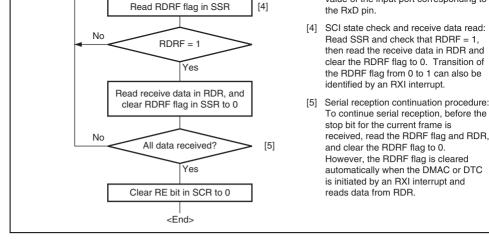

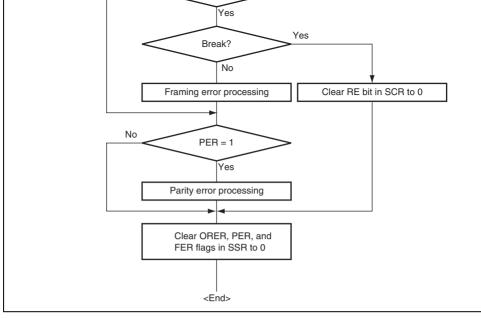

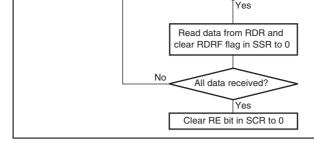

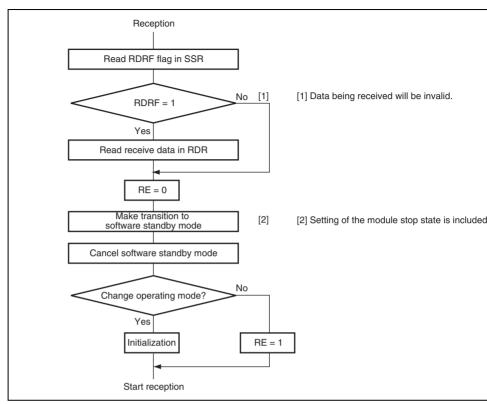

|      | 17.4.6   | Serial Data Reception (Asynchronous Mode)                        |

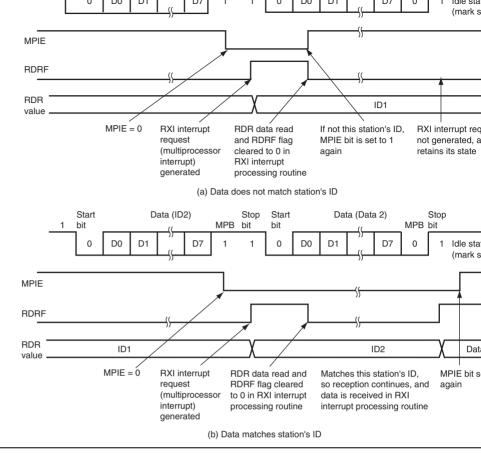

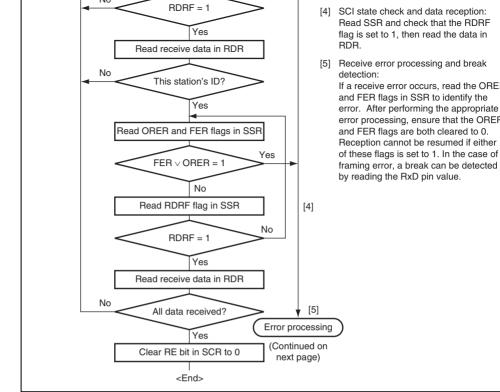

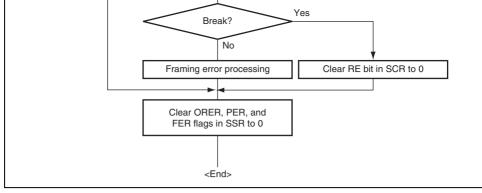

| 17.5 | Multipro | cessor Communication Function                                    |

|      | 17.5.1   | Multiprocessor Serial Data Transmission                          |

|      | 17.5.2   | Multiprocessor Serial Data Reception                             |

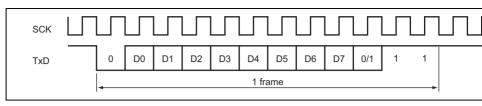

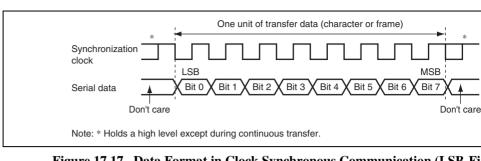

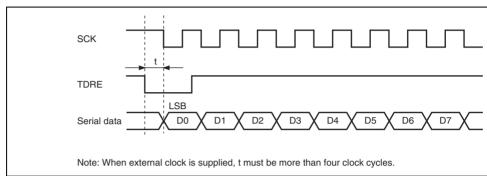

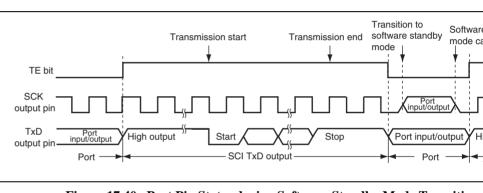

| 17.6 | Operatio | n in Clock Synchronous Mode                                      |

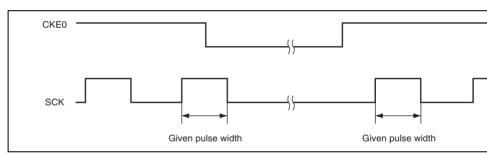

|      | 17.6.1   | Clock                                                            |

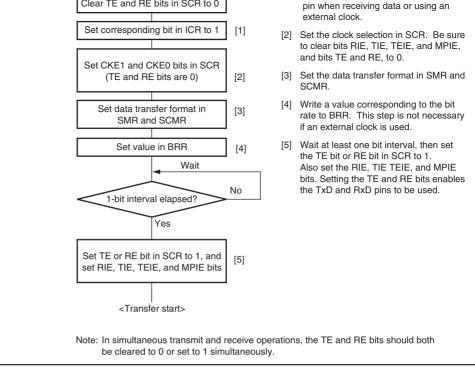

|      | 17.6.2   | SCI Initialization (Clock Synchronous Mode)                      |

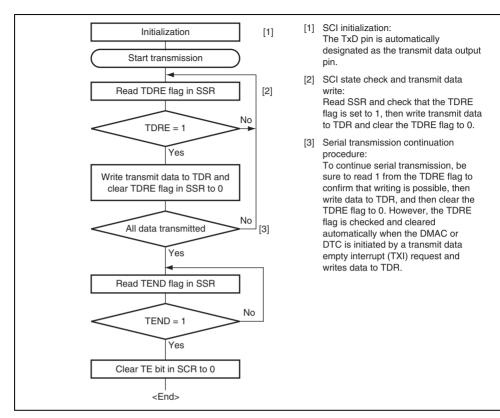

|      | 17.6.3   | Serial Data Transmission (Clock Synchronous Mode)                |

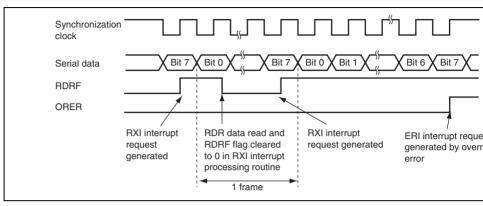

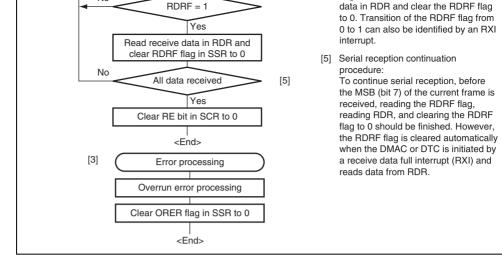

|      | 17.6.4   | Serial Data Reception (Clock Synchronous Mode)                   |

|      | 17.6.5   | Simultaneous Serial Data Transmission and Reception              |

|      |          | (Clock Synchronous Mode)                                         |

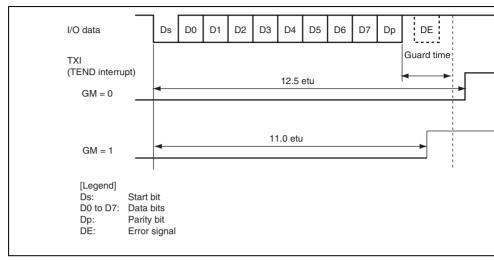

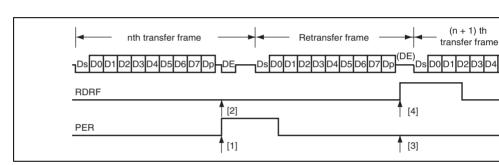

| 17.7 | Operatio | n in Smart Card Interface Mode                                   |

|      |          |                                                                  |

|      |          | Rev. 2.00 Sep. 10, 2008 Pag                                      |

|      |          | RENESAS                                                          |

|      |          |                                                                  |

|      |          |                                                                  |

Transmit Data Register (TDR).....

17.3.3

|       |                  | 1                                                      |  |  |

|-------|------------------|--------------------------------------------------------|--|--|

| 17.10 | Usage N          | otes                                                   |  |  |

|       | 17.10.1          | Module Stop State Setting                              |  |  |

|       | 17.10.2          | Break Detection and Processing                         |  |  |

|       | 17.10.3          | Mark State and Break Detection                         |  |  |

|       | 17.10.4          | Receive Error Flags and Transmit Operations            |  |  |

|       |                  | (Clock Synchronous Mode Only)                          |  |  |

|       | 17.10.5          | Relation between Writing to TDR and TDRE Flag          |  |  |

|       | 17.10.6          | Restrictions on Using DTC or DMAC                      |  |  |

|       | 17.10.7          | SCI Operations during Power-Down State                 |  |  |

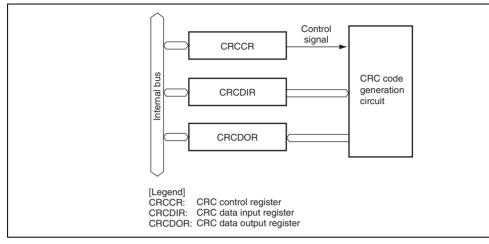

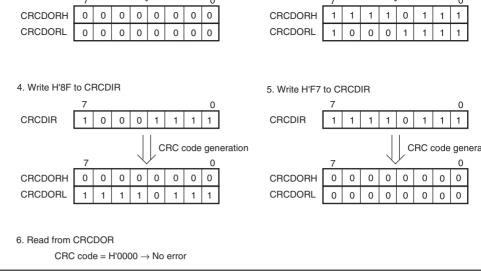

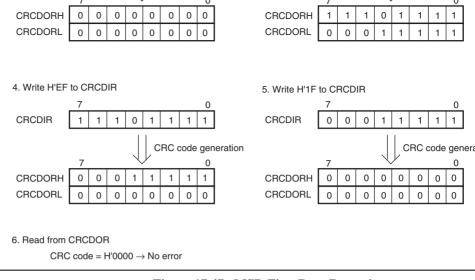

| 17.11 | CRC Op           | eration Circuit                                        |  |  |

|       | 17.11.1          | Features                                               |  |  |

|       | 17.11.2          | Register Descriptions                                  |  |  |

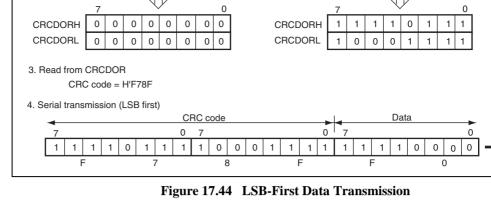

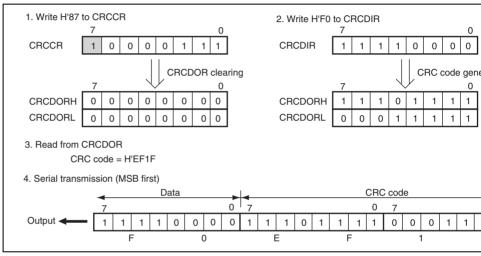

|       | 17.11.3          | CRC Operation Circuit Operation                        |  |  |

|       | 17.11.4          | Note on CRC Operation Circuit                          |  |  |

|       |                  |                                                        |  |  |

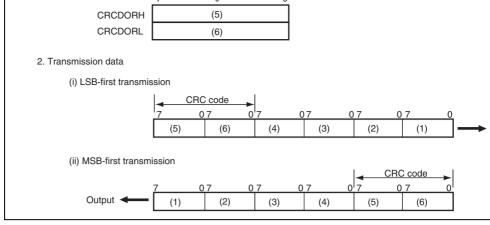

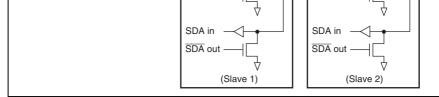

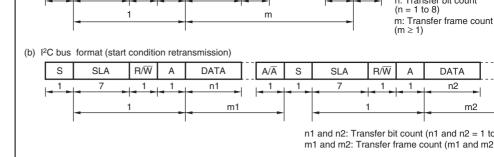

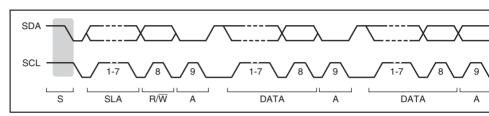

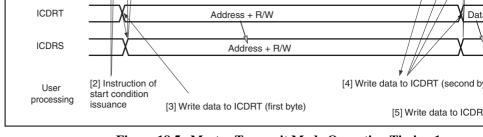

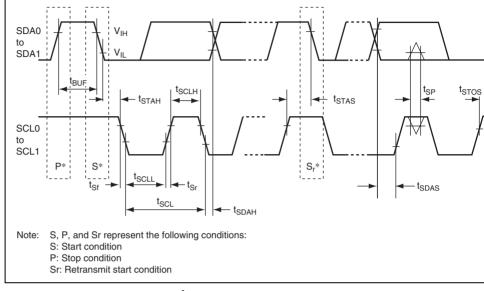

| Secti | on 18 I          | <sup>2</sup> C Bus Interface 2 (IIC2)                  |  |  |

| 18.1  | Features         | eatures                                                |  |  |

| 18.2  | Input/Ou         | ıtput Pins                                             |  |  |

| 18.3  | Register         | Descriptions                                           |  |  |

|       | 18.3.1           | I <sup>2</sup> C Bus Control Register A (ICCRA)        |  |  |

|       | 18.3.2           | I <sup>2</sup> C Bus Control Register B (ICCRB)        |  |  |

|       | 18.3.3           | I <sup>2</sup> C Bus Mode Register (ICMR)              |  |  |

|       | 18.3.4           | I <sup>2</sup> C Bus Interrupt Enable Register (ICIER) |  |  |

|       |                  | Te bus interrupt Enuoie Register (TelEit)              |  |  |

|       | 18.3.5           |                                                        |  |  |

|       | 18.3.5<br>18.3.6 | I <sup>2</sup> C Bus Status Register (ICSR)            |  |  |

|       |                  | I <sup>2</sup> C Bus Status Register (ICSR)            |  |  |

|       | 18.3.6           | I <sup>2</sup> C Bus Status Register (ICSR)            |  |  |

18.3.9

Rev. 2.00 Sep. 10, 2008 Page xxii of xxviii

Interrupts in Smart Card Interface Mode.....

I<sup>2</sup>C Bus Shift Register (ICDRS).....

RENESAS

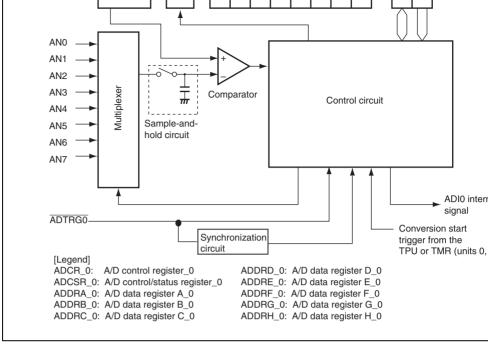

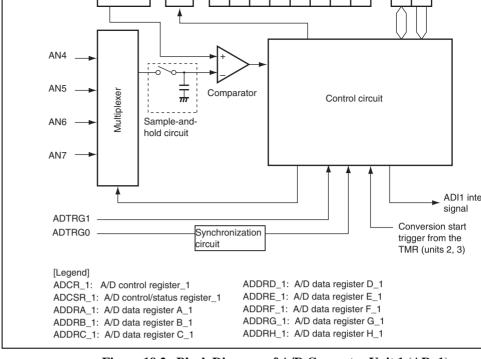

| 19.3 | Register Descriptions |                                                     |  |  |

|------|-----------------------|-----------------------------------------------------|--|--|

|      | 19.3.1                | A/D Data Registers A to H (ADDRA to ADDRH)          |  |  |

|      | 19.3.2                | A/D Control/Status Register for Unit 0 (ADCSR_0)    |  |  |

|      | 19.3.3                | A/D Control/Status Register for Unit 1 (ADCSR_1)    |  |  |

|      | 19.3.4                | A/D Control Register for Unit 0 (ADCR_0)            |  |  |

|      | 19.3.5                | A/D Control Register for Unit 1 (ADCR_1)            |  |  |

| 19.4 | Operatio              | n                                                   |  |  |

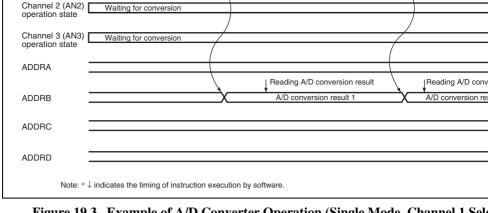

|      | 19.4.1                | Single Mode                                         |  |  |

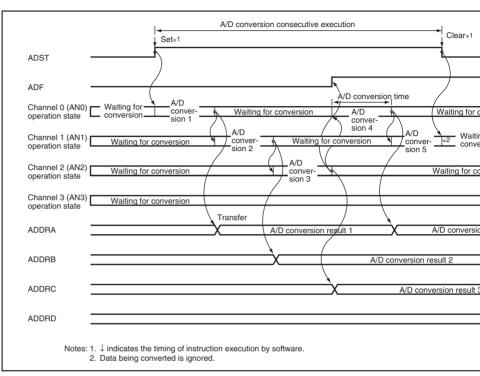

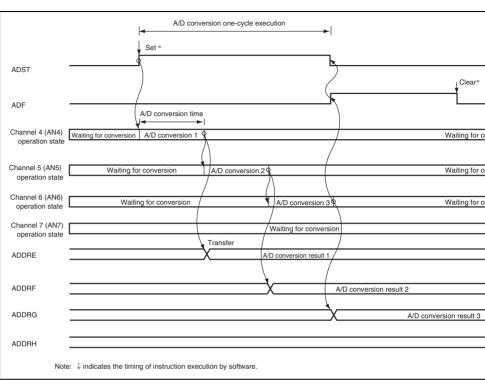

|      | 19.4.2                | Scan Mode                                           |  |  |

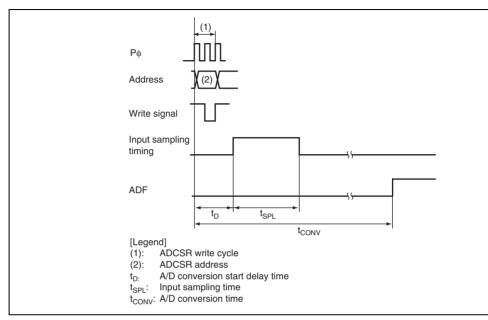

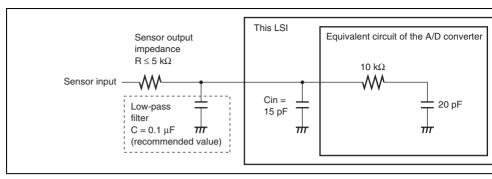

|      | 19.4.3                | Input Sampling and A/D Conversion Time              |  |  |

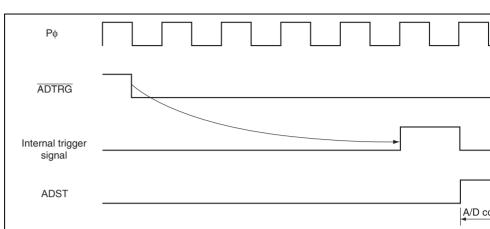

|      | 19.4.4                | External Trigger Input Timing                       |  |  |

| 19.5 | Interrupt             | Source                                              |  |  |

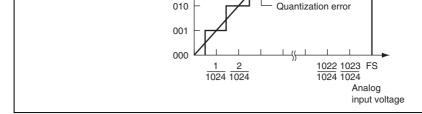

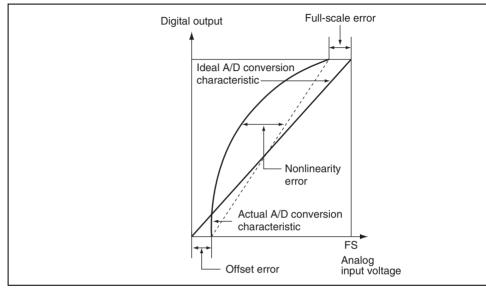

| 19.6 |                       | version Accuracy Definitions                        |  |  |

|      |                       | otes                                                |  |  |

|      | 19.7.1                | Module Stop Function Setting                        |  |  |

|      | 19.7.2                | A/D Input Hold Function in Software Standby Mode    |  |  |

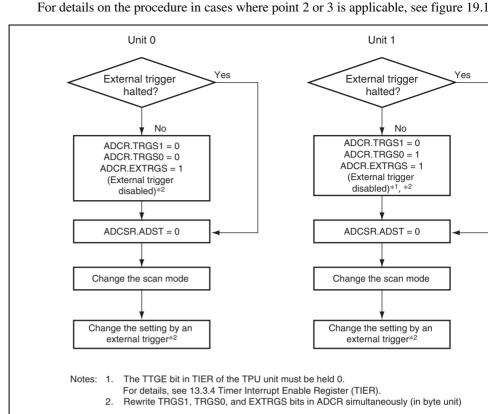

|      | 19.7.3                | Notes on A/D Activation by an External Trigger      |  |  |

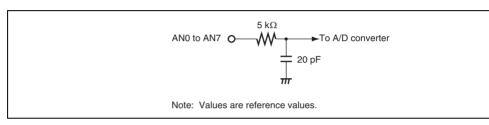

|      | 19.7.4                | Permissible Signal Source Impedance                 |  |  |

|      | 19.7.5                | Influences on Absolute Accuracy                     |  |  |

|      | 19.7.6                | Setting Range of Analog Power Supply and Other Pins |  |  |

|      |                       |                                                     |  |  |

Section 19 A/D Converter.....

19.2

19.7.7

19.7.8

Features

Input/Output Pins

| Se  | ection 2 | 1 RAM                             |  |  |  |

|-----|----------|-----------------------------------|--|--|--|

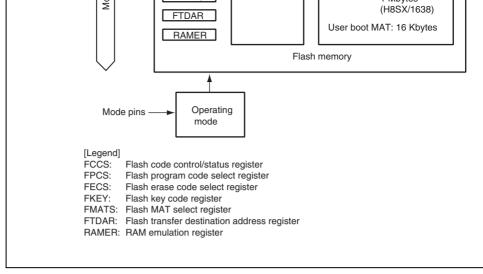

| Se  | ection 2 | 2 Flash Memory                    |  |  |  |

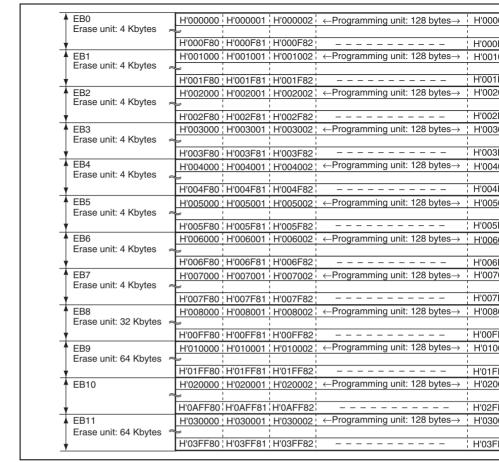

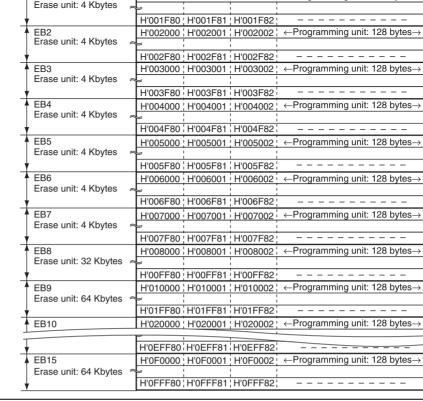

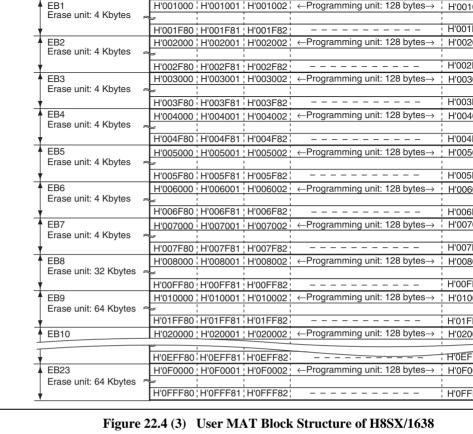

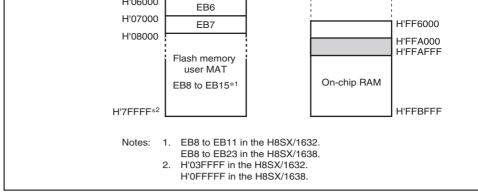

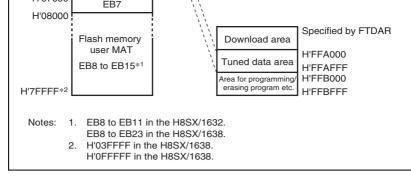

| 22. |          | ures                              |  |  |  |

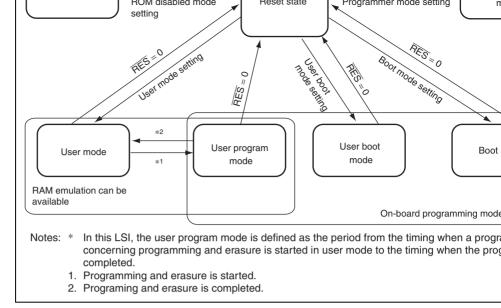

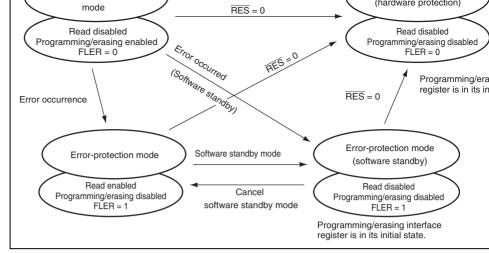

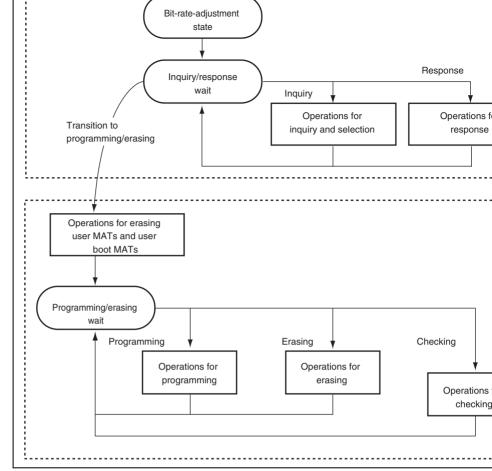

| 22. |          | Mode Transition Diagram           |  |  |  |

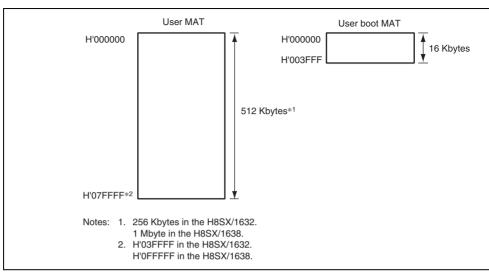

| 22. |          | Memory MAT Configuration          |  |  |  |

| 22. |          | Block Structure                   |  |  |  |

|     | 22.4     |                                   |  |  |  |

|     | 22.4     | .2 Block Diagram of H8SX/1634     |  |  |  |

|     |          | .3 Block Diagram of H8SX/1638     |  |  |  |

| 22. | .5 Prog  | gramming/Erasing Interface        |  |  |  |

| 22. |          | Input/Output Pins                 |  |  |  |

| 22. |          | Register Descriptions             |  |  |  |

|     | 22.7     |                                   |  |  |  |

|     | 22.7     |                                   |  |  |  |

|     | 22.7     | .3 RAM Emulation Register (RAMER) |  |  |  |

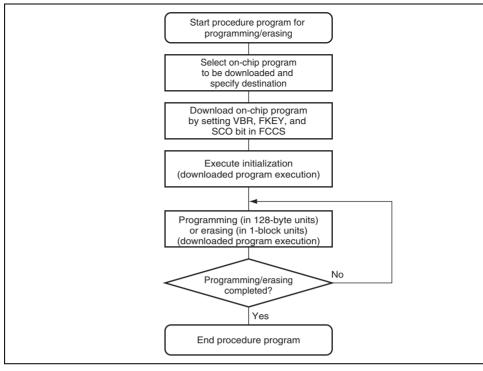

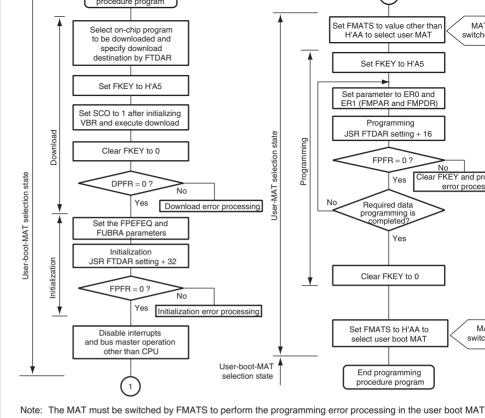

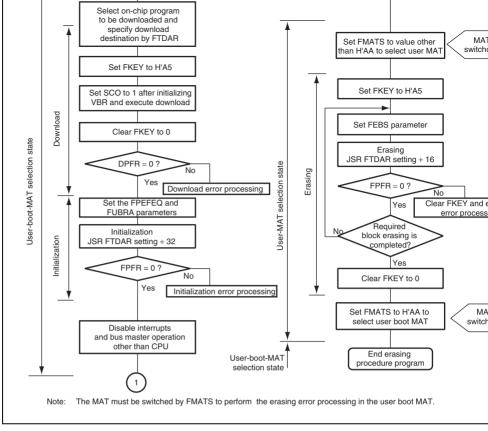

| 22. | .8 On-   | Board Programming Mode            |  |  |  |

Notes on Deep Software Standby Mode .....

Rev. 2.00 Sep. 10, 2008 Page xxiv of xxviii

20.5.3

22.8.1 22.8.2

22.8.3

22.8.4

22.9.1

22.9.2

22.9.3

22.9

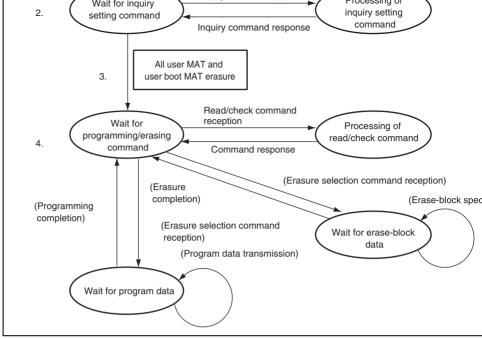

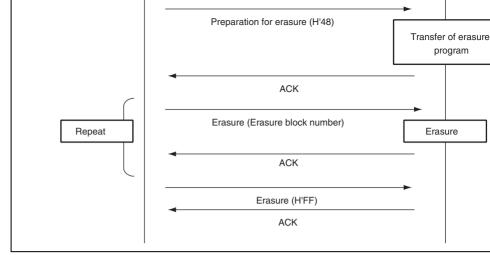

Boot Mode.....

User Program Mode.....

User Boot Mode....

On-Chip Program and Storable Area for Program Data .....

Hardware Protection

Software Protection....

Error Protection

Protection.....

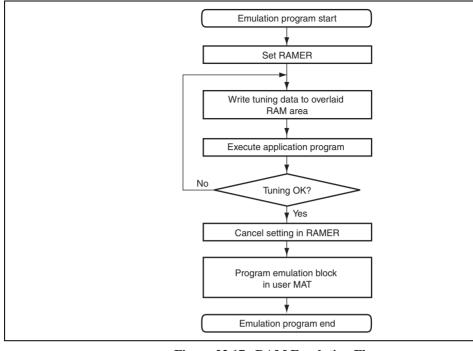

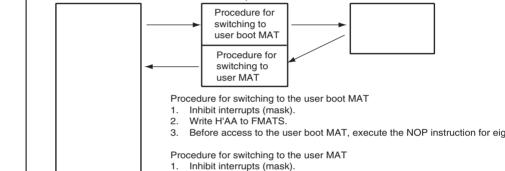

22.10 Flash Memory Emulation Using RAM.....22.11 Switching between User MAT and User Boot MAT.....

|       | 22.5.2    | C 1                                                         |

|-------|-----------|-------------------------------------------------------------|

|       | 23.5.2    | Commands                                                    |

| 23.6  | Usage No  | otes                                                        |

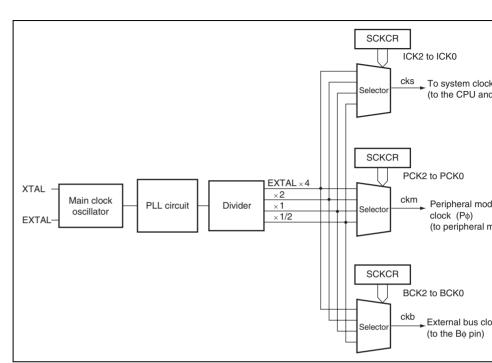

| Secti | on 24 C   | Clock Pulse Generator                                       |

| 24.1  | Register  | Description                                                 |

|       | 24.1.1    | System Clock Control Register (SCKCR)                       |

| 24.2  | Oscillato | vr                                                          |

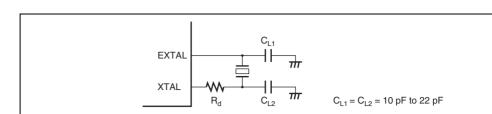

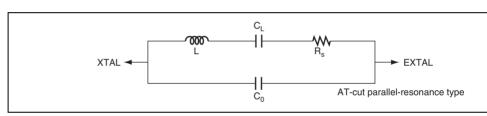

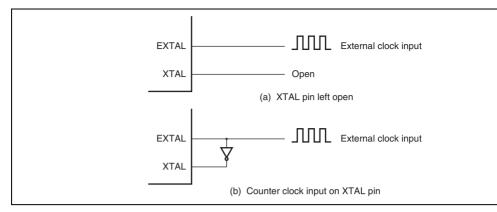

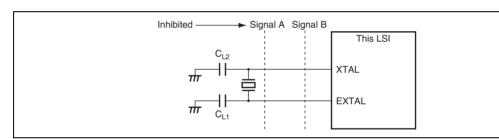

|       | 24.2.1    | Connecting Crystal Resonator                                |

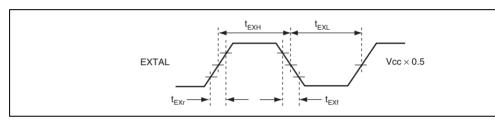

|       | 24.2.2    | External Clock Input                                        |

| 24.3  | PLL Circ  | cuit                                                        |

| 24.4  | Frequenc  | y Divider                                                   |

| 24.5  | Usage No  | otes                                                        |

|       | 24.5.1    | Notes on Clock Pulse Generator                              |

|       | 24.5.2    | Notes on Resonator                                          |

|       | 24.5.3    | Notes on Board Design                                       |

| ~ .   | 25 5      |                                                             |

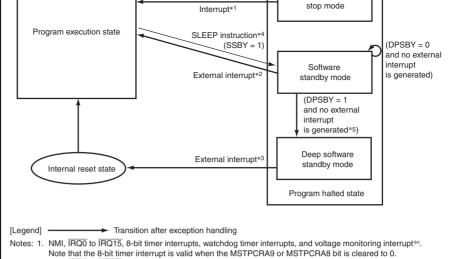

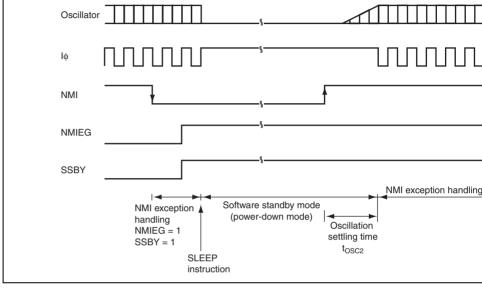

|       |           | Power-Down Modes                                            |

| 25.1  |           |                                                             |

| 25.2  | _         | Descriptions (GDVGD)                                        |

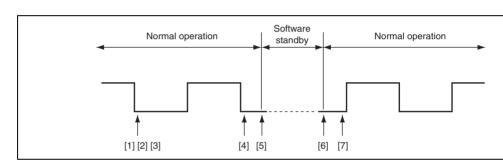

|       | 25.2.1    | Standby Control Register (SBYCR)                            |

|       | 25.2.2    | Module Stop Control Registers A and B (MSTPCRA and MSTPCRB) |

|       | 25.2.3    | Module Stop Control Register C (MSTPCRC)                    |

|       | 25.2.4    | Deep Standby Control Register (DPSBYCR)                     |

|       | 25.2.5    | Deep Standby Wait Control Register (DPSWCR)                 |

|       | 25.2.6    | Deep Standby Interrupt Enable Register (DPSIER)             |

|       |           | Rev. 2.00 Sep. 10, 2008 Pag                                 |

|       |           | RENESAS                                                     |

|       |           |                                                             |

|       |           |                                                             |

|       |           |                                                             |

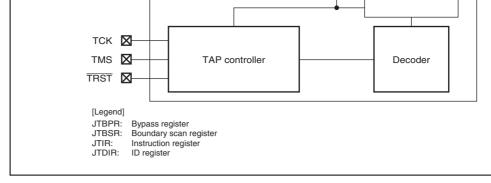

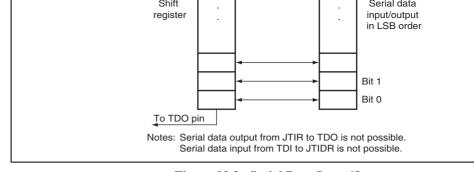

Boundary Scan Register (JTBSR).....

IDCODE Register (JTID)

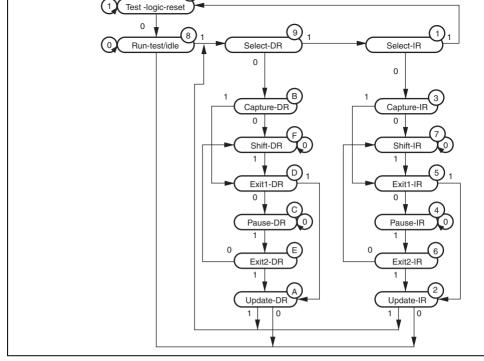

TAP Controller

Operations.....

23.4.3

23.4.4

23.5.1

23.5

|     |           | · · · · · · · · · · · · · · · · · · ·                                  |

|-----|-----------|------------------------------------------------------------------------|

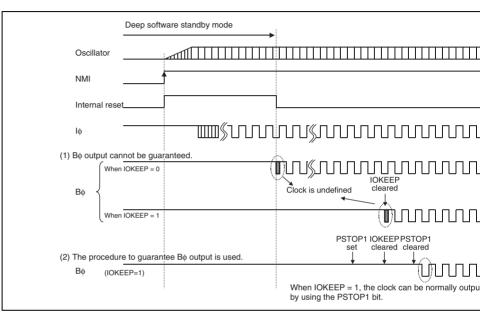

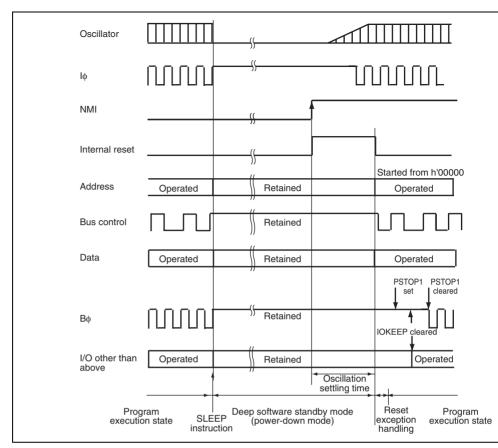

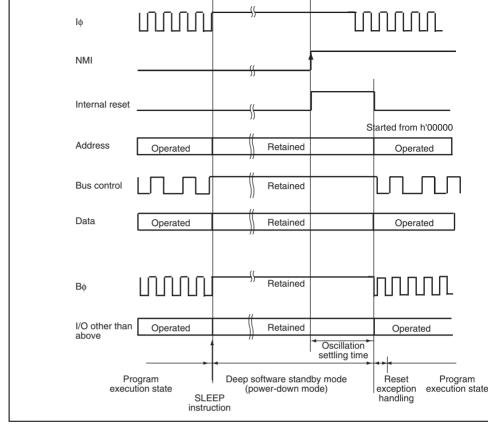

|     | 25.8.2    | 2 Exit from Deep Software Standby Mode                                 |

|     | 25.8.3    | Pin State on Exit from Deep Software Standby Mode                      |

|     | 25.8.4    | Bφ Operation after Exit from Deep Software Standby Mode                |

|     | 25.8.5    | Setting Oscillation Settling Time after Exit from Deep Software Standb |

|     |           | Mode                                                                   |

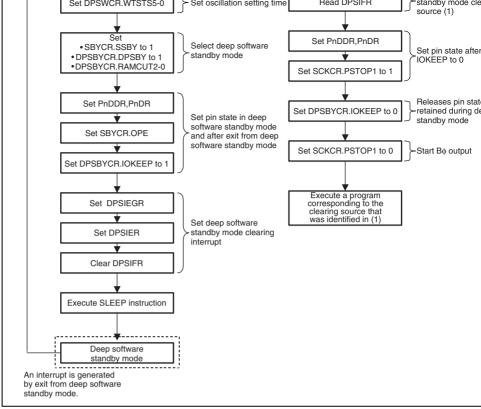

|     | 25.8.6    | Deep Software Standby Mode Application Example                         |

|     | 25.8.7    | Flowchart of Deep Software Standby Mode Operation                      |

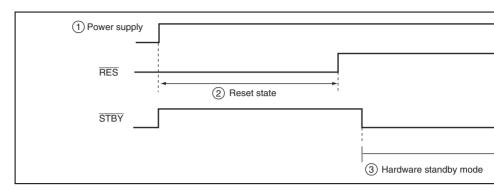

| 25. | .9 Hardy  | vare Standby Mode                                                      |

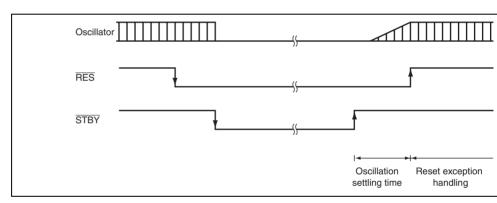

|     | 25.9.1    | Transition to Hardware Standby Mode                                    |

|     | 25.9.2    | Clearing Hardware Standby Mode                                         |

|     | 25.9.3    | Hardware Standby Mode Timing                                           |

|     | 25.9.4    | Timing Sequence at Power-On                                            |

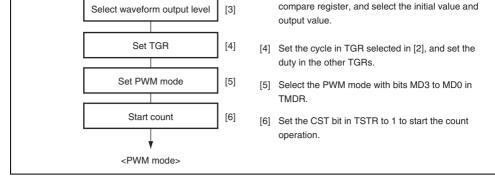

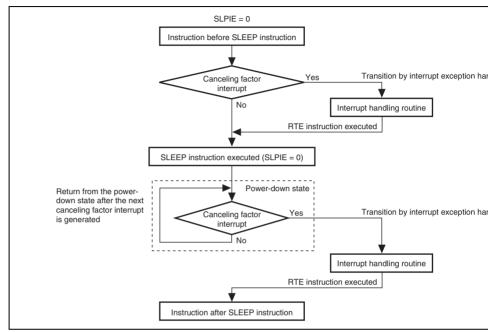

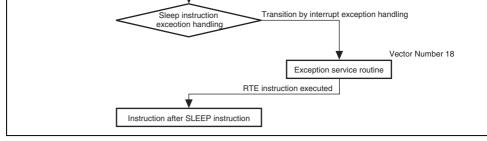

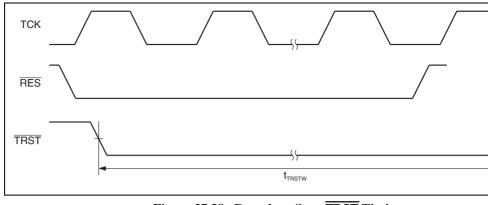

| 25. | .10 Sleep | Instruction Exception Handling                                         |