### **Advance Information**

MC92460EC/D Rev. 1.0, 5/2002

MC92460 HDLC Controller Hardware Specifications

NCSD Applications

This document contains detailed information on power considerations, DC/AC electrical characteristics, and AC timing specifications for the MC92460 Multichannel HDLC Controller.

The following topics are addressed:

| Topic                                                 | Page |

|-------------------------------------------------------|------|

| Section 1.1, "Features"                               | 2    |

| Section 1.2, "Electrical and Thermal Characteristics" | 4    |

| Section 1.2.1, "DC Electrical Characteristics"        | 4    |

| Section 1.2.2, "Thermal Characteristics"              | 6    |

| Section 1.2.3, "Power Considerations"                 | 6    |

| Section 1.2.4, "Power Dissipation"                    | 6    |

| Section 1.2.5, "AC Specifications"                    | 7    |

| Section 1.2.5.1, "SYSCLK Timing"                      | 7    |

| Section 1.2.5.2, "EXCLK Timing"                       | 7    |

| Section 1.2.5.3, "AC Timing"                          | 8    |

| Section 1.3, "Pinout"                                 | 11   |

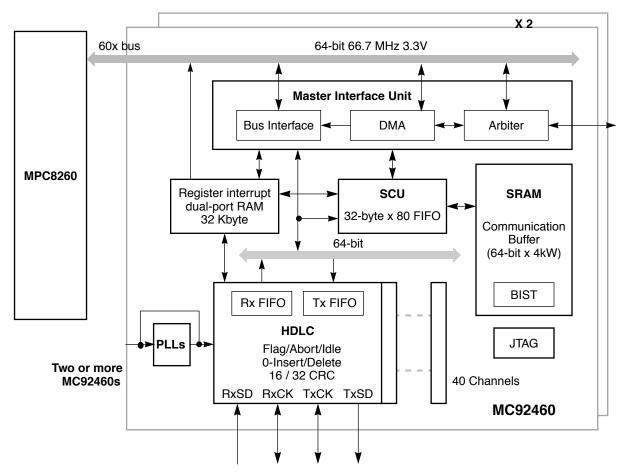

Figure 1 shows a block diagram of the MC92460.

Figure 1. MC92460 Block Diagram

# 1.1 Features

The following is an overview of the MC92460 feature set:

- Channels

- 40 full-duplex HDLC channels

- Programmable channel assignment (any logical channel to any signal)

- Each channel has a default of 64 buffer descriptors (Rx and Tx) but the number of buffer descriptors per channel is configurable

- Controllers

- Maximum throughput of 1919 Mbps; individual controllers operate up to 66.7 Mbps

- All communication controllers operate asynchronously

- Programmable frame size (maximum 65,535 bytes)

- Transparent memory access with internal memory controller

- 60x Bus

- MC92460 directly connects with a 64-bit data and 32-bit address 60x bus

- Supports 66.7 MHz 60x bus speed, with aggregate bandwidth of up to 1919 Mbps depending

- on the type of main memory used

- Up to four MC92460's may be connected in parallel on the 60x bus

- Bus supports multiple master design

- Communication Buffers

- Data Buffer

- 256 Kbits on-chip memory for data buffers

- 256 Kbit communication buffer can store up to 819 bytes per frame.

- 80 channel virtual DMA functionality executes between off-chip memory and the communication buffer

- BD Buffer

- 32 Kbyte on-chip dual-port RAM for buffer descriptors

- A total of 4096 buffer descriptors (2048 TxBD and 2048 RxBD)

- JTAG Support

- Supports the IEEE1149.1 JTAG controller standard

- Power and Clocks

- Supports single-beat and burst accesses

- On-chip PLL for baud rate generator (maximum of 66.7 MHz)

- Separate power supplies for core internal logic (1.8V) and for I/O (3.3V)

- Package

- 480 pin TPGA, 1.27 mm pitch

## 1.2 Electrical and Thermal Characteristics

This section provides AC and DC electical specifications and thermal characteristics for the MC92460.

### 1.2.1 DC Electrical Characteristics

This section describes the DC electrical characteristics for the MC92460. Table 1 shows the maximum electrical ratings.

**Table 1. Maximum Temperatures and Voltages**

| Rating                    | Symbol           | Value Name    | Unit |

|---------------------------|------------------|---------------|------|

| Core supply voltage       | VDD              | -0.3 – 2.5    | V    |

| I/O supply voltage        | VDDH             | -0.3 – 3.6    | V    |

| Input voltage             | VIN              | GND-0.3 – 3.6 | V    |

| Junction temperature      | Tj               | 120           | °C   |

| Storage temperature range | T <sub>STG</sub> | -55 – 150     | °C   |

| Ambient temperature       | T <sub>A</sub>   | -40 - 85      | °C   |

Table 2 lists recommended operational voltage conditions.

**Table 2. Recommended Operating Conditions**

| Rating               | Symbol | Value          | Unit |

|----------------------|--------|----------------|------|

| Core supply voltage  | VDD    | 1.65 – 1.95    | V    |

| I/O supply voltage   | VDDH   | 3.15 – 3.465   | V    |

| Input voltage        | VIN    | GND -0.3 – 3.6 | V    |

| Junction temperature | Tj     | 105            | °C   |

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (either GND or  $V_{CC}$ ).

Table 3 shows DC electrical characteristics.

**Table 3. DC Electrical Characteristics**

TA=0 to 85°C; VDD=2.0±5% Vdc; VDDH=3.3±5% Vdc; GND=0Vdc; Load Capacitance < 10pF

| Characteristics           | Conditions                 | Symbol          | Min | Max   | Unit |

|---------------------------|----------------------------|-----------------|-----|-------|------|

| Input high voltage        |                            | V <sub>IH</sub> | 2.0 | 3.465 | V    |

| Input low voltage         |                            | V <sub>IL</sub> | GND | 0.8   | V    |

| Input leakage current     | V <sub>IN</sub> =VDDH      | I <sub>IN</sub> | _   | 10    | uA   |

| HI-Z leakage current      | V <sub>IN</sub> =VDDH, GND | I <sub>OZ</sub> | -10 | +10   | uA   |

| Signal low input current  | V <sub>IL</sub> =0.8V      | I <sub>IL</sub> | _   | 60    | uA   |

| Signal high input current | V <sub>IH</sub> =2.0V      | I <sub>IH</sub> | _   | 60    | uA   |

| Output high voltage       | I <sub>OH</sub> =-7.0mA    | V <sub>OH</sub> | 2.4 | -     | V    |

### **Table 3. DC Electrical Characteristics (continued)**

TA=0 to 85°C; VDD=2.0±5% Vdc; VDDH=3.3±5% Vdc; GND=0Vdc; Load Capacitance < 10pF

| Output low voltage  BR BG ABB TS A[0-31] AP[0-3] APE TT[0-4] TBST TSIZ[0-2] GBL CI WT LBCLAIM BTO INT TC[0-1] AACK ARTRY DBG DBWO DBB DH[0-31],DL[0-31] DP[0-7] DPE DBDIS TA DRTRY TEA | I <sub>OL</sub> =7.0mA | V <sub>OL</sub> | 0.4 | V |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|-----|---|

| Output low voltage  Rx CLK[0-39]  Tx CLK[0-39]  Tx SD[0-39]  TDO  SBG  SDBG  SBR  SIRQ  CS0  CS1                                                                                       | I <sub>OL</sub> =5.0mA | V <sub>OL</sub> | 0.4 | V |

### 1.2.2 Thermal Characteristics

Table 4 describes thermal characteristics.

**Table 4. Maximum Temperatures and Voltages**

| Characteristics                 | Symbol           | Thermal<br>Resistance<br>Value | Unit | Air Flow |         |

|---------------------------------|------------------|--------------------------------|------|----------|---------|

| Thermal resistance for 480 TBGA |                  | 10.48                          | °C/W | 0 LFM    |         |

|                                 |                  | 8.61                           | °C/W | 100 LFM  |         |

|                                 | $	heta_{\sf JA}$ | $	heta_{\sf JA}$               | 7.78 | °C/W     | 200 LFM |

|                                 |                  |                                | 6.89 | °C/W     | 400 LFM |

|                                 |                  | 5.52                           | °C/W | 800 LFM  |         |

LFM = Linear Feet per Minute

### 1.2.3 Power Considerations

The average chip-junction temperature, Tj, can be obtained from the following:

$$T_J = T_A + (P_D \bullet \theta_{JA})$$

where

$\theta_{JA}\!=\!$  package thermal resistance, junction to ambient, °C/W

$T_A$  = ambient temperature, °C

Power equations are the following:

$$P_D = P_{VDD} + P_{VDDH}$$

= chip total power dissipation, W

$$P_{VDD} = I_{VDD} \times VDD = \text{chip core power, W}$$

$$P_{VDDH} = I_{VDDH} \times VDDH$$

= user-determined power dissipation on input/output pins, W

# 1.2.4 Power Dissipation

Table 5 describes maximum chip core power dissipation.

**Table 5. Maximum Core Power Dissipation (PVDD)**

| VDD(V) | SYSCLK<br>Frequency (MHz) | IVDD (mA) | PVDD (mW) | Pvddh(mW) |

|--------|---------------------------|-----------|-----------|-----------|

| 1.95   | 66.7                      | 650       | 980       | 920       |

# 1.2.5 AC Specifications

These AC specifications are target specifications.

# 1.2.5.1 SYSCLK Timing

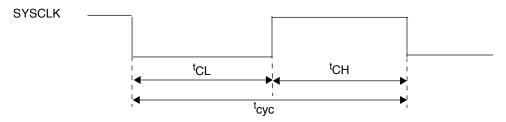

Table 6 shows the system clock timing.

**Table 6. Clock Timing**

| Characteristics           | Symbol                           | Min  | Max   | Unit |

|---------------------------|----------------------------------|------|-------|------|

| Operation Frequency       | f                                | 60.0 | 66.7  | MHz  |

| Clock period              |                                  | 15.0 | 16.7  | nS   |

| Clock pulse width         | t <sub>CL</sub> ,t <sub>CH</sub> | 7    | 8     | nS   |

| SYSCLK input high voltage | V <sub>IHC</sub>                 | 2.4  | 3.465 | V    |

| SYSCLK input low voltage  | V <sub>ILC</sub>                 | GND  | 0.4   | V    |

| SYSCLK Jitter             |                                  |      | ±200  | pS   |

Figure 2 shows the SYSCLK.

Figure 2. SYSCLK

# 1.2.5.2 EXCLK Timing

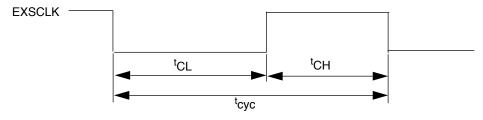

Table 7 shows the external clock timing.

**Table 7. Clock Timing**

| Characteristics          | Symbol                           | Min  | Max          | Unit |

|--------------------------|----------------------------------|------|--------------|------|

| Operation Frequency      | f                                | 14.0 | 16.0         | MHz  |

| Clock duty               |                                  | 40   | 60           | %    |

| Clock Pulse width        | t <sub>CL</sub> ,t <sub>CH</sub> | 25   | 42.8         | nS   |

| EXCLK input high voltage | V <sub>IHC</sub>                 | 2.4  | 3.465        | V    |

| EXCLK input low voltage  | V <sub>ILC</sub>                 | GND  | 0.4          | V    |

| EXCLK Jitter             |                                  |      | <u>+</u> 200 | pS   |

### **Electrical and Thermal Characteristics**

Figure 3 shows the EXCLK.

Figure 3. EXCLK

## 1.2.5.3 **AC Timing**

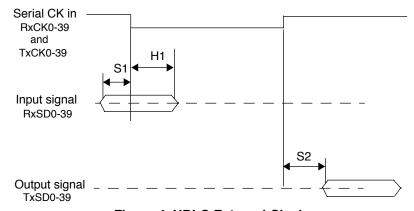

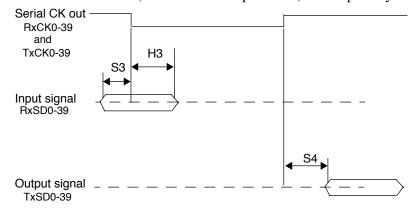

Figure 4 shows the HDLC external clock with polarity not inverted. All time specifications were measured at expected load capacitance  $C_L$ =8pF.

Figure 4. HDLC External Clock

Figure 5 shows an HDLC internal clock (TxCK/RxCK output mode) whose polarity is not inverted.

Figure 5. HDLC Internal Clock

Table 8 shows the AC electrical characteristics. The frequency is 20 MHz.

**Table 8. AC Electrical Characteristics**

| Spec Num | Characteristic                         | Min | Max | Unit |

|----------|----------------------------------------|-----|-----|------|

| S1       | HDLC input- external clock setup time  | 2   |     | nS   |

| H1       | HDLC input -external clock hold time   | 1   |     | nS   |

| S2       | HDLC output- external clock setup time |     | 14  | nS   |

| S3       | HDLC input- internal clock setup time  | 12  |     | nS   |

| H3       | HDLC input- internal clock hold time   | 0   |     | nS   |

| S4       | HDLC output- internal clock setup time |     | 4   | nS   |

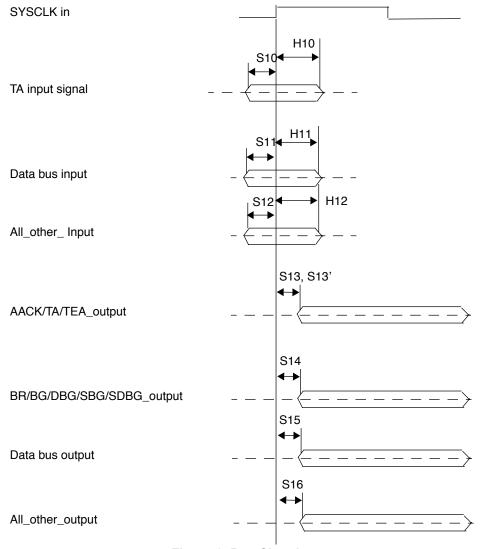

Figure 6 shows the interaction of several bus signals.

Figure 6. Bus Signals

### **Electrical and Thermal Characteristics**

Table 9 shows the bus signal I/O characteristics. The frequency is 20 MHz.

Table 9. Bus Input/Output Characteristics

| Spec Num | Characteristic            | Min | Max | Unit |

|----------|---------------------------|-----|-----|------|

| S10      | TA/TEA input              | 6   |     | nS   |

| H10      | TA/TEA input              |     | 1   | nS   |

| S11      | Data bus input signals    | 7   |     | nS   |

| H11      | Data bus input signals    |     | 1   | nS   |

| S12      | All other input signals   | 7   |     | nS   |

| H12      | All other input signals   |     | 1   | nS   |

| S13      | AACK/TEA output           | 1   | 7   | nS   |

| S13'     | TA output                 | 1   | 8.5 | nS   |

| S14      | BR/BG/DBG/SBG/SDBG output | 1   | 7   | nS   |

| S15      | Data bus output signals   | 1   | 8.5 | nS   |

| S16      | All other output signals  | 1   | 7   | nS   |

# 1.3 Pinout

**Table 10. Pin Assignments**

| Ball | A          | В          | ၁          | Q           | E          | 124        | Ů         | н        | r          | K          | ı         | ×        | z       | Ь         | ~           | H          | n         | >      | W          | Y         | AA      | AB        | AC        | ΑD       | AE        | AF        | AG       | ЧΗ          | Υ'          | Ball     |

|------|------------|------------|------------|-------------|------------|------------|-----------|----------|------------|------------|-----------|----------|---------|-----------|-------------|------------|-----------|--------|------------|-----------|---------|-----------|-----------|----------|-----------|-----------|----------|-------------|-------------|----------|

| _    | PowVdd5    | PowVdd6    | PowVdd30   | DP3         | CoreGnd0   | CoreVdd0   | ARTRY     | 112      | Pow Gnd2   | SBG        | Pow Gnd3  | æ        | SBR     | A15       | CoreVdd2    | A18        | A22       | A25    | A29        | E         | вто     | API       | CSA4      | CSA7     | ComVdd4   | TxSD0     | 3wVdd31  | Pow\vdd13   | PowVdd12    | -        |

| 7    | PowVdd7 F  | PowVdd4 F  | - I-40     | DP2         | PowGnd0 C  | <u>π</u>   | AACK      | DPE      | SDBG       | ¥1         | A4        | A7       | A11     | A12       | CoreGnd2    | 124        | CoreVdd20 | A26    | A30        | CoreVdd3  | CSA6    | AP2       | PowGnd10  | TC1      | SYSCLK    | ACoreGnd1 | TxSD1    | PowVdd11 Pi | PowVdd14 Pi | 7        |

| е    | PowVdd29   | DP5        | PowVdd3    | DP0         | 15120      | DBG        | ABB       | ů.       | 4 <u>T</u> | CareGnd1   | CoreVdd1  | Ħ        | A10     | PowGnd5   | A17         | A19        | V23       | A27    | PowGnd8    | SIRO      | APO     | APE       | MODE      | CareGnd4 | ACoreVdd1 | PACK0     | PowVdd10 | TxCK1       | PowVdd32    | 3        |

| 4    | DP4        | D56        | 8          | PowVdd2     | ¥          | TSIZ1      | 0_DBG     | PowGnd1  | E<br>E     | A0         | A3        | 9V       | PowGnd4 | A14       | A16         | PowGnd6    | A24       | A28    | A31        | LBCLAIM   | PowGnd9 | W         | JBE       | TxCK0    | PxSD0     | PowVdd9   | PxSD1    | TxCK2       | TxSD2       | 4        |

| w    | D3t        | D39        | D47        | 8           | PowVdd1    | TBST       | 18122     | <u>B</u> | Ē          | 980        | A2        | Y2       | 6V      | At3       | Core Gnd 20 | 970<br>VS0 | PowGnd7   | TEX    | CoreGnd3   | DRITRY    | AP3     | Ø         | TC0       | PIL10    | PowVdd8   | PACK1     | CSA8     | PACK2       | TxSD3       | w        |

| 9    | CoreGnd19  | D23        | CoreVdd25  | PowGnd35    | D63        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PowGnd11  | PxSD2     | CoreVdd5 | TxCK3       | RxCK3       | 9        |

| 7    | D54        | D62        | PowGnd34   | D15         | CoreVdd19  |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | CoreGnd5  | RxSD3     | TxCK4    | RxSD4       | RxCK4       | 7        |

| œ    | PowGnd33   | D30        | CoreGnd25  | D46         | 10         |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | TxSD4     | TxSD5     | TxCK5    | PacK5       | PowGnd12    | <b>∞</b> |

| 6    | D61        | 8          | D14        | D22         | B03        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PxSD5     | TxSD6     | TxCK6    | CoreGnd21   | PxCK6       | 6        |

| 2    | D45        | PowGnd32   | D63        | CoreVdd18   | DP6        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | RxSD6     | TxSD7     | TxCK7    | CoreGnd6    | RxSD7       | 10       |

| =    | DZI        | DP7        | D29        | SoreGnd18 ( | D37        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PxCK7     | CoreVdd6  | TxSD8    | TxCK8       | PxSD8       | 11       |

| 12   | D52        | 09G        | D5         | PowGnd31    | D13        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | ВжСКВ     | TxSD9     | TxCK9    | RxSD9       | ВхСК9       | 12       |

| 13   | D28        | PowGnd30   | 9EQ        | D44         | scan_out_i |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PowGnd13  | TxSD10    | TxCK10   | CoreVdd21   | PxSD10      | 13       |

| 4    | CoreVdd17  | D20        | D4         | D40         | D12        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | TxSD11    | TxCK11    | PxSD11   | PacK10      | PacK11      | 14       |

| 15   | 99 Q       | CoreGnd17  | PowGnd29   | D43         | D51        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | TxCK12    | CareGnd7  | PkSD12   | TxSD12      | CoreVdd7    | 15       |

| 16   | D35        | PowGnd28   | CoreVdd24  | D27         | D19        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PxSD13    | TxCK13    | TxSD13   | PacK13      | Pack12      | 16       |

| 17   | D11        | D3         | D58        | CoreGnd24   | D20        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PxSD14    | CoreGnd22 | TxCK14   | TxSD14      | PowGnd14    | 17       |

| 81   | D42        | PowGnd27   | D34        | D26         | D18        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PacK15    | PxSD15    | TxCK15   | TxSD15      | PxCK14      | 18       |

| 19   | D32        | D10        | CareVdd16  | 22          | PowGnd26   |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PxCK16    | CareGnd8  | PxSD16   | TxCK16      | TxSD16      | 19       |

| 20   | D57        | CoreGnd16  | D49        | P4          | D33        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PowGnd15  | PxSD17    | TxCK17   | CoreVddB    | TxSD17      | 20       |

| 21   | Core Vdd23 | D25        | PowGnd25   | 71Q         | D16        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | TxSD19    | CoreVdd22 | TxCK18   | TxSD18      | PacK17      | 21       |

| 22   | 80         | Б          | D56        | D48         | D24        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PxSD20    | PxSD19    | TxCK19   | PxCK18      | RxSD18      | 22       |

| 23   | PowGnd24   | scan_out_h | scan_out_g | scan_out_f  | CS0        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | CoreVdd9  | TxSD21    | TxCK20   | TxSD20      | PxCK19      | 23       |

| 2    | CoreGnd23  | 28         | CoreVdd15  | CSA2        | CS2        |            |           |          |            |            |           |          |         |           |             |            |           |        |            |           |         |           |           |          | PxSD22    | PowGnd16  | CoreGnd9 | TxCK21      | PxCK20      | 42       |

| 25   | PowGnd23   | CareGnd15  | scan_out_i | scan_out_e  | PowVdd22   | AMODE      | CoreVdd14 | CSA0     | TMS        | ACoveGnd2  | TxCK39    | TxCK38   | TxCK37  | PacK35    | Pack34      | PacK33     | TxCK32    | TxSD31 | TxCK30     | TxCK29    | PacK27  | scan_in_k | CareGnd10 | TxCK24   | PowVdd15  | PACK22    | TxSD22   | PACK21      | PxSD21      | 25       |

| 56   | scan_out_e | scan_out_k | PowGnd22   | PowVdd23    | SMODE1     | scan_out_d | CareGnd14 | HRESET   | 2          | Рыск39     | CoreGnd13 | PowGnd20 | TxSD37  | PxSD35    | PxSD34      | PowGnd19   | PwSD32    | TxCK31 | CoreVdd11  | PACK29    | PxSD28  | TxCK27    | CoreVdd10 | TxCK25   | TxSD24    | PowVdd16  | TxSD23   | TxCK22      | scan_in_j   | 56       |

| 7.7  | PowVdd36   | TESTO      | PowVdd24   | SMODEO      | TEST3      | DBWO       | DBDIS     | īΩ       | EXCLK      | CoreVdd13  | TxSD39    | TxSD38   | Pac K36 | TxCK35    | scan_out_b  | TxSD34     | PACK32    | PuSD31 | PvSD30     | PowGnd18  | PACK28  | PxSD27    | PxSD26    | TxSD26   | TxSD25    | PACK23    | PowVdd17 | TxCK23      | Pow\Vdd33   | 27       |

| 82   | PowVdd28   | PowVdd25   | TEST2      | POR         | CSA3       | PowGnd21   | TEST1     | TRSII    | ACoreVdd2  | Px.SD39    | PxCK38    | PxCK37   | Px.SD36 | TxSD36    | CoreGnd12 s | Px:SD33    | TxSD33    | PxCK31 | scan_out_a | TxSD30    | TxSD29  | TxSD28    | PxCK26    | PowGnd17 | PxSD25    | PxCK24    | Px:SD23  | PowVdd18    | PowVdd20    | 82       |

| 29   | PowVdd26   | PowVdd27   | PowVdd35   | SEN         | CSA5       | CSA1 F     | PCMD      | TCK      | PLLZO      | scan_out_c | PxSD38    | PscSD37  | TxCK36  | CoreVdd12 | TxSD35      | TxCK34     | TxCK33    | TxSD32 | PxCK30 s   | CoreGnd11 | PxSD29  | TxCK28    | TxSD27    | TxCK28   | PxCK25    | PxSD24    | PowVdd34 | PowVdd21    | PowVdd19    | 59       |

|      | A          | -          | ပ          | Q           | A          | F          | ß         | н        | r          | K          | 1         | M        | z       | 4         | ~           | L          | n         | >      | ×          | ۲         | AA      | AB        | AC        | AD       | AE        | AF        | AG F     | AH          | AJ F        |          |

#### **HOW TO REACH US:**

### **USA/EUROPE/LOCATIONS NOT LISTED:**

Motorola Literature Distribution P.O. Box 5405, Denver, Colorado 80217 1-303-675-2140 or 1-800-441-2447

#### JAPAN:

Motorola Japan Ltd. SPS, Technical Information Center 3-20-1, Minami-Azabu Minato-ku Tokyo 106-8573 Japan 81-3-3440-3569

#### ASIA/PACIFIC:

Motorola Semiconductors H.K. Ltd. Silicon Harbour Centre, 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong 852-26668334

### **TECHNICAL INFORMATION CENTER:**

1-800-521-6274

### **HOME PAGE:**

http://www.motorola.com/semiconductors

#### **DOCUMENT COMMENTS:**

FAX (512) 933-2625 Attn: NCSD Applications Engineering Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. digital dna is a trademark of Motorola, Inc. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2002

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Video ICs category:

Click to view products by Freescale manufacturer:

Other Similar products are found below:

ADV7343WBSTZ TW2964-LA2-CR TW9903-FB TW9919-PE1-GR TW9960-TA1-GR LA9520V-TLM-E TW9910-NA2-GR TW9900-TA1-GR ADV7625KBCZ-8 ADV7626KBCZ-8 MAX9406ETM+T PI3HDX414FCEEX PI3HDX511FZLEX M31245G-15

PI3HDX511DZLEX MAX4895EETE+T M23428G-33 PI7VD9008ABHFDE TW2984-NA2-CR ADV7186BBCZ-RL ADV7186BBCZ-TL PI3HDMI521FBE ADV7186BBCZ-T-RL ADV8003KBCZ-7C LT6554IGN#PBF M21324G-13 GS12181-INE3 PI3VDP411LSAZBEX PI3VDP411LSTZBEX M23145G-14 PI3VDP411LSRZBEX PI3HDX511EZLSEX TW2835-BA1-GR ISL59913IRZ TW9910-NB2-GR CM5100-01CP ADV7610BBCZ-RL BA7653AFV-E2 BA7654F-E2 BA7657F-E2 BH76331FVM-TR BH76332FVM-TR BH76363FV-E2 TVP5160PNP MAX9597CTI+ BA7602F-E2 BA7606FS-E2 BA7612F-E2 BA7626F-E2 BA7655AF-E2