# 3-Phase Brushless DC (BLDC) Motor Gate Driver with Power Module

#### Features:

- Three Half-bridge Drivers Configured to Drive External High-Side NMOS and Low-Side NMOS MOSFETs:

- Independent input control for high-side NMOS and low-side NMOS MOSFETs

- Peak output current: 0.5A @ 12V

- Shoot-through protection

- Overcurrent and short circuit protection

- Adjustable Output Buck Regulator (750 mW)

- · Fixed Output Linear Regulators:

- 5V @ 20 mA

- 12V @ 20 mA

- · Internal Bandgap Reference

- Three Operational Amplifiers for Motor Phase Current Monitoring and Position Detection

- · Overcurrent Comparator

- · Two Level Translators

- Operational Voltage Range 6 40V

- · Undervoltage Lockout (UVLO): 6V

- · Overvoltage Lockout (OVLO): 28V

- Transient (100 ms) Voltage Tolerance: 48V

- Extended Temperature Range: T<sub>A</sub> -40 to +150°C

- · Thermal Shutdown

#### **Applications:**

- · Automotive Fuel, Water, Ventilation Motors

- Home Appliances

- Permanent Magnet Synchronous Motor (PMSM) Control

- · Hobby Aircraft, Boats, Vehicles

#### **Related Literature:**

- AN885, "Brushless DC (BLDC) Motor Fundamentals", DS00885, Microchip Technology Inc., 2003

- AN1160, "Sensorless BLDC Control with Back-EMF Filtering Using a Majority Function", DS01160, Microchip Technology Inc., 2008

- AN1078, "Sensorless Field Oriented Control of a PMSM", DS01078, Microchip Technology Inc., 2010

### **Description:**

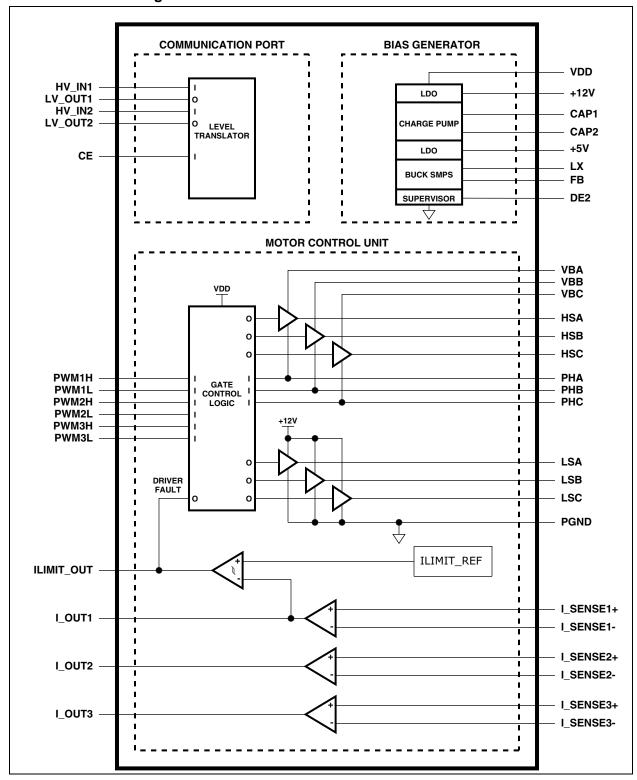

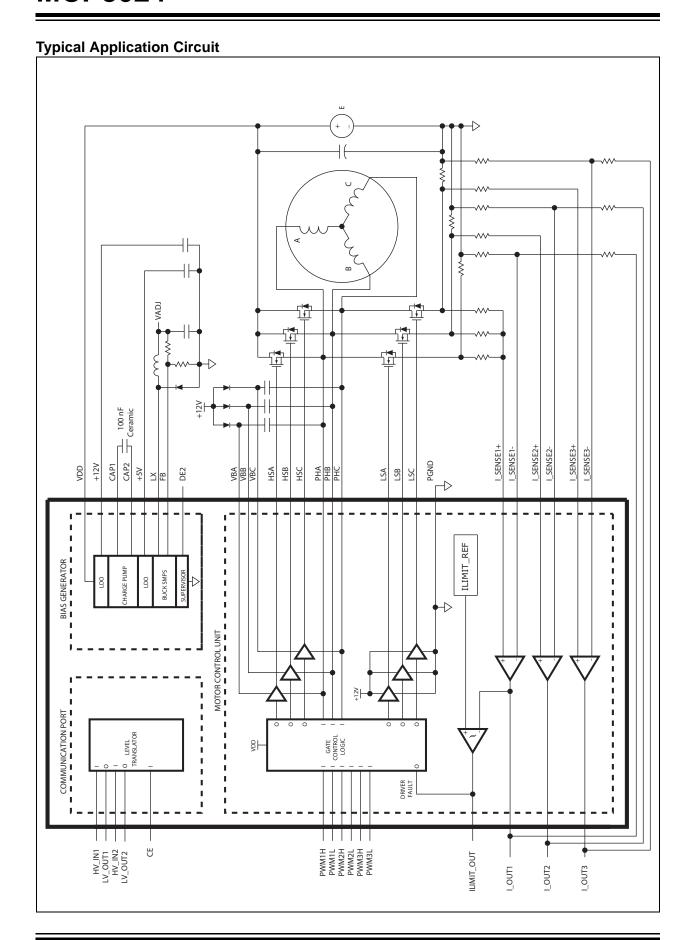

The MCP8024 is a 3-Phase Brushless DC (BLDC) power module. The MCP8024 device integrates three half-bridge drivers to drive external NMOS/NMOS transistor pairs configured to drive a 3-phase BLDC motor, a comparator, a voltage regulator to provide bias to a companion microcontroller, power monitoring comparators, an overtemperature sensor, two level translators and three operational amplifiers for motor current monitoring.

The MCP8024 has three half-bridge drivers capable of delivering a peak output current of 0.5A at 12V for driving high-side and low-side NMOS MOSFET transistors. The drivers have shoot-through, overcurrent, and short-circuit protection.

The MCP8024 buck converter is capable of delivering 750 mW of power for powering a companion microcontroller. The buck regulator may be disabled if not used. The on-board 5V and 12V low dropout voltage regulators are capable of delivering 20 mA of current.

The MCP8024 operation is specified over a temperature range of -40°C to +150°C.

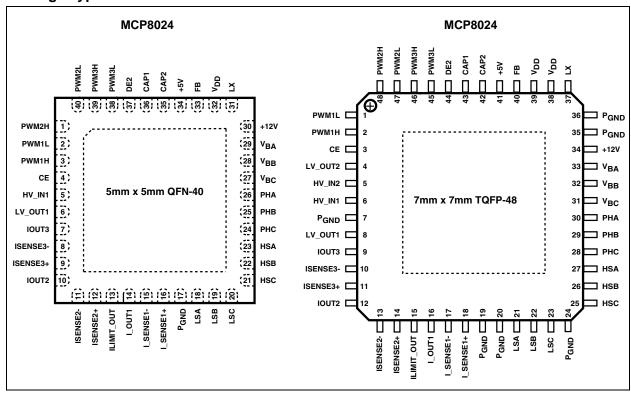

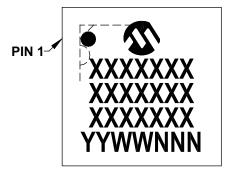

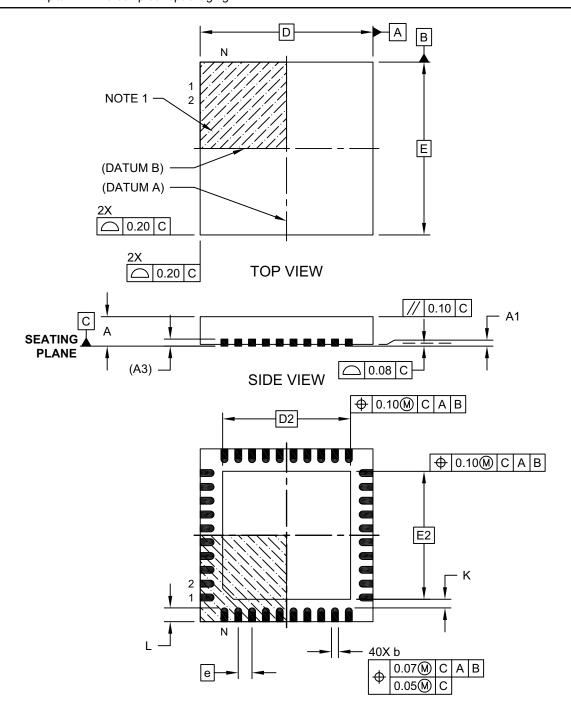

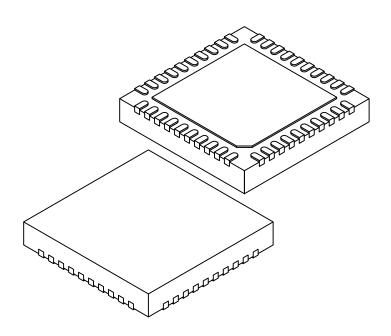

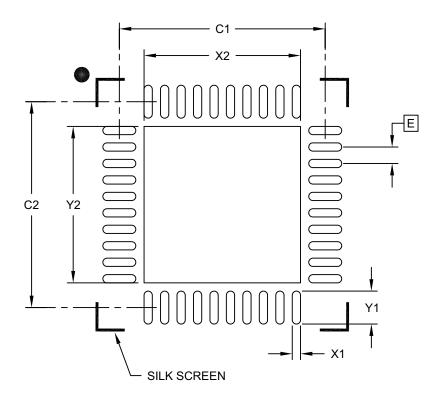

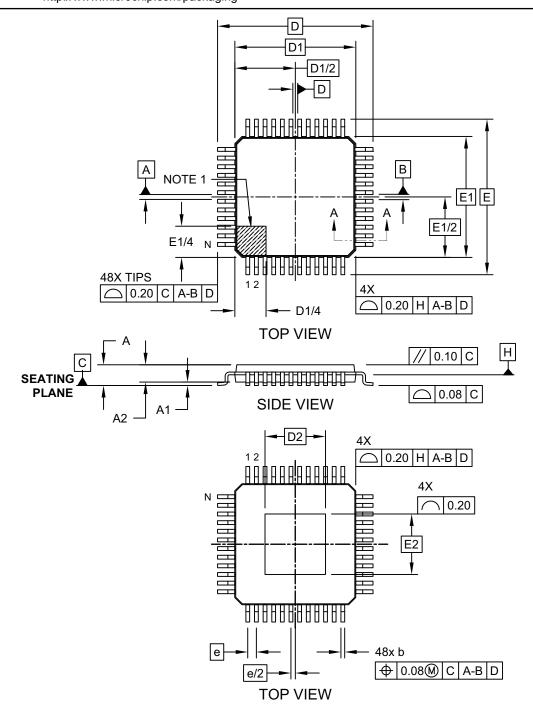

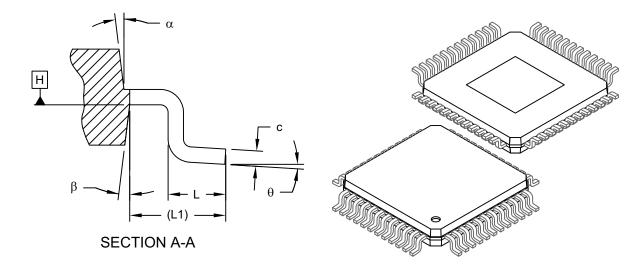

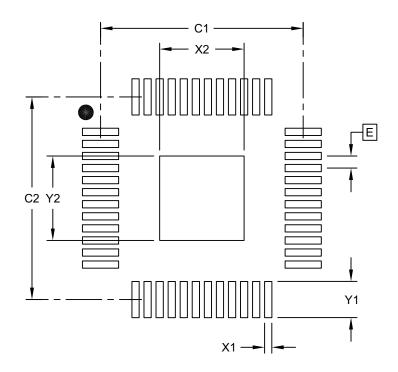

Package options include the 40-lead 5x5 QFN and 48-lead 7x7 TQFP.

### **Package Types**

### **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| Input Voltage, V <sub>DD</sub>          | +46.0V             |

|-----------------------------------------|--------------------|

| Input Voltage, < 100 ms Transient       | +48.0V             |

| Internal Power Dissipation              | Internally-Limited |

| Operating Ambient Temperature Range     | 40°C to +150°C     |

| Operating Junction Temperature (Note 1) | 40°C to +160°C     |

| Transient Junction Temperature*         | +170°C             |

| Storage temperature (Note 1)            | 55°C to +150°C     |

| Digital I/O                             | 0.3V to 5.5V       |

| LV Analog I/O                           | 0.3V to 5.5V       |

ESD and Latch-up protection:

| V <sub>DD</sub> , HV_IN1 pins | ≥ 12 kV HMM and     | ≥ 750V CDM         |

|-------------------------------|---------------------|--------------------|

| All other pins                | $\geq$ 4 kV HBM and | $\geq 750V \; CDM$ |

| Latch-up protection - all pin | ıs                  | > 100 mA           |

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

\* **Notice:** Transient junction temperatures should not exceed one second in duration. Sustained junction temperatures above 170°C may impact the device reliability.

#### AC/DC CHARACTERISTICS

| <b>Electrical Specifications:</b> Unless otherwise noted $T_J = -40^{\circ}\text{C}$ to $+150^{\circ}\text{C}$ . |                        |                       |                                      |                        |       |                                                                                                                                                                                                                                     |  |  |  |

|------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--------------------------------------|------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameters                                                                                                       | Symbol                 | Min.                  | Тур.                                 | Max.                   | Units | Conditions                                                                                                                                                                                                                          |  |  |  |

| Power Supply Input                                                                                               |                        |                       |                                      |                        |       |                                                                                                                                                                                                                                     |  |  |  |

| Input Operating Voltage                                                                                          | V <sub>DD</sub>        | 6.0<br>6.0            | _                                    | 28.0<br>40             | V     | Operating<br>Shutdown                                                                                                                                                                                                               |  |  |  |

| Transient Maximum Voltage                                                                                        | $V_{DDmax}$            | _                     | _                                    | 48                     | V     | < 100 ms                                                                                                                                                                                                                            |  |  |  |

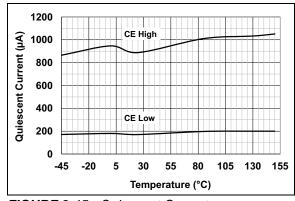

| Input Quiescent Current                                                                                          | Iα                     | _<br>_<br>_<br>_<br>_ | —<br>171<br>197<br>200<br>200<br>900 | <br>220<br><br><br>500 | μА    | $V_{DD}$ = 13V,<br>disabled, CE = 0V, T <sub>J</sub> = 25°C<br>disabled, CE = 0V, T <sub>J</sub> = 85°C<br>disabled, CE = 0V, T <sub>J</sub> = 130°C<br>disabled, CE = 0V, T <sub>J</sub> = 150°C<br>active, CE > $V_{DIG\_HI\_TH}$ |  |  |  |

| Digital Input/Output                                                                                             | DIGITAL <sub>I/O</sub> | 0                     | _                                    | 5.5                    | V     |                                                                                                                                                                                                                                     |  |  |  |

| Digital Open-Drain Drive<br>Strength                                                                             | DIGITAL <sub>IOL</sub> | _                     | 1                                    | _                      | mA    | V <sub>DS</sub> < 50 mV                                                                                                                                                                                                             |  |  |  |

| Digital Input Rising Threshold                                                                                   | V <sub>DIG_HI_TH</sub> | 1.26                  | _                                    | _                      | V     |                                                                                                                                                                                                                                     |  |  |  |

| Digital Input Falling Threshold                                                                                  | V <sub>DIG_LO_TH</sub> | _                     | _                                    | 0.54                   | V     |                                                                                                                                                                                                                                     |  |  |  |

| Digital Input Hysteresis                                                                                         | V <sub>DIG_HYS</sub>   | _                     | 500                                  | _                      | mV    |                                                                                                                                                                                                                                     |  |  |  |

| Digital Input Current                                                                                            | I <sub>DIG</sub>       | _                     | 30<br>0.2                            | 100<br>—               | μA    | V <sub>DIG</sub> = 3.0V<br>V <sub>DIG</sub> = 0V                                                                                                                                                                                    |  |  |  |

| Analog Low-Voltage Input                                                                                         | ANALOG <sub>VIN</sub>  | 0                     | _                                    | 5.5                    | V     | Excludes high voltage                                                                                                                                                                                                               |  |  |  |

| Analog Low-Voltage Output                                                                                        | ANALOG <sub>VOUT</sub> | 0                     | _                                    | V <sub>OUT5</sub>      | V     | Excludes high voltage                                                                                                                                                                                                               |  |  |  |

| BIAS GENERATOR                                                                                                   |                        |                       |                                      |                        |       |                                                                                                                                                                                                                                     |  |  |  |

| +12V Regulated Charge Pump                                                                                       |                        |                       |                                      |                        |       |                                                                                                                                                                                                                                     |  |  |  |

| Charge Pump Current                                                                                              | I <sub>CP</sub>        | 20                    |                                      | _                      | mA    | V <sub>DD</sub> = 9.0V                                                                                                                                                                                                              |  |  |  |

| Charge Pump Voltage                                                                                              | V <sub>CP</sub>        | +10                   | 2 * V <sub>DD</sub>                  | _                      | V     | V <sub>DD</sub> = 9.0V, I <sub>CP</sub> = 20 mA                                                                                                                                                                                     |  |  |  |

| Charge Pump Start                                                                                                | CP <sub>START</sub>    | 11.0                  | 11.5                                 | _                      | V     | V <sub>DD</sub> falling                                                                                                                                                                                                             |  |  |  |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation may cause the device operating junction temperature to exceed the maximum 160°C rating. Sustained junction temperatures above 150°C can impact the device reliability and OTP data retention.

2: 1000 hour cumulative maximum for OTP data retention (typical).

| Electrical Specifications: Unles                             | s otherwise noted I                                          | J = -40°( | to +150° ک | C.   | 1      |                                                                                                       |

|--------------------------------------------------------------|--------------------------------------------------------------|-----------|------------|------|--------|-------------------------------------------------------------------------------------------------------|

| Parameters                                                   | Symbol                                                       | Min.      | Тур.       | Max. | Units  | Conditions                                                                                            |

| Charge Pump Stop                                             | CP <sub>STOP</sub>                                           | _         | 12.0       | 12.5 | V      | V <sub>DD</sub> rising                                                                                |

| Charge Pump Frequency<br>(50% charging /<br>50% discharging) | CP <sub>FSW</sub>                                            | _         | 76.80<br>0 | _    | kHz    | $V_{DD}$ = 9.0V<br>$V_{DD}$ = 12.5V (stopped)                                                         |

| Charge Pump Switch<br>Resistance                             | CP <sub>RDSON</sub>                                          | _         | 14         | _    | Ω      | RDS <sub>ON</sub> sum of high side and low side                                                       |

| Output Voltage                                               | V <sub>OUT12</sub>                                           | 10        | 12         | _    | V      | V <sub>DD</sub> = V <sub>OUT12</sub> + 1V, I <sub>OUT</sub> = 1 mA                                    |

| Output Voltage Tolerance                                     | TOLV <sub>OUT12</sub>                                        |           | _          | 4.0  | %      | V <sub>DD</sub> = V <sub>OUT12</sub> + 1V, I <sub>OUT</sub> = 1 mA                                    |

| Output Current                                               | l <sub>OUT</sub>                                             | 20        | _          | _    | mA     | Average current                                                                                       |

| Output Current Limit                                         | I <sub>LIMIT</sub>                                           | 30        | 40         | _    | mA     | Average current                                                                                       |

| Output Voltage Temperature<br>Coefficient                    | TCV <sub>OUT12</sub>                                         | _         | 50         | _    | ppm/°C |                                                                                                       |

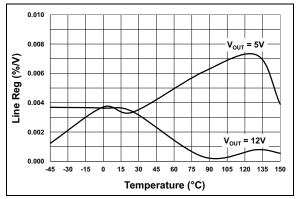

| Line Regulation                                              | ΔV <sub>OUT</sub> /<br>(V <sub>OUT</sub> XΔV <sub>DD</sub> ) | _         | 0.1        | 0.5  | %/V    | 13V < V <sub>DD</sub> < 19V, I <sub>OUT</sub> = 20 mA                                                 |

| Load Regulation                                              | ΔV <sub>OUT</sub> /V <sub>OUT</sub>                          | _         | 0.2        | 0.5  | %      | I <sub>OUT</sub> = 0.1 mA to 15 mA                                                                    |

| Dropout Voltage                                              | V <sub>DD</sub> -V <sub>OUT12</sub>                          | _         | 380        | _    | mV     | I <sub>OUT</sub> = 20 mA,<br>measurement taken when<br>output voltage drops 2% from<br>no-load value. |

| Power Supply Rejection Ratio                                 | PSRR                                                         | _         | 60         | _    | dB     | f = 1 kHz, I <sub>OUT</sub> = 10 mA                                                                   |

| +5V Linear Regulator                                         |                                                              |           | l          |      |        |                                                                                                       |

| Output Voltage                                               | V <sub>OUT5</sub>                                            | _         | 5          | _    | V      | $V_{DD} = V_{OUT5} + 1V$ , $I_{OUT} = 1$ mA                                                           |

| Output Voltage Tolerance                                     | TOLV <sub>OUT5</sub>                                         |           | _          | 4.0  | %      |                                                                                                       |

| Output Current                                               | l <sub>OUT</sub>                                             | 20        | _          | _    | mA     | Average current                                                                                       |

| Output Current Limit                                         | I <sub>LIMIT</sub>                                           | 30        | 40         | _    | mA     | Average current                                                                                       |

| Output Voltage Temperature Coefficient                       | TCV <sub>OUT5</sub>                                          | _         | 50         | _    | ppm/°C |                                                                                                       |

| Line Regulation                                              | ΔV <sub>OUT</sub> /<br>(V <sub>OUT</sub> XΔV <sub>DD</sub> ) | _         | 0.1        | 0.5  | %/V    | 6V < V <sub>DD</sub> < 19V, I <sub>OUT</sub> = 20 mA                                                  |

| Load Regulation                                              | ΔV <sub>OUT</sub> /V <sub>OUT</sub>                          | _         | 0.2        | 0.5  | %      | I <sub>OUT</sub> = 0.1 mA to 15 mA                                                                    |

| Dropout Voltage                                              | V <sub>DD</sub> -V <sub>OUT5</sub>                           | _         | 180        | 350  | mV     | I <sub>OUT</sub> = 20 mA,<br>measurement taken when<br>output voltage drops 2% from<br>no-load value. |

| Power Supply Rejection Ratio                                 | PSRR                                                         | _         | 60         | _    | dB     | f = 1 kHz, I <sub>OUT</sub> = 10 mA                                                                   |

| Buck Regulator                                               |                                                              |           |            |      |        |                                                                                                       |

| Feedback Voltage                                             | $V_{FB}$                                                     | 1.19      | 1.25       | 1.31 | V      |                                                                                                       |

| Feedback Voltage Tolerance                                   | TOLV <sub>FB</sub>                                           | _         | _          | 5.0  | %      | I <sub>FB</sub> = 1 μA                                                                                |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation may cause the device operating junction temperature to exceed the maximum 160°C rating. Sustained junction temperatures above 150°C can impact the device reliability and OTP data retention.

<sup>2: 1000</sup> hour cumulative maximum for OTP data retention (typical).

| Electrical Specifications: Unless             | s otherwise noted                               | $\Gamma_{\rm J} = -40^{\circ}$ | c to +150° | °C.  |       | ·                                                                          |

|-----------------------------------------------|-------------------------------------------------|--------------------------------|------------|------|-------|----------------------------------------------------------------------------|

| Parameters                                    | Symbol                                          | Min.                           | Тур.       | Max. | Units | Conditions                                                                 |

| Feedback Voltage Line<br>Regulation           | $ (\Delta V_{FB}/V_{FB}) /$<br>$\Delta V_{DD} $ | _                              | 0.1        | 0.5  | %/V   | V <sub>DD</sub> = 6V to 28V                                                |

| Feedback Voltage Load<br>Regulation           | $ \Delta V_{FB} / V_{FB} $                      |                                | 0.1        | 0.5  | %     | I <sub>OUT</sub> = 5 mA to 150 mA                                          |

| Feedback Input Bias Current                   | I <sub>FB</sub>                                 | -100                           | _          | +100 | nA    | Sink/Source                                                                |

| Switching Frequency                           | $f_{\sf SW}$                                    |                                | 461        | _    | kHz   |                                                                            |

| Duty Cycle Range                              | DC <sub>MAX</sub>                               | 3                              | _          | 96   | %     |                                                                            |

| PMOS Switch On Resistance                     | R <sub>DSON</sub>                               | _                              | 0.6        |      | Ω     | V <sub>DD</sub> = 13V, T <sub>J</sub> =25°C                                |

| PMOS Switch Current Limit                     | I <sub>P(MAX)</sub>                             | _                              | 2.5        |      | Α     |                                                                            |

| Ground Current – PWM Mode                     | I <sub>GND</sub>                                | _                              | 1.5        | 2.5  | mA    | Switching                                                                  |

| Quiescent Current – PFM<br>Mode               | lQ                                              | _                              | 150        | 200  | μΑ    | I <sub>OUT</sub> = 0mA                                                     |

| Output Voltage Adjust Range                   | $V_{OUT}$                                       | 2.0                            | _          | 5.0  | V     |                                                                            |

| Output Current                                | I <sub>OUT</sub>                                | 150                            | _          |      | mA    | 5v                                                                         |

|                                               |                                                 | 250                            | _          |      |       | 3v                                                                         |

| Output Power                                  | P <sub>OUT</sub>                                | _                              | 750        | _    | mW    | P = I <sub>OUT</sub> * V <sub>OUT</sub>                                    |

| Voltage Supervisor                            |                                                 | •                              |            |      |       |                                                                            |

| Undervoltage Lockout Start                    | UVLO <sub>STRT</sub>                            | _                              | 6.0        | 6.25 | V     | V <sub>DD</sub> rising                                                     |

| Undervoltage Lockout Stop                     | UVLO <sub>STOP</sub>                            | 5.1                            | 5.5        |      | V     | V <sub>DD</sub> falling                                                    |

| Undervoltage Lockout<br>Hysteresis            | UVLO <sub>HYS</sub>                             | 0.35                           | 0.5        | 0.65 | V     |                                                                            |

| Overvoltage Lockout All<br>Functions Disabled | OVLO <sub>STOP</sub>                            | _                              | 32.0       | 33.0 | V     | V <sub>DD</sub> rising                                                     |

| Overvoltage Lockout All<br>Functions Enabled  | OVLO <sub>STRT</sub>                            | 29.0                           | 30.0       | _    | V     | V <sub>DD</sub> falling                                                    |

| Overvoltage Lockout<br>Hysteresis             | OVLO <sub>HYS</sub>                             | 1.0                            | 2.0        | 3.0  | V     |                                                                            |

| Temperature Supervisor                        |                                                 |                                |            |      |       |                                                                            |

| Thermal Warning<br>Temperature (115°C)        | T <sub>WARN</sub>                               |                                | 72         |      | %     | Rising temperature,<br>percentage of thermal<br>shutdown temperature "MIN" |

| Thermal Warning Hysteresis                    | $\Delta T_{WARN}$                               | _                              | 15         | _    | °C    | Falling temperature                                                        |

| Thermal Shutdown<br>Temperature               | T <sub>SD</sub>                                 | 160                            | 170        | _    | °C    | Rising temperature                                                         |

| Thermal Shutdown Hysteresis                   | $\DeltaT_{SD}$                                  | _                              | 25         | _    | °C    | Falling temperature                                                        |

| MOTOR CONTROL UNIT                            |                                                 |                                |            |      |       | •                                                                          |

| Output Drivers                                |                                                 |                                |            |      |       |                                                                            |

| PWMH/L Input Pull-Down                        | R <sub>PULLDN</sub>                             | 32                             | 47         | 62   | kΩ    |                                                                            |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation may cause the device operating junction temperature to exceed the maximum 160°C rating. Sustained junction temperatures above 150°C can impact the device reliability and OTP data retention.

<sup>2: 1000</sup> hour cumulative maximum for OTP data retention (typical).

| Electrical Specifications: Unless                         | s otherwise noted                              | $T_{J} = -40^{\circ}$ | C to +150°                       | C.               |                |                                                                                                                                               |

|-----------------------------------------------------------|------------------------------------------------|-----------------------|----------------------------------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                                                | Symbol                                         | Min.                  | Тур.                             | Max.             | Units          | Conditions                                                                                                                                    |

| Output Driver Source Current                              | I <sub>SOURCE</sub>                            | 0.3                   | _                                | _                | Α              | V <sub>DD</sub> = 12V, H[A:C], L[A:C]                                                                                                         |

| Output Driver Sink Current                                | I <sub>SINK</sub>                              | 0.3                   | _                                | _                | Α              | V <sub>DD</sub> = 12V, H[A:C], L[A:C]                                                                                                         |

| Output Driver Source<br>Resistance                        | R <sub>DSON</sub>                              | _                     | 17                               | _                | Ω              | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 12V,<br>H[A:C], L[A:C]                                                                            |

| Output Driver Sink Resistance                             | R <sub>DSON</sub>                              | _                     | 17                               | _                | Ω              | I <sub>OUT</sub> = 10 mA, V <sub>DD</sub> = 12V,<br>H[A:C], L[A:C]                                                                            |

| Output Driver UVLO<br>Threshold                           | D <sub>UVLO</sub>                              | 7.2                   | 8.0                              | _                | V              |                                                                                                                                               |

| Output Driver Bootstrap<br>Voltage (w/ respect to ground) | V <sub>BOOTSTRAP</sub>                         | _<br>_                |                                  | 44<br>48         | V              | Continuous<br>< 100 ms                                                                                                                        |

| Output Driver HS Drive<br>Voltage                         | V <sub>HS</sub>                                | 8.0<br>-5.5           | 12<br>—                          | 13.5<br>—        | V              | With respect to Phase pin With respect to ground                                                                                              |

| Output Driver LS Drive<br>Voltage                         | $V_{LS}$                                       | 8.0                   | 12                               | 13.5             | V              | With respect to ground                                                                                                                        |

| Output Driver Phase Pin<br>Voltage                        | V <sub>PHASE</sub>                             | -5.5V                 | _                                | 34               | V              | With respect to ground                                                                                                                        |

| Output Driver Short Circuit<br>Protection Threshold       | D <sub>SC</sub>                                | _<br>_<br>_<br>_      | 0.250<br>0.500<br>0.750<br>1.000 | _<br>_<br>_<br>_ | V              | Set by DE2 CONFIG[1:0] word<br>00 - Default<br>01<br>10                                                                                       |

| Output Driver Short Circuit<br>Detected Propagation Delay | D <sub>SC_DEL</sub>                            | _<br>_<br>_           | 430<br>10                        | _<br>_<br>_<br>_ | ns             | C <sub>LOAD</sub> = 1000 pF, V <sub>DD</sub> =12V,<br>detection after blanking<br>detection during blanking, value<br>is delay after blanking |

| Output Driver Turn-off<br>Propagation Delay               | T <sub>DEL_OFF</sub>                           | _                     | 100                              | 250              | ns             | C <sub>LOAD</sub> = 1000 pF, V <sub>DD</sub> =12V,                                                                                            |

| Output Driver Turn-on<br>Propagation Delay                | T <sub>DEL_ON</sub>                            | _                     | 100                              | 250              | ns             | C <sub>LOAD</sub> = 1000 pF, V <sub>DD</sub> =12V,                                                                                            |

| Standby to Motor Operational $(C_{LOAD} = 10 \mu F)$      | t <sub>MOTOR</sub>                             | _                     | 10                               | 50<br>10         | μs             | CE High-Low-High Transition < 100 µs (Fault Clearing) Standby state to Operational state                                                      |

| CE Low to Standby State<br>CE Fault Clearing Pulse        | <sup>t</sup> STANDBY<br><sup>t</sup> FAULT_CLR | _<br>_<br>1           | 10<br>—                          | —<br>—           | ms<br>µs<br>µs | Time after CE = 0V CE High-Low-High Transition Time                                                                                           |

| Current Sense Amplifier                                   |                                                |                       |                                  |                  |                |                                                                                                                                               |

| Input Offset Voltage                                      | V <sub>OS</sub>                                | -3.0                  | _                                | +3.0             | mV             | V <sub>CM</sub> = 0V<br>T <sub>A</sub> = -40°C to +150°C                                                                                      |

| Input Offset Temperature Drift                            | $\Delta V_{OS}/\Delta T_{A}$                   | _                     | ±2.0                             | _                | μV/°C          | V <sub>CM</sub> = 0V                                                                                                                          |

| Input Bias Current                                        | I <sub>B</sub>                                 | -1                    | _                                | +1               | μΑ             |                                                                                                                                               |

| Common Mode Input Range                                   | $V_{CMR}$                                      | -0.3                  | _                                | 3.5              | V              |                                                                                                                                               |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation may cause the device operating junction temperature to exceed the maximum 160°C rating. Sustained junction temperatures above 150°C can impact the device reliability and OTP data retention.

<sup>2: 1000</sup> hour cumulative maximum for OTP data retention (typical).

| Electrical Specifications: Unless               | otherwise noted                   | $T_J = -40^{\circ}$ | C to +150° | C.    |          |                                                                  |

|-------------------------------------------------|-----------------------------------|---------------------|------------|-------|----------|------------------------------------------------------------------|

| Parameters                                      | Symbol                            | Min.                | Тур.       | Max.  | Units    | Conditions                                                       |

| Common Mode Rejection Ratio                     | CMRR                              | 65                  | 80         | _     | dB       | Freq = 1 kHz, I <sub>OUT</sub> = 10 μA                           |

| Maximum Output Voltage<br>Swing                 | $V_{OL}, V_{OH}$                  | 0.05                |            | 4.5   | V        | I <sub>OUT</sub> = 200 μA                                        |

| Slew Rate                                       | SR                                | _                   | ±7         | _     | V/μs     | Symmetrical                                                      |

| Gain Bandwidth Product                          | GBWP                              | _                   | 10.0       | _     | MHz      |                                                                  |

| Current Comparator<br>Hysteresis                | CC <sub>HYS</sub>                 | _                   | 10         | _     | mV       |                                                                  |

| Current Comparator Common<br>Mode Input Range   | V <sub>CC_CMR</sub>               | 1.0                 | _          | 4.5   | V        |                                                                  |

| Current Limit DAC                               |                                   |                     |            |       |          |                                                                  |

| Resolution                                      |                                   | _                   | 8          | _     | Bits     |                                                                  |

| Output Voltage Range                            | V <sub>OL</sub> , V <sub>OH</sub> | 0.991               | _          | 4.503 | V        | I <sub>OUT</sub> = 1 mA                                          |

| Output Voltage                                  | $V_{DAC}$                         | _<br>_<br>_         |            |       | V        | Code * 13.77 mV/Bit + 0.991V<br>Code 00H<br>Code 40H<br>Code FFH |

| Input to Output Delay                           | T <sub>DELAY</sub>                | _                   | 50         | _     | μs       | 5 time constants of 100 kHz filte                                |

| Integral Nonlinearity                           | INL                               | -0.5                | _          | +0.5  | %FSR     | %Full Scale Range                                                |

| Differential Nonlinearity                       | DNL                               | -50                 | _          | +50   | %LSB     | %LSB                                                             |

| ILIMIT_OUT Sink Current (Open-Drain)            | IL <sub>OUT</sub>                 | _                   | 1          | _     | mA       | V <sub>ILIMIT_OUT</sub> <= 50mV                                  |

| Voltage Level Translator                        |                                   |                     |            |       |          |                                                                  |

| High-Voltage Input Range                        | VIN                               | 0                   | _          | VDD   | V        |                                                                  |

| Low-Voltage Output Range                        | VOUT                              | 0                   | _          | 5.0V  | V        |                                                                  |

| Input Pull-up Resistor                          | RPU                               | 20                  | 30         | 47    | kΩ       |                                                                  |

| High-Level Input Voltage                        | VIH                               | 0.60                | _          | _     | $V_{DD}$ | V <sub>DD</sub> = 15V                                            |

| Low-Level Input Voltage                         | VIL                               | _                   | _          | 0.40  | $V_{DD}$ | V <sub>DD</sub> = 15V                                            |

| Input Hysteresis                                | VHYS                              | _                   | _          | 0.30  | $V_{DD}$ |                                                                  |

| Propagation Delay                               | TLV_OUT                           | _                   | 3.0        | 6.0   | μs       |                                                                  |

| Maximum Communication Frequency                 | FMAX                              | _                   | _          | 20    | kHz      |                                                                  |

| Low-Voltage Output Sink<br>Current (Open-Drain) | IOL                               | _                   | 1          | _     | mA       | V <sub>OUT</sub> <= 50 mV                                        |

| OTP Data Retention                              |                                   |                     |            |       |          |                                                                  |

| OTP Cell High Temperature<br>Operating Life     | HTOL                              | _                   | 1000       | _     | Hours    | T <sub>J</sub> = 150°C ( <b>Note 2</b> )                         |

| OTP Cell Operating Life                         |                                   | _                   | 10         | _     | Years    | T <sub>J</sub> = 85°C                                            |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation may cause the device operating junction temperature to exceed the maximum 160°C rating. Sustained junction temperatures above 150°C can impact the device reliability and OTP data retention.

**<sup>2:</sup>** 1000 hour cumulative maximum for OTP data retention (typical).

#### TEMPERATURE SPECIFICATIONS

| Parameters                   | Sym.              | Min. | Тур. | Max. | Units | Conditions                     |

|------------------------------|-------------------|------|------|------|-------|--------------------------------|

| Temperature Ranges (Notes 1) |                   |      |      |      |       |                                |

| Specified Temperature Range  | T <sub>A</sub>    | -40  |      | +150 | °C    |                                |

| Operating Temperature Range  | T <sub>A</sub>    | -40  |      | +150 | °C    |                                |

| Storage Temperature Range    | T <sub>A</sub>    | -55  |      | +150 | °C    | (Note 2)                       |

| Thermal Package Resistance   |                   |      |      |      |       |                                |

| 5mm x 5mm QFN-40             | $\theta_{JA}$     | _    | 34   | _    | °C/W  | 4-Layer JC51-7 standard board, |

|                              | $\theta_{\sf JC}$ |      | 5.2  | _    |       | natural convection             |

| 7mm x 7mm TQFP-48-EP         | $\theta_{JA}$     | _    | 30   | _    | °C/W  |                                |

|                              | $\theta_{\sf JC}$ | _    | 15   | _    |       |                                |

- Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum 150°C rating. Sustained junction temperatures above 150°C can impact the device reliability.

- 2: 1000 hour cumulative maximum for OTP data retention (typical).

#### ESD, SUSCEPTIBILITY, SURGE, AND LATCH-UP TESTING

| Parameter                                                                            | Standard and Test Condition                                                          | Value                                    |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------------------------------------------|

| Input voltage surges                                                                 | ISO 16750-2                                                                          | 28V for 1 minute,<br>45V for 0.5 seconds |

| ESD HBM with 1.5 kΩ / 100 pF                                                         | ESD-STM5.1-2001<br>JESD22-A114E 2007<br>CEI/IEC 60749-26: 2006<br>AEC-Q100-002-Ref_D | <u>+</u> 4 kV                            |

| ESD CDM (Charged Device Model, field-induced method – replaces machine-model method) | ESD-STM5.3.1-1999                                                                    | <u>+</u> 750 V all pins                  |

| Latch-up Susceptibility                                                              | AEC Q100-004, 150°C                                                                  | >100 mA                                  |

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**Note:** Unless otherwise indicated:  $T_A = +25$ °C; Junction Temperature  $(T_J)$  is approximated by soaking the device under test to an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in Junction temperature over the Ambient temperature is not significant.

**FIGURE 2-1:** LDO Line Regulation vs Temperature.

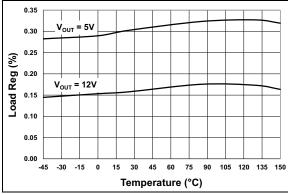

**FIGURE 2-2:** LDO Load Regulation vs Temperature.

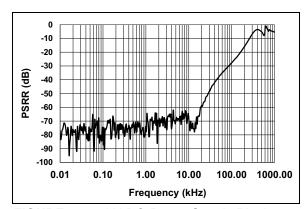

**FIGURE 2-3:** 5V LDO Power Supply Ripple Rejection vs Frequency.

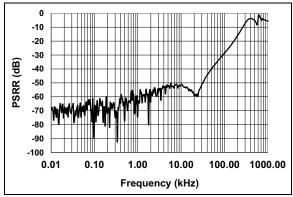

**FIGURE 2-4:** 12 V LDO Power Supply Ripple Rejection vs Frequency.

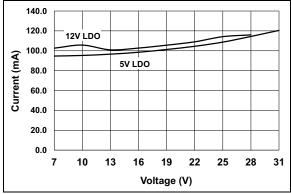

**FIGURE 2-5:** LDO Short Circuit Current vs Input Voltage.

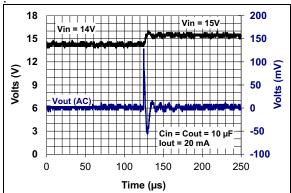

FIGURE 2-6: 5V LDO Dynamic Linestep - Rising V<sub>DD</sub>.

**Note:** Unless otherwise indicated:  $T_A = +25^{\circ}C$ ; Junction Temperature  $(T_J)$  is approximated by soaking the device under test to an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in Junction temperature over the Ambient temperature is not significant.

**FIGURE 2-7:** 5V LDO Dynamic Linestep - Falling V<sub>DD</sub>.

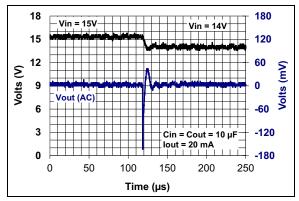

**FIGURE 2-8:** 12V LDO Dynamic Linestep - Rising  $V_{DD}$ .

**FIGURE 2-9:** 12V LDO Dynamic Linestep - Falling V<sub>DD</sub>.

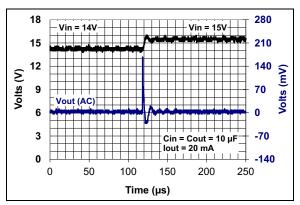

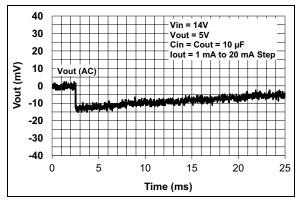

**FIGURE 2-10:** 5V LDO Dynamic Loadstep - Rising Current.

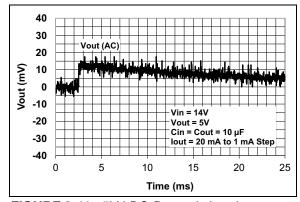

**FIGURE 2-11:** 5V LDO Dynamic Loadstep - Falling Current.

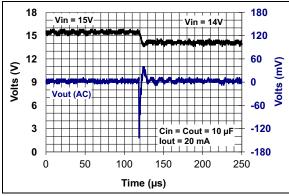

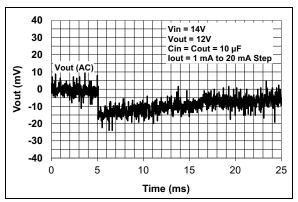

**FIGURE 2-12:** 12V LDO Dynamic Loadstep - Rising Current.

**Note:** Unless otherwise indicated:  $T_A = +25^{\circ}C$ ; Junction Temperature  $(T_J)$  is approximated by soaking the device under test to an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in Junction temperature over the Ambient temperature is not significant.

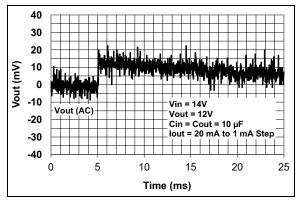

**FIGURE 2-13:** 12V LDO Dynamic Loadstep - Falling Current.

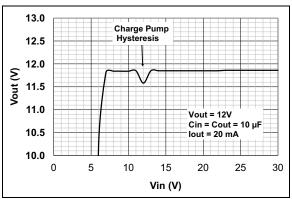

**FIGURE 2-14:** 12V LDO Output Voltage vs Rising Input Voltage.

**FIGURE 2-15:** Quiescent Current vs Temperature.

FIGURE 2-16: Trapezoidal Back EMF.

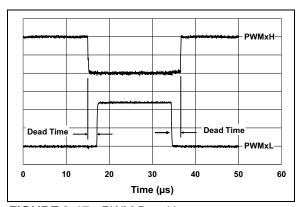

FIGURE 2-17: PWM Deadtime.

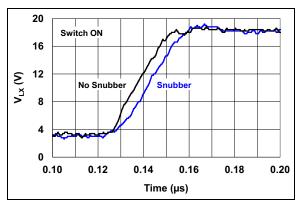

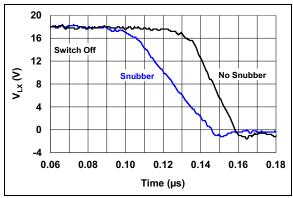

FIGURE 2-18: Buck Snubber Turn On.

**Note:** Unless otherwise indicated:  $T_A = +25^{\circ}C$ ; Junction Temperature  $(T_J)$  is approximated by soaking the device under test to an ambient temperature equal to the desired junction temperature. The test time is small enough such that the rise in Junction temperature over the Ambient temperature is not significant.

FIGURE 2-19: Buck Snubber Turn Off.

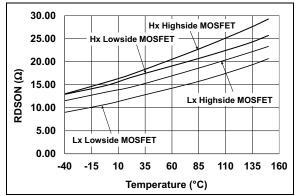

FIGURE 2-20: Gate Driver RDS<sub>ON</sub> vs Temperature.

### 3.0 PIN DESCRIPTIONS

# 3.1 Functional Pin Descriptions

| Pin No.<br>QFN | Pin No.<br>TQFP | Symbol      | 1/0   | Description                                                                 |

|----------------|-----------------|-------------|-------|-----------------------------------------------------------------------------|

| 1              | 48              | PWM2H       | I     | Digital input, phase B high-side control, 47K pulldown                      |

| 2              | 1               | PWM1L       | I     | Digital input, phase A low-side control, 47K pulldown                       |

| 3              | 2               | PWM1H       | I     | Digital input, phase A high-side control, 47K pulldown                      |

| 4              | 3               | CE          | I     | Digital input, device enable, 47K pulldown                                  |

| -              | 4               | LV_OUT2     | 0     | Digital logic level translated output interface, open drain                 |

| -              | 5               | HV_IN2      | I     | High-voltage input interface, 30K pullup via Configuration register 0 bit 6 |

| 5              | 6               | HV_IN1      | I     | High-voltage input interface, 30K pullup via Configuration register 0 bit 6 |

| -              | 7               | PGND        | Power | Power 0V reference                                                          |

| 6              | 8               | LV_OUT1     | 0     | Digital logic level translated output interface, open drain                 |

| 7              | 9               | I_OUT3      | 0     | Motor phase current sense amplifier output                                  |

| 8              | 10              | ISENSE3-    | I     | Motor phase current sense amplifier inverting input                         |

| 9              | 11              | ISENSE3+    | I     | Motor phase current sense amplifier non-inverting input                     |

| 10             | 12              | I_OUT2      | 0     | Motor phase current sense amplifier output                                  |

| 11             | 13              | ISENSE2-    | I     | Motor phase current sense amplifier inverting input                         |

| 12             | 14              | ISENSE2+    | I     | Motor phase current sense amplifier non-inverting input                     |

| 13             | 15              | /ILIMIT_OUT | 0     | Current limit comparator, MOSFET driver fault output, open drain            |

| 14             | 16              | I_OUT1      | 0     | Motor current sense amplifier output                                        |

| 15             | 17              | ISENSE1-    | 1     | Motor current sense amplifier inverting input                               |

| 16             | 18              | ISENSE1+    | I     | Motor current sense amplifier non-inverting input                           |

| 17             | 19,20           | PGND        | Power | Power 0V reference                                                          |

| 18             | 21              | LA          | 0     | Phase A low-side N-Channel MOSFET driver, active-high                       |

| 19             | 22              | LB          | 0     | Phase B low-side N-Channel MOSFET driver, active-high                       |

| 20             | 23              | LC          | 0     | Phase C low-side N-Channel MOSFET driver, active-high                       |

| -              | 24              | PGND        | Power | Power 0V reference                                                          |

| 21             | 25              | HC          | 0     | Phase C high-side N-Channel MOSFET driver, active-high                      |

| 22             | 26              | HB          | 0     | Phase B high-side N-Channel MOSFET driver, active-high                      |

| 23             | 27              | HA          | 0     | Phase A high-side N-Channel MOSFET driver, active-high                      |

| 24             | 28              | PHC         | I/O   | Phase C high-side MOSFET driver reference, back EMF sense input             |

| 25             | 29              | PHB         | I/O   | Phase B high-side MOSFET driver reference, back EMF sense input             |

| 26             | 30              | PHA         | I/O   | Phase A high-side MOSFET driver reference, back EMF sense input             |

| 27             | 31              | VBC         | Power | Phase C high-side MOSFET driver bias                                        |

| 28             | 32              | VBB         | Power | Phase B high-side MOSFET driver bias                                        |

| 29             | 33              | VBA         | Power | Phase A high-side MOSFET driver bias                                        |

| 30             | 34              | +12V        | Power | Analog circuitry and low-side gate drive bias                               |

| -              | 35,36           | PGND        | Power | Power 0V reference                                                          |

| 31             | 37              | LX          | Power | Buck regulator switch node, external inductor connection                    |

| 32             | 38, 39          | VDD         | Power | Input supply                                                                |

| 33             | 40              | FB          | I     | Buck regulator feedback node                                                |

| 34             | 41              | +5V         | Power | Internal circuitry bias                                                     |

| 35             | 42              | CAP2        | Power | Charge pump flying capacitor input                                          |

| 36             | 43              | CAP1        | Power | Charge pump flying capacitor input                                          |

| 37             | 44              | DE2         | 0     | Voltage and temperature supervisor output, open drain                       |

| 38             | 45              | PWM3L       | 1     | Digital input, phase C low-side control, 47K pulldown                       |

| 39             | 46              | PWM3H       | 1     | Digital input, phase C high-side control, 47K pulldown                      |

| 40             | 47              | PWM2L       | 1     | Digital input, phase B low-side control, 47K pulldown                       |

| EP             | EP              | PGND        | Power | Exposed Pad, Connect to Power 0V reference                                  |

### 3.2 V<sub>DD</sub>

Connect  $V_{DD}$  to the main supply voltage. This voltage must not exceed the maximum operating limits of the device. Connect a bulk capacitor close to this pin for good load step performance and transient protection.

The type of capacitor used can be ceramic, tantalum or aluminum electrolytic. The low ESR characteristics of the ceramic will yield better noise and PSRR performance at high frequency.

#### 3.3 PGND, Exposed Pad (EP)

Device ground. The PCB ground traces should be short, wide, and form a STAR pattern to the power source. The Exposed Pad (EP) PCB area should be a copper pour with thermal vias to help transfer heat away from the device.

#### 3.4 + 12V

+12 volt Low Dropout (LDO) voltage regulator output. The +12V LDO may be used to power external devices such as Hall-effect sensors or amplifiers. The LDO requires an output capacitor for stability. The positive side of the output capacitor should be physically located as close to the +12V pin as is practical. For most applications, 4.7  $\mu$ F of capacitance will ensure stable operation of the LDO circuit.

The type of capacitor used can be ceramic, tantalum or aluminum electrolytic. The low ESR characteristics of the ceramic will yield better noise and PSRR performance at high frequency.

#### 3.5 + 5V

+5 volt Low Dropout (LDO) voltage regulator output. The +5V LDO may be used to power external devices such as Hall-effect sensors or amplifiers. The LDO requires an output capacitor for stability. The positive side of the output capacitor should be physically located as close to the +5V pin as is practical. For most applications, 4.7  $\mu$ F of capacitance will ensure stable operation of the LDO circuit.

The type of capacitor used can be ceramic, tantalum or aluminum electrolytic. The low ESR characteristics of the ceramic will yield better noise and PSRR performance at high frequency.

#### 3.6 LX

Buck regulator switch node external inductor connection. Connect this pin to the external inductor chosen for the buck regulator.

#### 3.7 FB

Buck regulator feedback node that is compared with internal 1.25V reference voltage. Connect this pin to a resistor divider that sets the buck regulator output

voltage. Connecting this pin to the +5V LDO output disables the buck regulator.

#### 3.8 CAP1, CAP2

Charge pump flying capacitor inputs. Connect the charge pump capacitor across these two pins.

#### 3.9 CE

Chip Enable input used to enable/disable the output driver and on-board functions. When CE is high, all device functions are enabled. When CE is low, the device operates in Reduced mode. The H-Bridge, current amplifiers and 12V LDO are disabled. The buck regulator, 5V LDO, DE2, voltage and temperature sensor functions are not affected.

The CE is also used to clear any hardware faults. When a fault occurs, the CE input may be used to clear the fault by setting the pin low and then high again. The fault is cleared by the rising edge of the CE signal if the hardware fault is no longer active.

The CE pin has an internal 47K pulldown.

#### 3.10 | I OUT1, I OUT2, I OUT3

Current sense amplifier output. May be used with feedback resistors to set the current sense gain.

#### 3.11 ISENSE1, ISENSE2, ISENSE3 +/-

Current sense amplifier inverting and non-inverting inputs. Used in conjunction with I\_OUTx pins to set current sense gain.

### 3.12 /ILIMIT OUT

Current limit output signal. The open-drain output goes low when the current sensed by current sense amplifier 1 exceeds the value set by the internal current reference DAC. The DAC has an offset of 0.991V (typical) which represents zero current flow. The open-drain output will also go low while a motor fault is active.

#### 3.13 **PWM1H**, **PWM2H**, **PWM3H**

Digital PWM inputs for high-side driver control. Each input has a 47K pulldown to ground. The PWM signals may contain dead-time timing or the system may use the Configuration register 2 to set the dead time.

#### 3.14 PWM1L, PWM2L, PWM3L

Digital PWM inputs for low-side driver control. Each input has a 47K pulldown to ground. The PWM signals may contain dead-time timing or the system may use the Configuration register 2 to set the dead time.

#### 3.15 LA, LB, LC

Low-side N-channel MOSFET drive signal. Connect to the gate of the external MOSFETs. A low-impedance resistor may be used between these pins and the MOSFET gates to limit current and slew rate.

#### 3.16 HA, HB, HC

High-side N-channel MOSFET drive signal. Connect to the gate of the external MOSFETs. A low-impedance resistor may be used between these pins and the MOSFET gates to limit current and slew rate.

#### 3.17 PHA, PHB, PHC

Phase signals from motor. Provides high-side N-channel MOSFET driver reference and Back EMF sense input. The phase signals are also used with the bootstrap capacitors to provide high-side gate drive via the VBx inputs.

#### 3.18 VBA, VBB, VBC

High-side MOSFET driver bias. Connect these pins between the bootstrap charge pump diode cathode and bootstrap charge pump capacitor. The 12V LDO output is used to provide 12V at the diode anodes. The phase signals are connected to the other side of the bootstrap charge pump capacitors.

#### 3.19 DE2

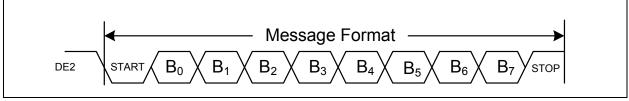

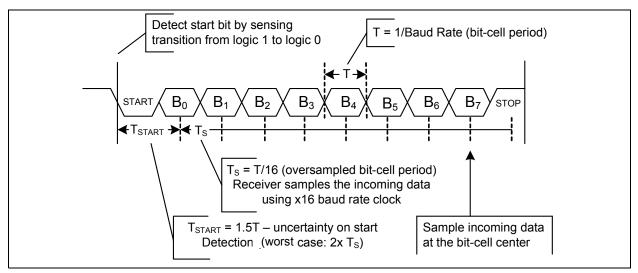

Open-drain communications node. The DE2 communications is a half-duplex 9600 baud, 8-bit, no parity communications link. The open-drain DE2 pin must be pulled high by an external pull-up resistor.

### 3.20 HV\_IN1, HV\_IN2, LV OUT1,LV OUT2

Unidirectional digital level translators. Translates digital input signal on the HV\_INx pin to a low-level digital output signal on the LV\_OUTx pin. The HV\_INx pins have internal  $30 \text{K}\Omega$  pullups to V\_DD that are controlled by Configuration register 0 bit 6. The Configuration register 0 bit 6 is only sampled during CE = 0. The HV\_IN1 pin has higher ESD protection than the HV\_IN2 pin. The higher ESD protection makes the HV\_IN1 pin better suited for connection to external switches.

LV\_OUT1 and LV\_OUT2 are open-drain outputs. An external pull-up resistor to the low-voltage logic supply is required.

#### 4.0 DETAILED DESCRIPTION

### 4.1 BIAS GENERATOR

The internal bias generator controls three voltage rails. Two fixed-output low-dropout linear regulators, an adjustable buck switch-mode power converter, and an unregulated charge pump are controlled through the bias generator. In addition, the bias generator performs supervisory functions.

# 4.1.1 +12V LOW-DROPOUT LINEAR REGULATOR (LDO)

The +12V rail is used for bias of the 3-phase power MOSFET bridge.

The regulator is capable of supplying 20mA of external load current. The regulator has a minimum overcurrent limit of 30 mA.

The low-dropout regulators require an output capacitor connected from VOUT to GND to stabilize the internal control loop. A minimum of  $4.7\mu F$  ceramic output capacitance is required for the 12V LDO.

# 4.1.2 +5V LOW-DROPOUT LINEAR REGULATOR (LDO)

The +5V LDO is used for bias of an external microcontroller, the internal current sense amplifier and the gate control logic.

The +5V LDO is capable of supplying 20mA of external load current. The regulator has a minimum overcurrent limit of 30 mA. If additional external current is required, the buck switch-mode power converter should be utilized.

A minimum of 4.7  $\mu\text{F}$  ceramic output capacitance is required for the 5V LDO.

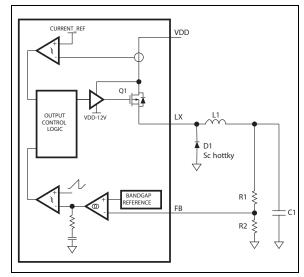

# 4.1.3 BUCK SWITCH-MODE POWER CONVERTER (SMPS)

The SMPS is a high-efficiency, fixed-frequency, stepdown DC-DC converter. The SMPS provides all the active functions for local DC-DC conversion with fast transient response and accurate regulation.

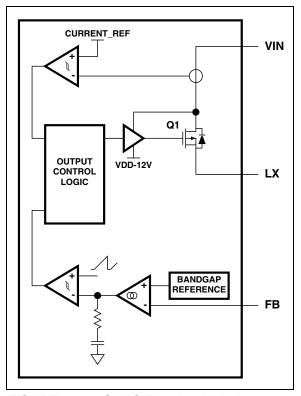

During normal operation of the buck power stage, Q1 is repeatedly switched on and off with the on and off times governed by the control circuit. This switching action causes a train of pulses at the LX node which are filtered by the L/C output filter to produce a DC output voltage, V<sub>O</sub>. Figure 4-1 depicts the functional block diagram of the SMPS.

FIGURE 4-1: SMPS Functional Block Diagram.

The SMPS is designed to operate in Discontinuous Conduction Mode (DCM) with Voltage mode control and current limit protection. The SMPS is capable of supplying 5V, 150mA to an external load at a fixed switching frequency of 460 kHz with an input voltage of 6V. The output of the SMPS is power limited. Therefore, for a programmed output voltage of 3V, the SMPS will be capable of supplying 250mA to an external load. An external diode is required between the LX pin and ground. The diode will be required to handle the inductor current when the switch is off. The diode is external to the device to reduce substrate currents and power dissipation caused by the switcher. The external diode carries the current during the switch off time, eliminating the current path back through the device.

At light loads the SMPS enters Pulse Frequency Modulation (PFM), improving efficiency at the expense of higher output voltage ripple. The PFM circuitry provides a means to disable the SMPS as well. If the SMPS is not utilized in the application, connecting the feedback pin (FB) to an external 2.5V-to-5.0V supply will force the SMPS to a shutdown state.

The maximum inductor value for operation in Discontinuous Conduction mode can be determined by the following equation.

#### EQUATION 4-1: LMAX SIMPLIFIED

$$L_{MAX} \leq \frac{V_O \times \left(1 - \frac{V_O}{V_{IN}}\right) \times T}{2 \times I_{O(CRIT)}}$$

Using the  $L_{MAX}$  inductor value calculated using Equation 4-1 will ensure Discontinuous Conduction mode operation for output load currents below the critical current level,  $I_{O(CR|T)}$ . For example, with an output voltage of +5V, a standard inductor value of 4.7 $\mu$ H will ensure Discontinuous Conduction mode operation with an input voltage of 6V, a switching frequency of 468 kHz, and a critical load current of 150 mA.

The output voltage is set by using a resistor divider network. The resistor divider is connected between the inductor output and ground. The divider common point is connected to the FB pin which is then compared to an internal 1.25V reference voltage.

The Buck regulator will set a Status bit and send a status message to the host whenever the input switching current exceeds two amperes peak (typical). The bit will be cleared when the peak input switching current drops back below the two ampere (typical) limit.

The Buck regulator will set a Status bit and send a status message to the host whenever the output voltage drops below 90% of the rated output voltage. The bit will be cleared when the output voltage returns to 94% of rated value.

If the Buck regulator output voltage falls below 80% of rated output voltage, the system will shutdown with a "Brown-out Error". This will notify the Host of a power failure and subsequent loss of configuration.

The Voltage Supervisor is designed to shutdown the buck regulator when  $V_{DD}$  rises above OVLO<sub>STOP</sub>. When shutting down the buck regulator is not desirable, the user should add a voltage suppression device to the  $V_{DD}$  input in order to prevent  $V_{DD}$  from rising above OVLO<sub>STOP</sub>.

The Voltage Supervisor is also designed to shutdown the buck regulator when  $V_{DD}$  falls below  $UVLO_{STOP}$ .

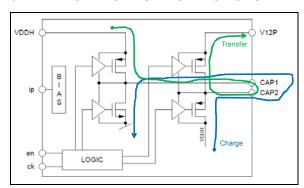

#### 4.1.4 CHARGE PUMP

An unregulated charge pump is utilized to boost the input to the +12V LDO during low-input conditions. When the input bias to the device ( $V_{DD}$ ) drops below  $CP_{START}$ , the charge pump is activated. When activated, 2 x  $V_{DD}$  is presented to the input of the +12V LDO, which maintains a minimum +10V at its output.

The typical charge pump flying capacitor is a 0.1  $\mu F$  to 1.0  $\mu F$  ceramic capacitor.

#### 4.1.5 SUPERVISOR

The bias generator incorporates a voltage supervisor and a temperature supervisor.

#### 4.1.5.1 Voltage Supervisor

The voltage supervisor protects the device, external power MOSFETs, and the external microcontroller from damage due to overvoltage or undervoltage of the input supply, VDD.

In the event of an undervoltage condition,  $V_{DD}$  < +5.5V, the motor drivers are switched off. The bias generator, communication port, and the remainder of the motor control unit remain active. The failure state is flagged on the DE2 pin with a status message. In extreme overvoltage conditions,  $V_{DD}$  > +32V, all functions are turned off.

#### 4.1.5.2 Temperature Supervisor

An integrated temperature sensor self protects the device circuitry. If the temperature rises above the overtemperature shutdown threshold, all functions are turned off. Active operation resumes when the temperature has cooled down below a set hysteresis value and the fault has been cleared by toggling CE.

It is desirable to signal the microcontroller with a warning message before the overtemperature threshold is reached. The microcontroller should take appropriate actions to reduce the temperature rise. The method to signal the microcontroller is through the DE2 pin.

#### 4.2 MOTOR CONTROL UNIT

The motor control unit is comprised of the following:

- External Drive for a 3-Phase Bridge with NMOS/ NMOS MOSFET pairs

- · Three Motor Current Sense Amplifiers

- · Motor Overcurrent Comparator

# 4.2.1 MOTOR CURRENT SENSE CIRCUITRY

The internal motor current sense circuitry consists of an operational amplifier and comparator. The amplifier output is presented to the inverting comparator input and as an output to the microcontroller. The non-inverting comparator input is connected to an internally programmable 8-bit DAC. A selectable motor current limit threshold may be set with a SET\_ILIMIT message from the host to the MCP8024 via the DE2 communications link. The 8-bit DAC is powered by the 5V supply. The DAC output voltage range is 0.991V to 4.503V. The DAC has a bit value of (4.503V - 0.991V) / (2^8 - 1) = 13.77 mV/bit. A DAC input of 00H yields a DAC output voltage of 0.991V. The default power-up DAC value is 40H (1.872V). The DAC uses a 100 kHz filter. Input code to output voltage delay is

approximately five time constants ~= 50 µs. The desired current sense gain is established with an external resistor network.

Note

The motor current limit comparator output is internally 'OR'd with the DRIVER FAULT output of the driver logic block. The microcontroller should monitor the comparator output and take appropriate actions. The motor current limit comparator circuitry does not disable the motor drivers when an overcurrent situation occurs. Only one current limit comparator is provided. The MCP8024 provides three current sense amplifiers which can be used for implementation of advanced control algorithms such as Field Oriented Control (FOC).

The comparator output may be employed as a current limit. Alternatively, the current sense output can be employed in a chop-chop PWM speed loop for any situations where the motor is being accelerated, either positively or negatively. An analog chop-chop speed loop can be implemented by hysteretic control or fixed off-time of the motor current. This makes for a very robust controller as the motor current is always in instantaneous control.

A sense resistor in series with the bridge ground return provides a current signal for both feedback and current limiting. This resistor should be non-inductive to minimize ringing from high di/dt. Any inductance in the power circuit represents potential problems in the form of additional voltage stress and ringing, as well as increasing switching times. While impractical to eliminate, careful layout and bypassing will minimize these effects. The output stage should be as compact as heat sinking will allow, with wide, short traces carrying all pulsed currents. Each half-bridge should be separately bypassed with a low ESR/ESL capacitor, decoupling it from the rest of the circuit. Some layouts will allow the input filter capacitor to be split into three smaller values, and serve double duty as the halfbridge bypass capacitors.

Note:

With a chop-chop control, motor current always flows through the sense resistor. When the PWM is off, however, the flyback diodes, or synchronous rectifiers, conduct, causing the current to reverse polarity through the sense resistor.

The current sense resistor is chosen to establish the peak current limit threshold, which is typically set 20% higher than the maximum current command level to provide overcurrent protection during abnormal conditions. Under normal circumstances with a properly compensated current loop, peak current limit will not be exercised.

#### 4.2.2 MOTOR CONTROL

The commutation loop of a BLDC motor control is a Phase-Locked Loop (PLL) which locks to the rotor's position. Note that this inner loop does not attempt to modify the position of the rotor, but modifies the commutation times to match whatever position the rotor has. An outer speed loop changes the rotor velocity, and the commutation loop locks to the rotor's position to commutate the phases at the correct times.

#### 4.2.2.1 Sensorless Motor Control

Many control algorithms can be implemented with the MCP8024 in conjunction with a microcontroller. The following discussion provides a starting point for implementing the MCP8024 in a sensorless control application of a 3-phase motor. The motor is driven by energizing two windings at a time and sequencing the windings in a six step per electrical revolution method. This method leaves one winding unenergized at all times, and the voltage on that unenergized (Back EMF) winding can be monitored to determine the rotor position.

#### 4.2.2.2 Start-Up Sequence

When the motor being driven is at rest, the back EMF is equal to zero. The motor needs to be rotating for the back EMF sensor to lock onto the rotor position and commutate the motor. The recommended start-up sequence to bring the rotor from rest up to a speed fast enough to allow back EMF sensing is comprised of three modes: Lock or Align mode, Ramp mode, and Run mode. Refer to the commutation state machine in Table 4-1. The order in which the microcontroller steps through the commutation state machine determines the direction the motor rotates.

#### 4.2.2.3 Disabled Mode (CE = 0)

When the driver is disabled (CE = 0), all of the drivers are turned off.

#### 4.2.2.4 Lock Mode

Before the motor can be started, the rotor must be in a known position. In Lock mode, the microcontroller drives phase B low and phases A and C high. This aligns the rotor 30 electrical degrees before the center of the first commutation state. Lock mode must last long enough to allow the motor and its load to settle into this position.

#### 4.2.2.5 Ramp Mode

At the end of Lock mode, Ramp mode is entered. In Ramp mode, the microcontroller steps through the commutation state machine, increasing linearly, until a minimum speed is reached. Ramp mode is an open-loop commutation. No knowledge of the rotor position is used.

#### 4.2.2.6 Run Mode

At the end of the Ramp mode, Run mode is entered. In Run mode, the back EMF sensor is enabled and commutation is now under the control of the phase-locked loop. Motor speed can be regulated by an outer speed control loop.

TABLE 4-1: COMMUTATION STATE MACHINE