**CMOS LSI**

# Iris/Zoom/Focus/ Day-Night switching Drive Controller

http://onsemi.com

# Overview

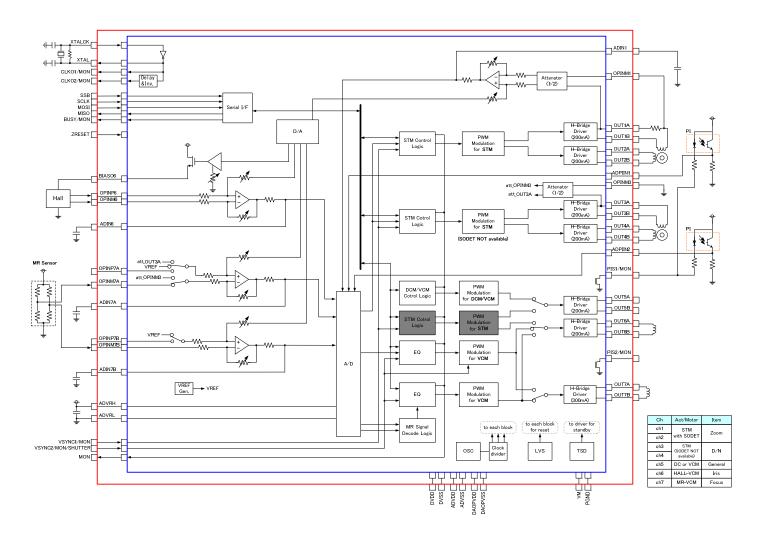

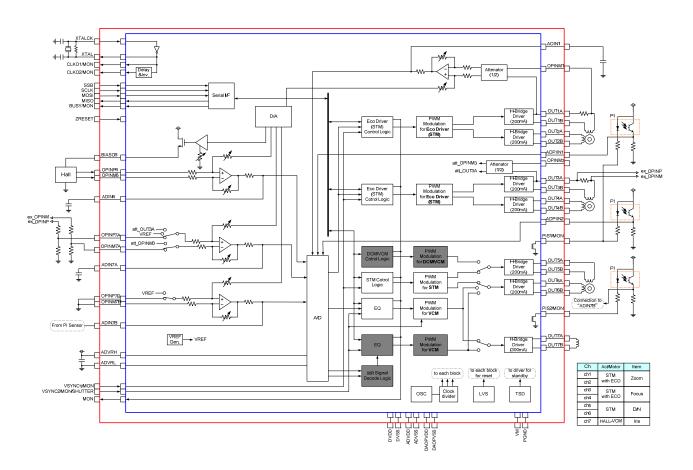

LC898201 is the appropriate motor control LSI for the surveillance camera usage, and it can drive iris, focus, zoom and Day/Night switching simultaneously.

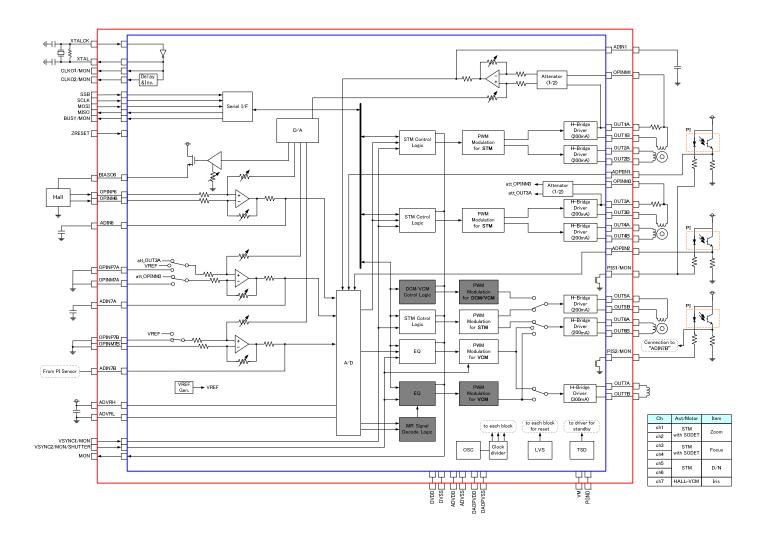

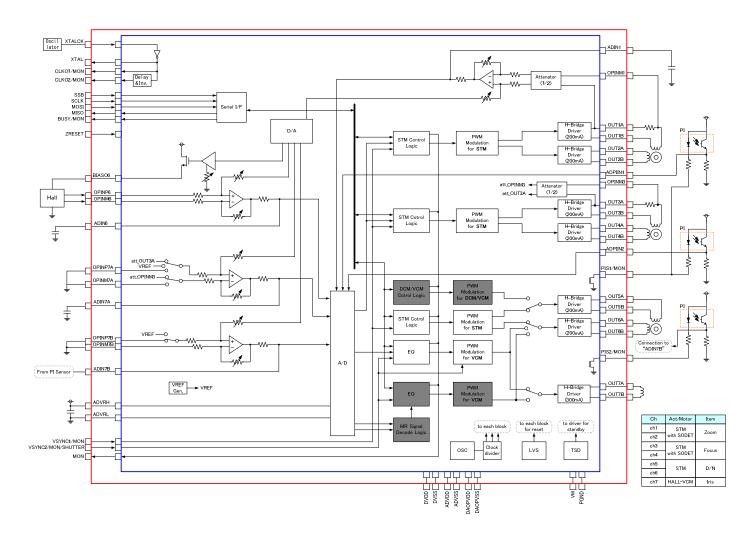

It incorporates two feedback circuits for iris and focus control, and two stepper motor control circuits for zoom and Day/Night switching (cf. P4 Application-1).

Moreover, the feedback control applies iris control, and stepper motor controls apply focus, zoom and Day/Night switching at the mode selection (cf. Application-2 to 4 of P5 to P7).

Stepper motor control circuits can drive the stepping motor efficiently(It is called "ECO(GREEN)-driver") (For a limited numerical usable channel, refer to Application-1 to 4 of P4 to P7).

TQFP64 7x7 [ LC898201TA-NH ]

# **Features**

- Built-in equalizer circuit by digital operation

- Iris control equalizer circuit

- Focus control equalizer circuit (MR sensor can be connected.)

- Coefficients can be set arbitrarily through the SPI interface.

- Computed values in the equalizer can be monitored.

- Built-in 3ch stepping motor control circuits (2ch are equipped with "ECO(GREEN)-driver" circuits) (Usable channel is shown in Application-1 to 4 of P4 to P7)

- SPI bus interface

- PI control circuit

- 30mA Sink output terminal

- Built-in PI detecting function (A/D method)

- A/D converter

- 12bit (6ch)

- : Iris, Focus, ECO, PI detection

- D/A converter

- 8bit (5ch)

- : Hall offset, Constant current bias, MR Sensor offset, ECO offset

- Operation Amplifier

- 4ch (ECO  $\times$ 1, Iris control x1, Focus control  $\times$ 2)

To the next page.

# ORDERING INFORMATION

See detailed ordering and shipping information on page 16 of this data sheet.

FBGA64 6x6 [ LC898201RA-NH ]

# ■ PWM pulse generator

- PWM Pulse generator for feedback control (Up to 12bit accuracy)

- PWM pulse generator for stepper motor control (Up to 1024 micro steps)

- PWM pulse generator for general-purpose H-Bridge (128 voltage levels)

# ■ Motor Driver

- ch1 to ch6: Io max=200mA

- ch7 : Io max=300mA

- Built-in thermal protection circuit

- Built-in low-voltage malfunction prevention circuit

- OSC (Type. 48MHz)

# ■ Package

- LC898201TA-NH: TQFP64(7×7) 0.4mm pitch

- LC898201RA-NH: FBGA64(6.0×6.0) 0.5mm pitch

- Lead-free, Halogen-free

# ■ Power supply voltage

Logic unit : 2.7V to 3.6V (IO, Internal core)

Driver unit : 2.7V to 5.5V (Motor drive)

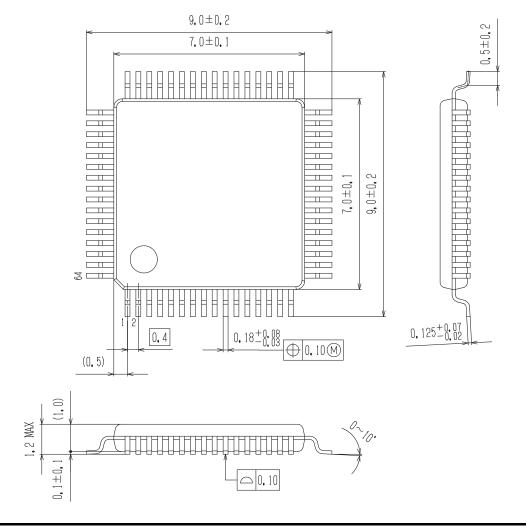

# **Package Dimensions**

unit: mm

[LC898201TA-NH]

# **TQFP64 7x7 / TQFP64**

CASE 932BC ISSUE O

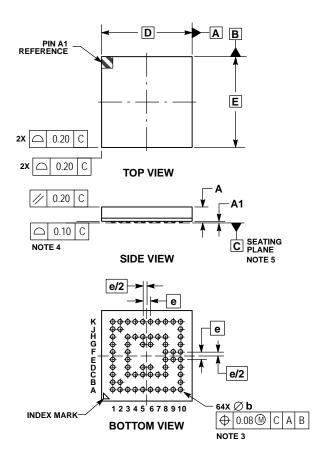

# **Package Dimensions**

unit: mm

[LC898201RA-NH]

# **FBGA64 6x6**

CASE 113BL **ISSUE O**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION & IS MEASURED AT THE MAXIMUM SOLDER BALL DIAMETER PARALLEL TO DATUM C.

4. COPLANARITY APPLIES TO SPHERICAL CROWNS OF SOLDER BALLS.

5. DIMENSION C, THE SEATING PLANE, IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.

|     | MILLIMETERS          |      |  |  |  |  |

|-----|----------------------|------|--|--|--|--|

| DIM | MIN                  | MAX  |  |  |  |  |

| Α   |                      | 1.05 |  |  |  |  |

| A1  | 0.05                 | 0.15 |  |  |  |  |

| b   | 0.24                 | 0.34 |  |  |  |  |

| D   | 6.00 BSC<br>6.00 BSC |      |  |  |  |  |

| Е   |                      |      |  |  |  |  |

| е   | 0.50                 | BSC  |  |  |  |  |

### **RECOMMENDED SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

# **Block Diagram**

# Application-1

MR-VCM

# Application-2

Stepper Motor 3ch & Crystal oscillator(or Ceramic oscillator)

# **Application-3**

Stepper Motor 3ch & Oscillator

# **Application-4**

Stepper Motor 3ch & ECO external connection

# **Pin Description**

| TYPE |              |   |            |    |             |  |  |  |

|------|--------------|---|------------|----|-------------|--|--|--|

| ı    | INPUT        | Р | Power, GND | NC | NOT CONNECT |  |  |  |

| 0    | OUTPUT       |   |            |    |             |  |  |  |

| B(I) | BIDIRECTION: |   |            |    |             |  |  |  |

| B(O) | BIDIRECTION: |   |            |    |             |  |  |  |

| ■ SPI interface (Slave) SSB SCLK MOSI MISO BUSY/MON                      | I<br>I<br>I<br>B(O)<br>B(O)     | Chip select Clock Received data Transmit data Transfer busy / Monitor output                                                                                                                                                                                                              |

|--------------------------------------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ■ PI sensor drive signa<br>PIS1/MON<br>PIS2/MON                          | l output<br>B(O)<br>B(O)        | PI sensor drive signal output 1 / Monitor output<br>PI sensor drive signal output 2 / Monitor output                                                                                                                                                                                      |

| ■ Video synchronizing :<br>VSYNC1/MON<br>VSYNC2/MON<br>/SHUTTER          | signal input<br>B(I)<br>B(I)    | Video synchronizing signal input / Monitor output (with pull-down resistance) Video synchronizing signal input / Monitor output / Shutter input (with pull-down resistance)                                                                                                               |

| <ul><li>Monitor output<br/>MON</li></ul>                                 | B(O)                            | Monitor output                                                                                                                                                                                                                                                                            |

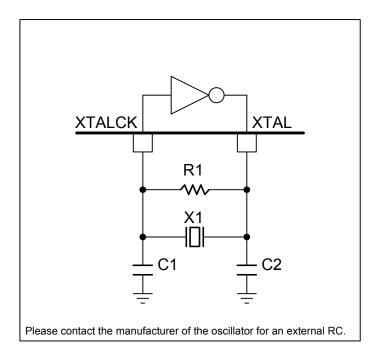

| ■ Clock output XTALCK XTAL CLKO1/MON CLKO2/MON                           | I<br>O<br>B(O)<br>B(O)          | Oscillation amplifier input : 27MHz Oscillation amplifier output Clock output 1 / Monitor output Clock output 2 / Monitor output                                                                                                                                                          |

| ■ Reset<br>ZRESET                                                        | I                               | Reset signal input(Low active)                                                                                                                                                                                                                                                            |

| ■ Bias current pin<br>BIASO6                                             | O                               | CH6 Bias current output                                                                                                                                                                                                                                                                   |

| ■ OP Amp pin OPINM1 OPINM3 OPINP6 OPINM6 OPINP7A OPINM7A OPINP7B OPINM7B | I<br>I<br>I<br>I<br>I<br>I<br>I | CH1 OP Amp input(-) with ATT CH3 OP Amp input(-) with ATT CH6 OP Amp input (+) CH6 OP Amp input (-) CH7-A OP Amp input (+) CH7-B OP Amp input (-) CH7-B OP Amp input (+)                                                                                                                  |

| ■ A/D input pin ADIN1 ADIN6 ADIN7A ADIN7B ADPIIN1 ADPIIN2 ADVRH ADVRL    | B<br>B<br>B<br>I<br>I<br>I      | CH1 A/D input (CH1 OP Amp output) CH6 A/D input (CH6 OP Amp output) CH7-A A/D input (CH7 OP Amp output) CH7-B A/D input (CH7 OP Amp output) CH1/2 PI sensor signal A/D input CH3/4 PI sensor signal A/D input A/D conversion range standard voltage A/D conversion range standard voltage |

| ■ H-Bridge  |   |                     |

|-------------|---|---------------------|

| OUT1A       | O | CH1 H-Bridge output |

| OUT1B       | O | CH1 H-Bridge output |

| OUT2A       | O | CH2 H-Bridge output |

| OUT2B       | O | CH2 H-Bridge output |

| OUT3A       | O | CH3 H-Bridge output |

| OUT3B       | O | CH3 H-Bridge output |

| OUT4A       | O | CH4 H-Bridge output |

| OUT4B       | O | CH4 H-Bridge output |

| OUT5A       | O | CH5 H-Bridge output |

| OUT5B       | O | CH5 H-Bridge output |

| OUT6A       | O | CH6 H-Bridge output |

| OUT6B       | O | CH6 H-Bridge output |

| OUT7A       | O | CH7 H-Bridge output |

| OUT7B       | О | CH7 H-Bridge output |

| ■ Power pin |   |                     |

| DVDD        | P | Digital VDD         |

| DVSS        | P | Digital GND         |

| DAOPVDD     | P | D/A, OP Amp VDD     |

| DAOPVSS     | P | D/A, OP Amp GND     |

| ADVDD       | P | A/D VDD             |

| ADVSS       | P | A/D GND             |

| VM          | P | H-Bridge VDD        |

| PGND        | P | H-Bridge GND        |

# \* Process when pins are not used

PIN TYPE "O" ····· The pin must be left open.

PIN TYPE "I" · · · · · The pin must not be left open. Please make sure to connect the pin to Vdd or Vss even when it

is not used. (Please check with us whether to connect to Vdd or Vss.)

PIN TYPE "B" ···· Please contact us if you are uncertain about a processing method in the pin description in the

PIN layout table.

A problem may occur if the processing method is used wrongly for any unused pin.

Please make sure to contact us.

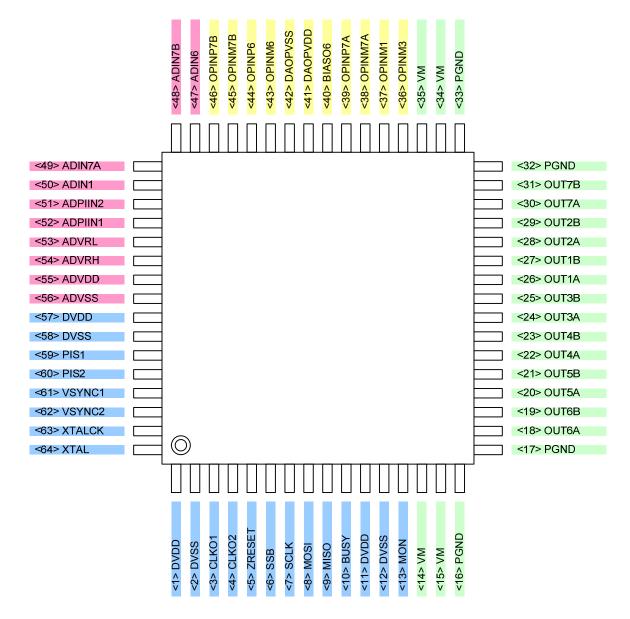

# **Pin Assignment**

<TOP VIEW> TQFP64(7X7)

| 10 | DVDD  | VSYNC2 | PIS2   | DVSS   | ADVSS | ADVDD | ADPI<br>IN1 | ADPI<br>IN2 | ADIN7A | ADIN7B      |

|----|-------|--------|--------|--------|-------|-------|-------------|-------------|--------|-------------|

| 9  | DVSS  |        |        |        | ADVRL | ADVRH |             |             |        | ADIN6       |

| 8  | CLKO1 |        | XTALCK | VSYNC1 | PIS1  | DVDD  | ADIN1       | OPINM<br>7B |        | OPINP<br>7B |

| 7  | CLKO2 |        | XTAL   |        |       |       |             | OPINM6      |        | OPINP6      |

| 6  | SSB   |        | ZRESET | SCLK   |       |       | BIASO6      | DAOP<br>VSS |        | DAOP<br>VDD |

| 5  | MISO  |        | BUSY   | MOSI   |       |       | OPINM1      | OPINP<br>7A |        | OPINM<br>7A |

| 4  | DVDD  |        | DVSS   |        |       |       |             | OPINM3      |        | OUT7A       |

| 3  | MON   |        | OUT6A  | OUT5A  | OUT4A | OUT3A | OUT1A       | OUT2A       |        | OUT7B       |

| 2  | VM    | VM     |        |        |       |       |             |             | VM     | VM          |

| 1  | PGND  | PGND   | OUT6B  | OUT5B  | OUT4B | OUT3B | OUT1B       | OUT2B       | PGND   | PGND        |

|    | A     | В      | С      | D      | E     | F     | G           | Н           | J      | К           |

<TOP VIEW> FBGA64(6.0X6.0)

# **PIN** number

| Pin    | Pin No. |      | Dia nama |

|--------|---------|------|----------|

| TQFP64 | FBGA64  | Туре | Pin name |

| 1      | A10     | Р    | DVDD     |

| 2      | A9      | Р    | DVSS     |

| 3      | A8      | B(O) | CLKO1    |

| 4      | A7      | B(O) | CLKO2    |

| 5      | C6      | I    | ZRESET   |

| 6      | A6      | I    | SSB      |

| 7      | D6      | I    | SCLK     |

| 8      | D5      | I    | MOSI     |

| 9      | A5      | B(O) | MISO     |

| 10     | C5      | B(O) | BUSY     |

| 11     | A4      | Р    | DVDD     |

| 12     | C4      | Р    | DVSS     |

| 13     | A3      | B(O) | MON      |

| 14     | B2      | Р    | VM       |

| 15     | A2      | Р    | VM       |

| 16     | B1      | Р    | PGND     |

| Pin    | No.    | Tuno | Din nama |

|--------|--------|------|----------|

| TQFP64 | FBGA64 | Type | Pin name |

| 33     | J1     | Р    | PGND     |

| 34     | J2     | Р    | VM       |

| 35     | K2     | Р    | VM       |

| 36     | H4     | - 1  | OPINM3   |

| 37     | G5     | 1    | OPINM1   |

| 38     | K5     | 1    | OPINM7A  |

| 39     | H5     | 1    | OPINP7A  |

| 40     | G6     | 0    | BIASO6   |

| 41     | K6     | Р    | DAOPVDD  |

| 42     | H6     | Р    | DAOPVSS  |

| 43     | H7     | I    | OPINM6   |

| 44     | K7     | 1    | OPINP6   |

| 45     | H8     | ı    | OPINM7B  |

| 46     | K8     | I    | OPINP7B  |

| 47     | K9     | В    | ADIN6    |

| 48     | K10    | В    | ADIN7B   |

| Pin    | No.    | Tuna | Din nome |

|--------|--------|------|----------|

| TQFP64 | FBGA64 | Type | Pin name |

| 17     | A1     | Р    | PGND     |

| 18     | C3     | 0    | OUT6A    |

| 19     | C1     | 0    | OUT6B    |

| 20     | D3     | 0    | OUT5A    |

| 21     | D1     | 0    | OUT5B    |

| 22     | E3     | 0    | OUT4A    |

| 23     | E1     | 0    | OUT4B    |

| 24     | F3     | 0    | OUT3A    |

| 25     | F1     | 0    | OUT3B    |

| 26     | G3     | 0    | OUT1A    |

| 27     | G1     | 0    | OUT1B    |

| 28     | H3     | 0    | OUT2A    |

| 29     | H1     | 0    | OUT2B    |

| 30     | K4     | 0    | OUT7A    |

| 31     | K3     | 0    | OUT7B    |

| 32     | K1     | Р    | PGND     |

| Pin No. |        | Tuno | Pin name |  |

|---------|--------|------|----------|--|

| TQFP64  | FBGA64 | Туре | Pin name |  |

| 49      | J10    | В    | ADIN7A   |  |

| 50      | G8     | В    | ADIN1    |  |

| 51      | H10    | I    | ADPIIN2  |  |

| 52      | G10    | I    | ADPIIN1  |  |

| 53      | E9     | I    | ADVRL    |  |

| 54      | F9     | I    | ADVRH    |  |

| 55      | F10    | Р    | ADVDD    |  |

| 56      | E10    | Р    | ADVSS    |  |

| 57      | F8     | Р    | DVDD     |  |

| 58      | D10    | Р    | DVSS     |  |

| 59      | E8     | B(O) | PIS1     |  |

| 60      | C10    | B(O) | PIS2     |  |

| 61      | D8     | B(I) | VSYNC1   |  |

| 62      | B10    | B(I) | VSYNC2   |  |

| 63      | C8     | I    | XTALCK   |  |

| 64      | C7     | 0    | XTAL     |  |

# **Electrical Characteristics**

# 1. Logic, Analog

Logic, Analog power: DVDD/DVSS, OPDAVDD/OPDAVSS, ADVDD/ADVSS, these should be connected at the same voltage. They are shown DVDD/DVSS as follows.

1) Absolute Maximum Ratings at DVSS=0V

| Parameter             | Symbol   | Conditions | Ratings          | Unit |

|-----------------------|----------|------------|------------------|------|

| Supply Voltage        | DVDD max | Ta ≤ 25°C  | -0.3 to 4.6      | V    |

| Input/Ouput Voltage   | Vin,Vout | Ta≤25°C    | -0.3 to DVDD+0.3 | V    |

| Storage Temperature   | Tstg     |            | −55 to 125       | °C   |

| Operating Temperature | Topr     |            | -20 to 85        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2) Allowable Operating Range at Ta=-20 to 85°C, DVSS=0V

| Parameter            | Symbol          | Min. | Тур. | Max. | Unit | Applicable pins              |

|----------------------|-----------------|------|------|------|------|------------------------------|

| Power Supply Voltage | DVDD            | 2.7  | 3.3  | 3.6  | V    |                              |

| Input Voltage Range  | V <sub>IN</sub> | 0    | -    | DVDD | V    | Except for OPINM1,<br>OPINM3 |

| Input Voltage Range  | $v_{IN}$        | 0    | -    | VM   | V    | OPINM1, OPINM3               |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

3) D.C Characteristics: Input/Ouput level at Ta=-20 to 85°C, DVSS=0V, DVDD=2.7 to 3.6V

| Parameter                 | Symbol | Conditions                           | Min.     | Тур. | Max.     | Unit | Applicable pins |

|---------------------------|--------|--------------------------------------|----------|------|----------|------|-----------------|

| High-level input voltage  | VIH    | CMOS                                 | 0.7DVDD  |      |          | V    | (2)(2)          |

| Low-level input voltage   | VIL    |                                      |          |      | 0.2DVDD  | V    | (2)(3)          |

| High-level input voltage  | VIH    | CMOS                                 | 0.75DVDD |      |          | V    | (1)             |

| Low-level input voltage   | VIL    | Schmidt                              |          |      | 0.15DVDD | V    | (1)             |

| High-level output voltage | VOH    | IOH=-4mA                             | DVDD-0.4 |      |          | V    | (2)(3)(4)       |

| Low-level output voltage  | VOL    | IOL=4mA                              |          |      | 0.4      | V    | (2)(3)          |

| Low-level output voltage  | VOL    | IOL= 30mA                            |          |      | 0.4      | V    | (4)             |

| PullDown resistance       | Rdn    |                                      | 40       | 80   | 200      | ΚΩ   | (3)             |

| Analog input voltage      | VAI    |                                      | DVSS     |      | DVDD     | V    | (5)             |

| Analog input voltage      | VAI    |                                      | PGND     |      | VM       | V    | (6)             |

| VGA output resistance     | Rout   |                                      |          | 1    |          | ΚΩ   | (7)             |

| Analog output current     | IAO    | CMSDAC<br>=001b &<br>WH_DAV4<br>=00h |          | 1    |          | mA   | (8)             |

# \* Applicable pins

- (1) ZRESET, SSB, SCLK, MOSI

- (2) MISO, BUSY, MON, CLKO1, CLKO2

- (3) VSYNC1, VSYNC2

- (4) PIS1, PIS2

- (5) OPINP6, OPINM6, OPINP7A, OPINM7A, OPINP7B, OPINM7B, ADPIIN1, ADPIIN2

- (6) OPINM1, OPINM3

- (7) ADIN1, ADIN6, ADIN7A, ADIN7B

- (8) BIASO6

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# 2. VM

1) Absolute Maximum Ratings at Ta=25°C, PGND=0V

| Parameter                 | Symbol  | Conditions                                                                      | Ratings     | Unit |

|---------------------------|---------|---------------------------------------------------------------------------------|-------------|------|

| Supply Voltage            | VMmax   |                                                                                 | -0.3 to 7.0 | V    |

| Ouput peak current        | Iopeak1 | OUT1A/B to OUT6A/B<br>t $\leq$ 10ms, On-duty $\leq$ 20%                         | 300         | mA   |

| Ouput peak current        | Iopeak2 | $\begin{array}{c} OUT7A/B \\ t \leq 10ms, On\text{-duty} \leq 20\% \end{array}$ | 450         | mA   |

| Output continuous current | Iomax1  | OUT1A/B to OUT6A/B                                                              | 200         | mA   |

| Output continuous current | Iomax2  | OUT7A/B                                                                         | 300         | mA   |

| Storage Temperature       | Tstg    |                                                                                 | -55 to 125  | °C   |

| Operating Temperature     | Topr    |                                                                                 | -20 to 85   | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

2) Allowable Operating Range at Ta=25°C, PGND=0V

| Item                 | Symbol | Conditions | Ratings    | Unit |

|----------------------|--------|------------|------------|------|

| Power Supply Voltage | VM     |            | 2.7 to 5.5 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

3) Electrical Characteristics at Ta=25°C, PGND=0V, VM=5V

| Parameter             | Symbol | Conditions   | Min. | Тур. | Max. | Unit | Applicable pins |

|-----------------------|--------|--------------|------|------|------|------|-----------------|

| Output ON resistance  | Ronu   | Io=200mA Pch |      | 0.85 |      | Ω    | (0)             |

|                       | Rond   | Io=200mA Nch |      | 0.45 |      | Ω    | (9)             |

| Output ON resistance  | Ronu   | Io=300mA Pch |      | 0.85 |      | Ω    | (10)            |

|                       | Rond   | Io=300mA Nch |      | 0.45 |      | Ω    | (10)            |

| Diode forward voltage | VD     | ID=-200mA    |      | 0.9  |      | V    | (9)             |

| Diode forward voltage | VD     | ID=-300mA    |      | 0.9  |      | V    | (10)            |

<sup>\*</sup> Applicable pins

(9) OUT1A, OUT1B, OUT2A, OUT2B, OUT3A, OUT3B, OUT4A, OUT4B, OUT5A, OUT5B, OUT6A, OUT6B (10) OUT7A, OUT7B

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

# **Example of External Circuit**

Connection example of oscillation circuit

\* In the case of X'tal, it takes about 50 ms for oscillation to stabilize (please check with the manufacturer for a precise time period).

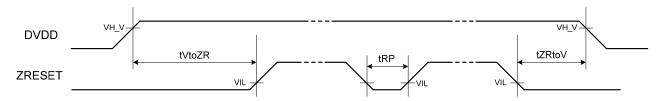

# **AC Characteristics**

# Power supply, Reset pin

# **Specification**

DVDD : DVDD, OPDAVDD, ADVDD

VH\_V : 2.7V VIL : 0.15×DVDD

| Parameter                                            | Symbol | Min. | Тур. | Max. | Unit |

|------------------------------------------------------|--------|------|------|------|------|

| The time from the rise of DVDD to the rise of ZRESET | tVtoZR | 1    |      |      | ms   |

| The time from the fall of DVDD to the fall of ZRESET | tZRtoV | 500  |      |      | μs   |

| Low period of ZRESET                                 | tRP    | 100  |      |      | μs   |

VM can be turn on/off regardless above power supply AC timing.

# ORDERING INFORMATION

| Device        | Package                                | Shipping (Qty / Packing) |  |

|---------------|----------------------------------------|--------------------------|--|

| LC898201TA-NH | TQFP64 7x7<br>(Pb-Free / Halogen Free) | 1000 / Tape & Reel       |  |

| LC898201RA-NH | FBGA64 6x6<br>(Pb-Free / Halogen Free) | 1000 / Tape & Reel       |  |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent reg

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Motor/Motion/Ignition Controllers & Drivers category:

Click to view products by ON Semiconductor manufacturer:

Other Similar products are found below:

LV8133JA-ZH LV8169MUTBG LV8774Q-AH LV8860PV-TLM-H MC33931EKR2 FSB50250UTD FSB50550TB2 FSBF15CH60BTH

FSBS10CH60T MP6507GR-P MP6508GF MSVCPM2-63-12 MSVGW45-14-2 MSVGW54-14-5 NTE7043 CAT3211MUTAG LA6245PCL-TLM-E LA6245P-TLM-E LA6565VR-TLM-E LB11650-E LB1694N-E LB1837M-TLM-E LB1845DAZ-XE LC898111AXB-MH

LC898300XA-MH SS30-TE-L-E STK531-345A-E STK581U3A0D-E STK58AUNPOD-E STK621-068C-E STK621-140C STK621-728S-E

STK625-728-E STK672-400B-E STK672-432AN-E STK672-432BN-E STK672-440AN-E STK672-442AN-E AMIS30621AUA

FSB50550ASE 26700 LV8161MUTAG LV8281VR-TLM-H LV8702V-TLM-H LV8734VZ-TLM-H LV8773Z-E LV8807QA-MH

MC33932EK MCP8024T-H/MP TND027MP-AZ