# **MachXO2 Product Family Qualification Summary**

Lattice Document # 25 – 106923 July 2013

Dear Customer,

Enclosed is Lattice Semiconductor's MachXO2 Product Family Qualification Report.

This report was created to assist you in the decision making process of selecting and using our products. The information contained in this report represents the entire qualification effort for this device family.

The information is drawn from an extensive qualification program of the wafer technology and packaging assembly processes used to manufacture our products. The program adheres to JEDEC and Automotive Industry standards for qualification of the technology and device packaging. This program ensures you only receive product that meets the most demanding requirements for Quality and Reliability.

Your feedback is valuable to Lattice. If you have suggestions to improve this report, or the data included, we encourage you to contact your Lattice representative.

Sincerely,

James M. Orr Vice President.

Corporate Quality & Product Development

Lattice Semiconductor Corporation

# **TABLE OF CONTENTS**

| 1.0 INTRODUCTION                                                                                        | 4     |

|---------------------------------------------------------------------------------------------------------|-------|

| 2.0 LATTICE PRODUCT QUALIFICATION PROGRAM                                                               | 5     |

| Figure 2.0.1 Lattice Standard Product Qualification Process Flow                                        | 6     |

| Table 2.0.2 Standard Qualification Testing                                                              | 8     |

| Table 2.0.3 Industry Standard Qualification Testing for WLCSP Packages                                  |       |

| 3.0 QUALIFICATION DATA MACHXO2 PRODUCT FAMILY                                                           | 10    |

| 3.1 MachXO2 Product Family Life (HTOL) Data                                                             | 11    |

| Table 3.1.1 MachXO2 Product Family Life Results using Pre-Production Wafer Fab Process Development L    | _ots1 |

| Table 3.1.2 MachXO2 Product Family Life Results Run on <b>Production-Process</b> Wafer Fabrication Lots |       |

| 3.2 MachXO2 Product Family High Temperature Retention (HTRX) Data                                       |       |

| 3.3 MachXO2 Product Family Flash Endurance Cycling Data                                                 |       |

| Table 3.3.1 MachXO2 Flash Extended Endurance Results                                                    | 14    |

| 3.4 MACHXO2 PRODUCT FAMILY - ESD AND LATCH UP DATA                                                      |       |

| Table 3.4.1 MachXO2 ESD-HBM Data                                                                        |       |

| Table 3.4.1 MachXO2 ESD-HBM Data (continued)                                                            |       |

| Table 3.4.3 MachXO2 ESD-OM Data                                                                         |       |

| Table 3.4.3 MachXO2 ESD-CDM Data (continued)                                                            | 19    |

| Table 3.4.4 MachXO2 I/O Latch Up >100mA @ HOT (105°C) Data                                              | 20    |

| Table 3.4.5 MachXO2 Vcc Latch Up >1.5X @ HOT (105°C) Data                                               | 21    |

| 4.0 PACKAGE QUALIFICATION DATA FOR MACHXO2 PRODUCT FAMILY                                               | 22    |

| Table 4.0.1 Product-Package Qualification-By-Extension Matrix                                           | 23    |

| 4.1 MachXO2 Product Family Surface Mount Preconditioning Testing                                        |       |

| Table 4.1.1 Surface Mount Precondition Data                                                             |       |

| Table 4.2.1 Temperature Cycling Data                                                                    |       |

| Table 4.3.1 Unbiased HAST Data                                                                          |       |

| Table 4.4.1 Biased HAST Data                                                                            |       |

| Table 4.5.1 MachXO2 High Temperature Storage Life Results                                               |       |

| 5.0 BOARD LEVEL RELIABILITY (BLR) STRESS METHODS                                                        | 29    |

| Table 5.0.1 Slow-Temperature Cycling, IPC-JEDEC9701A & JEDEC JESD22-A104D condition G, soak mod         |       |

| Table 5.0.2 Bend Testing, IPC-JEDEC9702 & JEDEC JESD22-B113A                                            | 30    |

| Table 5.0.3 Drop & Mechanical Shock Testing, IPC-JEDEC9703 & JEDEC JESD22-B111 / JESD-B104C             |       |

| 6.0 MACHXO2 PROCESS RELIABILITY WAFER LEVEL REVIEW                                                      |       |

| Table 6.0.1 Wafer Level Reliability (WLR) Results                                                       | 31    |

| 7.0 MACHXO2 SOFT ERROR RATE DATA                                                                        | 32    |

| Table 7.0.1 MachXO2 MEASURED FITs / Mb                                                                  | 32    |

| 8.0 MACHXO2 ADDITIONAL FAMILY DATA                                                                      | 33    |

| Table 8.0.1 MachXO2 Package Assembly Data – BGA & TQFP                                                  | 33    |

| 9.0 REVISION HISTORY                                                                                    | 34    |

| Table 0.0.1 MachXO2 Product Family Qualification Summany revisions                                      | 34    |

### 1.0 INTRODUCTION

The MachXO2 family of ultra-low power, instant-on, non-volatile PLDs has six devices with densities ranging from 256 to 6864 Look-Up Tables (LUTs). In addition to LUT-based, low-cost programmable logic these devices feature Embedded Block RAM (EBR), Distributed RAM, User Flash Memory (UFM), Phase Locked Loops (PLLs), pre-engineered source synchronous I/O support, advanced configuration support including dual-boot capability and hardened versions of commonly used functions such as SPI controller, I2C controller and timer/counter. These features allow these devices to be used in low cost, high volume consumer and system applications.

The MachXO2 devices are designed on a 65nm non-volatile low power process. The device architecture has several features such as programmable low swing differential I/Os and the ability to turn off I/O banks, on-chip PLLs and oscillators dynamically. These features help manage static and dynamic power consumption resulting in low static power for all members of the family.

The MachXO2 devices are available in three options – ultra low power (ZE) and high performance (HC and HE) devices. The ultra-low power devices are offered in three speed grades -1, -2 and -3, with -3 being the fastest. Similarly, the high-performance devices are offered in three speed grades: -4, -5 and -6, with -6 being the fastest. HC devices have an internal linear voltage regulator which supports external VCC supply voltages of 3.3V or 2.5V. ZE and HE devices only accept 1.2V as the external VCC supply voltage. With the exception of power supply voltage all three types of devices (ZE, HC and HE) are functionally compatible and pin compatible with each other.

The MachXO2 PLDs are available in a broad range of advanced halogen-free packages ranging from the space saving 2.5x2.5 mm WLCSP to the 23x23 mm fpBGA. MachXO2 devices support density migration within the same package.

### 2.0 LATTICE PRODUCT QUALIFICATION PROGRAM

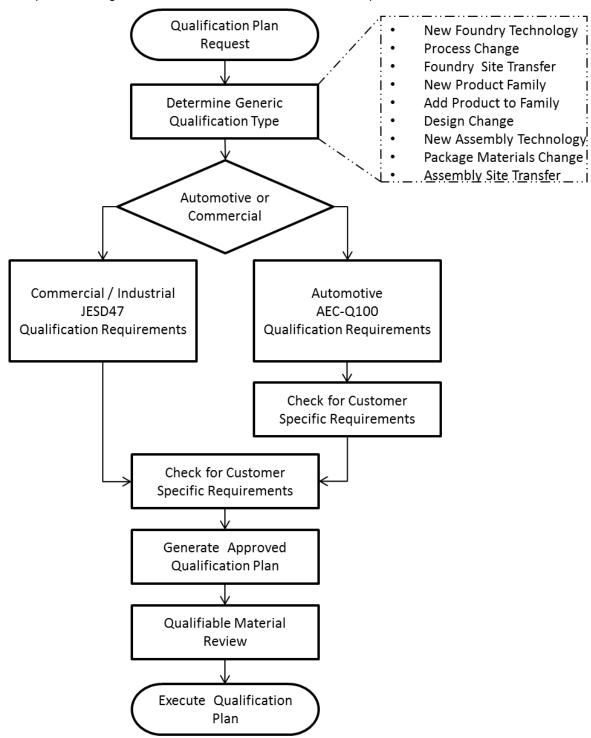

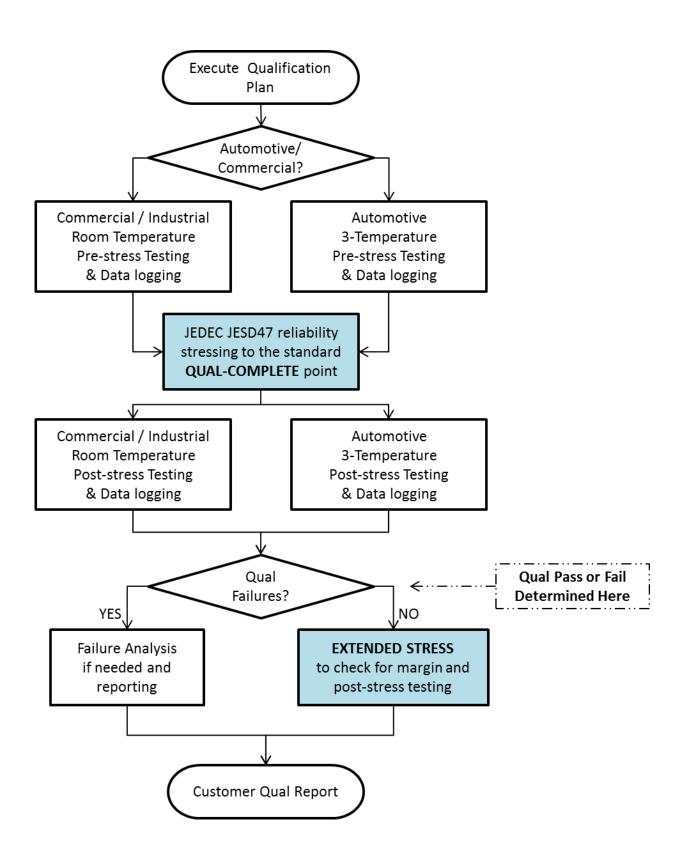

Lattice Semiconductor Corp. maintains a comprehensive reliability qualification program to assure that each product achieves its reliability goals. After initial qualification, the continued high reliability of Lattice products is assured through ongoing monitor programs as described in Lattice Semiconductor's Reliability Monitor Program Procedure (Doc. #70-101667). All product qualification plans are generated in conformance with Lattice Semiconductor's Qualification Procedure (Doc. #70-100164) with failure analysis performed in conformance with Lattice Semiconductor's Failure Analysis Procedure (Doc. #70-100166). Both documents are referenced in Lattice Semiconductor's Quality Assurance Manual, which can be obtained upon request from a Lattice Semiconductor sales office. Figure 2.1 shows the Product Qualification Process Flow.

If failures occur during qualification, an 8D process is used to find root cause and eliminate the failure mode from the design, materials, or process. The effectiveness of any fix or change is validated through additional testing as required. Final testing results are reported in the qualification reports.

Failure rates in this reliability report are expressed in FITs. Due to the very low failure rate of integrated circuits, it is convenient to refer to failures in a population during a period of 10<sup>9</sup> device hours; one failure in 10<sup>9</sup> device hours is defined as one FIT.

Product families are qualified based upon the requirements outlined in Table 2.2. In general, Lattice Semiconductor follows the current Joint Electron Device Engineering Council (JEDEC) and Military Standard testing methods. Lattice automotive products are qualified and characterized to the Automotive Electronics Council (AEC) testing requirements and methods. Product family qualification will include products with a wide range of circuit densities, package types, and package lead counts. Major changes to products, processes, or vendors require additional qualification before implementation.

The MachXO2 family is the third generation FPGA product family and first 65 nm (CS200FL) Flash Technology based product offering. The Lattice Semiconductor MachXO2 FPGA product family qualification efforts are based on the first MachXO2 devices in the family per the Lattice Semiconductor Qualification Procedure, doc#70-100164.

Lattice Semiconductor maintains a regular reliability monitor program. The current Lattice Reliability Monitor Report can be found at <a href="https://www.latticesemi.com/lit/docs/qa/product\_reliability\_monitor.pdf">www.latticesemi.com/lit/docs/qa/product\_reliability\_monitor.pdf</a>.

Figure 2.0.1 Lattice Standard Product Qualification Process Flow

This diagram represents the standard qualification flow used by Lattice to qualify new Product Families. The target end market for the Product Family determines which flow options are used. The MachXO2 Product Family was qualified using the Commercial / Industrial Qualification Option.

Table 2.0.2 Standard Qualification Testing

| TEST                                       | STANDARD                                                                                      | TEST CONDITIONS                                                                                                           | SAMPLE SIZE                                                           | PERFORMED ON                                                                                                                                                 |

|--------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            |                                                                                               |                                                                                                                           | (Typical)                                                             |                                                                                                                                                              |

| High Temperature<br>Operating Life<br>HTOL | Lattice Procedure<br># 87-101943,<br>MIL-STD-883,<br>Method 1005.8,<br>JESD22-A108C           | 125° C,<br>Maximum operating Vcc,<br>168, 500, 1000, 2000<br>hrs.                                                         | 77/lot<br>2-3 lots                                                    | Design, Foundry<br>Process, Package<br>Qualification                                                                                                         |

|                                            | MachXO2                                                                                       |                                                                                                                           |                                                                       |                                                                                                                                                              |

| High Temp<br>Storage Life<br>HTSL          | Lattice Procedure<br># 87-101925,<br>JESD22-A103C                                             | 150° C, at 168, 500,<br>1000, 2000 hours.                                                                                 | 77/lot<br>2-3 lots                                                    | Design, Foundry<br>Process, Package<br>Qualification                                                                                                         |

| ESD HBM                                    | MachXO2 Lattice Procedure # 70-100844, MIL-STD-883, Method 3015.7 JESD22-A114E                | Human Body Model                                                                                                          | 3 parts/lot<br>1-3 lots typical                                       | Design, Foundry<br>Process                                                                                                                                   |

| ESD MM                                     | JESD22-A115C                                                                                  | Machine Model (MM)<br>sweep to 200 volts                                                                                  | 3 parts/lot<br>1-3 lots typical                                       | Design, Foundry<br>Process                                                                                                                                   |

| ESD CDM                                    | Lattice Procedure<br># 70-100844,<br>JESD22-C101D                                             | Charged Device model                                                                                                      | 3 parts/lot<br>1-2 lots typical                                       | Design, Foundry<br>Process                                                                                                                                   |

| Latch Up<br>Resistance<br>LU               | Lattice Procedure<br># 70-101570,<br>JESD78A                                                  | ±100 ma on I/O's,<br>Vcc +50% on Power<br>Supplies. (Max operating<br>temp.)                                              | 6 parts/lot<br>1-2 lots typical                                       | Design, Foundry<br>Process                                                                                                                                   |

| Surface Mount<br>Pre-conditioning<br>SMPC  | Lattice Procedure<br># 70-103467,<br>IPC/JEDEC<br>J-STD-020D.1<br>JESD-A113F<br>MSL 3         | 10 Temp cycles,<br>24 hr 125° C Bake<br>192hr. 30/60 Soak<br>3 SMT simulation cycles                                      | All units going<br>into<br>Temp Cycling,<br>UHAST,<br>BHAST,<br>85/85 | Plastic Packages only                                                                                                                                        |

| Temperature<br>Cycling<br>TC               | Lattice Procedure<br>#70-101568,<br>MIL-STD- 883, Method<br>1010, Condition B<br>JESD22-A104C | (1000 cycles) Repeatedly cycled between -55° C and +125° C in an air environment                                          | 45 parts/lot<br>2-3 lots                                              | Design, Foundry<br>Process, Package<br>Qualification                                                                                                         |

| Power<br>Temperature<br>Cycling<br>PTC     |                                                                                               | (1000 cycles) Repeatedly cycled between -55° C and +125° C in an air environment with asynchronous power on- off cycling. | 45 parts/lot<br>2-3 lots                                              | Design, Foundry Process, Package Qualification. This test is required only for Automotive-qualified devices with maximum rated power > 1 watt or DTJ > 40°C. |

| Unbiased HAST<br>UHAST                     | Lattice Procedure<br># 70-104285<br>JESD22-A118                                               | 2 atm. Pressure,<br>264 hrs, 110 C,<br>85% Relative Humidity                                                              | 45 parts/lot<br>2-3 lots                                              | Foundry Process, Package Qualification Plastic Packages only                                                                                                 |

| TEST                                                                           | STANDARD                                                                                                       | TEST CONDITIONS                                                                                                                                 | SAMPLE SIZE (Typical)                            | PERFORMED ON                                                                  |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|

| Moisture Resistance Temperature Humidity Bias 85/85 THBS  or Biased HAST BHAST | Lattice Procedure<br># 70-101571,<br>JESD22-A101B                                                              | Biased to maximum operating Vcc, 85° C, 85% Relative Humidity, 1000 hours  Or, Biased to maximum operating Vcc, 2atm. Pressure, 264 hrs, 110 C, | 45 devices/lot<br>2-3 lots                       | Design, Foundry<br>Process, Package<br>Qualification<br>Plastic Packages only |

|                                                                                |                                                                                                                | 85% Relative Humidity                                                                                                                           |                                                  |                                                                               |

| Physical<br>Dimensions                                                         | Lattice Procedure<br># 70-100211,<br>MIL-STD- 883 Method<br>2016 or applicable<br>LSC case outline<br>drawings | Measure all dimensions listed on the case outline.                                                                                              | 5 devices                                        | Package Qualification                                                         |

| Ball Shear                                                                     | Lattice Procedure<br># 70-104056<br># 70-100433                                                                | Per Package Type                                                                                                                                | 3 devices per<br>package / 30<br>balls each unit | Package Qualification                                                         |

Table 2.0.3 Industry Standard Qualification Testing for WLCSP Packages

| STRESS TEST                                                        | STANDARD                                      | TEST CONDITIONS                                                                                                            | PASS<br>CONDITION                        | SAMPLE<br>SIZE                | Equipment                                                                                                |

|--------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Surface Mount<br>Preconditioning<br>Pre-BLR test<br>board assembly | JEDEC JESD22-<br>A113F<br>IPC/JEDEC J-STD-020 | 24 hours 125°C bake;<br>followed by 168 hours<br>85C/85%RH moisture soak;<br>plus 1x reflow (260C) onto<br>BLR test boards | Daisy chain<br>continuity,<br>Zero fails | 25 per lot<br>x 3 lots        | Universal Instr. Corp:<br>Vitronics Soltec XPM<br>1030 Solder Reflow<br>(10 heating, 3 cooling<br>zones) |

| Slow-Temperature<br>Cycling                                        | JEDEC JESD22-<br>A104D<br>IPC-JEDEC9701A      | Condition G, soak mode 2<br>(-40C to 125C, 7.5 min soak)<br>1-2 CPH for 3000 cycles                                        | 1000<br>Cycles,<br>Zero fails            | 25 per lot<br>x 3 lots        | Ransco<br>Model# 7102-1                                                                                  |

| Bend Qualification                                                 | JEDEC JESD22-<br>B113A<br>IPC-JEDEC9702       | 200,000 bends of test boards<br>at 1 to 3 Hz with maximum<br>cross-head displacement of 4<br>mm                            | 20,000<br>Bends,<br>Zero fails           | 36 per lot<br>x 3 lots        | Test Resources<br>Model#<br>1210OCCH-1K-B                                                                |

| Drop Qualification<br>Condition B<br>(Handheld apps)               | JEDEC JESD22-B111<br>IPC-JEDEC9703            | 1500g drops<br>0.5 millisecond duration<br>half-sine pulse                                                                 | 30 drops,<br>Zero fails                  | 60 per lot<br>x 3 lots<br>VIP | AVEX Shock Machine<br>Type SM105 Model<br>#MF                                                            |

| Drop Qualification<br>Condition H<br>(Shipping)                    | JEDEC JESD-B104C<br>IPC-JEDEC9703             | 2900g drops<br>0.3 millisecond duration<br>half-sine pulse                                                                 | 30 drops,<br>Zero fails                  | 25                            | AVEX Shock Machine<br>Type SM105 Model<br>#MF                                                            |

### 3.0 QUALIFICATION DATA MACHXO2 PRODUCT FAMILY

The MachXO2 devices are fabricated at Fujitsu on a 65nm non-volatile low power process, then assembled and tested at ASEM in Malaysia, ASET in Kaohsiung, Taiwan, and UTAC/ NEPES in Singapore. The MachXO2 devices are available in three options – ultra low power (ZE) and high performance (HC and HE) devices. The LCMXO2-1200 is the lead qualification vehicle for this product family.

Product Family: MachXO2

Packages offered: TQFP, µcBGA, csBGA, caBGA, ftBGA, fpBGA, QFN and WLCSP

Process Technology Node: 65 nm Flash

### 3.1 MachXO2 Product Family Life (HTOL) Data

#### **High Temperature Operating Life (HTOL) Test**

The High Temperature Operating Life test is used to thermally accelerate those wear out and failure mechanisms that would occur as a result of operating the device continuously in a system application. Consistent with JEDEC JESD22-A108 "Temperature, Bias, and Operating Life", a pattern specifically designed to exercise the maximum amount of circuitry is programmed into the device and this pattern is continuously exercised at specified voltages as described in test conditions for each device type. The Early Life Failure Rate (ELFR) test uses large samples sizes for a short duration (48 Hours) HTOL stress to determine the infant mortality rate of a device family.

#### MachXO2 Life Test (HTOL) Conditions:

**Devices Stressed**: LCMXO2

Pre-conditioning: All Flash cells Program/Erase cycled 10,000 times prior to HTOL stress.

Stress Duration: 48, 168, 500, 1000, 2000 hours.

Stress Conditions: MachXO2 (LCMXO2): HTOL Pattern, Vcc=1.26V, Vccio=3.47V T<sub>JUNCTION</sub> = ≥125°C

Method: Lattice Document #87-101943 and JESD22-A108C

The first 3 wafer lots of ELFR & HTOL stressed were pre-production process development lots.

Table 3.1.1 MachXO2 Product Family Life Results using Pre-Production Wafer Fab Process Development Lots

| Product Name  | Package | Lot #  | Qty  | 48 Hrs<br>Result | 168 Hrs<br>Result | 500 Hrs<br>Result | 1000 Hrs<br>Result | 2000 Hrs<br>Result | Cumulative<br>Hours |

|---------------|---------|--------|------|------------------|-------------------|-------------------|--------------------|--------------------|---------------------|

| LCMXO2-1200ZE | MG132   | Lot #1 | 293* | 1 <sub>A</sub>   | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200HE | MG132   | Lot #1 | 300* | 0                | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200HC | MG132   | Lot #1 | 299* | 0                | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200ZE | MG132   | Lot #2 | 300* | 1 <sub>A</sub>   | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200HE | MG132   | Lot #2 | 300* | 0                | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200HC | MG132   | Lot #2 | 300* | 0                | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200ZE | MG132   | Lot #3 | 300* | 0                | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200HE | MG132   | Lot #3 | 299* | 0                | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200HC | MG132   | Lot #3 | 300* | 0                | N/A               | N/A               | N/A                | N/A                | N/A                 |

| LCMXO2-1200ZE | MG132   | Lot #1 | 58   | N/A              | 0                 | 0                 | 0                  | N/A                | 58,000              |

| LCMXO2-1200HE | MG132   | Lot #1 | 59   | N/A              | 0                 | 0                 | 0                  | N/A                | 59,000              |

| LCMXO2-1200HC | MG132   | Lot #1 | 60   | N/A              | 0                 | 0                 | 0                  | N/A                | 60,000              |

| LCMXO2-1200ZE | TG144   | Lot #1 | 50   | N/A              | 0                 | 0                 | 0                  | N/A                | 50,000              |

| LCMXO2-1200HE | TG144   | Lot #1 | 50   | N/A              | 0                 | 0                 | 0                  | N/A                | 50,000              |

| LCMXO2-1200HC | TG144   | Lot #1 | 47   | N/A              | 0                 | 0                 | O <sub>B</sub>     | N/A                | 47,000              |

| LCMXO2-1200ZE | MG132   | Lot #2 | 60   | N/A              | 0                 | 0                 | 0                  | N/A                | 60,000              |

| LCMXO2-1200HE | MG132   | Lot #2 | 56   | N/A              | 0                 | 0                 | 0                  | N/A                | 56,000              |

| LCMXO2-1200HC | MG132   | Lot #2 | 40   | N/A              | 0                 | 0                 | 0                  | N/A                | 40,000              |

| LCMXO2-1200ZE | TG144   | Lot #2 | 49   | N/A              | 0                 | 0                 | 0                  | 0 <sub>D</sub>     | 98,000              |

| LCMXO2-1200HE | TG144   | Lot #2 | 49   | N/A              | 0                 | 0                 | 0                  | 0                  | 98,000              |

| LCMXO2-1200HC | TG144   | Lot #2 | 47   | N/A              | 0                 | 0                 | 0                  | 0                  | 94,000              |

| Product Name  | Package | Lot #  | Qty | 48 Hrs<br>Result | 168 Hrs<br>Result | 500 Hrs<br>Result | 1000 Hrs<br>Result | 2000 Hrs<br>Result | Cumulative<br>Hours |

|---------------|---------|--------|-----|------------------|-------------------|-------------------|--------------------|--------------------|---------------------|

| LCMXO2-1200ZE | MG132   | Lot #3 | 59  | N/A              | 0                 | 0                 | 0                  | N/A                | 59,000              |

| LCMXO2-1200HE | MG132   | Lot #3 | 60  | N/A              | 0                 | 0                 | 0                  | N/A                | 60,000              |

| LCMXO2-1200HC | MG132   | Lot #3 | 60  | N/A              | 0                 | 0                 | 0                  | N/A                | 60,000              |

| LCMXO2-1200ZE | TG144   | Lot #3 | 50  | N/A              | 0                 | 0                 | 0                  | 0                  | 100,000             |

| LCMXO2-1200HE | TG144   | Lot #3 | 49  | N/A              | 0                 | 0                 | 1 <sub>C</sub>     | 0                  | 98,000              |

| LCMXO2-1200HC | TG144   | Lot #3 | 50  | N/A              | 0                 | 0                 | 0                  | 0                  | 100,000             |

<sup>\*</sup> ELFR units did not receive Flash cell pre-condition cycling prior to stress.

Table 3.1.2 MachXO2 Product Family Life Results Run on Production-Process Wafer Fabrication Lots

| Product Name  | Package | Lot #  | Qty | 48 Hrs<br>Result | 168 Hrs<br>Result | 500 Hrs<br>Result | 1000 Hrs<br>Result | 2000 Hrs<br>Result | Cumulative<br>Hours |

|---------------|---------|--------|-----|------------------|-------------------|-------------------|--------------------|--------------------|---------------------|

| LCMXO2-1200ZE | MG132   | Lot #6 | 60  | N/A              | 0                 | 0                 | 0                  | N/A                | 60,000              |

| LCMXO2-1200HE | MG132   | Lot #6 | 60  | N/A              | 0                 | 0                 | 0                  | N/A                | 60,000              |

| LCMXO2-1200HC | MG132   | Lot #6 | 60  | N/A              | 0                 | 0                 | 0                  | N/A                | 60,000              |

| LCMXO2-1200ZE | TG144   | Lot #6 | 48  | N/A              | 0                 | 0                 | 0                  | N/A                | 48,000              |

| LCMXO2-1200HE | TG144   | Lot #6 | 49  | N/A              | 0                 | 0                 | 0                  | N/A                | 49,000              |

| LCMXO2-1200HC | TG144   | Lot #6 | 50  | N/A              | 0                 | 0                 | 0                  | N/A                | 50,000              |

| LCMXO2-7000ZE | FTG256  | Lot #1 | 40* | N/A              | 0                 | 0                 | 0                  | 0                  | 80,000              |

| LCMXO2-7000HE | FTG256  | Lot #1 | 40* | N/A              | 0                 | 0                 | 0                  | 0                  | 80,000              |

| LCMXO2-7000HC | FTG256  | Lot #1 | 40* | N/A              | 0                 | 0                 | 0                  | 0                  | 80,000              |

| LCMXO2-7000ZE | TG144   | Lot #1 | 50  | N/A              | 0                 | 0                 | 0                  | 0                  | 100,000             |

| LCMXO2-7000HE | TG144   | Lot #1 | 48  | N/A              | 0                 | 0                 | 0                  | 0                  | 96,000              |

| LCMXO2-7000HC | TG144   | Lot #1 | 48  | N/A              | 0                 | 0                 | 0                  | 0                  | 96,000              |

| LCMXO2-7000ZE | FTG256  | Lot #2 | 40* | N/A              | 0                 | 0                 | 0                  | 0                  | 80,000              |

| LCMXO2-7000HE | FTG256  | Lot #2 | 40* | N/A              | 0                 | 0                 | 0                  | 0                  | 80,000              |

| LCMXO2-7000HC | FTG256  | Lot #2 | 40* | N/A              | 0                 | 0                 | 0                  | 0                  | 80,000              |

| LCMXO2-7000ZE | TG144   | Lot #2 | 50  | N/A              | 0                 | 0                 | 0                  | 0                  | 100,000             |

| LCMXO2-7000HE | TG144   | Lot #2 | 48  | N/A              | 0                 | 0                 | 0                  | 0                  | 96,000              |

| LCMXO2-7000HC | TG144   | Lot #2 | 48  | N/A              | 0                 | 0                 | 0                  | 0                  | 96,000              |

<sup>\*</sup> FTG256 packaged units did not receive Flash cell pre-condition cycling prior to stress.

#### MachXO2 Product Family Life Results Run on Production-Process Wafer Fabrication Lots

MachXO2 Cumulative Life Testing Device Hours = 1,391,000 MachXO2 Cumulative Result = 0 failures at 1000 & 2000 hours MachXO2 Long Term Failure Rate = 9 FIT FIT Assumptions: CL=60%, AE=0.7eV, Tjref=55C

MachXO2 ELFR (168Hrs) Cumulative Result / Sample Size = 0 / 859 MachXO2 HTOL (1000 Hrs) Cumulative Result / Sample Size = 0 / 859 MachXO2 HTOL (2000 Hrs) Cumulative Result / Sample Size = 0 / 532

A: Two (2) pre-production ELFR failures due to too-thin ILDO. A pre-production corrective & preventive process change was incorporated and then validated using Flash Extended Endurance, High Temperature Data Retention, and High Temperature Operating Life stresses.

B: FAR#1389: One temperature-sensitive device was a test escape Pre-HTOL stress. Not an HTOL failure. Unit removed from sample size. C: FAR#1390: One working unit at 1k hr failed for flash "readback. Flash verified as good. Intermittent "Read" circuit. Not able to localize.

D: No FAR. One unit mechanically damaged due to handling. No longer able to retest that device. Unit removed from sample size.

### 3.2 MachXO2 Product Family High Temperature Retention (HTRX) Data

#### **High Temperature Data Retention (HTRX)**

The High Temperature Data Retention test measures the Flash cell reliability while the High Temperature Operating Life test is structured to measure functional operating circuitry failure mechanisms. The High Temperature Data Retention test is specifically designed to accelerate charge gain on to or charge loss off of the floating gates in the device's array. Since the charge on these gates determines the actual pattern and function of the device, this test is a measure of the reliability of the device in retaining programmed information. In High Temperature Data Retention, the Flash cell reliability is determined by monitoring the cell margin after biased static operation at 150°C ambient. Flash cells in the arrays are life tested with half the samples programmed with a checkerboard pattern and half with checkerboard-not patterns. Prior to data retention testing all Flash cells are pre-conditioned with 10,000 program/erase cycles.

#### MachXO2 Data Retention (HTRX) Conditions:

Stress Duration: 168, 500, 1000 hours.

Temperature: 150°C ambient

Stress Voltage MachXO2: V<sub>CC</sub>=1.26V/ V<sub>CCIO</sub>=3.47V

Method: Lattice Document #87-101925 and JESD22-A103C / JESD22-A117A

Table 3.2.1 MachXO2 High Temperature Retention Results

| Product Name  | Package | Assembler | Lot #  | Qty | 168 Hrs<br>Result | 500 Hrs<br>Result | 1000 Hrs<br>Result | 1500 Hrs<br>Result | Cumulative<br>Hours |

|---------------|---------|-----------|--------|-----|-------------------|-------------------|--------------------|--------------------|---------------------|

| LCMXO2-1200ZE | MG132   | ASEM      | Lot #3 | 76  | 0                 | 0                 | 0                  | NA                 | 76,000              |

| LCMXO2-1200ZE | MG132   | ASEM      | Lot #4 | 26* | 0                 | 0                 | 0                  | NA                 | 26,000              |

| LCMXO2-1200ZE | MG132   | ASEM      | Lot #4 | 26* | 0                 | 0                 | 0                  | NA                 | 26,000              |

| LCMXO2-1200ZE | MG132   | ASEM      | Lot #4 | 26* | 0                 | 0                 | 0                  | NA                 | 26,000              |

| LCMXO2-1200ZE | MG132   | ASEM      | Lot #5 | 80  | 0                 | 0                 | 0                  | NA                 | 80,000              |

| LCMXO2-1200ZE | MG132   | ASEM      | Lot #6 | 80  | 0                 | 0                 | 0                  | 0                  | 120,000             |

| LCMXO2-1200ZE | MG132   | ASEM      | Lot #6 | 80  | 0                 | 0                 | 0                  | 0                  | 120,000             |

| LCMXO2-7000ZE | TG144   | ASEM      | Lot #1 | 80  | 0                 | 0                 | 0                  | 0                  | 120,000             |

| LCMXO2-7000ZE | TG144   | ASEM      | Lot #2 | 80  | 0                 | 0                 | 0                  | 0                  | 120,000             |

<sup>\*</sup> Qual lot #4 includes tunnel oxide (TOX) process splits: nominal, thick and thin TOX respectively. All passed qual.

Note: A detailed MachXO2 Flash Data Retention report is available upon request. Lattice Semiconductor Corp. document #25-106925.

MachXO2 Cumulative HTRX Failure Rate = 0 / 554 MachXO2 Cumulative HTRX Device Hours = 714,000

### 3.3 MachXO2 Product Family Flash Endurance Cycling Data

Flash Extended Endurance testing measures the durability of the device through programming and erase cycles. Endurance testing consists of repeatedly programming and erasing all cells in the array at 25°C ambient to simulate programming cycles the user would perform. This test evaluates the integrity of the thin tunnel oxide through which current passes to program the floating gate in each cell of the array.

#### MachXO2 Flash Extended Endurance Test Conditions:

Stress Duration: 1K, 10K, 20K, 50K, 100K Cycles

Temperature: 25°C ambient

Stress Voltage MachXO2:  $V_{CC}=1.26V / V_{CCIO}=3.47V$

Method: Lattice Document # 70-104633 and JESD22-A117A

Table 3.3.1 MachXO2 Flash Extended Endurance Results

| Product Name  | Lot #  | Qty | Cycling<br>Temp | 1K<br>CYC | 10K<br>CYC | 20K<br>CYC | 50K<br>CYC | 100K<br>CYC |

|---------------|--------|-----|-----------------|-----------|------------|------------|------------|-------------|

| LCMXO2-1200ZE | Lot #6 | 54  | 25C             | 0         | 0          | 0          | 0          | 0           |

| LCMXO2-7000ZE | Lot #1 | 60  | 25C             | 0         | 0          | 0          | 0          | 0           |

| LCMXO2-7000ZE | Lot #2 | 60  | 25C             | 0         | 0          | 0          | 0          | 0           |

| LCMXO2-256ZE  | Lot #1 | 30  | 25C             | 0         | 0          | 0          | 0          | 0           |

| LCMXO2-256ZE  | Lot #2 | 30  | 25C             | 0         | 0          | 0          | 0          | 0           |

| LCMXO2-640ZE  | Lot #1 | 30  | 25C             | 0         | 0          | 0          | 0          | 0           |

| LCMXO2-2000ZE | Lot #1 | 30  | 25C             | 0         | 0          | 0          | 0          | 0           |

| LCMXO2-4000ZE | Lot #1 | 30  | 25C             | 0         | 0          | 0          | 0          | 0           |

The MachXO2 family uses the exact same Flash cell on all product densities and speed-power versions. The results above includes 8 separate foundry lots of the same flash cell.

### 3.4 MachXO2 Product Family - ESD and Latch UP Data

#### **Electrostatic Discharge-Human Body Model:**

MachXO2 product family was tested per the JESD22-A114E Electrostatic Discharge (ESD) Sensitivity Testing Human Body Lattice Procedure # 70-100844.

All units were Class tested at room ambient prior to reliability stress and after reliability stress. No failures were o classification.

Table 3.4.1 MachXO2 ESD-HBM Data

| Product           | 25-WLCSP<br>(2.5x2.5m,<br>0.4mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184csBGA<br>(8x8mm,<br>0.5 mm<br>pitch) | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch) | 332<br>(17 |

|-------------------|-------------------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|------------|

| LCMXO2-<br>7000ZE |                                           |                                        |                                          |                                         | HBM>2000V<br>Class 2                     |                                         | HBM>2000V<br>Class 2                      | HBM>2000V<br>Class 2                      | НВ         |

| LCMXO2-<br>4000ZE |                                           |                                        |                                          | HBM>2000V<br>Class 2                    | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2<br>by extension    | HBM>2000V<br>Class 2                      | HBM>2000V<br>Class 2                      | HB<br>(    |

| LCMXO2-<br>2000ZE |                                           |                                        | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2                    | HBM>2000V<br>Class 2                     |                                         | HBM>2000V<br>Class 2                      | HBM>2000V<br>Class 2                      |            |

| LCMXO2-<br>1200ZE | HBM>2000V<br>Class 2                      |                                        | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2                    | HBM>2000V<br>Class 2                     |                                         |                                           |                                           |            |

| LCMXO2-<br>640ZE  |                                           |                                        | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2                    |                                          |                                         |                                           |                                           |            |

| LCMXO2-<br>256ZE  |                                           | HBM>2000V<br>Class 2*                  | HBM>2000V<br>Class 2*                    | HBM>2000V<br>Class 2*<br>by extension   |                                          |                                         |                                           |                                           |            |

- The LCMXO2-256ZE HBM is JESD22-A114E Class 2 starting with die code revision B. See Lattice PCN-07A-12 for details.

- Qual-by-Extension HBM uses the smallest package for a given product because the lowest package parasitics have the worst-ca

packages for a given product are qualified by an extension.

- WLCSP HBM performance is the lowest package inductance and exceeds 2000V. This characterization exceeds the JEDEC req specific in a single package.

Table 3.4.1 MachXO2 ESD-HBM Data (continued)

| Product              | 32-QFN<br>(5x5mm,<br>0.5mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch) | 332<br>(17:<br>0 |

|----------------------|--------------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|----------------------------------------|-------------------------------------------|-------------------------------------------|------------------|

| LCMXO2-<br>7000HC/HE |                                      |                                        |                                          |                                         | HBM>2000V<br>Class 2                     |                                        | HBM>2000V<br>Class 2                      | HBM>2000V<br>Class 2                      | HBI<br>C         |

| LCMXO2-<br>4000HC/HE |                                      |                                        |                                          | HBM>2000V<br>Class 2                    | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2<br>by extension   | HBM>2000V<br>Class 2                      | HBM>2000V<br>Class 2                      | HBI<br>C         |

| LCMXO2-<br>2000HC/HE |                                      |                                        | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2                    | HBM>2000V<br>Class 2                     |                                        | HBM>2000V<br>Class 2                      | HBM>2000V<br>Class 2                      |                  |

| LCMXO2-<br>1200HC    |                                      |                                        | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2                    | HBM>2000V<br>Class 2                     |                                        |                                           |                                           |                  |

| LCMXO2-<br>640HC     |                                      |                                        | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2                    |                                          |                                        |                                           |                                           |                  |

| LCMXO2-<br>256HC     | HBM>2000V<br>Class 2                 | HBM>2000V<br>Class 2                   | HBM>2000V<br>Class 2                     | HBM>2000V<br>Class 2                    |                                          |                                        |                                           |                                           |                  |

- HBM classification for Commercial/Industrial products, per JESD22-A114E

- All HBM levels indicated are dual-polarity (±)

- Qual-by-Extension HBM uses the smallest package for a given product because the lowest package parasitics have the worst-ca packages for a given product are qualified by an extension.

### **Electrostatic Discharge-Machine Model:**

MachXO2 product family was tested per the JESD22-A115C Electrostatic Discharge (ESD) Sensitivity Testing, Machine Mod All units were tested at 25°C and +105°C prior to reliability stress and after reliability stress. No failures were observed within

Table 3.4.2 MachXO2 ESD-MM Data

| Product              | 32-QFN<br>(5x5mm,<br>0.5mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch)* | 332<br>(17)<br>0 |

|----------------------|--------------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|--------------------------------------------|------------------|

| LCMXO2-<br>2000HC/HE |                                      |                                        |                                          |                                         |                                          |                                         |                                           | >50V                                       |                  |

| LCMXO2-<br>2000HC/HE |                                      |                                        |                                          |                                         |                                          |                                         |                                           | >100V                                      |                  |

| LCMXO2-<br>2000HC/HE |                                      |                                        |                                          |                                         |                                          |                                         |                                           | >200V                                      |                  |

- All ESD-MM levels indicated are dual-polarity (±) ESD-MM stress level for Commercial/Industrial products, per JESD22-A115C

- ESD-MM stress level was performed at 3 voltages to ensure full coverage

#### **Electrostatic Discharge-Charged Device Model:**

MachXO2 product family was tested per the JESD22-C101D, Field-Induced Charged-Device Model Test Method for Electronic Components procedure and Lattice Procedure # 70-100844.

All units were Class tested at room ambient prior to reliability stress and after reliability stress. No failures were o classification.

Table 3.4.3 MachXO2 ESD-CDM Data

| Product           | 32-QFN<br>(5x5mm,<br>0.5mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch) | 332<br>(17)<br>0 |

|-------------------|--------------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|------------------|

| LCMXO2-<br>7000ZE |                                      |                                        |                                          |                                         | CDM>1kV<br>Class IV                      |                                         | CDM>1kV<br>Class IV                       | CDM>1kV<br>Class IV                       | CD               |

| LCMXO2-<br>4000ZE |                                      |                                        |                                          | CDM>900V<br>Class III                   | CDM>900V<br>Class III                    | CDM>900V<br>Class III<br>by extension   | CDM>900V<br>Class III                     | CDM>1kV<br>Class IV                       | CDI              |

| LCMXO2-<br>2000ZE |                                      |                                        | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     | CDM>1kV<br>Class IV                      |                                         | CDM>1kV<br>Class IV                       | CDM>1kV<br>Class IV                       |                  |

| LCMXO2-<br>1200ZE |                                      |                                        | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     | CDM>1kV<br>Class IV                      |                                         |                                           |                                           |                  |

| LCMXO2-<br>640ZE  |                                      |                                        | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     |                                          |                                         |                                           |                                           |                  |

| LCMXO2-<br>256ZE  |                                      | CDM>1kV<br>Class IV                    | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     |                                          |                                         |                                           |                                           |                  |

- CDM classification for Commercial/Industrial products, per JESD22-C101D

- All CDM levels indicated are dual-polarity (±)

- Qual-by-Extension CDM uses the largest package for a given product because the largest bulk package capacitance has the wor smaller packages for a given product are qualified by an extension.

### Table 3.4.3 MachXO2 ESD-CDM Data (continued)

| Product              | 32-QFN<br>(5x5mm,<br>0.5mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch) | 332<br>(17:<br>0 |

|----------------------|--------------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|------------------|

| LCMXO2-<br>7000HC/HE |                                      |                                        |                                          |                                         | CDM>1kV<br>Class IV                      |                                         | CDM>1kV<br>Class IV                       | CDM>1kV<br>Class IV                       | CD               |

| LCMXO2-<br>4000HC/HE |                                      |                                        |                                          | CDM>800V<br>Class III                   | CDM>800V<br>Class III                    | CDM>800V<br>Class III<br>by extension   | CDM>800V<br>Class III                     | CDM>900V<br>Class III                     | CDI<br>C         |

| LCMXO2-<br>2000HC/HE |                                      |                                        | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     | CDM>1kV<br>Class IV                      |                                         | CDM>1kV<br>Class IV                       | CDM>1kV<br>Class IV                       |                  |

| LCMXO2-<br>1200HC    |                                      |                                        | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     | CDM>1kV<br>Class IV                      |                                         |                                           |                                           |                  |

| LCMXO2-<br>640HC     |                                      |                                        | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     |                                          |                                         |                                           |                                           |                  |

| LCMXO2-<br>256HC     | CDM>1kV<br>Class IV                  | CDM>1kV<br>Class IV                    | CDM>1kV<br>Class IV                      | CDM>1kV<br>Class IV                     |                                          |                                         |                                           |                                           |                  |

- CDM classification for Commercial/Industrial products, per JESD22-C101D All CDM levels indicated are dual-polarity (±)

Qual-by-Extension CDM uses the largest package for a given product because the largest bulk package capacitance has the wor smaller packages for a given product are qualified by an extension.

### Latch-Up:

MachXO2 product family was tested per the JEDEC EIA/JESD78A IC Latch-up Test procedure and Lattice Procedure # 70-1

All units were Class tested at room ambient prior to reliability stress and after reliability stress. No failures were o classification.

Table 3.4.4 MachXO2 I/O Latch Up >100mA @ HOT (105°C) Data

| Product         | 32-QFN<br>(5x5mm,<br>0.5mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184-csBGA<br>(8x8mm,<br>0.5mm<br>pitch)           | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch) | 332-<br>(17x<br>0.<br>p |

|-----------------|--------------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|---------------------------------------------------|-------------------------------------------|-------------------------------------------|-------------------------|

| LCMXO2-<br>7000 |                                      |                                        |                                          |                                         | > +/-100mA<br>Class II<br>Level A        |                                                   | > +/-100mA<br>Class II<br>Level A         | > +/-100mA<br>Class II<br>Level A         | > +/-<br>Cl<br>Le       |

| LCMXO2-<br>4000 |                                      |                                        |                                          | > +/-100mA<br>Class II<br>Level A       | > +/-100mA<br>Class II<br>Level A        | > +/-100mA<br>Class II<br>Level A<br>by extension | > +/-100mA<br>Class II<br>Level A         | > +/-100mA<br>Class II<br>Level A         | > +/-<br>Cl<br>Le       |

| LCMXO2-<br>2000 |                                      |                                        | > +/-100mA<br>Class II<br>Level A        | > +/-100mA<br>Class II<br>Level A       | > +/-100mA<br>Class II<br>Level A        |                                                   | > +/-100mA<br>Class II<br>Level A         | > +/-100mA<br>Class II<br>Level A         |                         |

| LCMXO2-<br>1200 |                                      |                                        | > +/-100mA<br>Class II<br>Level A        | Class II<br>Level A<br>by extension     | > +/-100mA<br>Class II<br>Level A        |                                                   |                                           |                                           |                         |

| LCMXO2-<br>640  |                                      |                                        | > +/-100mA<br>Class II<br>Level A        | > +/-100mA<br>Class II<br>Level A       |                                          |                                                   |                                           |                                           |                         |

| LCMXO2-<br>256  | > +/-100mA<br>Class II<br>Level A    | Class II<br>Level A<br>by extension    | Class II<br>Level A<br>by extension      | > +/-100mA<br>Class II<br>Level A       |                                          |                                                   |                                           |                                           |                         |

- All IO-LU levels indicated are dual-polarity (±)

- Qual-by-Extension Latch Up uses the largest package for a given product because it has access to the most pins. All smaller pac qualified by an extension.

Table 3.4.5 MachXO2 Vcc Latch Up >1.5X @ HOT (105°C) Data

| Product         | 32-QFN<br>(5x5mm,<br>0.5mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch) | 332-<br>(17x<br>0.<br>pi |

|-----------------|--------------------------------------|----------------------------------------|------------------------------------------|-----------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------|

| LCMXO2-<br>7000 |                                      |                                        |                                          |                                         | > 1.5x Vcc<br>Class II                   |                                         | > 1.5x Vcc<br>Class II                    | > 1.5x Vcc<br>Class II                    | > 1.:<br>Cla             |

| LCMXO2-<br>4000 |                                      |                                        |                                          | > 1.5x Vcc<br>Class II                  | > 1.5x Vcc<br>Class II                   | > 1.5x Vcc<br>Class II<br>by extension  | > 1.5x Vcc<br>Class II                    | > 1.5x Vcc<br>Class II                    | > 1.                     |

| LCMXO2-<br>2000 |                                      |                                        | > 1.5x Vcc<br>Class II                   | > 1.5x Vcc<br>Class II                  | > 1.5x Vcc<br>Class II                   |                                         | > 1.5x Vcc<br>Class II                    | > 1.5x Vcc<br>Class II                    |                          |

| LCMXO2-<br>1200 |                                      |                                        | > 1.5x Vcc<br>Class II                   | Class II<br>by<br>extension             | > 1.5x Vcc<br>Class II                   |                                         |                                           |                                           |                          |

| LCMXO2-<br>640  |                                      |                                        | > 1.5x Vcc<br>Class II                   | > 1.5x Vcc<br>Class II                  |                                          |                                         |                                           |                                           |                          |

| LCMXO2-<br>256  | > 1.5x Vcc<br>Class II               | Class II<br>by extension               | Class II<br>by extension                 | > 1.5x Vcc<br>Class II                  |                                          |                                         |                                           |                                           |                          |

Qual-by-Extension Latch Up uses the largest package for a given product because it has access to the most pins. All smaller are qualified by an extension.

### 4.0 PACKAGE QUALIFICATION DATA FOR MACHXO2 PRODUCT FAMILY

The MachXO2 product family is offered in TQFP, uc/cs/ca/ftBGA, fpBGA, QFN and WLCSP packages assembled and tested at ASEM in Malaysia, ASET in Kaohsiung, Taiwan, and UTAC/ NEPES in Singapore. This report details the package qualification results of the initial MachXO2 product introductions. Package qualification tests include Surface Mount Pre-Conditioning (SMPC), Temperature Cycling (T/C), Un-biased HAST (UHAST), Biased HAST (BHAST) and High Temperature Storage (HTSL). Mechanical evaluation tests include Scanning Acoustic Tomography (SAT) and visual package inspection. SMPC is used prior to all other package stresses.

The generation and use of generic data applied across a family of packages emanating from one base assembly process is a Family Qualification, or Qualification by Extension. For the package stresses BHAST, UHAST and HTSL, these are considered generic for a given Package Technology. T/C is considered generic up to an evaluated die size + package size + 10%, for a given Package Technology. Surface Mount Pre-Conditioning (SMPC) is considered generic up to an evaluated Peak Reflow temperature, for a given Package Technology. The following table demonstrates the package stresses qualification matrix.

Table 4.0.1 Product-Package Qualification-By-Extension Matrix

|                                         |                | ASET                                 |                                        |                                          | Adva                                        | nced Semicono                            | luctor Engineer                         | ing, Malaysia (                           | ASEM)                                     |                                            |                                           |

|-----------------------------------------|----------------|--------------------------------------|----------------------------------------|------------------------------------------|---------------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|--------------------------------------------|-------------------------------------------|

| Product-<br>Package<br>Combinati<br>ons | Stress<br>Test | 32-QFN<br>(5x5mm,<br>0.5mm<br>pitch) | 64-ucBGA<br>(4x4mm,<br>0.4mm<br>pitch) | 100-TQFP<br>(14x14mm,<br>0.5mm<br>pitch) | 132-<br>csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 144-TQFP<br>(20x20mm,<br>0.5mm<br>pitch) | 184-csBGA<br>(8x8mm,<br>0.5mm<br>pitch) | 256-caBGA<br>(14x14mm,<br>0.8mm<br>pitch) | 256-ftBGA<br>(17x17mm,<br>1.0mm<br>pitch) | 332-caBGA<br>(17x17mm,<br>0.8mil<br>pitch) | 484-fpBGA<br>(23x23mm,<br>1.0mm<br>pitch) |

|                                         | SMPC           |                                      |                                        |                                          |                                             | MSL3                                     |                                         | 2                                         | 2                                         | MSL3                                       | MSL3                                      |

|                                         | T/C            |                                      |                                        |                                          |                                             | 1K cycles                                |                                         | 2                                         | 2                                         | 1K cycles                                  | 1K cycles                                 |

| LCMXO2-<br>7000                         | BHAST          | Package<br>not offered               | Package<br>not offered                 | Package<br>not offered                   | Package<br>not offered                      | 1                                        | Package<br>not offered                  | 2                                         | 2                                         | 2                                          | 264 hours                                 |

|                                         | UHAST          |                                      |                                        |                                          |                                             | 1                                        |                                         | 2                                         | 2                                         | 2                                          | 264 hours                                 |

|                                         | HTSL           |                                      |                                        |                                          |                                             | 1                                        |                                         | 2                                         | 2                                         | 2                                          | 1K hours                                  |

|                                         | SMPC           |                                      |                                        |                                          | 2                                           | 1                                        | MSL3                                    | 2                                         | 2                                         | 2                                          | 3                                         |

|                                         | T/C            |                                      |                                        |                                          | 2                                           | 1                                        | 1K cycles                               | 2                                         | 2                                         | 2                                          | 3                                         |

| LCMXO2-<br>4000                         | BHAST          | Package<br>not offered               | Package<br>not offered                 | Package<br>not offered                   | 2                                           | 1                                        | 264 hours                               | 2                                         | 2                                         | 2                                          | 3                                         |

|                                         | UHAST          |                                      |                                        |                                          | 2                                           | 1                                        | 2                                       | 2                                         | 2                                         | 2                                          | 3                                         |

|                                         | HTSL           |                                      |                                        |                                          | 2                                           | 1                                        | 1K cycles                               | 2                                         | 2                                         | 2                                          | 3                                         |

|                                         | SMPC           |                                      |                                        | 1                                        | 2                                           | 1                                        |                                         | 2                                         | 2                                         | Package<br>not offered                     |                                           |

|                                         | T/C            |                                      |                                        | 1                                        | 2                                           | 1                                        | Dankana                                 | 2                                         | 2                                         |                                            |                                           |

| LCMXO2-<br>2000                         | BHAST          | Package<br>not offered               | Package<br>not offered                 | 1                                        | 2                                           | 1                                        | Package<br>not offered                  | 2                                         | 2                                         |                                            | Package<br>not offered                    |

|                                         | UHAST          |                                      |                                        | 1                                        | 2                                           | 1                                        |                                         | 2                                         | 2                                         |                                            |                                           |

|                                         | HTSL           |                                      |                                        | 1                                        | 2                                           | 1                                        |                                         | 2                                         | 2                                         |                                            |                                           |

|                                         | SMPC           |                                      |                                        | 1                                        | MSL3                                        | MSL3                                     |                                         |                                           |                                           |                                            |                                           |

|                                         | T/C            |                                      |                                        | 1                                        | 1K cycles                                   | 1K cycles                                |                                         |                                           |                                           |                                            |                                           |

| LCMXO2-<br>1200                         | BHAST          | Package<br>not offered               | Package<br>not offered                 | 1                                        | 264 hours                                   | 264 hours                                | Package<br>not offered                  | Package<br>not offered                    | Package<br>not offered                    | Package<br>not offered                     | Package<br>not offered                    |

|                                         | UHAST          |                                      |                                        | 1                                        | 264 hours                                   | 264 hours                                |                                         |                                           |                                           |                                            |                                           |

|                                         | HTSL           |                                      |                                        | 1                                        | 1K hours                                    | 1K hours                                 |                                         |                                           |                                           |                                            |                                           |

|                                         | SMPC           |                                      |                                        | 1                                        | 2                                           |                                          |                                         |                                           |                                           |                                            |                                           |