## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# H8S/2168Group

## Hardware Manual

Renesas 16-Bit Single-Chip Microcomputer H8S Family / H8S/2100 Series

H8S/2168 HD64F2168 H8S/2167 HD64F2167 H8S/2166 HD64F2166

Rev. 3.00, 03/04, page ii of xl

- party's rights, originating in the use of any product data, diagrams, charts, programs, algorith circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, progra algorithms represents information on products at the time of publication of these materials, a subject to change by Renesas Technology Corp. without notice due to product improvements other reasons. It is therefore recommended that customers contact Renesas Technology Co an authorized Renesas Technology Corp. product distributor for the latest product informatio before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss from these inaccuracies or errors. Please also pay attention to information published by Renesas Technology Corp. by various

including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com

4. When using any or all of the information contained in these materials, including product data. diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a t

system before making a final decision on the applicability of the information and products. R

Technology Corp. assumes no responsibility for any damage, liability or other loss resulting f

contained therein.

information contained herein. 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a designed or manufac system that is used under circumstances in which human life is potentially at stake. Please of Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor v considering the use of a product contained herein for any specific purposes, such as apparat systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce

whole or in part these materials. 7. If these products or technologies are subject to the Japanese export control restrictions, they be exported under a license from the Japanese government and cannot be imported into a control of the control o other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the produ

through current flows internally, and a malfunction may occur.

### 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout chip and a low level is input on the reset pin. During the period where the states a undefined, the register settings and the output state of each pin are also undefined your system so that it does not malfunction because of processing while it is in the

your system so that it does not malfunction because of processing while it is in the undefined state. For those products which have a reset function, reset the LSI impafter the power supply has been turned on.

## 4. Prohibition of Access to Undefined or Reserved Addresses

Notes. Access to an defined an accessed addresses in muchilities

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test reg may have been be allocated to these addresses. Do not access these registers; the operation is not guaranteed if they are accessed.

Rev. 3.00, 03/04, page iv of xl

- The configuration of the functional description of each module differs according module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Exincludes notes in relation to the descriptions given, and usage notes are given, as require final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. Appendix

- 10. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier ve This does not include all of the revised contents. For details, see the actual locations in t manual.

11. Index

Rev. 3.00, 03/04, <sub>I</sub>

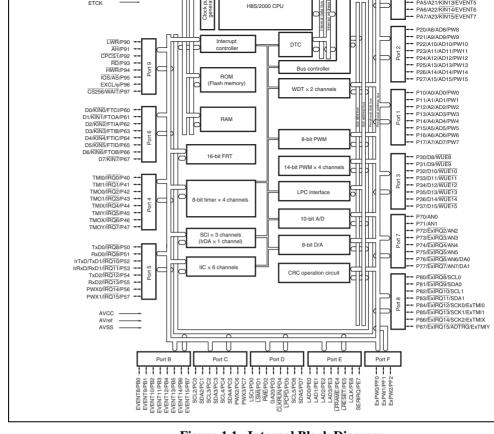

free running timer (FRT), an 8-bit timer (TMR), a watchdog timer (WDT), a serial comm interface (SCI), an I<sup>2</sup>C bus interface (IIC), an LPC interface (LPC), a D/A converter, an A converter, and I/O ports as on-chip peripheral modules required for system configuration

A data transfer controller (DTC) is included as a bus master.

A flash memory (F-ZTAT<sup>TM</sup>\*) version is available for this LSI's 256, 384, and 512-kbyte The CPU and ROM are connected to a 16-bit bus, enabling byte data and word data to be in a single state. This improves the instruction fetch and process speeds.

Two operating modes are provided, offering a choice of address space and single chip mode/external extended mode. Boot programming into a flash memory, on-chip emulation boundary scan can be selected as special operating modes.

Note: \* F-ZTAT<sup>™</sup> is a trademark of Renesas Technology Corp.

Target Users: This manual was written for users who use this LSI in the design of appli systems. Target users are expected to understand the fundamentals of elec-

circuits, logic circuits, and microcomputers.

This manual was written to explain the hardware functions and electrical Objective: characteristics of this LSI to the target users.

Refer to the H8S/2600 Series, H8S/2000 Series Programming Manual for detailed description of the instruction set.

Notes on reading this manual:

• In order to understand the overall functions of the chip Read this manual in the order of the table of contents. This manual can be roughly can

into the descriptions on the CPU, system control functions, peripheral functions and e characteristics.

Rev. 3.00, 03/04, page vi of xl

|                 | Signal notation:   | An overbar is added to a low-                                                               | active signal: xxxx |

|-----------------|--------------------|---------------------------------------------------------------------------------------------|---------------------|

| Related Manuals |                    | ions of all related manuals are av<br>you have the latest versions of all<br>nesas.com/eng/ |                     |

| H8S/2168 Group  | p manuals:         |                                                                                             |                     |

| Document Title  |                    |                                                                                             | Docume              |

| H8S/2168 Group  | Hardware Manual    |                                                                                             | This mar            |

| H8S/2600 Series | s, H8S/2000 Series | Programming Manual                                                                          | ADE-602             |

|                 |                    |                                                                                             |                     |

Number notation:

Binary is B'xxxx, hexadecimal is H'xxxx, decim

| User's manuals for development tools:                                                                    |               |

|----------------------------------------------------------------------------------------------------------|---------------|

| Document Title                                                                                           | Docum         |

| H8S, H8/300 Series C/C++ Compiler, Assembler, Optimizing Linkage E<br>User's Manual                      | Editor ADE-70 |

| H8S, H8/300 Series Simulator/Debugger User's Manual                                                      | ADE-70        |

| H8S, H8/300 Series High-performance Embedded Workshop, High-<br>performance Debugging Interface Tutorial | ADE-70        |

| High-performance Embedded Workshop User's Manual                                                         | ADE-70        |

Rev. 3.00, 03/04, p

Rev. 3.00, 03/04, page viii of xl

|     | 2.1.2   | Differences from 116/300 Cf C                                         |

|-----|---------|-----------------------------------------------------------------------|

|     | 2.1.3   | Differences from H8/300H CPU                                          |

| 2.2 | CPU C   | Operating Modes                                                       |

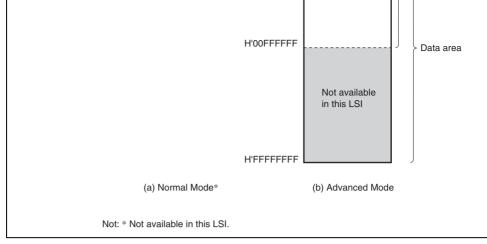

|     | 2.2.1   | Normal Mode                                                           |

|     | 2.2.2   | Advanced Mode                                                         |

| 2.3 | Addre   | ss Space                                                              |

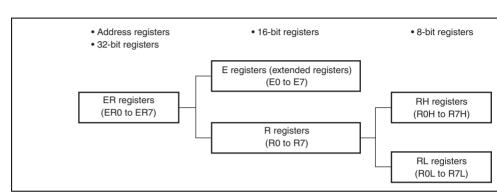

| 2.4 | Regist  | er Configuration                                                      |

|     | 2.4.1   | General Registers                                                     |

|     | 2.4.2   | Program Counter (PC)                                                  |

|     | 2.4.3   | Extended Control Register (EXR)                                       |

|     | 2.4.4   | Condition-Code Register (CCR)                                         |

|     | 2.4.5   | Initial Register Values                                               |

| 2.5 | Data F  | Formats                                                               |

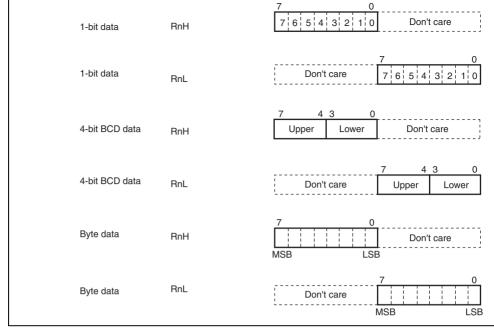

|     | 2.5.1   | General Register Data Formats                                         |

|     | 2.5.2   | Memory Data Formats                                                   |

| 2.6 | Instruc | ction Set                                                             |

|     | 2.6.1   | Table of Instructions Classified by Function                          |

|     | 2.6.2   | Basic Instruction Formats                                             |

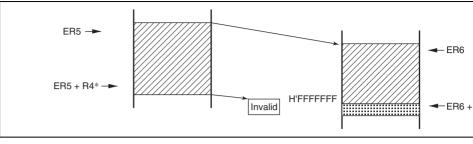

| 2.7 | Addre   | ssing Modes and Effective Address Calculation                         |

|     | 2.7.1   | Register Direct—Rn                                                    |

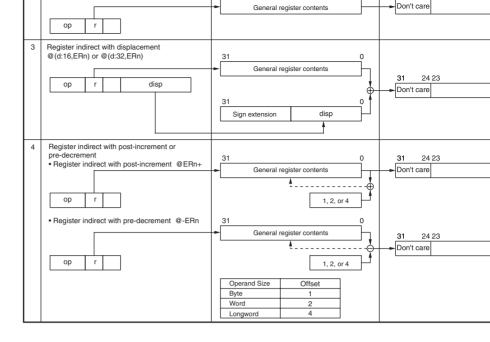

|     | 2.7.2   | Register Indirect—@ERn                                                |

|     | 2.7.3   | Register Indirect with Displacement—@(d:16, ERn) or @(d:32, ERn)      |

|     | 2.7.4   | Register Indirect with Post-Increment or Pre-Decrement—@ERn+ or @-ERn |

|     | 2.7.5   | Absolute Address—@aa:8, @aa:16, @aa:24, or @aa:32                     |

|     | 2.7.6   | Immediate—#xx:8, #xx:16, or #xx:32                                    |

|     | 2.7.7   | Program-Counter Relative—@(d:8, PC) or @(d:16, PC)                    |

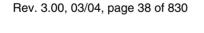

|     | 2.7.8   | Memory Indirect—@@aa:8                                                |

|     |         |                                                                       |

|     |         | Rev. 3.00, 03/04, p                                                   |

|     |         | I(CNC3/13                                                             |

|     |         |                                                                       |

|     |         |                                                                       |

|     |         |                                                                       |

|     |         |                                                                       |

|     |         |                                                                       |

|     |         |                                                                       |

|     |         |                                                                       |

Features.....

Differences between H8S/2600 CPU and H8S/2000 CPU .....

Differences from H8/300 CPU

2.1

2.1.1

2.1.2

|      | 3.3.1 Mode 2                         |                                       |

|------|--------------------------------------|---------------------------------------|

|      | 3.3.2 Pin Functions in Each Opera    | ting Mode                             |

| 3.4  | Address Map                          |                                       |

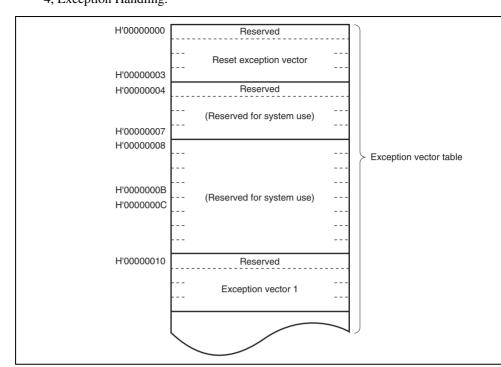

| Sect | ion 4 Exception Handling             |                                       |

| 4.1  |                                      | ity                                   |

| 4.2  |                                      | ector Table                           |

| 4.3  | _                                    |                                       |

|      | 4.3.1 Reset Exception Handling       |                                       |

|      |                                      |                                       |

|      |                                      | s after Reset is Cancelled            |

| 4.4  |                                      |                                       |

| 4.5  |                                      | · · · · · · · · · · · · · · · · · · · |

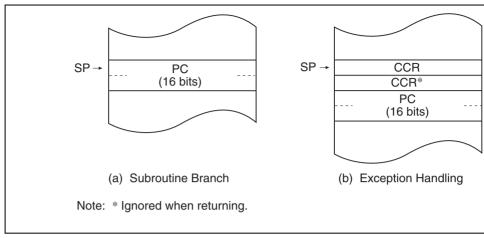

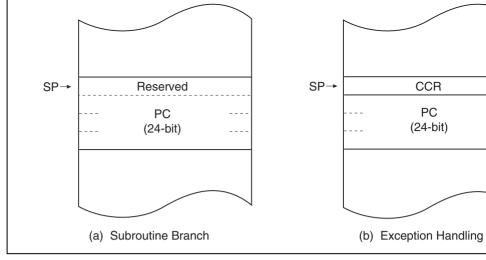

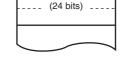

| 4.6  | Stack Status after Exception Handlin | ıg                                    |

| 4.7  | Usage Note                           |                                       |

| ~    |                                      |                                       |

|      | *                                    |                                       |

| 5.1  | Features                             |                                       |

| 5.2  | Input/Output Pins                    |                                       |

| 5.3  | Register Descriptions                |                                       |

|      | 5.3.1 Interrupt Control Registers A  | A to D (ICRA to ICRD)                 |

|      | 5.3.2 Address Break Control Regi     | ster (ABRKCR)                         |

|      | _                                    | o C (BARA to BARC)                    |

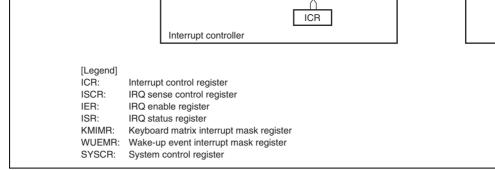

IRQ Sense Control Registers (ISCR16H, ISCR16L, ISCRH, ISCRL)......

Keyboard Matrix Interrupt Mask Registers (KMIMRA, KMIMR6) Wake-

Event Interrupt Mask Register (WUEMR3).....

Interrupt Sources.....

RENESAS

Operating Mode Descriptions

3.3

5.3.4 5.3.5

5.3.6

5.3.7

Rev. 3.00, 03/04, page x of xl

5.4

| ion 6   | Bus Controller (BSC)                                                                        |  |  |

|---------|---------------------------------------------------------------------------------------------|--|--|

|         | es                                                                                          |  |  |

| Input/0 | Input/Output Pins                                                                           |  |  |

|         | er Descriptions                                                                             |  |  |

|         | Bus Control Register (BCR)                                                                  |  |  |

|         | Bus Control Register 2 (BCR2)                                                               |  |  |

|         | Wait State Control Register (WSCR)                                                          |  |  |

| 6.3.4   | Wait State Control Register 2 (WSCR2)                                                       |  |  |

|         | ontrol                                                                                      |  |  |

| 6.4.1   | Bus Specifications                                                                          |  |  |

|         | Advanced Mode                                                                               |  |  |

| 6.4.3   | I/O Select Signals                                                                          |  |  |

|         | Featur<br>Input/0<br>Regist<br>6.3.1<br>6.3.2<br>6.3.3<br>6.3.4<br>Bus Co<br>6.4.1<br>6.4.2 |  |  |

Bus Interface

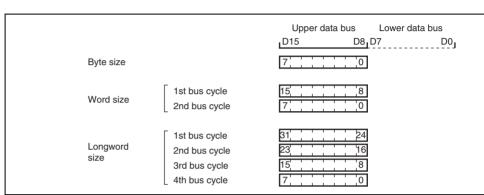

Data Size and Data Alignment.....

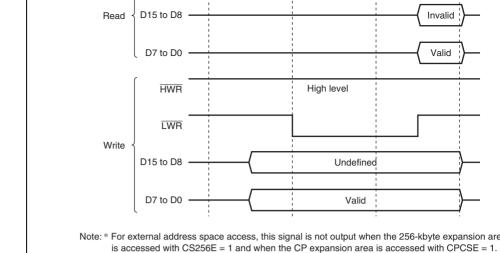

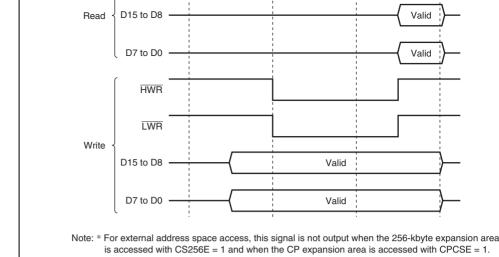

Valid Strobes

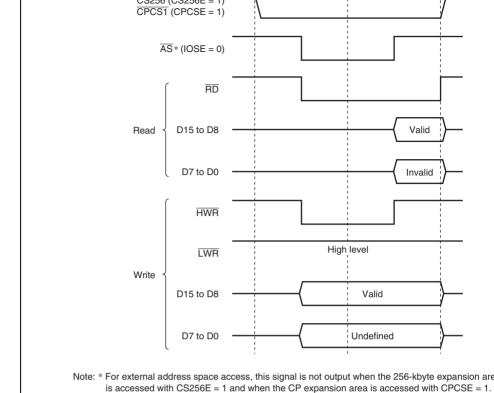

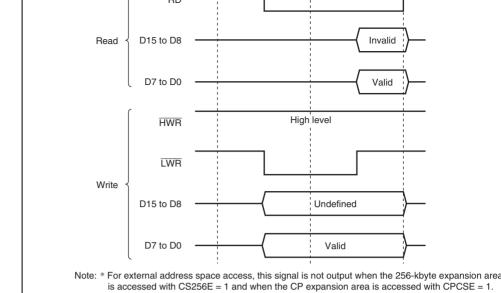

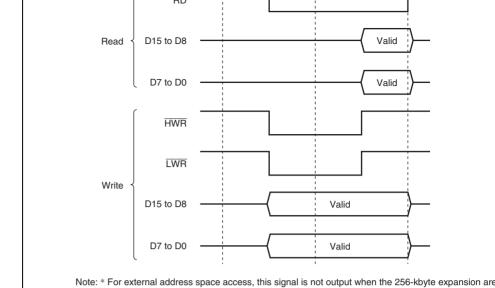

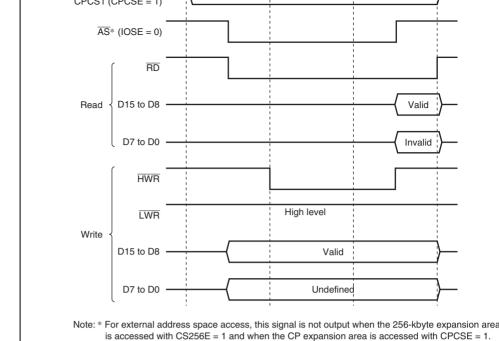

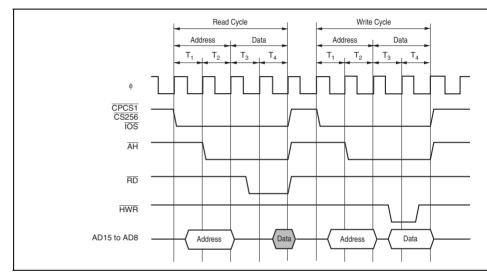

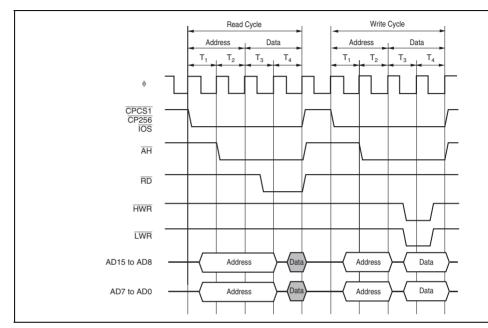

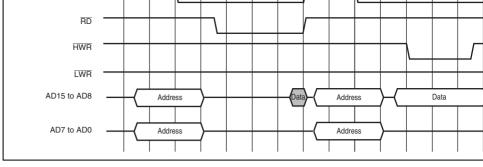

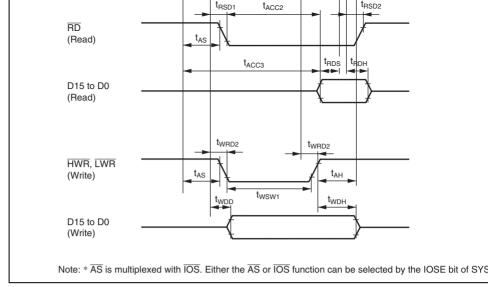

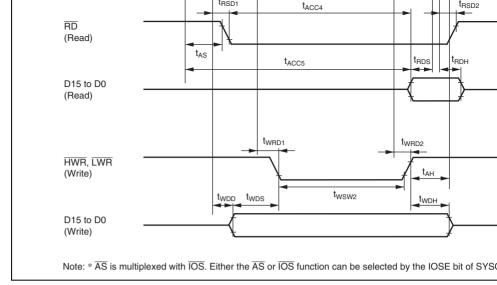

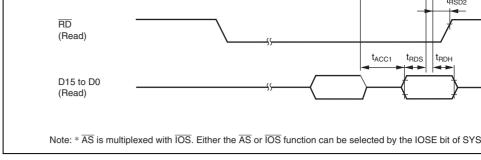

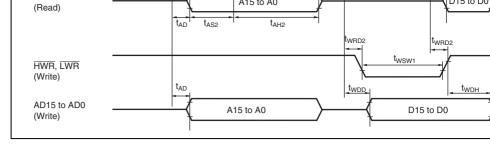

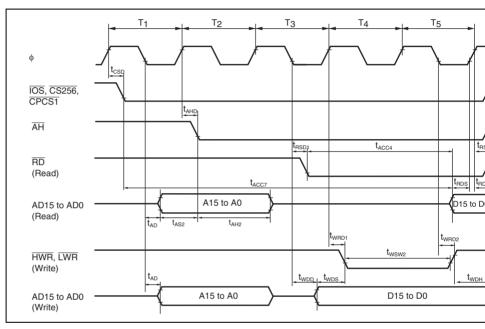

Basic Operation Timing in Normal Extended Mode .....

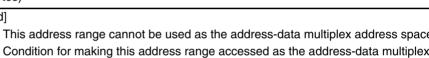

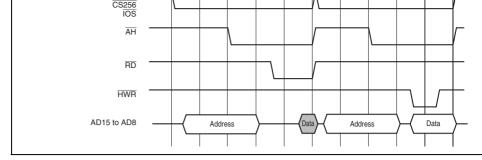

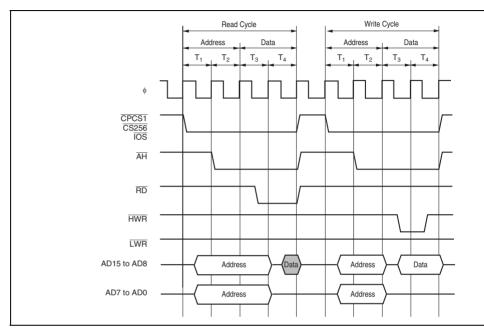

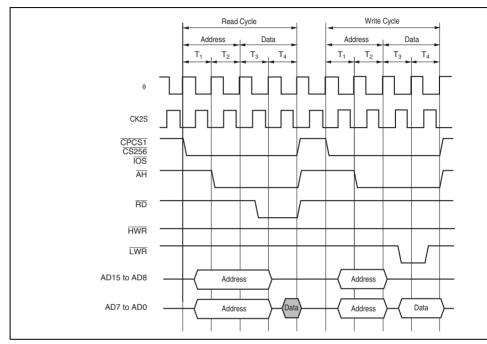

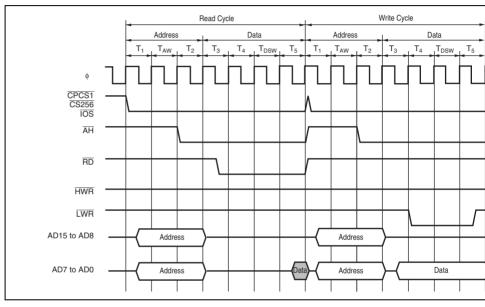

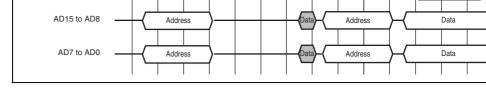

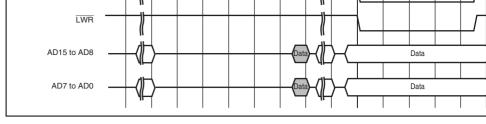

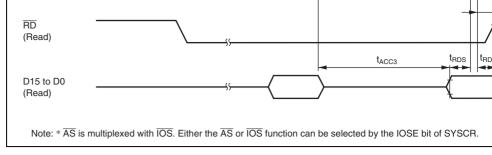

Basic Operation Timing in Address-Data Multiplex Extended Mode ......

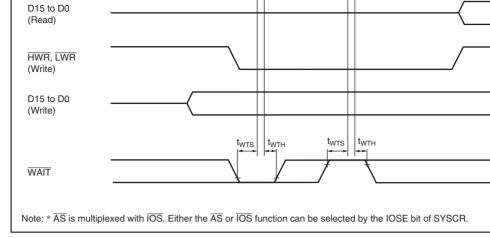

Wait Control

Overview.....

Operation .....

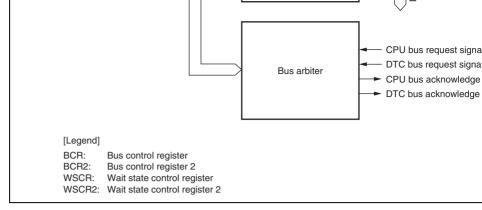

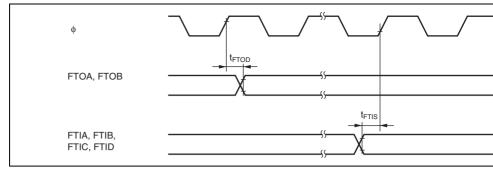

Bus Mastership Transfer Timing .....

IRQ Status Registers (ISR16, ISR).....

6.5

6.7

6.8

6.5.1

6.5.2

6.5.3

6.5.4

6.6.2

6.8.1

6.8.2

6.8.3

Rev. 3.00, 03/04, p

| 1.5 | DICI   | Zvent Counter                                                  |

|-----|--------|----------------------------------------------------------------|

|     | 7.3.1  | Event Counter Handling Priority                                |

|     | 7.3.2  | Usage Notes                                                    |

| 7.4 | Activa | tion Sources                                                   |

| 7.5 | Locati | on of Register Information and DTC Vector Table                |

| 7.6 |        | ion                                                            |

|     | 7.6.1  | Normal Mode                                                    |

|     | 7.6.2  | Repeat Mode                                                    |

|     | 7.6.3  | Block Transfer Mode                                            |

|     | 7.6.4  | Chain Transfer                                                 |

|     | 7.6.5  | Interrupt Sources                                              |

|     | 7.6.6  | Operation Timing                                               |

|     | 7.6.7  | Number of DTC Execution States                                 |

| 7.7 | Proced | lures for Using DTC                                            |

|     | 7.7.1  | Activation by Interrupt                                        |

|     | 7.7.2  | Activation by Software                                         |

| 7.8 | Examr  | oles of Use of the DTC                                         |

|     | 7.8.1  | Normal Mode                                                    |

|     | 7.8.2  | Software Activation                                            |

|     | ,      | OUT 11 MI V 1 IVII 1 MILOII 1111111111111111111111111111111111 |

Usage Notes.....

Module Stop Mode Setting

On-Chip RAM

DTCE Bit Setting.....

Setting Required on Entering Subactive Mode or Watch Mode .....

DTC Activation by Interrupt Sources of SCI, IIC, or A/D Converter .......

7.2.10 Event Counter Control Register (ECCR)..... 7.2.11 Event Counter Status Register (ECS)

Rev. 3.00, 03/04, page xii of xl

DTC Event Counter

73

7.9

7.9.1

7.9.2 7.9.3

7.9.4

7.9.5

| 8.3.2       | Port 3 Data Register (P3DR)                    |

|-------------|------------------------------------------------|

| 8.3.3       | Port 3 Pull-Up MOS Control Register (P3PCR)    |

| 8.3.4       | Pin Functions                                  |

| 8.3.5       | Port 3 Input Pull-Up MOS                       |

| 8.4 Port 4. |                                                |

| 8.4.1       | Port 4 Data Direction Register (P4DDR)         |

| 8.4.2       | Port 4 Data Register (P4DR)                    |

| 8.4.3       | Pin Functions                                  |

| 8.5 Port 5. |                                                |

| 8.5.1       | Port 5 Data Direction Register (P5DDR)         |

| 8.5.2       | Port 5 Data Register (P5DR)                    |

| 8.5.3       | Pin Functions                                  |

| 3.6 Port 6. |                                                |

| 8.6.1       | Port 6 Data Direction Register (P6DDR)         |

| 8.6.2       | Port 6 Data Register (P6DR)                    |

| 8.6.3       | Port 6 Pull-Up MOS Control Register (KMPCR6)   |

| 8.6.4       | System Control Register 2 (SYSCR2)             |

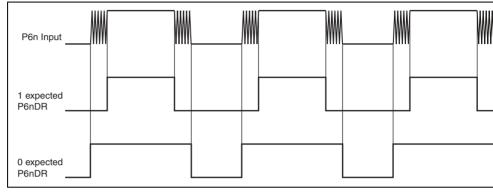

| 8.6.5       | Noise Canceler Enable Register (P6NCE)         |

| 8.6.6       | Noise Canceler Mode Control Register (P6NCMC)  |

| 8.6.7       | Noise Canceler Cycle Setting Register (P6NCCS) |

| 8.6.8       | Pin Functions                                  |

| 8.6.9       | Port 6 Input Pull-Up MOS                       |

|             |                                                |

| 8.7.1       | Port 7 Input Data Register (P7PIN)             |

| 8.7.2       | Pin Functions                                  |

|             |                                                |

| 8.8.1       | Port 8 Data Direction Register (P8DDR)         |

|             | Rev. 3.00, 03/04, p.                           |

|             | RENESAS                                        |

8.2.5

8.3.1

8.3

Port 2 Input Pull-Up MOS .....

Port 3 Data Direction Register (P3DDR).....

Port 3.....

| Port C                                                                         |

|--------------------------------------------------------------------------------|

| 8.12.1 Port C Data Direction Register (PCDDR)                                  |

| 8.12.2 Port C Output Data Register (PCODR)                                     |

| 8.12.3 Port C Input Data Register (PCPIN)                                      |

| 8.12.4 Pin Functions                                                           |

| Port D                                                                         |

| 8.13.1 Port D Data Direction Register (PDDDR)                                  |

| 8.13.2 Port D Output Data Register (PDODR)                                     |

| 8.13.3 Port D Input Data Register (PDPIN)                                      |

| 8.13.4 Pin Functions                                                           |

| 8.13.5 Input Pull-Up MOS                                                       |

| Port E                                                                         |

| 8.14.1 Port E Data Direction Register (PEDDR)                                  |

| 8.14.2 Port E Output Data Register (PEODR)                                     |

| 8.14.3 Port E Input Data Register (PEPIN)                                      |

| 8.14.4 Pin Functions                                                           |

| Port F                                                                         |

| 8.15.1 Port F Data Direction Register (PFDDR)                                  |

| 8.15.2 Port F Output Data Register (PFODR)                                     |

| 8.15.3 Port F Input Data Register (PFPIN)                                      |

| 8.15.4 Pin Functions                                                           |

| Change of Peripheral Function Pins                                             |

| 8.16.1 IRQ Sense Port Select Register 16 (ISSR16), IRQ Sense Port Select Regis |

| (ISSR)                                                                         |

| 8.16.2 Port Control Register 0 (PTCNT0)                                        |

|                                                                                |

| 3.00, 03/04, page xiv of xl                                                    |

|                                                                                |

8.11.1 Port B Data Direction Register (PBDDR)

8.11.2 Port B Output Data Register (PBODR)

8.11.3 Port B Input Data Register (PBPIN)

8.11.4 Pin Functions

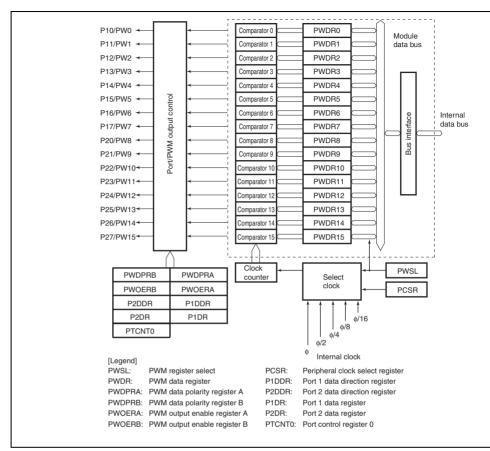

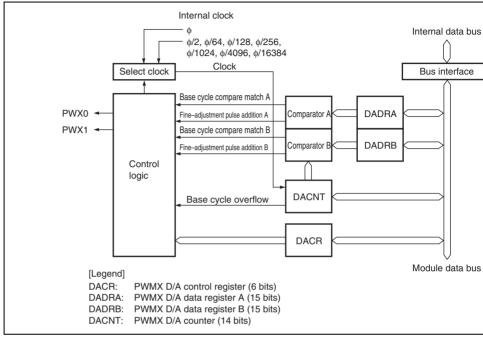

| 10 | 0.2 Input/C | Output Pins                                          |

|----|-------------|------------------------------------------------------|

| 10 | 0.3 Registe | er Descriptions                                      |

|    |             | PWMX (D/A) Counter (DACNT)                           |

|    | 10.3.2      | PWMX (D/A) Data Registers A and B (DADRA and DADRB)  |

|    |             | PWMX (D/A) Control Register (DACR)                   |

|    | 10.3.4      | Peripheral Clock Select Register (PCSR)              |

| 10 | 0.4 Bus M   | aster Interface                                      |

| 10 | 0.5 Operat  | ion                                                  |

|    |             |                                                      |

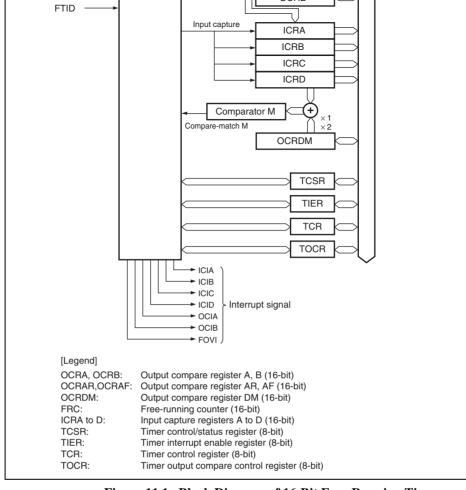

| S  | ection 11   | 16-Bit Free-Running Timer (FRT)                      |

| 11 |             | 28                                                   |

| 11 | -           | Output Pins                                          |

| 11 | _           | er Descriptions                                      |

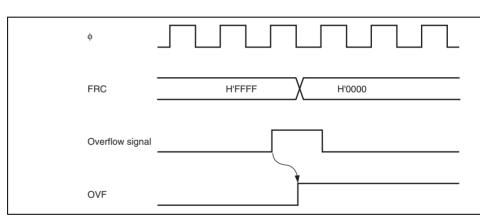

|    |             | Free-Running Counter (FRC)                           |

|    |             | Output Compare Registers A and B (OCRA and OCRB)     |

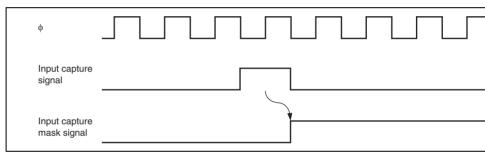

|    |             | Input Capture Registers A to D (ICRA to ICRD)        |

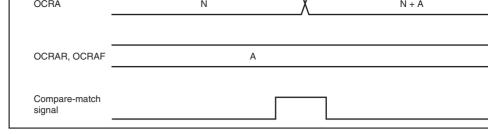

|    |             | Output Compare Registers AR and AF (OCRAR and OCRAF) |

|    |             | Output Compare Register DM (OCRDM)                   |

|    |             | Timer Interrupt Enable Register (TIER)               |

|    |             | Timer Control/Status Register (TCSR)                 |

|    |             | Timer Control Register (TCR)                         |

|    |             | Timer Output Compare Control Register (TOCR)         |

| 11 | -           | ion                                                  |

|    |             | Pulse Output                                         |

| 11 | -           | ion Timing                                           |

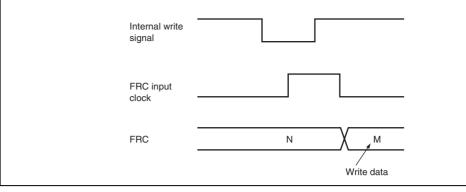

|    |             | FRC Increment Timing                                 |

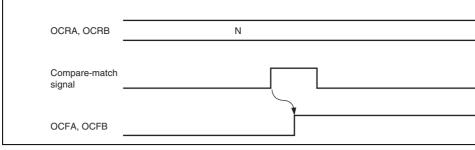

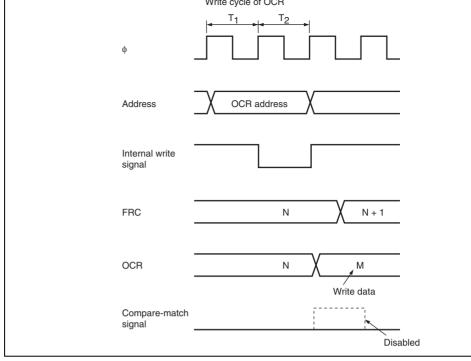

|    |             | Output Compare Output Timing                         |

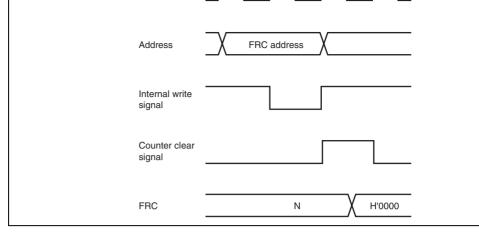

|    | 11.5.3      | FRC Clear Timing                                     |

RENESAS

Rev. 3.00, 03/04, pa

Section 10 14-Bit PWM Timer (PWMX).....

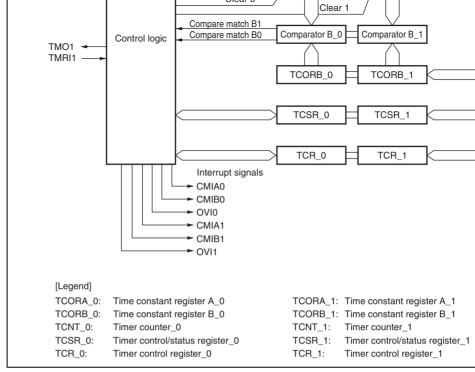

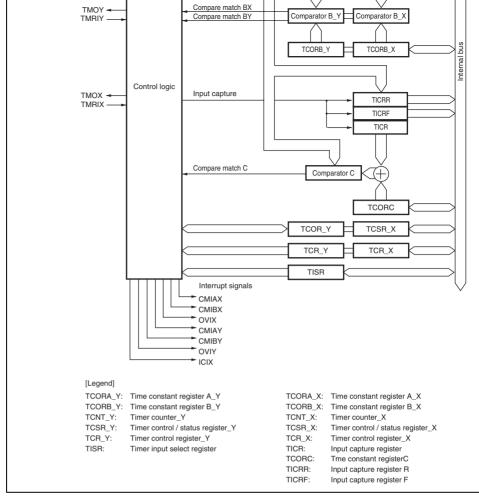

| Secti | ion 12 8-Bit Timer (TMR)                                 |

|-------|----------------------------------------------------------|

| 12.1  | Features                                                 |

| 12.2  |                                                          |

| 12.3  |                                                          |

|       | 12.3.1 Timer Counter (TCNT)                              |

|       | 12.3.2 Time Constant Register A (TCORA)                  |

|       | 12.3.3 Time Constant Register B (TCORB)                  |

|       | 12.3.4 Timer Control Register (TCR)                      |

|       | 12.3.5 Timer Control/Status Register (TCSR)              |

|       | 12.3.6 Input Capture Register (TICR)                     |

|       | 12.3.7 Time Constant Register C (TCORC)                  |

|       | 12.3.8 Input Capture Registers R and F (TICRR and TICRF) |

|       | 12.3.9 Timer Input Select Register (TISR)                |

|       | 12.3.10 Timer Connection Register I (TCONRI)             |

|       | 12.3.11 Timer Connection Register S (TCONRS)             |

| 12.4  | Operation                                                |

Rev. 3.00, 03/04, page xvi of xl

12.5.2 12.5.3

12.5

12.6

RENESAS

Interrupt Sources.....

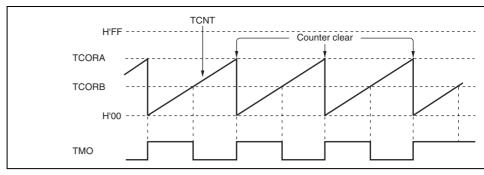

12.4.1 Pulse Output .....

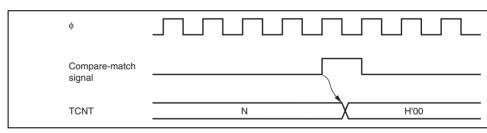

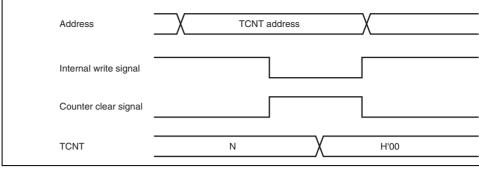

12.5.4 Timing of Counter Clear at Compare-Match

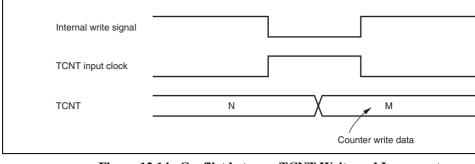

12.5.5 TCNT External Reset Timing

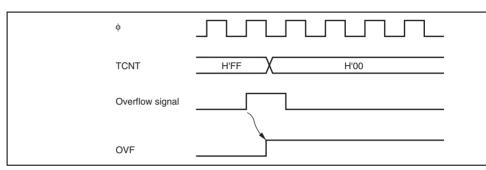

12.5.6 Timing of Overflow Flag (OVF) Setting

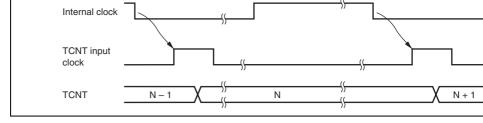

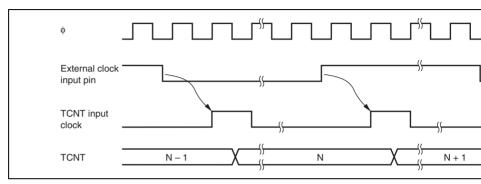

TCNT Count Timing ......

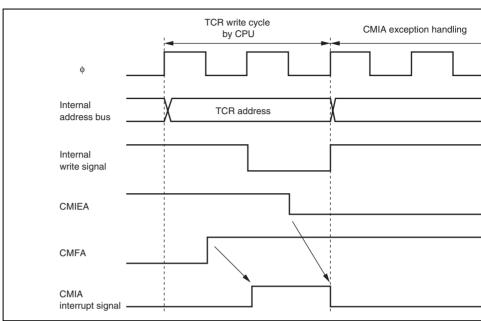

Timing of CMFA and CMFB Setting at Compare-Match ......

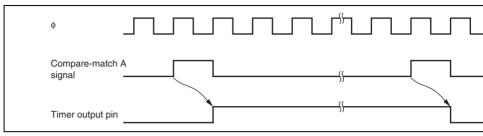

Timing of Timer Output at Compare-Match.....

Operation Timing.....

| 13.4 | Operat  | ion                                                           |   |

|------|---------|---------------------------------------------------------------|---|

|      | 13.4.1  | Watchdog Timer Mode                                           |   |

|      | 13.4.2  | Interval Timer Mode                                           |   |

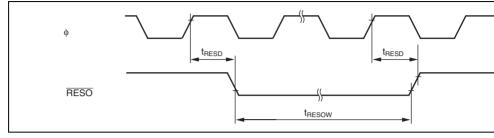

|      | 13.4.3  | RESO Signal Output Timing                                     |   |

| 13.5 | Interru | pt Sources                                                    |   |

| 13.6 |         | Notes                                                         |   |

|      | 13.6.1  | Notes on Register Access                                      |   |

|      | 13.6.2  | Conflict between Timer Counter (TCNT) Write and Increment     |   |

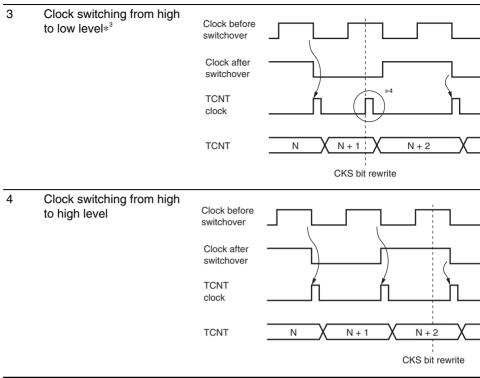

|      | 13.6.3  | Changing Values of CKS2 to CKS0 Bits                          |   |

|      | 13.6.4  | Changing Value of PSS Bit                                     |   |

|      | 13.6.5  | Switching between Watchdog Timer Mode and Interval Timer Mode |   |

|      | 13.6.6  | System Reset by RESO Signal                                   |   |

|      |         |                                                               |   |

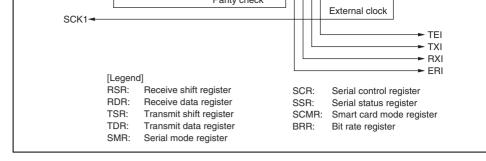

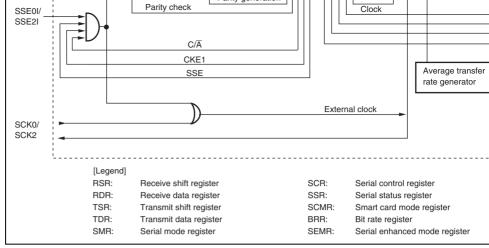

| Sec  | tion 14 | Serial Communication Interface (SCI, IrDA, and CRC)           |   |

| 14.1 | Feature | es                                                            |   |

| 14.2 | Input/C | Output Pins                                                   |   |

| 14.3 | Registe | er Descriptions                                               |   |

|      | 14.3.1  | Receive Shift Register (RSR)                                  |   |

|      | 14.3.2  | Receive Data Register (RDR)                                   |   |

|      | 14.3.3  | Transmit Data Register (TDR)                                  |   |

|      |         | Transmit Shift Register (TSR)                                 |   |

|      | 14.3.5  | Serial Mode Register (SMR)                                    |   |

|      | 14.3.6  | Serial Control Register (SCR)                                 |   |

|      | 14.3.7  | Serial Status Register (SSR)                                  |   |

|      | 14.3.8  | Smart Card Mode Register (SCMR)                               |   |

|      | 14.3.9  | Bit Rate Register (BRR)                                       |   |

|      | 14.3.10 | Serial Interface Control Register (SCICR)                     |   |

|      | 14.3.11 | Serial Enhanced Mode Register_0 and 2 (SEMR_0 and SEMR_2)     |   |

| 14.4 | Operat  | ion in Asynchronous Mode                                      |   |

|      |         | Rev. 3.00, 03/04, p                                           | a |

|      |         | RENESAS                                                       |   |

|      |         |                                                               |   |

|      |         |                                                               |   |

|      |         |                                                               |   |

13.3.2 Timer Control/Status Register (TCSR).....

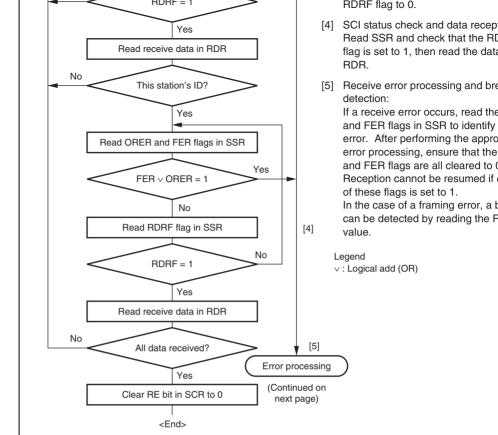

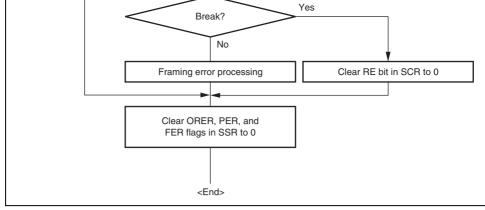

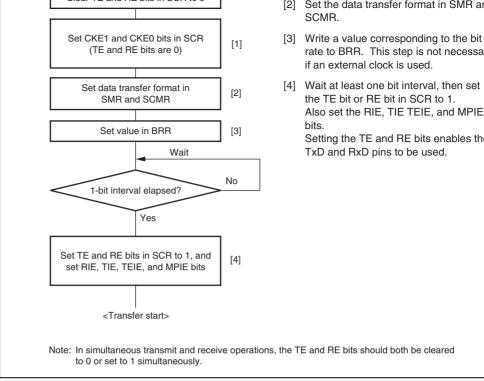

|      | 14.6.2 SCI Initialization (Clock Synchronous Mode)              |

|------|-----------------------------------------------------------------|

|      | 14.6.3 Serial Data Transmission (Clock Synchronous Mode)        |

|      | 14.6.4 Serial Data Reception (Clock Synchronous Mode)           |

|      | 14.6.5 Simultaneous Serial Data Transmission and Reception      |

|      | (Clock Synchronous Mode)                                        |

|      | 14.6.6 SCI Selection in Serial Enhanced Mode                    |

| 14.7 | Smart Card Interface Description                                |

|      | 14.7.1 Sample Connection                                        |

|      | 14.7.2 Data Format (Except in Block Transfer Mode)              |

|      | 14.7.3 Block Transfer Mode                                      |

|      | 14.7.4 Receive Data Sampling Timing and Reception Margin        |

|      | 14.7.5 Initialization                                           |

|      | 14.7.6 Serial Data Transmission (Except in Block Transfer Mode) |

|      | 14.7.7 Serial Data Reception (Except in Block Transfer Mode)    |

|      | 14.7.8 Clock Output Control                                     |

| 14.8 | IrDA Operation                                                  |

| 14.9 | Interrupt Sources                                               |

|      | 14.9.1 Interrupts in Normal Serial Communication Interface Mode |

|      | 14.9.2 Interrupts in Smart Card Interface Mode                  |

| 14.1 | 0 Usage Notes                                                   |

|      | 14.10.1 Module Stop Mode Setting                                |

|      | 14.10.2 Break Detection and Processing                          |

|      | 14.10.3 Mark State and Break Sending                            |

|      | 14.10.4 Receive Error Flags and Transmit Operations             |

|      | (Clock Synchronous Mode Only)                                   |

|      | 14.10.5 Relation between Writing to TDR and TDRE Flag           |

|      | 14.10.6 Restrictions on Using DTC                               |

|      | 14.10.7 SCI Operations during Mode Transitions                  |

|      | 14.10.8 Notes on Switching from SCK Pins to Port Pins           |

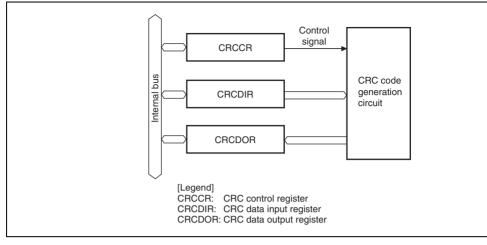

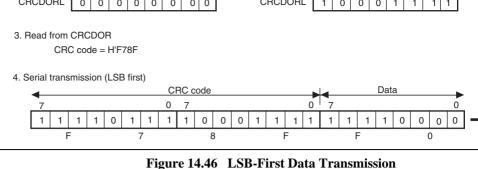

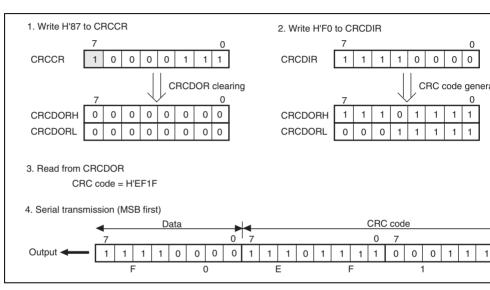

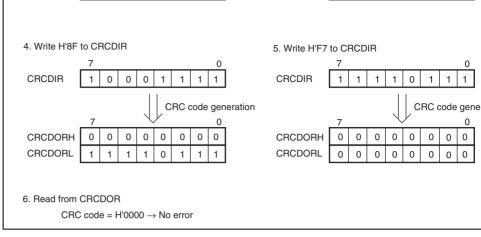

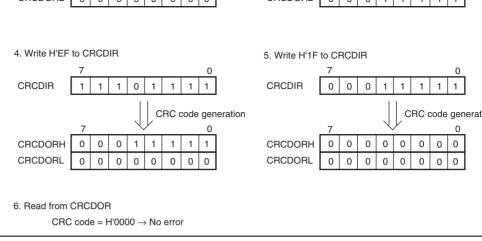

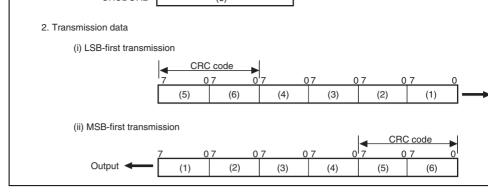

| 14.1 | 1 CRC Operation Circuit                                         |

|      | 3.00. 03/04. page xviii of xl                                   |

|      | 15.3.7  | I <sup>2</sup> C Bus Status Register (ICSR)               |

|------|---------|-----------------------------------------------------------|

|      |         | I <sup>2</sup> C Bus Extended Control Register (ICXR)     |

|      |         | I <sup>2</sup> C SMBus Control Register (ICSMBCR)         |

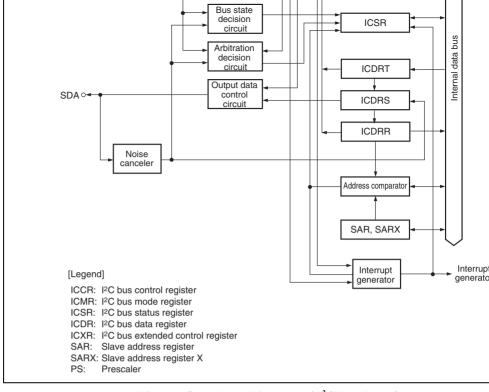

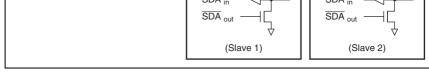

| 15.4 |         | on                                                        |

|      | _       | I <sup>2</sup> C Bus Data Format                          |

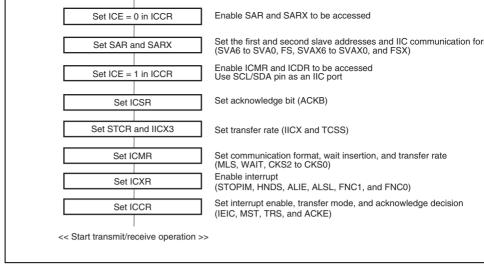

|      |         | Initialization                                            |

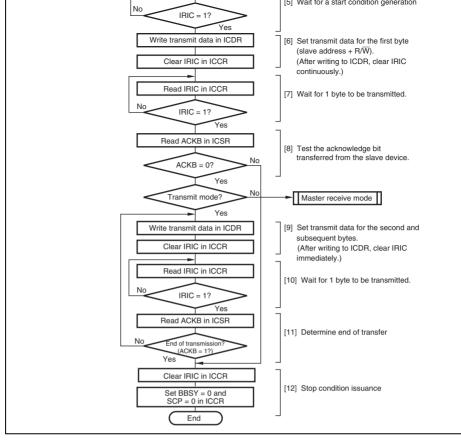

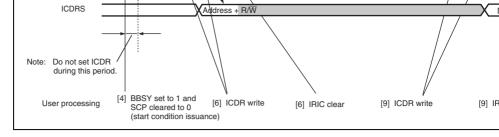

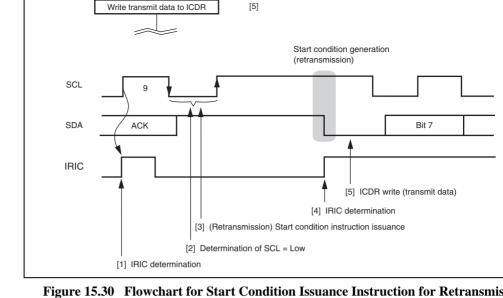

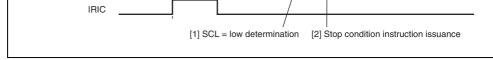

|      |         | Master Transmit Operation                                 |

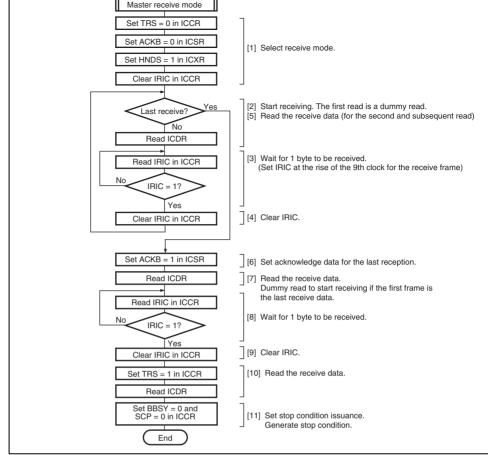

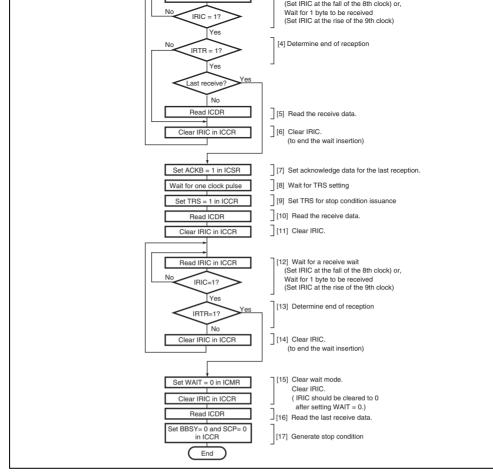

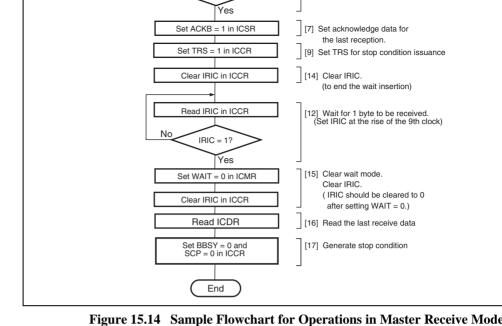

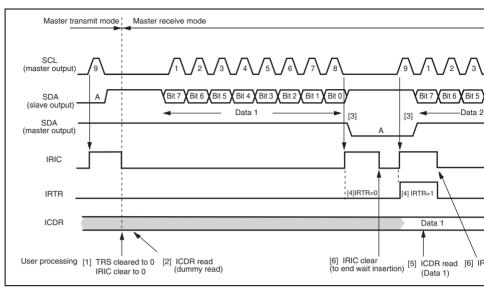

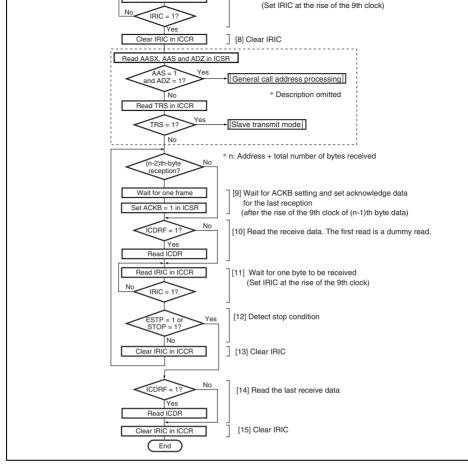

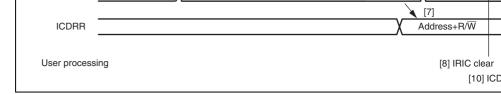

|      |         | Master Receive Operation                                  |

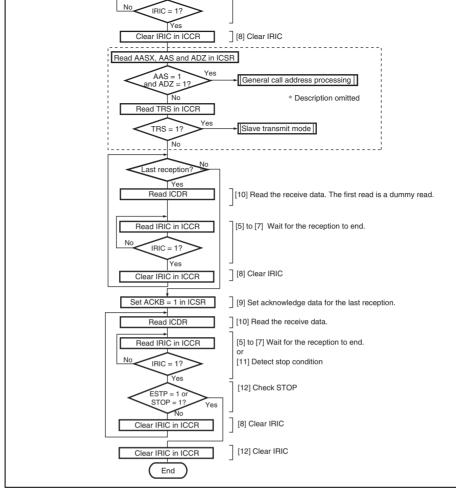

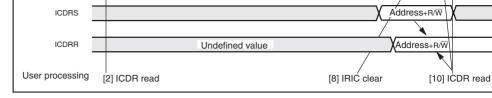

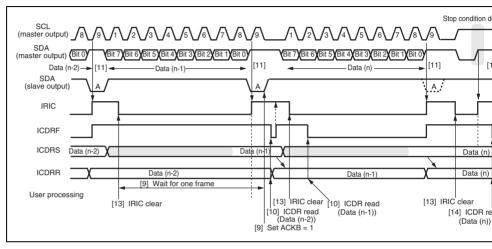

|      |         | Slave Receive Operation                                   |

|      |         | Slave Transmit Operation                                  |

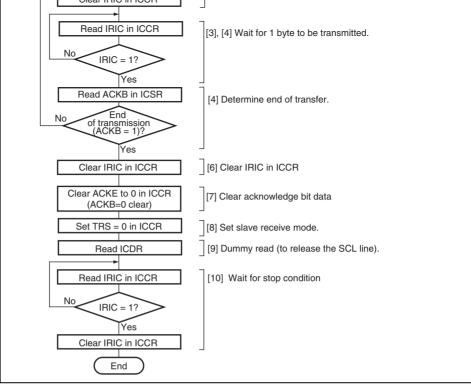

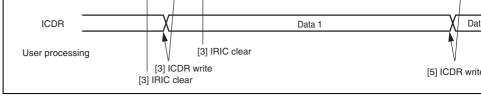

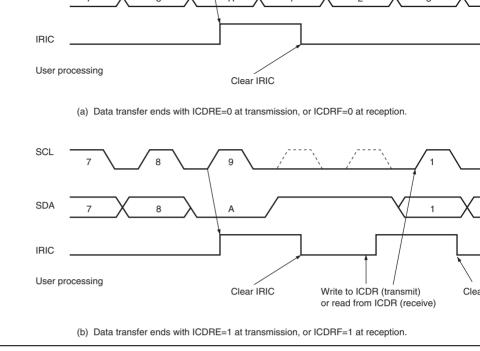

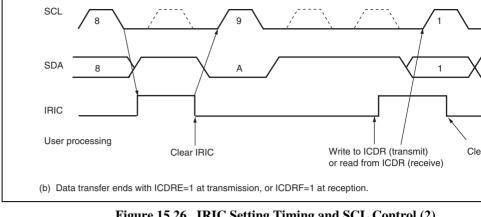

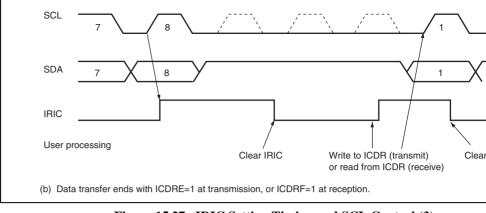

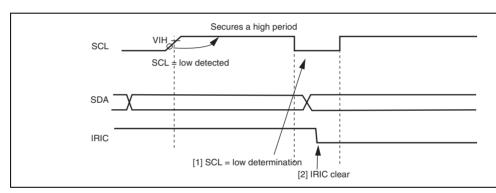

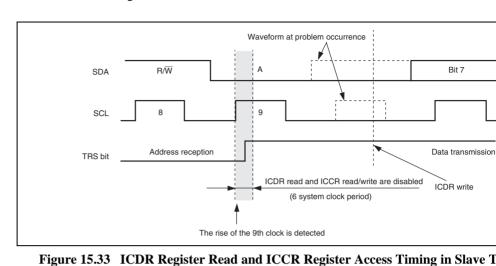

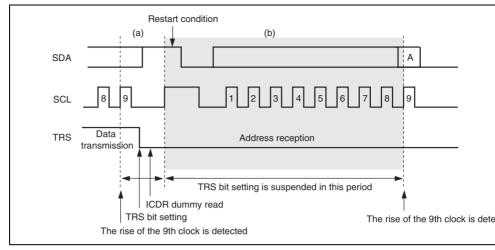

|      |         | IRIC Setting Timing and SCL Control                       |

|      |         | Operation Using the DTC                                   |

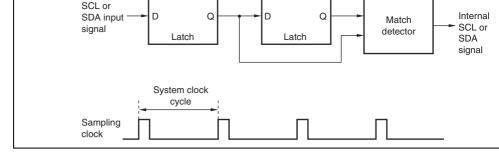

|      |         | Noise Canceler                                            |

|      |         | Initialization of Internal State                          |

| 15.5 |         | t Source                                                  |

| 15.6 | _       | Notes                                                     |

|      | C       |                                                           |

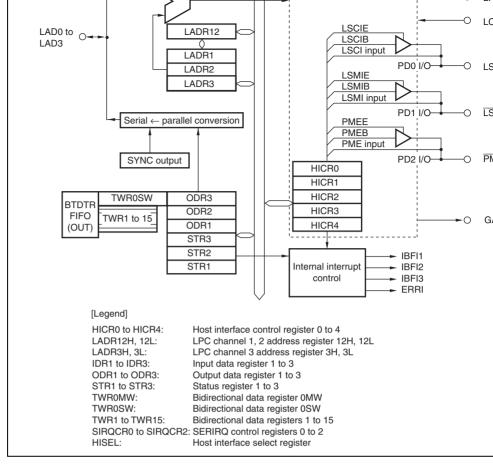

| Sect | ion 16  | LPC Interface (LPC)                                       |

| 16.1 |         | S                                                         |

| 16.2 | Input/O | utput Pins                                                |

| 16.3 | _       | Descriptions                                              |

|      | 16.3.1  | Host Interface Control Registers 0 and 1 (HICR0, HICR1)   |

|      | 16.3.2  | Host Interface Control Registers 2 and 3 (HICR2, HICR3)   |

|      | 16.3.3  | Host Interface Control Register 4 (HICR4)                 |

|      |         | LPC Channel 3 Address Register H, L (LADR3H, LADR3L)      |

|      | 16.3.5  | LPC Channel 1, 2 Address Register H, L (LADR12H, LADR12L) |

|      |         | Input Data Registers 1 to 3 (IDR1 to IDR3)                |

|      |         | Output Data Registers 0 to 3 (ODR1 to ODR3)               |

|      |         | Rev. 3.00, 03/04, pa                                      |

|      |         | RENESAS                                                   |

|      |         | - (-:                                                     |

|        | 16.3.21 BT Control Status Register 0 (BTCSR0)                |

|--------|--------------------------------------------------------------|

|        | 16.3.22 BT Control Status Register 1 (BTCSR1)                |

|        | 16.3.23 BT Control Register (BTCR)                           |

|        | 16.3.24 BT Data Buffer (BTDTR)                               |

|        | 16.3.25 BT Interrupt Mask Register (BTIMSR)                  |

|        | 16.3.26 BT FIFO Valid Size Register 0 (BTFVSR0)              |

|        | 16.3.27 BT FIFO Valid Size Register 1 (BTFVSR1)              |

| 16.4   | Operation                                                    |

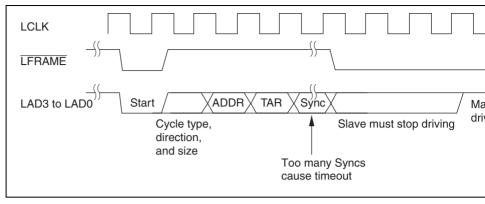

|        | 16.4.1 LPC Interface Activation                              |

|        | 16.4.2 LPC I/O Cycles                                        |

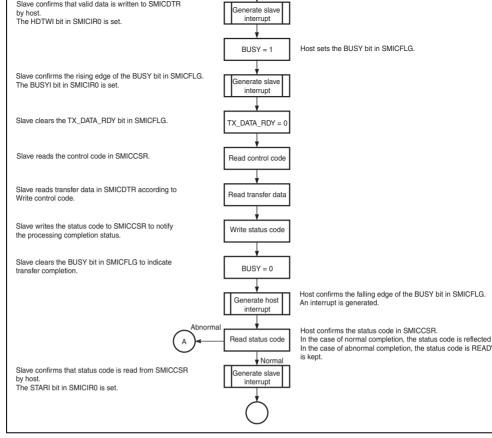

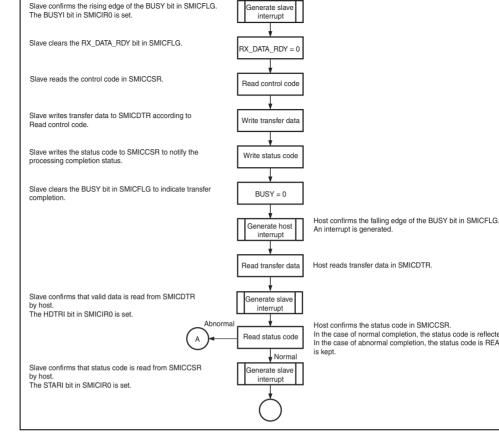

|        | 16.4.3 SMIC Mode Transfer Flow                               |

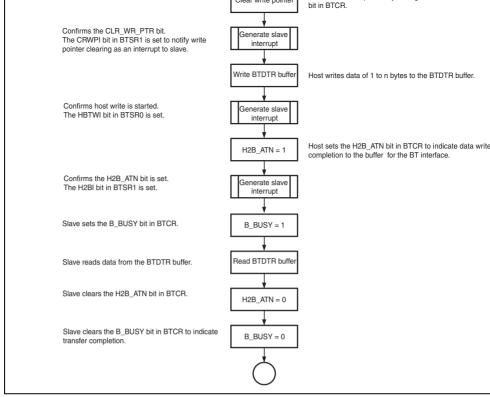

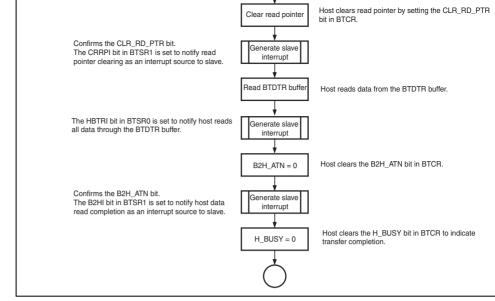

|        | 16.4.4 BT Mode Transfer Flow                                 |

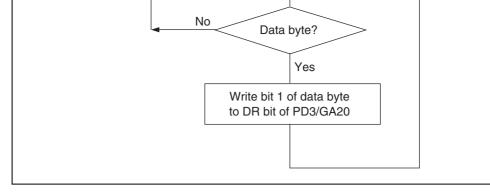

|        | 16.4.5 A20 Gate                                              |

|        | 16.4.6 LPC Interface Shutdown Function (LPCPD)               |

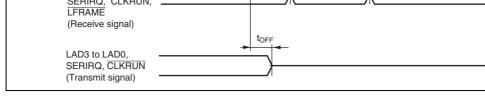

|        | 16.4.7 LPC Interface Serialized Interrupt Operation (SERIRQ) |

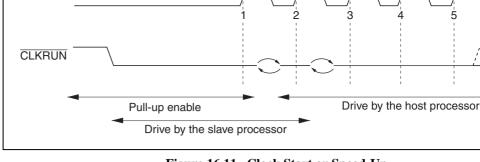

|        | 16.4.8 LPC Interface Clock Start Request                     |

| 16.5   | Interrupt Sources                                            |

|        | 16.5.1 IBFI1, IBFI2, IBFI3, ERRI                             |

|        | 16.5.2 SMI, HIRQ1, HIRQ6, HIRQ9, HIRQ10, HIRQ11, HIRQ12      |

| 16.6   | Usage Notes                                                  |

|        | 16.6.1 Module Stop Setting                                   |

|        | 16.6.2 Usage Note of LPC Interface                           |

|        |                                                              |

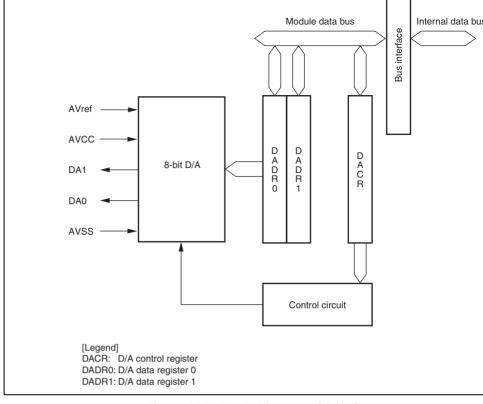

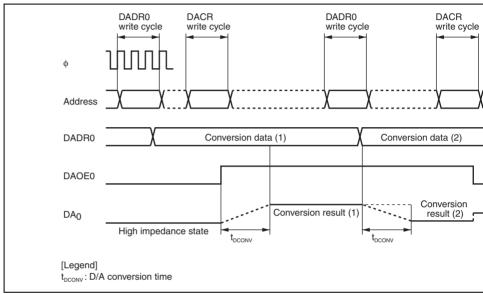

| Secti  | on 17 D/A Converter                                          |

| 17.1   | Features                                                     |

| 17.2   | Input/Output Pins                                            |

| 17.3   | Register Descriptions                                        |

|        | 17.3.1 D/A Data Registers 0 and 1 (DADR0, DADR1)             |

|        | 17.3.2 D/A Control Register (DACR)                           |

| 17.4   | Operation                                                    |

| Rev. 3 | 3.00, 03/04, page xx of xl                                   |

|        | RENESAS                                                      |

|        |                                                              |

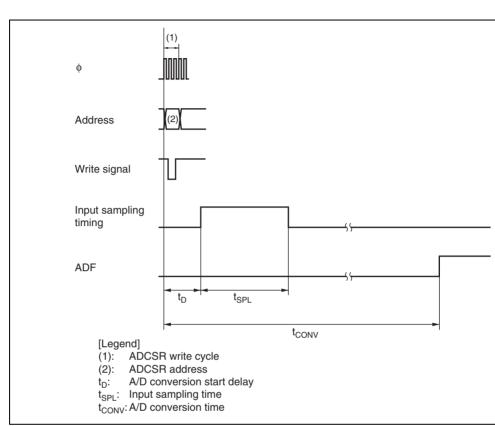

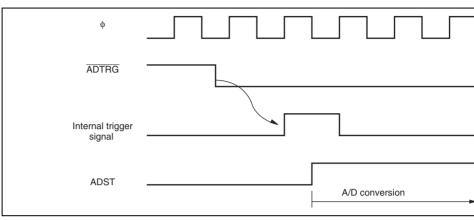

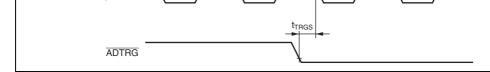

|       | 18.4.4   | External Trigger Input Timing                       |

|-------|----------|-----------------------------------------------------|

| 18.5  | Interrup | ot Source                                           |

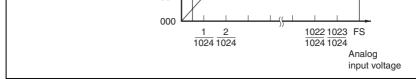

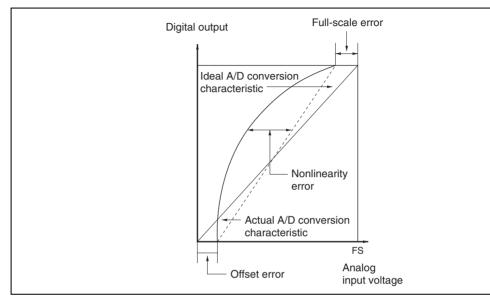

| 18.6  | A/D Co   | onversion Accuracy Definitions                      |

| 18.7  |          | Notes                                               |

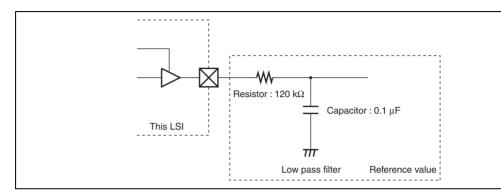

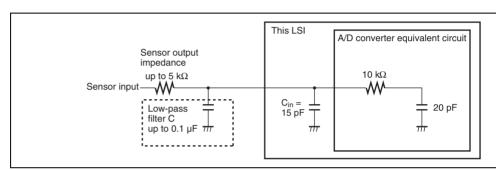

|       |          | Permissible Signal Source Impedance                 |

|       |          | Influences on Absolute Accuracy                     |

|       |          | Setting Range of Analog Power Supply and Other Pins |

|       | 18.7.4   | Notes on Board Design                               |

|       | 18.7.5   | Notes on Noise Countermeasures                      |

|       |          |                                                     |

| Secti | on 19    | RAM                                                 |

|       |          |                                                     |

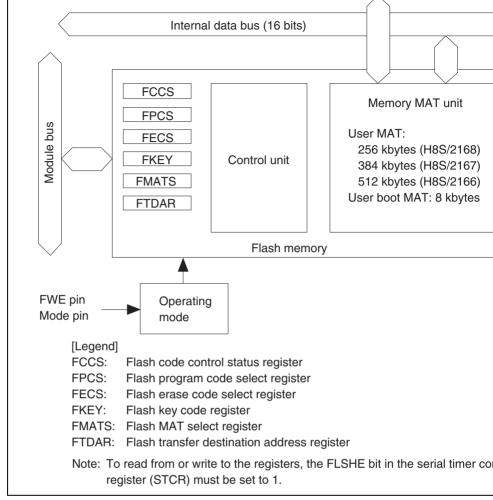

| Secti | on 20    | Flash Memory (0.18-µm F-ZTAT Version)               |

| 20.1  | Feature  | ·s                                                  |

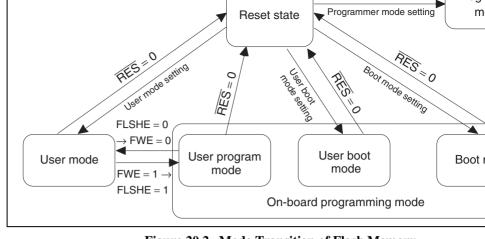

|       | 20.1.1   | Operating Mode                                      |

|       | 20.1.2   | Mode Comparison.                                    |

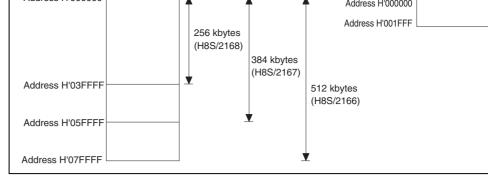

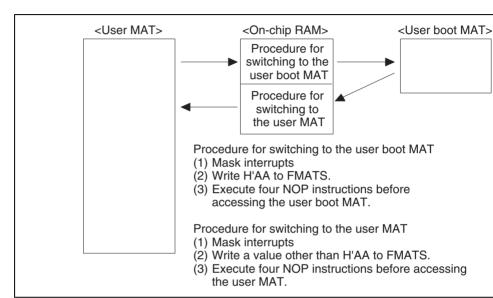

|       | 20.1.3   | Flash Memory MAT Configuration                      |

|       | 20.1.4   | Block Division                                      |

|       | 20.1.5   | Programming/Erasing Interface                       |

| 20.2  | Input/C  | Output Pins                                         |

| 20.3  | Registe  | r Descriptions                                      |

|       | 20.3.1   | Programming/Erasing Interface Register              |

|       | 20.3.2   | Programming/Erasing Interface Parameter             |

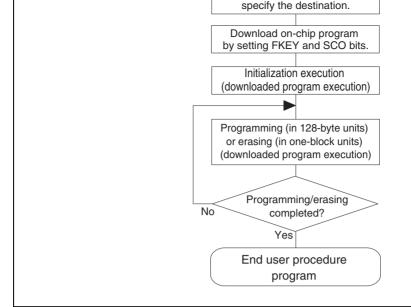

| 20.4  | On-Boa   | ard Programming Mode                                |

|       | 20.4.1   | Boot Mode                                           |

|       | 20.4.2   | User Program Mode                                   |

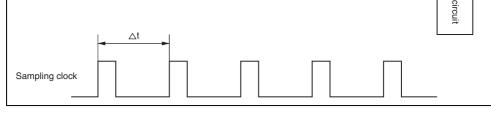

18.4.3 Input Sampling and A/D Conversion Time .....

RENESAS

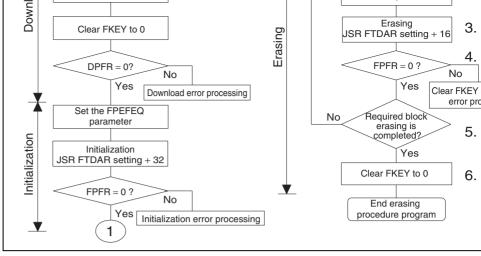

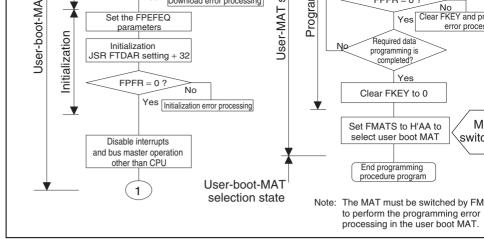

20.4.3 User Boot Mode....

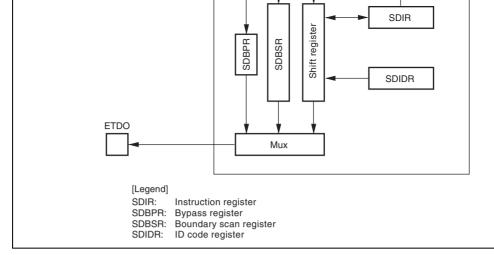

|      | 21.3.4 ID Code Register (SDIDR)         |

|------|-----------------------------------------|

| 21.4 | Operation                               |

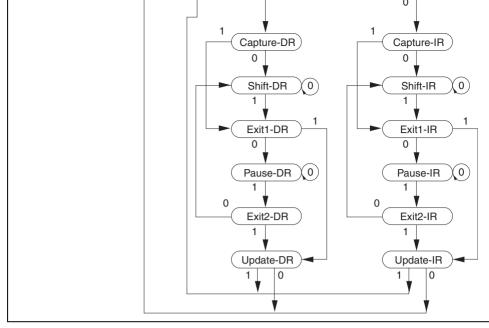

|      | 21.4.1 TAP Controller State Transitions |

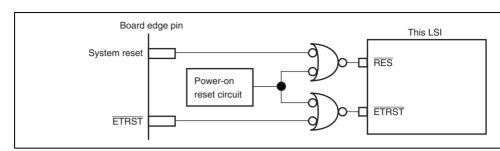

|      | 21.4.2 JTAG Reset                       |

| 21.5 | Boundary Scan                           |

|      | 21.5.1 Supported Instructions           |

| 21.6 | Usage Notes                             |

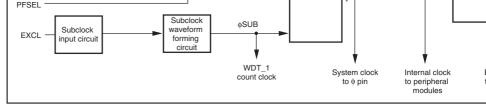

| Sect | ion 22 Clock Pulse Generator            |

|      | Oscillator                              |

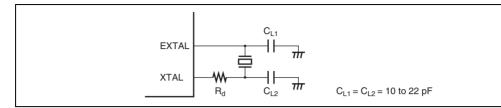

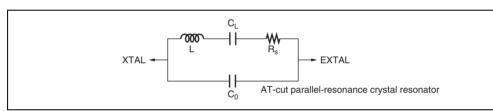

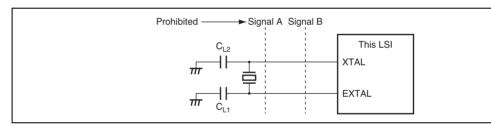

|      | 22.1.1 Connecting Crystal Resonator     |

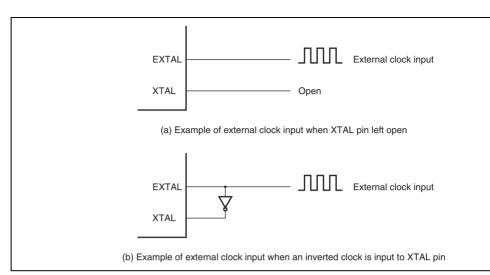

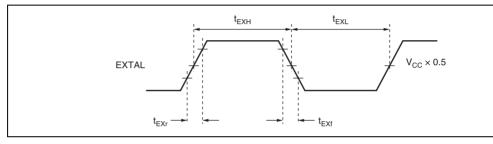

|      | 22.1.2 External Clock Input Method      |

| 22.2 | _                                       |

| 22.3 | Medium-Speed Clock Divider              |

| 22.4 | Bus Master Clock Select Circuit         |

| 22.5 | Subclock Input Circuit                  |

| 22.6 | Subclock Waveform Forming Circuit       |

| 22.7 | Clock Select Circuit                    |

| 22.8 | Usage Notes                             |

|      | 22.8.1 Note on Resonator                |

|      | 22.8.2 Notes on Board Design            |

|      | 22.8.3 Note on Operation Check          |

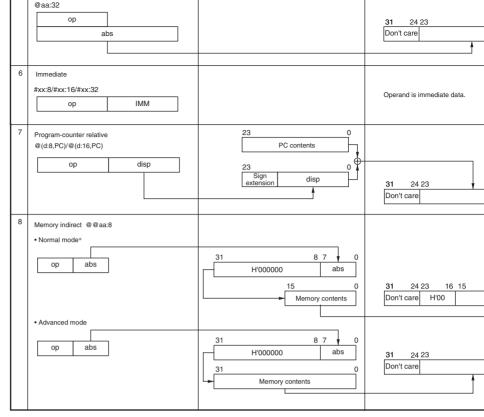

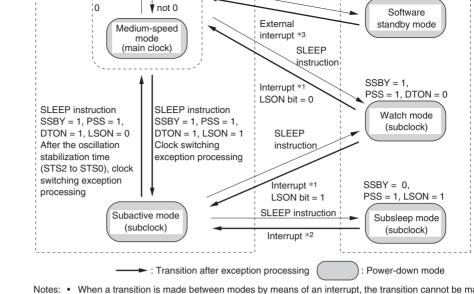

| Sect | ion 23 Power-Down Modes                 |

|      | Register Descriptions                   |

|      |                                         |

Rev. 3.00, 03/04, page xxii of xl

23.1.1 Standby Control Register (SBYCR)23.1.2 Low-Power Control Register (LPWRCR)

| 23.11 | Direct Transitions                                                |

|-------|-------------------------------------------------------------------|

| 23.12 | Usage Notes                                                       |

|       | 23.12.1 I/O Port Status                                           |

|       | 23.12.2 Current Consumption when Waiting for Oscillation Settling |

|       | 23.12.3 DTC Module Stop Mode                                      |

|       | 23.12.4 Notes on Subclock Usage                                   |

|       |                                                                   |

| Sect  | ion 24 List of Registers                                          |

|       | Register Addresses (Address Order)                                |

|       | Register Bits                                                     |

|       | Register States in Each Operating Mode                            |

| Cast  | ion 25 Electrical Characteristics                                 |

|       | ion 25 Electrical Characteristics                                 |

|       | Absolute Maximum Ratings                                          |

| 25.2  | DC Characteristics                                                |

| 25.3  | AC Characteristics                                                |

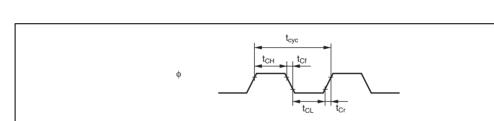

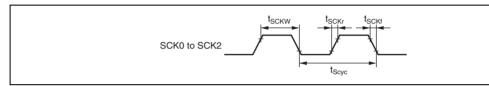

|       | 25.3.1 Clock Timing                                               |

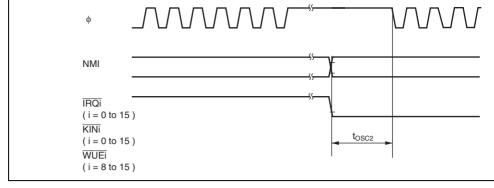

|       | 25.3.2 Control Signal Timing                                      |

|       | 25.3.3 Bus Timing                                                 |

Rev. 3.00, 03/04, page xxiv of xl

| Figure 2.7  | Usage of General Registers                                      |

|-------------|-----------------------------------------------------------------|

| Figure 2.8  | Stack                                                           |

| Figure 2.9  | General Register Data Formats (1)                               |

| Figure 2.9  | General Register Data Formats (2)                               |

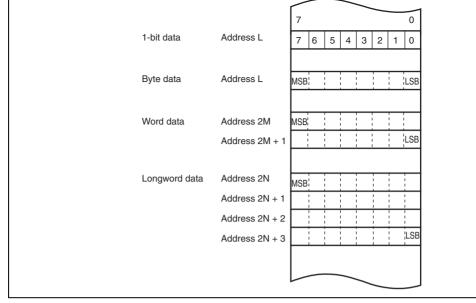

| Figure 2.10 | Memory Data Formats                                             |

|             | Instruction Formats (Examples)                                  |

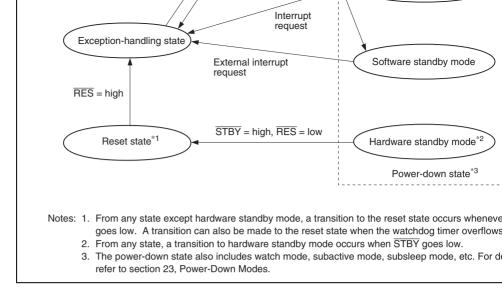

| _           | Branch Address Specification in Memory Indirect Addressing Mode |

| Figure 2.13 | State Transitions                                               |

| Section 2   | MCU Oneveting Modes                                             |

|             | MCU Operating Modes                                             |

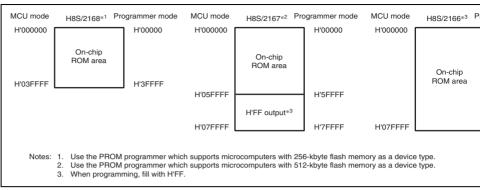

| Figure 3.1  | H8S/2168 Address Map                                            |

| Figure 3.2  | H8S/2167 Address Map                                            |

| Figure 3.3  | H8S/2166 Address Map                                            |

| Section 4   | <b>Exception Handling</b>                                       |

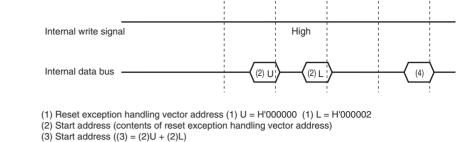

| Figure 4.1  | Reset Sequence                                                  |

| Figure 4.2  | Stack Status after Exception Handling                           |

| Figure 4.3  | Operation when SP Value Is Odd                                  |

| Section 5   | Interrupt Controller                                            |

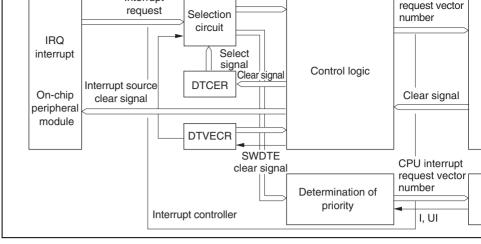

|             | Block Diagram of Interrupt Controller                           |

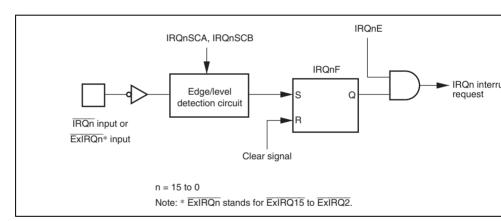

| _           | Block Diagram of Interrupts IRQ15 to IRQ0                       |

| -           |                                                                 |

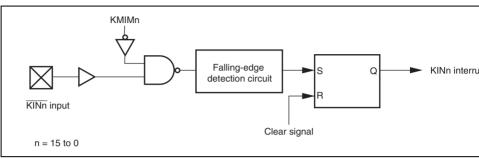

| Figure 5.3  | Block Diagram of Interrupts KIN15 to KIN0 and WUE15 to WUE8     |

|             | (Example of KIN15 to KIN0)                                      |

RENESAS

| Figure 6.16 | Bus Timing for 16-Bit, 2-State Access Space (1) (Even Byte Access) |

|-------------|--------------------------------------------------------------------|

| Figure 6.17 | Bus Timing for 16-Bit, 2-State Access Space (2) (Even Byte Access) |

| Figure 6.18 | Bus Timing for 16-Bit, 2-State Access Space (3) (Odd Byte Access)  |

| Figure 6.19 | Bus Timing for 16-Bit, 2-State Access Space (4) (Odd Byte Access)  |

| Figure 6.20 | Bus Timing for 16-Bit, 2-State Access Space (5) (Word Access)      |

| Figure 6.21 | Bus Timing for 16-Bit, 2-State Access Space (6) (Word Access)      |

| Figure 6.22 | Bus Timing for 16-Bit, 3-State Access Space (1) (Even Byte Access) |

| Figure 6.23 | Bus Timing for 16-Bit, 3-State Access Space (2) (Odd Byte Access)  |

| Figure 6.24 | Bus Timing for 16-Bit, 3-State Access Space (3) (Word Access)      |

| Figure 6.25 | Example of Wait State Insertion Timing (Pin Wait Mode)             |

| Figure 6.26 | Example of Wait State Insertion Timing                             |

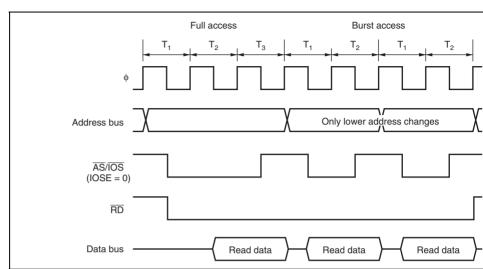

| Figure 6.27 | Access Timing Example in Burst ROM Space (AST = BRSTS1 = 1)        |

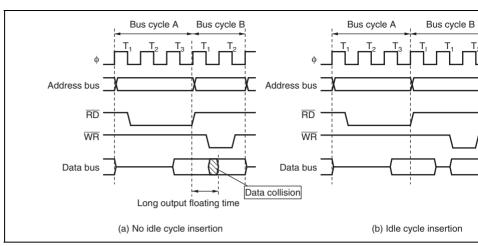

| Figure 6.28 | Access Timing Example in Burst ROM Space (AST = BRSTS1 = 0)        |

| Figure 6.29 | Examples of Idle Cycle Operation                                   |

| Section 7 I | Data Transfer Controller (DTC)                                     |

| Decidi / I  |                                                                    |

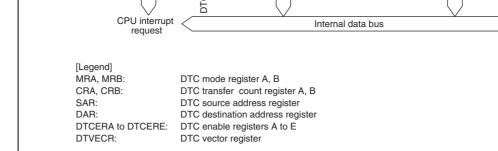

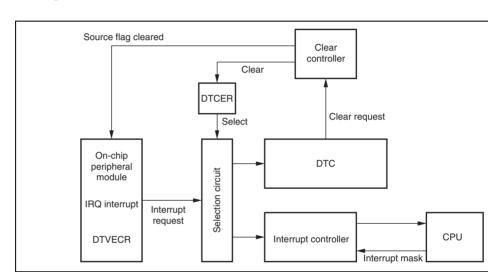

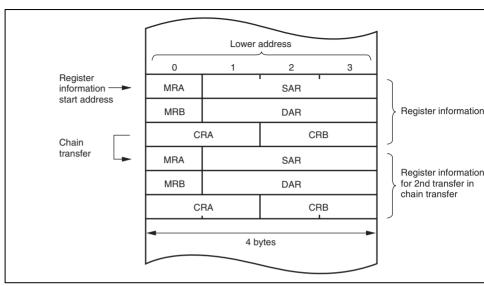

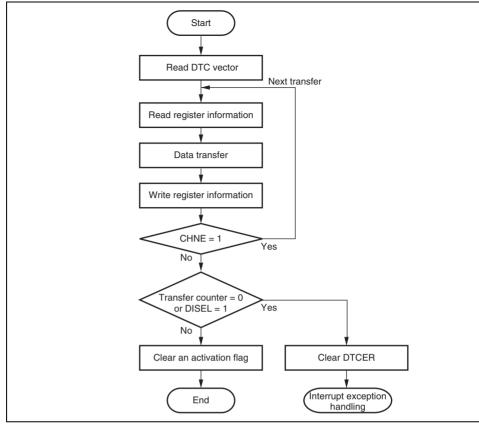

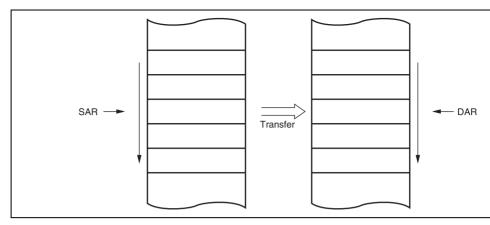

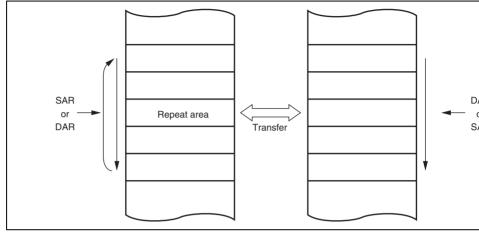

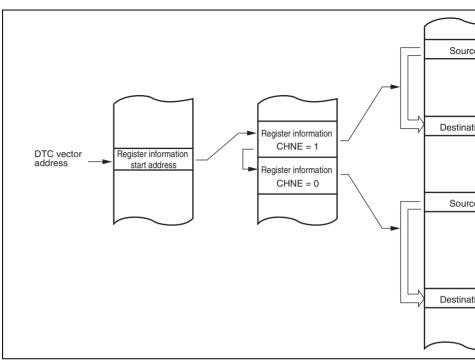

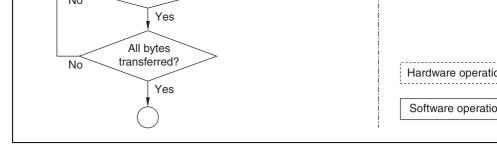

Figure 7.1 Block Diagram of DTC Figure 7.2 Block Diagram of DTC Activation Source Control Figure 7.3 DTC Register Information Location in Address Space..... Figure 7.4 DTC Operation Flowchart..... Figure 7.5 Memory Mapping in Normal Mode Figure 7.6 Memory Mapping in Repeat Mode

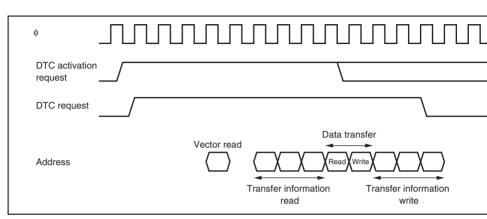

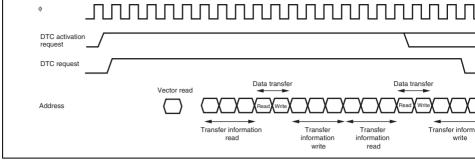

Figure 7.8 Chain Transfer Operation Figure 7.9 DTC Operation Timing (Example in Normal Mode or Repeat Mode) ......

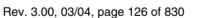

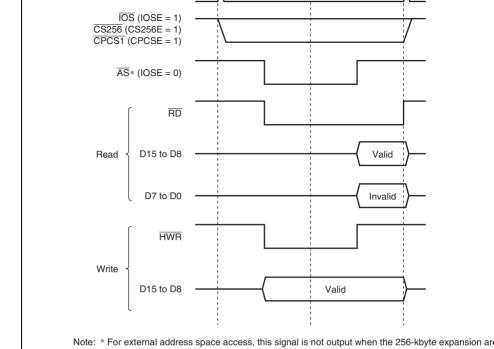

Figure 6.13 Bus Timing for 8-Bit, 2-State Access Space Figure 6.14 Bus Timing for 8-Bit, 2-State Access Space Figure 6.15 Bus Timing for 8-Bit, 3-State Access Space

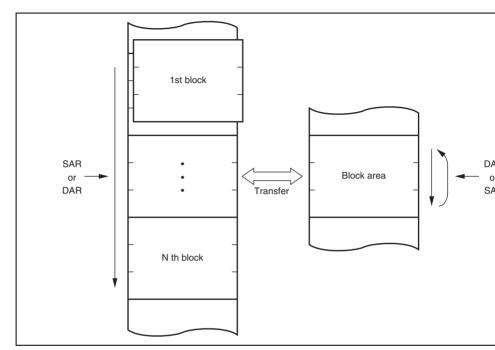

## Figure 7.7 Memory Mapping in Block Transfer Mode

Figure 7.10 DTC Operation Timing (Example of Block Transfer Mode, with Block Size of 2).....

RENESAS

Rev. 3.00, 03/04, page xxvi of xl

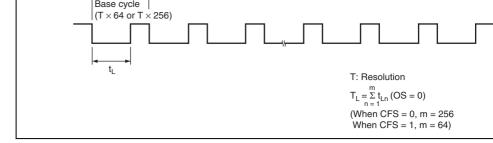

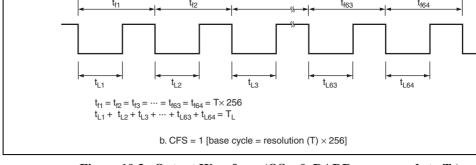

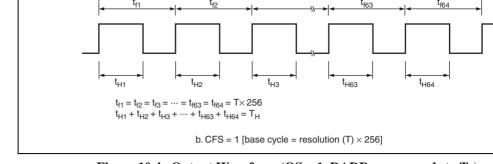

| -           | •                                                             |

|-------------|---------------------------------------------------------------|

| Figure 10.4 | Output Waveform (OS = 1, DADR corresponds to $T_H$ )          |

| Figure 10.5 | D/A Data Register Configuration when CFS = 1                  |

| Figure 10.6 | Output Waveform when DADR = H'0207 (OS = 1)                   |

| Section 11  | 16-Bit Free-Running Timer (FRT)                               |

| Figure 11.1 | Block Diagram of 16-Bit Free-Running Timer                    |

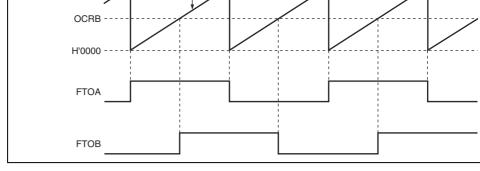

| Figure 11.2 | Example of Pulse Output                                       |

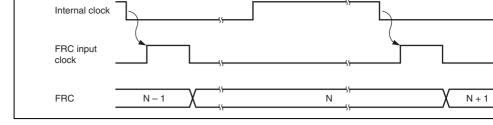

|             | Increment Timing with Internal Clock Source                   |

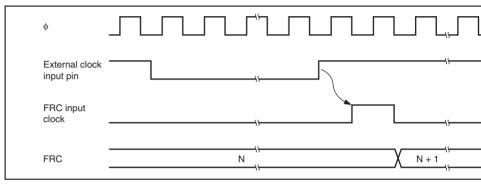

|             | Increment Timing with External Clock Source                   |

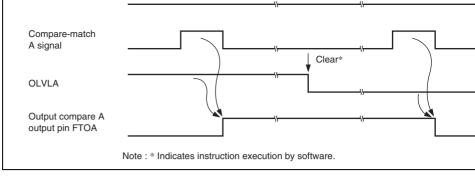

| Figure 11.5 | Timing of Output Compare A Output                             |

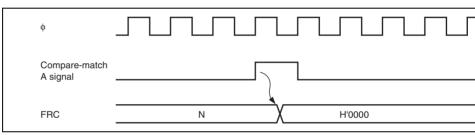

| -           | Clearing of FRC by Compare-Match A Signal                     |

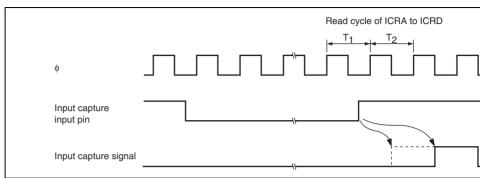

| Figure 11.7 | Input Capture Input Signal Timing (Usual Case)                |

| Figure 11.8 | Input Capture Input Signal Timing (When ICRA to ICRD is Read) |

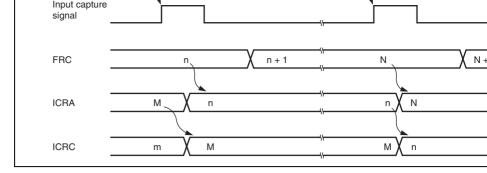

| Figure 11.9 | Buffered Input Capture Timing                                 |

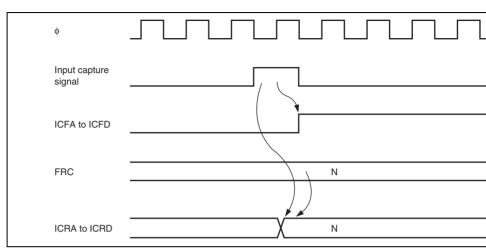

|             | Buffered Input Capture Timing (BUFEA = 1)                     |

| _           | Timing of Input Capture Flag (ICFA to ICFD) Setting           |

| _           |                                                               |

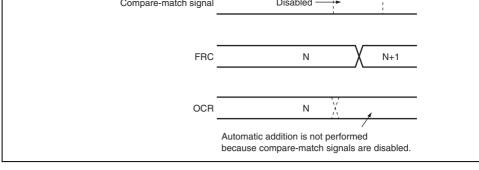

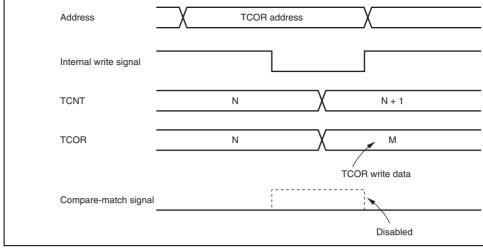

Figure 11.19 Conflict between OCR Write and Compare-Match

Figure 11.20 Conflict between OCR Write and Compare-Match

Figure 10.3 Output Waveform (OS = 0, DADR corresponds to  $T_1$ ).....

1 1guil 10.2 1 W WIX (D/A) Operation ......

RENESAS

(When Automatic Addition Function is Not Used).....

(When Automatic Addition Function is Used).....

Rev. 3.00, 03/04, pag

| Figure 12.13 | Conflict between TCNT Write and Counter Clear              |

|--------------|------------------------------------------------------------|

| Figure 12.14 | Conflict between TCNT Write and Increment                  |

| Figure 12.15 | Conflict between TCOR Write and Compare-Match              |

| Section 13   | Watchdog Timer (WDT)                                       |

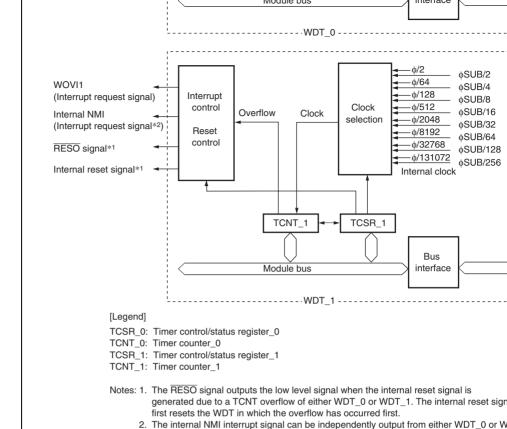

| Figure 13.1  | Block Diagram of WDT                                       |

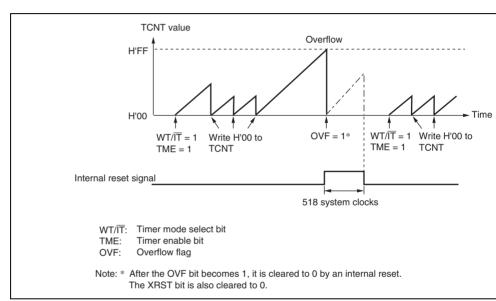

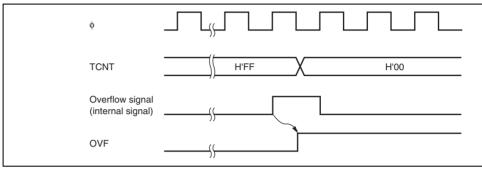

|              | Watchdog Timer Mode (RST/NMI = 1) Operation                |

| Figure 13.3  | Interval Timer Mode Operation                              |

| Figure 13.4  | OVF Flag Set Timing                                        |

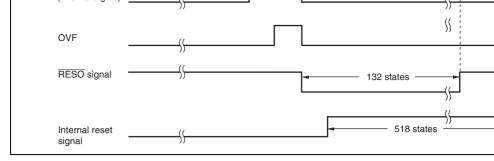

| -            | Output Timing of RESO signal                               |

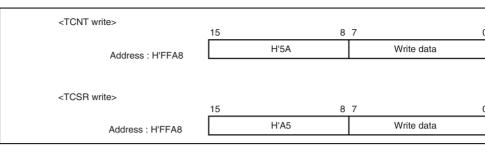

| -            | Writing to TCNT and TCSR (WDT_0)                           |

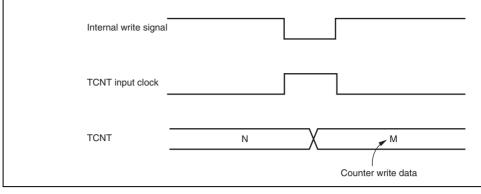

| _            | Conflict between TCNT Write and Increment                  |

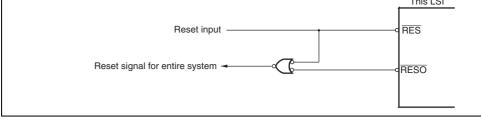

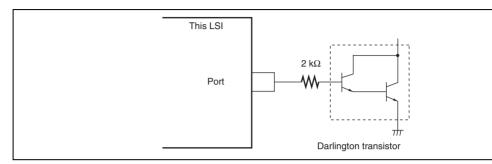

| •            | Sample Circuit for Resetting the System by the RESO Signal |

| C            |                                                            |

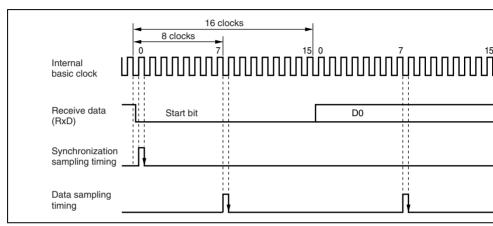

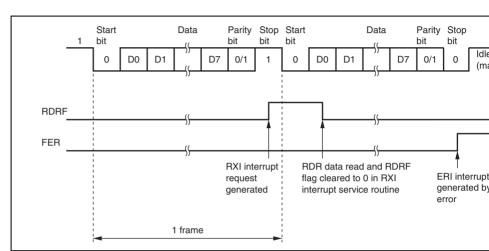

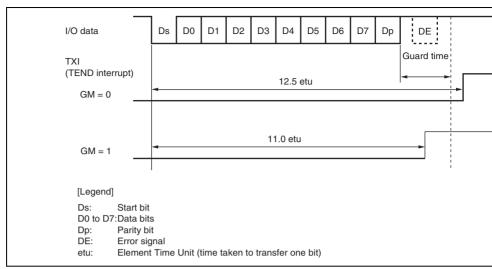

Figure 14.4 Receive Data Sampling Timing in Asynchronous Mode ......

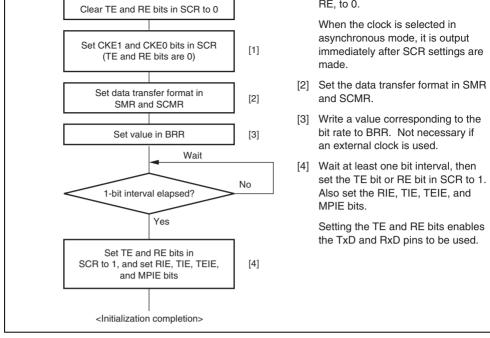

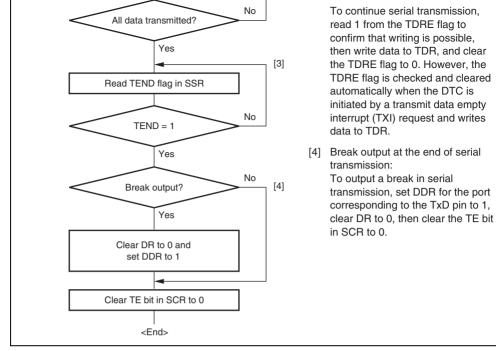

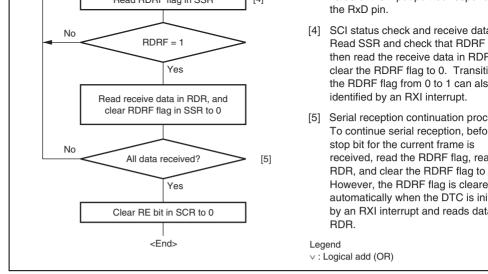

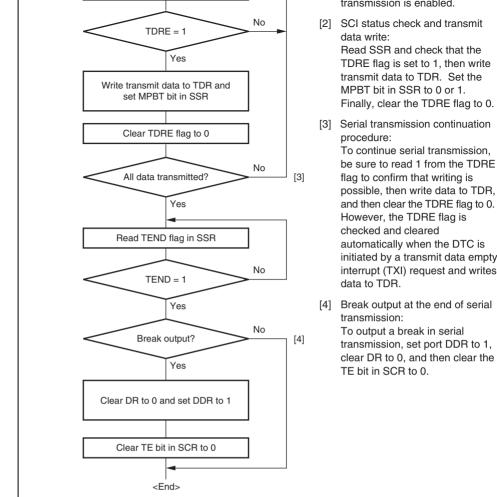

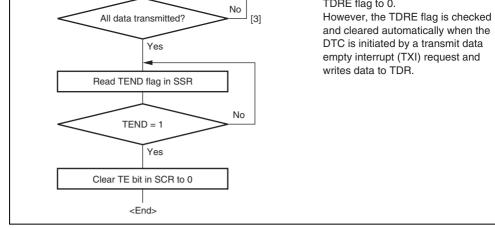

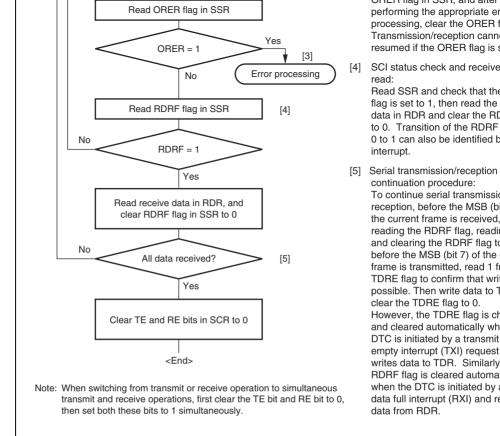

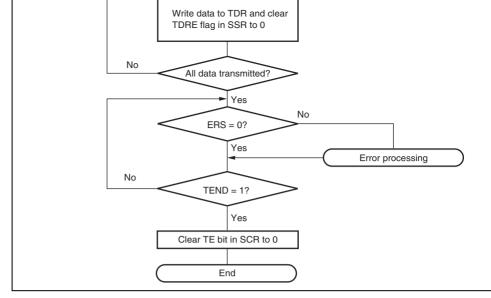

Figure 14.10 Sample Serial Transmission Flowchart.....

(Example with 8-Bit Data, Parity, Two Stop Bits).....

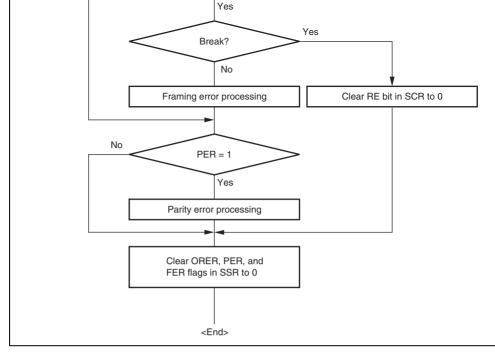

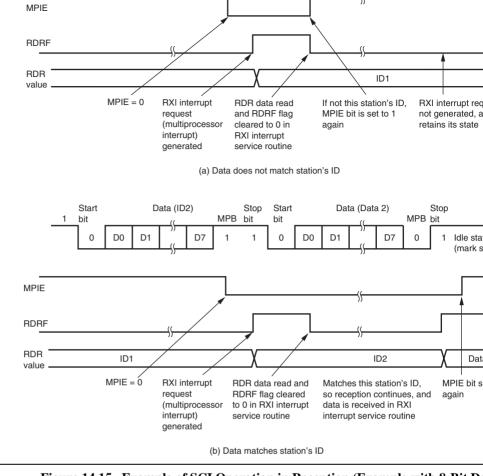

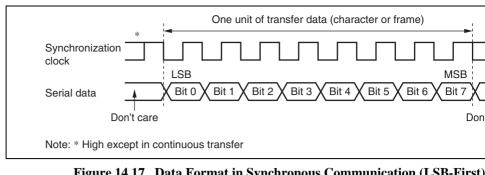

Section 14 Serial Communication Interface (SCI, IrDA, and CRC)

Figure 14.5 Relation between Output Clock and Transmit Data Phase

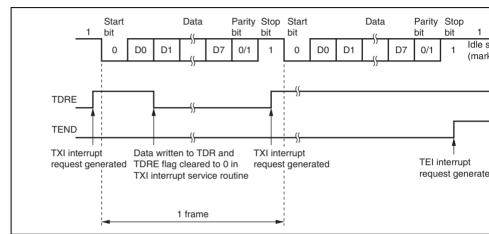

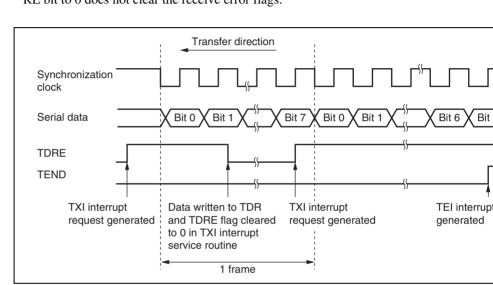

Figure 14.9 Example of Operation in Transmission in Asynchronous Mode

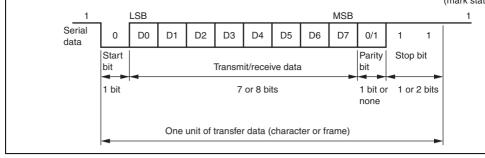

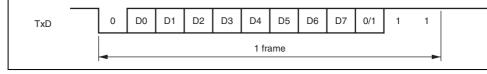

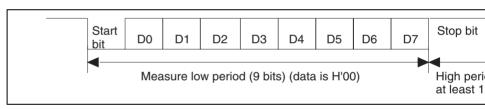

Figure 14.3 Data Format in Asynchronous Communication

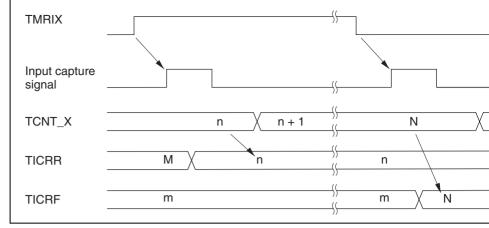

(Input capture signal is input during TICRR and TICRF read) .....

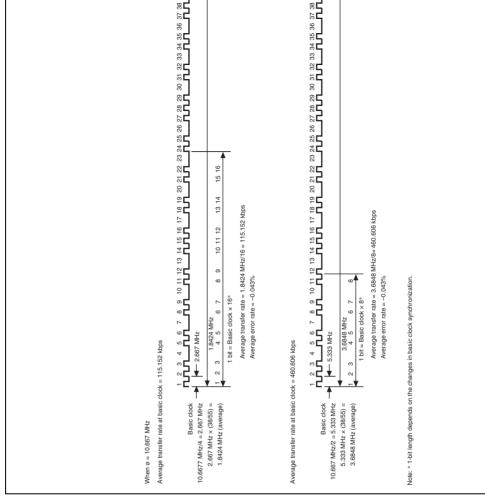

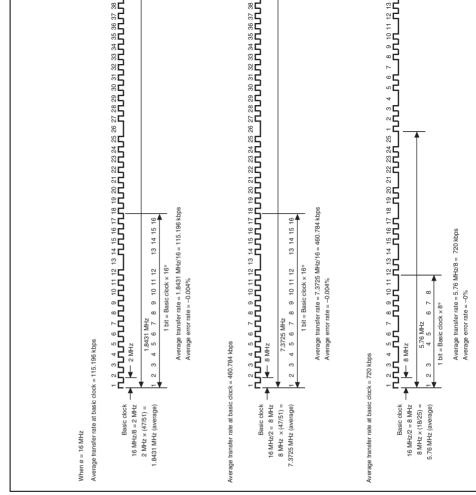

(Asynchronous Mode)......Figure 14.6 Basic Clock Examples When Average Transfer Rate is Selected (1) .........

rigule 12.12 Tilling of input Captule Signal

RENESAS

(Example with 8-Bit Data, Parity, One Stop Bit).....

Rev. 3.00, 03/04, page xxviii of xl

| $\mathcal{E}$ | 1                                                                      |

|---------------|------------------------------------------------------------------------|

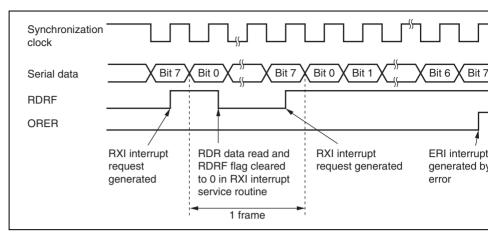

| Figure 14.21  | Example of SCI Receive Operation in Clock Synchronous Mode             |

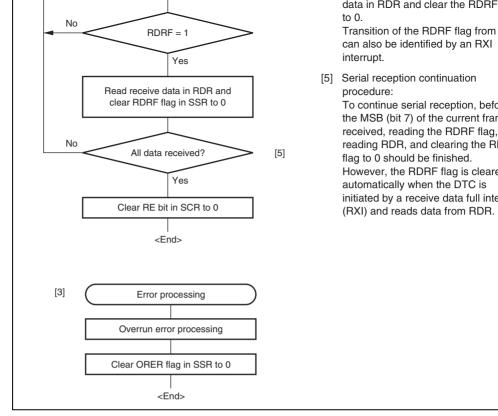

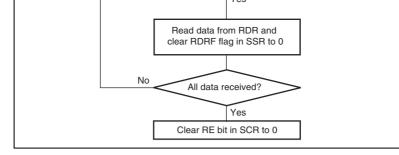

| Figure 14.22  | Sample Serial Reception Flowchart                                      |

| Figure 14.23  | Sample Flowchart of Simultaneous Serial Transmission and Reception     |

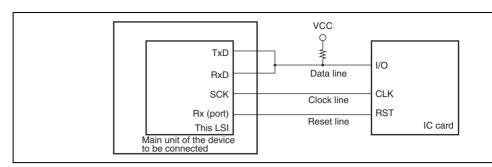

| Figure 14.24  | Pin Connection for Smart Card Interface                                |

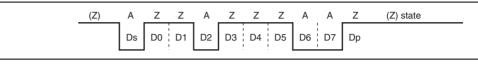

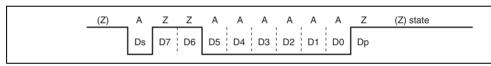

|               | Data Formats in Normal Smart Card Interface Mode                       |

|               | Direct Convention (SDIR = SINV = $O/\overline{E} = 0$ )                |

| Figure 14.27  | Inverse Convention (SDIR = SINV = $O/\overline{E} = 1$ )               |

| Figure 14.28  | Receive Data Sampling Timing in Smart Card Interface Mode              |

|               | (When Clock Frequency is 372 Times the Bit Rate)                       |

| Figure 14.29  | Data Re-transfer Operation in SCI Transmission Mode                    |

| Figure 14.30  | TEND Flag Set Timings during Transmission                              |

| Figure 14.31  | Sample Transmission Flowchart                                          |

| Figure 14.32  | Data Re-transfer Operation in SCI Reception Mode                       |

| Figure 14.33  | Sample Reception Flowchart                                             |

| Figure 14.34  | Clock Output Fixing Timing                                             |

| Figure 14.35  | Clock Stop and Restart Procedure                                       |

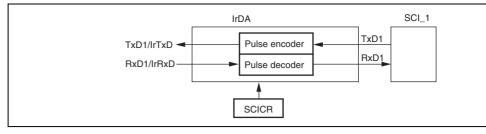

| Figure 14.36  | IrDA Block Diagram                                                     |

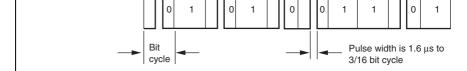

| Figure 14.37  | IrDA Transmission and Reception                                        |

| Figure 14.38  | Sample Transmission using DTC in Clock Synchronous Mode                |

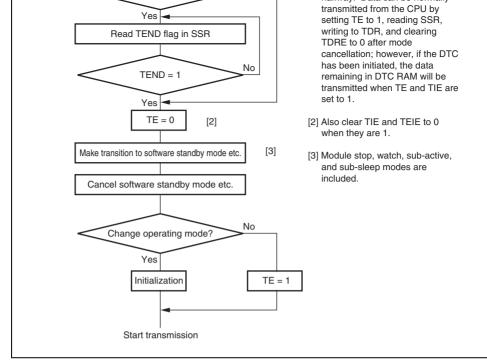

| Figure 14.39  | Sample Flowchart for Mode Transition during Transmission               |

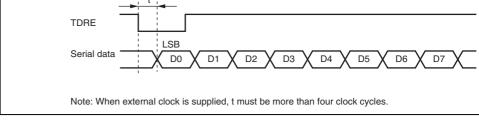

| Figure 14.40  | Pin States during Transmission in Asynchronous Mode (Internal Clock)   |

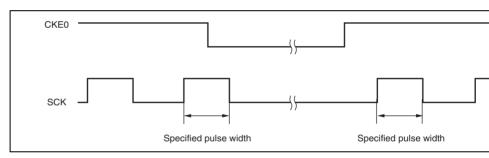

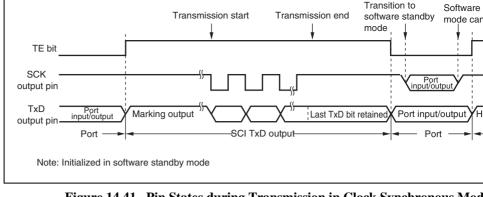

| Figure 14.41  | Pin States during Transmission in Clock Synchronous Mode               |

|               | (Internal Clock)                                                       |

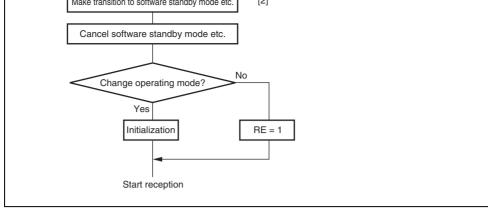

| Figure 14.42  | Sample Flowchart for Mode Transition during Reception                  |

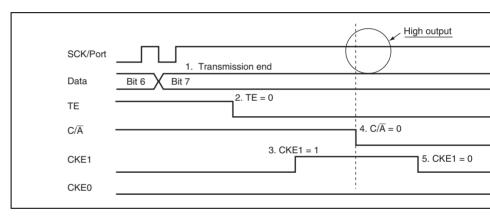

| Figure 14.43  | Switching from SCK Pins to Port Pins                                   |

| Figure 14.44  | Prevention of Low Pulse Output at Switching from SCK Pins to Port Pins |

| _             |                                                                        |

RENESAS

Rev. 3.00, 03/04, pag

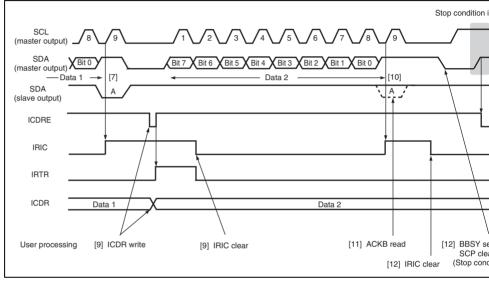

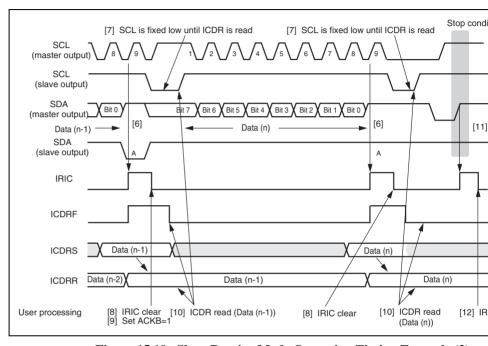

rigule 13.6 Operation rinning example in Master Transmit Mode (MLS – WATT – 0)...

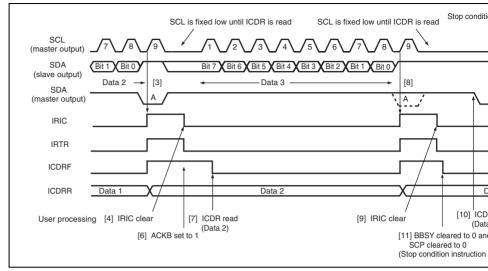

(receiving a single byte) (WAIT = 1) .....

(MLS = ACKB = 0, WAIT = 1)

(MLS = ACKB = 0, HNDS = 0)

(MLS = ACKB = 0, HNDS = 0)

```

Figure 15.16 Stop Condition Issuance Timing Example in Master Receive Mode

(MLS = ACKB = 0, WAIT = 1) ......

Figure 15.17 Sample Flowchart for Operations in Slave Receive Mode (HNDS = 1) .....

Figure 15.18 Slave Receive Mode Operation Timing Example (1) (MLS = 0, HNDS= 1)

```

Figure 15.21 Slave Receive Mode Operation Timing Example (1)

Figure 15.15 Master Receive Mode Operation Timing Example

Figure 15.22

Rev. 3.00, 03/04, page xxx of xl

Figure 15.19 Slave Receive Mode Operation Timing Example (2) (MLS = 0, HNDS= 1 Figure 15.20 Sample Flowchart for Operations in Slave Receive Mode (HNDS = 0).....

Slave Receive Mode Operation Timing Example (2)

| Figure 16.6 | BT Write Transfer Flow                     |

|-------------|--------------------------------------------|

| Figure 16.7 | BT Read Transfer Flow                      |

| Figure 16.8 | GA20 Output                                |

| Figure 16.9 | Power-Down State Termination Timing        |

|             | SERIRQ Timing                              |

| Figure 16.1 | l Clock Start or Speed-Up                  |

|             | 2 HIRQ Flowchart (Example of Channel 1)    |

| Section 17  | D/A Converter                              |

| Figure 17.1 | Block Diagram of D/A Converter             |

| Figure 17.2 | D/A Converter Operation Example            |

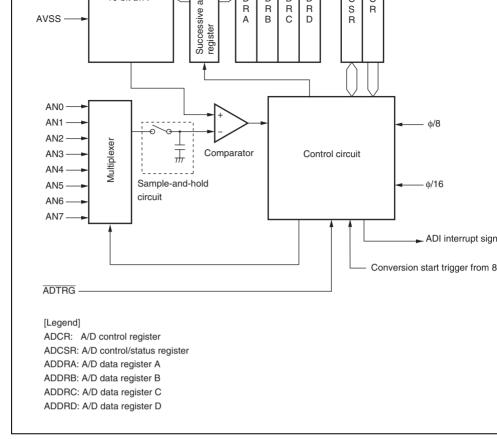

| Section 18  | A/D Converter                              |

| _           | Block Diagram of A/D Converter             |

|             | A/D Conversion Timing                      |

| Figure 18.3 | External Trigger Input Timing              |

| Figure 18.4 | A/D Conversion Accuracy Definitions        |

| Figure 18.5 | A/D Conversion Accuracy Definitions.       |

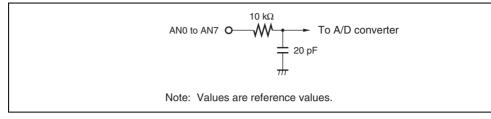

| Figure 18.6 | Example of Analog Input Circuit            |

| Figure 18.7 | Example of Analog Input Protection Circuit |

| Figure 18.8 | Analog Input Pin Equivalent Circuit        |

| Section 20  | Flash Memory (0.18-µm F-ZTAT Version)      |

|             | Block Diagram of Flash Memory              |

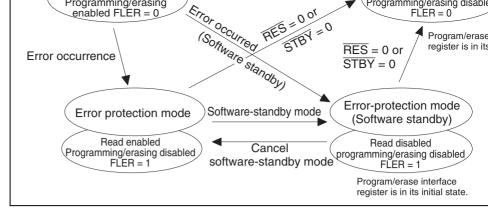

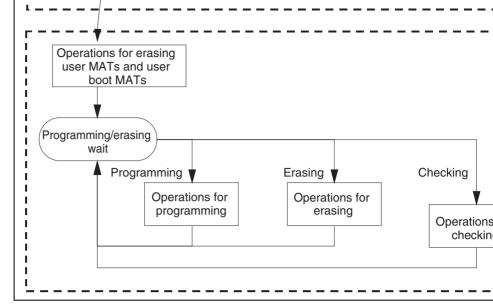

| Figure 20.2 | Mode Transition of Flash Memory            |

| Figure 20.3 | Flash Memory Configuration                 |

|             | Block Division of User MAT                 |

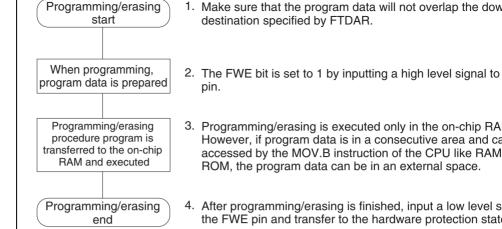

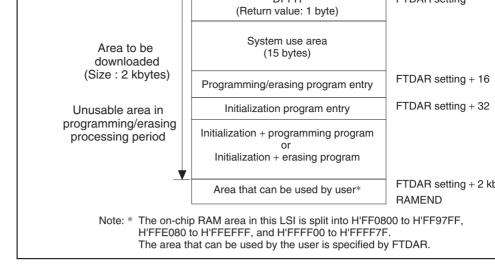

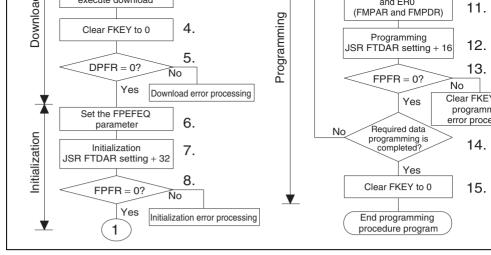

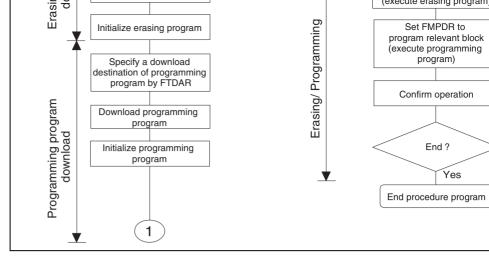

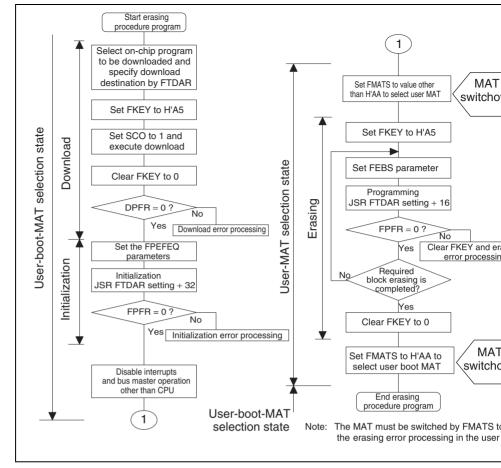

| Figure 20.5 | Overview of User Procedure Program         |

Figure 16.3 Abort Mechanism

Figure 16.4 SMIC Write Transfer Flow

Figure 16.5 SMIC Read Transfer Flow

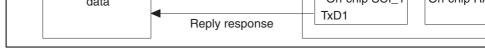

Figure 20.6 System Configuration in Boot Mode.....

Rev. 3.00, 03/04, pag

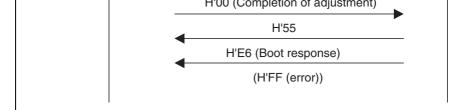

| Figure 20.21 | Communication Protocol Format                          |

|--------------|--------------------------------------------------------|

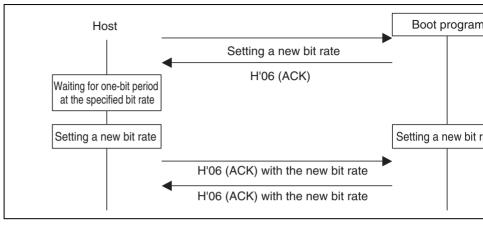

| Figure 20.22 | New Bit-Rate Selection Sequence                        |

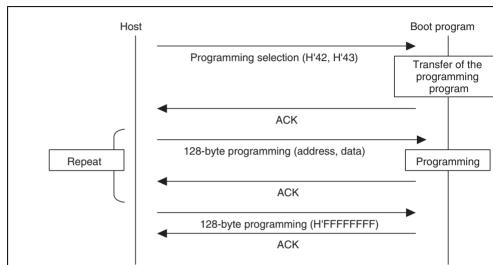

| Figure 20.23 | Programming Sequence                                   |

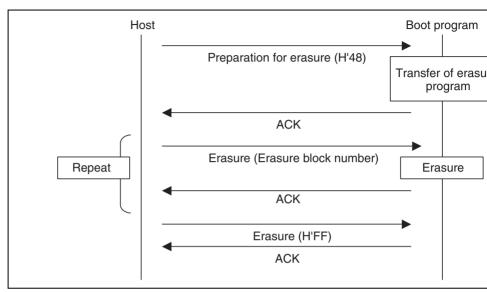

| Figure 20.24 | Frasure Sequence                                       |

| Section 21   | Boundary Scan (JTAG)                                   |

| Figure 21.1  | JTAG Block Diagram                                     |

| Figure 21.2  | TAP Controller State Transitions                       |

| Figure 21.3  | Reset Signal Circuit Without Reset Signal Interference |

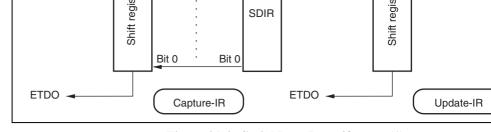

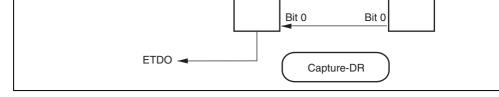

| Figure 21.4  | Serial Data Input/Output (1)                           |

| Figure 21.5  | Serial Data Input/Output (2)                           |

| Section 22   | Clock Pulse Generator                                  |

| Figure 22.1  | Block Diagram of Clock Pulse Generator                 |

| Figure 22.2  | Typical Connection to Crystal Resonator                |

| Figure 22.3  | Equivalent Circuit of Crystal Resonator                |

| Figure 22.4  | Example of External Clock Input                        |

| Figure 22.5  | Note on Board Design of Oscillation Circuit Section    |

| Section 23   | Power-Down Modes                                       |

| Figure 23.1  | Mode Transition Diagram                                |

| Figure 23.2  | Medium-Speed Mode Timing                               |

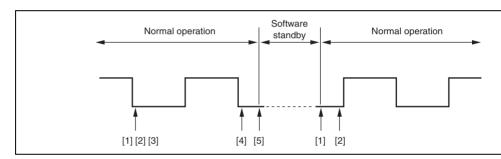

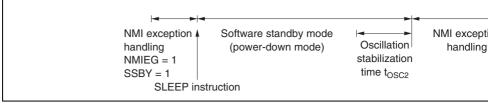

| Figure 23.3  | Software Standby Mode Application Example              |

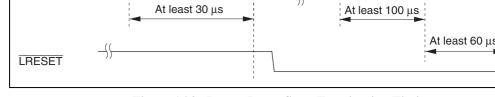

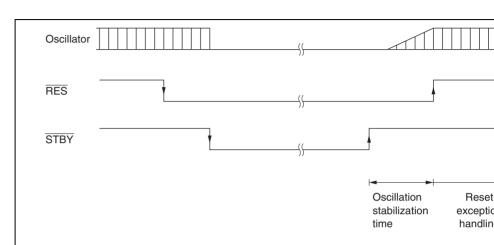

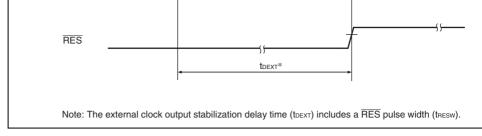

| Figure 23.4  | Hardware Standby Mode Timing                           |

| Section 25   | <b>Electrical Characteristics</b>                      |

RENESAS

Rev. 3.00, 03/04, page xxxii of xl

Figure 20.20 Bit-Rate-Adjustment Sequence

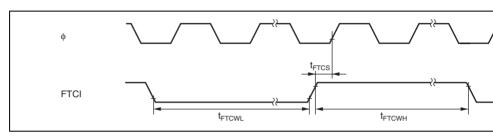

| Figure 25.20 | FRT Input/Output Timing                            |

|--------------|----------------------------------------------------|

| Figure 25.21 | FRT Clock Input Timing                             |

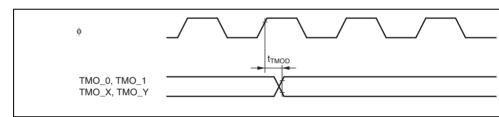

| Figure 25.22 | 8-Bit Timer Output Timing                          |

|              | 8-Bit Timer Clock Input Timing                     |

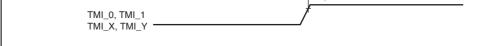

| Figure 25.24 | 8-Bit Timer Reset Input Timing                     |

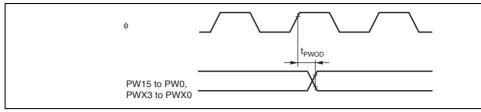

|              | PWM, PWMX Output Timing                            |

|              | SCK Clock Input Timing.                            |

|              | SCI Input/Output Timing (Clock Synchronous Mode)   |

| Figure 25.28 | A/D Converter External Trigger Input Timing        |

| Figure 25.29 | WDT Output Timing (RESO)                           |

|              | I <sup>2</sup> C Bus Interface Input/Output Timing |

|              | LPC Interface (LPC) Timing                         |

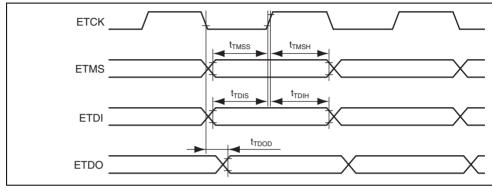

|              | JTAG ETCK Timing                                   |

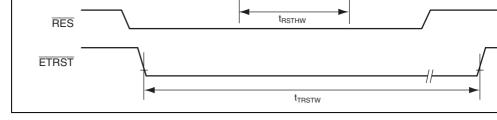

|              | Reset Hold Timing                                  |

|              | JTAG Input/Output Timing                           |

Figure 25.19 I/O Port Input/Output Timing.....

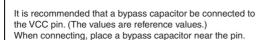

Figure 25.35 Connection of VCL Capacitor....

**Appendix**

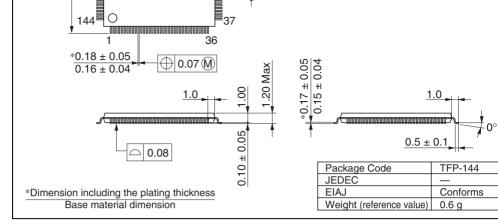

Figure C.1 Package Dimensions (TFP-144)

Rev. 3.00, 03/04, page xxxiv of xl

|             | =                                                                    |

|-------------|----------------------------------------------------------------------|

| Table 2.8   | Branch Instructions                                                  |

| Table 2.9   | System Control Instructions                                          |

| Table 2.10  | Block Data Transfer Instructions                                     |

| Table 2.11  | Addressing Modes                                                     |

| Table 2.12  | Absolute Address Access Ranges                                       |

| Table 2.13  | Effective Address Calculation (1)                                    |

| Table 2.13  | Effective Address Calculation (2)                                    |

| Section 3 N | MCU Operating Modes                                                  |

| Table 3.1   | MCU Operating Mode Selection                                         |

| Table 3.2   | Pin Functions in Each Mode                                           |

| Section 4 E | Exception Handling                                                   |

| Table 4.1   | Exception Types and Priority                                         |

| Table 4.2   | Exception Handling Vector Table                                      |

| Table 4.2   | Exception Handling Vector Table (cont)                               |

| Table 4.3   | Status of CCR after Trap Instruction Exception Handling              |

| Section 5 I | nterrupt Controller                                                  |

| Table 5.1   | Pin Configuration                                                    |

| Table 5.2   | Correspondence between Interrupt Source and ICR                      |

| Table 5.3   | Interrupt Sources, Vector Addresses, and Interrupt Priorities        |

|             |                                                                      |

| Table 5.3   | Interrupt Sources, Vector Addresses, and Interrupt Priorities (cont) |

Bit Manipulation Instructions (2).....

Table 2.6

Table 2.7 Table 2.7

Table 5.3 Table 5.4

Table 5.5

Table 5.6

Table 5.7

Interrupt Sources, Vector Addresses, and Interrupt Priorities (cont).......

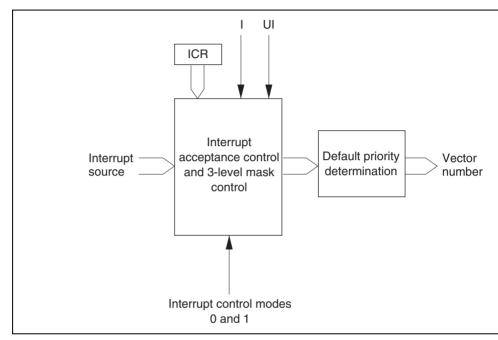

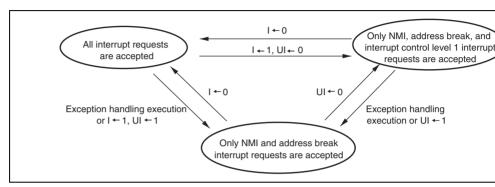

Operations and Control Signal Functions in Each Interrupt Control Mode

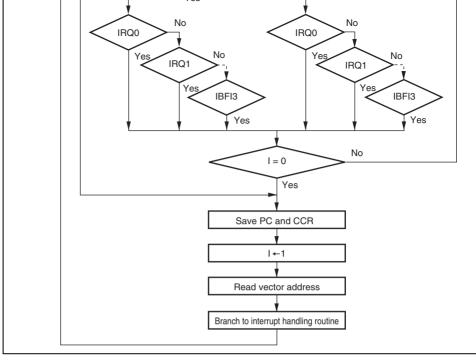

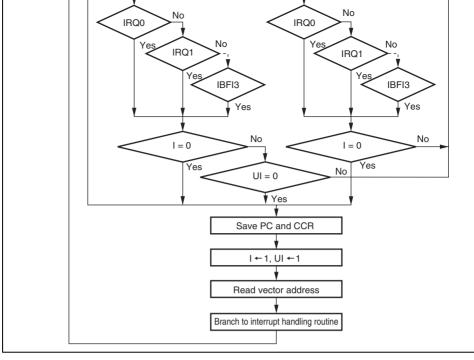

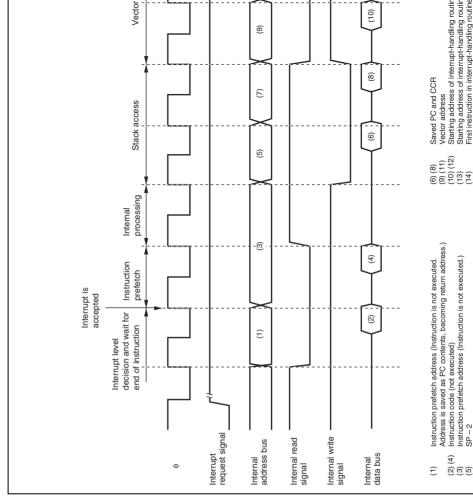

Interrupt Response Times .....

| - *** |               | r                                                                      |

|-------|---------------|------------------------------------------------------------------------|

|       |               | (Data Cycle)                                                           |

| Tal   | ble 6.11      | Bus Specifications for 256-kbyte Extended Area/Multiplex Bus Interface |

|       |               | (Address Cycle)                                                        |

| Tal   | ble 6.12      | Bus Specifications for 256-kbyte Extended Area/Multiplex Bus Interface |

|       |               | (Data Cycle)                                                           |

| Tal   | ble 6.13      | Bus Specifications for CP Extended Area/Multiplex Bus Interface        |

|       |               | (Address Cycle)                                                        |

| Tal   | ble 6.14      | Bus Specifications for CP Extended Area/Multiplex Bus Interface        |

|       |               | (Data Cycle)                                                           |

| Tal   | ble 6.15      | Address Range for IOS Signal Output                                    |

| Tal   | ble 6.16      | Data Buses Used and Valid Strobes                                      |

| Tal   | ble 6.17      | Pin States in Idle Cycle                                               |

| Sec   | ction 7 Da    | ta Transfer Controller (DTC)                                           |

| Tal   | ble 7.1       | Correspondence between Interrupt Sources and DTCER                     |

| Tal   | ble 7.2       | DTC Event Counter Conditions                                           |

| Tal   | ble 7.3       | Flag Status/Address Code                                               |

| Tal   | ble 7.4       | Interrupt Sources, DTC Vector Addresses, and Corresponding DTCEs       |

| Tal   | ble 7.4       | Interrupt Sources, DTC Vector Addresses, and Corresponding DTCEs (co   |

| Tal   | ble 7.5       | Register Functions in Normal Mode                                      |

| Tal   | ble 7.6       | Register Functions in Repeat Mode                                      |

| Tal   | ble 7.7       | Register Functions in Block Transfer Mode                              |

| Tal   | ble 7.8       | DTC Execution Status                                                   |

| Tal   | ble 7.9       | Number of States Required for Each Execution Status                    |

| Sec   | ction 8 I/O   | ) Ports                                                                |

| Tal   | ble 8.1       | Port Functions                                                         |

| Tal   | ble 8.1       | Port Functions (cont)                                                  |

| Tal   | ble 8.1       | Port Functions (cont)                                                  |

| Re    | v. 3.00, 03/0 | 04, page xxxvi of xl                                                   |

Table 6.10

Bus Specifications for IOS Extended Area/Multiplex Bus Interface

RENESAS

|            | when $\phi = 33 \text{ MHz}$                                      |

|------------|-------------------------------------------------------------------|

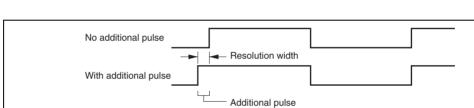

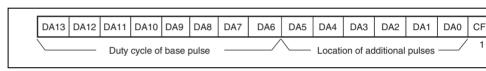

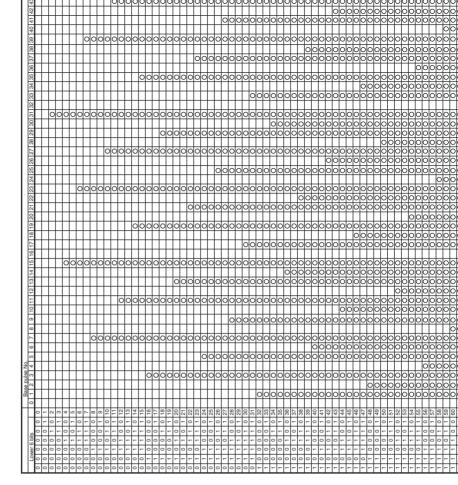

| Table 9.4  | Duty Cycle of Basic Pulse                                         |

| Table 9.5  | Position of Pulses Added to Basic Pulses                          |

| Section 10 | 14-Bit PWM Timer (PWMX)                                           |

| Table 10.1 | Pin Configuration                                                 |

| Table 10.2 | Clock Select of PWMX_1 and PWMX_0                                 |

| Table 10.3 | Settings and Operation (Examples when $\phi = 33$ MHz)            |

| Table 10.4 | Locations of Additional Pulses Added to Base Pulse (When CFS = 1) |

| Section 11 | 16-Bit Free-Running Timer (FRT)                                   |

| Table 11.1 | Pin Configuration                                                 |

| Table 11.2 | FRT Interrupt Sources                                             |

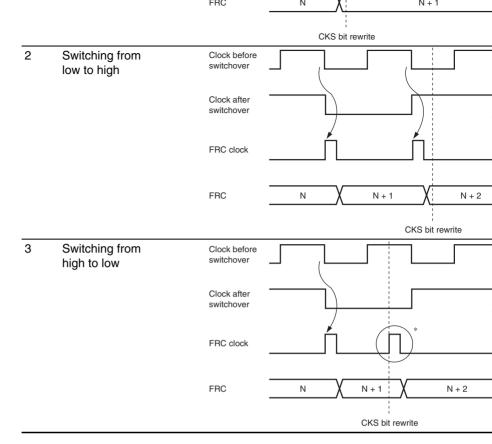

| Table 11.3 | Switching of Internal Clock and FRC Operation                     |

| Table 11.3 | Switching of Internal Clock and FRC Operation (cont)              |

| Section 12 | 8-Bit Timer (TMR)                                                 |

| Table 12.1 | Pin Configuration                                                 |

|            | -                                                                 |

Resolution, F w w Conversion Feriod, and Carrier Frequency

Table 12.5 Interrupt Sources of 8-Bit Timers TMR\_0, TMR\_1, TMR\_Y, and TMR\_

Table 12.6 Timer Output Priorities......

Watchdog Timer (WDT)

Table 12.2

Table 12.2

Table 12.3 Table 12.4

Table 12.7 Table 12.7

Section 13

Table 13.1

Table 13.2

RENESAS

Registers Accessible by TMR\_X/TMR\_Y .....

Input Capture Signal Selection

Switching of Internal Clocks and TCNT Operation.....

Switching of Internal Clocks and TCNT Operation (cont).....

Pin Configuration

WDT Interrupt Source

ESAS

|             | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                                   |

|-------------|-------------------------------------------------------------------------------------------|

| Table 14.12 | SSR Status Flags and Receive Data Handling                                                |

| Table 14.13 | IrCKS2 to IrCKS0 Bit Settings                                                             |

| Table 14.14 | SCI Interrupt Sources                                                                     |

| Table 14.15 | SCI Interrupt Sources                                                                     |