#### High Voltage Synchronous Buck Control IC with Low EMI Option

## **General Description**

The MIC2130/1 is a high voltage input PWM synchronous buck controller IC. It is a voltage mode controller with a fast hysteretic control loop (FHyCL) employed during fast line and load transients. The internal gate drivers are designed to drive high current MOSFETs.

The MIC2130/1 can produce output voltages down to 0.7V with input voltage from 8V to 40V. The MIC2130 family of control ICs implements fixed frequency PWM control. The active anti-shoot through drive scheme means a wide range of external MOSFETs may be used while maintaining optimum efficiency.

The MIC2131 is the fully functional version of the family and implements a new feature to minimize EMI. This function is critical for systems that need to be compliant with EMI standards throughout the world.

The MIC2130/1 is available in small size 16-pin 4mm x 4mm  $MLF^{\mbox{\ensuremath{\mathbb{S}}}}$  package, as well as 16-pin e-TSSOP at a junction temperature range of  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

- 8V to 40V input voltage range

- Adjustable output voltages down to 0.7V

- LOW EMI option MIC2131

- Fixed 150kHz and 400kHz frequency options

- Excellent line and load regulation due to fast hysteretic control loop during transients

- Adaptive gate drive allows efficiencies over 95%

- Programmable current limit with no sense resistor

- Senses low-side MOSFET current

- Internal drivers allow 15A output current

- Power Good output allow simple sequencing

- Programmable soft-start pin

- 100% increase in current limit (MIC2131)

- Output over-voltage protection

- Programmable Input UVLO

- 16-pin e-TSSOP and 16-pin 4mm x 4mm MLF<sup>®</sup>

- Junction temperature range of –40°C to +125°C

### **Applications**

- Industrial/Medical DC/DC point of use power

- Printer head drivers

- Automotive Systems

- Telecom systems

- LCD/ Plasma TV

- Gaming Machines

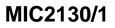

## **Typical Application**

MIC2130/1 High Input Voltage Converter

MLF and *Micro*LeadFrame are registered trademarks of Amkor Technology, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## **Ordering Information**

| Part Number   | Frequency | Output<br>Voltage | Low EMI | Junction Temp.<br>Range | Package                     | Lead Finish |

|---------------|-----------|-------------------|---------|-------------------------|-----------------------------|-------------|

| MIC2130-1YML  | 150kHz    | Adj.              | No      | –40° to +125°C          | 16-Pin 4x4 MLF <sup>®</sup> | Pb-Free     |

| MIC2130-4YML  | 400kHz    | Adj.              | No      | –40° to +125°C          | 16-Pin 4x4 MLF <sup>®</sup> | Pb-Free     |

| MIC2130-1YTSE | 150kHz    | Adj.              | No      | –40° to +125°C          | 16-Pin e-TSSOP              | Pb-Free     |

| MIC2130-4YTSE | 400kHz    | Adj.              | No      | –40° to +125°C          | 16-Pin e-TSSOP              | Pb-Free     |

| MIC2131-1YML  | 150kHz    | Adj.              | Yes     | –40° to +125°C          | 16-Pin 4x4 MLF <sup>®</sup> | Pb-Free     |

| MIC2131-4YML  | 400kHz    | Adj.              | Yes     | –40° to +125°C          | 16-Pin 4x4 MLF <sup>®</sup> | Pb-Free     |

| MIC2131-1YTSE | 150kHz    | Adj.              | Yes     | –40° to +125°C          | 16-Pin e-TSSOP              | Pb-Free     |

| MIC2131-4YTSE | 400kHz    | Adj.              | Yes     | –40° to +125°C          | 16-Pin e-TSSOP              | Pb-Free     |

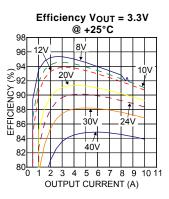

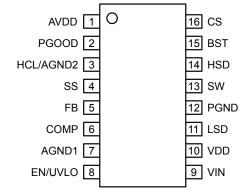

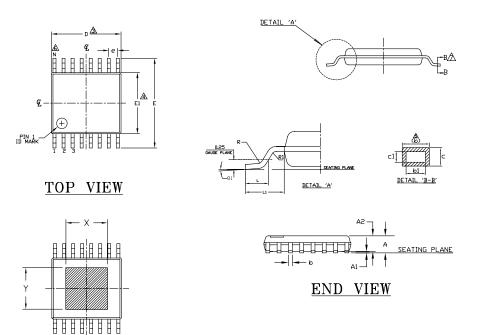

## **Pin Configuration**

16-Pin 4mm x 4mm  $MLF^{(R)}$  (ML)

# **Pin Description**

| Pin Number<br>MLF-16 | Pin Number<br>e-TSSOP-16 | Pin Name      | Pin Function                                                                                                                                                                                                                    |

|----------------------|--------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | 3                        | HCL*<br>AGND2 | High Current Limit (Output): The capacitor on this pin sets the duration of time so that the current limit will be set to 200% of its nominal set current. AGND2 for MIC2130                                                    |

| 2                    | 4                        | SS            | Soft Start (Output): Active at Power-up, Enable, and Current Limit recovery.                                                                                                                                                    |

| 3                    | 5                        | FB            | Feedback (Output): Input to error amplifier. Regulates to 0.7V.                                                                                                                                                                 |

| 4                    | 6                        | COMP          | Compensation (Output): Pin for external compensation.                                                                                                                                                                           |

| 5                    | 7                        | AGND1         | Analog Ground.                                                                                                                                                                                                                  |

| 6                    | 8                        | EN/UVLO       | Enable (Input): Logic low turns the IC off. When the voltage drops below the band gap reference voltage of the IC the device turns off. This accurate threshold allows the pin to be used as an accurate under voltage lockout. |

| 7                    | 9                        | VIN           | Supply Voltage (Input): 8V to 40V.                                                                                                                                                                                              |

| 8                    | 10                       | VDD           | 5V Internal Linear Regulator from VIN. When VIN is <8V, this regulator operates in drop-out mode. Connect external bypass capacitor.                                                                                            |

| 9                    | 11                       | LSD           | Low-Side Drive (Output): High-current driver output for external low-side MOSFET.                                                                                                                                               |

| 10                   | 12                       | PGND          | Power Ground: High current return for ext. Low side driver.                                                                                                                                                                     |

| 11                   | 13                       | SW            | Switch Node (Output): High current output driver return.                                                                                                                                                                        |

| 12                   | 14                       | HSD           | High-Side Drive (Output): High current output-driver for ext. high-side MOSFET.                                                                                                                                                 |

| 13                   | 15                       | BST           | Boost (Output): Provides voltage for high-side MOSFET driver. The gate drive voltage is higher than the source voltage by VDD minus a diode drop.                                                                               |

| 14                   | 16                       | CS            | Current Sense (Output): Current-limit comparator non<br>inverting input. The current limit is sensed across the low-<br>side FET during the OFF time. Current limit is set by the<br>resistor in series with the CS pin.        |

| 15                   | 1                        | AVDD          | Analog Supply Voltage (internal 5V LDO): Connect external By pass capacitor.                                                                                                                                                    |

| 16                   | 2                        | PGOOD         | Power Good (Output): High output when VOUT > 90% nominal.                                                                                                                                                                       |

Note: \* indicates that is only used on MIC2131.

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>IN</sub> )             | 42V                  |

|-----------------------------------------------|----------------------|

| Boot Strapped Voltage (V <sub>BST</sub> )     | V <sub>IN</sub> + 5V |

| Logic Inputs                                  |                      |

| EN Input                                      | 42V                  |

| Ambient Storage Temperature (T <sub>s</sub> ) | –65°C to +150°C      |

| ESD Rating <sup>(3)</sup>                     | 1.5kV                |

# **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>IN1,</sub> V <sub>IN2</sub> )<br>Output Voltage Range |          |

|------------------------------------------------------------------------------|----------|

| Junction Temperature (T <sub>J</sub> )                                       |          |

| Package Thermal Resistance                                                   |          |

| e-TSSOP (θ <sub>JA</sub> )                                                   | 97.5°C/W |

| e-TSSOP (θ <sub>JC</sub> )                                                   | 29.9°C/W |

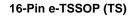

| 4x4 MLF-16 (θ <sub>JA</sub> )                                                | 50.6°C/W |

| 4x4 MLF-16 (θ <sub>JC</sub> )                                                | 15.8°C/W |

# Electrical Characteristics<sup>(4)</sup>

$T_J = 25^{\circ}C$ ;  $V_{EN} = V_{IN} = 24V$ ; Frequency = 150kHz;  $V_{OUT} = 3.3V$ , unless otherwise specified. **Bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ .

| Parameter                                                       | Condition                                                                                               | Min | Тур  | Max  | Units |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| V <sub>IN</sub> , V <sub>EN/UVLO</sub> , V <sub>DD</sub> Supply |                                                                                                         |     |      |      |       |

| Total Supply Current,<br>PWM Mode Supply Current                | V <sub>FB</sub> = 0.7V; Comp = 3V<br>(Outputs switching but excluding external MOSFET gate<br>current.) |     | 4    | 7.5  | mA    |

| Shutdown Current                                                | V <sub>EN</sub> = 0V; V <sub>IN</sub> = 12V                                                             |     | 180  | 300  | μA    |

| V <sub>EN</sub> /UVLO Turn-On Threshold                         |                                                                                                         |     | 1.1  | 1.3  | V     |

| V <sub>EN</sub> /UVLO Turn-Off Threshold                        |                                                                                                         | 0.7 | 1.0  |      | V     |

| VIN UVLO Hysteresis                                             |                                                                                                         |     | 100  |      | mV    |

| Internal Bias Voltages ( $AV_{DD}$ ,)<br>( $I_{DD}$ = 50mA)     |                                                                                                         | 4.6 | 5    | 5.3  | V     |

| Oscillator/PWM Section                                          |                                                                                                         |     |      |      |       |

| PWM Frequency                                                   | MIC2130/1-1                                                                                             | 130 | 150  | 170  | kHz   |

| PWM Frequency                                                   | MIC2130/1-4                                                                                             | 360 | 400  | 440  | kHz   |

| Maximum Duty Cycle                                              | MIC2130/1-1                                                                                             | 92  |      |      | %     |

| Maximum Duty Cycle                                              | MIC2130/1-4                                                                                             | 80  |      |      | %     |

| Minimum On-Time                                                 | Note 5                                                                                                  |     | 50   |      | ns    |

| Regulation                                                      |                                                                                                         |     | 1    |      |       |

| Feedback Voltage Reference                                      | (±2%) -40°C to +125°C                                                                                   | 686 | 700  | 714  | mV    |

| Feedback Bias Current                                           |                                                                                                         |     | 300  | 1000 | nA    |

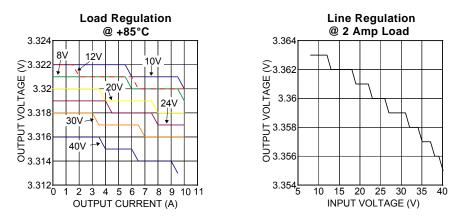

| Output Voltage<br>Line Regulation                               | $V_{IN} = 8V - 40V$                                                                                     |     | 0.03 |      | %/V   |

| Output Voltage<br>Load Regulation                               | $1A \le I_{OUT} \le 10A$                                                                                |     | 0.5  |      | %     |

| Error Amplifier (each channel                                   | )                                                                                                       |     |      |      |       |

| DC Gain                                                         |                                                                                                         |     | 70   |      | dB    |

| Output Impedance                                                |                                                                                                         |     | 2    |      | MΩ    |

| Transconductance                                                |                                                                                                         | 1.2 | 1.6  | 2.5  | ms    |

| Output Over voltage Protection                                  | on                                                                                                      |     |      |      |       |

| V <sub>FB</sub> Threshold                                       | (Latches LSD High)                                                                                      | 110 | 115  | 120  | %Nom  |

| Delay Blanking Time                                             |                                                                                                         |     | 1    |      | μs    |

| Soft Start/HCL                                                  |                                                                                                         |     |      |      |       |

| Internal Soft Start<br>Source Current                           |                                                                                                         | 1   | 2.75 | 5    | μA    |

| HCL (MIC2131) Pin Voltage<br>High                               | $I_{\text{LIMIT}}$ set to 200% when HCL charges to<br>2.4V                                              |     | 2.4  |      | V     |

| Parameter                                     | Condition                                              | Min | Тур        | Max | Units    |

|-----------------------------------------------|--------------------------------------------------------|-----|------------|-----|----------|

| HCL Low                                       | ILIMIT set to normal when HCL is low                   |     | 0.5        |     | V        |

| HCL Pin Charge Up Current                     |                                                        |     | 2.9        |     | μA       |

| HCL Pin Charge Down Current                   |                                                        |     | 12         |     | μA       |

| LOW/EMI                                       |                                                        |     |            |     | 1        |

| Frequency Dither Range                        | Of center freq                                         |     | ±12        |     | %        |

| Current Sense                                 |                                                        |     |            |     | 1        |

| CS Over Current Trip Point<br>Program Current |                                                        | 170 | 200        | 230 | μA       |

| Temperature Coefficient                       |                                                        |     | +2300      |     | ppm/°C   |

| CS Comparator Sense<br>Threshold              | (Senses drop across low-side FET)                      | -5  | 0          | +5  | mV       |

| Power Good                                    |                                                        |     |            |     | •        |

| V <sub>FB</sub> Threshold                     |                                                        | 86  | 90         | 93  | %Nom     |

| PGOOD Voltage Low                             | $V_{DD}$ = 5.0V; $V_{FB}$ = 0V; $I_{PGOOD}$ = 1mA      |     | 0.1        | 0.5 | V        |

| Gate Drivers                                  |                                                        |     | _          |     |          |

| Rise/Fall Time                                | Into 3000pF<br>Source<br>Sink                          |     | 23<br>16   |     | ns<br>ns |

| Output Driver Resistance                      | HSD: Source; $V_{DD}$ = 5V<br>HSD: Sink; $V_{DD}$ = 5V |     | 2<br>1.47  |     | Ω<br>Ω   |

|                                               | LSD: Source; $V_{DD}$ = 5V<br>LSD: Sink; $V_{DD}$ = 5V |     | 2.2<br>2.1 |     | Ω<br>Ω   |

| Driver Non-Overlap Time (Adaptive)            | Note 4                                                 | 40  | 60         |     | ns       |

| Thermal Shutdown Threshold                    | T <sub>J</sub> Increasing                              |     | 155        |     | °C       |

|                                               | T <sub>J</sub> Decreasing                              |     | 142        |     | °C       |

Notes:

1. Exceeding the absolute maximum rating may damage the device.

Electrical specifications do not apply when operating the device outside of its operating ratings. The maximum allowable power dissipation is a function of the maximum junction temperature, T<sub>J(Max)</sub>, the junction-to-ambient thermal resistance, θ<sub>JA</sub>, and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation will result in excessive die temperature, and the regulator will go into thermal shutdown.

3. Devices are ESD sensitive. Handling precautions recommended.

4. Guaranteed by design.

5. Minimum on-time before automatic cycle skipping begins.

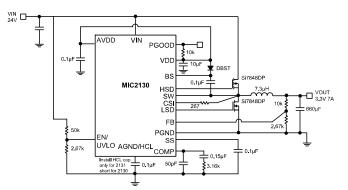

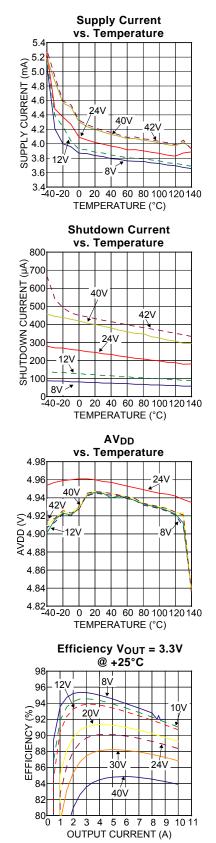

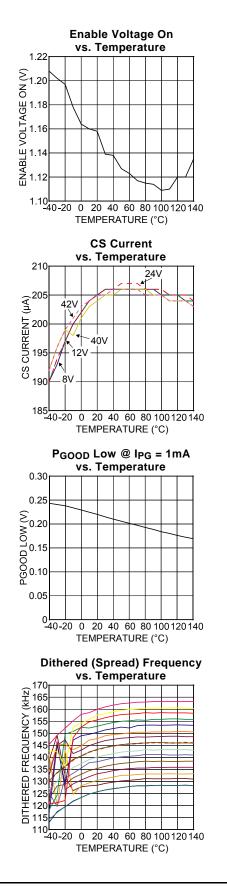

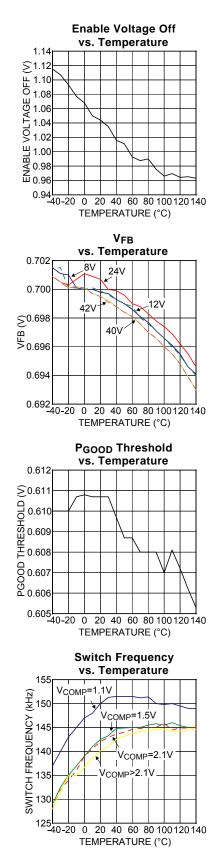

## **Typical Characteristics**

## **Typical Characteristics (continued)**

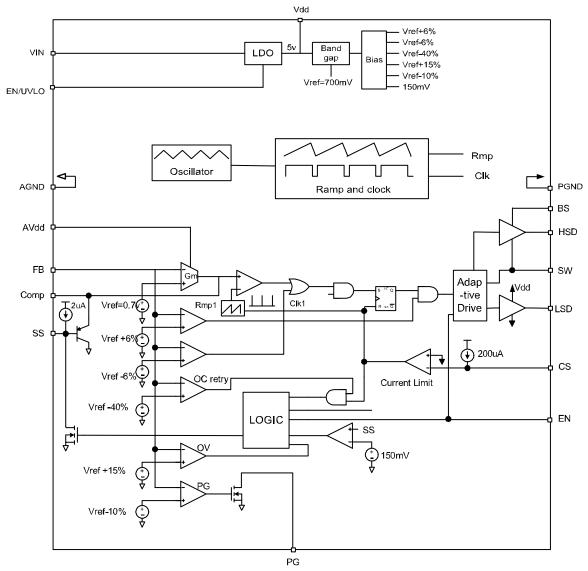

## **Functional Diagram**

Figure 1. MIC2130/1 Block Diagram

## **Functional Description**

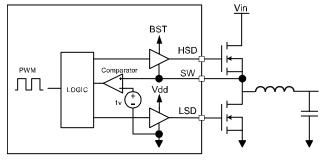

The MIC2130/31 is a voltage mode synchronous buck controller built for optimum speed and efficiency. It is designed for wide input voltage range and for high output power buck converters. Figure 1 shows the block diagram.

The control loop has two stages of regulation. During steady-state to medium output disturbances, the loop operates in fixed frequency, PWM mode while (gm loop), during a large output voltage disturbance ( $\sim\pm6\%$  nominal), the loop becomes hysteretic; meaning that for a short period, the switching MOSFETs are switched on and off continuously until the output voltage returns to it's nominal level. This maximizes transient response for

large load steps, while nominally operating in fixed frequency PWM mode. Voltage mode control is used to allow for maximum flexibility and maintains good transient regulation. The operating input voltage range is 8V to 40V and output can be set from 0.7V up to  $0.85^*V_{IN}$ . Start-up surges are prevented using built in soft start circuitry as well as resistor-less (LSD RDS<sub>ON</sub> is used to sense load current) current sensing for overload protection. Other protection features include UVLO, over voltage latch off protection, Power good signal.

## **Theory of Operation**

A voltage divider monitors the output voltage of the converter then sensed at the inverting input of the error amplifier. The non-inverting input of the error amplifier is connected to the internal 0.7V reference and the two inputs are compared to produce an analog error voltage. This error voltage is then fed into the non-inverting input of the PWM comparator and compared to the voltage ramp (1.1V to 2.1V) to create the PWM pulses. The PWM pulses propagate through to the MOSFET drivers which drive the external MOSFETs to create the power switching waveform at the set D (duty cycle). This is then filtered by a power inductor and low ESR capacitor to produce the output voltage where  $V_{OUT} \approx D^* V_{IN}$ . As an example, due to a load increase or an input voltage drop, the output voltage will instantaneously drop. This will cause the error voltage to rise, resulting in wider pulses at the output of the PWM comparator. The higher Duty Cycle power switching waveform will cause an associated rise in output voltage and will continue to rise until the feedback voltage is equal to the reference and the loop is again in equilibrium. As with any control system, it is necessary to compensate this feedback loop (by selecting the R and C values at the comp pin) in order to keep the system stable. One of the tradeoffs for stability is reduced transient regulation performance. However, the MIC2130/31 has an additional feature to correct this problem. The MIC2130/31 family features a fast hysteretic control loop (FHyCL) which bypasses the gm amp and the feedback compensation network during fast line and load transients.

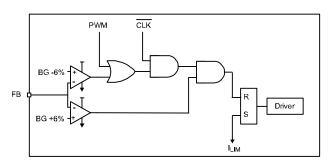

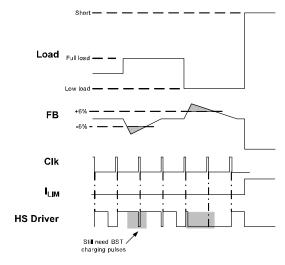

The fast hysteretic control loop (FHyCL) operates during large transients to provide excellent line and load regulation. Hysteretic mode is invoked when the output voltage is detected to be ±6% of its regulated value. If the input voltage step or output load step is large enough to cause a 6% deviation in  $V_{\text{OUT}}$ , then the additional hysteretic control loop functions to return the output voltage to its nominal set point in the fastest time possible. This is limited only by the time constant of the power inductor and output capacitor (an order of magnitude faster than the gm loop). This scheme is not used during normal operation because it creates switching waveforms whose frequency is dependant on V<sub>IN</sub>, passive component values and load current. Due to its large noise spectrum it is only used during surges to keep switching noise at a known, fixed frequency.

Figure 2. Hysteric Block Diagram

Figure 3. Hysteric Waveforms

Soft Start

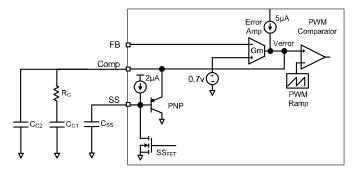

Figure 4. Soft Start Circuit

At startup, the Soft-start MOSFET (SS<sub>FET</sub>) is released and  $C_{SS}$  starts to charge at the rate  $dV_{SS}/dt-2\mu A/C_{SS}$ . The PNP transistor's emitter (COMP) starts to track  $V_{\text{SS}}$ (plus a junction voltage ≈0.65). When (COMP) reaches the lower end of the PWM ramp voltage at 1.10V, switching pulses will begin to drive the power MOSFETs. This voltage rise continues on the COMP pin until the control loop reaches the regulation point. During this soft start period, the gate drive pulses to the MOSFET will start at the minimum pulse width and increase up to the duty cycle D required for regulation. The COMP voltage can be anywhere from 1.1V to 2.1V which corresponds to a duty cycle D of 0-85%.  $V_{SS}$  will however, continue to rise as the PNP base-emitter junction becomes reverse biased. The SS pin is allowed to rise to 2.5V (four diode drops) max to allow fast response to fault conditions. During large over current or short circuit conditions, i.e., where current limit is detected and  $V_{OUT}$  is <60% of nominal, the SS<sub>FET</sub> is momentarily switched on. This discharges C<sub>SS</sub> to ~150mV at which point, it re-starts the soft start cycle once again. During soft start, hysteretic comparators are disabled.

Duty Cycle D can be written in terms of  $V_{\mbox{\scriptsize COMP}}$

$D = (0.85) \times V_{COMP} - (0.935) \text{ or } V_{COMP} = (D + 0.935)/0.85$

Example:  $V_{IN}$  = 12V;  $V_{OUT}$  = 3.3V; D =  $V_{OUT}/V_{IN}$  = 0.275

$V_{\text{COMP}}$  = 1.424V; i.e. the steady-state DC Value of  $V_{\text{COMP}}$  when D = 0.275

T1 is the time for  $V_{\text{COMP}}$  to charge up to 1.1V, therefore,  $V_{\text{SS}}$  is one diode drop below  $V_{\text{COMP}}.$

T2 is the time for V<sub>COMP</sub> to charge up to (D + 0.935)/ 0.85 + 1.1V.

Soft Start time = T1 + T2

Where

T1 = (1.1-Vdiode) x  $C_{SS}/2\mu A$ ; the time until output pulsing starts at minimum duty.

And,

T2 = (1/0.85) x D x C<sub>SS</sub>/ 2 $\mu$ A; the time until output pulsing increases to D.

The compensation capacitors at the COMP pin ( $C_{COMP}$  = Cc1+Cc2 in Figure 4) will also need to charge up to  $V_{COMP}$ . This charging time starts as soon as MOSFET ( $SS_{FET}$ ) is released. Depending upon the size of the  $C_{COMP}$ , the charging time could be greater than T1+T2.  $C_{COMP}$  could be used for the Soft Start cap by leaving SS pin open.

$Tc_{COMP}$  = (1/0.85) x D x C<sub>COMP</sub>/5µA: The time until output pulsing increases to D.

#### Protection

There exits four different types of output protection.

- 1. Output "hard short" over current

- 2. Output "soft short" over current

- 3. Output under voltage

- 4. Output over voltage

#### **Current Limit**

The MIC2130/31 uses the  $RDS_{ON}$  of the low-side MOSFET to sense overcurrent conditions. The lower MOSFET is used because it displays much lower parasitic oscillations during switching then the upper MOSFET. Using the low-side MOSFET  $RDS_{ON}$  as a current sense is an excellent method for circuit protection. This method will avoid adding cost, board space and power losses taken by discrete current sense resistors.

#### Hard Short

Generally, the MIC2130/31 current limit circuit acts to provide a fixed maximum output current until the resistance of the load is so low that the voltage across it is no longer within regulation limits. At this point (60% of nominal output voltage), the part employs Hiccup mode. During Hiccup mode, the output pulses stop and the soft start cap is discharged and soft start mode begins. After the soft start time, if the output voltage is still 60% low, then the process repeats again and continues until the short is removed. Hard short current mode is initiated to protect down stream loads from excessive current and also reduces overall power dissipation in the PWM converter components during a fault.

#### Soft Short

Before "Hard Short" mode (also called "hiccup mode") occurs "soft short" current limiting is provided to prevent system shutdown or disturbance if the overload is only marginal. When the load current exceeds the current limit by only a few ma for a short time (milliseconds) then the hard short mode is not desired. Instead, the "Soft Short" loop is used. When the current limit comparator senses an over current it then starts to discharge the SS Cap with a 40µA current source. The current limit comparator gets reset every cycle so if the short still exist during the next cycle then the SS cap will continue to get discharged with the 40µA current source. The comp pin follows the SS pin (Figure 4) and the gm control loop will lower the output voltage accordingly for as long as the short exists. So, instead of shutting down the output as in a hard short, the output is gently and slightly reduced until the over current condition discontinues. If however the short increase to the point of lowering the output to 60%, then hard short will result. The fast hysteretic control loop (FHvCL) is initiated by a 6% drop in output voltage and it is not desired during an over current condition therefore, the FHvCL feature will

be disabled during an over current condition.

#### **Under Voltage**

A  $\pm 6\%$  comparator monitors the output voltage and will initiate the fast hysteretic control loop (FHyCL) to regulate the output. A comparator monitors the output voltage and sets PGOOD true when the output reaches 90% of the regulated output.

#### **Over Voltage**

If the voltage at the FB pin is detected to be 15% higher than nominal for >2 $\mu$ s, then the controller is stopped from switching immediately and latched off. Switching can be re-started by taking EN below the channel's enable threshold and re-enabling or re-cycling power to the IC.

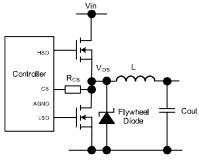

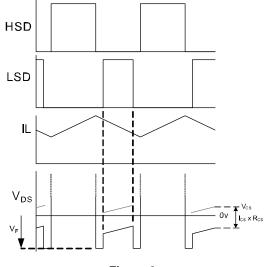

Figure 5.

During the normal operation of a synchronous Buck regulator, as the lower MOSFET is switched on, its drain voltage will become negative with respect to ground as the inductor current continues to flow from Source-to-Drain. This negative voltage is proportional to output load current, inductor ripple current and MOSFET RDS<sub>ON</sub>.

Figure 6.

The larger the inductor current, the more negative VDS becomes. This is utilized for the detection of over current by passing a known fixed current source (200µA) through a resistor R<sub>CS</sub> which sets up an offset voltage such that when  $200\mu A \times R_{CS} = I_{DRAIN} \times RDS_{ON}$  the MIC2130/31's over current trigger is set. This disables the next high side gate drive pulse. After missing the high side pulse, the over current (OC) trigger is reset. If on the next low side drive cycle, the current is still too high i.e.,  $V_{CS}$  is  $\leq$  0V, another high side pulse is missed and so on. Thus reducing the overall energy transferred to the output and V<sub>OUT</sub> starts to fall. As this successive missing of pulses results in an effectively lower switching frequency, power inductor ripple currents can get very high if left unlimited. The MIC2130/31 therefore limits Duty Cycle during current limit to prevent currents building up in the power inductor and output capacitors.

#### **Current Limit Setting**

#### The Simple Method

$R_{CS} = I_{OUT} \times RDS_{ON(max)}/200 \mu A.$

#### Accurate Method

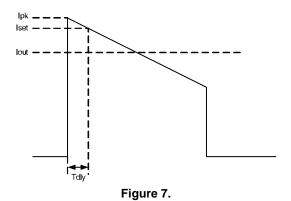

For designs where ripple current is significant when compared to  $I_{OUT}$ , or for low duty cycle operation, calculating the current setting resistor  $R_{CS}$  should take into account that one is sensing the peak inductor current and that there is a blanking delay of approximately 100ns.

$$I_{PK} = I_{OUT} + \frac{I_{RIPPLE}}{2}$$

$$I_{RIPPLE} = \frac{V_{OUT} \cdot (1 - D)}{F_{SWITCH} \cdot L}$$

$$I_{SET} = I_{PK} - \frac{V_{OUT} \cdot T_{DLY}}{L}$$

$$R_{CS} = \frac{I_{SET} \cdot RDS_{ON(max)}}{I_{CS(min)}}$$

D = Duty Cycle

F<sub>SWITCH</sub> = Switching Frequency

L = Power inductor value

$T_{DLY}$  = Current limit blanking time ~ 100ns

$I_{CS(min)} = 180 \mu A$

#### Example:

Consider a 12V to 3.3V @ 5A converter with 7.3 $\mu$ H power inductor and 93% efficiency at a 5A load and an LSD FET of RDS<sub>ON</sub> of 10m $\Omega$  (typical values).

$$D = \frac{V_{OUT}}{V_{IN} \cdot Efficiency}$$

$$I_{RIPPLE} = \frac{3.3 \cdot (1 - 0.306)}{150 kHz \cdot 7.3 \mu H} = 2.1A$$

$$I_{PK} = 5 + \frac{2.1}{2} = 6.05A$$

$$I_{SET} + 6.05 - \frac{3.3 \cdot 100 ns}{7.3 \mu H} = 6.00A$$

$$R_{CS} = \frac{6.00 \cdot 10 m\Omega}{180 \mu A} = 333\Omega \quad (332 \text{ std. value})$$

Using the simple method here would result in a current limit point lower than desired.

This equation sets the minimum current limit point of the converter, but maximum will depend upon the actual inductor value and  $RDS_{ON}$  of the MOSFET under current limit conditions. This could be in the region of 50% higher and should be considered to ensure that all the power components are within their thermal limits unless thermal protection is implemented separately.

#### HCL (MIC2131 only)

The high current limit (HCL) is a function of the MIC2131 only. It allows for twice the output load current (for a time T determined by the HCL cap) before the current limit comparator trips. During the time T, the current sense current source ( $200\mu$ A nominal) is increased to  $400\mu$ A.

$T = CHCL * 2/13\mu = CHCL * 153.85 *1e3$

Where CHCL is the cap at the HCL pin

#### **Frequency Dithering**

The MIC2131 has an additional useful feature. The switching frequency is dithered  $\pm 12\%$  in order to spread the frequency spectrum over a wider range to lower the EMI noise peaks generated by the switching components. A pseudo random generator is used to generate the  $\pm$ dithering which further reduces the EMI noise peaks.

#### Power Good Output

The power good output (PG) will go high only when output is above 90% of the nominal set output voltage.

#### **VDD Regulator**

The internal regulator provides a regulated 5V for supplying the analog circuit power (AV<sub>DD</sub>). V<sub>DD</sub> also powers the MOSFET drivers. V<sub>DD</sub> is designed to operate at input voltages down to 8V. The AV<sub>DD</sub> supply should be connected to V<sub>DD</sub> through an RC filter to provide decoupling of the switching noise generated by the MOSFET drivers taking large current pulses from the V<sub>DD</sub> regulator.

#### Gate Drivers

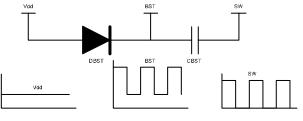

The MIC2130/31 is designed to drive both high side and low side N-Channel MOSFETs to enable high switching speeds with the lowest possible losses. The high side MOSFET gate driver is supplied by a bootstrap capacitor CBST connected at the SW pin and the BST pin. A high speed diode (a Schottky diode is recommended) between the V<sub>DD</sub> pin and BST pin is required as shown in Figure 8. This provides the high side MOSFET with a constant VGS drive voltage equal to V<sub>DD</sub> - V<sub>DIODE</sub>.

Figure 8.

When HSD goes high, this turns on the high side MOSFET and the SW node rises sharply. This is coupled through the bootstrap capacitor CBST and Diode DBST becomes reverse biased. The MOSFET Gate is held at  $V_{DD}$ - $V_{DIODE}$  above the Source for as long as CBST remains charged. This bias current of the High side driver is <10mA so a 0.1µF to1 µF is sufficient to hold the gate voltage with minimal droop for the power stroke (High side switching) cycle, i.e.  $\Delta$ BST = 10mA x 6µs / 0.1µF = 567mV. When the low side driver turns on every switching cycle, any lost charge from CBST is replaced via DBST as it becomes forward biased. Therefore minimum BST voltage is  $V_{DD}$  – 0.5V.

The Low side driver is supplied directly from  $V_{\text{DD}}$  at nominal 5V.

#### Adaptive Gate Drive

There is a period when both driver outputs are held off ('dead time') to prevent shoot through current flowing. Shoot through current flows if both MOSFETS are on momentarily as the same time and reduces efficiency and can destroy the FETs. This dead time must be kept to a minimum to reduce losses in the free wheeling diode which could either be an external Schottky diode placed across the lower MOSFET or the internal Schottky diode implemented in some MOSFETs. It is not recommended, for high current designs, to rely on the intrinsic body diode of the power MOSFET. These typically have large forward voltage drops and a slow reverse recovery characteristic which will add significant losses to the regulator. Dependant upon the MOSFETs used, the dead time could be required to be 150ns or 20ns. The MIC2130/31 solves this variability issue by using an adaptive gate-drive scheme.

When the High side driver is turned off, the inductor forces the voltage at the switching node (low side MOSFET drain) towards ground to keep current flowing. When the SW pin is detected to have reached 1V, the top MOSFET can be assumed to be off and the low side driver output is immediately turned on. There is also a short delay between the low side drive turning off and the high side driver turning on. This is fixed at ~80ns to allow for large gate charge MOSFETs to be used.

## **Application Information**

#### Passive Component Selection Guide

Transition losses in the power MOSFETs are not defined by inductor value. However, the inductor value is responsible for the ripple current which causes some of the resistive losses. These losses are proportional to  $I_{\text{RIPPLE}}^{2}$ . Minimizing inductor ripple current therefore reduces resistive losses and can be achieved by choosing a larger value inductor. This will generally improve efficiency by reducing the RMS current flowing in all of the power components. The actual value of inductance is really defined by space limitations, RMS rating (I<sub>RMS</sub>) and saturation current (I<sub>SAT</sub>) of available inductors. If we look at the newer flat wire inductors, these have higher saturation current ratings than the RMS current rating for lower values and as inductance value increases, these figures get closer in value. This mirrors what happens in the converter with ISAT analogous to the maximum peak switch current and IRMS analogous to output current. As inductance increases, so  $I_{SWITCHpk}$  tends towards  $I_{OUT}$ . This is a characteristic that makes these types of inductor optimal for use in high power buck converters such as MIC2130/31.

To determine the  $I_{SAT}$  and  $I_{RMS}$  rating of the inductor, we should start with a nominal value of ripple current. This should typically be no more than  $I_{OUT(max)}/2$  to minimize MOSFET losses due to ripple current mentioned earlier. Therefore:

$$L_{MIN} \sim 2 \frac{V_{O}}{I_{O} \cdot F_{SWITCH}} \cdot \left(1 - \frac{V_{O}}{V_{IN} \cdot Efficiency}\right)$$

$IL_{RMS} > 1.04 \text{ x } I_{OUT(max)}$

#### $IL_{SAT} > 1.25 \text{ x } I_{OUT(max)}$

Any value chosen above  $L_{\mbox{\scriptsize MIN}}$  will ensure these ratings are not exceeded.

In considering the actual value to choose, we need to look at the effect of ripple on the other components in the circuit. The chosen inductor value will have a ripple current of:

$$I_{RIPPLE} \sim \frac{(1-D)}{F_{SWITCH}} \cdot \frac{V_{OUT}}{L}$$

This value should ideally be kept to a minimum, within the cost and size constraints of the design, to reduce unnecessary heat dissipation.

#### **Output Capacitor Selection**

The output capacitor ( $C_{OUT}$ ) will have the full inductor ripple current IL<sub>RMS</sub> flowing through it. This creates the output switching noise which consists of two main components:

$$V_{OUTPK-PK} \approx \underbrace{I_{RIPPLE} \cdot ESR}_{\substack{ESR\\Noise}} + \underbrace{\frac{I_{RIPPLE} \cdot T_{ON}}{2 \cdot C_{OUT}}}_{\substack{Capacitor\\Noise}}$$

If therefore, the need is for low output voltage noise (e.g., in low output voltage converters),  $V_{OUT}$  ripple can be directly reduced by increasing inductor value, Output capacitor value or reducing ESR.

For tantalum capacitors, ESR is typically >40m $\Omega$  which usually makes loop stabilization easier by utilizing a pole-zero (type II) compensator.

Due to the many advantages of multi-layer ceramic capacitors, among them, cost, size, ripple rating and ESR, it can be useful to use these in many cases. However, one disadvantage is the CV product. This is lower than tantalum. A mixture of one tantalum and one ceramic can be a good compromise which can still utilize the simple type II compensator.

With ceramic output capacitors only, a double-pole, double-zero (type III) compensator is required to ensure system stability. Loop compensation is described in more detail later in the data sheet.

Ensure the RMS ripple current rating of the capacitor is above  $I_{RIPPLE} \cdot 0.6$  to improve reliability.

#### Input Capacitor Selection

The input filter needs to supply the load current when the high-FET is on and should to limit the ripple to the desire value. The  $C_{IN}$  ripple rating for a converter is typically  $I_{OUT}/2$  under worst case duty cycle conditions of 50%.

$$\mathsf{IRMS}_{\mathsf{CIN}} = I_{OUT} \times \sqrt{D \times (1 - D)}$$

Where  $D = V_{OUT} / (V_{IN} xeff)$

It is however, also important to closely decouple the Power MOSFETs with 2 x  $10\mu$ F Ceramic capacitors to reduce ringing and prevent noise related issues from causing problems in the layout of the regulator. The ripple rating of C<sub>IN</sub> may therefore be satisfied by these decoupling capacitors as they allow the use of perhaps one more ceramic or tantalum input capacitor at the input voltage node to decouple input noise and localize high di/dt signals to the regulator input.

#### Power MOSFET Selection

The MIC2130/31 drives N-channel MOSFETs in both the high-side and low-side positions. This is because the switching speed for a given  $RDS_{ON}$  in the N-Channel device is superior to the P-Channel device.

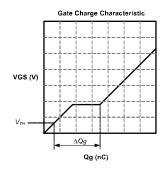

There are different criteria for choosing the high- and low-side MOSFETs and these differences are more significant at lower duty cycles such as 12V to 1.8V conversion. In such an application, the high-side MOSFET is required to switch as quickly as possible to minimize transition losses (power dissipated during rise and fall times). Whereas the low-side MOSFET can switch slower, but must handle larger RMS currents. When duty cycle approaches 50%, the current carrying capability of the upper MOSFET starts to become critical also and can sometimes require external high current drivers to achieve the necessary switching speeds.

MOSFET loss = Static loss + Transition loss

Static loss (Ps) =  $I_{FETRMS}^2 \times RDS_{ON}$

Transition loss (Pt) =  $I_{OUT} x$  (tr+tf) x  $V_{DSOFF} x F_{SWITCH}/2$

tr + tf = Rise time + Fall time

Due to the worst case driver currents of the MIC2130/31, the value of tr + tf simplifies to:

$tr + tf (ns) = \Delta Qg (nC)$

$\Delta$ Qg can be found in the MOSFET characteristic curves

V<sub>DSOFF</sub> = Voltage across MOSFET when it is off

$$I_{\text{FETRMS}} = \sqrt{D \cdot \frac{(I_{X}^{2} + I_{X} \cdot I_{Y} + I_{Y}^{2})}{3}}$$

$I_X = I_{OUT} - I_{RIPPLE}/2$

$I_{\rm Y} = I_{\rm OUT} + I_{\rm RIPPLE}/2$

| $D_{on} = T_{on} \times F_{switch}$  | high-side FET on time |

|--------------------------------------|-----------------------|

| $D_{off} = T_{ON} \times F_{SWITCH}$ | low-side FET on time  |

D\_on = D =  $V_0/(V_{IN} \times eff)$  since it changes depending on which MOSFET we are calculating losses for.

High-side FET  $T_{ON} = D_{ON}/F_{SWITCH}$

The lower MOSFET is not on for the whole time that the upper MOSFET is off due to the fixed 80ns high side driver delay. Therefore, there is an 80ns term subtracted from the lower FET on time equation.

Low-side FET  $T_{ON}$  = (1-D\_on)/F<sub>SWITCH</sub> - 80ns

There are many MOSFET packages available which have varying values of thermal resistance and can therefore dissipate more power if there is sufficient airflow or heat sink externally to remove the heat. However, for this exercise we can assume a maximum dissipation of 1.2W per MOSFET package. This can be altered if the final design has higher allowable package dissipation.

Look at lower MOSFET first:

Pdis\_max = 1.2 W = Ps + Pt

For the low side FET, Pt is small because  $\text{VDS}_{\text{OFF}}$  is clamped to the forward voltage drop of the Schottky diode. Therefore:

$RDS_{ON(max)} \sim 1.2/I_{FETRMS}^{2}$

Example: For 12V to 1.8V @ 10A

$RDS_{ON(max)} < 14m\Omega$

It is important to remember to use the  $RDS_{ON(max)}$  figure for the MOSFET at the maximum temperature to help prevent thermal runaway (as the temperature increases, the  $RDS_{ON}$  increases).

$\Delta Qg_{(max)}$  should be limited so that the low side MOSFET is off within the fixed 80ns delay before the high side driver turns on.

High side MOSFET:

For the high side FET, the losses should ideally be evenly spread between transition and static losses. Use the C of the  $V_{IN}$  range to balance the losses.

Pt = Pdis\_max/2 = 0.6 =  $I_{OUT} \times \Delta Qg \times V_{INMID} \times F_{SWITCH}/2$

$\Delta Qg_{(max)} < 0.6 \times 2 / (I_{OUT} \times V_{INMID} \times F_{SWITCH})$

RDSon is calculated similarly for the high side MOSFET:

$RDS_{ON(max)} \sim 0.6 / I_{FETRMS}^2$

Using previous example:

$\Delta Qg_{(max)} < 20nC$

$RDS_{ON(max)} < 35m\Omega$

Note that these are maximum values based upon thermal limits and are not targeted at the highest efficiency. Selection of lower values is recommended to achieve higher efficiency designs.

Limits to watch out for:

$Qg_{TOTAL} < 1500 \text{ nC/V}_{IN}$

Total of both high side and low side MOSFET Qg value at VGS = 5V for both channels.

Example: @ V<sub>IN(max)</sub> = 13.2V,

Qg<sub>TOTAL</sub> < 1500/13.2 = 114nC

$\Delta Qg_{LOW} < 120nC$

Maximum turn on gate charge for the low side MOSFET to ensure proper turn off before high side MOSFET is switched on.

# Control Loop Stability and Compensation

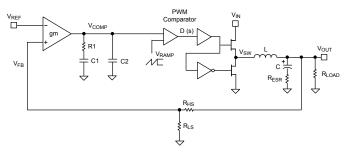

Figure 10 shows the simplified system schematic. The internal transconductance error amplifier is used for compensating the voltage feedback loop by placing a capacitor (C1) in series with a resistor (R1) and another capacitor C2 in parallel from the COMP pin-to-ground. (Note: Ceramic output caps may require type III compensation).

Figure 10 Simplified System Schematic

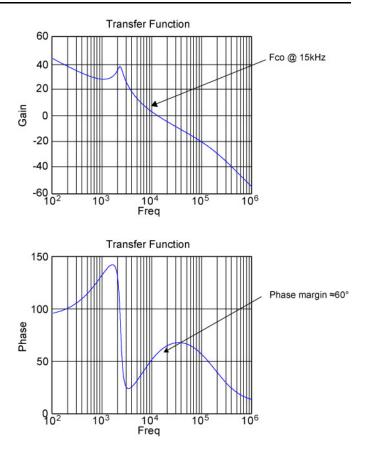

In order to have a stable system when the gain of  $T(s) = 1 \implies (0db)$  the phase has to be greater (less negative) than -180°. The amount the phase is greater than -180° is called the phase margin, typically 30 to 60 and is a key parameter predicting the stability of the system and how much overshoot and undershoot the system exhibits during transients.

The open loop transfer function is:

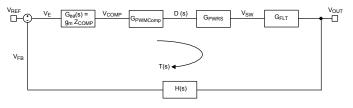

$$T(s) = G_{ea}(s) \times G_{PWMcomp}(s) \times G_{Pwrs}(s) \times G_{flt}(s) \times H_{fb}(s)$$

And the phase is:

$$\angle T(s) = \theta_{T}(s) = \theta_{ea} + \theta_{PWMcomp} + \theta_{PwrS} + \theta_{Flt} + \theta_{fb}$$

#### Figure 11 System Block Diagram

In the system block diagram in figure 11  $G_{ea}(s) = g_m \times Z_{comp}$  Gain of the Error amp where  $g_m = 1.5ms$  and

$$Z_{\text{comp}} = \left( R1 + \frac{1}{sC_1} \right) \left( \frac{1}{sC_2} \right)$$

$$G_{\text{PWMcomp}}(s) = \frac{\Delta D}{\Delta V_{\text{comp}}} = \frac{D_{\text{Max}}}{\Delta V_{\text{ramp}}} = \frac{0.85}{2.1 - 1.1} = 0.85$$

Gain of the PWM comparator

$$G_{P_{WrS}}(s) = \frac{\Delta V_{SW}}{\Delta d(s)} = \frac{V_{Out}}{\Delta d(s) * D} = \frac{V_{Out}}{D_{Max} * D}$$

Gain of the

Power Stage

$$G_{Flt}(s) = \frac{1 + sR_{esr}C_{out}}{1 + \frac{s}{Q\omega_0} + \frac{s^2}{\omega_0^2}}$$

Gain of the Filter

where:

$$Q = \frac{E_{stored}}{E_{Lost}} = \frac{R_{Load}}{\sqrt{L/C_{out}}} \quad \text{(Parallel loaded)}$$

and

$$\begin{split} \omega_{0} &= \frac{1}{\sqrt{LC_{out}}} \qquad F_{esr} = \frac{1}{2\pi R_{esr}C_{out}} \\ H(s) &= \frac{R_{LS}}{R_{LS} + R_{HS}} = \frac{V_{ref}}{V_{out}} \qquad \text{Gain of the feedback} \end{split}$$

network

For simplicity, combine the PWM comparator gain and the Power stage gain and call it the modulator gain.

$$\begin{split} G_{Mod}(s) &= G_{PWMcomp}(s) * G_{PWRsw}(s) \\ &= \frac{D_{Max}}{\Delta V_{ramp}} * \frac{V_{out}}{D * D_{Max}} = \frac{V_{out}}{\Delta V_{ramp} * D} \end{split} \quad \text{therefore;} \end{split}$$

$T(s) = G_{\text{ea}}(s) \mathrel{x} G_{\text{Mod}}(s) \mathrel{x} G_{\text{flt}}(s) \mathrel{x} H_{\text{fb}}(s) \ \text{and} \label{eq:tau}$

$$\boldsymbol{\theta}_{T}(s) = \boldsymbol{\theta}_{ea} + \boldsymbol{\theta}_{Mod} + \boldsymbol{\theta}_{flt} + \boldsymbol{\theta}_{fb}$$

The phase of the open loop is the phase of all the blocks in the loop added together.

The phase of T(s) is

$$\begin{split} \theta_{_{T}}(s) &= \theta_{_{ea}} + \theta_{_{PWMcomp}} + \theta_{_{PwrS}} + \theta_{_{Flt}} + \theta_{_{fb}} \\ \theta_{_{T}}(s) &= \theta_{_{ea}} + \theta_{_{Mod}} + \theta_{_{fb}} \end{split}$$

Where  $\theta_{ea} = -\theta_{pole0} + \theta_{Zero1} - \theta_{pole1}$

$\theta_{\rm pole0}$  = phase lag due to the pole at the origin

$\theta_{\text{Zerol}}$  =phase lead due to Zero1

$\theta_{\text{pole1}}$  = phase lag due to pole1

$$\begin{split} \theta_{\rm PWMcomp} &= 0^\circ\,, \qquad \theta_{\rm PwrS} = 0^\circ \qquad \theta_{\rm fb} = 0^\circ \qquad \text{therefore;}\\ \theta_{\rm Mod} &= 0^\circ \end{split}$$

The phase of the filter includes the complex poles of LC and the Zero caused by the ESR of the  $C_{OUT}$ .

The filter has 2 poles at  $\,F_{\scriptscriptstyle 0}\,$  and a zero at  $\,F_{\scriptscriptstyle esr}\,$

$\theta_{\rm Flt} = -180^\circ\,{\rm at}\,\,F_0$  and +90° at  $F_{\it esr}$

$V_{IN}$  = 24V;  $V_{OUT}$  = 3.3V;  $I_{OUT}$  = 10A; L = 7.3µH;  $C_{OUT}$  = 660µF; Resr = 40mΩ; Fsw = 150KHz

The gain and phase of the modulator and filter is:  $G_{\mbox{\scriptsize Mod}}(s) \mathrel{x} G_{\mbox{\scriptsize fit}}(s)$

This is the gain  $\frac{V_{\rm OUT}}{V_{\rm comp}}$  (s)  $\,$  in Figure 12  $\,$

A computer generated plot of  $G_{Mod}(s) \ge G_{fit}(s)$  is shown in Figure 12.

Figure 12. Modulator Transfer Function

There is a -180° phase change near  $F_{0.}$  At frequencies greater then  $F_{0}$  the phase increases towards -90° due to the zero of  $F_{esr}$ . The phase effects of poles and zeros start a decade below and finish a decade above the frequency of a pole or zero. Therefore, at the frequency of a pole or zero the phase effect is only half of the final value. At the complex pole 2.3kHz the phase is -90 and would be -180 at 23kHz if not for the +90 phase lead of the zero at around 6kHz due to the esr of the filter capacitors. (Actually, the phase gain plots reach their final values asymptotically).

By inspecting Figure 12 the DC and low frequency gain of  $G_{Mod}$  = 20Log(0.85 x 24) = 26.2db;  $F_0$  = 2.3kHz;  $F_{esr}$  = 6kHz and Q is 13.6db.

The peak Gain equals the low freq gain plus the Q = 26.2 + 13.6 = 39.9db.

It is desired that T(s) (the open loop transfer function) have a cross over frequency (Fco) of 1/10 the Switching frequency at 15kHz. It is require that  $\angle T(j2\pi Fco)$  (the phase of T(s) at Fco), to be greater than -180° by at least the phase margin. By inspecting the Gain plot of G<sub>Mod</sub>(s) at 15kHz, G<sub>Mod</sub>(s) has a gain of about 3.9db.

Therefore, to make  $T(j2\pi Fco) = 1 \rightarrow 0db$ ;

$T(s) = G_{ea}(s) \times G_{Mod}(s) \times H_{fb}(s) = 1$  at Fco

$\mathrm{H_{fb}} = \mathrm{Vref}/\mathrm{Vout} = 0.7/3.3 = 0.212 \rightarrow -13.5 \mathrm{db}$

$|G_{ea}|_{db} = |T|_{db} - |G_{Mod}|_{db} - |H_{fb}|_{db} = 0-3.9db - (-13.5db) = 9.6db =>3.02$  The error amp needs 9db of gain at Fco.

Therefore  $g_m \times Z_{Comp} = 3.02$  at 15kHz.

The location of the error amp's zero and poles are selected in order to achieve the desired phase margin of T(s). For the maximum phase boost at the cross over Frequency (Fco), place the first Zero1 of the EA at Fco/10 since the effect of its phase boost will be at the maximum at Fco. Likewise, place the pole of the EA at least 10 x Fco so the effects of its phase lag will be at a minimum at Fco. Therefore, use R1 = 2k; C1 =  $0.068\mu$ F; C2 = 470pF.

#### g<sub>m</sub> Error Amplifier

Usually, it is undesirable to have high error amplifier gain at high frequencies otherwise high frequency noise spikes at large amplitude would be present at the output. Hence, gain should be permitted to fall off at high frequencies. At low frequency, it is desired to have high open-loop gain to attenuate the power line ripple. Thus, the error amplifier gain should be allowed to increase rapidly at low frequencies.

The transfer function for the internal gm error amplifier with R1, C1, and C2 at the comp pin is given by the following equation:

$$G_{ea}(s) = g_m \cdot \left[ \frac{1 + R1 \cdot s \cdot C1}{s \cdot (C1 + C2) \cdot \left(1 + R1 \cdot \frac{C1 \cdot C2 \cdot s}{C1 \cdot C2}\right)} \right]$$

The above equation can be simplified by assuming C2<C1,

$$G_{ea}(s) = g_m \cdot \left[\frac{1 + R1 \cdot s \cdot C1}{s \cdot (C1) \cdot (1 + R1 \cdot C2 \cdot s)}\right]$$

From the above transfer function, one can see that R1 and C1 introduce a zero and R1 and C2 a pole at the following frequencies:

$$\begin{split} F_{zero1} &= 1/2 \ \pi \times R1 \times C1 \ \ F_{pole1} = 1/2 \ \pi \times C2 \times R1 \\ F_{pole@origin} &= 1/2 \ \pi \times C1 \end{split}$$

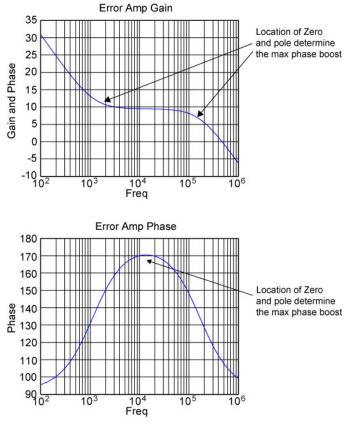

Figure 14 shows the gain and phase curves for the above transfer function with R1 = 2k, C1 =  $0.068\mu$ F, C2 = 470pF, and gm =  $0.0015\Omega$ -1. It can be seen that at 15kHz, the error amplifier exhibits approximately 9.6db of gain and 170° of phase. Figure 13 shows the open loop transfer function T(s) with these compensation values. It has a cross over frequency of 15KHz and phase margin of 60°.

Figure 13. Error Amp Gain and Phase

## **Package Information**

EXPOSED PAD

16-Pin 4mm x 4mm MLF<sup>®</sup> (ML)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2007 Micrel, Incorporated.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Switching Controllers category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

LV5065VB-TLM-H LV5066V-TLM-H LV5725JAZ-AH 633888R MP2908AGF AZ7500EP-E1 NCP1012AP133G NCP1217P133G NCP1218AD65R2G NCP1234AD100R2G NCP1244BD065R2G NCP1336ADR2G NCP1587GDR2G NCP6153MNTWG NCP81005MNTWG NCP81101BMNTXG NCP81205MNTXG HV9123NG-G-M934 IR35207MTRPBF ISL6367HIRZ CAT874-80ULGT3 SJ6522AG SJE6600 TLE63893GV50XUMA1 IR35215MTRPBF SG3845DM NCP1216P133G NCP1236DD65R2G NCP1247BD100R2G NCP1250BP65G NCP4202MNR2G NCP4204MNTXG NCP6132AMNR2G NCP81141MNTXG NCP81142MNTXG NCP81172MNTXG NCP81203MNTXG NCP81206MNTXG NX2155HCUPTR UC3845ADM UBA2051C IR35201MTRPBF MAX8778ETJ+ MAX17500AAUB+T MAX17411GTM+T MAX16933ATIR/V+ NCP1010AP130G NCP1063AD100R2G NCP1216AP133G NCP1217AP100G