# DELKIN DEVICES.

## **High Performance SLC Industrial CompactFlash**

## **Engineering Specification**

**Document Number L5006**

**Revision: A**

No part of this document may be reproduced, copied, recorded, stored in a retrieval system, or transmitted in any form without the written permission of Delkin Devices. This document is for informational use only and is subject to change without prior notice. Delkin Devices assumes no responsibility for any errors that may appear in this document.

## **Table of Contents**

| 1.0  | Product Overview                                                          | ε  |

|------|---------------------------------------------------------------------------|----|

| 1.1  | Part Numbers                                                              | 8  |

| 1.2  | Mechanical Specifications                                                 | 9  |

| 1.3  | Dimensions                                                                | 9  |

| 2.0  | Product Specifications                                                    | 10 |

| 2.1  | System Performance                                                        |    |

| 2.2  | Reliability                                                               | 10 |

| 2.3  | Environmental Specifications                                              |    |

| 2.4  | CHS Parameters                                                            | 10 |

| 3.0  | CF Card Interface                                                         | 11 |

| 3.1  | Card Pin Assignment                                                       | 11 |

| 3.2  | Card Pin Explanation                                                      | 12 |

| 4.0  | Electrical Interface                                                      | 18 |

| 4.1  | Absolute Maximum Conditions                                               | 18 |

| 4.2  | Input Power                                                               | 18 |

| 4.3  | Input Leakage Current                                                     | 18 |

| 4.4  | Input Characteristics                                                     | 19 |

| 4.5  | Output Drive Type                                                         | 19 |

| 4.6  | Output Drive Characteristics                                              | 19 |

| 4.7  | Interface/Bus Timing                                                      | 19 |

| 4.8  | Attribute Memory Read Timing                                              | 20 |

| 4.9  | Configuration Register (Attribute Memory) Write Timing                    | 21 |

| 4.10 | Common Memory Read Timing                                                 | 22 |

| 4.11 | 1 Common Memory Write Timing                                              | 23 |

| 4.12 | 2 I/O Input (Read) Timing                                                 | 24 |

| 4.13 | 3 I/O Input (Write) Timing                                                | 25 |

| 4.14 | 4 True IDE PIO Mode Read/Write Timing                                     | 26 |

| 4.15 | 5 True IDE Multiword DMA Mode Read/Write Timing                           | 28 |

| 5.0  | Card Configuration                                                        | 30 |

| 5.1  | Delkin Card Configuration                                                 | 30 |

| 5.2  | Attribute Memory Function                                                 | 32 |

| 5.3  | Configuration Option Register (Address 200H in Attribute Memory)          | 33 |

| 5.4  | Card Configuration and Status Register (Address 200H in Attribute Memory) | 34 |

| 5.5  | Pin Replacement Register (Address 200H in Attribute Memory)               |    |

| 5.6  | Socket and Copy Register (Address 200H in Attribute Memory)               | 36 |

| 6.0  | Transfer Functions                                                        | 37 |

| 6.1  | Input/Output                                                              | 37 |

| 6.2  | Common Memory                                                             |    |

| 6.3  | True IDE Mode I/O                                                         | 38 |

| 7.0  | Software Interface                                                        | 40 |

| 7.1  | CF-ATA Drive Register Set Definition and Protocol                         |    |

|      |                                                                           |    |

| 7.2        |          | nary and Secondary Address Configurations                                        |    |

|------------|----------|----------------------------------------------------------------------------------|----|

| 7.3        | •        | ous I/O Mapped Addressing                                                        |    |

| 7.4        |          | / Mapped Addressing                                                              |    |

| 7.5        |          | E Mode Addressing                                                                |    |

| 7.6<br>7.6 |          | \ Registersta Register (Address – 1F0H[170H];Offset 0,8,9)                       |    |

| 7.6        |          | or Register (Address – 1701 [1701]; Offset 1, 0DH Read Only)                     |    |

| 7.6        |          | ature Register (Address – 1F1H[171H]; Offset 1, 0DH Write Only)                  |    |

| 7.6        |          | ctor Number (LBA 7-0) Register (Address – 1F3H[173H]; Offset 3)                  |    |

| 7.6        |          | linder Low (LBA 15-8) Register (Address – 1F4H[174H]; Offset 4)                  |    |

| 7.6        | .6 Cy    | linder High (LBA 23-16) Register (Address – 1F5H[175H]; Offset 5)                | 47 |

| 7.6        |          | ve/Head (LBA 27-24) Register (Address 1F6H[176H]; Offset 6)                      |    |

| 7.6        |          | ve/Head (LBA 27-24) Register (Address 1F6H[176H]; Offset 6)                      |    |

| 7.6        |          | atus & Alternate Status Registers (Address 1F7H[177H]&3F6H[376H]; Offsets 7 & E) |    |

| 7.6        |          | vice Control Register (Address – 3F6H[376H]; Offset E)                           |    |

| 7.6        |          | rd (Drive) Address Register (Address – 3F7H[377H]; Offset F)                     |    |

| 7.7<br>7.7 |          | A Command Description                                                            |    |

| 7.7<br>7.7 |          | eck Power Mode – 98H or E5H                                                      |    |

| 7.7        |          | ecute Drive Diagnostics – 90H                                                    |    |

| 7.7        |          | ase Sector(s) – C0H                                                              |    |

| 7.7        |          | ish Cache – E7h                                                                  |    |

| 7.7        |          | rmat Track – 50H                                                                 |    |

| 7.7        | .7 Ide   | entify Drive - ECH                                                               | 57 |

| -          | 7.7.7.1  | General Configuration                                                            | 59 |

| -          | 7.7.7.2  | Default Number of Cylinders                                                      | 59 |

| -          | 7.7.7.3  | Default Number of Heads                                                          | 59 |

| -          | 7.7.7.4  | Default Number of Sectors per Track                                              | 59 |

| -          | 7.7.7.5  | Number of Sectors per Card                                                       | 59 |

| -          | 7.7.7.6  | Serial Number                                                                    | 59 |

| -          | 7.7.7.7  | ECC Count                                                                        | 59 |

| -          | 7.7.7.8  | Firmware Revision                                                                | 59 |

| -          | 7.7.7.9  | Model Number                                                                     | 60 |

| -          | 7.7.7.10 | Read/Write Multiple Sector Count                                                 | 60 |

| -          | 7.7.7.11 | Capabilities                                                                     | 60 |

| -          | 7.7.7.12 | PIO Data transfer Cycle Timing Mode                                              | 60 |

| -          | 7.7.7.13 | Translation Parameters Valid                                                     | 60 |

| -          | 7.7.7.14 | Current Number of Cylinders, Heads, Sectors/Track                                | 60 |

| -          | 7.7.7.15 | Current Capacity                                                                 | 60 |

| -          | 7.7.7.16 | Multiple Sector Setting                                                          | 60 |

| -          | 7.7.7.17 | Total Sectors Addressable in LBA Mode                                            | 61 |

| -          | 7.7.7.18 | Multiword DMA transfer                                                           | 61 |

| -          | 7.7.7.19 | Advanced PIO transfer modes supported                                            | 61 |

|     | 7.7.7         | 7.20 Minimum Multiword DMA transfer cycle time                 | 61 |

|-----|---------------|----------------------------------------------------------------|----|

|     | 7.7.7         | 7.21 Recommended Multiword DMA transfer cycle time             | 62 |

|     | 7.7.7         | .22 Minimum PIO transfer cycle time without flow control       | 62 |

|     | 7.7.7         | .23 Minimum PIO transfer cycle time with IORDY                 | 62 |

|     | 7.7.7         |                                                                |    |

|     | 7.7.8         | Idle – 97H or E3H                                              |    |

|     | 7.7.9         | Idle Immediate – 95H or E1H                                    |    |

|     | 7.7.10        | Initialize Drive Parameters – 91H                              |    |

|     | 7.7.11        | Key Management Structure Read – B9h (Feature: 0-127)           | 65 |

|     | 7.7.12        | Key Management Read Keying Material - B9h (Feature: 80)        | 65 |

|     | 7.7.13        | Key Management Change Key Management Value – B9h (Feature: 81) | 66 |

|     | 7.7.14        | NOP - 00h                                                      | 67 |

|     | 7.7.15        | Read Buffer – E4H                                              | 67 |

|     | 7.7.16        | Read DMA – C8h                                                 | 68 |

|     | 7.7.17        | Read Long Sector - 22h or 23h                                  | 69 |

|     | 7.7.18        | Read Multiple – C4H                                            | 69 |

|     | 7.7.19        | Read Sector(s) – 20H or 21H                                    | 71 |

|     | 7.7.20        | Read Verify Sector(s) – 40H or 41H                             |    |

|     | 7.7.21        | Recalibrate – 1XH                                              |    |

|     | 7.7.22        | Request Sense – 03H                                            | 72 |

|     | 7.7.23        | Security Disable Password - F6h                                | 74 |

|     | 7.7.24        | Security Erase Prepare - F3h                                   |    |

|     | 7.7.25        | Security Erase Unit - F4h                                      |    |

|     | 7.7.26        | Security Freeze Lock - F5h                                     |    |

|     | 7.7.27        | Security Set Password - F1h                                    |    |

|     | 7.7.28        | Security Unlock - F2h                                          |    |

|     | 7.7.29        | Seek – 7XH                                                     |    |

|     | 7.7.30        | Set Feature – EFH                                              |    |

|     | 7.7.31        | Set Multiple Mode – C6H                                        |    |

|     | 7.7.32        | Set Sleep Mode – 99H or E6H                                    |    |

|     | 7.7.33        | Standby – 96H or E2H                                           |    |

|     | 7.7.34        | Standby – 94H or E0H                                           |    |

|     | 7.7.35        | Translate Sector – 87H                                         |    |

|     | 7.7.36        | Wear Level – F5H                                               |    |

|     | 7.7.37        | Write Buffer – E8H                                             |    |

|     | 7.7.38        | Write DMA – CAh                                                |    |

|     | 7.7.39        | Write Long Sector – 32H or 33H                                 |    |

|     | 7.7.40        | Write Multiple Command – C5H                                   |    |

|     | 7.7.41        | Write Multiple without Erase – CDH                             |    |

|     | 7.7.42        | Write Sector(s) – 30H or 31H                                   |    |

|     | 7.7.43        | Write Verify 3CH                                               |    |

|     | 7.7.44<br>Err | Write Verify – 3CHor Posting                                   |    |

| 7.8 |               |                                                                |    |

| 8.0 |               | paring CF-ATA to PC Card-ATA and True IDE                      |    |

| 8.′ | 1 Ele         | ectrical Differences                                           | 92 |

| High Perfe | ormance SLC Industrial CompactFlash                              | L5006 Rev. A |

|------------|------------------------------------------------------------------|--------------|

| 8.1.1      |                                                                  |              |

| 8.1.2      | Pull Up Resistor Input Leakage Current                           | 92           |

| 8.2        | Functional Differences                                           |              |

| 8.2.1      |                                                                  |              |

| 8.2.2      |                                                                  |              |

| 8.2.3      |                                                                  |              |

| 8.2.4      | Recovery from Sleep Mode                                         | 93           |

| Table      | of Figures                                                       |              |

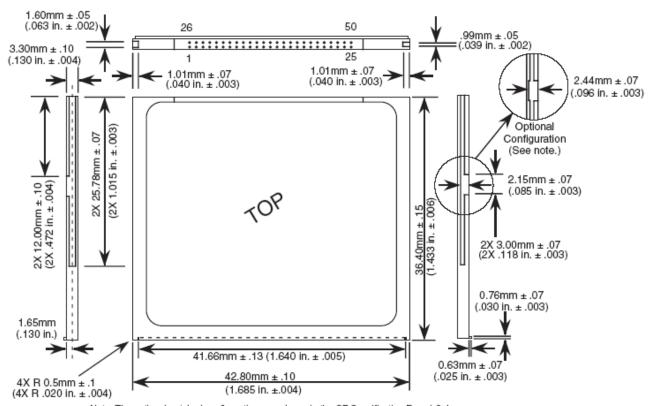

| Figure 1   | . CF Card Dimensions                                             | 9            |

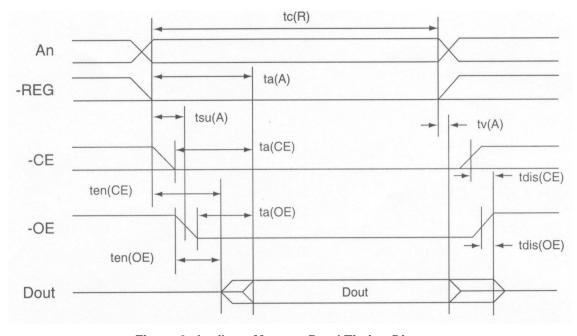

| Figure 2   | . Attribute Memory Read Timing Diagram                           | 20           |

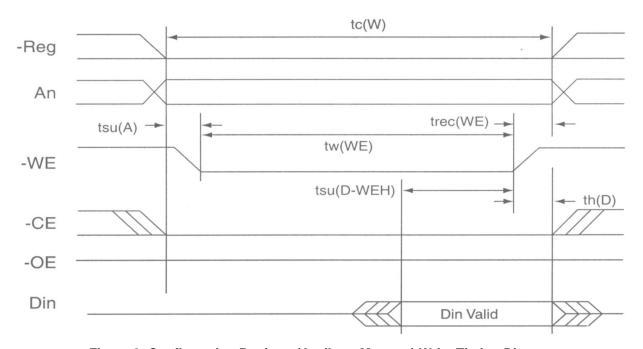

| Figure 3   | . Configuration Register (Attribute Memory) Write Timing Diagram | 21           |

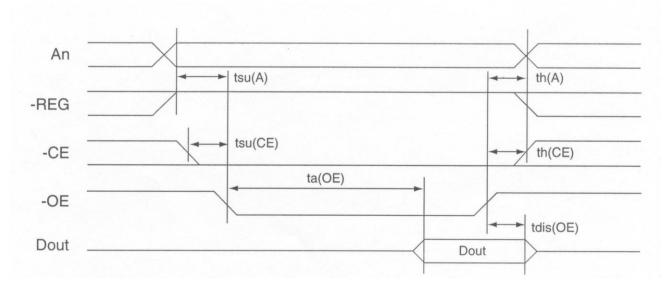

| Figure 4   | . Common Memory Read Timing Diagram                              | 22           |

| Figure 5   | . Common Memory Write Timing Diagram                             | 23           |

| Figure 6   | . I/O read Timing Diagram                                        | 24           |

| Figure 7   | . I/O Write Timing Diagram                                       | 25           |

| Figure 8   | . True IDE PIO Mode Read/Write Timing Diagram                    | 27           |

| Figure 9   | . True IDE Multiword DMA Mode Read/Write Timing Diagram          | 29           |

#### 1.0 Product Overview

Delkin's *High Performance Industrial Temperature CompactFlash* memory cards feature significant performance upgrades for industrial applications. These cards have superior features such as:

- Global Wear Leveling

- ECC error correction 15 bit / 512 Byte

- Up to 95 MB/sec sustained write speed\*

- Industrial temperature (-40 to 85°C) operating range

- Compliant with CompactFlash Specification Rev. 4.1, Type 1, and ATA/ATAPI-7

- Operating modes Memory, PCMCIA I/O, True IDE (PIO6 & DMA4) IDE UDMA6, PCMCIA UDMA6

- Compliant with European Union Directive 2002/95/EC (RoHS)

- Shock: 40g's at 11ms, MIL-STD-810, Method 516.6

- Vibration: 15Hz to 2,000Hz, MIL-STD-810, Method 514.5

- Humidity: 95% R-H, MIL-STD-810, Method 507.4

- Altitude: 80,000 feet

- Capacities supported: 4GB, 8GB, 16GB, 32 GB & 64 GB (Other capacities available upon request.)

- NAND Single Level Cell flash (SLC)

- Supports 3.3-Volt and 5-Volt operation

- Fixed Drive available

- Solid State no moving parts

- Ultrasonic welded case No press fit components

- Available upon request Custom CIS, mechanical features, labels and packaging

- All capacity configurations are available with proprietary conformal coating

<sup>\*</sup>Dependent on host configuration and testing equipment.

The High Performance SLC Industrial CompactFlash cards are manufactured in the USA at our own facilities in Poway, California. The cards are supported by Delkin's locked-down Bill of Materials that ensures consistent product performance and future compatibility. Delkin's Industrial line of CompactFlash is the perfect solution for enterprises demanding specific higher qualitative and performance functions in a widely accepted, time-tested form factor.

#### **Applications:**

Industrial Computers

• Flight Systems

Agriculture

• Embedded Systems

Manufacturing

Gaming

Data Acquisition

Military

Automotive

Telecommunications

#### **Optional Conformal Coating**

Delkin's proprietary conformal coating defends data integrity in harsh environments. Delkin utilizes a low-viscosity silicon elastomer that thoroughly covers exposed board and component surfaces with a protective coating. This process shields memory electronics from moisture and contamination, preventing metal corrosion and insulating conductors against electrical leakage. The coating also ruggedizes devices against the vibration, shock, and thermal stress of severe-service applications. Conformal coating is available as an option for Delkin industrial flash memory products in many form factors, including solid state drives, CompactFlash, Secure Digital, removable and embedded USB, PCMCIA, and mSATA.

#### 1.1 Part Numbers

Delkin Devices High Performance SLC Industrial CompactFlash cards are available in the following Configurations:

| Capacity * | Configuration        | Part Number       |  |

|------------|----------------------|-------------------|--|

|            | Fixed Drive, DMA ON  | CE04TFHVA-FD000-D |  |

| 4.00       | Fixed Drive, DMA OFF | CE04TFHVA-F1000-D |  |

| 4 GB       | Removable, DMA ON    | CE04TFHVA-XX000-D |  |

|            | Removable DMA, OFF   | CE04TFHVA-X1000-D |  |

|            | Fixed Drive, DMA ON  | CE08TFNVA-FD000-D |  |

| 0.00       | Fixed Drive, DMA OFF | CE08TFNVA-F1000-D |  |

| 8 GB       | Removable, DMA ON    | CE08TFNVA-XX000-D |  |

|            | Removable DMA, OFF   | CE08TFNVA-X1000-D |  |

|            | Fixed Drive, DMA ON  | CE16TFPVA-FD000-D |  |

| 40 OD      | Fixed Drive, DMA OFF | CE16TFPVA-F1000-D |  |

| 16 GB      | Removable, DMA ON    | CE16TFPVA-XX000-D |  |

|            | Removable DMA, OFF   | CE16TFPVA-X1000-D |  |

|            | Fixed Drive, DMA ON  | CE32MGGVA-FD000-D |  |

| 00 OD      | Fixed Drive, DMA OFF | CE32MGGVA-F1000-D |  |

| 32 GB      | Removable, DMA ON    | CE32MGGVA-XX000-D |  |

|            | Removable DMA, OFF   | CE32MGGVA-X1000-D |  |

|            | Fixed Drive, DMA ON  | CE64MGMVA-FD000-D |  |

| C4 CD      | Fixed Drive, DMA OFF | CE64MGMVA-F1000-D |  |

| 64 GB      | Removable, DMA ON    | CE64MGMVA-XX000-D |  |

|            | Removable DMA, OFF   | CE64MGMVA-X1000-D |  |

#### **Notes:**

• To add optional Conformal Coating, change the 000 in the part number to 050.

The CompactFlash cards are manufactured at our facilities in Poway, California USA. Many custom configurations are available including custom CIS, mechanical features, labels and packaging.

<sup>\*</sup> Note: Usable capacities are within 10% of the gross capacity figures shown above, as is typical with all NAND flash devices, as a small portion of the total is needed for controller firmware and spare block reserves.

## 1.2 Mechanical Specifications

Delkin Devices High Performance SLC Industrial cards are Type I CompactFlash cards.

#### 1.3 Dimensions

| Length:                            | 36.4 ± 0.15 mm (1.433 ±.006 in.)                                 |

|------------------------------------|------------------------------------------------------------------|

| Width:                             | 42.80 ± 0.10 mm (1.685 ±.004 in.)                                |

| Thickness Including<br>Label Area: | $3.3 \text{ mm} \pm 0.10 \text{ mm} (.130 \pm .004 \text{ in.})$ |

| Weight:                            | 12.0 g typical                                                   |

Note: The optional notched configuration was shown in the CF Specification Rev. 1.0. In specification Rev. 1.2, the notch was removed for ease of tooling. This optional configuration can be used but it is not recommended.

Figure 1. CF Card Dimensions

## 2.0 Product Specifications

#### 2.1 System Performance

| Parameter          | Value          |  |

|--------------------|----------------|--|

| Data Transfer Rate | Up to 105 MB/s |  |

| Sustained Read     | Up to 105 MB/s |  |

| Sustained Write    | Up to 95 MB/s  |  |

Note: All values dependent on configuration and testing environment.

#### 2.2 Reliability

| Parameter            | Value                   |  |

|----------------------|-------------------------|--|

| Cycle Endurance**    | Up to 2,000,000 cycles  |  |

| MTBF***              | Up to 2,000,000 hours   |  |

| Data Retention       | 10 Years                |  |

| Connector Durability | 10,000 insertion cycles |  |

<sup>\*\*</sup> Dependent on configuration, write size, etc. Contact Delkin for endurance calculation based on specific card configuration and application workload.

#### 2.3 Environmental Specifications

| Features                         | Operating                                  |

|----------------------------------|--------------------------------------------|

| Storage Temperature              | -50 ~ 100°C                                |

| Industrial Operating Temperature | -40 ~ 85°C                                 |

| Humidity                         | 5% – 95% RH, non-condensing                |

| Vibration                        | 15Hz to 2000Hz (MIL-STD-810, Method 514.5) |

| Shock                            | 40g's at 11ms                              |

| Altitude                         | 80,000 feet max.                           |

#### 2.4 CHS Parameters\*\*\*

| Capacity | Cylinders | Heads | Sectors/Track |

|----------|-----------|-------|---------------|

| 4GB      | 7785      | 16    | 63            |

| 8GB      | 15538     | 16    | 63            |

| 16GB     | 31045     | 16    | 63            |

| 32GB     | 62041     | 16    | 63            |

| 64GB     | 65535     | 16    | 63            |

<sup>\*\*\*</sup>Custom CHS settings available. Contact Delkin for more information.

<sup>\*\*\*</sup> Dependent on configuration, testing environment and operating temperature.

## 3.0 CF Card Interface

## 3.1 Card Pin Assignment

|         | Memory card mode |     | I/O card mode |     | True IDE mode |     |

|---------|------------------|-----|---------------|-----|---------------|-----|

| Pin No. | Signal Name      | I/O | Signal Name   | I/O | Signal Name   | I/O |

| 1       | GND              | _   | GND           | _   | GND           | _   |

| 2       | D3               | I/O | D3            | I/O | D3            | I/O |

| 3       | D4               | I/O | D4            | I/O | D4            | I/O |

| 4       | D5               | I/O | D5            | I/O | D5            | I/O |

| 5       | D6               | I/O | D6            | I/O | D6            | I/O |

| 6       | D7               | I/O | D7            | I/O | D7            | I/O |

| 7       | -CE1             | I   | -CE1          | I   | -CS0          | I   |

| 8       | A10              | I   | A10           | 1   | A10           | I   |

| 9       | -OE              | I   | -OE           | 1   | -ATASEL       | I   |

| 10      | A9               | I   | A9            | I   | A9            | I   |

| 11      | A8               | I   | A8            | 1   | A8            | I   |

| 12      | A7               | I   | A7            | I   | A7            | I   |

| 13      | Vcc              | _   | Vcc           | _   | Vcc           | _   |

| 14      | A6               | I   | A6            | I   | A6            | I   |

| 15      | A5               | I   | A5            | I   | A5            | I   |

| 16      | A4               | I   | A4            | I   | A4            | I   |

| 17      | A3               | I   | A3            | I   | A3            | I   |

| 18      | A2               | I   | A2            | I   | A2            | I   |

| 19      | A1               | I   | A1            | 1   | A1            | 1   |

| 20      | A0               | I   | A0            | I   | A0            | I   |

| 21      | D0               | I/O | D0            | I/O | D0            | I/O |

| 22      | D1               | I/O | D1            | I/O | D1            | I/O |

| 23      | D2               | I/O | D2            | I/O | D2            | I/O |

| 24      | WP               | 0   | -IOIS16       | 0   | -IOCS16       | 0   |

| 25      | -CD2             | 0   | -CD2          | 0   | -CD2          | 0   |

| 26      | -CD1             | 0   | -CD1          | 0   | -CD1          | 0   |

| 27      | D11              | I/O | D11           | I/O | D11           | I/O |

| 28      | D12              | I/O | D12           | I/O | D12           | I/O |

|         | Memory card mode |     | I/O card mode |     | True IDE mode |     |

|---------|------------------|-----|---------------|-----|---------------|-----|

| Pin No. | Signal Name      | I/O | Signal Name   | I/O | Signal Name   | I/O |

| 29      | D13              | I/O | D13           | I/O | D13           | I/O |

| 30      | D14              | I/O | D14           | I/O | D14           | I/O |

| 31      | D15              | I/O | D15           | I/O | D15           | I/O |

| 32      | -CE2             | 1   | -CE2          | I   | -CS1          | I   |

| 33      | -VS1             | 0   | -VS1          | 0   | -VS1          | 0   |

| 34      | -IORD            | 1   | -IORD         | 1   | -IORD         | I   |

| 35      | -IOWR            | I   | -IOWR         | I   | -IOWR         | I   |

| 36      | -WE              | 1   | -WE           | I   | -WE           | 1   |

| 37      | RDY/-BSY         | 0   | -IREQ         | 0   | INTRQ         | 0   |

| 38      | Vcc              | _   | Vcc           | _   | Vcc           | _   |

| 39      | -CSEL            | 1   | -CSEL         | 1   | -CSEL         | I   |

| 40      | -VS2             | 0   | -VS2          | 0   | -VS2          | 0   |

| 41      | RESET            | 1   | RESET         | 1   | -RESET        | 1   |

| 42      | -WAIT            | 0   | -WAIT         | 0   | IORDY         | 0   |

| 43      | -INPACK          | 0   | -INPACK       | 0   | DMARQ         | 0   |

| 44      | -REG             | 1   | -REG          | 1   | -DMACK        | 1   |

| 45      | BVD2             | I/O | -SPKR         | I/O | -DASP         | I/O |

| 46      | BVD1             | I/O | -STSCHG       | I/O | -PDIAG        | I/O |

| 47      | D8               | I/O | D8            | I/O | D8            | I/O |

| 48      | D9               | I/O | D9            | I/O | D9            | I/O |

| 49      | D10              | I/O | D10           | I/O | D10           | I/O |

| 50      | GND              | _   | GND           |     | GND           |     |

## 3.2 Card Pin Explanation

| Signal Name                                                      | Direction | Pin Number                                        | Description                                         |

|------------------------------------------------------------------|-----------|---------------------------------------------------|-----------------------------------------------------|

| A10 to A0 (PC Card Memory mode)  A10 to A0 (PC Card Memory mode) | I         | 8, 10, 11,<br>12, 14,15,<br>16, 17, 18,<br>19, 20 | Address bus is A10 to A0. A10 is MSB and A0 is LSB. |

| Signal Name                                                                                                 | Direction | Pin Number    | Description                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------|-----------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2 to A0<br>(True IDE mode)                                                                                 |           | 18, 19,<br>20 | Address bus is A10 to A0. Only A2 to A0 are used, A10 to A3 should be grounded by the host.                                                                  |

| BVD1<br>(PC Card Memory<br>mode)                                                                            |           |               | BVD1 outputs the battery voltage status in the card. This output line is constantly driven to a high state since a battery is not required for this product. |

| -STSCHG<br>(PC Card I/O mode)                                                                               | ode)      |               | -STSCHG is used for changing the status of Configuration and status register in attribute area.                                                              |

| -PDIAG<br>(True IDE mode)                                                                                   |           |               | -PDIAG is the Pass Diagnostic signal in Master/Slave handshake protocol.                                                                                     |

| BVD2<br>(PC Card Memory<br>mode)                                                                            |           |               | BVD2 outputs the battery voltage status in the card. This output line is constantly driven to a high state since a battery is not required for this product. |

| -SPKR<br>(PC Card I/O mode)                                                                                 | I/O       | 45            | -SPKR outputs speaker signals. This output line is constantly driven to a high state since this product does not support the audio function.                 |

| -DASP<br>(True IDE mode)                                                                                    |           |               | -DASP is the Disk Active/Slave<br>Present signal in the Master/Slave<br>handshake protocol.                                                                  |

| -CD1, -CD2<br>(PC Card Memory<br>mode)<br>-CD1, -CD2<br>(PC Card I/O mode)<br>-CD1, -CD2<br>(True IDE mode) | О         | 26, 25        | -CD1 and -CD2 are the card detection signalsCD1 and -CD2 are connected to ground, so host can detect that the card is inserted or not.                       |

| -CE1, -CE2 PC Card Memory mode) Card Enable -CE1, -CE2 (PC Card I/O mode) Card Enable                       | I         | 7, 32         | -CE1 and -CE2 are low active card<br>select signals. Byte/Word/Odd<br>byte modes are defined by<br>combination Card Enable of -CE1,<br>-CE2 and A0.          |

| Signal Name                                                                            | Direction | Pin Number                                                            | Description                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -CS0, -CS1<br>(True IDE mode)<br>Card Enable                                           |           |                                                                       | -CE2 is used for select the Alternate Status Register and the Device Control Register while - CE1 is the chip select for the other task file registers.                                                                                                                           |

| -CSEL (PC Card Memory mode) -CSEL (PC Card I/O mode)                                   |           |                                                                       | This signal is not used.                                                                                                                                                                                                                                                          |

| -CSEL<br>(True IDE mode)                                                               | I         | 39                                                                    | This signal is used to configure this device as a Master or a Slave when configured in the True IDE mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave.                                           |

| D15 to D0 (PC Card Memory mode) D15 to D0 (PC Card I/O mode) D15 to D0 (True IDE mode) | I/O       | 31, 30, 29,<br>28, 27, 49,<br>48, 47, 6,<br>5, 4, 3, 2,<br>23, 22, 21 | Data bus is D15 to D0. D0 is the LSB of the even byte of the word. D8 is the LSB of the odd byte of the word.                                                                                                                                                                     |

| GND (PC Card Memory mode) GND (PC Card I/O mode) GND (True IDE mode)                   | _         | 1, 50                                                                 | Ground                                                                                                                                                                                                                                                                            |

| -INPACK (PC Card Memory mode) -INPACK (PC Card I/O mode) Input Acknowledge             | 0         | 43                                                                    | This signal is not used and should not be connected at the host.  This signal is asserted low by this card when the card is selected and responding to an I/O read cycle at the address that is on the address bus during -CE and-IORD are low. This signal is used for the input |

| Signal Name                          | Direction | Pin Number | Description                                                                                                                                                                                                          |

|--------------------------------------|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMARQ<br>(True IDE mode)             |           |            | This signal is a DMA Request that is used for DMA data transfers between host and device.                                                                                                                            |

| -IORD<br>(PC Card Memory<br>mode)    |           |            | This signal is not used.                                                                                                                                                                                             |

| -IORD<br>(PC Card I/O mode)          | I         | 34         | -IORD is used for control of read data in I/O task file area. This card does not respond to -IORD until I/O card interface setting up.                                                                               |

| -IORD<br>(True IDE mode)             |           |            | -IORD is used for control of read data in I/O task file area. This card does not respond to -IORD until True IDE interface setting up.                                                                               |

| -IOWR<br>(PC Card Memory<br>mode)    |           |            | This signal is not used.                                                                                                                                                                                             |

| -IOWR<br>(PC Card I/O mode)          | I         | 35         | -IOWR is used for control of data<br>write in I/O task file area. This card<br>does not respond to -IOWR until<br>I/O card interface setting up.                                                                     |

| -IOWR<br>(True IDE mode)             |           |            | -IOWR is used for control of data<br>write in I/O task file area. This card<br>does not respond to -IOWR until<br>True IDE interface setting up.                                                                     |

| -OE<br>(PC Card Memory<br>mode)      |           |            | -OE is used for the control of reading register's data in attribute area or task file area.                                                                                                                          |

| -OE<br>(PC Card I/O mode)            | I         | 9          | -OE is used for the control of reading register's data in attribute area.                                                                                                                                            |

| -ATASEL<br>(True IDE mode)           |           |            | To enable True IDE mode this input should be grounded by the host.                                                                                                                                                   |

| RDY/-BSY<br>(PC Card Memory<br>mode) | О         | 37         | The signal is RDY/-BSY pin. RDY/-BSY pin turns low level during the card internal initialization operation at Vcc applied or reset applied, so next access to the card should be after the signal turned high level. |

| Signal Name                                             | Direction | Pin Number | Description                                                                                                                                                                                                                                           |

|---------------------------------------------------------|-----------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -IREQ<br>(PC Card I/O mode)<br>INTRQ<br>(True IDE mode) |           |            | This signal is active low -IREQ pin. The signal of low level indicates that the card is requesting software service to host, and high level indicates that the card is not requesting.  This signal is the active high Interrupt Request to the host. |

| -REG<br>(PC Card Memory<br>mode)                        |           | 44         | -REG is used during memory cycles to distinguish between task file and attribute memory accesses. Attribute memory select High for task file, Low for attribute memory is accessed.                                                                   |

| -REG<br>(PC Card I/O mode)                              | ·         |            | -REG is constantly low when task file or attribute memory is accessed.                                                                                                                                                                                |

| -DMACK<br>(True IDE mode)                               |           |            | This is a DMA Acknowledge signal by the host in response to DMARQ to initiate DMA transfers.                                                                                                                                                          |

| RESET<br>(PC Card Memory<br>mode)                       |           |            | This signal is active high RESET pin. If this signal is asserted high, the card internal initialization begins to operate. During the card internal initialization RDY/-BSY is low. After the card internal initialization RDY/-BSY is high.          |

| RESET<br>(PC Card I/O mode)                             | I         | 41         | This signal is active high RESET pin. If this signal is asserted high, the card internal initialization begins to operate. In this mode, RDY/-BSY signal cannot be used, so using Status Register the Ready/Busy status can be confirmed.             |

| -RESET<br>(True IDE mode)                               |           |            | This signal is active low -RESET pin. If this signal is asserted low, all the registers in this card are reset. In this mode, RDY/-BSY signal cannot be used, so using status register the Ready/Busy status can be confirmed.                        |

| Vcc<br>(PC Card Memory<br>mode)                         | _         | 13, 38     | +5 V, +3.3 V power.                                                                                                                                                                                                                                   |

| Signal Name                                                                | Direction | Pin Number | Description                                                                                                               |

|----------------------------------------------------------------------------|-----------|------------|---------------------------------------------------------------------------------------------------------------------------|

| Vcc                                                                        |           |            |                                                                                                                           |

| (PC Card I/O mode)                                                         |           |            |                                                                                                                           |

| Vcc                                                                        |           |            |                                                                                                                           |

| (True IDE mode)                                                            |           |            |                                                                                                                           |

| -VS1, -VS2<br>(PC Card Memory<br>mode)<br>-VS1, -VS2<br>(PC Card I/O mode) | 0         | 33, 40     | These signals are intended to notify Vcc requirement to host VS1 is held grounded and -VS2 is non-connected in this card. |

| -VS1, -VS2<br>(True IDE mode)                                              | -         |            |                                                                                                                           |

| -WAIT (PC Card Memory mode) -WAIT (PC Card I/O mode)                       | 0         | 42         | This signal is active low -WAIT pin. In this card this signal is constantly high level.                                   |

| IORDY<br>(True IDE mode)                                                   |           |            | This output signal may be used as IORDY. In this card this signal is constantly high impedance.                           |

| -WE<br>(PC Card Memory<br>mode)                                            |           |            | -WE is used for the control of writing register's data in attribute memory area or task file area.                        |

| -WE<br>(PC Card I/O mode)                                                  | I         | 36         | -WE is used for the control of writing register's data in attribute memory area.                                          |

| -WE<br>(True IDE mode)                                                     |           |            | This input signal is not used and should be connected to Vcc by the host.                                                 |

| WP<br>(PC Card Memory<br>mode)                                             |           |            | WP is held low because this card does not have write-protect switch.                                                      |

| -IOIS16<br>(PC Card I/O mode)                                              | 0         | 24         | -IOIS16 is asserted when task file registers are accessed in 16-bit mode.                                                 |

| -IOCS16<br>(True IDE mode)                                                 |           |            | This output signal is asserted low when this device is expecting a word data transfer cycle.                              |

#### 4.0 Electrical Interface

#### 4.1 Absolute Maximum Conditions

| Parameter                                         | Symbol | Conditions                      |

|---------------------------------------------------|--------|---------------------------------|

| Input Power                                       | Vcc    | -0.3V min. to 6.5V Max          |

| Voltage on any pin except Vcc with respect to GND | V      | -0.5V min. to Vcc + 0.5V<br>Max |

#### 4.2 Input Power

| Voltage      | Maximum Average RMS Active Current | Maximum Average RMS Sleep Current | Measurement<br>Method |  |  |

|--------------|------------------------------------|-----------------------------------|-----------------------|--|--|

| 3.135-3.465V | 75 mA                              | 200 μΑ                            | 3.3V at 25°C1         |  |  |

| 4.5-5.5V     | 100 mA                             | 300 µA                            | 5.0V at 25°C1         |  |  |

Current measurement is accomplished by connecting an amp meter (set to the 2 amp scale range) in series with the Vcc supply to the CompactFlash card. Current measurements are to be taken while looping on a data transfer command with a sector count of 128. Current consumption values for both Read and Write commands are not to exceed the Maximum Average RMS Current specified in this table.

CompactFlash products shall operate correctly in both voltage ranges as shown in the above. To comply with this specification, current requirements must not exceed the maximum limit.

#### 4.3 Input Leakage Current

| Туре | Parameter                | Symbol | Conditions               | Min | Тур | Max  | Units |

|------|--------------------------|--------|--------------------------|-----|-----|------|-------|

| IxZ  | Input Leakage<br>Current | IL     | VHI = Vcc / VIL =<br>GND | -1  |     | 1    | μΑ    |

| IxU  | Pull Up Resistor         | RPU1   | Vcc = 5.0V               | 50k |     | 500k | Ohm   |

| IxD  | Pull Down Resister       | RPD1   | Vcc = 5.0V               | 50k |     | 500k | Ohm   |

#### 4.4 Input Characteristics

| Туре | Parameter                                | Symbo      | Mir<br>V | n<br>Max<br>/cc = 3.3 | Тур | Mir<br>V | Max<br>cc = 5.0 | Тур<br>V | Unit<br>s |

|------|------------------------------------------|------------|----------|-----------------------|-----|----------|-----------------|----------|-----------|

| 1    | Input Voltage                            | Vih        | 2.4      |                       |     | 4.0      |                 |          | Volt      |

|      | CMOS                                     | Vil        |          |                       | 0.6 |          |                 | 0.8      | S         |

| 2    | Input Voltage                            | Vih        | 1.5      |                       |     | 2.0      |                 |          | Volt      |

| 2    | CMOS                                     | Vil        |          |                       | 0.6 |          |                 | 0.8      | S         |

| 3    | Input Voltage<br>CMOS Schmitt<br>Trigger | Vth<br>Vtl |          | 1.8<br>1.0            |     |          | 2.8<br>2.0      |          | Volt<br>s |

#### 4.5 Output Drive Type

All outputs drive types are CMOS level.

### 4.6 Output Drive Characteristics

| Type | Parameter         | Symbol     | Conditions                   | Min       | Тур | Max          | Units |

|------|-------------------|------------|------------------------------|-----------|-----|--------------|-------|

| O1   | Output<br>Voltage | Voh<br>Vol | Ioh = -4<br>mA<br>Iol = 4 mA | Vcc -0.8V |     | GND<br>+0.4V | Volts |

| 02   | Output<br>Voltage | Voh<br>Vol | Ioh = -8<br>mA<br>Iol = 8 mA | Vcc -0.8V |     | GND<br>+0.4V | Volts |

#### 4.7 Interface/Bus Timing

There are two types of bus cycles and timing sequences that occur in the PCMCIA type interface, a direct mapped I/O transfer and a memory access. The two timing sequences are explained in detail in the PCMICA PC Card Standard. Delkin's CompactFlash Card conforms to the timing in that reference document.

## 4.8 Attribute Memory Read Timing

The Attribute Memory access time is defined as 300 ns.

| Item                              | Symbol   | IEEE Symbol | Min | Max | Units |

|-----------------------------------|----------|-------------|-----|-----|-------|

| Read Cycle Time                   | tc(R)    | tAVAV       | 300 |     | ns    |

| Address Access Time               | ta(A)    | tAVQV       |     | 300 | ns    |

| Card Enable Access Time           | ta(CE)   | tELQV       |     | 300 | ns    |

| Output Enable Access<br>Time      | ta(OE)   | tGLQV       |     | 150 | ns    |

| Output disable Time from CE       | tdis(CE) | tEHQZ       |     | 100 | ns    |

| Output disable Time from OE       | tdis(OE) | tGHQZ       |     | 100 | ns    |

| Address Setup Time                | tsu(A)   | tAVGL       | 30  |     | ns    |

| Output Enable Time from CE        | ten(CE)  | tELQNZ      | 5   |     | ns    |

| Output Enable Time from OE        | ten(OE)  | tGLQNZ      | 5   |     | ns    |

| Data Valid from Address<br>Charge | tv(A)    | tAXQX       | 0   |     | ns    |

<sup>&</sup>lt;sup>1</sup>All times are in nanoseconds. Dout signifies data provided by the CompactFlash card to the system. The –CE signal or both the –OE signal and the –WE must be de-asserted between consecutive cycle operations.

Figure 2. Attribute Memory Read Timing Diagram

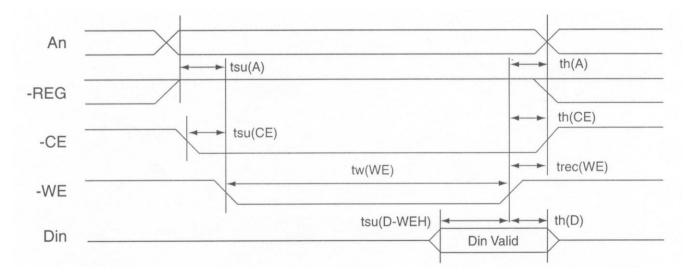

## 4.9 Configuration Register (Attribute Memory) Write Timing

The Card Configuration write access time is defined as 250 ns.

| Item                   | Symbol         | IEEE<br>Symbol | Min <sup>1</sup> | Max <sup>1</sup> | Units |

|------------------------|----------------|----------------|------------------|------------------|-------|

| Write Cycle Time       | tc(W)          | tAVAV          | 250              |                  | ns    |

| Write Pulse Width      | tw(WE)         | tWLWH          | 150              |                  | ns    |

| Address Setup Time     | tsu(A)         | tAVWL          | 30               |                  | ns    |

| Write Recovery<br>Time | Trec(WE)       | tWMAX          | 30               |                  | ns    |

| Data Setup Time for WE | tsu(D-<br>WEH) | tDVWH          | 80               |                  | ns    |

| Data Hold Time         | th(D)          | tWMDX          | 30               |                  | ns    |

<sup>&</sup>lt;sup>1</sup>All times are in nanoseconds. DIN signifies data provided by the system to the CompactFlash card.

Figure 3. Configuration Register (Attribute Memory) Write Timing Diagram

## 4.10 Common Memory Read Timing

The Card Common Memory access time is defined as 250 ns.

| Item                        | Symbol   | IEEE Symbol | Min <sup>1</sup> | Max <sup>1</sup> |

|-----------------------------|----------|-------------|------------------|------------------|

| Output Enable Access Time   | ta(OE)   | tGLQV       |                  | 125              |

| Output Disable Time from OE | tdis(OE) | tGHQZ       |                  | 100              |

| Address Setup Time          | Tsu(A)   | tAVGL       | 30               |                  |

| Address Hold Time           | thA      | tGHAX       | 20               |                  |

| CE Setup before OE          | Tsu(CE)  | tELGL       | 5                |                  |

| CE Hold following OE        | th(CE)   | tGHEH       | 20               |                  |

<sup>&</sup>lt;sup>1</sup>All times are in nanoseconds.

Figure 4. Common Memory Read Timing Diagram

## **4.11 Common Memory Write Timing**

The Card Common Memory write access time is defined as 250 ns.

| Item                   | Symbol         | IEEE Symbol | Min¹ ns | Max <sup>1</sup> ns |

|------------------------|----------------|-------------|---------|---------------------|

| Data Setup before WE   | tsu(D-<br>WEH) | tDVWH       | 80      |                     |

| Data Hold following WE | th(D)          | tWMDX       | 30      |                     |

| WE Pulse Width         | tw(WE)         | tWLWH       | 150     |                     |

| Address Setup Time     | tsu(A)         | tAVWL       | 30      |                     |

| CE Setup before WE     | tsu(CE)        | tELWL       | 5       |                     |

| Write Recovery Time    | trec(WE)       | tWMAX       | 30      |                     |

| Address Hold Time      | th(A)          | tGHAX       | 20      |                     |

| CE Hold following WE   | th(CE)         | tGHEH       | 20      |                     |

<sup>&</sup>lt;sup>1</sup>All times are in nanoseconds.

**Figure 5. Common Memory Write Timing Diagram**

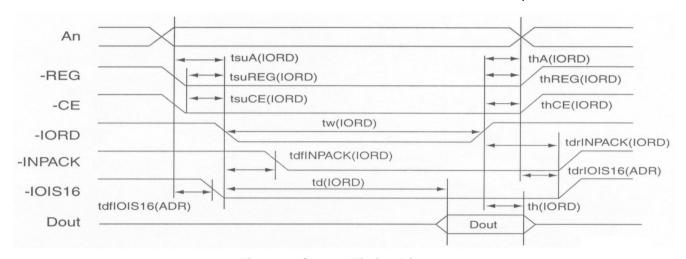

## 4.12 I/O Input (Read) Timing

The Card I/O read access time is defined as 250 ns.

| Item                           | Symbol          | IEEE Symbol | Min <sup>1</sup> | Max <sup>1</sup> |

|--------------------------------|-----------------|-------------|------------------|------------------|

| Data Delay after IORD          | td(IORD)        | tlGLQV      |                  | 100              |

| Data Hold following IORD       | th(IORD)        | tlGHQX      | 0                |                  |

| IORD Width Time                | tw(IORD)        | tIGLIGH     | 165              |                  |

| Address Setup before IORD      | tsuA(IORD)      | tAVIGL      | 70               |                  |

| Address Hold following IORD    | thA(IORD)       | tIGHAX      | 20               |                  |

| CE Setup before IORD           | tsuCE(IORD)     | tELIGL      | 5                |                  |

| CE Hold following IORD         | thCE(IORD)      | tlGHEH      | 20               |                  |

| REG Setup before IORD          | tsuREG(IORD)    | tRGLIGL     | 5                |                  |

| REG Hold following IORD        | thREG(IORD)     | tlGHRGH     | 0                |                  |

| INPACK Delay Falling from IORD | tdfINPACK(IORD) | tlGLIAL     | 0                | 45               |

| INPACK Delay Rising from IORD  | tdrINPACK(IORD) | tIGHIAH     |                  | 45               |

| IOIS16 Delay Falling from IORD | tdfIOIS16(ADR)  | tAVISL      |                  | 35               |

| IOIS16 Delay Rising from IORD  | tdrlOIS16(ADR)  | tAVISH      |                  | 35               |

<sup>&</sup>lt;sup>1</sup>All times are in nanoseconds.

Note: The maximum load on -INPACK and IOIS16 is 1 LSTTL with 50pF total load.

Figure 6. I/O read Timing Diagram

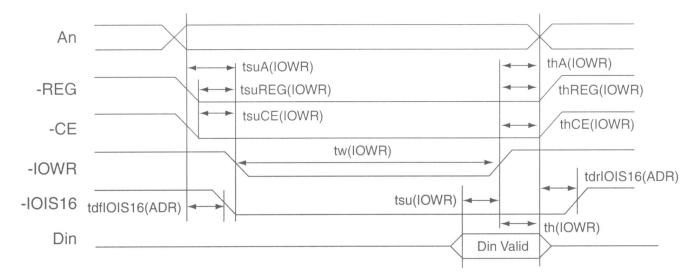

## 4.13 I/O Input (Write) Timing

The Card I/O Input write access time is defined as 250 ns.

| Item                              | Symbol         | IEEE Symbol | Min <sup>1</sup> | Max <sup>1</sup> |

|-----------------------------------|----------------|-------------|------------------|------------------|

| Data Setup before IOWR            | tsu(IOWR)      | tDVIWH      | 60               |                  |

| Data Hold following IOWR          | th(IOWR)       | tlWHDX      | 30               |                  |

| IOWR Width Time                   | tw(IOWR)       | tlWLlWH     | 165              |                  |

| Address Setup before IOWR         | tsuA(IOWR)     | tAVIWL      | 70               |                  |

| Address Hold following IOWR       | thA(IOWR)      | tlWHAX      | 20               |                  |

| CE Setup before IOWR              | tsuCE(IOWR)    | tELIWL      | 5                |                  |

| CE Hold following IOWR            | thCE(IOWR)     | tlWHEH      | 20               |                  |

| REG Setup before IOWR             | tsuREG(IOWR)   | tRGLIWL     | 5                |                  |

| REG Hold following IOWR           | thREG(IOWR)    | tlWHRGH     | 0                |                  |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR) | tAVISL      |                  | 35               |

| IOIS16 Delay Rising from Address  | tdrIOIS16(ADR) | tAVISH      |                  | 35               |

<sup>&</sup>lt;sup>1</sup>All times are in nanoseconds.

Note: The maximum load on –INPACK and IOIS16 is 1 LSTTL with 50pF total load.

Figure 7. I/O Write Timing Diagram

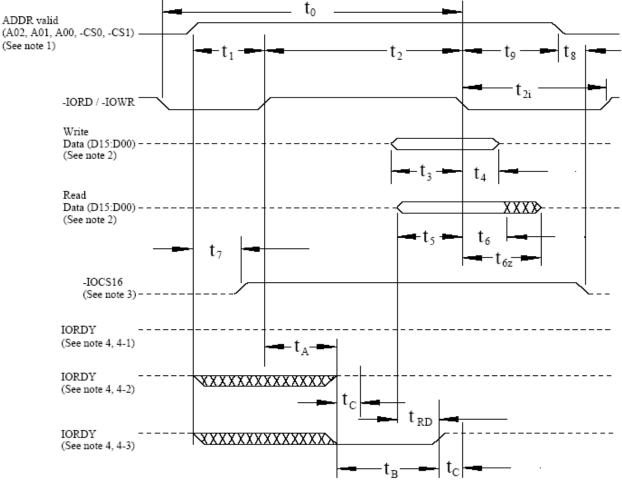

#### 4.14 True IDE PIO Mode Read/Write Timing

The timing diagram for True IDE mode of operation in this section is drawn using the conventions in the ATA-4 specification. Signals are shown with their asserted state as high regardless of whether the signal is actually negative or positive true. Consequently, the -IORD, the -IOWR and the -IOCS16 signals are shown in the diagram inverted from their electrical states on the bus.

|     | Item                                                                   | Mode<br>0 | Mode<br>1 | Mode<br>2 | Mode<br>3 | Mode<br>4 | Mode<br>5 | Mode<br>6 |

|-----|------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| tO  | Cycle time (min)                                                       | 600       | 383       | 240       | 180       | 120       | 100       | 80        |

| t1  | Address Valid to -IORD/-IOWR setup (min)                               | 70        | 50        | 30        | 30        | 25        | 15        | 10        |

| t2  | -IORD/-IOWR (min)                                                      | 165       | 125       | 100       | 80        | 70        | 65        | 55        |

| t2  | -IORD/-IOWR (min) Register (8 bit)                                     | 290       | 290       | 290       | 80        | 70        | 65        | 55        |

| t2i | -IORD/-IOWR recovery time (min)                                        | -         | -         | -         | 70        | 25        | 25        | 20        |

| t3  | -IOWR data setup (min)                                                 | 60        | 45        | 30        | 30        | 20        | 20        | 15        |

| t4  | -IOWR data hold (min)                                                  | 30        | 20        | 15        | 10        | 10        | 5         | 5         |

| 5   | -IORD data setup (min)                                                 | 50        | 35        | 20        | 20        | 20        | 15        | 10        |

| t6  | -IORD data hold (min)                                                  | 5         | 5         | 5         | 5         | 5         | 5         | 5         |

| t6Z | -IORD data tristate (max)                                              | 30        | 30        | 30        | 30        | 30        | 20        | 20        |

| t7  | Address valid to -IOCS16 assertion (max)                               | 90        | 50        | 40        | n/a       | n/a       | n/a       | n/a       |

| t8  | Address valid to -IOCS16 released (max)                                | 60        | 45        | 30        | n/a       | n/a       | n/a       | n/a       |

| t9  | -IORD/-IOWR to address valid hold                                      | 20        | 15        | 10        | 10        | 10        | 10        | 10        |

| tRD | Read Data Valid to IORDY active (min), if IORDY initially low after tA | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

| tA  | IORDY Setup time                                                       | 35        | 35        | 35        | 35        | 35        | na5       | na5       |

| tB  | IORDY Pulse Width (max)                                                | 1250      | 1250      | 1250      | 1250      | 1250      | na5       | na5       |

| tC  | IORDY assertion to release (max)                                       | 5         | 5         | 5         | 5         | 5         | na5       | na5       |

Notes: All timings are in nanoseconds. The maximum load on -IOCS16 is 1 LSTTL with a 50 pF (40pF below 120nsec Cycle Time) total load. All waveforms in the following waveform are shown with the asserted state high. The negative true signal appears inverted on the bus relative to the diagram.

#### Notes:

- (1) Device address consists of -CS0, -CS1, and A[02::00]

- (2) Data consists of D[15::00] (16-bit) or D[07::00] (8 bit)

- (3) -IOCS16 is shown for PIO modes 0, 1 and 2. For other modes, this signal is ignored.

- (4) The negation of IORDY by the device is used to extend the PIO cycle. The determination of whether the cycle is to be extended is made by the host after tA from the assertion of IORD or IOWR. The assertion and negation of IORDY is described in the following three cases:

- (4-1) Device never negates IORDY: No wait is generated.

- (4-2) Device starts to drive IORDY low before tA, but causes IORDY to be asserted before tA: No wait generated.

- (4-3) Device drives IORDY low before tA: wait generated. The cycle completes after IORDY is reasserted. For cycles where a wait is generated and -IORD is asserted, the device shall place read data on D15-D00 for tRD before causing IORDY to be asserted.

Figure 8. True IDE PIO Mode Read/Write Timing Diagram

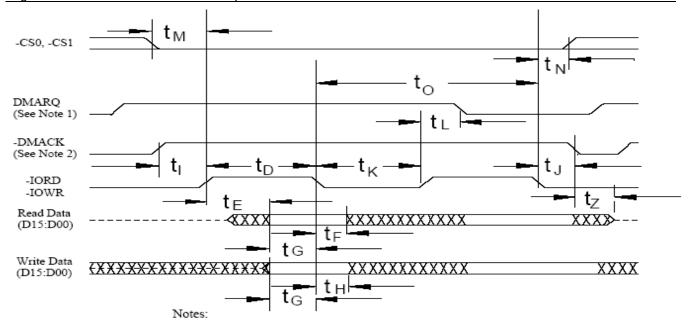

## 4.15 True IDE Multiword DMA Mode Read/Write Timing

The timing diagram for True IDE DMA mode of operation in this section is drawn using the conventions in the ATA-4 specification. Signals are shown with their asserted state as high regardless of whether the signal is actually negative or positive true. Consequently, the -IORD, the -IOWR and the -IOCS16 signals are shown in the diagram inverted from their electrical states on the bus.

|     | Item                               | Mode 0<br>(ns) | Mode 1<br>(ns) | Mode 2<br>(ns) | Mode 3<br>(ns) | Mode 4<br>(ns) |

|-----|------------------------------------|----------------|----------------|----------------|----------------|----------------|

| tO  | Cycle time (min)                   | 480            | 150            | 120            | 100            | 80             |

| tD  | -IORD / -IOWR asserted width (min) | 215            | 80             | 70             | 65             | 55             |

| tΕ  | -IORD data access (max)            | 150            | 60             | 50             | 50             | 45             |

| tF  | -IORD data hold (min)              | 5              | 5              | 5              | 5              | 5              |

| tG  | -IORD/-IOWR data setup (min)       | 100            | 30             | 20             | 15             | 10             |

| tH  | -IOWR data hold (min)              | 20             | 15             | 10             | 5              | 5              |

| tl  | DMACK to -IORD/-IOWR setup (min)   | 0              | 0              | 0              | 0              | 0              |

| tJ  | -IORD / -IOWR to -DMACK hold (min) | 20             | 5              | 5              | 5              | 5              |

| tKR | -IORD negated width (min)          | 50             | 50             | 25             | 25             | 20             |

| tKW | -IOWR negated width (min)          | 215            | 50             | 25             | 25             | 20             |

| tLR | -IORD to DMARQ delay (max)         | 120            | 40             | 35             | 35             | 35             |

| tLW | -IOWR to DMARQ delay (max)         | 40             | 40             | 35             | 35             | 35             |

| tM  | CS(1:0) valid to –IORD / -IOWR     | 50             | 30             | 25             | 10             | 5              |

| tN  | CS(1:0) hold                       | 15             | 10             | 10             | 10             | 10             |

| tZ  | -DMACK                             | 20             | 25             | 25             | 25             | 25             |

**Notes:** All timings are in nanoseconds. All waveforms in the following waveform are shown with the asserted state high. The negative true signal appears inverted on the bus relative to the diagram.

28

- (1) If the Card cannot sustain continuous, minimum cycle time DMA transfers, it may negate DMARQ within the time specified from the start of a DMA transfer cycle to suspend the DMA transfers in progress and reassert the signal at a later time to continue the DMA operation.

- (2) This signal may be negated by the host to suspend the DMA transfer in progress.

Figure 9. True IDE Multiword DMA Mode Read/Write Timing Diagram

## **5.0 Card Configuration**

The Delkin CompactFlash cards are identified by appropriate information in the Card Information Structure (CIS). The following registers are used to coordinate the I/O spaces and the Interrupt level of the cards that are located in the system. In addition, these registers provide a method for accessing status information about the Delkin CompactFlash cards that may be used to arbitrate between multiple interrupt sources on the same interrupt level or to replace status information that appears on dedicated pins in memory cards that have alternate use in I/O cards.

#### 5.1 Delkin Card Configuration

#### **Register and Memory Space Decoding**

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | A3 | A2 | A1 | A0 | Selected Space                  |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|---------------------------------|

| 1    | 1    | Х    | Х   | Х   | Х   | Χ  | XX    | Х  | Х  | Х  | Х  | Standby                         |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | XX    | Х  | Х  | Х  | 0  | Configuration<br>Register Read  |

| 1    | 0    | 1    | 0   | 1   | Х   | X  | XX    | Х  | Х  | Х  | Х  | Common<br>Memory Read           |

|      |      |      |     |     |     |    |       |    |    |    |    | (8 bit D7-D0)                   |

| 0    | 1    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х  | Х  | Х  | Common<br>Memory Read           |

|      |      |      |     |     |     |    |       |    |    |    |    | (8 bit D15-D8)                  |

| 0    | 0    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х  | Х  | 0  | Common<br>Memory Read           |

|      |      |      |     | -   |     |    | 7.0.1 |    |    |    |    | (16 bit D15-D0)                 |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | XX    | Х  | Х  | Х  | 0  | Configuration<br>Register Write |

| 1    | 0    | 1    | 1   | 0   | Х   | X  | XX    | Х  | Х  | Х  | Х  | Common<br>Memory Write          |

|      |      |      |     |     |     |    |       |    |    |    |    | (8 bit D7-D0)                   |

| 0    | 1    | 1    | 1   | 0   | Х   | Х  | XX    | Х  | Х  | Х  | Х  | Common<br>Memory Write          |

|      |      |      |     |     |     |    |       |    |    |    |    | (8 bit D15-D8)                  |

| 0    | 0    | 1    | 1   | 0   | Х   | Х  | XX    | Х  | Х  | Х  | 0  | Common<br>Memory Write          |

|      |      |      |     | -   |     |    |       |    |    |    |    | (16 bit D15-D0)                 |

| Х    | 0    | 0    | 0   | 1   | 0   | 0  | XX    | Х  | Х  | Х  | 0  | Card<br>Information             |

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | А3 | A2 | A1       | A0 | Selected Space           |

|------|------|------|-----|-----|-----|----|-------|----|----|----------|----|--------------------------|

|      |      |      |     |     |     |    |       |    |    |          |    | Structure Read           |

| 1    | 0    | 0    | 1   | 0   | 0   | 0  | XX    | Х  | Х  | Х        | 0  | Invalid Access           |

| •    | U    | O    | '   | )   | )   | U  |       |    |    | <b>X</b> | U  | (CIS Write)              |

|      |      |      |     |     |     |    |       |    |    |          |    | Invalid Access           |

| 1    | 0    | 0    | 0   | 1   | Χ   | Х  | XX    | Х  | Х  | X        | 1  | (Odd Attribute<br>Read)  |

|      |      |      |     |     |     |    |       |    |    |          |    | Invalid Access           |

| 1    | 0    | 0    | 1   | 0   | Χ   | X  | XX    | Х  | Х  | X        | 1  | (Odd Attribute<br>Write) |

|      |      |      |     |     |     |    |       |    |    |          |    | Invalid Access           |

| 0    | 1    | 0    | 0   | 1   | Χ   | X  | XX    | Х  | Х  | X        | X  | (Odd Attribute<br>Read)  |

|      |      |      |     |     |     |    |       |    |    |          |    | Invalid Access           |

| 0    | 1    | 0    | 1   | 0   | Χ   | Х  | XX    | Х  | Х  | X        | X  | (Odd Attribute<br>Write) |

#### **Configuration Register Decoding**

|      | 9    | _    | ,   |     | •   |    |       |    |    |    |    |                                   |

|------|------|------|-----|-----|-----|----|-------|----|----|----|----|-----------------------------------|

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | A9 | A8-A4 | A3 | A2 | A1 | A0 | Selected Register                 |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 0  | 0  | 0  | Configuration Option Reg Read     |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 0  | 0  | 0  | Configuration Option Reg Write    |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 0  | 1  | 0  | Card Status<br>Register Read      |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 0  | 1  | 0  | Card Status<br>Register Write     |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 1  | 0  | 0  | Pin Replacement<br>Register Read  |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 1  | 0  | 0  | Pin Replacement<br>Register Write |

| Х    | 0    | 0    | 0   | 1   | 0   | 1  | 00    | 0  | 1  | 1  | 0  | Socket and Copy<br>Register Read  |

| Х    | 0    | 0    | 1   | 0   | 0   | 1  | 00    | 0  | 1  | 1  | 0  | Socket and Copy<br>Register Write |

**Note**: The location of the card configuration registers should always be read from the CIS location 0000H to 0198H. No writes should be performed to the CompactFlash card attribute

memory except to the card configuration register address. All other attribute memory locations are reserved.

#### **5.2 Attribute Memory Function**

Attribute memory is a space where CompactFlash card identification and configuration information are stored, and is limited to 8-bit wide accesses only at even addresses. The card configuration registers are also located here.

For the Attribute Memory function, signals –REG and –OE must be active and –WE inactive during the cycle.

As in the Main Memory Read functions, the signals –CE1 and –CE2 control the Even Byte and Odd Byte address, but only the Even Byte data is valid during the Attribute Memory access.

#### **Attribute Memory Function**

| Function Mode                                     | -REG | -CE2 | -CE1 | A10 | A9  | A0      | -OE | -WE | D15-D8        | D7-D0        |

|---------------------------------------------------|------|------|------|-----|-----|---------|-----|-----|---------------|--------------|

| Standby Mode                                      | Χ    | VIH  | VIH  | Х   | Χ   | Χ       | Х   | Χ   | High Z        | High Z       |

| Read Byte Access<br>CIS ROM (8 bits)              | VIL  | VIH  | VIL  | VIL | VIL | VI<br>L | VIL | VIH | High Z        | Even<br>Byte |

| Write Byte Access<br>CIS (8 bits)<br>(Invalid)    | VIL  | VIH  | VIL  | VIL | VIL | VI<br>L | VIH | VIL | Don't<br>Care | Even<br>Byte |

| Read Byte Access<br>Configuration (8<br>bits)     | VIL  | VIH  | VIL  | VIL | VIH | VI<br>L | VIL | VIH | High Z        | Even<br>Byte |

| Write Byte Access<br>Configuration (8<br>bits)    | VIL  | VIH  | VIL  | VIL | VIH | VI<br>L | VIH | VIL | Don't<br>Care | Even<br>Byte |

| Read Word<br>Access CIS                           | VIL  | VIL  | VIL  | VIL | VIL | Х       | VIL | VIH | Not<br>Valid  | Even<br>Byte |

| (16 bits)                                         |      |      |      |     |     |         |     |     |               | -            |

| Write Word<br>Access CIS                          | VIL  | VIL  | VIL  | VIL | VIL | Х       | VIH | VIL | Don't<br>Care | Even<br>Byte |

| (16 bits)                                         |      |      |      |     |     |         |     |     | Care          | Dyte         |

| Read Word<br>Access<br>Configuration (16<br>bits) | VIL  | VIL  | VIL  | VIL | VIH | Х       | VIL | VIH | Not<br>Valid  | Even<br>Byte |

33

| Function Mode                                      | -REG | -CE2 | -CE1 | A10 | A9  | A0 | -OE | -WE | D15-D8        | D7-D0        |

|----------------------------------------------------|------|------|------|-----|-----|----|-----|-----|---------------|--------------|

| Write Word<br>Access<br>Configuration (16<br>bits) | VIL  | VIL  | VIL  | VIL | VIH | х  | VIH | VIL | Don't<br>Care | Even<br>Byte |

**Note**: The –CE signal or both the –OE and the –WE signal must be de-asserted between consecutive cycle operations.

## 5.3 Configuration Option Register (Address 200H in Attribute Memory)

The Configuration Option Register is used to configure the interface, address decoding and interrupt and to issue a soft reset to the CompactFlash card.

| Operation | D7     | D6      | D5    | D4    | D3    | D2    | D1    | D0    |

|-----------|--------|---------|-------|-------|-------|-------|-------|-------|

| R/W       | SRESET | LevIREQ | Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 |

| SRESET          | Soft Reset – Setting this bit to one (1), waiting the minimum reset width time and returning to zero (0) places the CompactFlash card in the Reset state. Setting this bit to one (1) is equivalent to assertion of the +RESET signal except that the SRESET bit is not cleared. Returning this bit to zero (0) leaves the CompactFlash card in the same un-configured Reset state as following power-up and hardware reset. This bit is set to zero (0) by power-up and hardware reset. Using the PCMCIA Soft Reset is considered a hard Reset by the ATA Commands. Contrast with Soft Reset in the Device Control register. |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|