# **Tsi568A Serial RapidIO Switch Hardware Manual**

Formal April 2007 80B8000\_MA002\_04

#### **Trademarks**

TUNDRA is a registered trademark of Tundra Semiconductor Corporation (Canada, U.S., and U.K.). TUNDRA, the Tundra logo, Tsi568A, and Silicon Behind the Network, are trademarks of Tundra Semiconductor Corporation. All other registered and unregistered marks (including trademarks, service marks and logos) are the property of their respective owners. The absence of a mark identifier is not a representation that a particular product name is not a mark.

#### Copyright

Copyright © April 2007 Tundra Semiconductor Corporation. All rights reserved. Published in Canada

This document contains information that is proprietary to Tundra and may be used for non-commercial purposes within your organization in support of Tundra products. No other use or transmission of all or any part of this document is permitted without written permission from Tundra, and must include all copyright and other proprietary notices. Use or transmission of all or any part of this document in violation of any applicable Canadian or other legislation is hereby expressly prohibited.

User obtains no rights in the information or in any product, process, technology or trademark which it includes or describes, and is expressly prohibited from modifying the information or creating derivative works without the express written consent of Tundra.

#### **Disclaimer**

Tundra assumes no responsibility for the accuracy or completeness of the information presented, which is subject to change without notice. Tundra products may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. In no event will Tundra be liable for any direct, indirect, special, incidental or consequential damages, including lost profits, lost business or lost data, resulting from the use of or reliance upon the information, whether or not Tundra has been advised of the possibility of such damages. The information contained in this document does not affect or change Tundra's product warranties.

Mention of non-Tundra products or services is for information purposes only and constitutes neither an endorsement nor a recommendation.

As this information will change over time, please ensure you have the most recent version by contacting a member of the Tundra technical support team, or by checking the Support section of www.tundra.com.

# **Corporate Profile**

#### **About Tundra**

Tundra Semiconductor Corporation is the global leader in System Interconnect providing world-class support and leading edge semiconductor solutions to the world's foremost communications, networking, storage system, and information technology vendors. Consistently delivering on system-level performance promises that reduce time to market, Tundra System Interconnect ensures market advantage in wireless infrastructure, storage networking, network access, military, industrial automation, and information technology applications. Tundra headquarters are located in Ottawa, Ontario, Canada. The Company also has a design center in South Portland, Maine, and sales offices through out Europe, across the US and in Asia. Tundra sells its products worldwide through a network of direct sales personnel, independent distributors, and manufacturers' representatives.

### **Tundra System Interconnect**

Tundra uses the term *System Interconnect* to refer to the technology used to connect all the components and sub-systems in almost any embedded system. This concept applies to the interfacing of functional elements (CPU, memory, I/O complexes) within a single-board system, and the interconnection of multiple boards in a larger system.

Advanced communications networks need advanced System Interconnect. It is a vital enabling technology for the networked world. Tundra System Interconnect provides the latest interface and throughput features, which enable communications infrastructure vendors to design and build more powerful, faster equipment in shorter timeframes.

Tundra System Interconnect — vital to building the communications systems of the future:

- Tundra System Interconnect products enable customers to get the performance, scalability, and reliability from their systems to meet today's and tomorrow's bandwidth demands.

- Tundra System Interconnect products are standards-based, off-the-shelf products that help customers speed their time to market.

- Tundra System Interconnect products meet the growing customer demand for outsourced standards-based interconnect products.

### **Partnerships**

Fundamental to the success of Tundra is its partnerships with leading technology companies, including IBM, Intel, and Freescale. As a result of these alliances, Tundra devices complement our partners' products, and greatly influence the design of customers' architecture. Customers are changing their designs to incorporate Tundra products. This is evidence of our commitment to be a significant part of its customers' success.

4 Corporate Profile

### **Customers**

Tundra Semiconductor products are used by the world's leading communications infrastructure and storage vendors, including Cisco Systems, Freescale, Siemens, Nortel Networks, Lucent Technologies, Nokia, Ericsson, Alcatel, and Hewlett-Packard.

The Tundra design philosophy is one in which a number of strategic customers are invited to participate in the definition, design, test, and early silicon phases of product development. Close working relationships with customers and clear product roadmaps ensure that Tundra can anticipate and meet the future directions and needs of communications systems designers and manufacturers.

### **Support**

Tundra is respected throughout the industry for its outstanding commitment to customer support. Tundra ensures that its customers can take immediate advantage of the company's products through its in-house Applications Engineering Group, unmatched design support tools, and full documentation accessible through the Web.

Design. Connect. GoTM

# **Contact Information**

Tundra is dedicated to providing superior technical documentation and design support to its customers. The following support options are available:

| 1/1/ | • | h  |

|------|---|----|

| * *  | c | IJ |

Product information www.tundra.com/Tsi568A contains the features, benefits,

typical applications, and block diagram for the Tsi568A. This webpage also provides links to other product information

located on the Tundra website.

Technical support resources www.tundra.com/support contains an extensive list of technical

resources to assist with your design needs. Some of the key

support resources include:

Technical support FAQ

User documentation

• Schematic design checklists and debug guidelines

You can also opt to receive email notification when a support

resource is added or changed.

Technical support request To contact Tundra support personnel about a technical

question, fill out the Technical Support Request Form in the

Support section of the website.

Sales support www.tundra.com/sales contains information that will help you

locate a Tundra sales representative nearest you.

Email docfeedback@tundra.com can be used to provide feedback

on a Tsi568A customer document.

Mail Tundra Semiconductor Corporation

603 March Road Ottawa, ON, Canada

K2K 2M5

**Fax** 613-592-1320

6 Contact Information

This section discusses the following topics:

- "Scope" on page 7

- "Document Conventions" on page 7

- "Revision History" on page 8

# Scope

The *Tsi568A Serial RapidIO Switch Hardware Manual* discusses the features, capabilities, and configuration requirements for the *Tsi568A*. It is intended for hardware and software engineers who are designing system interconnect applications with the device.

### **Document Conventions**

This document uses the following conventions.

### **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "\_b". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |

|-------------|--------------------|-------------------|

| Active low  | NAME_b             | NAME_b[3]         |

| Active high | NAME               | NAME[3]           |

### **Differential Signal Notation**

Differential signals consist of pairs of complement positive and negative signals that are measured at the same time to determine a signal's active or inactive state (they are denoted by "\_p" and "\_n", respectively). The following table illustrates the differential signal naming convention.

| State    | Single-line signal       | Multi-line signal                |

|----------|--------------------------|----------------------------------|

| Inactive | NAME_p = 0<br>NAME_n = 1 | NAME_p[3] = 0<br>NAME_n[3] =1    |

| Active   | NAME_p = 1<br>NAME_n = 0 | NAME_p[3] is 1<br>NAME_n[3] is 0 |

### **Object Size Notation**

- A byte is an 8-bit object.

- A word is a 16-bit object.

- A doubleword (Dword) is a 32-bit object.

#### **Numeric Notation**

- Hexadecimal numbers are denoted by the prefix 0x (for example, 0x04).

- Binary numbers are denoted by the prefix *0b* (for example, 0b010).

- Registers that have multiple iterations are denoted by {x..y} in their names; where x is first register and address, and y is the last register and address. For example, REG{0..1} indicates there are two versions of the register at different addresses: REG0 and REG1.

### **Symbols**

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

#### **Document Status Information**

- Advance Contains information that is subject to change, and is available once prototypes are released to customers.

- Preliminary Contains information about a product that is near production-ready, and is revised as required.

- Formal Contains information about a final, customer-ready product, and is available once the product is released to production.

# **Revision History**

### 80B8000\_MA002\_04, Formal, April 2007

This is the current release of the *Tsi568A Serial RapidIO Switch Hardware Manual*. The following information was updated:

- "Power Distribution" on page 60

- "Package Characteristics" on page 25

- "Heatsink Attachment" on page 29

### 80B8000\_MA002\_03, Final, February 2007

The following information was updated:

• "Thermal Characteristics" on page 28

### 80B8000\_MA002\_02, Formal, December 2006

The following information was added to the document:

- "Line Rate Support" on page 73

- "Power Sequencing" on page 34.

- The T<sub>storage</sub> minimum value was changed to -55°C (see Table 6 on page 31).

- "Heatsink Requirement and Analysis" on page 29

### 80B8000\_MA002\_01, Formal, March 2006

This was the first release of the Tsi568A Serial RapidIO Switch Hardware Manual.

# **Contents**

| Co | rpora  | ate Pro    | ofile                                                   | 3  |

|----|--------|------------|---------------------------------------------------------|----|

| Co | ntact  | Inforn     | mation                                                  | 5  |

| Ab | out tl | his Do     | ocument                                                 | 7  |

|    | Scop   | e          |                                                         | 7  |

|    | Docu   | ıment Coı  | onventions                                              | 7  |

|    | Revis  | sion Histo | ory                                                     | 8  |

| 1. | Sig    | nals aı    | nd Packaging                                            | 17 |

|    | 1.1    |            | · · · · · · · · · · · · · · · · · · ·                   |    |

|    | 1.2    |            | S                                                       |    |

|    |        | 1.2.1      | Endian Ordering                                         |    |

|    |        | 1.2.2      | Signal Groupings                                        |    |

|    | 1.3    | Packag     | ge Characteristics                                      |    |

|    | 1.4    | Therma     | nal Characteristics                                     | 28 |

|    |        | 1.4.1      | Junction-to-Ambient Thermal Characteristics (Theta ja)  | 28 |

|    |        | 1.4.2      | Heatsink Requirement and Analysis                       | 29 |

| 2. | Ele    | ctrical    | Characteristics                                         | 31 |

|    | 2.1    |            | ute Maximum Ratings                                     |    |

|    | 2.2    |            | ical Characteristics and Operating Conditions           |    |

|    |        | 2.2.1      | Power Sequencing                                        |    |

|    |        | 2.2.2      | LVTTL I/O and Open Drain Electrical Characteristics     |    |

|    |        | 2.2.3      | Serial Interface Electrical Characteristics             |    |

|    |        | 2.2.4      | Serial Reference Clock Input Electrical Characteristics | 38 |

|    |        | 2.2.5      | Serial Interface Capability and Implementation          |    |

|    |        | 2.2.6      | I2C Interface AC Specifications                         | 41 |

|    |        | 2.2.7      | Boundary Scan Interface AC Specifications               | 42 |

|    | 2.3    | AC Tir     | ming Waveforms                                          | 43 |

|    |        | 2.3.1      | LVTLL I/O pins                                          | 43 |

|    |        | 2.3.2      | Serial Interface Pins                                   | 44 |

| 3. | Lay    | out Gu     | uidelines                                               | 47 |

|    | 3.1    | Overvi     | iew                                                     | 47 |

|    | 3.2    | Impeda     | ance Requirements                                       | 47 |

|    | 3.3    | _          | ng Topologies                                           |    |

|    |        | 3.3.1      | Stripline                                               | 48 |

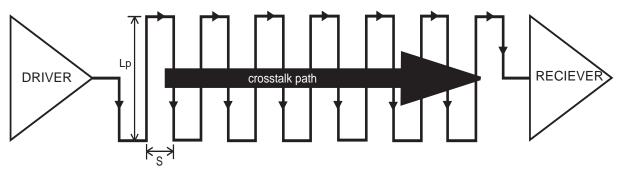

|    |        | 3.3.2      | Crosstalk Considerations                                | 56 |

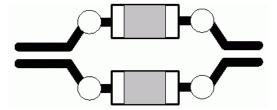

|    |        | 3.3.3      | Receiver DC Blocking Capacitors                         | 57 |

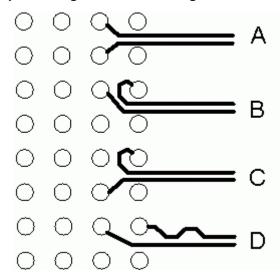

|    |        | 3.3.4      | Escape Routing                                          | 57 |

|    |        | 3.3.5      | Board Stackup                                           | 58 |

|    | 3.4    | Power      | Distribution                                            | 60 |

12 Contents

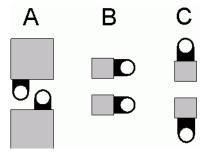

|    | 3.5 | Decou   | pling Requirements                  | 60 |

|----|-----|---------|-------------------------------------|----|

|    |     | 3.5.1   | Component Selection                 |    |

|    |     | 3.5.2   | Power Plane Impedance and Resonance | 62 |

|    | 3.6 | Clocki  | ng and Reset                        |    |

|    |     | 3.6.1   | Clock Overview                      | 64 |

|    |     | 3.6.2   | Clock Domains                       | 66 |

|    |     | 3.6.3   | Reset Requirements                  | 67 |

|    | 3.7 | Modeli  | ing and Simulation                  | 68 |

|    | 3.8 | Testing | g and Debugging Considerations      | 69 |

|    |     | 3.8.1   | Logic Analyzer Connection Pads      | 69 |

|    |     | 3.8.2   | JTAG Connectivity                   | 71 |

|    | 3.9 | Reflow  | v Profile                           | 71 |

| 4. | Lin | e Rate  | Support                             | 73 |

| Α. | Ord | lering  | Information                         | 75 |

|    | A.1 | Orderii | ng Information                      | 75 |

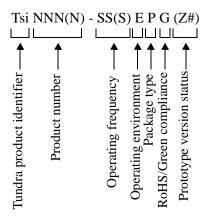

|    | ۸.2 |         | Sumbaring Information               |    |

# **Figures**

| Figure 1:  | Tsi568A Pinout List                                                    | 19 |

|------------|------------------------------------------------------------------------|----|

| Figure 2:  | Package Diagram — Top view                                             | 26 |

| Figure 3:  | Package Diagram — Side View                                            | 26 |

| Figure 4:  | Package Diagram — Bottom View                                          | 27 |

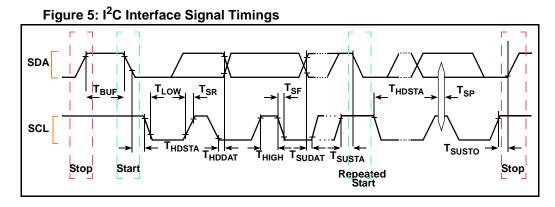

| Figure 5:  | I2C Interface Signal Timings                                           | 41 |

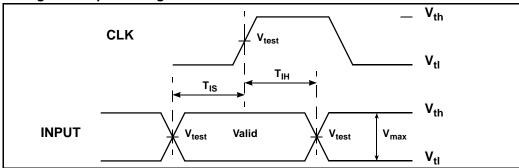

| Figure 6:  | Input Timing Measurement Waveforms                                     | 43 |

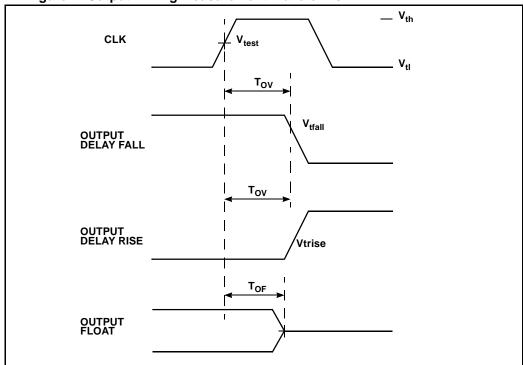

| Figure 7:  | Output Timing Measurement Waveforms                                    | 43 |

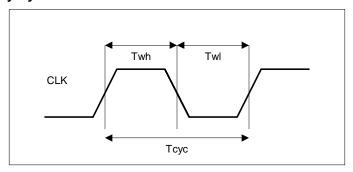

| Figure 8:  | Duty Cycle Definition Waveforms                                        | 44 |

| Figure 9:  | Serial Interface Transmitter and Receiver signal waveforms             | 44 |

| Figure 10: | Serial Reference Clock Waveforms                                       |    |

| Figure 11: | Recommended Edge Coupled Differential Stripline (symmetric when h1=h2) | 48 |

| Figure 12: | Not Recommended Broadside Coupled or Dual Stripline Construction       | 49 |

| Figure 13: | Differential Microstrip Construction.                                  | 49 |

| Figure 14: | Equation                                                               | 51 |

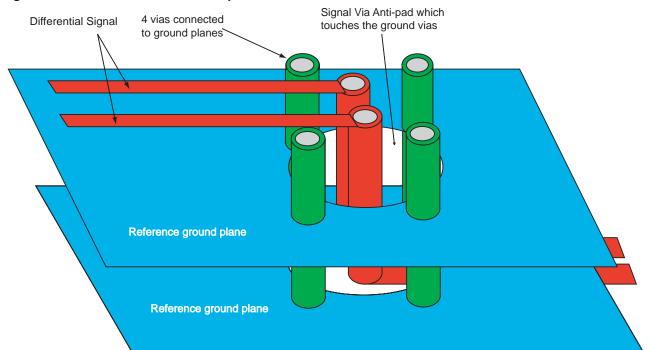

| Figure 15: | Differential Controlled Impedance Via                                  | 52 |

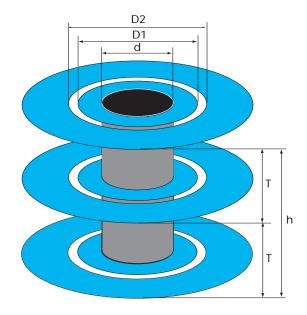

| Figure 16: | Via Construction                                                       | 53 |

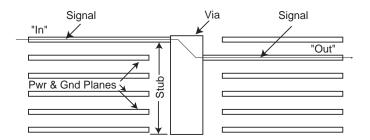

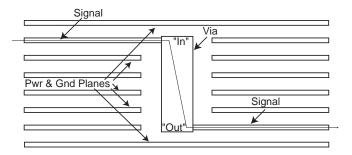

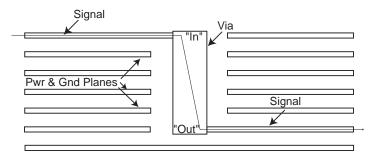

| Figure 17: | Signal Across a Via                                                    | 53 |

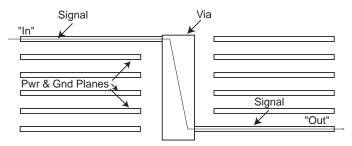

| Figure 18: | Signal Through a Via.                                                  | 54 |

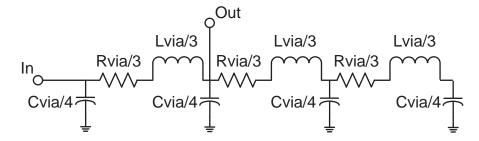

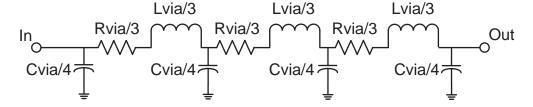

| Figure 19: | Signal Transitioning Across a Via Simulation Model                     | 54 |

| Figure 20: | Signal Transitioning Through a Via Simulation Model                    | 54 |

| Figure 21: | Buried Via Example                                                     | 55 |

| Figure 22: | Blind Via Example                                                      | 55 |

| Figure 23: | Serpentine Signal Routing                                              | 56 |

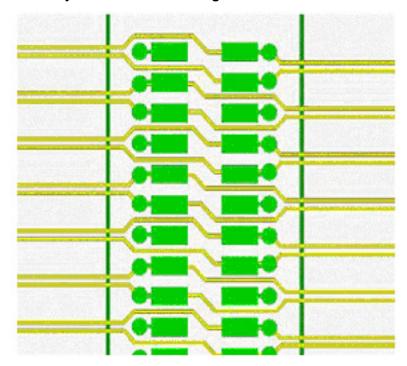

| Figure 24: | Receiver Coupling Capacitor Positioning Recommendation                 | 57 |

| Figure 25: | Escape Routing for Differential Signal Pairs                           | 58 |

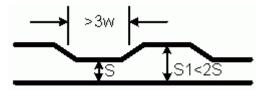

| Figure 26: | Differential Skew Matching Serpentine                                  |    |

| Figure 27: | Recommended Board Stackup                                              | 59 |

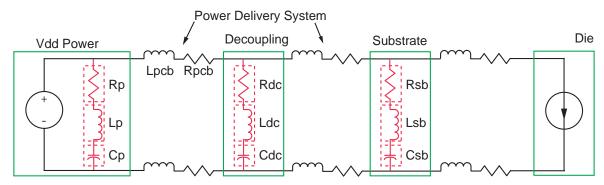

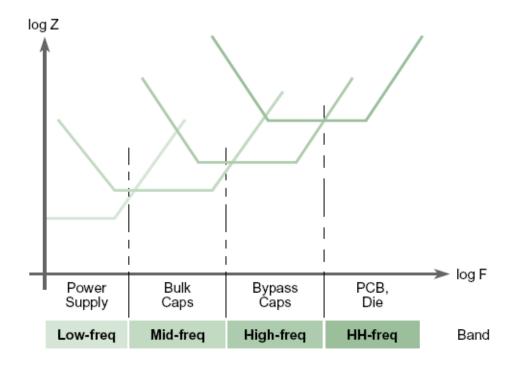

| Figure 28: | System Power Supply Model                                              | 61 |

| Figure 29: | PLL Filter                                                             | 61 |

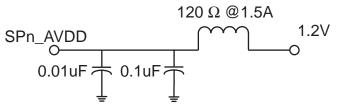

| Figure 30: | Recommended Decoupling Capacitor Pad Designs                           | 62 |

| Figure 31: | Decoupling Bypass Frequency Bands                                      | 63 |

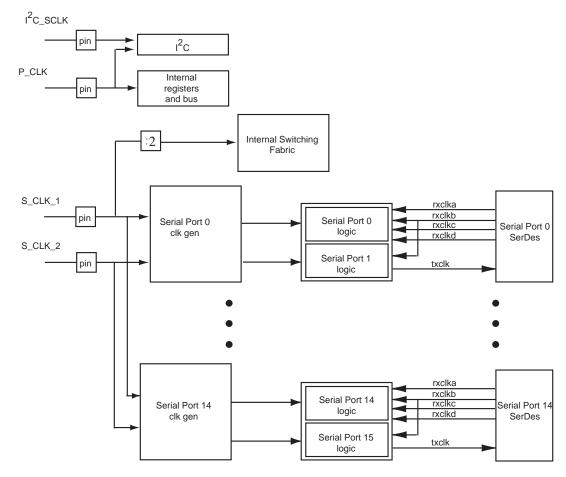

| Figure 32: | Tsi568A Clocking Architecture                                          | 64 |

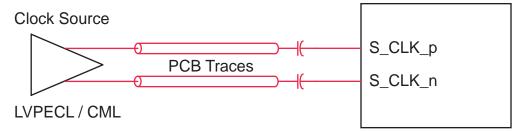

| Figure 33: | Tsi568A driven by LVPECL or CML clock source                           | 67 |

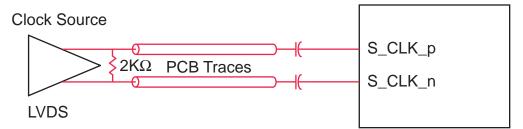

| Figure 34: | Tsi568A driven by an LVDS clock source                                 | 67 |

| Figure 35: | Analyzer Probe Pad Tracking Recommendation                             | 70 |

14 Figures

# **Tables**

| Table 1:  | Signal Types                                                           | 17 |

|-----------|------------------------------------------------------------------------|----|

| Table 2:  | Tsi568A Signal Description                                             | 20 |

| Table 3:  | Package Characteristics                                                | 25 |

| Table 4:  | Thermal Characteristics of Tsi568A                                     | 28 |

| Table 5:  | Simulated Junction to Ambient Characteristics                          | 28 |

| Table 6:  | Absolute Maximum Ratings                                               | 31 |

| Table 7:  | Power Supply Electrical Characteristics and Operating Conditions       | 32 |

| Table 8:  | LVTTL I/O and Open Drain Electrical Characteristics                    | 34 |

| Table 9:  | Serial Interface Receiver Input Electrical Characteristics             | 36 |

| Table 10: | Serial Interface Transmitter Output Electrical Specifications          | 37 |

| Table 11: | Serial Reference Clock Input Electrical Characteristics                |    |

| Table 12: | RapidIO Specification Requirements                                     | 39 |

| Table 13: | Drive Current Register Setting                                         | 39 |

| Table 14: | Idr/Inom Ratios vs. DTX[3:0]Swing into Termination                     | 40 |

| Table 15: | VTT to Output Swing Limits                                             | 40 |

| Table 16: | AC Specifications for I2C Interface                                    | 41 |

| Table 17: | Boundary Scan Test Signal Timings                                      | 42 |

| Table 18: | Decoupling Capacitor Quantities and Values Recommended for the Tsi568A | 61 |

| Table 19: | Clock Input Sources                                                    | 65 |

| Table 20: | Tsi568A Clock Domains                                                  | 66 |

| Table 21: | 8-Channel Probe Pin Assignment                                         | 69 |

| Table 22: | Tsi568A Supported Standard RapidIO Line Rates                          | 73 |

| Table 23: | Tsi568A Supported Non-standard Line Rates                              | 74 |

| Table 24: | Ordering Information                                                   | 75 |

16 Tables

# 1. Signals and Packaging

This chapter describes the packaging (mechanical) features for the Tsi568A. It includes the following information:

- "Pinlist" on page 17

- "Signals" on page 17

- "Package Characteristics" on page 25

- "Thermal Characteristics" on page 28\

### 1.1 Pinlist

Please refer to the *Tsi568A User Manual* and the Tundra website at www.tundra.com for information on the package pinlist and ballmap.

# 1.2 Signals

The following conventions are used in the pin description table:

- Signals with the suffix "\_p" are the positive half of a differential pair.

- Signals with the suffix "\_n" are the negative half of a differential pair.

- Signals with the suffix "\_b" are active low.

- DDR signals are Double Data Rate, data is transferred on both edges of the associated clock.

Signals are classified according to the types defined in Table 1 on page 17.

Table 1: Signal Types

| Pin Type | Definition                                                                       |

|----------|----------------------------------------------------------------------------------|

| I        | Input                                                                            |

| 0        | Output                                                                           |

| I/O      | Input/Output                                                                     |

| OD       | Open Drain                                                                       |

| SRIO     | CML driver/receiver defined by RapidIO Interconnect Specification (Revision 1.2) |

| PU       | Pulled Up internal to the Tsi568A                                                |

| PD       | Pulled Down internal to the Tsi568A                                              |

Table 1: Signal Types (Continued)

| Pin Type    | Definition            |

|-------------|-----------------------|

| Hyst        | Hysteresis            |

| Core Power  | Core supply           |

| Core Ground | Ground for core logic |

| I/O Power   | I/O supply            |

### 1.2.1 Endian Ordering

This document follows the bit-numbering convention adopted by *RapidIO Interconnect Specification* (*Revision 1.2*), where [0:7] is used to represent an 8 bit bus with bit 0 as the most-significant bit.

## 1.2.2 Signal Groupings

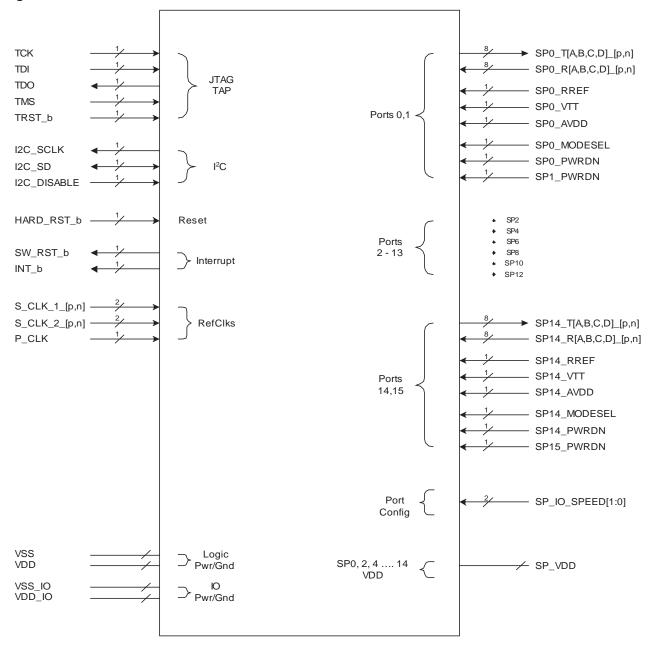

Figure 1 summarizes the Tsi568A signals.

1. Signals and Packaging 19

Figure 1: Tsi568A Pinout List

Table 2 describes the Tsi568A signals.

Table 2: Tsi568A Signal Description

| Pin Name                                                            | Pin<br>Count                                                                                               | Туре       | Description                                                                                                                                |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                     | PORT n - 1x/4x Mode Serial RapidIO PORT (n+1) - 1x Mode Serial RapidIO where n = 0, 2, 4, 6, 8, 10, 12, 14 |            |                                                                                                                                            |  |  |  |

|                                                                     | SERIAL                                                                                                     | PORT n/n+  | 1 TRANSMIT where n = 0, 2, 4, 6, 8, 10, 12, 14                                                                                             |  |  |  |

| SP{n}_TA_p                                                          | 1                                                                                                          | O, SRIO    | Port n Lane A Differential Non-inverting Transmit Data output (4x mode) Port n Differential Non-inverting Transmit Data output (1x mode)   |  |  |  |

| SP{n}_TA_n                                                          | 1                                                                                                          | O, SRIO    | Port n Lane A Differential Inverting Transmit Data output (4x mode) Port n Differential Inverting Transmit Data output (1x mode)           |  |  |  |

| SP{n}_TB_p                                                          | 1                                                                                                          | O, SRIO    | Port n Lane B Differential Non-inverting Transmit Data output (4x mode) Port n+1 Differential Non-inverting Transmit Data output (1x mode) |  |  |  |

| SP{n}_TB_n                                                          | 1                                                                                                          | O, SRIO    | Port n Lane B Differential Inverting Transmit Data output (4x mode) Port n+1 Differential Inverting Transmit Data output (1x mode)         |  |  |  |

| SP{n}_TC_p                                                          | 1                                                                                                          | O, SRIO    | Port n Lane C Differential Non-inverting Transmit Data output (4x mode)                                                                    |  |  |  |

| SP{n}_TC_n                                                          | 1                                                                                                          | O, SRIO    | Port n Lane C Differential Inverting Transmit Data output (4x mode)                                                                        |  |  |  |

| SP{n}_TD_p                                                          | 1                                                                                                          | O, SRIO    | Port n Lane D Differential Non-inverting Transmit Data output (4x mode)                                                                    |  |  |  |

| SP{n}_TD_n                                                          | 1                                                                                                          | O, SRIO    | Port n Lane D Differential Inverting Transmit Data output (4x mode)                                                                        |  |  |  |

|                                                                     | SERIAL                                                                                                     | . PORT n/n | +1 RECEIVE where n = 0, 2, 4, 6, 8, 10, 12, 14                                                                                             |  |  |  |

| SP{n}_RA_p                                                          | 1                                                                                                          | I, SRIO    | Port n Lane A Differential Non-inverting Receive Data input (4x node)  Port n Differential Non-inverting Receive Data input (1x mode)      |  |  |  |

| SP{n}_RA_n                                                          | 1                                                                                                          | I, SRIO    | Port n Lane A Differential Inverting Receive Data input (4x node) Port n Differential Inverting Receive Data input (1x mode)               |  |  |  |

| SP{n}_RB_p                                                          | 1                                                                                                          | I, SRIO    | Port n Lane B Differential Non-inverting Receive Data input (4x mode) Port n+1 Differential Non-inverting Receive Data input (1x mode)     |  |  |  |

| SP{n}_RB_n                                                          | 1                                                                                                          | I, SRIO    | Port n Lane B Differential Inverting Receive Data input (4x mode) Port n+1 Differential Inverting Receive Data input (1x mode)             |  |  |  |

| SP{n}_RC_p                                                          | 1                                                                                                          | I, SRIO    | Port n Lane C Differential Non-inverting Receive Data input (4x mode)                                                                      |  |  |  |

| SP{n}_RC_n                                                          | 1                                                                                                          | I, SRIO    | Port n Lane C Differential Inverting Receive Data input (4x mode)                                                                          |  |  |  |

| SP{n}_RD_p                                                          | 1                                                                                                          | I, SRIO    | Port n Lane D Differential Non-inverting Receive Data input (4x mode)                                                                      |  |  |  |

| SP{n}_RD_n                                                          | 1                                                                                                          | I, SRIO    | Port n Lane D Differential Inverting Receive Data input (4x mode)                                                                          |  |  |  |

| SERIAL PORT n/n+1 CONFIGURATION where n = 0, 2, 4, 6, 8, 10, 12, 14 |                                                                                                            |            |                                                                                                                                            |  |  |  |

1. Signals and Packaging 21

Table 2: Tsi568A Signal Description (Continued)

| Pin Name                 | Pin<br>Count | Туре               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP{n}_RREF               | 1            |                    | Used to connect a 1K +/-1% resistor to SP{n}_AVDD to provide a reference current for the driver and equalization circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SP{n}_MODESEL            | 1            | I/O,<br>CMOS<br>PD | Selects the serial port operating mode for ports n and n+1 0 - Port n operating in 4x mode (Port n+1 not available) 1 - Ports n and n+1 operating in 1x mode Must remain stable for 10 P_CLK cycles after HW_RST_b is de-asserted in order to be sampled correctly. Ignored after reset.                                                                                                                                                                                                                                                                         |

| SP{n}_PWRDN              | 1            | I/O,<br>CMOS<br>PU | Port n Transmit and Receive Power Down control This signal controls the state of Port n and Port n+1 The PWRDN controls the state of all four lanes (A/B/C/D) of SerDes Macro. 0 - Port n Powered Up. Port n+1 controlled by SP{n+1}_PWRDN. 1 - Port n Powered Down. Port n+1 Powered Down. Override SP{n}_PWRDN using PWDN_x1 field in SRIO MAC x Clock Selection Register Output capability of this pin is only used in test mode. Must remain stable for 10 P_CLK cycles after HW_RST_B is de-asserted in order to be sampled correctly. Ignored after reset. |

| SP{n+1}_PWRDN            | 1            | I/O,<br>CMOS<br>PU | Port n+1 Transmit and Receive Power Down control This signal controls the state of Port n+1. Note that Port n+1 is never used when 4x mode is selected for a Serial Rapid IO MAC, and it must be powered down.  0 - Port n+1 Powered Up 1 - Port n+1 Powered Down Override SP{n+1}_PWRDN using PWDN_x4 field in SRIO MAC x Clock Selection Register.  Output capability of this pin is only used in test mode.  Must remain stable for 10 P_CLK cycles after HW_RST_B is de-asserted in order to be sampled correctly. Ignored after reset.                      |

| SERIAL PORT SPEED SELECT |              |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 2: Tsi568A Signal Description (Continued)

| Pin Name       | Pin<br>Count | Туре                | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|--------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SP_IO_SPEED[1] | 1            | I/O,<br>CMOS,<br>PD | Serial Port Transmit and Receive operating frequency select, bit 1. When combined with SP_IO_SPEED[0], this pin selects the default serial port frequency for all ports.  00 - S_CLK_2 reference divided by 2                                                                                                                                                                                    |

|                |              |                     | 01 - S_CLK_2 reference (default)                                                                                                                                                                                                                                                                                                                                                                 |

|                |              |                     | 10 - S_CLK_1 reference                                                                                                                                                                                                                                                                                                                                                                           |

|                |              |                     | 11 - reserved                                                                                                                                                                                                                                                                                                                                                                                    |

|                |              |                     | The output data rate per lane is 10 times the selected input clock.                                                                                                                                                                                                                                                                                                                              |

|                |              |                     | Selects the speed at which the ports operates when reset is removed. This could be either due to HARD_RST_b being de-asserted or by the completion of a self-reset.                                                                                                                                                                                                                              |

|                |              |                     | This signal must remain stable for 10 P_CLK cycles after HW_RST_B is de-asserted in order to be sampled correctly. The signal is ignored after reset.                                                                                                                                                                                                                                            |

|                |              |                     | The SP_IO_SPEED[1:0] setting is equal to the SCLK_SEL field in the SRIO MAC x Clock Selection Register                                                                                                                                                                                                                                                                                           |

|                |              |                     | Output capability of this pin is only used in test mode.                                                                                                                                                                                                                                                                                                                                         |

| SP_IO_SPEED[0] | 1            | I/O,<br>CMOS,       | See SP_IO_SPEED[1]                                                                                                                                                                                                                                                                                                                                                                               |

|                |              | PU                  |                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |              |                     | CLOCK and RESET                                                                                                                                                                                                                                                                                                                                                                                  |

| P_CLK          | 1            | 1                   | This clock is used for the register bus clock.                                                                                                                                                                                                                                                                                                                                                   |

|                |              | CMOS                | The maximum frequency of this input clock is 100 MHz.                                                                                                                                                                                                                                                                                                                                            |

| S_CLK_1_p      | 1            | I<br>CML            | Differential non-inverting reference clock. The clock is used for following purposes: SerDes reference clock, serial port system clock, ISF clock (equal to half of this clock) and test clock. The clock frequency is defined in the Minimum Clock Frequency Requirements section.                                                                                                              |

|                |              |                     | The maximum frequency of this input clock is 312.5 MHz.  If this clock input is not used, pull this signal up.                                                                                                                                                                                                                                                                                   |

|                |              |                     | ir this clock input is not used, pair this signar up.                                                                                                                                                                                                                                                                                                                                            |

| S_CLK_1_n      | 1            | CML                 | Differential inverting reference clock. The clock is used for following purposes: SerDes reference clock, serial port system clock, ISF clock (equal to half of this clock) and test clock. The clock frequency is defined in the Minimum Clock Frequency Requirements section. The maximum frequency of this input clock is 312.5 MHz.  If this clock input is not used, pull this signal down. |

| 0.0117.5       |              |                     | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                         |

| S_CLK_2_p      | 1            | CML                 | Differential non-inverting reference clock. The clock is used for following purposes: SerDes reference clock, serial port system clock, 125MHz clock (equal to half of this clock) and test clock. The clock frequency is defined in the Minimum Clock Frequency Requirements section.                                                                                                           |

|                |              |                     | The maximum frequency of this input clock is 250 MHz.  If this clock input is not used, pull this signal up.                                                                                                                                                                                                                                                                                     |

|                |              |                     | in this clock input is not used, pull this signal up.                                                                                                                                                                                                                                                                                                                                            |

Table 2: Tsi568A Signal Description (Continued)

| Pin Name    | Pin<br>Count          | Туре                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------------|-----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| S_CLK_2_n   | 1                     | I<br>CML                  | Differential inverting reference clock. The clock is used for following purposes: SerDes reference clock, serial port system clock, 125MHz clock (equal to half of this clock) and test clock. The clock frequency is defined in the Minimum Clock Frequency Requirements section. The maximum frequency of this input clock is 250 MHz.  If this clock input is not used, pull this signal down.                                                                              |  |  |  |  |  |

| HARD_RST_b  | 1                     | I<br>CMOS,<br>Hyst,<br>PU | Schmidt-triggered hard reset. Asynchronous active low reset for the entire device.                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|             |                       |                           | INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| INT_b       | 1                     | O, OD,<br>CMOS            | Interrupt signal (open drain output)                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| SW_RST_b    | 1                     | O, OD,<br>CMOS            | Software reset (open drain output): This signal is asserted when a RapidIO port receives a valid reset request on a RapidIO link. If self-reset is not selected, this pin remains asserted until the reset request is cleared from the status registers. If self-reset is selected, this pin remains asserted until the self reset is complete. If the Tsi568A is reset from the HARD_RST_b pin, this pin is de-asserted and remains de-asserted after HARD_RST_b is released. |  |  |  |  |  |

|             |                       |                           | I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| I2C_SCLK    | 1                     | O, OD,<br>CMOS,<br>PU     | I <sup>2</sup> C clock, up to 100 kHz. Although this clock is open drain, the I2C controller does not support multiple bus masters. This clock signal must be connected to the clock of the serial EEPROM on the I2C bus.                                                                                                                                                                                                                                                      |  |  |  |  |  |

| I2C_SD      | 1                     | I/O, OD,<br>CMOS,P<br>U   | I <sup>2</sup> C input and output data bus (bidirectional open drain)                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| I2C_DISABLE | -                     | I,<br>CMOS,<br>PD         | Disable I <sup>2</sup> C register loading after reset. When asserted, the Tsi568A will not attempt to load register values from I <sup>2</sup> C.  0 - Enable I <sup>2</sup> C register loading  1- Disable I <sup>2</sup> C register loading                                                                                                                                                                                                                                  |  |  |  |  |  |

|             | JTAG / TAP CONTROLLER |                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| тск         | 1                     | I,<br>CMOS,<br>PD         | IEEE 1149.1 Test Access Port - Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TDI         | 1                     | I,<br>CMOS,<br>PU         | IEEE 1149.1 Test Access Port - Serial Data Input                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

Table 2: Tsi568A Signal Description (Continued)

| Pin Name               | Pin<br>Count | Туре                                                                       | Description                                                                                        |  |  |  |  |

|------------------------|--------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| 1 111 11441110         | - Count      | .,,,,,                                                                     | 2000/ipii0/ii                                                                                      |  |  |  |  |

| TDO                    | 1            | O,<br>CMOS                                                                 | IEEE 1149.1 Test Access Port - Serial Data Output                                                  |  |  |  |  |

| TMS                    | 1            | I,<br>CMOS,<br>PU                                                          | IEEE 1149.1 Test Access Port - Test Mode Select                                                    |  |  |  |  |

| TRST_b                 | 1            | I,                                                                         | IEEE 1149.1 Test Access Port - TAP Reset Input                                                     |  |  |  |  |

|                        |              | CMOS,<br>PU                                                                |                                                                                                    |  |  |  |  |

| POWER SUPPLIES         |              |                                                                            |                                                                                                    |  |  |  |  |

|                        |              | PORT                                                                       | n/n+1 n = 0, 2, 4, 6, 8, 10, 12, 14                                                                |  |  |  |  |

| SP{n}_AVDD             | 1            | -                                                                          | Port n & n+1: 1.2V supply for bias generator circuitry. This is required to be a low-noise supply. |  |  |  |  |

| SP{n}_VTT              | 1            | -                                                                          | Port n & n+1: Driver termination voltage - common to all lanes                                     |  |  |  |  |

|                        |              |                                                                            | COMMON SUPPLY                                                                                      |  |  |  |  |

| VDD_IO                 | 15           | -                                                                          | Common 3.3V supply for CMOS I/O                                                                    |  |  |  |  |

| VSS_IO                 | 12           | -                                                                          | Common ground supply for I/Os                                                                      |  |  |  |  |

| VSS                    | 285          | -                                                                          | Common ground supply for digital logic                                                             |  |  |  |  |

| VDD                    | 50           | -                                                                          | Common 1.2V supply for digital logic                                                               |  |  |  |  |

| SP_VDD                 | 114          | 1.2V supply for CDR, Tx/Rx, and digital logic for all Serial RapidIO ports |                                                                                                    |  |  |  |  |

| Total Power and Ground |              |                                                                            | 474                                                                                                |  |  |  |  |

# 1.3 Package Characteristics

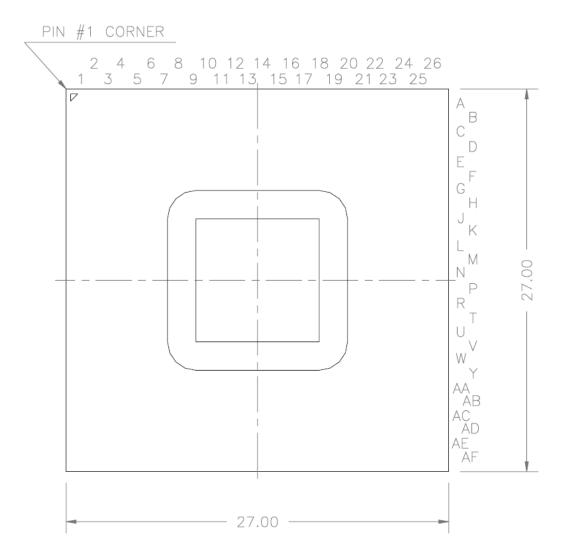

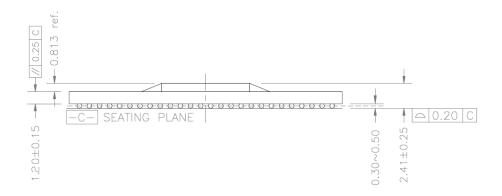

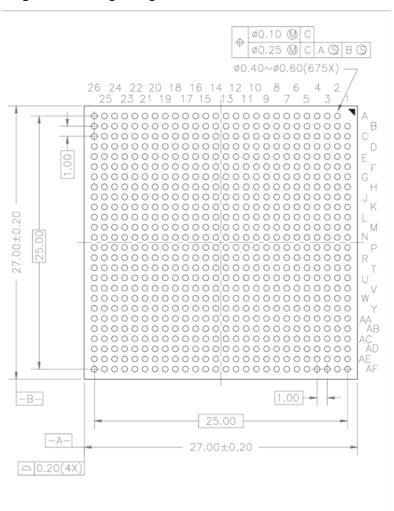

Tsi568A's package characteristics are summarized in the following table. Figure 2 and Figure 3 illustrates the Top and Side views of the Tsi568A package. Figure 4 presents the Bottom view of the device.

**Table 3: Package Characteristics**

| Feature                    | Description                       |

|----------------------------|-----------------------------------|

| Package Type               | Flip-Chip Ball Grid Array (FCBGA) |

| Package Body Size          | 27x27 mm                          |

| JEDEC Specification        | 95-1 Section 14                   |

| Pitch                      | 1.00 mm                           |

| Ball pad size              | 500 um                            |

| Soldermask opening         | 400 um                            |

| Moisture Sensitivity Level | 4                                 |

Figure 2: Package Diagram — Top view

Figure 3: Package Diagram — Side View

Figure 4: Package Diagram — Bottom View

### 1.4 Thermal Characteristics

Heat generated by the packaged IC has to be removed from the package to ensure that the IC is maintained within its functional and maximum design temperature limits. If heat buildup becomes excessive, the IC temperature may exceed the temperature limits. A consequence of this is that the IC may fail to meet the performance specifications and the reliability objectives may be affected.

Failure mechanisms and failure rate of a device have an exponential dependence of the IC operating temperatures. Thus, the control of the package temperature, and by extension the Junction Temperature, is essential to ensure product reliability. The Tsi568A is specified safe for operation when the Junction Temperature is within the recommended limits.

Table 4 shows the simulated Theta jb and Theta jc thermal characteristics of the Tsi568A FCBGA package.

Table 4: Thermal Characteristics of Tsi568A

| Interface                    | Result       |

|------------------------------|--------------|

| Theta jb (junction to board) | 11.8 °C/watt |

| Theta jc (junction to case)  | 0.09 °C/watt |

### 1.4.1 Junction-to-Ambient Thermal Characteristics (Thetaja)

Table 5 shows the simulated Theta ja thermal characteristic of the Tsi568A FCBGA package. The results in Table 5 are based on a JEDEC Thermal Test Board configuration (JESD51-9) and do not factor in system level characteristics. As such, these values are for reference only.

The Theta ja thermal resistance characteristics of a package depend on multiple system level variables.

**Table 5: Simulated Junction to Ambient Characteristics**

|               | Theta ja at | specified airflow (no l | Heat Sink)   |

|---------------|-------------|-------------------------|--------------|

| Package       | 0 m/s       | 1 m/s                   | 2 m/s        |

| Tsi568A FCBGA | 14.3 C/watt | 13.5 °C/watt            | 12.8 °C/watt |

#### 1.4.1.1 System-level Characteristics

In an application, the following system-level characteristics and environmental issues must be taken into account:

- Package mounting (vertical / horizontal)

- System airflow conditions (laminar / turbulent)

- Heat sink design and thermal characteristics (see "Heatsink Requirement and Analysis" on page 29)

- Heat sink attachment method (see "Heatsink Requirement and Analysis" on page 29)

- PWB size, layer count and conductor thickness

- Influence of the heat dissipating components assembled on the PWB (neighboring effects)

### Example on Thermal Data Usage

Based on the Theta<sub>JA</sub> data and specified conditions, the following formula can be used to derive the junction temperature (Tj) of the Tsi568A with a 0m/s airflow:

•  $Tj = \theta_{JA} * P + Tamb$

Where: Tj is Junction Temperature, P is the Power consumption, Tamb is the Ambient Temperature

Assuming a power consumption (P) of 3.5 W and an ambient temperature (Tamb) of 70°C, the resulting junction temperature (Tj) would be 121.1°C.

### 1.4.2 Heatsink Requirement and Analysis

The Tsi568A is packaged in a Flip-Chip Ball Grid Array (FCBGA). With this package technology, the silicon die is exposed and serves as the interface between package and heatsink. Where a heatsink is required to maintain junction temperatures at or below specified maximum values, it is important that attachment techniques and thermal requirements be critically analyzed to ensure reliability of this interface. Factors to be considered include: surface preparations, selection of thermal interface materials, curing process, shock and vibration requirements, and thermal expansion coefficients, among others. Each design should be individually analyzed to ensure that a reliable thermal solution is achieved.

#### 1.4.2.1 Heatsink Attachment

Both mechanical and adhesive techniques are available for heatsink attachment.

Both mechanical and adhesive techniques are available for heatsink attachment. Tundra makes no recommendations as to the reliability or effectiveness of either approach. The designer must critically analyze heatsink requirements, selection criteria, and attachment techniques.

For heatsink attachment methods that induce a compressive load to the FCBGA package, the maximum force that can be applied to the package should be limited to 5 gm / BGA ball (provided that the board is supported to prevent any flexing or bowing). The maximum force for the Tsi568A package is 3.38 Kg.

# 2. Electrical Characteristics

This chapter provides the electrical characteristics for the Tsi568A. It includes the following information:

- "Absolute Maximum Ratings" on page 31

- "Electrical Characteristics and Operating Conditions" on page 32

- "AC Timing Waveforms" on page 43

# 2.1 Absolute Maximum Ratings

Operating the device beyond the operating conditions is not recommended. Stressing the Tsi568A beyond the Absolute Maximum Rating can cause permanent damage.

Table 6 lists the absolute maximum ratings.

**Table 6: Absolute Maximum Ratings**

| Symbol                              | Parameter                                     | Min  | Max                     | Unit |

|-------------------------------------|-----------------------------------------------|------|-------------------------|------|

| T <sub>storage</sub>                | Storage Temperature                           | -55  | 125                     | °C   |

| T <sub>case</sub> (T <sub>j</sub> ) | Case Temperature under Bias                   | -40  | 120                     | °C   |

| V <sub>DD_33</sub>                  | 3.3V DC Supply Voltage                        | -0.5 | 4.6                     | V    |

| $V_{DD}$ , $SP_{-}V_{DD}$           | 1.2V DC Supply Voltage                        | -0.5 | 1.7                     | V    |

| SP{n}_AV <sub>DD</sub>              | 1.2V Analogue Supply voltage                  | -0.5 | 1.7                     | V    |

| SP{n}_V <sub>TT</sub>               | Driver Termination Voltage                    | -0.5 | 2.5                     | V    |

| $V_{I\_SP\{n\}-R\{A-D\}\_\{p,n\}}$  | SERDES Port CML Receiver Input<br>Voltage     | -0.3 | 3                       | V    |

| $V_{O\_SP\{n\}-T\{A-D\}\_\{p,n\}}$  | SERDES Port CML Transmitter Output<br>Voltage | -0.3 | 3                       | V    |

| V <sub>I_LVTTL</sub>                | LVTTL Input Voltage                           | -0.5 | V <sub>DD_33</sub> +0.5 | V    |

| V <sub>O_LVTTL</sub>                | LVTTL Output or I/O Voltage                   | -0.5 | V <sub>DD_33</sub> +0.5 | V    |

32 2. Electrical Characteristics

**Table 6: Absolute Maximum Ratings**

| Symbol               | Parameter                                                                                                                           | Min | Max  | Unit |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| V <sub>ESD_HBM</sub> | Maximum ESD Voltage Discharge<br>Tolerance for Human Body Model (HBM).<br>[Test Conditions per JEDEC standard -<br>JESD22-A114-B]   |     | 1000 | ٧    |

| V <sub>ESD_CDM</sub> | Maximum ESD Voltage Discharge<br>Tolerance for Charged Device Model<br>(CDM). Test Conditions per JEDEC<br>standard - JESD22-C101-A |     | 300  | V    |

# 2.2 Electrical Characteristics and Operating Conditions

Table 7 lists the recommended operating conditions and electrical characteristics for the power supply pins of the Tsi568A.

**Table 7: Power Supply Electrical Characteristics and Operating Conditions**

| Symbol                        | Parameter                          | Min  | Тур | Max  | Unit | Notes                                                                                                                                                                                                                                      |

|-------------------------------|------------------------------------|------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tj                            | Junction temperature               | -40  |     | 120  | °C   |                                                                                                                                                                                                                                            |

| V <sub>DD_33</sub>            | 3.3V DC Supply Voltage             | 2.97 |     | 3.63 | ٧    | Maximum AC voltage ripple must be less than 2.5% measured at device pin                                                                                                                                                                    |

| SP_VDD,<br>VDD,<br>SP{n}_AVDD | 1.2V DC Supply Voltage             | 1.14 |     | 1.29 | ٧    | Maximum AC voltage ripple must be less than 2.5% measured at device pin                                                                                                                                                                    |

| SP{n}_VTT                     | 1.2V Driver Termination<br>Voltage | 1.14 |     | 1.26 | V    | Maximum AC voltage ripple must be less than 2.5% measured at device pin                                                                                                                                                                    |

|                               | 1.5V Driver Termination<br>Voltage | 1.42 |     | 1.58 | V    | Maximum AC voltage ripple must be less than 2.5% measured at device pin                                                                                                                                                                    |

|                               | 1.8V Driver Termination<br>Voltage | 1.71 |     | 1.89 | V    | Maximum AC voltage ripple must be less than 2.5% measured at device pin                                                                                                                                                                    |

| I <sub>VDD</sub>              | Core Supply Current                |      |     | 2420 | mA   | I <sub>VDD</sub> (in mA) = (I_VDDC1 x<br>N1)+(I_VDDC4 x N4), where I_VDDC1 is<br>the active x1 port current, N1 is the<br>number of active x1 ports, I_VDDC4 is<br>the active x4 port current, and N4 is the<br>number of x4 ports active. |

|                               |                                    |      |     |      |      | I_VDDC1(in mA) = 0.0361 x F + 38.4,<br>where F is the SERDES port frequency of<br>operation in MHz                                                                                                                                         |

|                               |                                    |      |     |      |      | I_VDDC4(in mA) = 0.062 x F + 72.7,<br>where F is the SERDES port frequency of<br>operation in MHz                                                                                                                                          |

2. Electrical Characteristics 33

**Table 7: Power Supply Electrical Characteristics and Operating Conditions**

| Symbol               | Parameter                            | Min | Тур | Max  | Unit | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|--------------------------------------|-----|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>VDD_33</sub>  | 3.3V IO Supply Current               |     |     | 10   | mA   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I <sub>SP_VDD</sub>  | SERDES Digital Supply<br>Current     |     |     | 2600 | mA   | I <sub>SP_VDD</sub> (in mA)=0.026xCxNxF, where C is the number of active SERDES channels, N is the number of active SERDES ports, and F is the SERDES port frequency of operation in MHz                                                                                                                                                                                                                                                                                          |

| I <sub>SP—AVDD</sub> | SERDES Analog<br>Supply Current      |     |     | 80   | mA   | I <sub>SP_AVDD</sub> (in mA)=10xN, where N is the number of SERDES Ports active Brent to get Cpk of 2 number                                                                                                                                                                                                                                                                                                                                                                      |

| I <sub>SP_VTT</sub>  | SERDES Termination<br>Supply Current |     |     | 1140 | mA   | I <sub>SP_VTT</sub> =Inom x RIdr/Inom x C x N, where Ridr/Inom is the Idr to Inom ratio, C is the number of active SERDES channels, and N is the number of SERDES Ports with termination active.                                                                                                                                                                                                                                                                                  |

| PD_Core              | Core Power Dissipation               |     |     | 3050 | mW   | PD_Core(in mW)= VDD x Rvdd/vdd_max x I_VDDC, where Rvdd/vdd_max is the ratio of VDD to VDD_MAX, and I_VDDC is the core current calculated for the Core Supply Current Parameter                                                                                                                                                                                                                                                                                                   |

| PD_IO                | IO Power Dissipation                 |     |     | 5570 | mW   | PD_IO(in mW)= (SP_VDD x Rsp_vdd/sp_vddmax x ISP_VDD) + (VDD33 x Rvdd33/vdd33_max x I_VDD33) + (SP_AVDD x Rsp_avdd/sp_avddmax x ISP_AVDD) + (SP_VTT x ISP_VTT), where Rxxxx/xxxx is the ratio of the supply voltage to the supply voltage maximum, ISP_VDD is the SERDES Digital Supply Current parameter, I_VDD33 is the 3.3V IO Supply Current parameter, ISP_AVDD is the SERDES Analog Supply Current parameter, and ISP_VTT is the SERDES Termination Supply Current parameter |

| PD_standby           | Standby Power<br>Dissipation         |     |     | 256  | mW   | PD_standby (in mW) = 32 x N, where N is the number of disabled ports. The standby power of each disabled port must be included in the total power dissipation calculation. The value shown here is for 8 ports in standby.                                                                                                                                                                                                                                                        |

| PD                   | Total Power Dissipation              |     |     | 7890 | mW   | This parameter is configuration dependent and can be calculated from the PD_Core, PD_IO, and PD_standby parameters for a given configuration. The number shown here is for the Maximum power configuration of 8 x4 ports operating at 3.125Gb/s                                                                                                                                                                                                                                   |

34 2. Electrical Characteristics

### 2.2.1 Power Sequencing

The recommended power sequence for the Tsi568A is in the following order:

- VDD (1.2V), SP\_VDD, and SP{n}\_VDDA (1.2V) power-up together

- $SP\{n\}_VTT$

- VDD\_IO (3.3V)

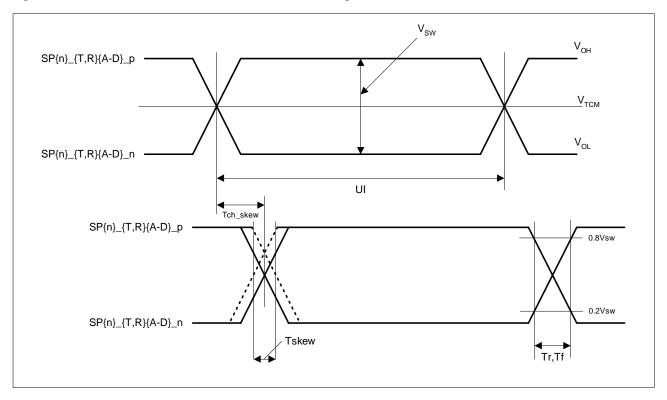

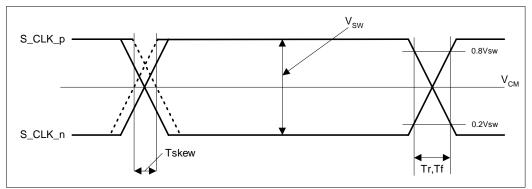

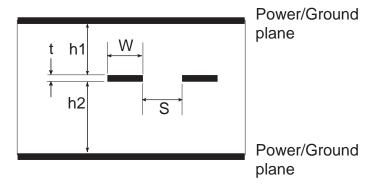

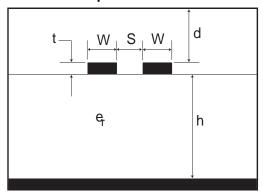

It is recommended that there not be more than 50ms between ramping of the 1.2V and 3.3V supplies. The power supply ramp rates must be kept between 10V/sec and  $1x10^6V/\text{sec}$  to minimize power current spikes during power up. For applications requiring Power sequencing that is different than the recommended sequence, please contact Tundra Applications Engineering.