# PTN5100 USB Type-C power delivery PHY and protocol IC Rev. 1.1 – 25 July 2017 Pro

**Product data sheet**

## 1. General description

PTN5100 is a single port USB Type-C Power Delivery (PD) PHY and Protocol IC that provides Type-C Configuration channel interface and USB PD Physical and Protocol layer functions to a System PD Port Policy Controller (Policy Engine and Device Policy Manager, Alternate mode controller). It complies with USB PD[1] and Type-C[2] specifications and delta updates of PD spec. This IC is targeted for a wide range of platforms (Standard Notebook PCs, Desktop PCs, Chromebooks, Tablets, Convertibles, Smart phones) and PC Accessories (e.g. Docks, Monitors, Cable adapters etc.) applications. PTN5100 is architected to deliver robust performance, compliant behavior, configurability and system implementation flexibility that are essential to tide over interoperability and compliance hurdles in the platform applications.

PTN5100 can support system realization of the following PD roles: (i) Provider (P) only, (ii) Provider/Consumer (P/C) (iii) Consumer only (C) (iv) Consumer/Provider (C/P). Further, it can be register programmed to operate in Type-C specific Upstream Facing Port (UFP), Downstream Facing Port (DFP) or Dual Role Port (DRP) role.

PTN5100 implements VCONN low RON switch with register programmable Forward Current protection feature. The VCON switch also provides Reverse current protection feature to detect reverse current flow into the system whenever (inductive or) charged cable is unplugged from the connector.

PTN5100 operates from platform power supply VDD, or it can also be powered from USB power VBUS directly, which is especially required for operation under Dead Battery (DB) condition and certain platform use cases. The host interface operates on VIO supply to facilitate interfacing to systems that use IO supply rail different from VDD supply rail.

It provides SPI/I2C interface for system host control/status update. The interface choice is pre- configured in NXP factory.

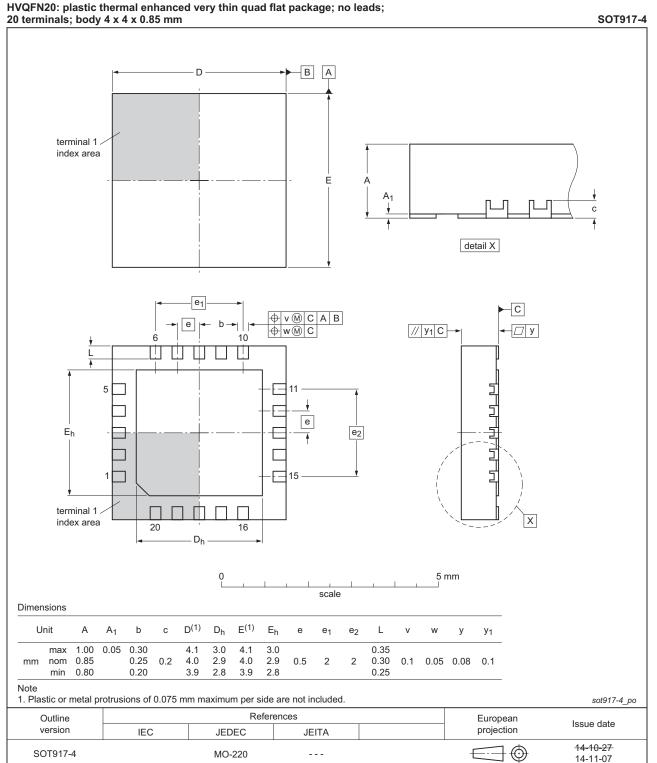

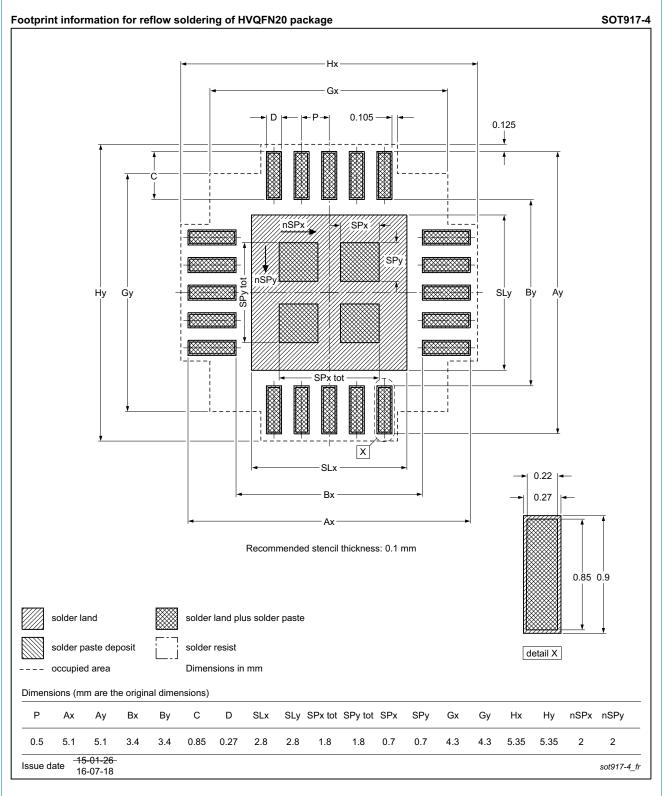

PTN5100 is available in a small footprint package option: HVQFN20 4 mm x 4 mm, 0.5 mm pitch.

## Remark:

- 1. The term 'EC' is used interchangeably with 'Embedded Controller', 'AP', 'Application Processor' or 'System Management Controller, SMC' or System Host Controller throughout this document.

- 2. The terms 'PMIC', 'Power Management Interface Controller', 'Charger IC' are used interchangeably throughout this document.

## 2. Features and benefits

## 2.1 USB PD and Type-C Features

Complies with USB PD[1] and USB Type-C[2] specifications.

- Supports implementation of various system PD roles: P, P/C, C, C/P

- Supports Type-C role configurability

- Type-C role (DFP, UFP, DRP) is Non-Volatile Memory (NVM) and register programmable based on OEM platform requirements

- Implements UFP role pull down behavior to handle dead battery condition on battery powered platforms

- Supports register programmable and variable 'Rp' indication (for DRP/DFP usage and accessory detection)

- Implements 'Rd' indication on CC pin (for Device side implementation)

- CC detection/indication scheme based on Type-C role

- Indication of orientation detection via CC\_ORIENT pin and status register(s)

- Debug and Audio Accessory detection and indication in status register(s)

- Cooperatively works under the control of Policy controller MCU for power delivery negotiation and contract(s), Alternate mode and VDM exchanges

- Implements BMC (de)coding, 4B5B symbol (de)coding, CRC generation/checking, PD packet assembling/disassembling including Preamble, SOP, EOP, Good CRC response, Retries, Hard and Cable resets

- PD PHY and Protocol layer interface control and status update handled via SPI/I2C interface

- SOP\* Configurability

- Register programmable to generate and receive SOP, SOP', SOP'-debug, SOP", SOP"-debug" in DFP/DRP (host use case)

- Register programmable to receive and respond on SOP, SOP'-debug and SOP"-debug commands

- Supports low RON VCONN switch with enable/disable (Hi-Z) support

- Capable of maximum current delivery of 1 A over 2.7 V to 5.5 V

- Supports register programmable Forward current protection control

- Supports register programmable Reverse current protection

## 2.2 System protection features

- Back current protection on all pins when PTN5100 is unpowered

- CC1 and CC2 pins are 5.5 V tolerant

- VBUS pin and VBUS power path MOSFET enable pins are 28 V tolerant

## 2.3 General

- Delivers (active LOW enable) gate control signals for PMOS Power MOSFETs on VBUS source and sink power paths

- Provides dedicated IO pin (CC\_ORIENT) for indicating Cable/plug orientation and IO pin (DBGACC\_FOUND) for indicating Debug accessory detection

- Delivers up to 30 mA (max) for powering Policy controller MCU

- Supports SPI slave interface (SPI modes 1 and 2 supported) up to 30 MHz

- Supports I2C slave interface standard mode (100 kHz), Fast mode (400 kHz) and Fast mode plus (1 MHz)

- I2C Device slave address programmable up to 3 values

- Supports 3.3 V or 1.8 V capable I<sup>2</sup>C-bus or SPI interface

- Supports register access device configuration, control and status/interrupt interfacing through Slave I<sup>2</sup>C-bus interface

- Power supplies VDD (3.3 V ±10 %) or VBUS

- ◆ Tolerant up to 28 V on VBUS and operational up to maximum of 25 V on VBUS

- Operating temperature –20 °C to 85 °C

- ESD 8 kV HBM, 1 kV CDM

- Package: HVQFN20 4 mm × 4 mm, 0.5 mm pitch

## 3. Applications

- PC platforms: Notebook PCs, Desktop PCs, Ultrabooks, Chromebooks

- Tablets, 2:1 Convertibles, Smartphones and Portable devices

- PC accessories/peripherals: Docking, Mobile Monitors, Multi-Function Monitors, Portable/External hard drives, Cable adaptors, Dongles and accessories, etc.

## 4. Ordering information

| Table 1. Ordering inform | ation |

|--------------------------|-------|

|--------------------------|-------|

| Type number | Topside | Package |                                                                                                                                 |          |

|-------------|---------|---------|---------------------------------------------------------------------------------------------------------------------------------|----------|

|             | marking | Name    | Description                                                                                                                     | Version  |

| PTN5100BS   | 5100    | HVQFN20 | plastic thermal enhanced very thin quad flat package;<br>no leads; 20 terminals; body $4 \times 4 \times 0.85 \text{ mm}^{[2]}$ | SOT917-4 |

| PTN5100ABS  | 510A    | HVQFN20 | plastic thermal enhanced very thin quad flat package;<br>no leads; 20 terminals; body $4 \times 4 \times 0.85 \text{ mm}^{[3]}$ | SOT917-4 |

[1] Total height after printed-circuit board mounting <=1 mm (maximum)

[2] Supported system interface - SPI

[3] Supported system interface - I<sup>2</sup>C

## 4.1 Ordering options

| Table 2. Orde | ering options            |         |                                                  |                           |                                                  |

|---------------|--------------------------|---------|--------------------------------------------------|---------------------------|--------------------------------------------------|

| Type number   | Orderable<br>part number | Package | Packing method                                   | Minimum<br>order quantity | Temperature                                      |

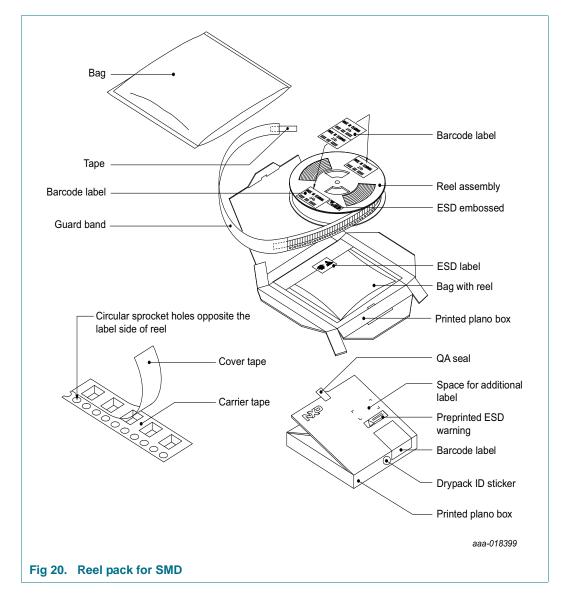

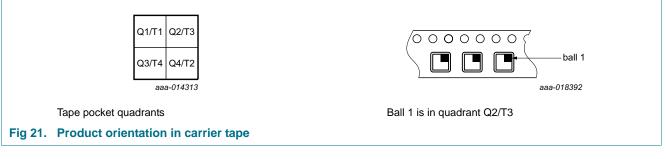

| PTN5100BS     | PTN5100BSMP              | HVQFN20 | Reel 13" Q2/T3<br>*standard mark SMD<br>dry pack | 6000                      | $T_{amb} = -20 \ ^{\circ}C \ to +85 \ ^{\circ}C$ |

| PTN5100ABS    | PTN5100ABSMP             | HVQFN20 | Reel 13" Q2/T3<br>*standard mark SMD<br>dry pack | 6000                      | $T_{amb} = -20 \text{ °C to } +85 \text{ °C}$    |

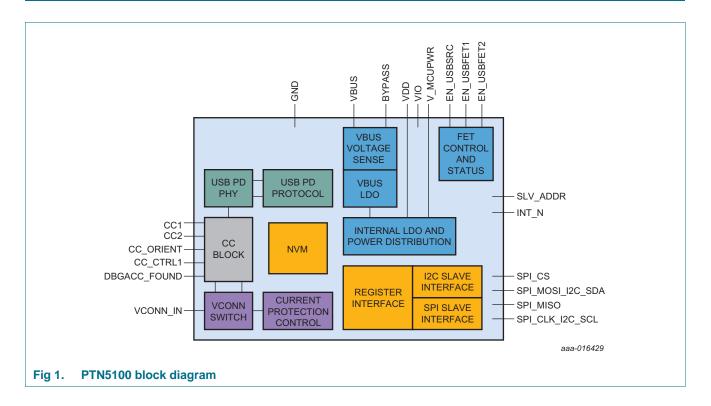

## 5. Block diagram

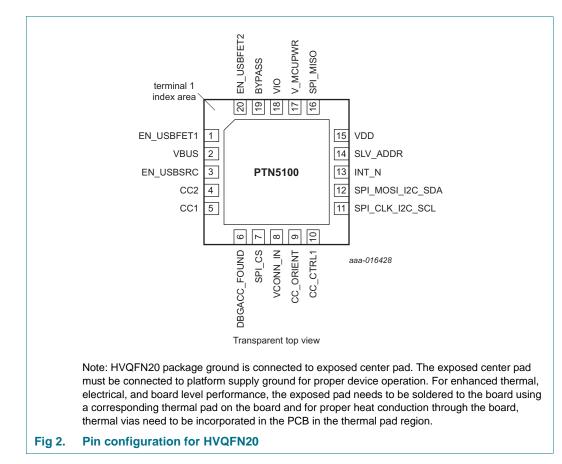

## 6. Pinning information

## 6.1 Pinning

## 6.2 Pin description

| Symbol       | Pin | Pin<br>direction | Pin Type                  | Description                                                                                                                                                                                                              |

|--------------|-----|------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN_USBSRC    | 3   | Output           | Open drain                | USB PD VBUS Source Power path PMOS FET gate Active Low enable.                                                                                                                                                           |

|              |     |                  |                           | At default/POR, this pin is Hi-Z; PTN5100 drives this pin LOW based on Type-C connection state and/or policy controller MCU command.                                                                                     |

|              |     |                  |                           | The pin status can be read in the internal register(s).                                                                                                                                                                  |

| EN_USBFET1   | 1   | Output           | Open drain                | USB PD VBUS Source or Sink Power path PMOS FET gate Active Low enable.                                                                                                                                                   |

|              |     |                  |                           | At default/POR, this pin is Hi-Z; PTN5100 drives this pin LOW based on Type-C connection state and/or policy controller MCU command.                                                                                     |

|              |     |                  |                           | The pin status can be read in the internal register(s).                                                                                                                                                                  |

| EN_USBFET2   | 20  | Output           | Open drain                | USB PD VBUS Source or Sink Power path PMOS<br>FET gate Active Low enable.                                                                                                                                                |

|              |     |                  |                           | At default/POR, this pin is Hi-Z; PTN5100 drives this pin LOW based on policy controller MCU command.                                                                                                                    |

|              |     |                  |                           | The pin status can be read in the internal register(s).                                                                                                                                                                  |

| CC1          | 5   | IO               | Custom IO                 | Type-C Configuration channel #1                                                                                                                                                                                          |

|              |     |                  |                           | TVS or similar protection diode (e.g.<br>PESD5V0S1USF, PESD5V0S1UL, etc.) shall be<br>used to protect the CC1/2 pins from<br>overshoot/undershoot during cable plug/unplug and<br>cable discharge events.                |

| CC2          | 4   | IO               | Custom IO                 | Type-C Configuration channel #2                                                                                                                                                                                          |

|              |     |                  |                           | TVS protection diode (e.g. PESD5V0S1USF,<br>PESD5V0S1UL, etc) shall be used to protect the<br>CC1/2 pins from overshoot/undershoot during cable<br>plug/unplug and cable discharge events.                               |

| CC_ORIENT    | 9   | Output           | CMOS IO on VIO power      | This pin indicates Type-C cable plug orientation.                                                                                                                                                                        |

|              |     |                  | rail                      | The pin's polarity is inverted at power-on reset and<br>the PD policy controller MCU has to initialize<br>PTN5100D before the pin level is valid. After the<br>initialization, the pin indicates orientation as follows: |

|              |     |                  |                           | LOW = Normal plug orientation (CC communication on CC1)                                                                                                                                                                  |

|              |     |                  |                           | HIGH = Reverse plug orientation (CC communication on CC2)                                                                                                                                                                |

|              |     |                  |                           | Default pin value is LOW even if there is no<br>connection or normal plug connection                                                                                                                                     |

| CC_CTRL1     | 10  | Input            | Analog Input              | Input to indicate whether to present 'Rd' or Open on CC pin under Unpowered condition                                                                                                                                    |

| DBGACC_FOUND | 6   | Output           | CMOS IO on VIO power rail | Indicates the presence of Type-C Debug accessory<br>Default/POR value is LOW                                                                                                                                             |

| VCONN_IN     | 8   | Input            | Power                     | VCONN power input from system side                                                                                                                                                                                       |

| Symbol               | Pin           | Pin<br>direction | Pin Type                                                                                      | Description                                                                                                                                                                               |

|----------------------|---------------|------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI_MOSI_<br>I2C_SDA | 12            | IO               | Open drain IO (I2C<br>mode) referenced to VIO<br>voltage<br>V_MCUPWR power rail<br>(SPI mode) | Dual purpose pin. In I2C slave mode, this serves as<br>I2C data input/output (open drain)<br>In SPI slave mode, this pin serves Master Output<br>Slave Input function (push pull CMOS IO) |

| SPI_MISO             | 16            | Output           | V_MCUPWR rail                                                                                 | This serves Master Input Slave Output function of SPI interface                                                                                                                           |

| SPI_CLK_I2C_SCL      | 11            | Input            | Open drain IO (I2C<br>mode) referenced to VIO<br>voltage<br>V_MCUPWR power rail<br>(SPI mode) | Dual purpose pin. In I2C slave mode, this serves as<br>I2C clock input (open drain).<br>In SPI slave mode, it serves as SPI clock input pin                                               |

| SPI_CS               | 7             | Input            | V_MCUPWR rail                                                                                 | This pin provides SPI chip select Input                                                                                                                                                   |

| INT_N                | 13            | Output           | Open drain                                                                                    | Level triggered interrupt. Open drain output; This pin needs to be externally pulled up VIO.                                                                                              |

| SLV_ADDR             | 14            | Ternary<br>input | V_MCUPWR rail                                                                                 | This pin is usable only when VDD is valid<br>Ternary slave address (I2C) pin                                                                                                              |

| V_MCUPWR             | 17            | Output           | Power                                                                                         | This pin delivers current up to 30 mA (max) to policy controller MCU. External supply de-coupling capacitor(s) (2.2 $\mu F$ $\pm 10$ % ceramic capacitor) are required                    |

| VIO                  | 18            | Input            | Power                                                                                         | IO domain power supply. External supply de-coupling capacitor(s) are required                                                                                                             |

| VBUS                 | 2             | Input            | Power                                                                                         | VBUS power supply. External supply de-coupling capacitor(s) are required                                                                                                                  |

| VDD                  | 15            | Input            | Power                                                                                         | Core domain power supply. External supply de-coupling capacitor(s) are required                                                                                                           |

| BYPASS               | 19            | Internal         | Internal power rail                                                                           | Internal power rail. A ceramic capacitor (2.2 $\mu F$ $\pm 10$ %) is to be connected to this pin                                                                                          |

| GND                  | Center<br>pad |                  | GND                                                                                           | Ground Center pad                                                                                                                                                                         |

#### Table 3. Pin description ... continued

## 7. Functional description

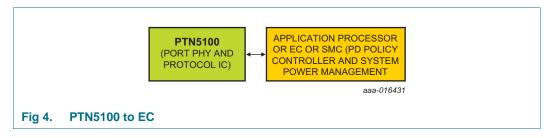

PTN5100 is a 1-port USB Type-C PD Physical and Protocol Layer IC that can be used to realize single or multi-port USB Type-C PD and/or Alternate mode implementations. It complies with USB PD [1] and Type-C specifications [2]. PTN5100 supports the following use configurations:

- 1. On a System Host (single or multi-port configuration)

- a. Controlled by a PD Policy controller and/or Alternate mode control MCU

- b. Controlled by Embedded controller or Application processor

- 2. On a Device platform

Product data sheet

a. Controlled by a PD policy controller or Alternate mode control MCU or existing processor

On the host and device use cases, different PD roles are possible: (P), (P/C), (C), (C/P).

PTN5100 supports two levels of configurability and programmability:

- NVM configuration options configurability in the factory through NVM configuration utility

- I2C/SPI register programmable read/write accesses at application/Firmware (FW) level

PTN5100 can be partitioned into the following major functional blocks along with their respective interfaces:

- Type-C Configuration Channel functional block

- USB Power Delivery function

- VCONN Low RON Switch

- Power FET Enable Control

- MCU interface and Control

The following subsections describe the PTN5100 with its major functional blocks.

## 7.1 Type-C Configuration Channel functional block

Type-C Configuration Channel (CC) function operates as a front end to cable/plug interface.

PTN5100 can operate autonomously or under MCU control. To support use cases especially with autonomous mode, PTN5100 implements HW circuitry to perform the following operations:

- Applying 'Rp' or 'Rd' depending on the (NVM) configured role

- · Detecting cable/plug connect and disconnect events

- Indicating Type-C current limit level in a system under DFP role

- Detecting the current level supported by remote end under UFP role

- Identifying plug orientation and indicating through CC\_ORIENT pin

- Identifying Type-C Debug accessory detection and indicating through DBGACC\_FOUND pin

- Updating event, interrupt and status registers and raising interrupt signal using INT\_N pin

In order to provide reliable connect/disconnect event triggers, debouncing is also implemented as per [2].

PTN5100 allows for NVM configurability and/or register programmability to enable usage under different platform configurations.

## 7.2 USB Power Delivery Function

In general, the Embedded Controller (EC) or System Management Controller (SMC) handles the overall Application/Platform power management given the system states, battery status, etc. It reviews capabilities and status of various power providers (USB PD, AC-DC adapter, battery, docking, etc.) dynamically and determines a specific source for powering/charging the platform - the power source selection is an important and platform dependent aspect of Application power delivery scheme.

- For example, in some computing applications, EC plays a central role in controlling the various power sources including USB PD. To support this, PTN5100 and Policy controller MCU can be configured to negotiate and agree on power contract based on command/response exchanges with EC

- In several applications, EC may not even exist or EC wants to play a hands-off role. To support these applications, PTN5100 and Policy controller MCU can be configured to operate autonomously

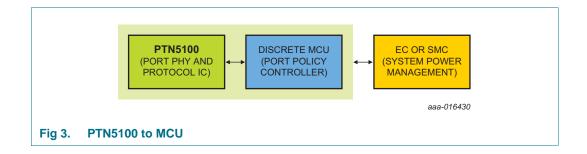

In a Type-C PD implementation, the system partitioning involves the following parts:

- Port PHY and Protocol layer functions  $\rightarrow$  PTN5100

- Port policy engine and device policy management, Alternate mode support → Discrete policy controller MCU

- System management  $\rightarrow$  EC or SMC

PTN5100 implements USB PD PHY layer and HW intensive Protocol functions and it works along with a discrete MCU to implement Full PD functionality. The combined 2-chip system solution (PTN5100 and MCU) can be configured to support one or more of the following PD roles:

- 1. PD Consumer (C)

- 2. PD Consumer/Provider (C/P)

- 3. PD Provider (P)

- 4. PD Provider/Consumer (P/C)

The interface between PTN5100 and Policy controller MCU can be either SPI or I2C. PTN5100 provides a transparent set of commands and register interface for the MCU to control the operation and ensure safe/suitable system behavior/response. PTN5100 Application Programming guide [3] describes the register set supported for the PD control, status updates and operational control/sequences.

The policy controller MCU implements PD port policy layer as per [1]. The default PD power profiles are configured in the MCU and the EC could request for specific profile and PD contract based on platform application. The 2-chip solution can operate autonomously or under EC control.

PTN5100 implements USB PD PHY layer function as follows:

- Slew rate controlled IO

- Bit transmission and data recovery

- Bi-phase Mark Coding

- 4B5B Line coding

- CRC computation and checking

It handles the following Protocol layer functions:

- Data Packetization and Extraction

- Good CRC Response

- Automated Retries

- Hard reset, Cable reset

- Tx and Rx buffer management

It handles both Transmit and Receive operation and it maintains dedicated TX and RX data buffers. To minimize chances of collision, PTN5100 checks the CC line before start of transmission. Once the data is transmitted or received, the I2C interface status is updated and MCU is interrupted.

BIST mode (Tx, Rx) is also supported.

Note: NXP is open to engage on Firmware licensing to give a head start to customers on USB PD Policy and Alternate mode Firmware front. Please contact NXP for further details.

## 7.3 VCONN Switch

Type-C specification defines a dedicated power pin VCONN\_IN to deliver power to full featured cables, dongles and cable adapters.

PTN5100 implements very low RON switch that can deliver up to 1 A current. Depending on the pin over which CC communication is established, VCONN power is delivered into the other CC pin. With patented architecture, the switch implements Soft Start behavior to avoid heavy inrush current flow.

The VCONN switch is to be used only when VCONN\_IN lies within the valid range (2.7 V to 5.5 V).

The VCONN switch can be enabled or disabled by Firmware. When in disabled condition, it presents Hi-Z condition. The switch implements two important features related to robustness:

- Forward Current Protection (FCP) that monitors over current condition (over current limit is register programmable) and trips the connection by disabling the switch

- Reverse Current Protection (RCP) that avoids reverse current flow back into the system due to inductive effects of cable unplug events

Further, both FCP and RCP circuitry shall be activated only when VCONN\_IN is within valid range.

## 7.3.1 Forward Current Protection (FCP)

PTN5100 implements Forward current protection in VCONN switch that keeps monitoring for a current flow above the preconfigured level from the system side and whenever the threshold is exceeded, the switch is opened and an interrupt event is raised. The switch remains open until the port controller MCU reads the status and re-enables the switch.

## 7.3.2 Reverse Current Protection (RCP)

PTN5100 implements Reverse Current Protection in VCONN switch that watches for any instantaneous reverse current flow back into the system via VCONN and whenever the preconfigured threshold is exceeded, the switch is opened and an interrupt event is raised. The switch remains open until the port controller MCU reads the status and re-enables the switch.

## 7.4 Power FET control

PTN5100 implements three dedicated open drain IOs that can be used to control the external power MOSFETs and enable/ disable VBUS source and sink power paths of the system. These are enabled or disabled based on PD power role (provider or consumer) of the Type-C interface. Based on PD negotiation and contract, the policy controller MCU enables/disables the specific power path (source FET or sink FETs).

- EN\_USBSRC: This pin is used to enable/disable the power MOSFETs that corresponds to VBUS source (e.g. 5V regulated output). The FET enable can be configured and controlled through the register interface by the MCU. The pin status is monitored and updated in a status register.

- EN\_USBFET1: This pin is used to enable/disable the power MOSFETs that corresponds to USB PD power from external power sources or delivering VBUS power to external peripherals. Its specific use as a VBUS source or sink path control is programmable. The FET enable can be configured and controlled through the register interface by the MCU. The pin status is monitored and updated in a status register.

• EN\_USBFET2: This pin is used to enable/disable the power MOSFETs that corresponds to USB PD power from external power sources or delivering VBUS power to external peripherals. It specific use as a VBUS source or sink path control is programmable. The FET enable can be configured and controlled through the register interface by the MCU. The pin status is monitored and updated in a status register.

## 7.5 MCU interface and control

PTN5100 works along with policy controller MCU to realize USB PD functionality and/or Alternate mode support. The MCU can control and interface with PTN5100 through a dedicated I2C/SPI interface. In a given system implementation, only one of the two interfaces (I2C, SPI) can be used. This selection can be static configured via NVM.

PTN5100 provides up to three I2C slave address combinations based on ternary pin (SLV\_ADDR) setting as per the table below.

| SLV_ADDR pin | Device address (Write/read) |

|--------------|-----------------------------|

| GND          | 0xE0/0xE1                   |

| VDDIO        | 0xE4/0xE5                   |

| Unconnected  | 0xE8/0xE9                   |

#### Table 4. I2C slave address combinations

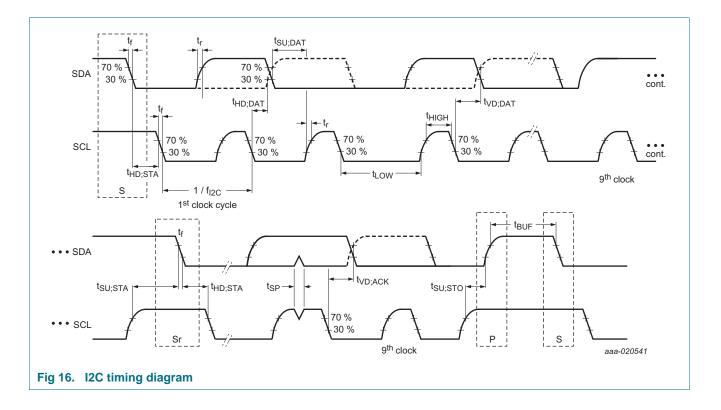

## 7.5.1 I<sup>2</sup>C-bus interface

PTN5100 has a slave I2C interface through which it provides a mechanism for control and status interaction/communication with the MCU. It supports Standard mode, Fast mode and Fast mode plus.

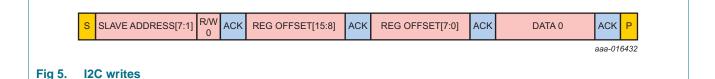

#### 7.5.1.1 I2C writes

The following figure shows the basic protocol for I2C writes. A 16-bit offset is used to address each register.

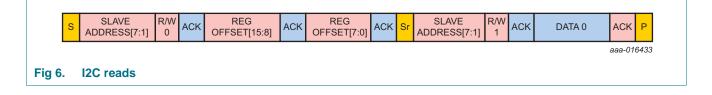

#### 7.5.1.2 I2C reads

The following figure shows the basic protocol for I2C reads. They start off like I2C writes by specifying a 16-bit register offset. This is followed by a repeat start condition, the Slave Address (Read), and the read data.

' I N5100

## 7.5.1.3 I2C address auto-incrementing

Bursts are allowed during writes and reads. Bit 15 of the register offset is the auto-increment indication. If '0' then the internally generated MMIO address will not increment with each data byte. If '1', then the address will increment with each data byte.

A detailed description of the I<sup>2</sup>C-bus specification, with applications, is given in user manual UM10204, "I<sup>2</sup>C-bus specification and user manual" [4]. Referring to I2C protocol, PTN5100 positively acknowledges all 256 register offset addresses, though there are certain undefined address offsets.

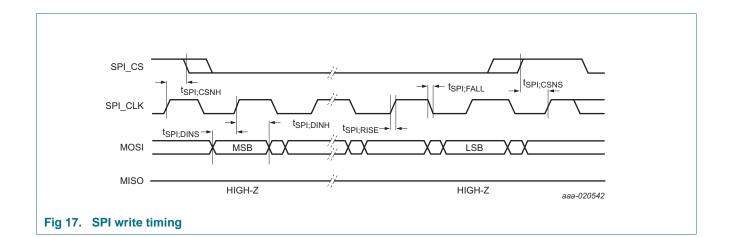

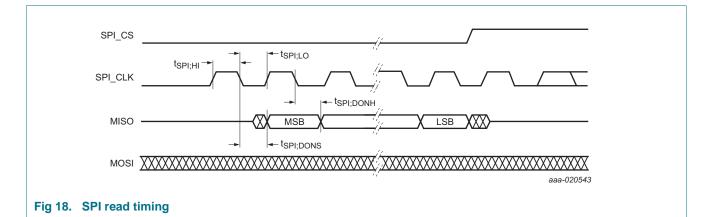

## 7.5.2 SPI interface

PTN5100 provides an SPI slave interface as well. It supports SPI modes 1 and 2. This interface exposes same register interface as that of I2C. Its main advantage is faster command and data transport and relaxes MCU response time/latency requirements.

## 7.5.3 Register interface

PTN5100 Application programming guide [3] describes the various registers with their bit definitions, POR values and the various functions. Also, sample 'C' programs corresponding to various functions and operations are given. This guide can be used by the platform system architects to implement the EC firmware to control the operations with PTN5100. Refer to programming guide for more information. The register definitions are also described in the guide.

## 7.5.4 Relevant Interface pins - SLV\_ADDR, SPI\_CLK\_I2C\_SCL, SPI\_MOSI\_I2C\_SDA, SPI\_CS, SPI\_MISO, INT\_N

- SLV\_ADDR is a ternary input pin that is used to support up to 3 slave PTN5100 devices on a given platform. This pin can be pulled to V\_MCUPWR rail, left open or pulled to GND.

- While in SPI mode, SPI\_CLK\_I2C\_SCL, SPI\_MISO, SPI\_MOSI\_I2C\_SDA and SPI\_CS provide the necessary interface for connecting to SPI master controller on the MCU.

- While in I2C mode, SPI\_CLK\_I2C\_SCL and SPI\_MOSI\_I2C\_SDA are used for I2C clock and data interfacing to MCU

- INT\_N pin is used to raise Active LOW level triggered interrupt signal to EC. PTN5100

processes various events and raises interrupt that require SMC intervention. Once all

relevant events are processed by the MCU, the INT\_N pin goes HIGH. At POR, this

pin remains HIGH (when VIO is valid). The specific events that can generate the

interrupt can be selected.

## 7.6 Power supplies

PTN5100 is designed to operate under various power supplies. It can operate under both normal battery and dead battery environments (while drawing power from VBUS). PTN5100 handles power supply transitions (VBUS, VDD) transparently and there is no specific power supply ramp requirement imposed on the system (between VDD and VIO rails) also.

The following table highlights the power supplies and operating conditions for PTN5100.

| Valid power supply input combination | Operational condition                                                                                                                            | Remarks                                                        |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| VDD, VIO                             | Normal powered condition (both battery based or non-battery based platforms)                                                                     | All interfaces operational                                     |

| VDD, VIO, VBUS                       | Normal powered condition; Host Platform<br>may be powered/charged through VBUS<br>simultaneously                                                 | All interfaces operational                                     |

| VBUS,<br>VIO(=V_MCUPWR)              | Dead battery in battery based platforms or<br>Normal powered condition under other<br>platforms; Host Platform powered/charged<br>through USB PD | All interfaces operational                                     |

| VBUS                                 | Dead battery operation; PTN5100 draws<br>power from VBUS for its operation; Host<br>Platform may be powered/charged through<br>USB PD later      | PTN5100 pins<br>(dependent on VIO rail)<br>are not operational |

#### Table 5. Power supplies vs. operating conditions

Remark: The Policy controller MCU is powered by PTN5100.

The relevant pins associated with this functional block are:

- VDD

- VIO

- VBUS

- V\_MCUPWR

- BYPASS

## 8. PTN5100 - Use case view

Given that USB Power Delivery could address the requirements of a wide set of markets and product segments, PTN5100 is designed to work over a range of product categories, platform applications, use cases and usage roles. With its configurability, it can be serve the needs of both general and custom applications. Not limited to these but the following subsections illustrate a set the use cases of PTN5100.

## 8.1 System use cases

## 8.1.1 USB PD Provider/Consumer - Notebook/Ultrabook/Chromebook/Tablet PC

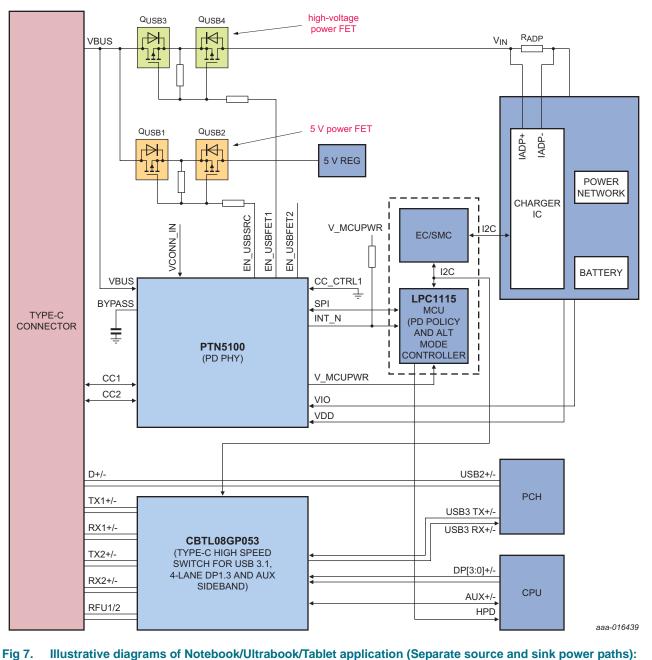

Fig 7. Illustrative diagrams of Notebook/Ultrabook/Tablet application (Separate source and sink power paths): PD Provider/Consumer role (DFP role under Normal power/battery; UFP role under dead battery condition) 1 of 2

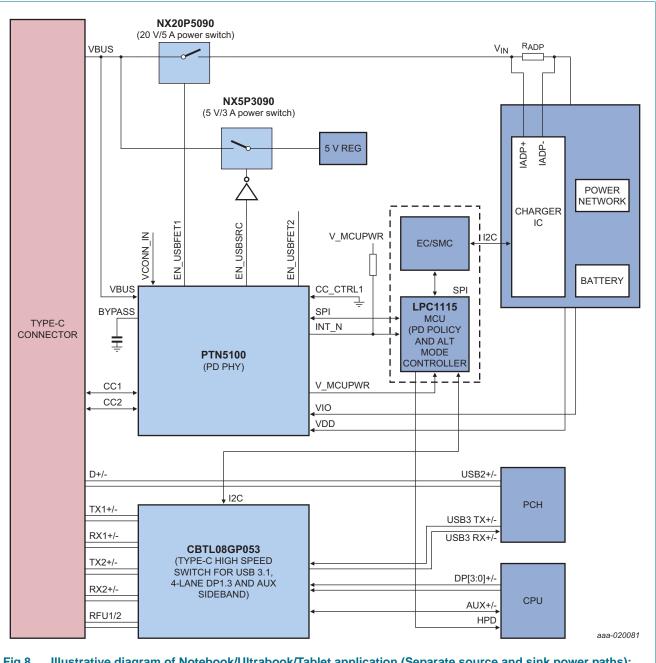

#### Fig 8. Illustrative diagram of Notebook/Ultrabook/Tablet application (Separate source and sink power paths): PD Provider/Consumer role (DFP role under Normal power/battery; UFP role under dead battery condition) 2 of 2

## 8.1.1.1 Brief description

In this illustration, the 2-chip solution (PTN5100 + Policy controller & Alternate mode MCU) is behind the Type-C receptacle and it is configured as a PD Provider/ Consumer. The EC interfaces with the Charger IC to configure at specific voltage/ current levels to perform battery charging and/or powering of the platform.

This application is expected to:

Product data sheet

- Source VBUS 5 V (if not under dead battery)

- Charge from VBUS PD and AC barrel power, if applicable

- Source VCONN power

The EC communicates with controller MCU via an I2C bus and control the operations. The PTN5100 and MCU can operate autonomously or under the control of EC.

Figure 7 and Figure 8 illustrate the configurations with discrete MOSFETs and Power switches respectively. PTN5100 controls the power FETs/switch to determine charging (Green colored FETs/switch on VBUS power inputs) and 5 V VBUS power delivery (Orange colored FETs/switch on VBUS). If NXP5P3090 is used, then the Active HIGH switch enable control is required to be generated based on the EN\_USBSRC control output.

An important aspect to consider here is that PTN5100 would indicate a 'Rd' pulldown (UFP) under dead battery condition and this enables the port partner to provide VBUS at 5 V (provided the port partner is capable of acting as DFP). However, after system starts up, role swap has to be performed to become DFP. This is handled by PTN5100 and MCU together.

CC\_ORIENT and DBGACC\_FOUND outputs can be used by the platform, if necessary.

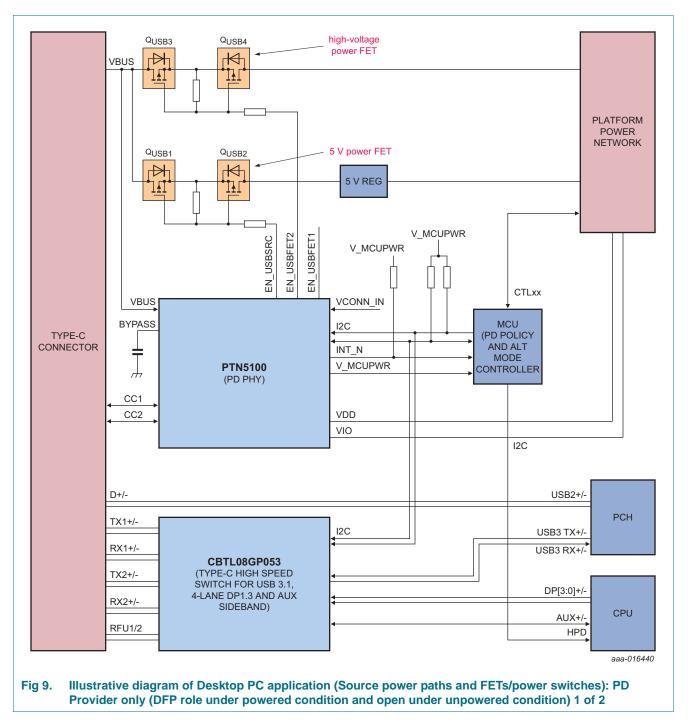

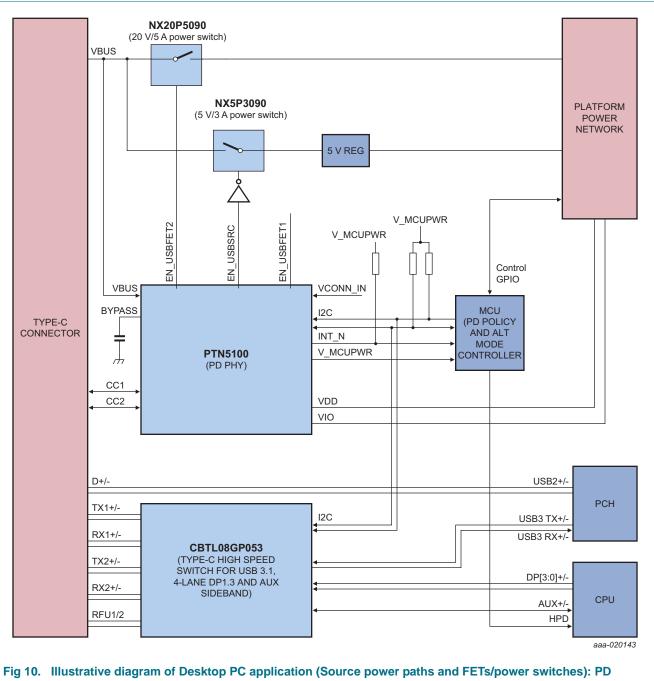

## 8.1.2 USB PD Provider with Type-C receptacle - Desktop PC

Provider only (DFP role under powered condition and open under unpowered condition) 2 of 2

#### 8.1.2.1 Brief description

In this illustration also, the 2-chip solution (PTN5100+ Policy controller & Alternate mode control MCU) is behind Type-C receptacle and it is configured to act as a PD Provider (Autonomous mode) based on pre-configured Power profiles. The PC system uses the ATX or similar power supply and it can deliver power to all USB ports. In this diagram, there is no EC to interface with and so, the 2-chip solution (MCU and PTN5100) is configured for autonomous operation.

For USB ports, this application:

- Sources VBUS 5 V

- Sources USB PD power (specific wattage depends on the system application)

- Sources VCONN power

Figure 9 and Figure 10 illustrate the configurations with discrete MOSFETs and Power switches respectively. PTN5100 controls the power FETs/switches to VBUS 5V and PD power (Orange colored FETs/Switch). The handshake with power supply unit is dependent on OEM/ODM design.

An important aspect to consider here is that a Desktop PC does not have dead battery condition though it can be unpowered. If not powered, it presents 'Open' on CC pins. After power up initialization, PTN5100 would indicate 'Rp'. After PD negotiation, the Desktop platform could deliver higher voltage/current.

CC\_ORIENT and DBGACC\_FOUND connections can be used based on platform need.

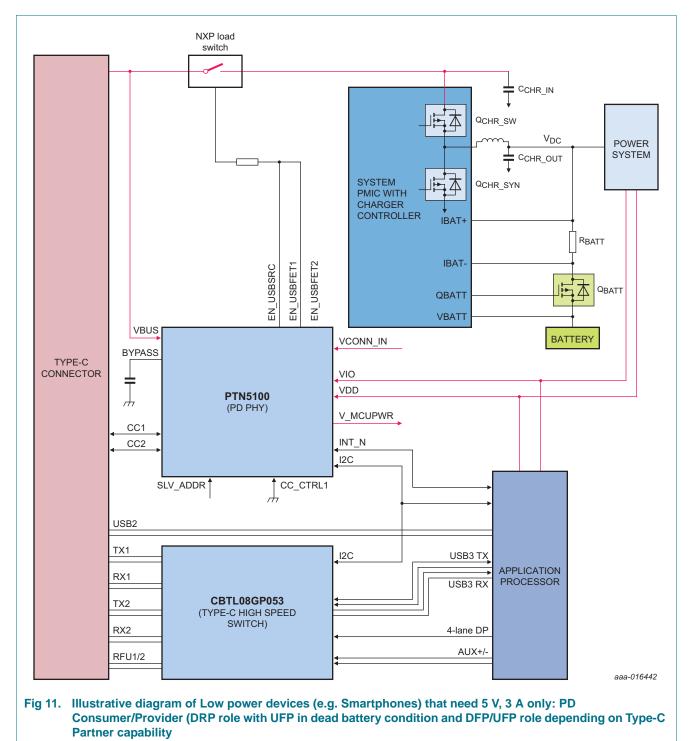

## 8.1.3 USB PD Consumer/Provider (Smartphone use case) - Standalone PTN5100

#### 8.1.3.1 Application description

In this illustration, PTN5100 is behind Type-C receptacle and it is configured to act as a PD consumer/ Provider. It is important to note that there is no dedicated policy controller MCU associated with the PD functionality as this application can operate with 5V, 3A only. Under normal battery/powered condition, PTN5100 is configured as DFP, DRP or UFP based on register configuration setting and it performs cable/plug connect and disconnect detection, orientation detection. However, on dead battery condition, it defaults to UFP role. The power path FET control may or may not be used in the application depending on the capabilities of System PMIC.

This application is expected to

- Receive VBUS 5 V @ 3 A

- Provides VBUS 5 V @ 3 A

- Sourcing VCONN power is dependent on the Type-C role taken

PTN5100 operates autonomously but it is possible for the system processor to control it via I2C interface. Though there may not be a need to negotiate higher voltage/current, the platform may still need to support Alternate modes and VDMs. The Application Processor is used to handle those capabilities.

PTN5100

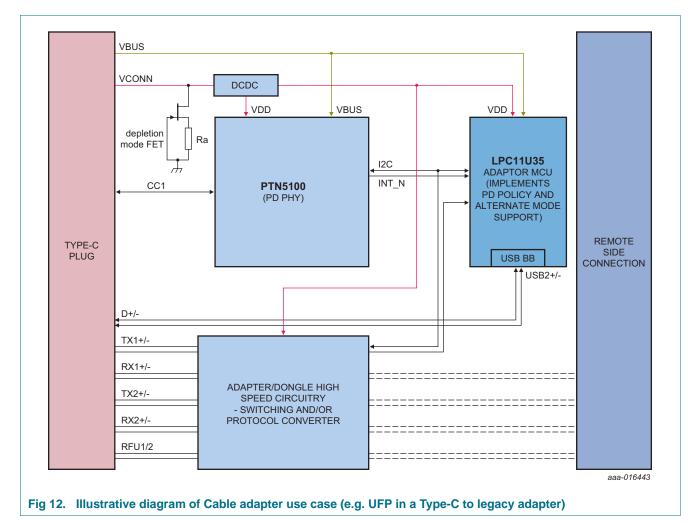

## 8.1.4 Type-C cable adapters with PTN5100

#### 8.1.4.1 Application description

In this illustration, PTN5100 is inside Type-C cable adapter operating in UFP role. Some example use cases are Type-C to DP adapter, Type-C to VGA adapter, Type-C to Thunderbolt adapter etc. PTN5100 serves as PD PHY layer device for a Cable adapter management MCU or dedicated PD MCU wherein PD policy management, Alternate mode and VDM support are handled. The USB Billboard device is assumed to be implemented as part of adapter management MCU.

The cable adapter implementation operates on VCONN supply. Discrete depletion mode FET has to be used in the application for 'Ra' indication on CC pin.

## 8.1.5 USB PD Consumer/Provider with Type-C receptacle

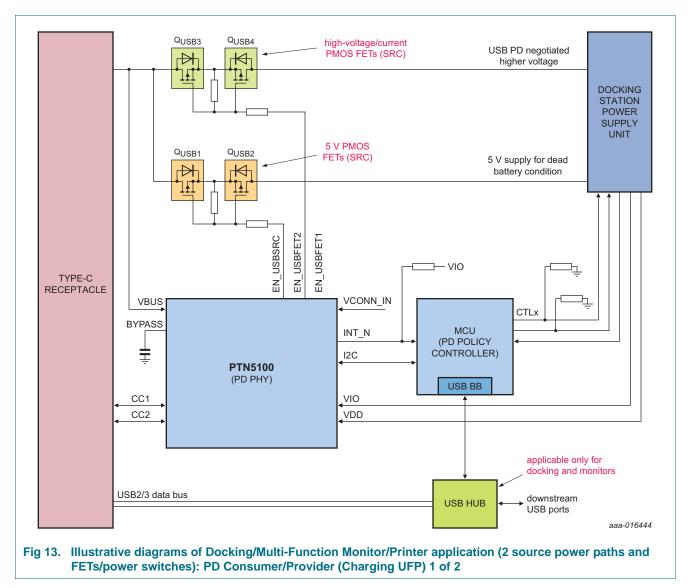

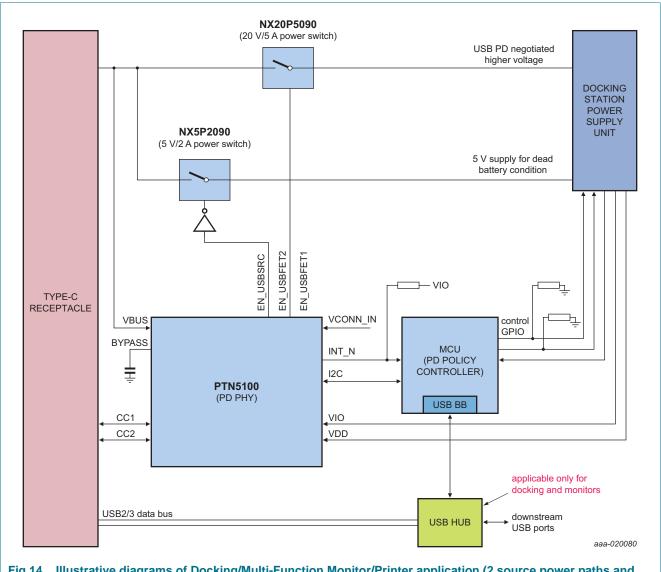

Fig 14. Illustrative diagrams of Docking/Multi-Function Monitor/Printer application (2 source power paths and FETs/power switches): PD Consumer/Provider (Charging UFP) 2 of 2

## 8.1.5.1 Application description

The example applications are Multi-function monitor, Dock or Printer. PTN5100 is configured for Charging UFP role. The policy controller MCU would probe PTN5100 to make sure there is no dead battery device connected at the other end. If a pulldown 'Rd' is detected at the remote cable end, this platform supplies VBUS 5V. Once the remote end system is capable of performing power role swap, the roles would be reversed.

This application is expected to:

- Receive VBUS 5 V (or provide power during Dead battery operation VBUS 5 V)

- Provides VBUS PD power

The PD software running on the MCU controls the power FETs/switches to determine VBUS 5 V and USB PD power delivery (Orange colored power FETs/switch on VBUS).

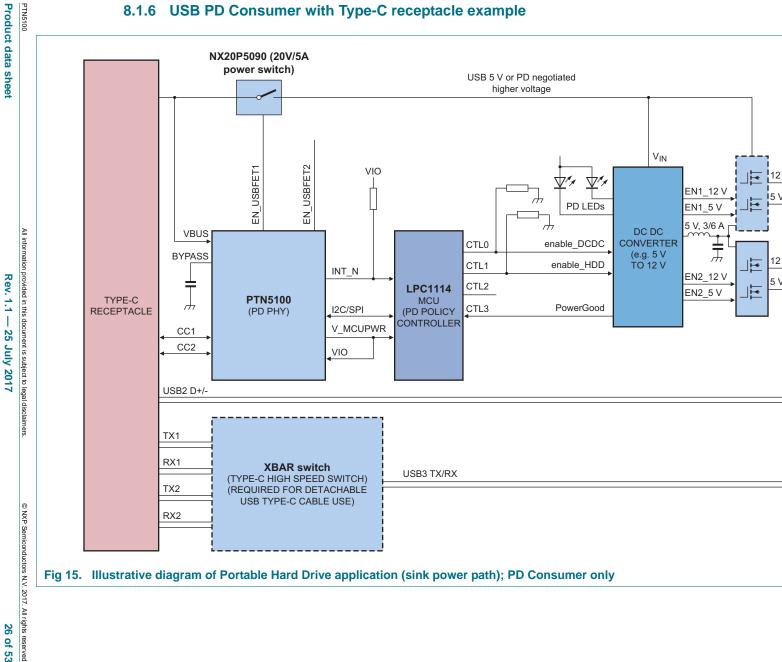

## 8.1.6 USB PD Consumer with Type-C receptacle example

26 of 53

## 8.1.6.1 Application description

In a USB PD based hard drive application, PTN5100 + Policy controller MCU operates autonomously. At POR, PTN5100 presents UFP role and starts to receive VBUS 5 V. Then based on configured power profile, PD negotiation and contracting is performed. The MCU interfaces with Hard drive electronics and delivers power after handshake. The MCU's GPIO pins can be reused to handshake with DCDC converter and the handshake mechanism is OEM platform dependent.

This application is expected to:

• Receive VBUS 5 V, USB PD power

#### 9. **Limiting values**

| Symbol           | Parameter           | Conditions                                                                                                                                                                 |        | Min  | Max  | Unit |

|------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|------|

| V <sub>DD</sub>  | supply voltage      |                                                                                                                                                                            |        | -0.5 | +4.6 | V    |

| VIO              | IO voltage          |                                                                                                                                                                            |        | -0.5 | +4.6 | V    |

| VBUS             | USB VBUS voltage    |                                                                                                                                                                            |        | -0.5 | +28  | V    |

| VI               | Input voltage       | voltage at the pin                                                                                                                                                         |        |      |      |      |

|                  |                     | CC_CTRL1, CC_ORIENT,<br>DBGACC_FOUND                                                                                                                                       |        | -0.5 | +4.6 | V    |

|                  |                     | CC1, CC2                                                                                                                                                                   |        | -0.5 | +6.0 | V    |

|                  |                     | EN_USBSRC, EN_USBFET1,<br>EN_USBFET2                                                                                                                                       |        | -0.5 | +28  | V    |

|                  |                     | BYPASS                                                                                                                                                                     |        | -0.5 | +2.5 | V    |

|                  |                     | VCONN_IN                                                                                                                                                                   |        | -0.5 | +6.0 | V    |

|                  |                     | INT_N                                                                                                                                                                      |        | -0.5 | +4.6 | V    |

|                  |                     | SLV_ADDR                                                                                                                                                                   |        | -0.5 | +4.6 | V    |

|                  |                     | SPI_CLK_I2C_SCL,<br>SPI_MOSI_SDA, SPI_MISO,<br>SPI_CS                                                                                                                      |        | -0.5 | +4.6 | V    |

| T <sub>stg</sub> | Storage temperature |                                                                                                                                                                            |        | -65  | +150 | °C   |

| V <sub>ESD</sub> | electrostatic       | HBM: VBUS, CC1, CC2                                                                                                                                                        | [1][2] | 8000 | -    | V    |

|                  | discharge voltage   | HBM for internal pins:<br>CC_CTRL1, CC_ORIENT,<br>DBGACC_FOUND, BYPASS,<br>VCONN_IN, VDD, VIO,<br>INT_N, SLV_ADDR, SPI,<br>EN_USBFET1, EN_USBFET2<br>and EN_USBSRC signals | [2]    | 2000 | -    | V    |

|                  |                     | CDM                                                                                                                                                                        | [3]    | 1000 | -    | V    |

Table 6. **Limiting values**

[1] All voltage values, except differential voltages, are with respect to network ground terminal.

[2] Human Body Model: ANSI/ESDA/JEDEC JDS-001-2012 (Revision of ANSI/ESDA/JEDEC JS-001-2011), ESDA/JEDEC Joint standard for ESD sensitivity testing, Human Body Model - Component level; Electrostatic Discharge Association, Rome, NY, USA; JEDEC Solid State Technology Association, Arlington, VA, USA.

[3] Charged Device Model: JESD22-C101E December 2009 (Revision of JESD22-C101D, October 2008), standard for ESD sensitivity testing, Charged Device Model - Component level; JEDEC Solid State Technology Association, Arlington, VA, USA.

# **10. Recommended operating conditions**

| Symbol           | Parameter                               | Conditions                | Specification guaranteed by | Min  | Тур  | Max  | Unit |

|------------------|-----------------------------------------|---------------------------|-----------------------------|------|------|------|------|

| VDD              | System supply voltage                   |                           | ATE                         | 3.0  | -    | 3.6  | V    |

| VIO              | System IO supply voltage                | when 3.3 V supply is used | ATE                         | 3.0  | -    | 3.6  | V    |

|                  |                                         | when 1.8 V supply is used | ATE                         | 1.7  | -    | 1.9  | V    |

| VBUS             | USB VBUS voltage                        |                           | ATE or bench                | 3.7  | -    | 25   | V    |

| Vi               | input voltage on the pin                |                           | ATE                         |      | -    |      |      |

|                  | CC_CTRL1,<br>CC_ORIENT,<br>DBGACC_FOUND | ATE                       | -0.3                        | -    | +3.6 | V    |      |

|                  |                                         | CC1, CC2                  | ATE                         | -0.3 | -    | +5.5 | V    |

|                  | EN_USBSRC,<br>EN_USBFET1,<br>EN_USBFET2 | ATE                       | -0.3                        | -    | +25  | V    |      |

|                  |                                         | VCONN_IN                  | ATE                         | -0.3 | -    | +5.5 | V    |

|                  | INT_N                                   | ATE                       | -0.3                        | -    | +3.6 | V    |      |

|                  | SLV_ADDR                                | ATE                       | -0.3                        | -    | +3.6 | V    |      |

| T <sub>amb</sub> | Ambient Operating temperature           |                           |                             | -20  | -    | +85  | °C   |

## **11. Characteristics**

## **11.1 Device characteristics**

#### Table 8. Device characteristics

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27  $\degree$  (unless otherwise noted).

| Symbol                 | Parameter                                                            | Conditions                                                                                         | Min | Тур | Max | Unit |

|------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| T <sub>FET_EN</sub>    | Time duration between I2C<br>write/ACK and FET enable<br>asserted    | Applicable to all FET enable pins                                                                  | -   | -   | 10  | μS   |

| T <sub>FET_DIS</sub>   | Time duration between I2C<br>write/ACK and FET enable<br>de-asserted | Applicable to all FET enable pins                                                                  | -   | -   | 10  | μs   |

| I <sub>DD,Active</sub> | Active mode operating current                                        | UFP role; attached condition; $V_{DD} = 3.3 V$                                                     | -   | 200 | -   | μA   |

|                        |                                                                      | DFP role; attached condition; $V_{DD} = 3.3 \text{ V}$                                             | -   | 300 | -   | μA   |

|                        |                                                                      | SPI interface is active                                                                            | -   | 3   | -   | μΑ   |

|                        |                                                                      | PD mode is functional; does<br>not include power delivered<br>on V_MCUPWR pin; $V_{DD} =$<br>3.3 V | -   | 3   | -   | mA   |

|                        | Additional current consumed on VDD                                   | VCONN switch is enabled without FCP and RCP; $V_{DD} = 3.3 V$                                      | -   | 175 | 250 | μΑ   |

|                        |                                                                      | VCONN switch is enabled<br>with FCP and RCP; $V_{DD} =$<br>3.3 V                                   | -   | 250 | 340 | μΑ   |

| I <sub>DD(idle)</sub>  | Idle mode current on VDD                                             | UFP role; Unattached condition                                                                     | -   | 50  | -   | μΑ   |

|                        |                                                                      | DFP role; Unattached<br>condition (Rp at standard<br>current level)                                | -   | 70  | -   | μΑ   |

|                        |                                                                      | DRP mode; Unattached condition                                                                     | -   | 100 | -   | μΑ   |

| I <sub>VIO(idle)</sub> | Idle mode supply current (VIO)                                       |                                                                                                    | -   | -   | 10  | μΑ   |

| bckdrv                 | Backdrive current                                                    | Backdrive current on VDD pin when that pin is at 0 V                                               |     |     |     |      |

|                        |                                                                      | CC1, CC2 = 5V                                                                                      | -10 | -   | 10  | μA   |

| I <sub>LIH,EN</sub>    | HIGH-level input leakage current                                     | VI=3.3V, applies to CC1, CC2                                                                       | -   | -   | 20  | μΑ   |

| I <sub>LIL,EN</sub>    | LOW-level input leakage current                                      | VI=GND,<br>Applies to CC1, CC2                                                                     | -20 | -   | 0   | μA   |

## 11.2 USB PD and Type-C characteristics

#### Table 9. USB PD and Type-C AC/DC characteristics

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27  $\degree$  (unless otherwise noted).

| Symbol                         | Parameter                                                                                                                                                                                 | Conditions                                                                                                                            | Min  | Тур   | Max  | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|

| USB PD normat                  | tive specification                                                                                                                                                                        | -                                                                                                                                     |      |       |      |      |

| f <sub>Bitrate</sub>           | Bit rate                                                                                                                                                                                  |                                                                                                                                       | 270  | 300   | 330  | Kbps |

| t <sub>UnitInterval</sub>      | unit interval                                                                                                                                                                             |                                                                                                                                       | 3.03 | -     | 3.7  | μS   |

| PBitRate                       | Maximum difference between<br>the bit-rate during the payload<br>and the reference bit-rate (The<br>reference bit rate is the<br>average bit rate of the last 32<br>bits of the preamble) | At the transmitter                                                                                                                    | -    | -     | 0.25 | %    |

| t <sub>Inter</sub> FrameGap    | Time from the end of last bit of<br>a Frame until the start of the<br>first bit of the next Preamble.                                                                                     |                                                                                                                                       | 25   | -     | -    | μS   |

| t <sub>StartDrive</sub>        | Time before the start of the<br>first bit of the Preamble when<br>the transmitter shall start<br>driving the line.                                                                        |                                                                                                                                       | -1   | -     | 1    | μS   |

| USB PD transm                  | itter normative specification                                                                                                                                                             | ·                                                                                                                                     |      | ·     |      |      |

| t <sub>EndDriveBMC</sub>       | Time to cease driving the line<br>after the end of the last bit of<br>the Frame.                                                                                                          | Min value is limited by t <sub>HoldLowBMC</sub>                                                                                       | -    | -     | 23   | μs   |

| t <sub>Fall</sub>              | Fall time                                                                                                                                                                                 | 10 % and 90 % amplitude points, minimum is under unloaded condition                                                                   | 300  | -     | -    | ns   |

| t <sub>HoldLowBMC</sub>        | Time to cease driving the line<br>after the final high-to-low<br>transition                                                                                                               | Max value is limited by<br>t <sub>EndDriveBMC</sub>                                                                                   | 1    | -     | -    | us   |

| t <sub>Rise</sub>              | Rise time                                                                                                                                                                                 | 10 % and 90 % amplitude points, minimum is under unloaded condition                                                                   | 300  | -     | -    | ns   |

| VSwing                         | Voltage swing                                                                                                                                                                             |                                                                                                                                       | 1.05 | 1.125 | 1.2  | V    |

| Z <sub>Driver</sub>            | Transmitter output impedance                                                                                                                                                              | Source output impedance<br>at the Nyquist frequency of<br>[USB2.0] low speed (750<br>kHz) while the source is<br>driving the CC line. | 33   | -     | 75   | Ω    |

| USB PD receive                 | er normative specification                                                                                                                                                                |                                                                                                                                       |      |       |      |      |

| C <sub>Receiver</sub>          | CC Receiver capacitance                                                                                                                                                                   | The CC pin (DFP or UFP)<br>capacitance when not<br>transmitting on the line                                                           | 200  | -     | 600  | pF   |

| <b>N</b> TransitionCount       | Transitions for signal detect                                                                                                                                                             |                                                                                                                                       | 3    | -     | -    |      |

| t <sub>RxFilter</sub>          | Time constant of Rx bandwidth limiting filter                                                                                                                                             |                                                                                                                                       | 100  | -     | -    | ns   |

| t <sub>Transition</sub> Window | Time window for detecting non-idle                                                                                                                                                        |                                                                                                                                       | 12   | -     | 20   | μs   |

| Z <sub>BmcRx</sub>             | Receiver Input Impedance                                                                                                                                                                  |                                                                                                                                       | 10   | -     | -    | MΩ   |

#### Table 9. USB PD and Type-C AC/DC characteristics ... continued

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27  $\degree$  (unless otherwise noted).

| Symbol              | Parameter                                          | Conditions                                                      | Min  | Тур  | Max  | Unit |

|---------------------|----------------------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| Type-C speci        | ification                                          |                                                                 | -    |      |      | I    |

| I <sub>pullup</sub> | Current source for DFP pullup                      | Default current                                                 | 64   | 80   | 96   | μA   |

|                     | indication                                         | 1.5 A                                                           | 166  | 180  | 194  | μA   |

|                     |                                                    | 3 A                                                             | 314  | 330  | 346  | μA   |

| R <sub>pulldn</sub> | Pulldown termination on UFP                        | After on-board calibration is completed                         | 4.6  | 5.1  | 5.6  | kΩ   |

| ZOPEN               | UFP CC termination                                 | Applies to self-powered<br>UFP to remain<br>undetectable by DFP | 126  | -    | -    | kΩ   |

| V <sub>CLAMPH</sub> | High current mode clamp voltage                    | UFP mode; VDD = 0,<br>VBUS = 0                                  | 0.85 | -    | 2.18 | V    |

| V <sub>CLAMPM</sub> | Medium current mode clamp voltage                  | UFP mode; VDD = 0,<br>VBUS = 0                                  | 0.45 | -    | 1.25 | V    |

| V <sub>CLAMPD</sub> | Default current mode clamp voltage                 | UFP mode; $VDD = 0$ ,<br>VBUS = 0                               | 0.25 | -    | 1.25 | V    |

| V <sub>TUM</sub>    | Medium current mode detection threshold            | UFP mode                                                        | 1.16 | 1.23 | 1.31 | V    |

| V <sub>TUS</sub>    | Standard current mode detection threshold          | UFP mode                                                        | 0.61 | 0.66 | 0.70 | V    |

| V <sub>TURa</sub>   | Powered Accessory (Ra)<br>mode detection threshold | UFP mode                                                        | 0.15 | 0.2  | 0.25 | V    |

| V <sub>TDH,Ra</sub> | High current mode Ra detection threshold           | DFP mode                                                        | 0.75 | 0.8  | 0.85 | V    |

| V <sub>TD,Rd</sub>  | Rd detection threshold                             | DFP mode                                                        | 2.45 | 2.6  | 2.75 | V    |

| V <sub>TDM,Ra</sub> | Medium current mode Ra detection threshold         | DFP mode                                                        | 0.35 | 0.4  | 0.45 | V    |

| V <sub>TDS,Ra</sub> | Standard current mode Ra detection threshold       | DFP mode                                                        | 0.15 | 0.2  | 0.25 | V    |

## **11.3 VCONN switch characteristics**

#### Table 10. VCONN switch characteristics

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27  $\degree$  (unless otherwise noted).

| Symbol                | Parameter        | Conditions                                                                                                  | Min | Тур | Max | Unit |

|-----------------------|------------------|-------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>VCONN_IN</sub> | VCONN_IN voltage |                                                                                                             | 2.7 | -   | 5.5 | V    |

| I <sub>VCONN_IN</sub> | DC Current       |                                                                                                             | -   | -   | 1   | А    |

| R <sub>ON</sub>       | ON resistance    |                                                                                                             | -   | 150 | 240 | mΩ   |

| C <sub>ON</sub>       | ON capacitance   |                                                                                                             | -   | 450 | -   | pF   |

| C <sub>OFF</sub>      | OFF Capacitance  |                                                                                                             | -   | 250 | -   | pF   |

| l <sub>inrush</sub>   | Inrush current   | When VCONN switch is<br>enabled; corresponding<br>CCx pin voltage is zero; CC<br>capacitance = $10 \ \mu F$ | -   | -   | 150 | mA   |

#### Table 10. VCONN switch characteristics ... continued

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27  $\degree$  (unless otherwise noted).

| Symbol           | Parameter                                         | Conditions            | Min | Тур  | Max  | Unit |

|------------------|---------------------------------------------------|-----------------------|-----|------|------|------|

| I <sub>FCP</sub> | Forward Current Protection<br>Limit               | @ threshold of 250 mA | 125 | 250  | 350  | mA   |

|                  |                                                   | @ threshold of 500 mA | 350 | 500  | 700  | mA   |

|                  |                                                   | @ threshold of 1 A    | 700 | 1000 | 1300 | mA   |

| I <sub>RCP</sub> | Reverse Current Protection limit                  |                       | -   | 60   | 110  | mA   |

| T <sub>dis</sub> | VCONN Switch disable time due to FCP or RCP fault |                       | -   | -    | 300  | μs   |

## **11.4 Power AC/DC characteristics**

#### Table 11. Power AC/DC characteristics

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27 °C (unless otherwise noted). [1]

| Symbol                 | Parameter                                   | Conditions                                                                      | Min | Тур | Max | Unit |

|------------------------|---------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>MCUPWR</sub>    | DC Voltage on V_MCUPWR pin                  | Applies to both VBUS and VDD                                                    | 2.5 | -   | 3.6 | V    |

| I <sub>MCUPWR</sub>    | DC Current delivered out of<br>V_MCUPWR pin | Applies to both VBUS and VDD;                                                   | -   | -   | 30  | mA   |

|                        |                                             | 2.2 μF ±10 %                                                                    |     |     |     |      |

|                        |                                             | De-coupling capacitor on<br>V_MCUPWR pin                                        |     |     |     |      |

| l <sub>inrush</sub>    | Inrush current                              | 2.2 $\mu$ F capacitors on<br>BYPASS and V_MCUPWR<br>pins, these pins are at 0 V | -   | 150 | -   | mA   |

| V <sub>OUT_load</sub>  | V_MCUPWR voltage                            | VBUS @ 3.7 V, load current 30 mA                                                | 2.5 | -   | 3.6 | V    |

| $V_{Line\_reg}$        | Line voltage regulation                     | VBUS sweep 3.7 V to 25 V;<br>load current 30 mA                                 | -   | -   | 200 | mV   |

| V <sub>Load_reg</sub>  | Load voltage regulation                     | VBUS @ 3.7 V; load<br>current sweep 0 mA to<br>30 mA                            | -   | -   | 50  | mV   |

| V <sub>Load_step</sub> | Load voltage variation under load step      | VBUS @ 3.7 V; load<br>current step from 0 to<br>30 mA over 30 μS interval       | -   | -   | 150 | mV   |

| PSRR                   | Power supply rejection ratio                | VBUS @ 3.7 V to 25 V                                                            |     |     |     |      |

|                        |                                             | DC                                                                              |     | 70  |     | dB   |

|                        |                                             | F = 100 kHz                                                                     |     | 50  |     | dB   |

|                        |                                             | F = 1 MHz                                                                       |     | 30  |     | dB   |

[1] For all the specification measurements, supply decoupling capacitor 2.2  $\mu$ A ±10 % is considered to be present on V\_MCUPWR pin. Also, the capacitor is charged up to V\_MCUPWR voltage unless otherwise specified.

## **11.5 I2C characteristics**

#### Table 12. I2C characteristics

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27  $\degree$  (unless otherwise noted).<sup>[1]</sup>

| Symbol              | Parameter                                         | Conditions                                                            | Min            | Тур | Max            | Unit |

|---------------------|---------------------------------------------------|-----------------------------------------------------------------------|----------------|-----|----------------|------|

| F <sub>I2C</sub>    | I2C clock frequency                               |                                                                       | 0              | -   | 1000           | kHz  |

| V <sub>IH</sub>     | HIGH-level Input voltage                          |                                                                       | 0.7 ×<br>VDDIO | -   | -              | V    |

| V <sub>IL</sub>     | LOW-level Input voltage                           |                                                                       | -              | -   | 0.3 ×<br>VDDIO | V    |

| V <sub>hys</sub>    | Hysteresis of Schmitt trigger inputs              | VDDIO > 2 V                                                           | 0.05×<br>VDDIO | -   | -              | V    |

|                     |                                                   | VDDIO < 2 V                                                           | 0.1 ×<br>VDDIO | -   | -              | V    |

| V <sub>OL</sub>     | LOW-level output voltage at                       | VDDIO > 2 V                                                           | 0              | -   | 0.4            | V    |

|                     | 3mA sink current                                  | VDDIO < 2 V                                                           | 0              | -   | 0.2×<br>VDDIO  | V    |

| l <sub>OL</sub>     | LOW-level output current                          | V <sub>OL</sub> = 0.4 V;                                              | 3              | -   | -              | mA   |

|                     |                                                   | Standard and Fast modes                                               |                |     |                |      |

|                     |                                                   | V <sub>OL</sub> = 0.4 V;                                              | 20             | -   | -              | mA   |

|                     |                                                   | Fast mode plus                                                        |                |     |                |      |

|                     |                                                   | V <sub>OL</sub> = 0.6 V;                                              | 6              | -   | -              | mA   |

|                     |                                                   | Fast mode                                                             |                |     |                |      |

| IIL                 | LOW-level input current                           | Pin voltage - 0.1×VDDIO to 0.9×VIO, max                               | -10            | -   | 10             | μA   |

| CI                  | Capacitance of IO pin                             |                                                                       | -              | -   | 10             | pF   |

| t <sub>HD,STA</sub> | Hold time (repeated) START condition              | Fast mode plus; After this period, the first clock pulse is generated | 0.26           | -   | -              | μS   |

| t <sub>LOW</sub>    | LOW period of I2C clock                           | Fast mode plus                                                        | 0.5            | -   | -              | μs   |

| <sup>t</sup> HIGH   | HIGH period of I2C clock                          | Fast mode plus                                                        | 0.26           | -   | -              | μs   |

| t <sub>SU;STA</sub> | Setup time (repeated)<br>START condition          | Fast mode plus                                                        | 0.26           | -   | -              | μS   |

| t <sub>HD;DAT</sub> | Data Hold time                                    | Fast mode plus                                                        | 0              | -   | -              | μs   |

| t <sub>SU;DAT</sub> | Data Setup time                                   | Fast mode plus                                                        | 50             | -   | -              | ns   |

| t <sub>r</sub>      | Rise time of I2C_SCL and I2C_SDA signals          | Fast mode plus                                                        | -              | -   | 120            | ns   |

| t <sub>f</sub>      | Fall time of I2C_SCL and I2C_SDA signals          | Fast mode plus                                                        | -              | -   | 120            | ns   |

| t <sub>SU;STO</sub> | Setup time for STOP condition                     | Fast mode plus                                                        | 0.26           | -   | -              | μS   |

| t <sub>BUF</sub>    | Bus free time between<br>STOP and START condition | Fast mode plus                                                        | 0.5            | -   | -              | μS   |

#### Table 12. I2C characteristics ... continued

Applicable across operating temperature and power supply ranges as per <u>Section 10</u> (unless otherwise noted). Typical values are specified at 27  $\degree$  (unless otherwise noted).<sup>[1]</sup>

| Symbol              | Parameter                                                           | Conditions     | Min  | Тур | Max | Unit |