# Lark Board

# **User Manual**

Version 1.1 – Aug. 30<sup>th</sup>, 2014

# **Copyright Statement:**

- Lark Board and its related intellectual property are owned by Shenzhen Embest Technology Co., Ltd.

- Shenzhen Embest Technology has the copyright of this document and reserves all rights. Any part of the document should not be modified, distributed or duplicated in any approach and form with the written permission issued by Embest Technology Co., Ltd.

# **Disclaimer:**

Shenzhen Embest Technology does not take warranty of any kind, either expressed or implied, as to the program source code, software and documents in the CD/DVD-ROMs provided along with the products, and including, but not limited to, warranties of fitness for a particular purpose; The entire risk as to the quality or performance of the program is with the user of products.

# FCC NOTICE:

# This kit is designed to allow:

(1) Product developers to evaluate electronic components, circuitry, or software associated with the kit to determine whether to incorporate such items in a finished product and

(2) Software developers to write software applications for use with the end product. This kit is not a finished product and when assembled may not be resold or otherwise marketed unless all required FCC equipment authorizations are first obtained. Operation is subject to the condition that this product not cause harmful interference to licensed radio stations and that this product accept harmful interference.. For evaluation only; not FCC approved for resale

# **European Union Notice:**

This kit is a custom built evaluation kit destined for professionals to be used solely at research and development facilities for such purposes.

# **Revision History:**

| Version | Date      | Description      |

|---------|-----------|------------------|

| 1.0     | 2014-6-30 | Original Version |

| 1.1     | 2014-8-30 | Revision         |

# **Table of Contents**

| Chapter 1 | Product    | t Overview               | 1 |

|-----------|------------|--------------------------|---|

| 1.1       | Brief Inti | roduction                | 1 |

|           | 1.1.1      | Packing List             | 1 |

|           | 1.1.2      | Product Features         | 2 |

| 1.2       | System     | Block Diagram            | 4 |

| 1.3       | Product    | Dimensions(mm)           | 5 |

| Chapter 2 | Introdu    | ction to Hardware System | 6 |

| 2.1       | Overviev   | w of CPU                 | 6 |

| 2.2       | Introduc   | tion to Peripheral Chips | 6 |

|           | 2.2.1      | DDR3                     | 6 |

|           | 2.2.2      | eMMC Flash               | 1 |

|           | 2.2.3      | CH7033B1                 | 1 |

|           | 2.2.4      | AR80351                  | 1 |

| 2.3       | I/O Volta  | ages12                   | 2 |

| 2.4       | Details o  | of Interfaces12          | 2 |

|           | 2.4.1      | LCD/VGA/HDMI1            | 3 |

|           | 2.4.2      | SDI18                    | 8 |

|           | 2.4.3      | PCIe1                    | 8 |

|           | 2.4.4      | Camera20                 | 0 |

|           | 2.4.5      | ADC & Pre-Amp2           | 1 |

|           | 2.4.6      | Gigabit Ethernet24       | 4 |

|           | 2.4.7      | eMMC& TF Card2           | 5 |

|           | 2.4.8      | USB PHY & HUB2           | 7 |

|           | 2.4.9      | USB Blaster & JTAG24     | 8 |

|           | 2.4.10     | DIP Switch               | 0 |

|           | 2.4.11     | Jumpers                  | 3 |

|           | 2.4.12     | Buttons                  | 3 |

|           | 2.4.13     | UART                     | 4 |

|           | 2.4.14     | LED                      | 5 |

|           | 2.4.15     | RTC                      | 6 |

|           | 2.4.16     | Extension Interfaces     | 6 |

# mbest Embest Technology

| Chapter 3 | Quick U   | se of Lark Board                           | 39 |

|-----------|-----------|--------------------------------------------|----|

| Chapter 4 | Linux     |                                            | 44 |

| 4.1       | Linux Sy  | vstem Structure of Lark Board              | 44 |

| 4.2       | Software  | e Resources                                | 44 |

| 4.3       | Building  | Development Environment                    | 46 |

|           | 4.3.1     | Building Linux Development Environment     | 46 |

|           | 4.3.2     | Installing Altera SoC Development Software | 47 |

|           | 4.3.3     | Installing Linux Cross-Compiler (Optional) | 47 |

| 4.4       | System    | Compilation                                | 47 |

|           | 4.4.1     | Compiling U-boot and Preloader             | 48 |

|           | 4.4.2     | Compiling Linux Kernel                     |    |

|           | 4.4.3     | Generating FPGA RBF Configuration File     | 49 |

| 4.5       | System    | Update                                     | 52 |

|           | 4.5.1     | Updating Images in TF Card                 | 52 |

|           | 4.5.2     | Updating Images in eMMC Flash              | 56 |

| 4.6       | Introduc  | tion to Drivers                            | 60 |

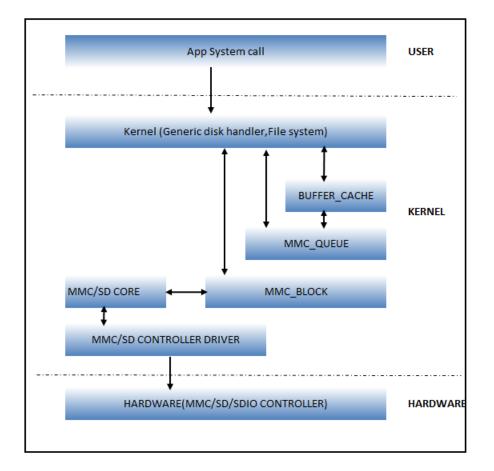

|           | 4.6.1     | MMC/SD Driver                              | 61 |

|           | 4.6.2     | Frame Buffer Driver                        | 62 |

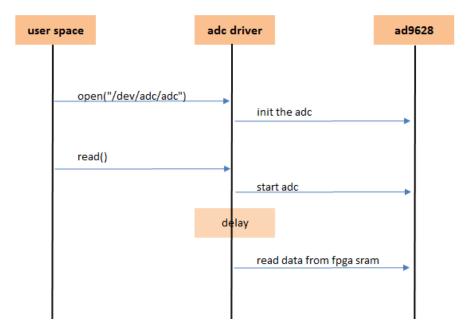

|           | 4.6.3     | ADC Driver                                 | 63 |

| 4.7       | Configur  | ing Display Modes                          | 65 |

|           | 4.7.1     | VGA/HDMI Output                            | 65 |

|           | 4.7.2     | Configuring for 7" LCD                     | 66 |

|           | 4.7.3     | Configuring for 4.3" LCD                   | 66 |

| 4.8       | Example   | Applications                               | 66 |

|           | 4.8.1     | LED Test                                   | 66 |

|           | 4.8.2     | Button (Keypad) Test                       | 67 |

|           | 4.8.3     | PCIe Test                                  | 68 |

|           | 4.8.4     | Network Interface Test                     | 69 |

|           | 4.8.5     | ADC Test                                   | 70 |

|           | 4.8.6     | CAM8000-D Camera Test                      | 70 |

| 4.9       | Applicati | on Development and DS-5 Debugging          | 72 |

|           | 4.9.1     | Development of LED Application             | 72 |

# mbes: Embest Technology

|           | 4.9.2   | Development of FFT Application                           | .73 |

|-----------|---------|----------------------------------------------------------|-----|

|           | 4.9.3   | DS-5 Debugging                                           | .77 |

| Chapter 5 | FPGA    |                                                          | .79 |

| 5.1       | FPGA    | Resources                                                | .79 |

| 5.2       | FPGA    | Development                                              | .79 |

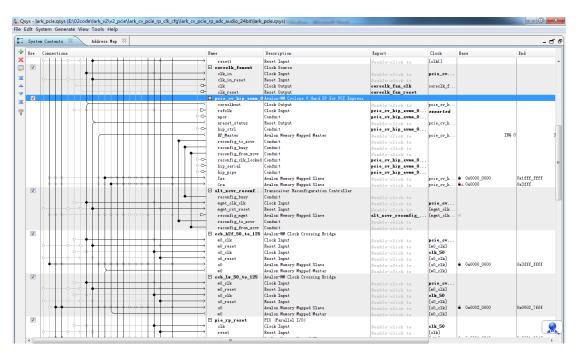

|           | 5.2.1   | Building FPGA Project and Programming SOF File into FPGA | .80 |

|           | 5.2.2   | Elipse Debugging                                         | .83 |

| 5.3       | FPGA    | Function Implementation on Lark Board                    | .87 |

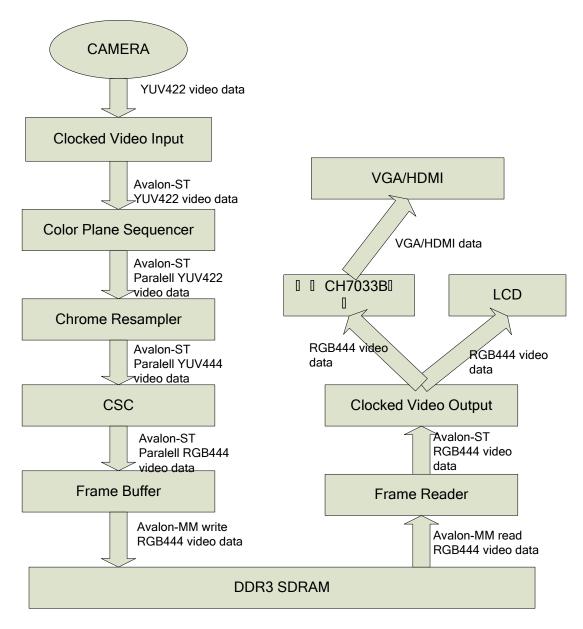

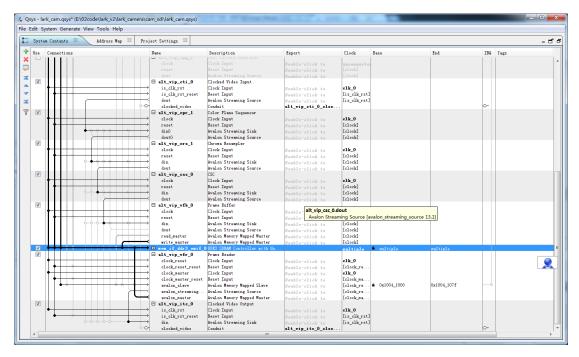

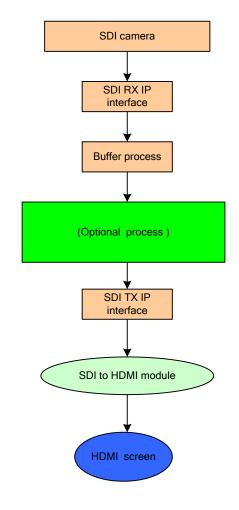

|           | 5.3.1   | Input of Camera Video                                    | .87 |

|           | 5.3.2   | Output of Camera Video                                   | .89 |

|           | 5.3.3   | LCD/VGA/HDMI Video Output                                | .92 |

|           | 5.3.4   | Input/output of SDI Video                                | .95 |

|           | 5.3.5   | Input Data from ADC                                      | .99 |

|           | 5.3.6   | PCIe Function1                                           | 100 |

| Technical | Support | and Warranty1                                            | 104 |

# **Chapter 1 Product Overview**

# **1.1 Brief Introduction**

Lark Board is an evaluation board designed by Embest based on an Altera ARM (Cortex-A9 dual-core)+FPGA processor for areas such as medical instruments, video surveillance and industrial control. The SoC, named 5CSXFC6D6F31 that comes from Cyclone V SX family, integrates not only the traditional FPGA fabric, but also an ARM Cortex-A9-based HPS (operating at 800MHz) and a high-speed transceiver (3Gbps Serdes) hard subsystem.

Lark Board provides 1GB DDR3 SDRAM separately for both ARM and FPGA, and has 4 high-speed USB2.0 Host interfaces, a TF card slot for mass storage, a 12-bit camera interface, a VGA interface, a 24-bit LCD interface, PCIe, UART, JTAG, 3Gbps SDI input/output and a HDMI interface. Additionally, two 2\*200-pin connectors are mounted on the board in order to make the unused pins of HPS/FPGA available for users. Lark Board uses a switching power supply controller chip (integrated with inductor) that comes from Altera's Enpirion family to provide a stable and efficient output for each BANK of FPGA. Meanwhile, it has two on-board DIP switches used to enable various voltage levels required by the different interfaces on the board with the purpose to facilitate power consumption evaluation conducted by users.

Lark Board comes with a lot of FPGA example applications and the corresponding source code, Linux 3.10 and u-boot source code and Debian 7.4 system image, as well as schematics and key chips' datasheets to help users implement evaluation and secondary development fast.

# 1.1.1 Packing List

- Lark Board×1

- USB cable for FPGA programming and control×1

- 19V DC power adapter×1

- 8GB TF card×1

- 12V-DC Fan

# 1.1.2 Product Features

- General Specifications:

- Operating Temperature: 0°C ~ 70°C

- Power Supply: 12~20V

- Operating Humidity: 20% ~ 90%

- Dimensions: 180mm x 120mm

- PCB Layers: 10-layer PCB

- SoC Specifications:

- FPGA: up to 110K logic cells (LE), 5570 M10K, 621 MLABs, 112 variable-precision DSP blocks, 224 18x18 multipliers, 6 PLLs, 288 IOs, 72+72 LVDS transceiver, and a memory controller.

- HPS: a dual-core ARM Cortex A9 MPCore processor, a memory controller (DDR3), 3 PLLs and 181 general IOs, as well as a rich set of peripheral interfaces such as UART, I2C, USB, SPI, GPIO and EMAC.

- High-speed transceiver includes 2 PCIe hard IPs and 9 3Gbps transceivers.

- On-Board Memories:

- 1GB DDR3 SDRAM for HPS

- 1GB DDR3 SDRAM for FPGA

- 4GB eMMC Flash

- Data Transfer Interfaces:

- A SDI high-resolution serial digital interface that supports SMD standard interface and provides a SDI TX and a SDI RX

- A 12-bit digital camera input

- Two 12-bit high-speed ADC interfaces that support SMA input

- A PCIex4 connector for PCIex4, PCIex2 and PCIex1 adapter cards

- A RJ45 interface that supports RGMII gigabit Ethernet

- Four high-speed USB2.0 Host interfaces

- A TF card slot (TF card and eMMC flash cannot be used simultaneously)

- A 40-pin FPGA expansion interface (for LVDS, RSDS, SLVS, mini-LVDS signals)

- A 40-pin HPS expansion IO (for I2C, SPI, QSPI, UART, GPIO signals)

# • Debugging Interfaces:

- An on-board USB Blaster II (Mini USB Type B)

- A 10-pin JTAG interface can be used to connect an external USB Blaster

- Support UART serial debugging

# • Audio/Video Interfaces:

- A 24-bit true-color LCD interface (supporting 4-wire touch screen)

- A VGA interface

- A HDMI interface

# • Other Interfaces & Buttons

- A power jack (12V~30V round DC power jack and ATX 4-pin standard power connector)

- A reset button and 5 user-defined buttons

- A RTC

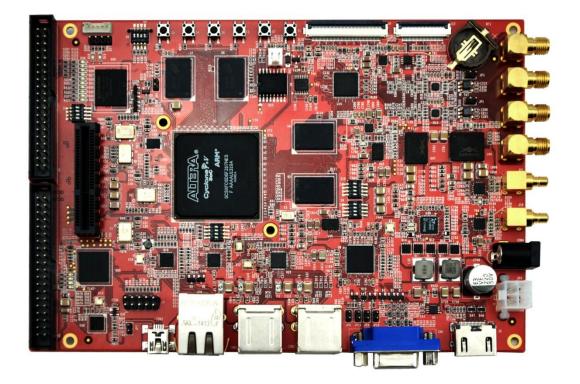

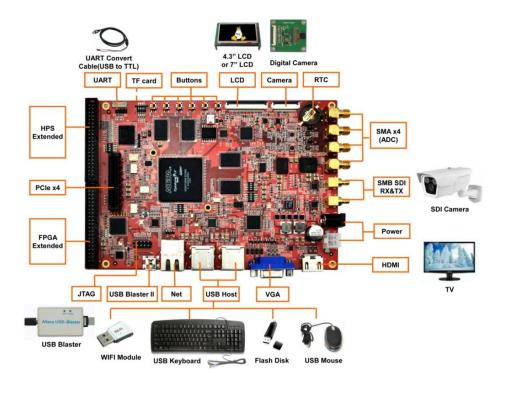

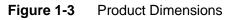

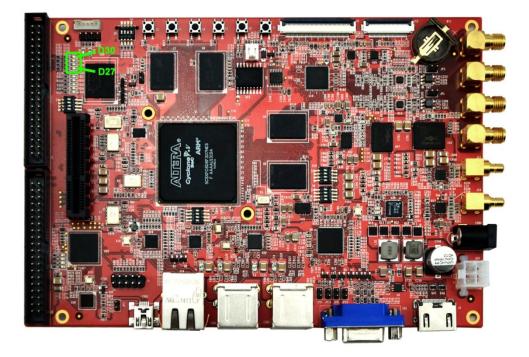

Figure 1-1 Interfaces and Buttons

# 1.2 System Block Diagram

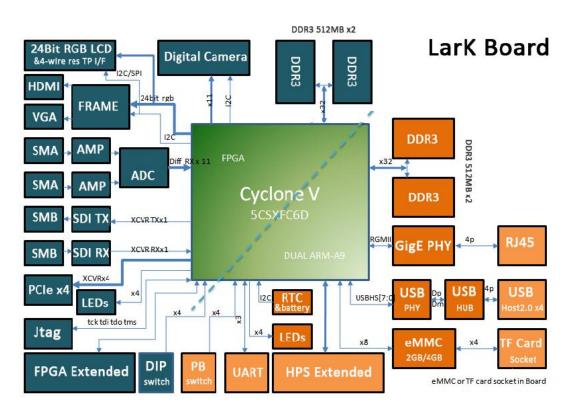

Figure 1-2 System block diagram

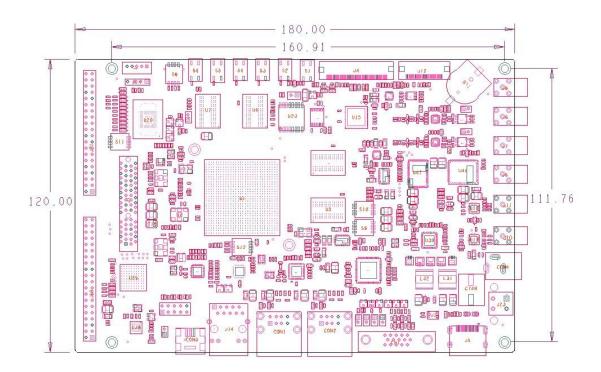

# 1.3 Product Dimensions(mm)

# Chapter 2 Introduction to Hardware System

This chapter will introduce in detail the structure, expansion and peripheral interfaces of Lark Board hardware system.

# 2.1 Overview of CPU

Cyclone SX SoC FPGAs is the new generation developed by Altera to satisfy the demand for products that require low power, low cost and short time-to-market, while need high-speed and stable processing bandwidth. It not only has the logic resources of traditional FPGAs, but also integrates a dual-core ARM Cortex A9 processor system and a high-speed serial transceiver hard core, making it suited for the areas such as industrial control, wireless and wired communication, medical, military and automotive electronics.

The SoC used on Lark Board is the most sophisticated FPGA chip in SX family (5CSXFC6D6F31 in FBGA 896 package). It has three core resources:

- FPGA: up to 110K logic cells (LE), 5570 M10K memory blocks, 621 MLABs, 112 variable-precision DSP blocks, 224 18x18 multipliers, 6 PLLs, 288 IOs, 72+72 LVDS transceiver, and a memory controller.

- HPS: a dual-core ARM Cortex A9 MPCore processor, a memory controller (DDR3), 3 PLLs and 181 general IOs, as well as a rich set of peripheral interfaces such as UART, I2C, USB, SPI, GPIO and EMAC.

- Serdes: 9 3Gbps transceivers and 2 PCIe hard IPs.

# 2.2 Introduction to Peripheral Chips

# 2.2.1 DDR3

5CSXFC6D6F SoC has a hard memory controller separately for FPGA and HPS with a purpose to extend more external dynamic memory spaces. Accordingly, Lark Board

integrates two DDR3 SDRAM chips for FPGA and another two chips for HPS, giving each of them 1GB external memory space.

### HPS DDR3

The HMC of HPS is an effective expansion for the access space of ARM Cortex A9 processor; It receives events come from AMBA AXI bus and Avalon-MM bus, and converts them into proper SDRAM instructions to manage the accesses to SDRAM.

As for hardware circuitry design, there a 73 signal lines in total on DDR3 SDRAM interface, which includes 44 data lines (32 DQ, 4 DM, 4 pairs of DQS), 15 address lines, 11 instruction lines, 2 clock lines and 1 ZQ calibration resistive line. Because DDR is source-synchronous time sequence interface model, the signals related to each other require same-length traces on PCB layout to ensure timing closure. In addition, parameters such as time sequence, driving capability and on-chip match can be configured in Qsys, and therefore being consistent with the physical design is required; it would be wise to add a matching resistor in parallel on the board because the address and instruction signals are working under two-driven-by-one mode.

The following table contains the interface definition and signal connections of HPS DDR3.

|     | HPS DDR3                       |     |                |             |  |  |

|-----|--------------------------------|-----|----------------|-------------|--|--|

| Pin | Pin Bank Direction Signal Name |     | Signal Name    | Signal Type |  |  |

| M23 | 6A                             | Out | DDR3_HPS_CLK_P | Clock       |  |  |

| L23 | 6A                             | Out | DDR3_HPS_CLK_N | CIUCK       |  |  |

| F26 | 6A                             | Out | DDR3_HPS_A0    |             |  |  |

| G30 | 6A                             | Out | DDR3_HPS_A1    |             |  |  |

| F28 | 6A                             | Out | DDR3_HPS_A2    |             |  |  |

| F30 | 6A                             | Out | DDR3_HPS_A3    | Address     |  |  |

| J25 | 6A                             | Out | DDR3_HPS_A4    | Address     |  |  |

| J27 | 6A                             | Out | DDR3_HPS_A5    |             |  |  |

| F29 | 6A                             | Out | DDR3_HPS_A6    |             |  |  |

| E28 | 6A                             | Out | DDR3_HPS_A7    |             |  |  |

| Table 2-1 HPS DDR3 |

|--------------------|

|--------------------|

|     |    |     | HPS DDR3          |           |

|-----|----|-----|-------------------|-----------|

| H27 | 6A | Out | DDR3_HPS_A8       |           |

| G26 | 6A | Out | DDR3_HPS_A9       |           |

| D29 | 6A | Out | DDR3_HPS_A10      |           |

| C30 | 6A | Out | DDR3_HPS_A11      |           |

| B30 | 6A | Out | DDR3_HPS_A12      |           |

| C29 | 6A | Out | DDR3_HPS_A13      |           |

| H25 | 6A | Out | DDR3_HPS_A14      |           |

| P30 | 6A | Out | DDR3_HPS_RESETn   |           |

| L29 | 6A | Out | DDR3_HPS_CKE      | -         |

| H28 | 6A | Out | DDR3_HPS_ODT      |           |

| E29 | 6A | Out | DDR3_HPS_BA0      | -         |

| J24 | 6A | Out | DDR3_HPS_BA1      | -         |

| J23 | 6A | Out | DDR3_HPS_BA2      | Control & |

| E27 | 6A | Out | <br>DDR3_HPS_CASn | Command   |

| D30 | 6A | Out | DDR3_HPS_RASn     | -         |

| H24 | 6A | Out | DDR3_HPS_CSn      | -         |

| C28 | 6A | Out | DDR3_HPS_WEn      | -         |

| D27 | 6A | In  | HPS_RZQ           | -         |

| K23 | 6A | IO  | DDR3_HPS_DQ0      |           |

| K22 | 6A | IO  | DDR3_HPS_DQ1      |           |

| H30 | 6A | IO  | DDR3_HPS_DQ2      |           |

| G28 | 6A | IO  | DDR3_HPS_DQ3      |           |

| L25 | 6A | 10  | DDR3_HPS_DQ4      |           |

| L24 | 6A | 10  | DDR3_HPS_DQ5      | Data      |

| J30 | 6A | 10  | DDR3_HPS_DQ6      | Group 0   |

| J29 | 6A | Ю   | DDR3_HPS_DQ7      |           |

| K28 | 6A | Ю   | DDR3_HPS_DM0      |           |

| N18 | 6A | IO  | DDR3_HPS_DQS_P0   |           |

| M19 | 6A | IO  | DDR3_HPS_DQS_N0   |           |

| K26 | 6A | IO  | DDR3_HPS_DQ8      |           |

| L26 | 6A | IO  | DDR3_HPS_DQ9      |           |

| K29 | 6A | IO  | DDR3_HPS_DQ10     |           |

| K27 | 6A | IO  | DDR3_HPS_DQ11     |           |

| M26 | 6A | IO  | DDR3_HPS_DQ12     | Data      |

| M27 | 6A | IO  | DDR3_HPS_DQ13     | Data      |

| L28 | 6A | Ю   | DDR3_HPS_DQ14     | Group 1   |

| M30 | 6A | IO  | DDR3_HPS_DQ15     |           |

| M28 | 6A | Ю   | DDR3_HPS_DM1      | 1         |

| N25 | 6A | IO  | DDR3_HPS_DQS_P1   |           |

| N24 | 6A | IO  | DDR3_HPS_DQS_N1   |           |

| U26 | 7A | Ю   | DDR3_HPS_DQ16     | Data      |

| T26 | 7A | Ю   | DDR3_HPS_DQ17     | Group 2   |

|     |    |    | HPS DDR3        |         |

|-----|----|----|-----------------|---------|

| N29 | 7A | IO | DDR3_HPS_DQ18   |         |

| N28 | 7A | IO | DDR3_HPS_DQ19   |         |

| P26 | 7A | IO | DDR3_HPS_DQ20   |         |

| P27 | 7A | IO | DDR3_HPS_DQ21   |         |

| N27 | 7A | IO | DDR3_HPS_DQ22   |         |

| R29 | 7A | IO | DDR3_HPS_DQ23   |         |

| R28 | 7A | IO | DDR3_HPS_DM2    |         |

| R19 | 7A | IO | DDR3_HPS_DQS_P2 |         |

| R18 | 7A | IO | DDR3_HPS_DQS_N2 |         |

| P24 | 7A | IO | DDR3_HPS_DQ24   |         |

| P25 | 7A | IO | DDR3_HPS_DQ25   |         |

| T29 | 7A | IO | DDR3_HPS_DQ26   |         |

| T28 | 7A | IO | DDR3_HPS_DQ27   |         |

| R27 | 7A | IO | DDR3_HPS_DQ28   | Data    |

| R26 | 7A | IO | DDR3_HPS_DQ29   |         |

| V30 | 7A | IO | DDR3_HPS_DQ30   | Group 3 |

| W29 | 7A | IO | DDR3_HPS_DQ31   |         |

| W30 | 7A | IO | DDR3_HPS_DM3    |         |

| R22 | 7A | IO | DDR3_HPS_DQS_P3 |         |

| R21 | 7A | IO | DDR3_HPS_DQS_N3 |         |

### • FPGA DDR3

FPGA has the similar HMC which also enjoys an extended 1GB dynamic RAM; the hardware design of FPGA DDR3 is almost the same as HPS DDR3.

The following table contains interface definition and signal connection of FPGA DDR3.

#### Table 2-2 FPGA DDR3

|      | FPGA DDR3 |           |                 |             |  |  |

|------|-----------|-----------|-----------------|-------------|--|--|

| Pin  | Bank      | Direction | Signal Name     | Signal Type |  |  |

| AA14 | 3B        | Out       | DDR3_FPGA_CLK_P | Clock       |  |  |

| AA15 | 3B        | Out       | DDR3_FPGA_CLK_N | Clock       |  |  |

| AJ14 | 3B        | Out       | DDR3_FPGA_A0    |             |  |  |

| AK14 | 3B        | Out       | DDR3_FPGA_A1    | Address     |  |  |

| AH12 | 3B        | Out       | DDR3_FPGA_A2    |             |  |  |

| AJ12 | 3B        | Out       | DDR3_FPGA_A3    |             |  |  |

| AG15 | 3B        | Out       | DDR3_FPGA_A4    |             |  |  |

| AH15 | 3B        | Out       | DDR3_FPGA_A5    |             |  |  |

| AK12 | 3B        | Out       | DDR3_FPGA_A6    |             |  |  |

|      |    |     | FPGA DDR3        |                   |

|------|----|-----|------------------|-------------------|

| AK13 | 3B | Out | DDR3_FPGA_A7     |                   |

| AH13 | 3B | Out | DDR3_FPGA_A8     |                   |

| AH14 | 3B | Out | DDR3_FPGA_A9     |                   |

| AJ9  | 3B | Out | DDR3_FPGA_A10    |                   |

| AK9  | 3B | Out | DDR3_FPGA_A11    |                   |

| AK7  | 3B | Out | DDR3_FPGA_A12    |                   |

| AK8  | 3B | Out | DDR3_FPGA_A13    |                   |

| AG12 | 3B | Out | DDR3_FPGA_A14    |                   |

| AK21 | 4A | Out | DDR3_FPGA_RESETn |                   |

| AJ21 | 4A | Out | DDR3_FPGA_CKE    |                   |

| AE16 | 4A | Out | DDR3_FPGA_ODT    |                   |

| AH10 | 3B | Out | DDR3_FPGA_BA0    |                   |

| AJ11 | 3B | Out | DDR3_FPGA_BA1    | Control 8         |

| AK11 | 3B | Out | DDR3_FPGA_BA2    | Control & Command |

| AH7  | 3B | Out | DDR3_FPGA_CASn   | Command           |

| AH8  | 3B | Out | DDR3_FPGA_RASn   |                   |

| AB15 | 3B | Out | DDR3_FPGA_CSn    |                   |

| AJ6  | 3B | Out | DDR3_FPGA_WEn    |                   |

| AG17 | 4A | In  | FPGA_RZQ         |                   |

| AF18 | 4A | IO  | DDR3_FPGA_DQ0    |                   |

| AE17 | 4A | IO  | DDR3_FPGA_DQ1    |                   |

| AG16 | 4A | IO  | DDR3_FPGA_DQ2    |                   |

| AF16 | 4A | IO  | DDR3_FPGA_DQ3    |                   |

| AH20 | 4A | IO  | DDR3_FPGA_DQ4    | Dete              |

| AG21 | 4A | IO  | DDR3_FPGA_DQ5    | Data<br>Group 0   |

| AJ16 | 4A | IO  | DDR3_FPGA_DQ6    | Gloup 0           |

| AH18 | 4A | IO  | DDR3_FPGA_DQ7    |                   |

| AH17 | 4A | IO  | DDR3_FPGA_DM0    |                   |

| V16  | 4A | IO  | DDR3_FPGA_DQS_P0 |                   |

| W16  | 4A | IO  | DDR3_FPGA_DQS_N0 |                   |

| AK18 | 4A | IO  | DDR3_FPGA_DQ8    |                   |

| AJ17 | 4A | IO  | DDR3_FPGA_DQ9    |                   |

| AG18 | 4A | 10  | DDR3_FPGA_DQ10   |                   |

| AK19 | 4A | 10  | DDR3_FPGA_DQ11   |                   |

| AG20 | 4A | IO  | DDR3_FPGA_DQ12   | Dete              |

| AF19 | 4A | 10  | DDR3_FPGA_DQ13   | Data<br>Group 1   |

| AJ20 | 4A | IO  | DDR3_FPGA_DQ14   |                   |

| AH24 | 4A | 10  | DDR3_FPGA_DQ15   |                   |

| AG23 | 4A | IO  | DDR3_FPGA_DM1    |                   |

| V17  | 4A | 10  | DDR3_FPGA_DQS_P1 |                   |

| W17  | 4A | 10  | DDR3_FPGA_DQS_N1 |                   |

| AE19 | 4A | IO  | DDR3_FPGA_DQ16   | Data              |

|      |    |    | FPGA DDR3        |         |

|------|----|----|------------------|---------|

| AE18 | 4A | IO | DDR3_FPGA_DQ17   | Group 2 |

| AG22 | 4A | 10 | DDR3_FPGA_DQ18   |         |

| AK22 | 4A | 10 | DDR3_FPGA_DQ19   |         |

| AF21 | 4A | 10 | DDR3_FPGA_DQ20   |         |

| AF20 | 4A | 10 | DDR3_FPGA_DQ21   |         |

| AH23 | 4A | 10 | DDR3_FPGA_DQ22   |         |

| AK24 | 4A | 10 | DDR3_FPGA_DQ23   |         |

| AK23 | 4A | 10 | DDR3_FPGA_DM2    |         |

| Y17  | 4A | 10 | DDR3_FPGA_DQS_P2 |         |

| AA18 | 4A | 10 | DDR3_FPGA_DQS_N2 |         |

| AF24 | 4A | 10 | DDR3_FPGA_DQ24   |         |

| AF23 | 4A | 10 | DDR3_FPGA_DQ25   |         |

| AJ24 | 4A | 10 | DDR3_FPGA_DQ26   |         |

| AK26 | 4A | 10 | DDR3_FPGA_DQ27   |         |

| AE23 | 4A | 10 | DDR3_FPGA_DQ28   | Data    |

| AE22 | 4A | 10 | DDR3_FPGA_DQ29   | Group 3 |

| AG25 | 4A | 10 | DDR3_FPGA_DQ30   | Gloup 5 |

| AK27 | 4A | IO | DDR3_FPGA_DQ31   |         |

| AJ27 | 4A | IO | DDR3_FPGA_DM3    |         |

| AC20 | 4A | IO | DDR3_FPGA_DQS_P3 |         |

| AD19 | 4A | 10 | DDR3_FPGA_DQS_N3 |         |

# 2.2.2 eMMC Flash

KE4CN2H5A is the eMMC Flash used on Lark Board with a memory space of 4GB.

# 2.2.3 CH7033B

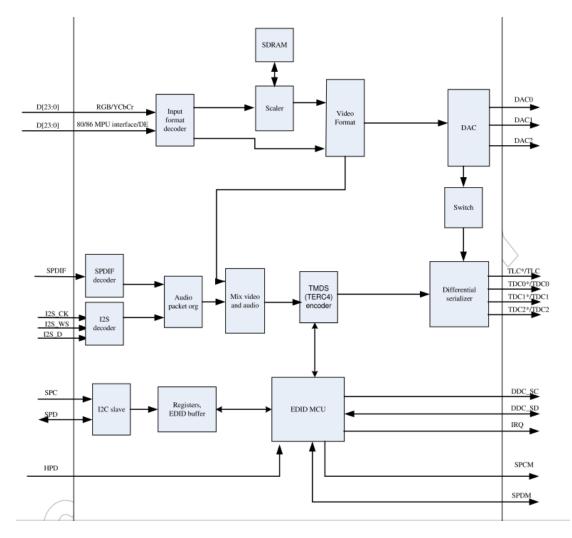

CH7033B is a video encoder designed to drive high-resolution displays through HDMI, DVI, YPbPr and VGA interfaces. It is suited for mobile Internet devices, laptops, tablet computers, portable e-books and smart phones.

This chip possesses advanced scaling engine that supports 1080P HDTV. The integrated frequency shifting engine can provide 60fps under 1080p mode. Additionally, CH7033B supports SPDIF and IIS digital audio output.

# 2.2.4 AR8035

AR8035 is a low-power and low-cost Ethernet PHY used on Lark Board and integrated with a 10/100/1000Mb transceiver. It is a single-port tri-speed Ethernet PHY and supports MAC.TM RGMII interfaces.

AR8035 is compliant with the IEEE 802.3az Energy Efficiency Ethernet Standard and the Atheros's proprietary SmartEEE standard, which allows traditional MAC/SoC devices incompatible with 802.3az to function as a complete 802.3az system.

Lark Board can be connected to a hub with a straight-though network cable, or connected to a computer with a crossover cable.

# 2.3 I/O Voltages

The following figure shows the number of valid I/O on each I/O bank of SoC and their voltages applied.

|    | I/O Bank Name | Pin No. | VCCIO Voltage | VREF Voltage | VCCPD Voltage |

|----|---------------|---------|---------------|--------------|---------------|

| 1  | BOL           | 14      | -             | -            | -             |

| 2  | B1L           | 14      | -             | -            | -             |

| 3  | B2L           | 14      | -             | -            | -             |

| 4  | 3A            | 42      | 3.3V          | GND          | 3.3V          |

| 5  | 3B            | 49      | 1.5V          | 0.75V        | 2.5V          |

| 6  | 4A            | 81      | 1.5V          | 0.75V        | 2.5V          |

| 7  | 5A            | 33      | 1.8V          | GND          | 2.5V          |

| 8  | 5B            | 17      | 1.8V          | GND          | 2.5V          |

| 9  | 6A            | 58      | 1.5V          | 0.75V        | 2.5V          |

| 10 | 6B            | 45      | 1.5V          | 0.75V        | 2.5V          |

| 11 | 7A            | 34      | 3.3V          | GND          | 3.3V          |

| 12 | 7B            | 22      | 3.3V          | GND          | 3.3V          |

| 13 | 7C            | 12      | 3.3V          | GND          | 3.3V          |

| 14 | 7D            | 14      | 3.3V          | GND          | 3.3V          |

| 15 | 8A            | 80      | 3.3V          | GND          | 3.3V          |

| 16 | 9A            | 10      | -             | -            | -             |

#### Table 2-3 I/O and voltages

# 2.4 Details of Interfaces

This section will introduce in detail the constructions, principles, interface definitions and considerations of use of peripherals on Lark Board so that users may have a deep understanding of the hardware circuitry of the board.

The peripheral interfaces and key on-board chips are shown below;

Figure 2-1 Top view of Lark Board

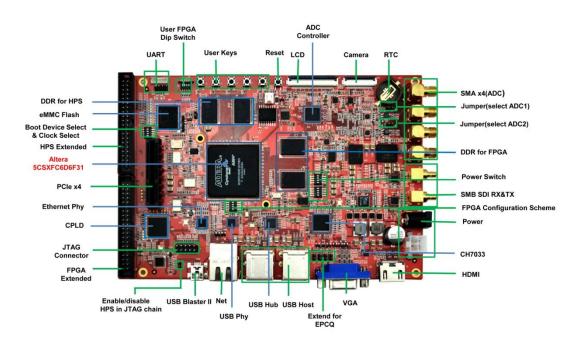

Figure 2-2 Bottom view of Lark Board

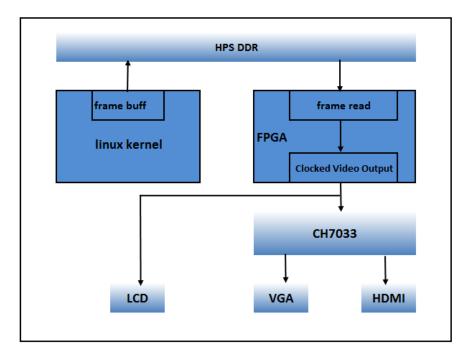

# 2.4.1 LCD/VGA/HDMI

The powerful video performance is one of the important features of Lark Board. It supports multiple types of displays including 50-pin medium-/small-sized LCD modules, VGA/HDMI and SDI monitors. LCD/VGA/HDMI shares the same video data source – Frame Buffer created in FPGA. Now let's take a deep look at the hardware implementation of the

display function of LCD/VGA/HDMI interfaces.

## • Frame Buffer

The video output of Lark Board comes from a frame buffer implemented by FPGA. The buffer has 28 signal lines in which there are 24 data lines, 3 control lines and 1 clock line. A 50-pin LCD can be connected directly to them to display images, while VGA/HDMI displays need the on-board chip CH7033B to convert the data before they can display any images; SDI also receive data from the frame buffer, but before that, conversions by the logic resources of FPGA are required as well.

|     | Display Data Output |           |             |             |  |

|-----|---------------------|-----------|-------------|-------------|--|

| Pin | Bank                | Direction | Signal Name | Signal Type |  |

| K12 | 8A                  | Out       | DSS_CLK     | Clock       |  |

| J12 | 8A                  | Out       | DSS_VSYNC   |             |  |

| H13 | 8A                  | Out       | DSS_HSYNC   | Control     |  |

| G13 | 8A                  | Out       | DSS_ACBIAS  |             |  |

| E11 | 8A                  | Out       | DSS_D0      |             |  |

| D9  | 8A                  | Out       | DSS_D1      |             |  |

| E9  | 8A                  | Out       | DSS_D2      |             |  |

| B6  | 8A                  | Out       | DSS_D3      |             |  |

| B5  | 8A                  | Out       | DSS_D4      |             |  |

| D5  | 8A                  | Out       | DSS_D5      |             |  |

| C4  | 8A                  | Out       | DSS_D6      |             |  |

| B1  | 8A                  | Out       | DSS_D7      |             |  |

| D7  | 8A                  | Out       | DSS_D8      |             |  |

| E8  | 8A                  | Out       | DSS_D9      |             |  |

| E2  | 8A                  | Out       | DSS_D10     | Data        |  |

| D2  | 8A                  | Out       | DSS_D11     |             |  |

| C2  | 8A                  | Out       | DSS_D12     |             |  |

| E3  | 8A                  | Out       | DSS_D13     |             |  |

| E6  | 8A                  | Out       | DSS_D14     |             |  |

| F6  | 8A                  | Out       | DSS_D15     |             |  |

| G12 | 8A                  | Out       | DSS_D16     |             |  |

| G11 | 8A                  | Out       | DSS_D17     |             |  |

| G7  | 8A                  | Out       | DSS_D18     |             |  |

| H8  | 8A                  | Out       | DSS_D19     |             |  |

| G8  | 8A                  | Out       | DSS_D20     |             |  |

Table 2-4 Display output pins

|     | Display Data Output |     |         |  |  |

|-----|---------------------|-----|---------|--|--|

| J7  | 8A                  | Out | DSS_D21 |  |  |

| H7  | 8A                  | Out | DSS_D22 |  |  |

| H14 | 8A                  | Out | DSS_D23 |  |  |

# LCD

The LCD interface (J4) of Lark Board is implemented with a 50-pin FPC connector which connects LCD module to the board. Currently LCD8000-43T (4.3 inch), LCD8000-70T (7 inch) and VGA8000 conversion module are supported by the board. The following table contains pin definitions of LCD interface (including the fixed pins of the connector).

|     | LCD Display: J4 |          |             |  |  |

|-----|-----------------|----------|-------------|--|--|

| Pin | Signal Name     | Device   | Signal Type |  |  |

| 1   | DSS_D0          | 5CSXFC6D |             |  |  |

| 2   | DSS_D1          | 5CSXFC6D |             |  |  |

| 3   | DSS_D2          | 5CSXFC6D |             |  |  |

| 4   | DSS_D3          | 5CSXFC6D | Data        |  |  |

| 5   | DSS_D4          | 5CSXFC6D | Blue        |  |  |

| 6   | DSS_D5          | 5CSXFC6D |             |  |  |

| 7   | DSS_D6          | 5CSXFC6D |             |  |  |

| 8   | DSS_D7          | 5CSXFC6D |             |  |  |

| 9   | GND             |          | Ground      |  |  |

| 10  | DSS_D8          | 5CSXFC6D |             |  |  |

| 11  | DSS_D9          | 5CSXFC6D |             |  |  |

| 12  | DSS_D10         | 5CSXFC6D |             |  |  |

| 13  | DSS_D11         | 5CSXFC6D | Data        |  |  |

| 14  | DSS_D12         | 5CSXFC6D | Green       |  |  |

| 15  | DSS_D13         | 5CSXFC6D |             |  |  |

| 16  | DSS_D14         | 5CSXFC6D |             |  |  |

| 17  | DSS_D15         | 5CSXFC6D |             |  |  |

| 18  | GND             |          | Ground      |  |  |

| 19  | DSS_D16         | 5CSXFC6D |             |  |  |

| 20  | DSS_D17         | 5CSXFC6D |             |  |  |

| 21  | DSS_D18         | 5CSXFC6D | Data        |  |  |

| 22  | DSS_D19         | 5CSXFC6D | Data<br>Red |  |  |

| 23  | DSS_D20         | 5CSXFC6D |             |  |  |

| 24  | DSS_D21         | 5CSXFC6D |             |  |  |

| 25  | DSS_D22         | 5CSXFC6D |             |  |  |

#### Table 2-5 LCD interface

|    | LCD               | Display: J4 |              |

|----|-------------------|-------------|--------------|

| 26 | DSS_D23           | 5CSXFC6D    |              |

| 27 | GND               |             | Ground       |

| 28 | DSS_ACBIAS        | 5CSXFC6D    | Data         |

| 29 | DSS_HSYNC         | 5CSXFC6D    | Data         |

| 30 | DSS_VSYNC         | 5CSXFC6D    | Sync         |

| 31 | GND               |             | Ground       |

| 32 | DSS_CLK           | 5CSXFC6D    | Clock        |

| 33 | GND               |             | Ground       |

| 34 | TOUCH_X1          | TSC2046     |              |

| 35 | TOUCH_X1          | TSC2046     | Touch        |

| 36 | TOUCH_X1          | TSC2046     | Panel        |

| 37 | TOUCH_X1          | TSC2046     |              |

| 38 | SPI0_FPGA_CLK     | 5CSXFC6D    |              |

| 39 | SPI0_FPGA_MOSI    | 5CSXFC6D    | SPI          |

| 40 | SPI0_FPGA_MISO    | 5CSXFC6D    | J SF1        |

| 41 | SPI0_FPGA_CSn1    | 5CSXFC6D    |              |

| 42 | LCD_I2C1_SCL      | 5CSXFC6D    | 12C          |

| 43 | LCD_I2C1_SDA      | 5CSXFC6D    | 120          |

| 44 | GND               |             | Ground       |

| 45 | 3.3V_LCD_VDD      |             | Power 3.3V   |

| 46 | 3.3V_LCD_VDD      |             | 1 Ower 3.3 V |

| 47 | 5V_LCD_VDD        |             | Power 5V     |

| 48 | 5V_LCD_VDD        |             |              |

| 49 | RESET_HPS_GLOBELn | S1          | Reset        |

| 50 | LCD_PWM           | 5CSXFC6D    | Control      |

| 51 | GND               |             | Ground       |

| 52 | GND               |             | Ground       |

### • VGA

The VGA interface (CN1) is realized by using a standard D-SUB 15-pin connector. The following table contains pin definitions of CN1.

|     | VGA Display: CN1 |         |             |  |  |

|-----|------------------|---------|-------------|--|--|

| Pin | Signal Name      | Device  | Signal Type |  |  |

| 1   | VGA_REG          |         |             |  |  |

| 2   | VGA_GRN          | CH7033B | Data        |  |  |

| 3   | VGA_BLU          |         |             |  |  |

| 4   | NC               |         | Other       |  |  |

| 5   | GND              |         | Cround      |  |  |

| 6   | GND              |         | Ground      |  |  |

#### Table 2-6 VGA interface

|    | VGA Display: CN1 |  |          |  |  |

|----|------------------|--|----------|--|--|

| 7  | GND              |  |          |  |  |

| 8  | GND              |  |          |  |  |

| 9  | VGA_VDD          |  | Power 5V |  |  |

| 10 | GND              |  | Ground   |  |  |

| 11 | NC               |  | Other    |  |  |

| 12 | I2C_SDA_VGA      |  | 12C      |  |  |

| 13 | I2C_SCL_VGA      |  | 120      |  |  |

| 14 | 5V_HSYNC         |  | SYNC     |  |  |

| 15 | 5V_VSYNC         |  | 51110    |  |  |

### • HDMI

The HDMI interface on Lark Board is named as J5, which is a standard 19-pin HDMI connector. The following table contains pin definitions of the interface (including the fixed pins of the connector).

#### Table 2-7 HDMI interface

|     | HDMI Display: J5 |           |                                      |  |  |

|-----|------------------|-----------|--------------------------------------|--|--|

| Pin | Signal Name      | Device    | Signal Type                          |  |  |

| 1   | HDMI_TX2+        | СН7033В   |                                      |  |  |

| 2   | GND              | CH7033B   |                                      |  |  |

| 3   | HDMI_TX2-        | CH7033B   |                                      |  |  |

| 4   | HDMI_TX1+        | CH7033B   |                                      |  |  |

| 5   | GND              | CH7033B   | Differential                         |  |  |

| 6   | HDMI_TX1-        | CH7033B   | Differential<br>Data & Clock, GND as |  |  |

| 7   | HDMI_TX0+        | CH7033B   | reference for signal                 |  |  |

| 8   | GND              | CH7033B   |                                      |  |  |

| 9   | HDMI_TX0-        | CH7033B   |                                      |  |  |

| 10  | HDMI_CLK+        | CH7033B   |                                      |  |  |

| 11  | GND              | CH7033B   |                                      |  |  |

| 12  | HDMI_CLK-        | CH7033B   |                                      |  |  |

| 13  | NC               |           | Other                                |  |  |

| 14  | NC               |           | Other                                |  |  |

| 15  | HDMICONN_I2CSCL  | TXS0102DC | 12C                                  |  |  |

| 16  | HDMICONN_I2CSDA  | TXS0102DC | 120                                  |  |  |

| 17  | GND              |           | Ground                               |  |  |

| 18  | 5V_VDD           |           | Power 5V                             |  |  |

| 19  | HDMICONN_HPLG    | 5CSXFC6D  | Status                               |  |  |

| 20  | GND_SHELDS       |           |                                      |  |  |

| 21  | GND_SHELDS       |           | Ground                               |  |  |

| 22  | GND_SHELDS       |           |                                      |  |  |

| HDMI Display: J5 |            |  |  |  |

|------------------|------------|--|--|--|

| 23               | GND_SHELDS |  |  |  |

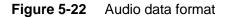

# 2.4.2 SDI

The SDI interface on Lark Board is used to implement high-resolution video input and output, which means that it could be connected to a HD camera or display. There are two SMB connectors on the board for connections to SDI devices through co-axial cables. J10 is an output interface which is the destination of the signal that travels from SoC's serial transmitter to LMH0303 driver. J11 is an input interface that receives high-resolution serial signal from external devices and passes it to LMH0384 equalizer which provides input to SoC's serial receiver.

The connections between SoC and LMH0303/LH0384 are shown in the following table;

|     | SDI Input & Output: |           |               |             |  |

|-----|---------------------|-----------|---------------|-------------|--|

| Pin | Bank                | Direction | Signal Name   | Signal Type |  |

| T4  | GXB_L1              | Out       | SDI_TX_P      |             |  |

| L4  | GXB_L1              | Out       | SDI_TX_N      |             |  |

| C13 | 8A                  | Out       | SDI_TX_SH_HDn |             |  |

| E13 | 8A                  | Out       | SDI_RSTIn     | SDI Out     |  |

| F13 | 8A                  | In        | SDI_FAULTn    | SDI Out     |  |

| F14 | 8A                  | Out       | SDI_TX_EN     |             |  |

| F15 | 8A                  | IO        | SDI_I2C_SDA   |             |  |

| B12 | 8A                  | Out       | SDI_I2C_SCL   |             |  |

| U2  | GXB_L1              | In        | SDI_RX_P      |             |  |

| U1  | GXB_L1              | In        | SDI_RX_N      | SDI In      |  |

| E12 | 8A                  | Out       | SDI_RX_BYPASS |             |  |

| D12 | 8A                  | Out       | SDI_RX_EN     |             |  |

Table 2-8 SDI input/output

# 2.4.3 PCIe

5CSXFC6D6F SoC integrates 2 PCIe hard IPs and 9 pairs of 3Gbps serial transceiver. Lark Board has a PCIe X1/X4 (J1) connector on board to make part of the SoC's IPs available for various PCIe X1/X4-compliant expansion boards. The following table contains pin definitions of the PCIe connector;

#### Table 2-9 PCIe connector

|     | PCIe              | Connector: J1 |                          |

|-----|-------------------|---------------|--------------------------|

| Pin | Signal Name       |               | Signal Type              |

| A1  | 12V_EXP           |               |                          |

| A2  | 12V_EXP           |               |                          |

| A3  | 12V_EXP           |               | Power 12V                |

| A4  | GND               |               |                          |

| A5  | NC                |               |                          |

| A6  | NC                |               | Other                    |

| A7  | NC                |               | - Other                  |

| A8  | NC                |               |                          |

| A9  | 3.3V_EXP          |               | Power 2.2                |

| A10 | 3.3V_EXP          |               | Power 3.3V               |

| A11 | PCIE_RSTn         | 5CSX6D6F      | Reset                    |

| A12 | GND               |               |                          |

| A13 | PCIE_REFCLK_SYN_P | 100M_OSC      | Differential clock and   |

| A14 | PCIE_REFCLK_SYN_N | 100M_OSC      | reference ground         |

| A15 | GND               |               |                          |

| A16 | PCIE_RX_P0        | 5CSX6D6F      |                          |

| A17 | PCIE_RX_N0        | 5CSX6D6F      |                          |

| A18 | GND               |               |                          |

| A19 | NC                |               |                          |

| A20 | GND               |               |                          |

| A21 | PCIE_RX_P1        | 5CSX6D6F      |                          |

| A22 | PCIE_RX_N1        | 5CSX6D6F      |                          |

| A23 | GND               |               | RX differential data and |

| A24 | GND               |               | reference ground         |

| A25 | PCIE_RX_P2        | 5CSX6D6F      |                          |

| A26 | PCIE_RX_N2        | 5CSX6D6F      |                          |

| A27 | GND               |               |                          |

| A28 | GND               |               |                          |

| A29 | PCIE_RX_P3        | 5CSX6D6F      |                          |

| A30 | PCIE_RX_N3        | 5CSX6D6F      |                          |

| A31 | GND               |               |                          |

| A32 | NC                |               |                          |

| B1  | 12V_EXP           |               |                          |

| B2  | 12V_EXP           |               | – Power 12V              |

| B3  | 12V_EXP           |               |                          |

| B4  | GND               |               |                          |

| B5  | PCIE_SMBCLK       | 5CSX6D6F      | Control                  |

|     | PCIe Connector: J1 |          |                          |  |  |

|-----|--------------------|----------|--------------------------|--|--|

| B6  | PCIE_SMBDAT        | 5CSX6D6F |                          |  |  |

| B7  | GND                |          | Ground                   |  |  |

| B8  | 3.3V_EXP           |          | Power 3.3V               |  |  |

| B9  | 3.3V_EXP (Pull-up) |          | Status                   |  |  |

| B10 | 3.3V_EXP           |          | Power 3.3V               |  |  |

| B11 | PCIE_WAKEn         | 5CSX6D6F | Control                  |  |  |

| B12 | NC                 |          | Other                    |  |  |

| B13 | GND                |          |                          |  |  |

| B14 | PCIE_TX_P0         | 5CSX6D6F | TX Differential data and |  |  |

| B15 | PCIE_TX_P1         | 5CSX6D6F | reference ground         |  |  |

| B16 | GND                |          |                          |  |  |

| B17 | PCIE_PRSNT2_X1     | 5CSX6D6F | Status                   |  |  |

| B18 | GND                |          |                          |  |  |

| B19 | PCIE_TX_P0         | 5CSX6D6F |                          |  |  |

| B20 | PCIE_TX_P1         | 5CSX6D6F |                          |  |  |

| B21 | GND                |          |                          |  |  |

| B22 | GND                |          |                          |  |  |

| B23 | PCIE_TX_P0         | 5CSX6D6F | TX Differential data and |  |  |

| B24 | PCIE_TX_P1         | 5CSX6D6F | reference ground         |  |  |

| B25 | GND                |          |                          |  |  |

| B26 | GND                |          |                          |  |  |

| B27 | PCIE_TX_P0         | 5CSX6D6F |                          |  |  |

| B28 | PCIE_TX_P1         | 5CSX6D6F |                          |  |  |

| B29 | GND                |          |                          |  |  |

| B30 | NC                 |          | Other                    |  |  |

| B31 | PCIE_PRSNT2_X4     | 5CSX6D6F | Status                   |  |  |

| B32 | GND                |          | Ground                   |  |  |

# 2.4.4 Camera

The 30-pin FPC connector (J12) on Lark Board is used to support 12-bit input of digital cameras. It is currently compatible with Embest's CAM8000-D camera module.

The following table contains pin definitions of the FPC connector;

|     | Camera(J12) |          |             |  |

|-----|-------------|----------|-------------|--|

| Pin | Signal Name | Device   | Signal Type |  |

| 1   | GND         |          | Ground      |  |

| 2   | CAM_D0      | 5CSXFC6D | Data        |  |

|    | Came           | ra(J12)      |            |

|----|----------------|--------------|------------|

| 3  | CAM_D1         |              |            |

| 4  | CAM_D2         |              |            |

| 5  | CAM_D3         |              |            |

| 6  | CAM_D4         |              |            |

| 7  | CAM_D5         |              |            |

| 8  | CAM_D6         |              |            |

| 9  | CAM_D7         |              |            |

| 10 | CAM_D8         |              |            |

| 11 | CAM_D9         |              |            |

| 12 | CAM_D10        |              |            |

| 13 | CAM_D11        |              |            |

| 14 | GND            |              | Ground     |

| 15 | PCLK           | 5CSXFC6D     | Clock      |

| 16 | GND            |              | Ground     |

| 17 | CAM_HS         | 5CSXFC6D     | SYNC       |

| 18 | GND            |              | Ground     |

| 19 | CAM_VS         | 5CSXFC6D     | SYNC       |

| 20 | 3.3V_CAMERA    |              | Power 3.3V |

| 21 | CAM_CLK        | 5CSXFC6D     | Clock      |

| 22 | CAM_CLK1       | 3C3AFC0D     | CIUCK      |

| 23 | GND            |              | Ground     |

| 24 | CAM_FLD        | 5CSXFC6D     |            |

| 25 | CAM_WEN        | 5CSXFC6D     | Status     |

| 26 | CAM_STROBE     | 5CSXFC6D     |            |

| 27 | CAM_SDA        |              |            |

| 28 | CAM_SCL        | TXS0102D I2C |            |

| 29 | GND            |              | Ground     |

| 30 | 3.3V_CAMERA_IO |              | Power 3.3V |

| 31 | GND            |              | Power      |

| 32 | GND            |              |            |

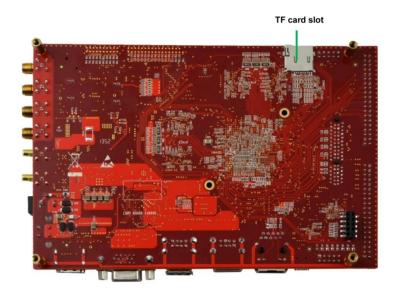

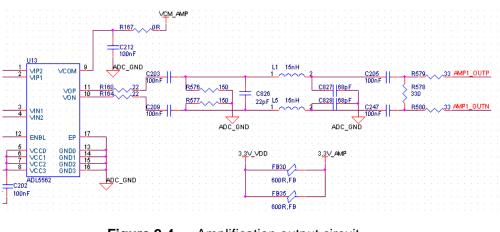

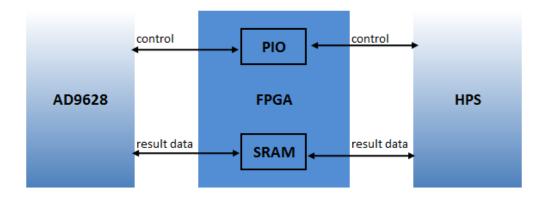

# 2.4.5 ADC & Pre-Amp

Since a long time ago, FPGA is always involved in data acquisition, especially in the high-speed applications, the data acquisition systems built up with FPGA and ADC can be often found. Lark Board has a data acquisition system prototype which is made up of high-bandwidth amplifier, anti-alias filter, high-speed ADC, FPGA and ARM to support dual-channel single-ended analog signal based on SMA input or differential analog signal.

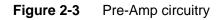

# • Pre-Amp

The pre-amp circuitry is used to receive and amplify analog input. Lark Board provides two analog input channels that support single-ended SMA input or differential input.

As shown in the figure above, pre-amp circuitry is made up of a Balun (T46) and a balanced filtering circuit. The jumpers JP1 and JP3 are used to select working mode of Balun. When JP1 and JP3 are both opened, J6 and J7 constitute a differential channel A, J8 and J9 constitute channel B; When JP1 and JP3 are both shorted, J6 input is a single-ended channel A and J8 is a single-ended channel B. The resistors R159, R158, R166, and R168 are used to set the gains of amplifier ADL5562 to 6dB, 12dB or 15.5dB. (For more details, please refer to ADL5562 datasheet)

As shown in the figure above, an optimized third-order butterworth anti-alias filter is placed between amplifier output end and ADC.

### ADC

The ADC AD962 can provide a capability of 12-bit, 105MSPS sampling performance and support quantified data output of CMOS or LVDS.

The following table contains pin definitions and signal connections between ADC and FPGA;

|      | Interface between ADC & FPGA |           |              |              |

|------|------------------------------|-----------|--------------|--------------|

| Pin  | Bank                         | Direction | Signal Name  | Signal Type  |

| AE29 | 5B                           | Out       | ADC_CLK105_P | Clock        |

| AD29 | 5B                           | Out       | ADC_CLK105_N | CIUCK        |

| W25  | 5B                           | In        | ADC_Dp0      |              |

| V25  | 5B                           | In        | ADC_Dn0      |              |

| Y26  | 5B                           | In        | ADC_Dp1      |              |

| Y27  | 5B                           | In        | ADC_Dn1      |              |

| V23  | 5A                           | In        | ADC_Dp2      |              |

| W24  | 5A                           | In        | ADC_Dn2      |              |

| AA26 | 5B                           | In        | ADC_Dp3      |              |

| AB27 | 5B                           | In        | ADC_Dn3      |              |

| AA24 | 5A                           | In        | ADC_Dp4      |              |

| AB25 | 5A                           | In        | ADC_Dn4      |              |

| W21  | 5A                           | In        | ADC_Dp5      |              |

| W22  | 5A                           | In        | ADC_Dn5      | Differential |

| AD26 | 5A                           | In        | ADC_Dp6      | Data         |

| AC27 | 5A                           | In        | ADC_Dn6      |              |

| AA13 | 3B                           | In        | ADC_Dp7      |              |

| AB13 | 3B                           | In        | ADC_Dn7      |              |

| Y23  | 5A                           | In        | ADC_Dp8      |              |

| Y24  | 5A                           | In        | ADC_Dn8      |              |

| AD25 | 5A                           | In        | ADC_Dp9      |              |

| AC25 | 5A                           | In        | ADC_Dn9      |              |

| AF11 | 3B                           | In        | ADC_Dp10     |              |

| AG11 | 3B                           | In        | ADC_Dn10     |              |

| AB22 | 5A                           | In        | ADC_Dp11     |              |

| AB23 | 5A                           | In        | ADC_Dn11     |              |

| W20  | 5A                           | Out       | ADC_ORp      | Differential |

| Y21  | 5A                           | Out       | ADC_ORn      | Status       |

#### Table 2-11 Interface between ADC and FPGA

|      | Interface between ADC & FPGA |     |                  |              |  |

|------|------------------------------|-----|------------------|--------------|--|

| AB30 | 5B                           | In  | ADC_DCOp         |              |  |

| AA30 | 5B                           | In  | ADC_DCOn         |              |  |

| AE13 | 3B                           | In  | ADC_D0B          |              |  |

| AK4  | 3B                           | In  | ADC_D1B          | Single-Ended |  |

| AJ4  | 3B                           | In  | ADC_D2B          | Data         |  |

| AK3  | 3B                           | In  | ADC_D3B          |              |  |

| AF30 | 5A                           | Out | FPGA_ADC_OEB     |              |  |

| AD24 | 4A                           | Out | FPGA_ADC_SPICSn  | SPI          |  |

| AE24 | 4A                           | Out | FPGA_ADC_SPICLK  | 551          |  |

| AC23 | 4A                           | Out | FPGA_ADC_SPIMOSI |              |  |

# 2.4.6 Gigabit Ethernet

Lark Board can provide a relatively high network performance of gigabit Ethernet. The Ethernet is implemented by utilizing part of the EMAC controller integrated in HPS. The AR8035 is added to realize connections between PHY and EMAC. The RJ-45 interface is named as J14 to provide connection to network devices.

### RGMII

RGMII is the interfacing protocol applied on the connection between EMAC and AR8035 (PHY). It uses a 4-bit data port and operates at 125MHz. It supports data transmission at both rising edge and fall edge, providing a transmission rate up to 1000Mbps. The following table contains pin definitions of RGMII interface on Lark Board.

|     | Interface between HPS MAC & PHY |           |             |             |

|-----|---------------------------------|-----------|-------------|-------------|

| Pin | Bank                            | Direction | Signal Name | Signal Type |

| H19 | 7B                              | Out       | MII1_TX_CLK |             |

| A20 | 7B                              | Out       | MII1_TX_EN  |             |

| F20 | 7B                              | Out       | MII1_TXD0   | тх          |

| J19 | 7B                              | Out       | MII1_TXD1   |             |

| F21 | 7B                              | Out       | MII1_TXD2   |             |

| F19 | 7B                              | Out       | MII1_TXD3   |             |

| G20 | 7B                              | In        | MII1_RX_CLK |             |

| K17 | 7B                              | In        | MII1_RX_DV  | Rx          |

| A21 | 7B                              | In        | MII1_RXD0   |             |

Table 2-12

Interface between HPS MAC and PHY

| Interface between HPS MAC & PHY |    |     |           |        |

|---------------------------------|----|-----|-----------|--------|

| B20                             | 7B | In  | MII1_RXD1 |        |

| B18                             | 7B | In  | MII1_RXD2 |        |

| D21                             | 7B | In  | MII1_RXD3 |        |

| B21                             | 7B | Out | MII_MDC   |        |

| E21                             | 7B | 10  | MII_MDIO  | Manage |

| C19                             | 7B | In  | MII_INT   |        |

### • RJ-45

The following table contains pin definitions of RJ-45 (J14) Ethernet interface;

|     | RJ45 Ethernet: J14 |             |             |  |

|-----|--------------------|-------------|-------------|--|

| Pin | Signal Name        | Device      | Signal Type |  |

| 1   | MIIA_TRP0          |             |             |  |

| 2   | MIIA_TRN0          | AR8035      | Data        |  |

| 3   | MIIA_TRP1          | AR0035      | Dala        |  |

| 4   | MiIA_TRN1          |             |             |  |

| 5   | NC                 |             | Shield      |  |

| 6   | NC                 |             | Shield      |  |

| 7   | MIIA_TRP2          |             |             |  |

| 8   | MIIA_TRN2          | AR8035      | Data        |  |

| 9   | MIIA_TRP3          | AI\0000     |             |  |

| 10  | MIIA_TRN3          |             |             |  |

| 11  | MIIA_LED_LINK      |             |             |  |

| 12  | Pull-down          | LED Control | LED         |  |

| 13  | MIIA_LED_ACT       |             |             |  |

| 14  | Pull-up            |             |             |  |

| 15  | GND                |             | GND         |  |

| 16  | GND                |             | GND         |  |

| 17  | NC                 |             | Fix         |  |

| 18  | NC                 |             |             |  |

Table 2-13Ethernet interface

# 2.4.7 eMMC& TF Card

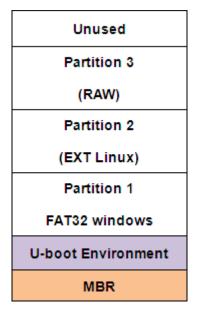

eMMC and TF card are used to provide solid storage of boot code and system. Although there is only one MMC/SD controller in HPS, TF card and eMMC could work alternatively by the help of eMMC/TF card power switch design on Lark Board.

### • eMMC Interface

eMMC and TF card share the MMC/SD controller of HPS, so they work on the same clock, lower 4-bit data and control signal, but the higher 4-bit data is reserved for eMMC. The following table contains pin definitions of eMMC interface

|     | eMMC between HPS & Device |        |             |             |  |

|-----|---------------------------|--------|-------------|-------------|--|

| Pin | Bank                      | Device | Signal Name | Signal Type |  |

| G18 | 7C                        | Ю      | MMC_DAT0    |             |  |

| C17 | 7C                        | Ю      | MMC_DAT1    |             |  |

| D17 | 7C                        | Ю      | MMC_DAT2    |             |  |

| B16 | 7C                        | Ю      | MMC_DAT3    | Data        |  |

| H17 | 7C                        | Ю      | MMC_DAT4    | Dala        |  |

| C18 | 7C                        | Ю      | MMC_DAT5    |             |  |

| G17 | 7C                        | IO     | MMC_DAT6    |             |  |

| E18 | 7C                        | Ю      | MMC_DAT7    |             |  |

| A16 | 7C                        | Out    | MMC_CLK     | Clock       |  |

| F18 | 7C                        | Out    | MMC_CMD     | Control     |  |

| B17 | 7C                        | Out    | MMC_CD      | Control     |  |

Table 2-14

eMMC interface

# • TF Card Interface

The TF1 interface on the back of Lark Board is a TF card slot. The following table contains pin definitions of the interface;

Table 2-15TF card interface

|     | TF card connector: TF1 |          |             |  |

|-----|------------------------|----------|-------------|--|

| Pin | Signal Name            | Device   | Signal Type |  |

| 1   | MMC_DAT2               | 5CSX6F6D | Data        |  |

| 2   | MMC_DAT3               | 5CSX6F6D | Dala        |  |

| 3   | MMC_CMD                | 5CSX6F6D | Command     |  |

| 4   | 3.3V_VDD               |          | Power 3.3V  |  |

| 5   | MMC_CLK                | 5CSX6F6D | Clock       |  |

| 6   | GND                    |          | Ground      |  |

| 7   | MMC_DAT0               | 5CSX6F6D | Data        |  |

| 8   | MMC_DAT1               | 5CSX6F6D | Data        |  |

| 9   | MMC_CD                 | 5CSX6F6D | Command     |  |

| 10  | GND                    |          | Cround      |  |

| 11  | GND                    |          | Ground      |  |

|    | TF card connector: TF1 |     |  |       |

|----|------------------------|-----|--|-------|

| 12 | 2                      | GND |  |       |

| 13 | 3                      | GND |  |       |

| 14 | 4                      | NC  |  | Fixed |

| 15 | 5                      | NC  |  | Fixeu |

# 2.4.8 USB PHY & HUB

To satisfy diverse applications involving USB interfaces, Lark Board provides 4 USB ports. However, there are only 2 USB controllers in HPS, thus a PHY and a HUB are added to ensure 4 USB port can work at the same time. The USB3320 on Lark Board is used to implement ULPI protocol between PHY and controller. The USB2514 is used to expand the ports of PHY. The following contents will introduce the implementation of USB in detail.

### • USB PHY

USB3320 is an on-board USB PHY chip which exchange data with the controller of HPS by using ULPI protocol. The following table contains pin definitions of ULPI interface;

|     | ULPI between USB Controller and PHY |           |             |             |  |

|-----|-------------------------------------|-----------|-------------|-------------|--|

| Pin | Bank                                | Direction | Signal Name | Signal Type |  |

| E16 | 7D                                  | IO        | USB1HS_D0   |             |  |

| G16 | 7D                                  | IO        | USB1HS_D1   |             |  |

| D16 | 7D                                  | IO        | USB1HS_D2   |             |  |

| D14 | 7D                                  | IO        | USB1HS_D3   | Data        |  |

| A15 | 7D                                  | IO        | USB1HS_D4   | Dala        |  |

| C14 | 7D                                  | IO        | USB1HS_D5   |             |  |

| D15 | 7D                                  | IO        | USB1HS_D6   |             |  |

| M17 | 7D                                  | IO        | USB1HS_D7   |             |  |

| N16 | 7D                                  | IO        | USB1HS_CLK  | Clock       |  |

| A14 | 7D                                  | In        | USB1HS_NXT  |             |  |

| E14 | 7D                                  | In        | USB1HS_DIR  | Control     |  |

| C15 | 7D                                  | Out       | USB1HS_STP  |             |  |

| Table 2-16 | ULPI interface |

|------------|----------------|

|            |                |

• USB HUB

The USB2514 is a HUB chip used to expand more USB ports. It expands a differential pair up to 4 pairs to accomplish connections to external USB devices. CON1/CON2 are two USB connectors, each of which provides two USB ports. The following table contains pin definitions of USB interface.

| USB Connector: CON1/CON2 |             |         |             |  |  |

|--------------------------|-------------|---------|-------------|--|--|

| Pin                      | Signal Name | Device  | Signal Type |  |  |

| 1                        | VBUS1_CN    |         |             |  |  |

| 2                        | DN1         | USB2514 | USB1        |  |  |

| 3                        | DP1         | USB2514 |             |  |  |

| 4                        | GND         |         |             |  |  |

| 5                        | VBUS2_CN    |         |             |  |  |

| 6                        | DN2         | USB2514 | USB2        |  |  |

| 7                        | DP2         | USB2514 |             |  |  |

| 8                        | GND         |         |             |  |  |

| 9                        | GND_SHIELDS |         |             |  |  |

| 10                       | GND_SHIELDS |         |             |  |  |

| 11                       | GND_SHIELDS |         | FIX         |  |  |

| 12                       | GND_SHIELDS |         |             |  |  |

| Table 2-17 US |

|---------------|

|---------------|

# 2.4.9 USB Blaster & JTAG

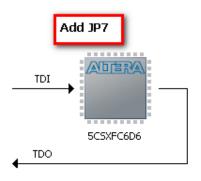

JTAG is used to download firmware and obtain debugging information during FPGA development. It is very important in product development stage. The debugging function mainly depends on the four signals: TCK, TMS, TDI and TDO. The standard debugging interface for Altera FPGA is a 5Px2 connector used to connect debuggers such as USB Blaster. There is an on-board USB Blaster II debugger on Lark Board, enabling the powerful debugging function of USB Blaster II by using just a mini-USB cable, without the need to purchase a separate debugger. Moreover, a separate USB Blaster could be supported by Lark Board by using an additional 5Px2 connector.

# • On-Board USB Blaster II

The on-board USB Blaster II is implemented with MAX II chip (EPM570GF100) and a controller (CY7C68013A). The IP authorized by Altera needs to be programmed into MAX II. Embest has obtained that authorization on Lark Board.

The CON3 on the board is used to connect to a computer installed with Quartus through a mini-USB cable. There is a jumper JP7 near CON3 for selecting components involved in JTAG chain. The following figures show the detection results of SoC chip when JP7 is shorted and opened.

Figure 2-5 JP7 shorted

Figure 2-6 JP7 opened

# • JTAG

J3 is used to connect the JTAG interface of an external USB Blaster debugger (please note that the position and direction of pin 1 when connector an external USB Blaster; wrong connection might damage the JTAG interface of SoC). The following table contains pin definitions of JTAG interface.

| Table 2-18 | JTAG interface |

|------------|----------------|

|            |                |

|     | JTAG Connector: J3 |          |             |  |  |

|-----|--------------------|----------|-------------|--|--|

| Pin | Signal Name        | Device   | Signal Type |  |  |

| 1   | JTAG_TCK           | 5CSX6D6F | JTAG        |  |  |

| 2   | USB_DISABLEn       |          | Control     |  |  |

| 3   | JTAG_TDI           | 5CSX6D6F | JTAG        |  |  |

| JTAG Connector: J3 |               |          |         |  |  |

|--------------------|---------------|----------|---------|--|--|

| 4                  | 3.3V_VDD      |          | Power   |  |  |

| 5                  | JTAG_TMS      | 5CSX6D6F | JTAG    |  |  |

| 6                  | HPS_WARM_RSTn | JP5      | Control |  |  |

| 7                  | NC            |          |         |  |  |

| 8                  | NC            |          |         |  |  |

| 9                  | FPGA_TDI      | 5CSX6D6F | JTAG    |  |  |

| 10                 | GND           |          | Ground  |  |  |

# 2.4.10 DIP Switch

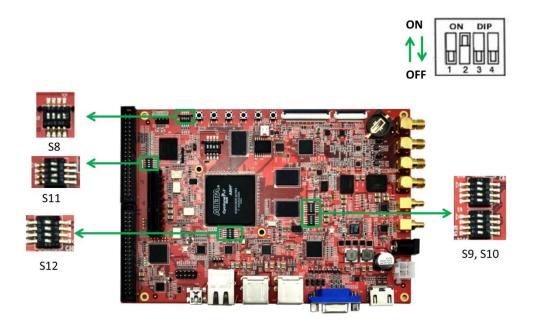

There are 5 DIP switches on Lark Board for power supply control, HPS boot selection, FPGA configuration mode selection and SDI rate selection. The following contents will introduce the function, connections and signal definitions of each DIP switch(the DIP Switches location as show below).

Figure 2-7 DIP Switches Location

S8 is connected to the general I/O of FPGA Bank 8A and cam be used as a typical status input switch.

Table 2-1 DIP switch 1

| Switch Pin Signal Name Function |  |

|---------------------------------|--|

| S8: User FPGA Dip Switch |                  |                               |  |  |

|--------------------------|------------------|-------------------------------|--|--|

| 1                        | USER_FPGA_DIPSW0 | C8, function defined by user  |  |  |

| 2                        | USER_FPGA_DIPSW1 | B8, function defined by user  |  |  |

| 3                        | USER_FPGA_DIPSW2 | C10, function defined by user |  |  |

| 4                        | USER_FPGA_DIPSW3 | C9, function defined by user  |  |  |

S9 and S10 are used to enable and disable various voltages on the board. When a voltage is disabled or unavailable, a LED in the corresponding power supply area will be turned on, indicating the voltage has been disabled or unavailable.

| Table | 2-2 DIP | switch 2 |

|-------|---------|----------|

|-------|---------|----------|

| Switch Pin      | Signal Name                           | Function                             |  |  |  |

|-----------------|---------------------------------------|--------------------------------------|--|--|--|

| S9: Power on/o  | S9: Power on/off for 5V/12V/3.3V/2.5V |                                      |  |  |  |

| 1               | 5V_SHDNn                              | On: disable 5V; Off: enable 5V       |  |  |  |

| 2               | 12V_SHDNn                             | On: disable 12V; Off: enable 12V     |  |  |  |

| 3               | 3.3V_POWER_EN                         | On: disable 3.3V; Off: enable 3.3V   |  |  |  |

| 4 2.5V_POWER_EN |                                       | On: disable 2.5V; Off: enable 2.5V   |  |  |  |

| S10: Power on   | /off for 1.8V/1.1V/1.5V/VTT           |                                      |  |  |  |

| 1               | 1.8V_POWER_EN                         | On: disable 1.8V; Off: enable 1.8V   |  |  |  |

| 2               | 1.1V_POWER_EN                         | On: disable 1.1V; Off: enable 1.1V   |  |  |  |

| 3               | 1.5V_POWER_EN                         | On: disable 1.5V; Off: enable 1.5V   |  |  |  |

| 4               | VTT_POWER_EN                          | On: disable 0.75V; Off: enable 0.75V |  |  |  |

S11 is used to select clock and booting of HPS; the default configurations on Lark Board are CLKSEL1/0=00 and BOOTSEL2/1/0=101.

#### Table 2-3 DIP switch 3

| Switch Pin     | Signal Name               | Function                      |  |

|----------------|---------------------------|-------------------------------|--|

| S11: Boot Devi | ice Select & Clock Select |                               |  |

|                | HPS_UART0_RX              | Default: CLKSEL0=0            |  |

| 1 HPS_GPIO62   |                           | Off:CLKSEL1=1; On:CLKSEL1=0   |  |

| 2              | HPS_SPIM0_CS0n            | Off:BOOTSEL0=1; On:BOOTSEL0=0 |  |

| 3              | QSPI_SS0                  | Off:BOOTSEL1=1; On:BOOTSEL1=0 |  |

| 4 HPS_GPIO28   |                           | Off:BOOTSEL2=1; On:BOOTSEL2=0 |  |

The figure shown below is the configurations of CSEL and BSEL provided in Cyclone V datasheet.

| Setting                         | CSEL Pin                  |                                |                                |                               |

|---------------------------------|---------------------------|--------------------------------|--------------------------------|-------------------------------|

| setung                          | 0                         | 1                              | 2                              | 3                             |

| oscl_clk (EOSC1 pin) range      | 10–50 MHz                 | 10-12.5 MHz                    | 12.5–25 MHz                    | 25–50 MHz                     |

| nand_x_clk /25 device frequency | osc1_clk/25,<br>2 MHz max | osc1_clk*20/25,<br>9.6 MHz max | osc1_clk*10/25,<br>9.6 MHz max | osc1_c1k*5/25,<br>9.6 MHz max |

| nand_x_clk controller clock     | osc1_clk,<br>50 MHz max   | osc1_clk*20,<br>240 MHz max    | osc1_clk*10,<br>240 MHz max    | osc1_clk*5,<br>240 MHz max    |

| mpu_clk                         | osc1_clk,<br>50 MHz max   | osc1_clk*32,<br>400 MHz max    | osc1_clk*16,<br>400 MHz max    | osc1_clk*8,<br>400 MHz max    |

| PLL modes                       | Bypassed                  | Locked                         | Locked                         | Locked                        |

### Figure 2-8 CSEL pin

| bsel Field Value | Flash Device                                        |  |  |

|------------------|-----------------------------------------------------|--|--|

| 0x0 Reserved     |                                                     |  |  |

| 0x1              | FPGA (HPS-to-FPGA bridge)                           |  |  |

| 0x2              | 1.8 V NAND flash memory                             |  |  |

| 0x3              | 3.0 V NAND flash memory                             |  |  |

| 0x4              | 1.8 V SD/MMC flash memory with external transceiver |  |  |

| 0x5              | 3.0 V SD/MMC flash memory with internal transceiver |  |  |

| 0x6              | 1.8 V SPI or quad SPI flash memory                  |  |  |

| 0x7              | 3.0 V SPI or quad SPI flash memory                  |  |  |

### Figure 2-9 BSEL

S12 is used to select FPGA configuration mode. The default FPGA configuration mode on Lark Board is MSEL[4:0]=00000.

#### Table 2-4 DIP switch 4

| Switch Pin   | Signal Name                     | Function                  |  |

|--------------|---------------------------------|---------------------------|--|

| S12: FPGA Co | nfiguration Scheme              |                           |  |

| 1            | MSEL0                           | On: MSEL0=0; Off: MSEL0=1 |  |

| 2            | MSEL1                           | On: MSEL1=0; Off: MSEL0=1 |  |

| 3            | MSEL2 On: MSEL2=0; Off: MSEL0=1 |                           |  |

| 4            | MSEL3                           | On: MSEL3=0; Off: MSEL0=1 |  |

|              | MSEL4                           | Default: MSEL4=0          |  |

The figure shown below can be found in Cyclone V datasheet. It lists all the configuration modes supported by FPGA.

| Configuration Scheme     | Compression<br>Feature                 | Design Security<br>Feature | V <sub>CCPGM</sub> (V) | Power-On Reset<br>(POR) Delay | Valid MSEL[40]                           |

|--------------------------|----------------------------------------|----------------------------|------------------------|-------------------------------|------------------------------------------|

|                          | Disabled                               | Disabled                   | 1.8/2.5/3.0/3.3        | Fast                          | 10100                                    |

|                          | Disabled                               |                            |                        | Standard                      | 11000                                    |

| FPP x8                   | Disabled                               | Enabled                    | 1.8/2.5/3.0/3.3        | Fast                          | 10101                                    |

| FFF X0                   | Disabled                               | Ellabled                   | 1.0/2.3/3.0/3.3        | Standard                      | 11001                                    |

|                          | Enabled                                | Enabled/                   | 1.8/2.5/3.0/3.3        | Fast                          | 10110                                    |

|                          | Lilableu                               | Disabled                   | 1.0/ 2.3/ 3.0/ 3.3     | Standard                      | 11010                                    |

|                          | Disabled Di                            | Disabled                   | 1.8/2.5/3.0/3.3        | Fast                          | 00000                                    |

|                          |                                        | Disabled                   |                        | Standard                      | 00100                                    |

| FPP x16                  | Disabled                               | Enabled                    | 1.8/2.5/3.0/3.3        | Fast                          | 00001                                    |

| FFF XIO                  |                                        |                            |                        | Standard                      | 00101                                    |

|                          | Enabled Enabled/<br>Disabled           |                            | 1.8/2.5/3.0/3.3        | Fast                          | 00010                                    |

|                          |                                        | Disabled                   |                        | Standard                      | 00110                                    |

| PS                       | Enabled/ Enabled/<br>Disabled Disabled | Enabled/                   | 18/25/30/33            | Fast                          | 10000                                    |

| 13                       |                                        | Disabled                   |                        | Standard                      | 10001                                    |

| AS (x1 and x4)           | Enabled/ Enabled/                      | Enabled/                   | 3.0/3.3                | Fast                          | 10010                                    |

| A3 (X1 aliu X4)          | Disabled                               | Disabled                   |                        | Standard                      | 10011                                    |