HCSL-Compatible Clock Generator for PCI Express

#### **General Description**

The PL60203X is the smallest, high performance, lowest power, 2 differential output clock IC available for HCSL timing applications. PL60203X offers -130dBc at 10kHz offset at 100MHz, with a very low jitter (2ps TIE RMS), making it ideal for HCSL applications requiring small size and low power.

Datasheets and support documentation are available on Micrel's web site at: <u>www.micrel.com</u>.

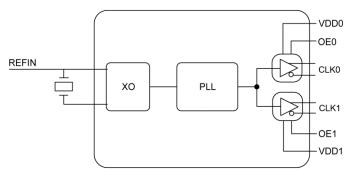

#### **Block Diagram**

#### **Features**

- Input frequency:

- Fundamental crystal or reference input: 25MHz.

- Output frequency:

- PL602031: 2 x 25MHz differential outputs.

- PL602032: 2 x 100MHz differential outputs.

- PL602033: 2 x 125MHz differential outputs.

PL602034: 2 x 200MHz differential outputs.

- Very low jitter: 28ps peak-to-peak typical.

- Very low phase noise:

- 130dBc at 10kHz offset at 100MHz.

- Compliant with PCI-Express Gen1, Gen2, and Gen3.

- Power supply range: 2.25V to 3.63V.

- Operating temperature range: -40°C to +85°C.

- Available in 16-pin QFN, RoHS and PFOS compliant package.

#### Applications

- Servers

- Storage systems

- Switches and routers

- Gigabit Ethernet

- Set-top boxes/DVRs

Ripple Blocker is a trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

## **Ordering Information**

| Part Number <sup>(1)</sup> | Marking | Shipping      | Junction Temperature<br>Range | Package              |

|----------------------------|---------|---------------|-------------------------------|----------------------|

| PL602031UMG                | 602031  | Tube          | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

| PL602031UMG TR             | 602031  | Tape and Reel | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

| PL602032UMG                | 602032  | Tube          | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

| PL602032UMG TR             | 602032  | Tape and Reel | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

| PL602033UMG                | 602033  | Tube          | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

| PL602033UMG TR             | 602033  | Tape and Reel | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

| PL602034UMG                | 602034  | Tube          | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

| PL602034UMG TR             | 602034  | Tape and Reel | –40° to +85°C                 | 16-Pin 3mm x 3mm QFN |

Note:

1. The devices are RoHS and PFOS compliant.

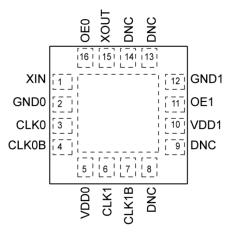

## **Pin Configuration**

16-Pin QFN (Top View)

## **Pin Description**

| Pin Number     | Pin Name  | Pin Type | Pin Function                                                                             |

|----------------|-----------|----------|------------------------------------------------------------------------------------------|

| 1              | XIN, FIN  | I        | Crystal input pin or reference clock input.                                              |

| 2              | GND0      | I        | GND connection for CLK0.                                                                 |

| 3, 4           | CLK0[0:1] | 0        | Differential clock output pair                                                           |

| 5              | VDD0      | Р        | VDD connection for CLK0                                                                  |

| 6, 7           | CLK1[0:1] | 0        | Differential clock output pair                                                           |

| 10             | VDD1      | Р        | VDD connection for CLK1                                                                  |

| 11             | OE1       | I        | Output enable pin for CLK1. High=Enabled, Low=Disabled. OE1 has a 60KΩ pull-up resistor. |

| 12             | GND1      | Р        | GND connection for CLK1                                                                  |

| 15             | XOUT      | 0        | Crystal output pin                                                                       |

| 16             | OE0       | I        | Output enable pin for CLK0. High=Enabled, Low=Disabled. OE0 has a 60KΩ pull-up resistor. |

| 8, 9<br>13, 14 | DNC       |          | Do not connect.                                                                          |

|                | ePad      |          | Center pad for thermal relief. Connect to GND.                                           |

## Absolute Maximum Ratings<sup>(2)</sup>

| Supply Voltage (V <sub>IN</sub> )     | +4.6V |

|---------------------------------------|-------|

| Lead Temperature (soldering, 10s)     |       |

| Storage Temperature (T <sub>s</sub> ) | 150°C |

| ESD Rating <sup>(3)</sup>             | 2.0kV |

# Operating Ratings<sup>(4)</sup>

| Supply Voltage (V <sub>IN</sub> )         | –0.5V to +4.6V |

|-------------------------------------------|----------------|

| Ambient Temperature (T <sub>A</sub> )     | –40°C to +85°C |

| Package Thermal Resistance <sup>(5)</sup> |                |

| QFN Still-air ( $\theta_{JA}$ )           | 60°C/W         |

| QFN Junction-to-board ( $\psi_{JB}$ ) .   | 33°C/W         |

# AC Electrical Characteristics<sup>(6)</sup>

| Parameter                                 | Condition                                                                                      | Min. | Тур. | Max.            | Units |

|-------------------------------------------|------------------------------------------------------------------------------------------------|------|------|-----------------|-------|

| Crystal input frequency                   | Fundamental crystal                                                                            |      | 25   |                 | MHz   |

| Input (FIN) frequency                     |                                                                                                |      | 25   |                 | MHz   |

| Input (F <sub>IN</sub> ) signal amplitude | Internally AC coupled                                                                          | 0.9  |      | V <sub>DD</sub> | Vpp   |

|                                           | PL602031                                                                                       |      | 25   |                 | MHz   |

| Output frequency                          | PL602032                                                                                       |      | 100  |                 | MHz   |

| Output frequency                          | PL602033                                                                                       |      | 125  |                 | MHz   |

|                                           | PL602034                                                                                       |      | 200  |                 | MHz   |

| Output enable time                        | OE function, $T_A=25$ °C, add one clock period to this measurement for a useable clock output. |      |      | 10              | ns    |

| Output disable time                       | OE function, $T_A=25^{\circ}C$                                                                 |      |      | 10              | ns    |

| Setting time                              | At power up ( $V_{DD} \ge 2.25V$ )                                                             |      |      | 10              | ms    |

| VDD sensitivity                           | Frequency vs. V <sub>DD</sub> ±10%, crystal input only.                                        | -2   |      | 2               | ppm   |

| Output rise time                          | 20/80%                                                                                         |      | 0.3  | 0.5             | ns    |

| Output fall time                          | 20/80%                                                                                         |      | 0.3  | 0.5             | ns    |

| Duty cycle                                | At V <sub>DD</sub> /2                                                                          | 45   | 50   | 55              | %     |

| Period jitter, peak-to-peak               | With capacitive decoupling between $V_{\text{DD}}$ and GND at 100MHz; 10,000 samples measured  |      | 28   |                 | ps    |

| Phase jitter, RMS                         | For 10kHz to 10MHz integration range                                                           |      | 2.1  |                 | ps    |

$V_{\text{DD}}$  = 3.3V ±10% or 2.5V ±10%,  $T_{\text{A}}$  = -40°C to +85°C, HCSL termination applied.

### DC Electrical Characteristics<sup>(6)</sup>

$V_{\text{DD}}$  = 3.3V ±10% or 2.5V ±10%,  $T_{\text{A}}$  = -40°C to +85°C, HCSL termination applied.

| Symbol          | Parameter               | Condition                                                    | Min. | Тур. | Max. | Units |

|-----------------|-------------------------|--------------------------------------------------------------|------|------|------|-------|

| I <sub>DD</sub> | Supply current, dynamic | At 100MHz, no load                                           |      | 50   | 70   | mA    |

| V <sub>DD</sub> | Operating voltage       |                                                              | 2.25 |      | 3.63 | V     |

| V <sub>OL</sub> | Output low voltage      | HCSL termination,                                            |      |      | 0.05 | V     |

| V <sub>OH</sub> | Output high voltage     | (RS = 150Ω, RT = 49.9Ω) 3.3V<br>(RS = 100Ω, RT = 49.9Ω) 2.5V | 0.65 | 0.75 | 0.85 | V     |

# Crystal Characteristics<sup>(6)</sup>

$V_{DD} = 3.3V \pm 10\%$  or 2.5V  $\pm 10\%$ ,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ .

| Symbol                | Parameter                                | Min. | Тур. | Max. | Units |

|-----------------------|------------------------------------------|------|------|------|-------|

| F <sub>XIN</sub>      | Fundamental crystal resonator            |      | 25   |      | MHz   |

| C <sub>L (XTAL)</sub> | Crystal load rating                      |      | 18   |      | pF    |

|                       | Maximum sustainable drive level          |      |      | 500  | μW    |

|                       | Operating drive level                    |      | 100  |      | μW    |

| C0                    | Crystal shunt capacitance                |      |      | 6    | pF    |

| ESR                   | Effective series resistance, fundamental |      |      | 45   | Ω     |

Notes:

- 2. Exceeding the absolute maximum ratings may damage the device.

- 3. Devices are ESD sensitive. Handling precautions are recommended. Human body model, 1.5k in series with 100pF.

- 4. The device is not guaranteed to function outside its operating ratings.

- Package thermal resistance assumes exposed pad is soldered (or equivalent) to the device's most negative potential on the PCB. θ<sub>JA</sub> and ψ<sub>JB</sub> values are determined for a 4-layer board in still-air number, unless otherwise stated.

- 6. Specification for packaged product only

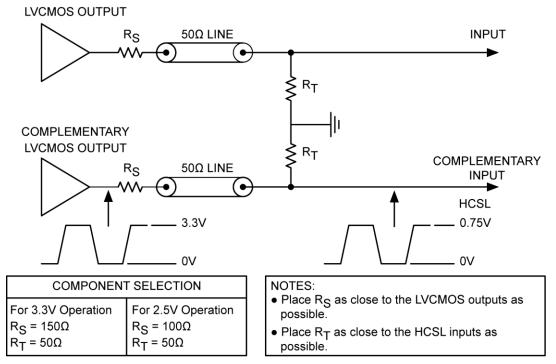

#### PCI Express/HCSL Compatible Layout Guidelines

Figure 1 below demonstrates how to terminate the complementary LVCMOS outputs of PL60203X for use with HCSL inputs.

Figure 1. Terminating the complementary LVCMOS outputs for use with HCSL inputs.

## PCB Layout Considerations for Performance Optimization

The following guidelines are designed to assist you with a performance-optimized PCB design:

- Keep all the PCB traces to PL60203X as short as possible. Also keep all other traces as far away from PL60203X as possible.

- Place the crystal as close as possible to both crystal pins of the device. This will reduce the cross-talk between the crystal and the other signals.

- Separate crystal pin traces from the other signals on the PCB, but allow ample distance between the two crystal pin traces.

- Place a 0.01µF decoupling capacitor between VDD and GND on the component side of the PCB, close to the VDD pin. It is not recommended to place this component on the backside of the PCB.

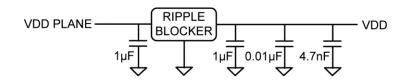

## **Power Supply Filtering Recommendations**

- It is highly recommended to keep the VDD and GND traces as short as possible.

- When connecting long traces (>1 inch) to a CMOS output, it is important to design the traces as a transmission line, or "stripline", to avoid reflections or ringing. In this case, the CMOS output needs to be matched to the trace impedance. Usually, "striplines" are designed for  $50\Omega$  impedance and CMOS outputs usually have an impedance of less than  $50\Omega$ , so matching can be achieved by adding a resistor in series with the CMOS output pin to the "stripline" trace.

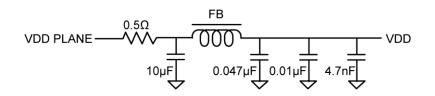

Preferred filter, using Micrel MIC94300 or MIC94310 Ripple Blocker™:

Alternative, traditional filter, using a ferrite bead:

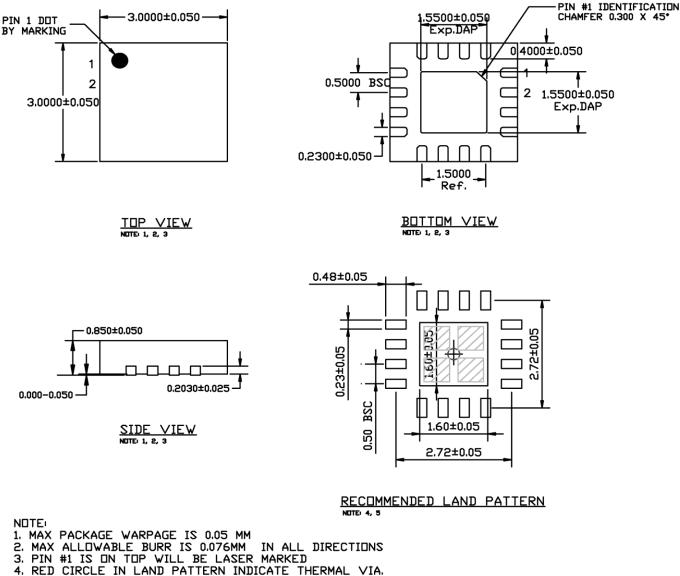

## Package Information<sup>(7)</sup>

3. PIN #1 IS ON TOP WILL BE LASER MARKED 4. RED CIRCLE IN LAND PATTERN INDICATE THERMAL VIA. SIZE SHOULD BE 0.30-0.3M IN DIAMETER AND SHOULD BE CONNECTED TO GND FOR MAX THERMAL PERFORMANCE 5. GREEN RECTANGLES (SHADED AREA) INDICATE SOLDER STENCIL OPENING ON EXPOSED PAD AREA. SIZE SHOULD BE 0.60×0.60 MM IN SIZE, 0.20 MM SPACING.

#### 16-Pin QFN

#### Note:

7. Package information is correct as of the publication date. For updates and most current information, go to: <u>www.micrel.com</u>.

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB <u>http://www.micrel.com</u>

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2013 Micrel, Incorporated.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Generators & Support Products category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

5P49V5901A748NLGI 5P49V5901B680NLGI 5P49V5901B744NLGI 5P49V5929B502NLGI 5P49V5935B520LTGI 5V49EE903-116NLGI CV183-2TPAG 82P33814ANLG/W 8T49N004A-002NLGI 8T49N004A-039NLGI 9FGV0631CKLF 9FGV0641AKLFT 9LRS3197AKLF 9UMS9633BFILF 9VRS4450AKLF NB3N51132DTR2G 8N3Q001EG-0035CDI 932SQ426AKLF 950810CGLF 9DBV0531AKILF 9DBV0741AKILF 9FGV0641AKLF 9UMS9633BKLF 9VRS4420DKILF 9VRS4420DKLF 9VRS4420DKLFT CY25404ZXI226 CY25422SXI-004 5P49V5901B712NLGI NB3H5150-01MNTXG 6INT61041NDG PL602-20-K52TC PL613-51QC 8N3Q001FG-1114CDI 9FGV0641AKILF ZL30314GKG2 ZL30253LDG1 ZL30251LDG1 ZL30250LDG1 ZL30169LDG1 ZL30142GGG2 9UMS9633BKILFT 9FGV0631CKLFT 9FGV0631CKILF 5P49V5935B536LTGI PI6LC48P0101LIE DS1099U-ST+ MAX24305EXG+ PI6LC48H02-01LIE 82P33814ANLG