## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

### Typical Applications

The HMC914LP4E is ideal for:

- SONET/SDH-Based Transmission Systems

- OC-192 Fiber Optic Modules

- · 10 Gigabit Ethernet

- 8x and 10x Fiber Channel

- · Wideband RF Gain Block

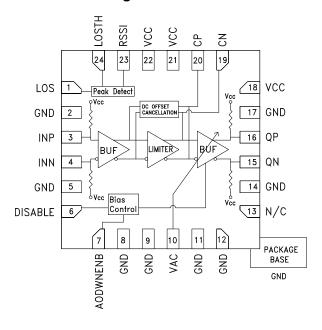

### **Functional Diagram**

#### **Features**

Supports Data Rates up to 12.5 Gbps

Differential Small Signal Gain: 32 dB

Programmable Loss-of-Signal Detection (LOS)

Automatic Output Disable Mode

Adjustable Output Voltage Swing up to 750 mVp-p Differential

Integrated DC Offset Correction

Received Signal Strength Indicator (RSSI) Output

24 Lead Plastic 4x4mm SMT Package: 16mm<sup>2</sup>

### **General Description**

HMC914LP4E is a limiting amplifier designed to support data transmission rates up to 12.5 Gbps. The amplifier can operate over a wide range of input voltage levels and provides constant-level differential output swing. HMC914LP4E features a loss of signal (LOS) indicator output where the input signal amplitude threshold level can be adjusted using the LOSTH pin. HMC914LP4E also features an output level control pin, VAC, which allows for loss compensation or for output signal level optimization. Differential output signal swing can be adjusted up to 750 mVp-p. An integrated DC offset compensation is also provided on chip. The HMC914LP4E provides an analog RSSI output voltage which is proportional to input signal amplitude.

All single-ended input signals are terminated with 50 ohms to +3.3V on-chip, and may be either AC or DC coupled. The outputs of the HMC914LP4E may be operated either differentially or single-ended. The HMC914LP4E operates from a single +3.3V DC supply and is available in a plastic RoHS compliant 4x4 mm SMT package.

### Electrical Specifications, $T_A = +25^{\circ}$ C, Vcc = +3.3V

| Parameter                                  | Conditions                  | Min. | Тур. | Max. | Units |

|--------------------------------------------|-----------------------------|------|------|------|-------|

| Power Supply Voltage, Vcc                  |                             | 3    | 3.3  | 3.6  | V     |

| Supply Current, Icc                        | VAC = 1V                    |      | 47   |      | mA    |

| Output Amplitude Control Voltage, VAC      |                             | 0.4  |      | 2.2  | ٧     |

| Differential Small Signal Gain             | VAC = 1V                    |      | 32   |      | dB    |

| Maximum Data Rate                          |                             | 12.5 |      |      | Gbps  |

| Small Signal Bandwidth, f <sub>3dB-H</sub> | 3-dB cutoff frequency       |      | 9.5  |      | GHz   |

| Low Frequency Cut-off, f <sub>3dB-L</sub>  | 100 nF off chip cap is used |      | 10   |      | kHz   |

# 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

### **Electrical Specifications** (Continued)

| Parameter                               | Conditions                                                     | Min. | Тур. | Max. | Units      |

|-----------------------------------------|----------------------------------------------------------------|------|------|------|------------|

| Input return loss, S11                  | Up to 12 GHz                                                   | 12   |      |      | dB         |

| Output return loss, S22                 | Up to 12 GHz                                                   | 11   |      |      | dB         |

| Input Sensitivity [1]                   | VAC = 1V                                                       |      | 15   |      | mVp-p      |

| Maximum Input Swing                     | VAC = 1V                                                       |      | 1200 |      | mVp-p diff |

| Adjustable Data Output Swing Range      | VAC = 0.4V - 2.2V                                              | 240  |      | 750  | mVp-p diff |

| Output P1dB [2]                         | @ 5 GHz, VAC = 1V                                              |      | -9.5 |      | dBm        |

| Rise time, tr [3]                       | VAC = 1V, %20 to %80                                           |      | 29   |      | ps         |

| Fall time, tf [3]                       | VAC = 1V, %80 to %20                                           |      | 29   |      | ps         |

| Additive RMS jitter, Jd [4]             | VAC = 1V                                                       |      | 0.3  |      | ps         |

|                                         | @ 5 GHz                                                        |      | 3.8  |      | nV/rtHz    |

| Input referred voltage noise            | @ 8 GHz                                                        |      | 3.6  |      | nV/rtHz    |

| DISABLE Input HIGH Voltage, VIH         |                                                                | 2    |      | Vcc  | V          |

| DISABLE Input LOW Voltage, VIL          |                                                                | 0    |      | 0.8  | V          |

| AODWNENB Input HIGH Voltage, VIH        |                                                                | 2    |      | Vcc  | V          |

| AODWNENB Input LOW Voltage, VIL         |                                                                | 0    |      | 0.8  | V          |

| 100                                     | R <sub>TH</sub> = 80 kOhm between LOSTH and GND, Single-Ended  |      | 20   |      | mV         |

| LOS assert threshold level [5]          | R <sub>TH</sub> = 8.5 kOhm between LOSTH and VCC, Single-Ended |      | 380  |      | mV         |

| (6)                                     | assert, LOSTH internally set, single-ended                     |      | 63   |      | mV         |

| LOS Assert/Deassert Threshold Level [5] | deassert, LOSTH internally set, single-ended                   |      | 110  |      | mV         |

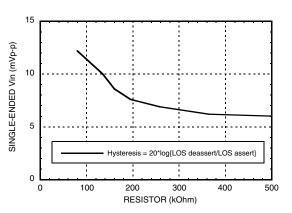

|                                         | R <sub>TH</sub> between LOSTH and VCC                          | 2    |      | 4.8  | dB         |

| LOS Hysteresis [5][6]                   | R <sub>TH</sub> between LOSTH and GND                          | 5.8  |      | 12.2 | dB         |

|                                         | LOSTH internally set                                           |      | 4.84 |      | dB         |

| LOS Output HIGH Voltage                 | 1.82 kOhm to VCC (R <sub>LOS</sub> )                           |      | 3.3  |      | V          |

| LOS Output LOW Voltage                  | 1.82 kOhm to VCC (R <sub>LOS</sub> )                           |      | 2.65 |      | V          |

| RSSI Sensitivity                        |                                                                |      | 2.7  |      | mV/V       |

<sup>[1]</sup> Signal-ended input signal level for limited output

<sup>[2]</sup> Single-ended output

<sup>[3]</sup> Data Amplitude: Differential 200 mVp-p, Data Rate: 10 Gbps PRBS 2<sup>23</sup>-1 pattern

<sup>[4]</sup> Data Amplitude: Differential 200 mVp-p, Data Rate: 10 Gbps 10101... pattern

<sup>[5]</sup> See application notes for detailed information

<sup>[6]</sup> LOS Hysteresis=20\*Log(LOS deassert/LOS assert)

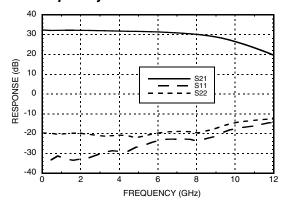

### Differential Gain & Return Loss vs. Frequency [1] [2]

# 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

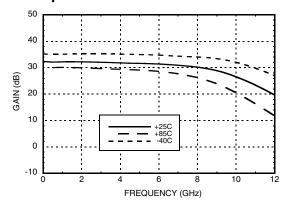

### Differential Gain vs. Frequency & Temperature [1] [2]

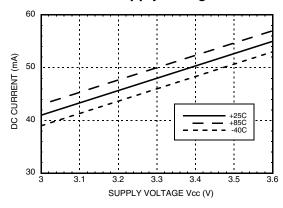

#### DC Current vs. Supply Voltage [1] [3]

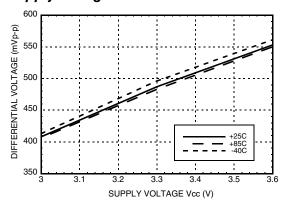

### Differential Output Swing vs. Supply Voltage [1] [3]

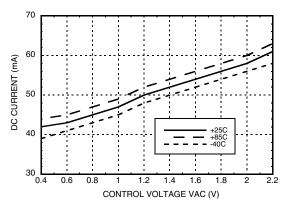

#### DC Current vs. VAC [2] [3]

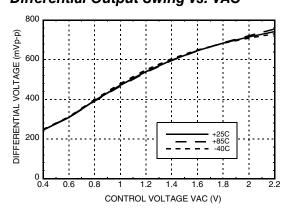

### Differential Output Swing vs. VAC [2] [3]

[1] VAC = 1V

[2] VCC=3.3V

[3] Input Data: Differential 200 mVp-p 10 Gbps NRZ PRBS 2<sup>23</sup>-1 pattern

## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

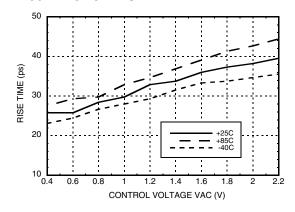

### Rise Time vs. VAC [1] [2]

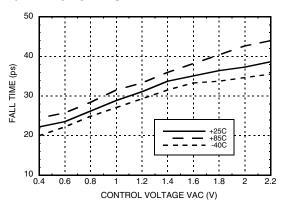

#### Fall Time vs. VAC [1] [2]

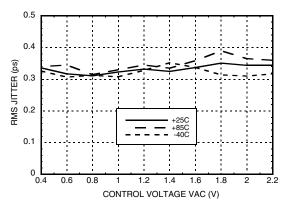

#### RMS Jitter vs. VAC [1] [3]

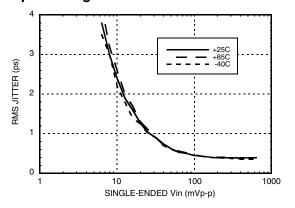

### RMS Jitter vs. Single-Ended Input Voltage [1] [4] [5]

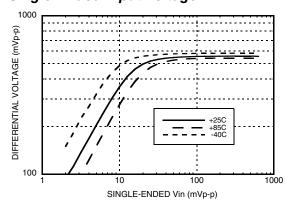

### Differential Output Swing vs. Single-Ended Input Voltage [1] [4] [5]

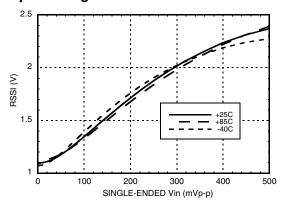

### RSSI Voltage vs. Single-Ended Input Voltage [1] [4] [5]

[1] VCC = 3.3V [2] Input Data: Differential 200 mVp-p 10 Gbps NRZ PRBS 2<sup>23</sup>-1 pattern

[3] Input Data: Differential 200 mVp-p 10 Gbps 10101... pattern [4] VAC = 1V [5] Frequency = 5 GHz

## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

### **Absolute Maximum Ratings**

| Power Supply Voltage (VCC)                                      | 3.8V to -0.5V |

|-----------------------------------------------------------------|---------------|

| Input Voltage (INP-INN)                                         | 1V to 3.3V    |

| Output Amplitude Control Voltage (VAC)                          | 0 to 2.4V     |

| Power down input voltage (DISABLE)                              | 0 to 3.6V     |

| Auto power down enable voltage (AOPDWNENB)                      | 0 to 3.6V     |

| Loss of Signal threshold programming current (LOSTH)            | ±3 mA         |

| Channel Temperature                                             | 125 °C        |

| Continuous Pdiss (T = 85 °C)<br>(derate 13.6 mW/°C above 85 °C) | 0.54 W        |

| Thermal Resistance (channel to package bottom)                  | 73.5 °C/W     |

| Storage Temperature                                             | -55 to 125 °C |

| Operating Temperature                                           | -40 to +85 °C |

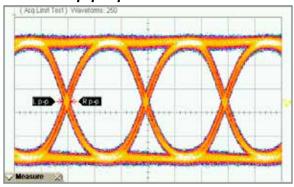

### 11.25 Gbps Differential Output Eye Diagram for 200 mVp-p Input

|            | Current  | Minimum  | Maximum  | Total Meas |

|------------|----------|----------|----------|------------|

| Eye Amp    | 481 mV   | 481 mV   | 482 mV   | 83         |

| Rise Time  | 30.00 ps | 30.00 ps | 31.33 ps | 83         |

| Fall Time  | 28.67 ps | 28.67 ps | 29.33 ps | 83         |

| p-p Jitter | 9.333 ps | 6.667 ps | 9.333 ps | 83         |

Time Scale: 30 ps/div Amplitude Scale: 100 mV/div

Test Conditions: VCC = 3.3V, VAC = 1V

Data Input:

Differential 200 mVp-p 11.25 Gbps NRZ PRBS  $2^{23}$ -1 pattern

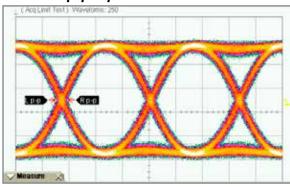

### 10 Gbps Differential Output Eye Diagram for 10 mVp-p Input

|            | Current   | Minimum   | Maximum   | Total Meas |

|------------|-----------|-----------|-----------|------------|

| Eye Amp    | 358 mV    | 358 mV    | 358 mV    | 81         |

| Rise Time  | 36.00 ps  | 36.00 ps  | 37.33 ps  | 81         |

| Fall Time  | 35.33 ps  | 34.67 ps  | 36.00 ps  | 81         |

| p-p Jitter | 15.333 ps | 12.000 ps | 15.333 ps | 81         |

Time Scale: 30 ps/div Amplitude Scale: 90 mV/div

Test Conditions: VCC = 3.3V, VAC = 1V

Data Input: Differential 10 mVp-p 10 Gbps NRZ PRBS 2<sup>23</sup>-1 pattern

## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

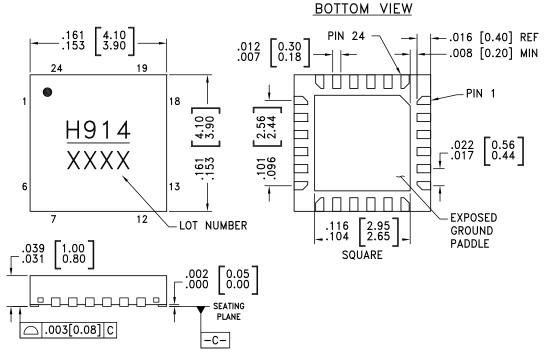

### **Outline Drawing**

#### NOTES:

- 1. LEADFRAME MATERIAL: COPPER ALLOY

- 2. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- 3. LEAD SPACING TOLERANCE IS NON-CUMULATIVE

- 4. PAD BURR LENGTH SHALL BE 0.15mm MAXIMUM.

PAD BURR HEIGHT SHALL BE 0.05mm MAXIMUM.

- 5. PACKAGE WARP SHALL NOT EXCEED 0.05mm.

- 6. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

- 7. REFER TO HMC APPLICATION NOTE FOR SUGGESTED PCB LAND PATTERN.

### **Package Information**

| Part Numbe |   | Package Body Material                              | Lead Finish   | MSL Rating | Package Marking [1] |

|------------|---|----------------------------------------------------|---------------|------------|---------------------|

| HMC914LP4  | Ē | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 [2]   | H914<br>XXXX        |

<sup>[1] 4-</sup>Digit lot number XXXX

<sup>[2]</sup> Max peak reflow temperature of 260 °C

# 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

### **Pin Descriptions**

| Pin Number                                    | Function | Description                                                                                                                                                                                                                                                 | Interface Schematic                        |

|-----------------------------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 1                                             | LOS      | Loss of signal indicator. Open collector output. Requires an external resistor to VCC. This output sinks 500 uA DC current when input is lower than the threshold.                                                                                          | LOS                                        |

| 2, 5, 8, 9,<br>11, 12, 14, 17<br>Package Base | GND      | Signal and supply ground.                                                                                                                                                                                                                                   | GND                                        |

| 3, 4                                          | INP, INN | Differential (INP-INN) or single-ended (INP) data inputs.                                                                                                                                                                                                   | Vcc<br>500<br>INP O                        |

| 6                                             | DISABLE  | Disables output buffer. Internally set to VCC. Data outputs are enabled when DISABLE is high or floating.                                                                                                                                                   | 20k DISABLE O                              |

| 7                                             | AODWNENB | Enables the automatic output disable feature. If asserted, outputs automatically disable when the input signal is below programmed loss threshold. Active low. Internally set to VCC. Outputs enable when the input signal returns its desired swing level. | 20k AODWNENB                               |

| 10                                            | VAC      | Output Amplitude Control.<br>Internally set for 500 mV differential p-p.                                                                                                                                                                                    | Vcc<br>12k0<br>VAC<br>3300<br>5.5k0<br>GND |

| 13                                            | N/C      | The pins are not connected internally; however, all data shown herein was measured with these pins connected to RF/DC ground externally.                                                                                                                    |                                            |

# 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

### Pin Descriptions (Continued)

| Pin Number | Function | Description                                                                            | Interface Schematic  |

|------------|----------|----------------------------------------------------------------------------------------|----------------------|

| 15, 16     | QN, QP   | Differential data outputs                                                              | Vcc<br>500 QP,<br>QN |

| 18, 21, 22 | Vcc      | Power Supply (+3.3V)                                                                   |                      |

| 19, 20     | CN, CP   | Filter capacitor for offset correction. 100 nF should be connected between these pins. | 1.8k CP CN           |

| 23         | RSSI     | Received Signal Strength Output.                                                       | RSSI                 |

| 24         | LOSTH    | Loss of signal threshold setting input. User programmable with resistor to VCC or GND. | LOSTH                |

## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

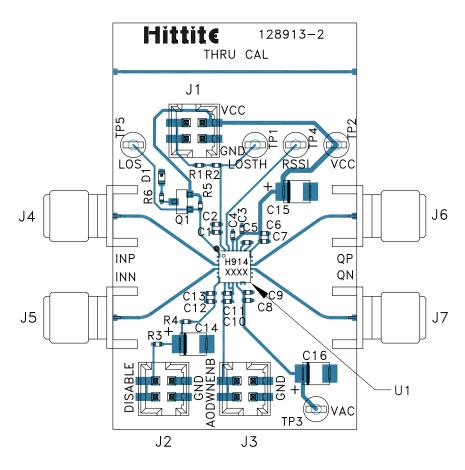

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB 128915 [1]

| Item                     | Description                   |

|--------------------------|-------------------------------|

| J1 - J3                  | 4 Pin DC Connector            |

| J4 - J7                  | SMA Connector                 |

| TP1 - TP5                | DC Pin                        |

| C1 - C2                  | 100 nF Capacitor, 0402 Pkg.   |

| C3, C5, C6, C8, C10, C12 | 100 nF Capacitor, 0402 Pkg.   |

| C4, C7, C9, C11, C13     | 1 nF Capacitor, 0402 Pkg.     |

| C14 - C16                | 4.7 μF Capacitor, Tantalum    |

| R1 - R2                  | 4.75 kOhm Resistor, 0402 Pkg. |

| R3 - R4                  | 0 Ohm Resistor, 0402 Pkg.     |

| R5                       | 1.82K Ohm Resistor, 0402 Pkg. |

| R6                       | 390 Ohm Resistor, 0402 Pkg.   |

| D1                       | LED                           |

| Q1                       | PNP Transistor                |

| Item    | Description                   |

|---------|-------------------------------|

| U1      | HMC914LP4E Limiting Amplifier |

| PCB [2] | 128913 Evaluation PCB         |

[1] Reference this number when ordering complete evaluation PCB[2] Circuit Board Material: Arlon 25FR or Rogers 4350

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

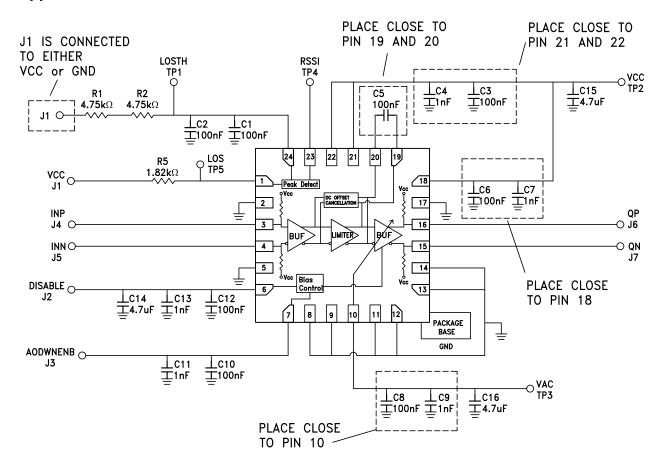

### **Application Circuit**

## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

### Application Information

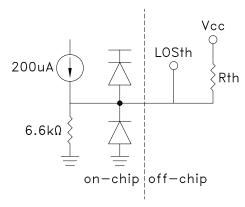

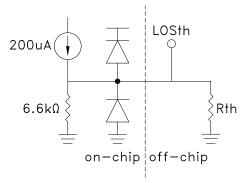

#### Loss of Signal and Setting the Input Signal Threshold

The HMC914LP4E features an input signal level monitoring over a broad range. En external resistor is used at LOSTH pin to program the input signal amplitude threshold for generating the LOS output indicator. When this pin is kept floating LOSTH level is set internally to single-ended 63 mVp-p.

LOS is an open collector output suitable for wired-OR connection for parallel alarm signals; it requires an external pull-up resistor, RLOS. If the input signal level drops below the asserted threshold level then, LOS output DC voltage goes low. It goes high only when the input level exceeds the upper hysteresis threshold level. When LOSTH pin is floating then the de-assert level will be single-ended 110 mVp-p. If this function is not required, the LOS output can be left floating.

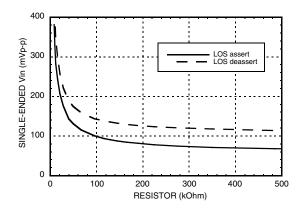

If input threshold value is desired to be higher than 63 mVp-p then an external RTH resistor should be connected between LOSTH pin and VCC. Desired threshold value can be obtained by changing the value of the resistor RTH as shown in the figures below.

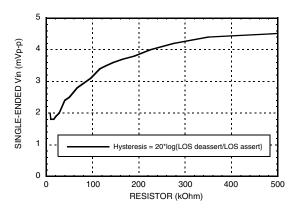

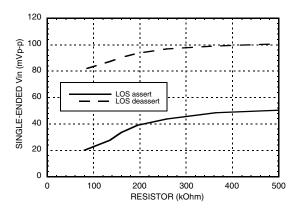

#### LOS Assert/Deassert Voltage vs. Rth

#### LOS Hysteresis vs. Rth

## 12.5 Gbps LIMITING AMPLIFIER w/ LOSS OF SIGNAL FEATURE

If input threshold value is desired to be lower than 63 mV down to 20 mVp-p then an external RTH resistor should be connected between LOSTH pin and GND. Desired threshold value can be obtained by changing the value of the resistor value as shown in the figures below.

### LOS Assert/Deassert Voltage vs. Rth

### LOS Hysteresis vs. Rth

#### **Automatic Output Disable**

The HMC914LP4E has two different disable features; one is manual and other is automatic.

DISABLE pin provides manual control over the output. DISABLE pin is a CMOS input and active "low". There is an integrated pull-up resistor to VCC at this input. If a low level voltage is applied to this input, differential data outputs QP / QN are forced to VCC and Disabled. If this input is left floating or logic high is applied then data outputs are enabled. Disable supply current when DISABLE=0 is 32mA.

Automatic disable mode is activated by AODWNENB CMOS input. This input is active low. To activate the automatic output disable mode logic, a low level voltage should be applied. When this mode is activated, if the input signal is lower than the programmed loss threshold, differential outputs automatically get set to VCC and are disabled. Outputs start toggling for normal operation when the input signal returns to its desired swing level. Disable supply current when AODWNENB =0 is 40mA.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Limiting Amplifiers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

MAX3747AEUBT MAX3711ETG+ MAX3945ETE+ MAX3768CUB MAX3748HETE#G16 MAX3747AEUB+T MAX3645ESE+

MAX3268CUB+ MAX3748HETE+ MAX3964AETP+T MAX3645ESE MAX3748HETE MAX3945ETE SY88943VKG SY88149HALMG

SY88073LMG SY88063CLMG HMC914LP4ETR ADN2891ACPZ-500RL7 HMC865LC3 HMC866LC3 HMC914LP4E SY88403BLEY

SY88993AVKG SY88933ALKG SY88903ALKG MAX3747BEUB+T MAX3945ETE+T MAX3748HETE+T MAX3272AETP+T

MAX3264CUE+ MAX3272AETP+ MAX3645EEE+ MAX3645EEE+T MAX3747AEUB+ MAX3747BEUB+ MAX3761EEP+

MAX3762EEP+ MAX3799ETJ+ MAX3861ETG+ MAX3969ETP+ SY88993AVKG SY88307BLEY SY88149HLMG SY88149NDLMG

SY88403BLMG SY88773VMG SY88923VKG SY88803VKG-TR SY88903VKG-TR