# **OLED DISPLAY MODULE**

# **Application Notes**

| PRODUCT<br>NUMBER | DD-12832XX-1A with EVK board |

|-------------------|------------------------------|

|-------------------|------------------------------|

# TABLE OF CONTENTS

| 1 | EVK SCHEMATIC                          |   |

|---|----------------------------------------|---|

| 2 | 2 SYMBOL DEFINITION                    | 5 |

| 3 | 3 TIMING CHARACTERISTICS               | 6 |

|   | 3.1 80 SERIES MPU PARALLEL INTERFACE   |   |

|   | 3.2 6800 SERIES MPU PARALLEL INTERFACE |   |

|   | 3.3 SPI INTERFACE                      | 9 |

| 4 | CONNECTION BETWEEN OLED AND EVK        |   |

| 5 | 5 POWER DOWN AND POWER UP SEQUENCE     |   |

| 6 | 6 HOW TO USE THE DD-12832XX-1A         |   |

|   | 6.1 RECOMMENDED INITIAL CODE           |   |

| Product No. | DD-12832XX-1A | REV. A | ] | Daga | 2/15 |

|-------------|---------------|--------|---|------|------|

| Product No. |               |        |   | Page | 2/13 |

### **REVISION RECORD**

| Rev. | Date                                 | Page | Chapt. | Comment     | ECR no. |

|------|--------------------------------------|------|--------|-------------|---------|

| А    | 08 <sup>th</sup><br>December<br>2008 |      |        | First Issue |         |

|      |                                      |      |        |             |         |

|      |                                      |      |        |             |         |

|      |                                      |      |        |             |         |

|      |                                      |      |        |             |         |

|      |                                      |      |        |             |         |

|      |                                      |      |        |             |         |

|      |                                      |      |        |             |         |

| riduct No. rage 37 13 | Product No. | DD-12832XX-1A | REV. A | Daga | 2/15 |

|-----------------------|-------------|---------------|--------|------|------|

|                       | Product No. |               |        | Page | 5/15 |

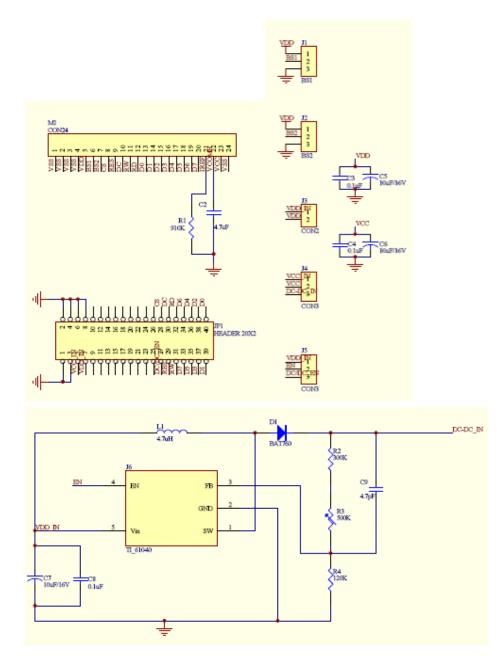

# **1 EVK Schematic**

| Product No  | DD-12832XX-1A | REV. A | Daga | 4/15 |

|-------------|---------------|--------|------|------|

| Product No. |               |        | Page | 4/13 |

# 2 Symbol Definition

VCC: Power supply for panel driving voltage.

**VSS:** This is ground pin.

**VDD:** Power supply for core logic operation.

**VDDIO:** Power supply for interface logic level.

BS0~BS2: MUC bus interface selection pin (BS0 pulled LOW in internal).

CS: This pin is chip select input (active LOW).

RES: This pin is reset signal input (active LOW).

**D/C:** This is DATA/COMMAND control pin. When it is Pulled HIGH, the data at D[0~7] is treated as data. When it is pulled LOW, the data at D[0~7] will be transferred to the command register. In I2C mode, this pin acts as SA0 for slave address select.

**R/W:** This is read/write control input pin connecting to the MCU interface. When interface to a 6800series microprocessor, Read mode will be carried out when this pin is pulled HIGH and write mode when low. When interface to an 8080-microprocessor, this pin when be the data Write input. When serial interface is selected, this pin must be connected to Vss.

**E/RD:** When interface to a 6800-series microprocessor, this pin will be used as the Enable (E) signal. When interface to an 8080-microprocessor, this pin receives the Read (RD#)signal.

**D0~D7**: These are 8-bit bi-directional data bus to be connected to the microprocessors data bus. When serial interface mode is selected, D0 (SCLK) will be the serial clock input, D1 (SDIN) will be the serial data input and D2 should be left opened. When I2C mode is selected, D1 (SDAin) AND D2 (SDAout) should be tied together, D0 (SCL) is the I2Cclock input

**IREF:** This is segment output current reference pin.

VCOMH: This pin for COM signal deselected level voltage.

| Product No. | DD-12832XX-1A | REV. A | Daga | 5/15 |

|-------------|---------------|--------|------|------|

| Product No. |               |        | Page | 5/15 |

## **3** Timing characteristics

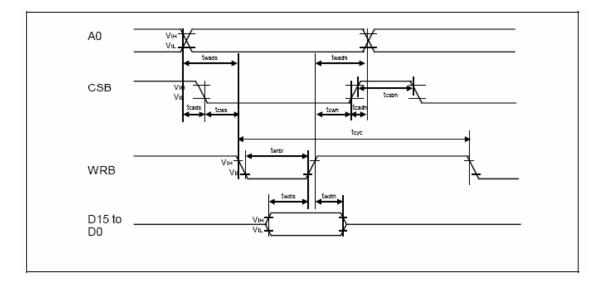

### 3.1 80 Series MPU parallel interface

#### Write Characteristics

Figure 1: 80-series MPU parallel interface write timing characteristics

|                                        |                                                               | (VDD       | ) = 2.8V,    | Ta = 25  | °C) |     |      |

|----------------------------------------|---------------------------------------------------------------|------------|--------------|----------|-----|-----|------|

| Symbol                                 | Parameter                                                     | Conditions | Related Pins | MIN      | TYP | MAX | Unit |

| t <sub>cyc</sub>                       | Write cycle time                                              | -          | WRB          | 100      | -   | -   | ns   |

| t <sub>cads</sub><br>t <sub>cadh</sub> | Address and Select setup time<br>Address and Select hold time | -          | CSB,A0       | 0<br>0   | -   | -   | ns   |

| t <sub>wads</sub><br>t <sub>wadh</sub> | Address setup time<br>Address hold time                       | -          | A0           | 50<br>20 | -   | -   | ns   |

| t <sub>ows</sub><br>t <sub>own</sub>   | Select setup time<br>Select hold time                         | -          | CSB          | 10<br>10 | -   | -   | ns   |

| t <sub>wrbi</sub>                      | Write Low pulse width                                         | -          | WRB          | 30       | -   | -   | ns   |

| t <sub>csbh</sub>                      | Select High pulse width                                       | -          | CSB          | 10       | -   | -   | ns   |

| t <sub>wats</sub><br>t <sub>wath</sub> | Data setup time<br>Data hold time                             | -          | D15 to D0    | 10<br>20 | -   | -   | ns   |

#### Table 1: 80-Series MPU Parallel Interface Write Timing Characteristics

| Product No. | DD-12832XX-1A | REV. A | Paga | 6/15 |

|-------------|---------------|--------|------|------|

| Product No. |               |        | Page | 0/13 |

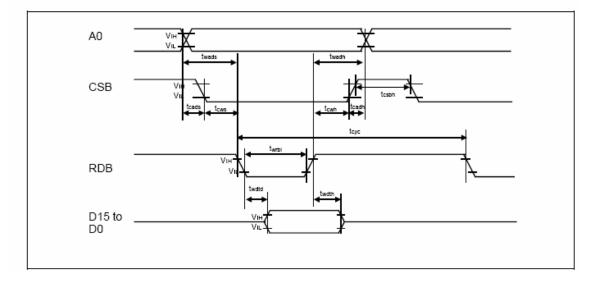

#### READ CHARACTERISTICS

Figure 2: 80-series MPU parallel interface Read timing characteristics

| Symbol                                 | Parameter                                                     | Conditions | Related Pins | MIN      | TYP | MAX | Unit |

|----------------------------------------|---------------------------------------------------------------|------------|--------------|----------|-----|-----|------|

| t <sub>cyc</sub>                       | Read cycle time                                               | -          | RDB          | 500      | -   | -   | ns   |

| t <sub>cads</sub><br>t <sub>cadh</sub> | Address and Select setup time<br>Address and Select hold time | -          | CSB,A0       | 0<br>0   | -   | -   | ns   |

| t <sub>rads</sub><br>t <sub>radh</sub> | Address setup time<br>Address hold time                       | -          | A0           | 50<br>20 | -   | -   | ns   |

| t <sub>ors</sub><br>t <sub>orn</sub>   | Select setup time<br>Select hold time                         | -          | CSB          | 10<br>10 | -   |     | ns   |

| t <sub>rdbl</sub>                      | Read Low pulse width                                          | -          | RDB          | 250      | -   | -   | ns   |

| t <sub>csbh</sub>                      | Select High pulse width                                       | -          | CSB          | 10       | -   | -   | ns   |

| t <sub>rata</sub><br>t <sub>rath</sub> | Data output delay time<br>Data output hold time               | CL = 100pF | D15 to D0    | - 5      | -   | 200 | ns   |

Table 2: 80-Series MPU Parallel Interface Read Timing Characteristics

| Product No  | DD-12832XX-1A | REV. A | Daga | 7/15 |

|-------------|---------------|--------|------|------|

| Product No. |               |        | Page | //15 |

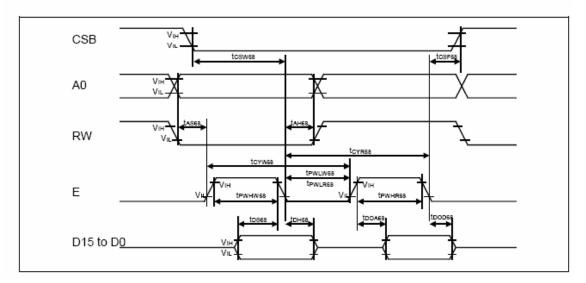

### 3.2 6800 Series MPU parallel interface

#### PARALLEL INTERFACE CHARACTERISTICS (6800-SERIES MPU)

#### Figure 3: 6800-Series MPU Parallel Interface Write Timing Characteristics

|                                                      | (Vss=0V, Vdd=2.8V,Ta = 25°C)                                                                |            |              |                  |     |          |      |

|------------------------------------------------------|---------------------------------------------------------------------------------------------|------------|--------------|------------------|-----|----------|------|

| Symbol                                               | Parameter                                                                                   | Conditions | Related Pins | MIN              | TYP | MAX      | Unit |

| tcsw68<br>tcsF68                                     | Chip select setup time<br>Chip select hold time                                             | -          | CSB          | 10<br>10         | -   | -        | ns   |

| taseb<br>t <sub>aheb</sub>                           | Address setup time<br>Address hold time                                                     | -          | A0<br>RW     | 50<br>20         | -   | -        | ns   |

| t <sub>cyw68</sub><br>tpwhw68<br>t <sub>pwlw68</sub> | Write cycle time<br>Write High Time<br>Write Low Time                                       | -          | E            | 160<br>40<br>90  | -   | -        | ns   |

| t <sub>cyr68</sub><br>tpwhr68<br>tpwlr68             | Read cycle time (Parameter read)<br>Read High (Parameter read)<br>Read Low (Parameter read) | -          | E            | 160<br>40<br>90  | -   | -        | ns   |

| tcyr68<br>tpwhr68<br>tpwlr68                         | Read cycle time (Data read)<br>Read High (Data read)<br>Read Low (Data read)                | -          | E            | 450<br>355<br>90 | -   | -        | ns   |

| t <sub>ossa</sub><br>t <sub>ohsa</sub>               | Data setup time<br>Data hold time                                                           | -          | D15 to D0    | 10<br>20         | -   | -        | ns   |

| t <sub>doa68</sub><br>tdod68                         | Data output access time<br>Data output disable time                                         | CL = 30pF  | D15 to D0    | -<br>40          | -   | 40<br>80 | ns   |

#### Table 3: 6800-Series MPU Parallel Interface Write Timing Characteristics

| Product No. | DD-12832XX-1A | REV. A | Dago | 8 / 15 |

|-------------|---------------|--------|------|--------|

| Product No. |               |        | Page | 0/13   |

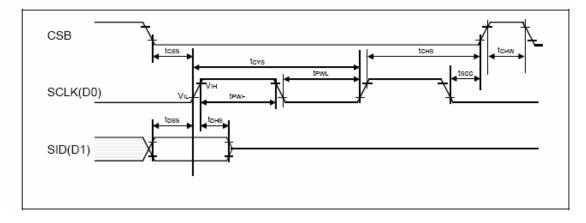

### 3.3 SPI INTERFACE

#### SERIAL INTERFACE CHARACTERISTICS

#### Figure 4: Serial Peripheral Interface Timing Characteristics

|                                  |                                                                                 |            | (Vs          | s=0V, Vo        | D=2.8V,     | Ta = 25°(   | C)   |

|----------------------------------|---------------------------------------------------------------------------------|------------|--------------|-----------------|-------------|-------------|------|

| Symbol                           | Parameter                                                                       | Conditions | Related Pins | MIN             | түр         | MAX         | Unit |

| tcys<br>t <sub>wнs</sub><br>twis | Serial clock cycle<br>High pulse width<br>Low pulse width                       | -          | SCLK         | 160<br>60<br>60 | -           | -           | ns   |

| toss<br>toнe                     | Data setup time<br>Data hold timo                                               |            | SID (D1)     | 60<br>60        | -           | -           | ns   |

| t <sub>css</sub><br>tcнs<br>tcнw | Chip select setup time<br>Chip select hold time<br>Chip select high pulse width | -          | CSB          | 60<br>65<br>45  | -<br>-<br>- | -<br>-<br>- | ns   |

| tscc                             | SCLK to Chip select                                                             | -          | SCLK, CSB    | 20              | -           | -           | ns   |

**Table 4: Serial Peripheral Interface Timing Characteristics**

| Product No. | DD-12832XX-1A | REV. A | Daga | 0/15 |

|-------------|---------------|--------|------|------|

| Product No. |               |        | Page | 9/13 |

## 4 Connection Between OLED and EVK

#### Figure 5 EVK PCB and DD-12832XX-1A Module

The DD-12832XX-1A is COG type module; please refer to figure 1 & 2. User can use leading wire to connect EVK with customers systems. The example shown in Fig

#### **Figure 6 combination of the module**

| Product No. | DD-12832XX-1A | REV. A | ] | Daga | 10/15 |

|-------------|---------------|--------|---|------|-------|

| Product No. |               |        |   | Page | 10/13 |

Figure 7: EVK with test platform

Note 1: It is OLED high voltage supply

Note 2: It is logic voltage supply

Note 3: Those are leading wire connect to control board. Those are data pin (D0~D7)

Note 4: Those are leading wore connect to control board. Those are control pin. (DC, CS, RD, WR, RES)

| Product No. | DD-12832XX-1A | REV. A | Daga | 11/15 |

|-------------|---------------|--------|------|-------|

| Product No. |               |        | rage | 11/13 |

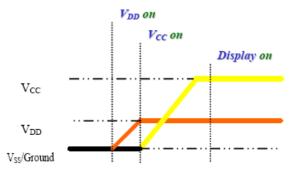

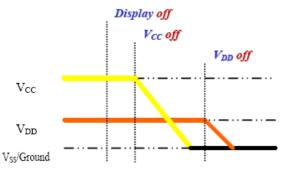

# 5 Power down and Power Up sequence

To protect the OLED panel and extend the panel life time the driver IC power up/down routine should include a delay period between high voltage and low voltage power sources during turn on/off. So that the panel has enough time to charge up or discharge before/ after operation.

#### Power up Sequence:

- 1. Power up V<sub>DD</sub>

- 2. Send Display off command

- 3. Driver IC Initial Setting

- Clear Screen

- Power up V<sub>DDH</sub>

- Delay 100ms (when V<sub>DD</sub> is stable)

- 7. Send Display on command

#### Power down Sequence:

- 1. Send Display off command

- Power down V<sub>DDH</sub>

- Delay 100ms

- (when V<sub>DDH</sub> is reach 0 and panel is completely

- 4. Power down V<sub>DD</sub>

discharges)

| Product No. | DD-12832XX-1A | REV. A | Daga | 12/15 |

|-------------|---------------|--------|------|-------|

| Product No. |               |        | Page | 12/13 |

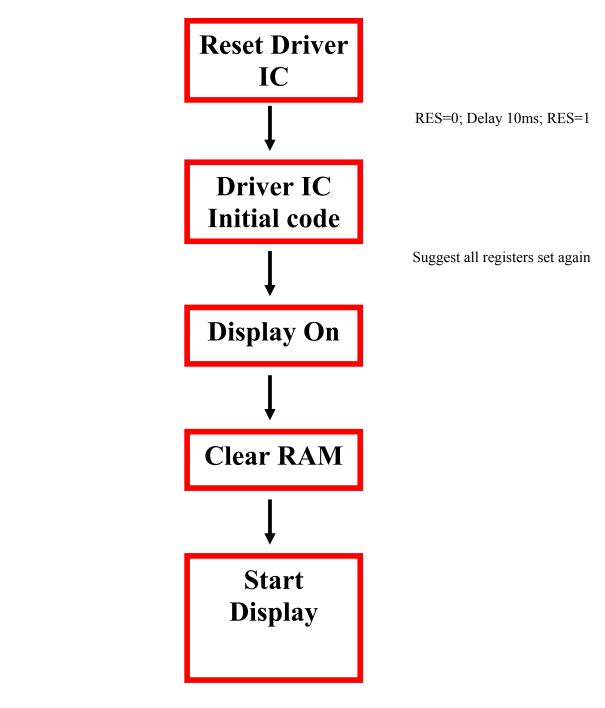

6 How to use the DD-12832XX-1A

| riduce into rage 13/13 | Product No. | DD-12832XX-1A | REV. A | Dago | 12/15 |

|------------------------|-------------|---------------|--------|------|-------|

|                        | Product No. |               |        | Page | 13/13 |

## 6.1 Recommended Initial code

void initial()

| {                    |                                                          |

|----------------------|----------------------------------------------------------|

| write_command(0xae); | //(display on)                                           |

| write command(0x00); | //set low column address                                 |

| write_command(0x10); | //set high column address                                |

| write_command(0x40); | //(display start set)                                    |

| write_command(0x2e); | //(stop horzontal scroll)                                |

| write_command(0xb0); | //(page address)                                         |

| write_command(0x81); | //(set contrast control register)                        |

| write_command(0x7f); |                                                          |

| write_command(0xa1); | //(set segment re-map)                                   |

| write command(0xa4); | //(normal display mode)                                  |

| write_command(0xa6); | //(set normal/inverse display)                           |

| write_command(0xa8); | //(set multiplex ratio)                                  |

| write_command(0x3f); |                                                          |

| write_command(0xd3); | //(set display offset)                                   |

| write_command(0x00); |                                                          |

| write_command(0xad); | //(set dc-dc on/off)                                     |

| write_command(0x8e); | // ······//                                              |

| write_command(0xc8); | //(set com output scan direction)                        |

| write_command(0xd5); | //(set display clock divide ratio/oscillator/frequency)  |

| write_command(0xf0); | // ···································                   |

| write_command(0xd8); | //(set area color mode on/off & low power display mode ) |

| write_command(0x05); | // ···································                   |

| write_command(0xd9); | //(set pre-charge period)                                |

| write_command(0xc2); |                                                          |

| write_command(0xda); | //(set com pins hardware configuration)                  |

| write_command(0x12); | ······································                   |

| write_command(0xdb); | //(set vcom deselect level)                              |

| write_command(0x08); | ()                                                       |

| write_command(0xaf); | //(display on)                                           |

| }                    | V - F - J - J                                            |

| ,                    |                                                          |

| Product No. | DD-12832XX-1A | REV. A | Daga | 14/15 |

|-------------|---------------|--------|------|-------|

| Product No. |               |        | Page | 14/13 |

#### WRITE DATA & COMMAND SUB FUNCTION

```

void write_command(unsigned char aa)

IOCLR = 0x00000ff;

//RD=1

IOSET = RD IN;

IOCLR = DC_IN;

//DC=0

IOCLR = CS_IN;

//CS=0

IOCLR = WR_IN;

//WR=0

IOSET = aa;

//----input command

IOSET = WR_IN;

//WR=1

IOSET = CS_IN;

//CS=1

IOCLR = RD_IN;

}

void write_data(unsigned char bb)

IOCLR = 0x000000ff;

IOSET = RD_IN;

//RD=1

IOSET = DC_IN;

//DC=1

IOCLR = CS_IN;

//CS=0

IOCLR = WR_IN;

//WR=0

IOSET = bb;

//-----input data

IOSET = WR_IN;

//WR=1

IOSET = CS_IN;

//CS=1

}

```

Note: RD recommends Initial code and sub function for 8080 series CPU interface.

| Product No. | DD-12832XX-1A | REV. A | Daga | 15/15 |

|-------------|---------------|--------|------|-------|

| Product No. |               |        | Page | 13/13 |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for densitron manufacturer:

Other Similar products are found below :

DMT024QVNUNT0-2C DMT028QVNTNT0S-1A DMT028QVHXCMI-1A DMT024QVNUCMI-2A LMR4048BG2C16HNG/5V