MPC755\_D PNS 010410

Freescale Part Numbers Affected: XPC745BPX300LD XPC745BPX350LD

**Application-Specific Information**

XPC755BRX300LD XPC755BRX350LD XPC755BRX400LD -XPC755BPX300LD XPC755BPX350LD XPC755BPX350LD XPC755BPX400LD

# **MPC755 Part Number Specification**

This document describes part number specific changes to recommended operating conditions and revised electrical specifications, as applicable, from those described in the general *MPC755 Hardware Specifications*.

Specifications provided in this Part Number Specification supersede those in the *MPC755 Hardware Specifications* (order #: MPC755EC/D) for these part numbers only; specifications not addressed herein are unchanged. Because this document is frequently updated, refer to the website at http://www.freescale.com/ for the latest version.

Note that headings and table numbers in this data sheet are not consecutively numbered. They are intended to correspond to the heading or table affected in the general hardware specification.

Table A lists the part numbers having specifications that differ from the *MPC755 Hardware Specifications*. Part numbers not listed in Table A do not differ from the *MPC755 Hardware Specifications*. For more detailed ordering information see Table B.

| Freescale Part Number | Opera         | ting Conditions |                     | Significant Differences from Hardware Specification                                                                                 |

|-----------------------|---------------|-----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Freescale Fart Number | CPU Frequency | Vdd             | Т <sub>Ј</sub> (°С) | Significant Differences from hardware Specification                                                                                 |

| XPC755BRX300LD        | 300 MHz       | 2.0V±100mV      | 0 to 105            | 2.0V/1.8V I/O voltage supported, 2.5V I/O not supported; all nom-                                                                   |

| XPC755BRX350LD        | 350 MHz       |                 |                     | inal core voltages are 2.0V±100mV; AC timing different for pro-<br>cessor bus and L2 bus interfaces; L2 bus interface AC timing not |

| XPC755BRX400LD        | 400 MHz       |                 |                     | guaranteed in 1.8V/2.0V mode.                                                                                                       |

| XPC755BPX300LD        | 300 MHz       |                 |                     |                                                                                                                                     |

| XPC755BPX350LD        | 350 MHz       |                 |                     |                                                                                                                                     |

| XPC755BPX400LD        | 400 MHz       |                 |                     |                                                                                                                                     |

| XPC745BPX300LD        | 300 MHz       | 2.0V±100mV      | 0 to 105            | 2.0V/1.8V I/O voltage supported, 2.5V I/O not supported; all nom-                                                                   |

| XPC745BPX350LD        | 350 MHz       |                 |                     | inal core voltages are 2.0V±100mV; AC timing different for processor bus interface.                                                 |

#### Table A. Significant Differences from Hardware Specification by Part Number

Note: The X prefix in a Freescale PowerPC part number designates a "Pilot Production Prototype" as defined by Freescale SOP 3-13. These are from a limited production volume of prototypes manufactured, tested and Q.A. inspected on a qualified technology to simulate normal production. These parts have only preliminary reliability and characterization data. Before pilot production prototypes may be shipped, written authorization from the customer must be on file in the applicable sales office acknowledging the qualification status and the fact that product changes may still occur while shipping pilot production prototypes.

#### Errata

There are currently no known errata for the part numbers addressed by this data sheet.

The PowerPC name and the PowerPC logotyp are trademarks of International Business Machines Corporation used by Freescale under license from International Business Machines Corporation.

This document contains information on a new product under development by Freescale. Freescale reserves the right to change or discontinue this product without notice.

© . 2001. All rights reserved.

#### **1.3 General Parameters**

The following general parameters apply to all part numbers described herein:

| Core power supply: | $2.0 V \pm 100 \text{ mV}$ dc (nominal; see Table 3 for recommended operating conditions)      |

|--------------------|------------------------------------------------------------------------------------------------|

| I/O power supply   | $1.8 V \pm 100 \text{ mV}$ dc (processor bus interface only; not supported on L2 interface) or |

|                    | $2.0 V \pm 100 \text{ mV}$ dc (processor bus interface only; not supported on L2 interface) or |

|                    | $3.3 \text{ V} \pm 165 \text{ mV}$ dc (input thresholds are configuration pin selectable)      |

Note that part revisions prior to Rev 2.8 (Rev E) do not support core voltages down to 1.8 V.

#### 1.4.1 DC Electrical Characteristics

All part numbers affected by this specification support 3.3V and 1.8V/2.0V I/O voltages but do not support 2.5V I/O voltages. Table 2 describes the input threshold voltage settings. These settings apply to all device revisions prior to Rev. 2.8 (Rev E), including all part numbers described herein. Note that the MPC745 does not provide an L2 interface.

| BVSEL Signal | L2VSEL Signal | Processor Bus Interface<br>Voltage | L2 Bus<br>Interface Voltage |

|--------------|---------------|------------------------------------|-----------------------------|

| 0            | 0             | 1.8V or 2.0V                       | 1.8V or 2.0V                |

| 0            | 1             | 1.8V or 2.0V                       | 3.3V                        |

| 1            | 0             | 3.3V                               | 1.8V or 2.0V                |

| 1            | 1             | 3.3V                               | 3.3V                        |

| Table 2 Input | Threshold | Voltage | Settings |

|---------------|-----------|---------|----------|

|---------------|-----------|---------|----------|

Caution: The input threshold selection must agree with the OVdd/L2OVdd voltages supplied.

Table 3 provides the recommended operating conditions for all device revisions prior to Rev. 2.8 (Rev E), including all part numbers described herein.

| Table 3 | Recommended | Operating Conditions |  |

|---------|-------------|----------------------|--|

|         |             |                      |  |

| Characte                     | ristic             | Symbol | Recommended Value               | Unit |

|------------------------------|--------------------|--------|---------------------------------|------|

| Core supply voltage          |                    | Vdd    | 2.0 ± 100 mV                    | V    |

| PLL supply voltage           | PLL supply voltage |        | 2.0 ± 100 mV                    | V    |

| L2 DLL supply voltage        |                    | L2AVdd | 2.0 ± 100 mV                    | V    |

| Processor bus supply voltage | BVSEL = 0          | OVdd   | 1.8 ± 100 mV or<br>2.0 ± 100 mV | V    |

|                              | BVSEL = 1          | OVdd   | 3.3 ± 165 mV                    | V    |

| L2 bus supply voltage        | L2VSEL = 0         | L2OVdd | 1.8 ± 100 mV or<br>2.0 ± 100 mV | V    |

|                              | L2VSEL = 1         | L2OVdd | 3.3 ± 165 mV                    | V    |

Note: These are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

Table 6 provides the DC electrical specifications for all device revisions prior to Rev. 2.8 (Rev E), including all part numbers described herein.

#### Table 6 DC Electrical Specifications

At recommended operating conditions (see Table 3)

| Characteristic                                | Nominal Bus<br>Voltage <sup>1</sup> | Symbol           | Min             | Max             | Unit | Notes |

|-----------------------------------------------|-------------------------------------|------------------|-----------------|-----------------|------|-------|

| Input high voltage (all inputs except SYSCLK) | 1.8/2.0                             | V <sub>IH</sub>  | 0.65 * (L2)OVdd | (L2)OVdd + 0.3  | V    | 2,3   |

|                                               | 3.3                                 | V <sub>IH</sub>  | 2.0             | (L2)OVdd + 0.3  | V    | 2,3   |

| Input low voltage (all inputs except SYSCLK)  | 1.8/2.0                             | VIL              | -0.3            | 0.35 * (L2)OVdd | V    | 2     |

|                                               | 3.3                                 | VIL              | -0.3            | 0.8             | V    |       |

| SYSCLK input high voltage                     | 1.8/2.0                             | кv <sub>IH</sub> | 1.5             | OVdd + 0.3      | V    |       |

|                                               | 3.3                                 | кv <sub>IH</sub> | 2.4             | OVdd + 0.3      | V    |       |

| SYSCLK input low voltage                      | 1.8/2.0                             | κν <sub>il</sub> | -0.3            | 0.2             | V    |       |

|                                               | 3.3                                 | κν <sub>il</sub> | -0.3            | 0.4             | V    |       |

| Output high voltage, I <sub>OH</sub> = -6 mA  | 1.8/2.0                             | V <sub>OH</sub>  | (L2)OVdd - 0.45 | —               | V    |       |

|                                               | 3.3                                 | V <sub>OH</sub>  | 2.4             | —               | V    |       |

| Output low voltage, $I_{OL} = 6 \text{ mA}$   | 1.8/2.0                             | V <sub>OL</sub>  | -               | 0.45            | V    |       |

|                                               | 3.3                                 | V <sub>OL</sub>  | -               | 0.4             | V    |       |

#### Notes:

1. Nominal voltages; see Table 3 for recommended operating conditions.

2. For processor bus signals, the reference is OVdd. L2OVdd is the reference for the L2 bus signals.

3. Excludes test signals (LSSD\_MODE, L1\_TSTCLK, L2\_TSTCLK) and IEEE 1149.1 boundary scan (JTAG) signals.

### 1.4.2.2 Processor Bus AC Specifications

All part numbers described herein have slower AC timing characteristics than later revisions of the part. The affected processor bus AC timing specifications are given in Table 10.

#### Table 10 Processor Bus AC Timing Specifications

At recommended operating conditions (see Table 3)

| Parameter                    | Symbols           | 300, 350 | Unit |      |

|------------------------------|-------------------|----------|------|------|

|                              | Cymbolo           | Min      | Max  | onic |

| Input Hold Times: All Inputs | t <sub>IXKH</sub> | 0.6      | —    | ns   |

| Valid Times: All Outputs     | t <sub>KHOV</sub> | —        | 4.5  | ns   |

## 1.4.2.4 L2 Bus AC Specifications

The AC timing characteristics of the L2 bus interface in 3.3V mode are slower for parts affected by this specification than for later revisions of the part. Additionally, the AC timing of the L2 interface is not guaranteed in 1.8V/2.0V mode. These affect the following part numbers only:

- XPC755BRX300LD

- XPC755BRX350LD

- XPC755BRX400LD

- XPC755BPX300LD

- XPC755BPX350LD

- XPC755BPX400LD

Table 12 provides the L2 bus interface AC timing specifications for the MPC755 described in this Part Number Specification when the L2 bus interface is in 3.3V mode only. The L2 bus interface of the part described herein is not tested in 1.8V/2.0V mode and does not meet these specifications. The L2 interface output drivers display a non-linear, stepped behavior when switching that prolongs the rise and fall times in this mode. This delay is typically on the order of 2 ns but is not guaranteed.Freescale does not recommend or support the use of the L2 bus interface of the affected part numbers described herein in 1.8V/2.0V mode.

### Table 12 L2 Bus Interface AC Timing Specifications

At recommended operating conditions (see Table 3)

| Parameter                                                                                                                                                                        | Symbol              | 300 MHz     |                          | 350 MHz     |                          | 400 MHz     |                          | Unit | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------|--------------------------|-------------|--------------------------|-------------|--------------------------|------|-------|

| Falameter                                                                                                                                                                        | Symbol              | Min         | Max                      | Min         | Max                      | Min         | Max                      | onn  | Notes |

| Setup Times: Data and parity                                                                                                                                                     | t <sub>DVL2CH</sub> | 1.5         | -                        | 1.5         | -                        | 1.5         | -                        | ns   | 2     |

| Input Hold Times: Data and parity                                                                                                                                                | t <sub>DXL2CH</sub> | 0.5         | -                        | 0.5         | -                        | 0.5         | -                        | ns   | 2     |

| Valid Times:<br>All outputs when L2CR[14-15] = 00<br>All outputs when L2CR[14-15] = 01<br>All outputs when L2CR[14-15] = 10<br>All outputs when L2CR[14-15] = 11                 | t <sub>L2CHOV</sub> | -<br>-<br>- | 3.6<br>3.8<br>4.0<br>4.2 |             | 3.6<br>3.8<br>4.0<br>4.2 |             | 3.6<br>3.8<br>4.0<br>4.2 | ns   | 3,4   |

| L2SYNC_IN to high impedance:<br>All outputs when L2CR[14-15] = 00<br>All outputs when L2CR[14-15] = 01<br>All outputs when L2CR[14-15] = 10<br>All outputs when L2CR[14-15] = 11 | t <sub>L2CHOZ</sub> |             | 3.5<br>4.0<br>4.2<br>4.5 | -<br>-<br>- | 3.5<br>4.0<br>4.2<br>4.5 | -<br>-<br>- | 3.5<br>4.0<br>4.2<br>4.5 | ns   | 3,5   |

Notes:

See General specifications.

### 1.10 Ordering Information

Table B provides the ordering information for the MPC755 part described in this Part Number Specification.

Table B. Ordering Information for the MPC755 Microprocessor

| Package Type | Device<br>Rev | Process | Mask Code | CPU<br>Frequency<br>(MHz) | Freescale<br>Part Number |

|--------------|---------------|---------|-----------|---------------------------|--------------------------|

| 360          | 2.7           | HIP4DP  | 57K76D    | 300MHz                    | XPC755BRX300LD           |

| CBGA         |               |         |           | 350MHz                    | XPC755BRX350LD           |

|              |               |         |           | 400MHz                    | XPC755BRX400LD           |

| 360          | 2.7           | HIP4DP  | 57K76D    | 300MHz                    | XPC755BPX300LD           |

| PBGA         |               |         |           | 350MHz                    | XPC755BPX350LD           |

|              |               |         |           | 400MHz                    | XPC755BPX400LD           |

| 255          | 2.7           | HIP4DP  | 57K76D    | 300MHz                    | XPC745BPX300LD           |

| PBGA         |               |         |           | 350MHz                    | XPC745BPX350LD           |

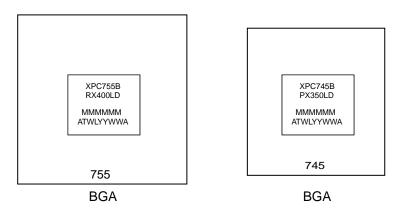

## 1.10.1 Part Marking

Parts are marked as the examples shown in Figure A.

#### Notes:

MMMMMM is the 6-digit mask number.

ATWLYYWWA is the traceability code.

CCCCC is the country of assembly. (This space is left blank if parts are assembled in the United States.)

### Figure A. Freescale Part Marking for BGA Device

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Microprocessors - MPU category:

Click to view products by NXP manufacturer:

Other Similar products are found below :

MC68302EH20C MC7457RX1000LC MC7457RX1267LC MC7457VG1267LC A2C00010998 A A2C52004004 R5F117BCGNA#20 R5F52106BDLA#U0 ADJ3400IAA5DOE MPC8245TVV266D MPC8245TZU300D MPC8260ACVVMHBB MPC8323ECVRAFDCA MPC8536ECVJAVLA BOXNUC5PGYH0AJ 20-668-0024 P1010NSN5DFB P2010NSN2MHC P2020NXE2HHC P5020NSE7QMB P5020NSE7TNB P5020NSE7VNB LS1020ASN7KQB LS1020AXN7HNB LS1020AXN7KQB A2C00010729 A A2C00039344 T1022NSE7MQB T1022NXN7PQB T1023NSE7MQA T1024NXE7PQA T1042NSE7MQB T1042NSN7MQB T1042NXN7WQB T2080NSE8TTB T2080NSN8PTB T2080NXE8TTB T2081NXN8TTB R5F101AFASP#V0 MC68302CEH20C MPC8260ACVVMIBB MPC8280CZUUPEA MPC8313ECVRAFFC MPC8313ECVRAGDC MPC8313EVRADDC MPC8313EVRAFFC MPC8313VRADDC MPC8314CVRAGDA MPC8314VRAGDA MPC8315VRAGDA