# ATmega48A/PA/88A/PA/168A/PA/328/P

# ATMEL 8-BIT MICROCONTROLLER WITH 4/8/16/32KBYTES IN-SYSTEM PROGRAMMABLE FLASH

## **Features**

- High Performance, Low Power Atmel®AVR® 8-Bit Microcontroller Family

- Advanced RISC Architecture

- 131 Powerful Instructions Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 20 MIPS Throughput at 20MHz

- On-chip 2-cycle Multiplier

- High Endurance Non-volatile Memory Segments

- 4/8/16/32KBytes of In-System Self-Programmable Flash program memory

- 256/512/512/1KBytes EEPROM

- 512/1K/1K/2KBytes Internal SRAM

- Write/Erase Cycles: 10,000 Flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C<sup>(1)</sup>

- Optional Boot Code Section with Independent Lock Bits

- In-System Programming by On-chip Boot Program

- True Read-While-Write Operation

- Programming Lock for Software Security

- Atmel<sup>®</sup> QTouch<sup>®</sup> library support

- Capacitive touch buttons, sliders and wheels

- QTouch and QMatrix<sup>®</sup> acquisition

- Up to 64 sense channels

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Six PWM Channels

- 8-channel 10-bit ADC in TQFP and QFN/MLF package

- Temperature Measurement

- 6-channel 10-bit ADC in PDIP Package

- Temperature Measurement

- Programmable Serial USART

- Master/Slave SPI Serial Interface

- Byte-oriented 2-wire Serial Interface (Philips I<sup>2</sup>C compatible)

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Interrupt and Wake-up on Pin Change

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby

- I/O and Packages

- 23 Programmable I/O Lines

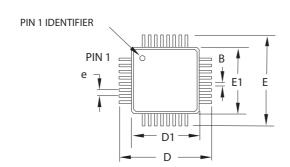

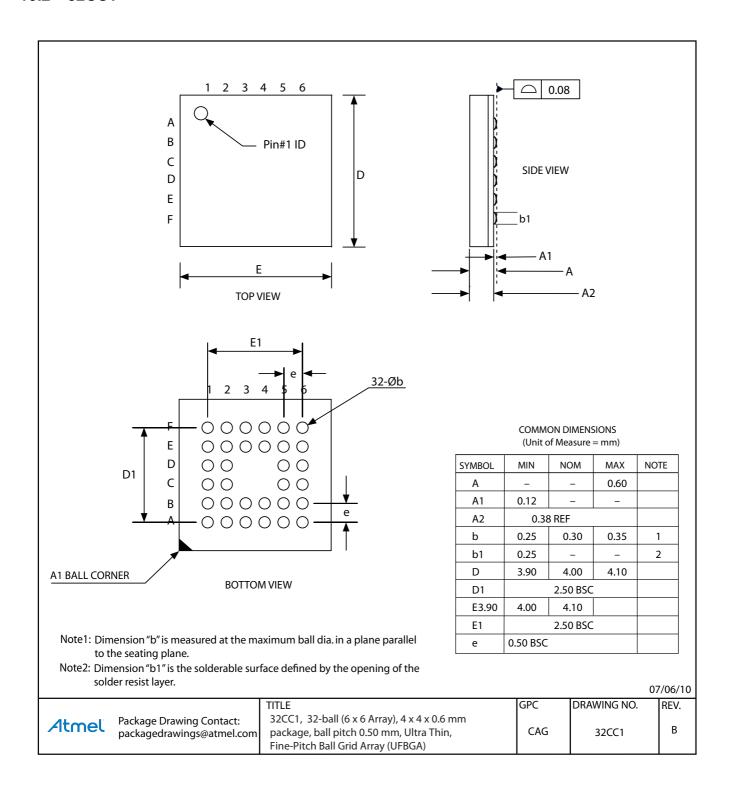

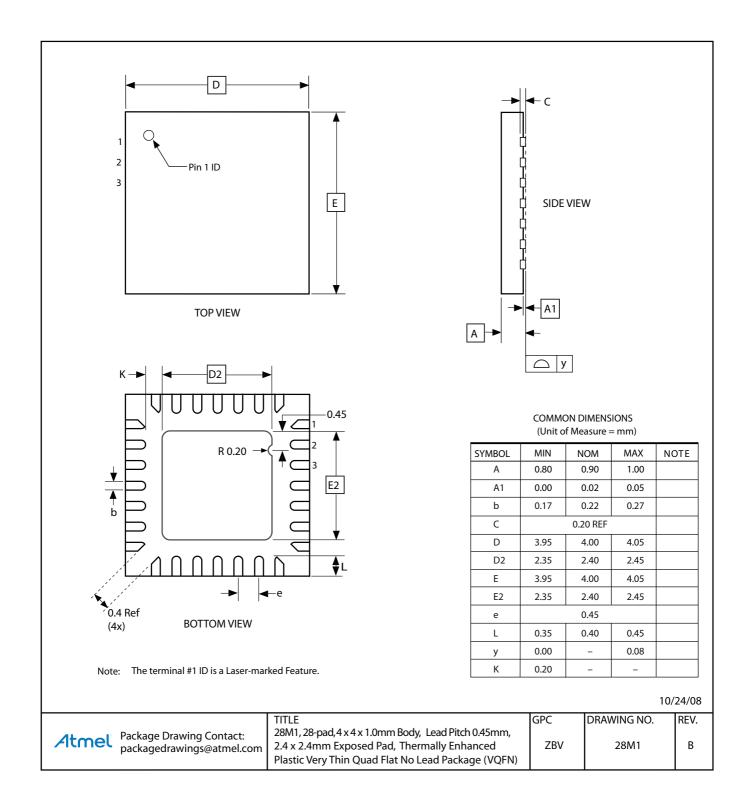

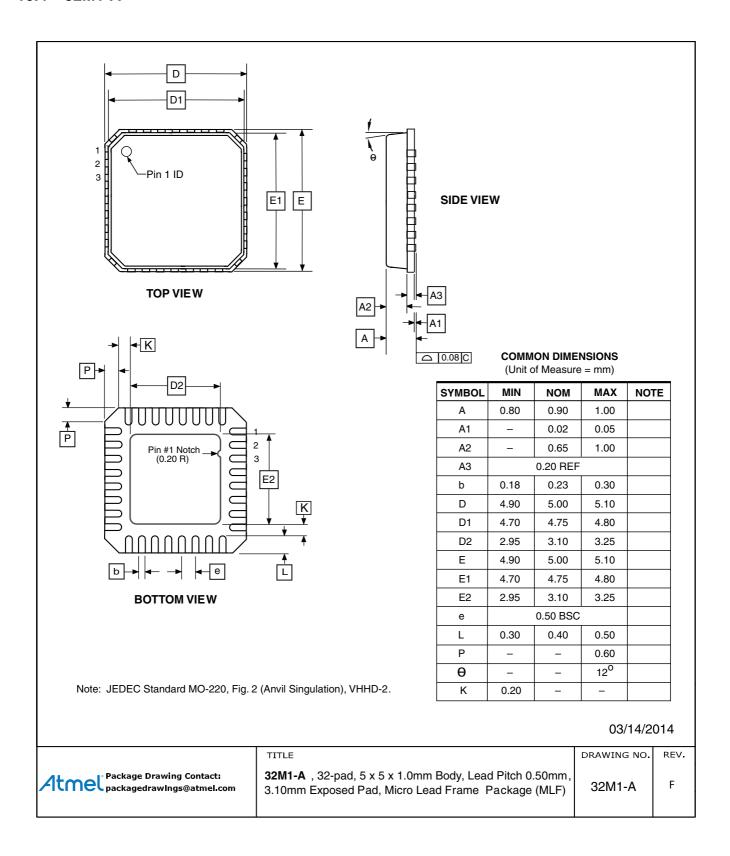

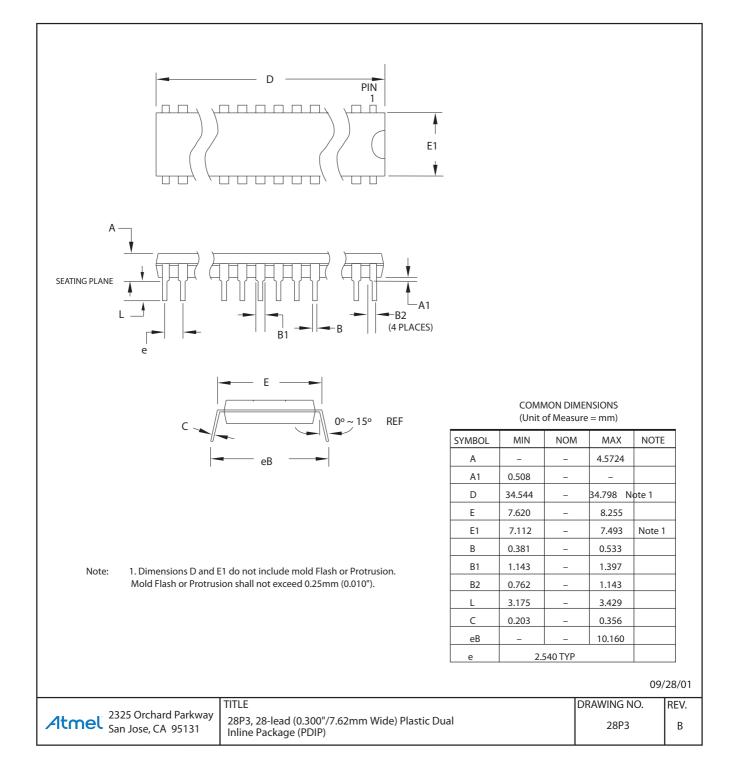

- 28-pin PDIP, 32-lead TQFP, 28-pad QFN/MLF and 32-pad QFN/MLF

- Operating Voltage:

- \_ 1.8 5.5V

- Temperature Range:

- -40°C to 85°C

- Speed Grade:

- 0 4MHz@1.8 5.5V, 0 10MHz@2.7 5.5.V, 0 20MHz @ 4.5 5.5V

- Power Consumption at 1MHz, 1.8V, 25°C

- Active Mode: 0.2mAPower-down Mode: 0.1μA

- Power-save Mode: 0.75µA (Including 32kHz RTC)

# 1. Pin Configurations

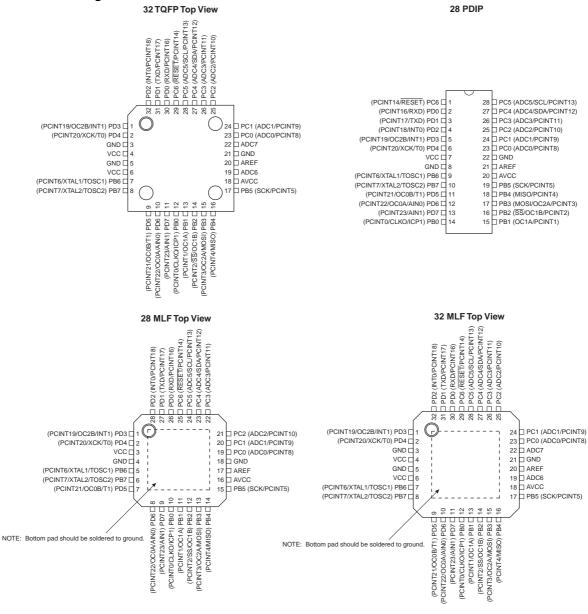

Figure 1-1. Pinout ATmega48A/PA/88A/PA/168A/PA/328/P

Table 1-1. 32UFBGA - Pinout ATmega48A/48PA/88A/88PA/168A/168PA

|   | 1   | 2   | 3   | 4   | 5    | 6    |

|---|-----|-----|-----|-----|------|------|

| Α | PD2 | PD1 | PC6 | PC4 | PC2  | PC1  |

| В | PD3 | PD4 | PD0 | PC5 | PC3  | PC0  |

| С | GND | GND |     |     | ADC7 | GND  |

| D | VDD | VDD |     |     | AREF | ADC6 |

| E | PB6 | PD6 | PB0 | PB2 | AVDD | PB5  |

| F | PB7 | PD5 | PD7 | PB1 | PB3  | PB4  |

# 1.1 Pin Descriptions

#### 1.1.1 VCC

Digital supply voltage.

#### 1.1.2 GND

Ground.

#### 1.1.3 Port B (PB7:0) XTAL1/XTAL2/TOSC1/TOSC2

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tristated when a reset condition becomes active, even if the clock is not running.

Depending on the clock selection fuse settings, PB6 can be used as input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

Depending on the clock selection fuse settings, PB7 can be used as output from the inverting Oscillator amplifier.

If the Internal Calibrated RC Oscillator is used as chip clock source, PB7...6 is used as TOSC2...1 input for the Asynchronous Timer/Counter2 if the AS2 bit in ASSR is set.

The various special features of Port B are elaborated in "Alternate Functions of Port B" on page 82 and "System Clock and Clock Options" on page 27.

#### 1.1.4 Port C (PC5:0)

Port C is a 7-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The PC5...0 output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tristated when a reset condition becomes active, even if the clock is not running.

#### 1.1.5 PC6/RESET

If the RSTDISBL Fuse is programmed, PC6 is used as an I/O pin. Note that the electrical characteristics of PC6 differ from those of the other pins of Port C.

If the RSTDISBL Fuse is unprogrammed, PC6 is used as a Reset input. A low level on this pin for longer than the minimum pulse length will generate a Reset, even if the clock is not running. The minimum pulse length is given in Table 29-11 on page 305. Shorter pulses are not guaranteed to generate a Reset.

The various special features of Port C are elaborated in "Alternate Functions of Port C" on page 85.

#### 1.1.6 Port D (PD7:0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tristated when a reset condition becomes active, even if the clock is not running.

The various special features of Port D are elaborated in "Alternate Functions of Port D" on page 88.

# 1.1.7 AV<sub>CC</sub>

$AV_{CC}$  is the supply voltage pin for the A/D Converter, PC3:0, and ADC7:6. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter. Note that PC6...4 use digital supply voltage,  $V_{CC}$ .

#### 1.1.8 **AREF**

AREF is the analog reference pin for the A/D Converter.

## 1.1.9 ADC7:6 (TQFP and QFN/MLF Package Only)

In the TQFP and QFN/MLF package, ADC7:6 serve as analog inputs to the A/D converter. These pins are powered from the analog supply and serve as 10-bit ADC channels.

# 2. Overview

The ATmega48A/PA/88A/PA/168A/PA/328/P is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the ATmega48A/PA/88A/PA/168A/PA/328/P achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

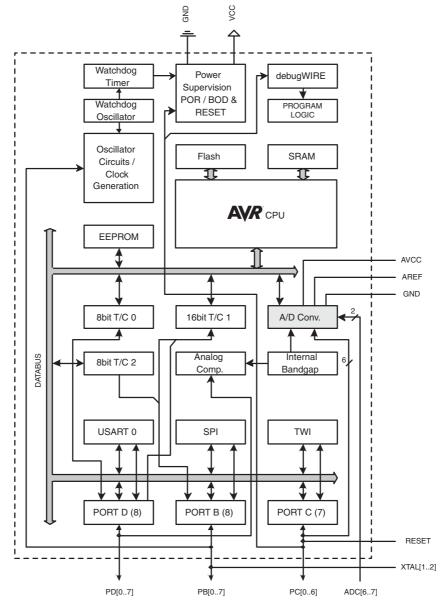

# 2.1 Block Diagram

Figure 2-1. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega48A/PA/88A/PA/168A/PA/328/P provides the following features: 4K/8Kbytes of In-System Programmable Flash with Read-While-Write capabilities, 256/512/512/1Kbytes EEPROM, 512/1K/1K/2Kbytes SRAM, 23 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte-oriented 2-wire Serial Interface, an SPI serial port, a 6-channel 10-bit ADC (8 channels in TQFP and QFN/MLF packages), a programmable Watchdog Timer with internal Oscillator, and five software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, USART, 2-wire Serial Interface, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or hardware reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption.

Atmel® offers the QTouch® library for embedding capacitive touch buttons, sliders and wheels functionality into AVR® microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys and includes Adjacent Key Suppression® (AKS™) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop and debug your own touch applications.

The device is manufactured using Atmel's high density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by a conventional non-volatile memory programmer, or by an On-chip Boot program running on the AVR core. The Boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega48A/PA/88A/PA/168A/PA/328/P is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega48A/PA/88A/PA/168A/PA/328/P AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, In-Circuit Emulators, and Evaluation kits.

## 2.2 Comparison Between Processors

The ATmega48A/PA/88A/PA/168A/PA/328/P differ only in memory sizes, boot loader support, and interrupt vector sizes. Table 2-1 summarizes the different memory and interrupt vector sizes for the devices.

Table 2-1. Memory Size Summary

| Device      | Flash    | EEPROM   | RAM      | Interrupt Vector Size      |

|-------------|----------|----------|----------|----------------------------|

| ATmega48A   | 4KBytes  | 256Bytes | 512Bytes | 1 instruction word/vector  |

| ATmega48PA  | 4KBytes  | 256Bytes | 512Bytes | 1 instruction word/vector  |

| ATmega88A   | 8KBytes  | 512Bytes | 1KBytes  | 1 instruction word/vector  |

| ATmega88PA  | 8KBytes  | 512Bytes | 1KBytes  | 1 instruction word/vector  |

| ATmega168A  | 16KBytes | 512Bytes | 1KBytes  | 2 instruction words/vector |

| ATmega168PA | 16KBytes | 512Bytes | 1KBytes  | 2 instruction words/vector |

| ATmega328   | 32KBytes | 1KBytes  | 2KBytes  | 2 instruction words/vector |

| ATmega328P  | 32KBytes | 1KBytes  | 2KBytes  | 2 instruction words/vector |

ATmega48A/PA/88A/PA/168A/PA/328/P support a real Read-While-Write Self-Programming mechanism. There is a separate Boot Loader Section, and the SPM instruction can only execute from there. In ATmega 48A/48PA there is no Read-While-Write support and no separate Boot Loader Section. The SPM instruction can execute from the entire Flash

# 3. Resources

A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr.

## 4. Data Retention

Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

# 5. About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

# 6. Capacitive Touch Sensing

The Atmel® QTouch® Library provides a simple to use solution to realize touch sensitive interfaces on most Atmel AVR® microcontrollers. The QTouch Library includes support for the Atmel QTouch and Atmel QMatrix® acquisition methods.

Touch sensing can be added to any application by linking the appropriate Atmel QTouch Library for the AVR Microcontroller. This is done by using a simple set of APIs to define the touch channels and sensors, and then calling the touch sensing APIs to retrieve the channel information and determine the touch sensor states.

The QTouch Library is FREE and downloadable from the Atmel website at the following location: www.atmel.com/qtouchlibrary. For implementation details and other information, refer to the Atmel QTouch Library User Guide - also available for download from Atmel website.

# 7. Register Summary

| Address          | Name                 | Bit 7   | Bit 6   | Bit 5  | Bit 4     | Bit 3            | Bit 2          | Bit 1              | Bit 0  | Page    |

|------------------|----------------------|---------|---------|--------|-----------|------------------|----------------|--------------------|--------|---------|

| (0xFF)           | Reserved             | _       | -       | _      | _         | -                | -              | -                  | _      |         |

| (0xFE)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xFD)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xFC)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xFB)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xFA)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xF9)           | Reserved             | _       | -       | -      | _         | -                | -              | _                  | _      |         |

| (0xF8)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xF7)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xF6)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xF5)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xF4)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xF3)           | Reserved             | _       | _       | _      | _         | -                | -              | _                  | _      |         |

| (0xF2)           | Reserved             | _       | -       | -      | _         | -                | -              | _                  | _      |         |

| (0xF1)           | Reserved             | -       | _       | -      | -         | _                | _              | _                  | -      |         |

| (0xF0)<br>(0xEF) | Reserved<br>Reserved | -       | _       | _      | -         | _                | _              | _                  | -      |         |

| (0xEF)           | Reserved             | _       | _       |        | _         | _                | _              | _                  |        |         |

| (0xED)           | Reserved             | _       | _       | _      |           | _                | _              |                    |        |         |

| (0xEC)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xEB)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xEA)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xE9)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xE8)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xE7)           | Reserved             | _       | -       | -      | _         | -                | -              | _                  | _      |         |

| (0xE6)           | Reserved             | _       | _       | _      | _         | _                | _              | -                  | _      |         |

| (0xE5)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xE4)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xE3)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xE2)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xE1)           | Reserved             | _       | _       | _      | _         | -                | -              | _                  | _      |         |

| (0xE0)           | Reserved             | _       | _       | -      | -         | _                | _              | _                  | -      |         |

| (0xDF)<br>(0xDE) | Reserved             | -       | -       | _      | -         | -                | -              | _                  | -      |         |

| (0xDE)           | Reserved<br>Reserved | _       |         |        |           |                  |                |                    |        |         |

| (0xDC)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xDB)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xDA)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xD9)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xD8)           | Reserved             | _       | -       | -      | _         | -                | -              | _                  | _      |         |

| (0xD7)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xD6)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xD5)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xD4)           | Reserved             | -       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xD3)           | Reserved             | _       | -       | -      | -         | -                | -              | -                  | -      |         |

| (0xD2)           | Reserved             | -       | -       | -      | _         | -                | -              | _                  | _      |         |

| (0xD1)           | Reserved             | _       | -       | -      | -         | -                | -              | _                  | -      |         |

| (0xD0)<br>(0xCF) | Reserved<br>Reserved | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xCF)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | -      |         |

| (0xCE)           | Reserved             | _       | _       | _      |           | _                | _              | _                  | _      |         |

| (0xCC)           | Reserved             | _       | _       | _      | _         | _                | _              | _                  | _      |         |

| (0xCB)           | Reserved             | -       | -       | -      | _         | -                | -              | _                  | _      |         |

| (0xCA)           | Reserved             | _       | _       | _      | -         | _                | _              | -                  | -      |         |

| (0xC9)           | Reserved             | -       | -       | -      | -         | -                | -              | _                  | -      |         |

| (0xC8)           | Reserved             | -       | -       | -      | -         | -                | -              | _                  | -      |         |

| (0xC7)           | Reserved             | -       | -       | -      | _         | -                | -              | _                  | _      |         |

| (0xC6)           | UDR0                 |         |         |        | USART I/O | Data Register    |                |                    |        | 191     |

| (0xC5)           | UBRR0H               |         |         |        |           |                  |                | Rate Register High | l      | 195     |

| (0xC4)           | UBRR0L               |         |         |        |           | ate Register Low |                |                    |        | 195     |

| (0xC3)           | Reserved             | -       | -       | -      | -         | -                | -              | _                  | -      |         |

| (0xC2)           | UCSR0C               | UMSEL01 | UMSEL00 | UPM01  | UPM00     | USBS0            | UCSZ01 /UDORD0 | UCSZ00 / UCPHA0    | UCPOL0 | 193/204 |

| (0xC1)           | UCSR0B               | RXCIE0  | TXCIE0  | UDRIE0 | RXEN0     | TXEN0            | UCSZ02         | RXB80              | TXB80  | 192     |

| Address          | Name                 | Bit 7           | Bit 6           | Bit 5          | Bit 4                                       | Bit 3             | Bit 2         | Bit 1          | Bit 0          | Page       |

|------------------|----------------------|-----------------|-----------------|----------------|---------------------------------------------|-------------------|---------------|----------------|----------------|------------|

| (0xC0)           | UCSR0A               | RXC0            | TXC0            | UDRE0          | FE0                                         | DOR0              | UPE0          | U2X0           | MPCM0          | 191        |

| (0xBF)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0xBE)           | Reserved             | -<br>TIA/ANAC   | -<br>T)A/AA45   | -<br>T10/0.044 | -<br>TA/ANA                                 | -<br>TIA/AAAO     | -<br>T)A/AA4  | -<br>TIA/ANAO  | _              | 000        |

| (0xBD)<br>(0xBC) | TWAMR<br>TWCR        | TWAM6<br>TWINT  | TWAM5<br>TWEA   | TWAM4<br>TWSTA | TWAM3<br>TWSTO                              | TWAM2<br>TWWC     | TWAM1<br>TWEN | TWAM0          | TWIE           | 233<br>230 |

| (0xBB)           | TWDR                 |                 |                 |                | 2-wire Serial Inte                          |                   |               |                |                | 232        |

| (0xBA)           | TWAR                 | TWA6            | TWA5            | TWA4           | TWA3                                        | TWA2              | TWA1          | TWA0           | TWGCE          | 232        |

| (0xB9)           | TWSR                 | TWS7            | TWS6            | TWS5           | TWS4                                        | TWS3              | _             | TWPS1          | TWPS0          | 231        |

| (0xB8)           | TWBR                 | _               |                 | _              | 2-wire Serial Interfa                       | ace Bit Rate Regi | ster _        | -              | _              | 230        |

| (0xB7)<br>(0xB6) | Reserved<br>ASSR     | _               | EXCLK           | AS2            | TCN2UB                                      | OCR2AUB           | OCR2BUB       | TCR2AUB        | TCR2BUB        | 158        |

| (0xB5)           | Reserved             | _               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0xB4)           | OCR2B                |                 |                 | Tir            | mer/Counter2 Outp                           | ut Compare Regis  | ster B        | •              |                | 157        |

| (0xB3)           | OCR2A                |                 |                 | Ti             | mer/Counter2 Outp                           |                   | ster A        |                |                | 157        |

| (0xB2)           | TCNT2                | EOC3A           | FOCAB           | _              | Timer/Cou                                   | inter2 (8-bit)    | Cenn          | C921           | C830           | 157<br>156 |

| (0xB1)<br>(0xB0) | TCCR2B<br>TCCR2A     | FOC2A<br>COM2A1 | FOC2B<br>COM2A0 | COM2B1         | COM2B0                                      | WGM22             | CS22          | CS21<br>WGM21  | CS20<br>WGM20  | 153        |

| (0xAF)           | Reserved             | -               | -               | -              | -                                           | _                 | _             | -              | -              |            |

| (0xAE)           | Reserved             | -               | _               | _              | _                                           | _                 | _             | -              | _              |            |

| (0xAD)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | _              |            |

| (0xAC)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | _              | -              |            |

| (0xAB)<br>(0xAA) | Reserved<br>Reserved | _               | _               | _              | -                                           | _                 | _             | _              | _              |            |

| (0xA9)           | Reserved             | _               | -               | -              | -                                           | _                 | -             | _              | _              |            |

| (0xA8)           | Reserved             | -               | -               | -              | _                                           | -                 | -             | -              | _              |            |

| (0xA7)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0xA6)           | Reserved             | -               | _               | -              | -                                           | -                 | _             | -              | _              |            |

| (0xA5)<br>(0xA4) | Reserved<br>Reserved | -               | _               | _              | -                                           | _                 | _             | _              | -              |            |

| (0xA3)           | Reserved             | _               | -               | _              | _                                           | _                 | -             | _              | _              |            |

| (0xA2)           | Reserved             | -               | _               | _              | -                                           | _                 | _             | -              | _              |            |

| (0xA1)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0xA0)           | Reserved             | -               | -               | -              | -                                           | -                 | _             | -              | -              |            |

| (0x9F)<br>(0x9E) | Reserved<br>Reserved | _               |                 |                |                                             |                   |               |                |                |            |

| (0x9D)           | Reserved             | _               | _               | _              | _                                           | _                 | _             | _              | _              |            |

| (0x9C)           | Reserved             | -               | _               | _              | -                                           | _                 | _             | -              | _              |            |

| (0x9B)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0x9A)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0x99)<br>(0x98) | Reserved<br>Reserved | -               | _               | _              | -                                           | _                 | _             | _              | -              |            |

| (0x97)           | Reserved             | _               | _               | _              | _                                           | _                 | _             | _              | _              |            |

| (0x96)           | Reserved             | -               | _               | _              | _                                           | _                 | _             | -              | _              |            |

| (0x95)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0x94)           | Reserved             | -               | _               | _              | -                                           | -                 | _             | -              | -              |            |

| (0x93)<br>(0x92) | Reserved<br>Reserved | _               | _               | _              | _                                           | _                 | _             | _              | -              |            |

| (0x91)           | Reserved             | _               | -               | -              | -                                           | _                 | -             | _              | _              |            |

| (0x90)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0x8F)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0x8E)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0x8D)<br>(0x8C) | Reserved<br>Reserved | _               | _               | _              | -                                           | _                 | _             | _              | _              |            |

| (0x8C)           | OCR1BH               |                 | _               |                | ounter1 - Output Co                         |                   |               | _              |                | 135        |

| (0x8A)           | OCR1BL               |                 |                 |                | ounter1 - Output Co                         |                   |               |                |                | 135        |

| (0x89)           | OCR1AH               |                 |                 |                | ounter1 - Output Co                         |                   |               |                |                | 135        |

| (0x88)           | OCR1AL               |                 |                 |                | ounter1 - Output Co                         |                   |               |                |                | 135        |

| (0x87)<br>(0x86) | ICR1H<br>ICR1L       |                 |                 |                | /Counter1 - Input C<br>r/Counter1 - Input C |                   |               |                |                | 135<br>135 |

| (0x85)           | TCNT1H               |                 |                 |                | ner/Counter1 - Input C                      | · · · · · ·       |               |                |                | 135        |

| (0x84)           | TCNT1L               |                 |                 |                | ner/Counter1 - Cou                          |                   |               |                |                | 134        |

| (0x83)           | Reserved             | -               | -               | -              | -                                           | -                 | -             | -              | -              |            |

| (0x82)           | TCCR1C               | FOC1A           | FOC1B           | -              | _                                           | -                 | -             | -              | -              | 134        |

| (0x81)           | TCCR1B               | ICNC1           | ICES1           | COM1P1         | WGM13                                       | WGM12             | CS12          | CS11           | CS10           | 133        |

| (0x80)<br>(0x7F) | TCCR1A<br>DIDR1      | COM1A1          | COM1A0          | COM1B1         | COM1B0                                      | _                 | -             | WGM11<br>AIN1D | WGM10<br>AIN0D | 131<br>236 |

| (0x7F)<br>(0x7E) | DIDR1                | _               | _               | ADC5D          | ADC4D                                       | ADC3D             | ADC2D         | ADC1D          | ADC0D          | 251        |

| (0x7D)           | Reserved             | _               | _               | -              | _                                           | -                 | _             | -              | _              |            |

| Address                                                                                                              | Name                                                 | Bit 7         | Bit 6                 | Bit 5                | Bit 4                                                         | Bit 3                                                                                   | Bit 2     | Bit 1         | Bit 0         | Page                       |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------|-----------------------|----------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------|---------------|---------------|----------------------------|

|                                                                                                                      |                                                      |               |                       |                      |                                                               |                                                                                         |           |               |               |                            |

| (0x7C)                                                                                                               | ADMUX                                                | REFS1         | REFS0                 | ADLAR                | -                                                             | MUX3                                                                                    | MUX2      | MUX1          | MUX0          | 248                        |

| (0x7B)                                                                                                               | ADCSRB                                               | -             | ACME                  | -                    | -                                                             | -                                                                                       | ADTS2     | ADTS1         | ADTS0         | 251                        |

| (0x7A)                                                                                                               | ADCSRA                                               | ADEN          | ADSC                  | ADATE                | ADORATA                                                       | ADIE                                                                                    | ADPS2     | ADPS1         | ADPS0         | 249                        |

| (0x79)                                                                                                               | ADCH<br>ADCL                                         |               |                       |                      | •                                                             | gister High byte                                                                        |           |               |               | 250                        |

| (0x78)<br>(0x77)                                                                                                     | Reserved                                             | _             | _                     | _                    | ADC Data Reg                                                  | gister Low byte<br>–                                                                    | _         | _             | _             | 250                        |

| (0x77)<br>(0x76)                                                                                                     | Reserved                                             |               | _                     | _                    | _                                                             |                                                                                         | _         |               | _             |                            |

| (0x75)                                                                                                               | Reserved                                             |               | _                     | _                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x74)                                                                                                               | Reserved                                             | _             | _                     | _                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x73)                                                                                                               | Reserved                                             | _             | _                     | _                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x72)                                                                                                               | Reserved                                             | _             | _                     | _                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x71)                                                                                                               | Reserved                                             | _             | _                     | _                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x70)                                                                                                               | TIMSK2                                               | _             | _                     | _                    | _                                                             | _                                                                                       | OCIE2B    | OCIE2A        | TOIE2         | 157                        |

| (0x6F)                                                                                                               | TIMSK1                                               | _             | _                     | ICIE1                | _                                                             | _                                                                                       | OCIE1B    | OCIE1A        | TOIE1         | 135                        |

| (0x6E)                                                                                                               | TIMSK0                                               | _             | _                     | _                    | _                                                             | _                                                                                       | OCIE0B    | OCIE0A        | TOIE0         | 109                        |

| (0x6D)                                                                                                               | PCMSK2                                               | PCINT23       | PCINT22               | PCINT21              | PCINT20                                                       | PCINT19                                                                                 | PCINT18   | PCINT17       | PCINT16       | 74                         |

| (0x6C)                                                                                                               | PCMSK1                                               | _             | PCINT14               | PCINT13              | PCINT12                                                       | PCINT11                                                                                 | PCINT10   | PCINT9        | PCINT8        | 74                         |

| (0x6B)                                                                                                               | PCMSK0                                               | PCINT7        | PCINT6                | PCINT5               | PCINT4                                                        | PCINT3                                                                                  | PCINT2    | PCINT1        | PCINT0        | 74                         |

| (0x6A)                                                                                                               | Reserved                                             | _             | _                     | _                    | -                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x69)                                                                                                               | EICRA                                                | -             | -                     | -                    | -                                                             | ISC11                                                                                   | ISC10     | ISC01         | ISC00         | 71                         |

| (0x68)                                                                                                               | PCICR                                                | -             | -                     | -                    | -                                                             | _                                                                                       | PCIE2     | PCIE1         | PCIE0         |                            |

| (0x67)                                                                                                               | Reserved                                             | -             | -                     | -                    | -                                                             | -                                                                                       | _         | -             | _             |                            |

| (0x66)                                                                                                               | OSCCAL                                               |               |                       |                      | Oscillator Calib                                              | oration Register                                                                        |           |               |               | 37                         |

| (0x65)                                                                                                               | Reserved                                             | -             | _                     | _                    | -                                                             |                                                                                         | _         | _             | _             |                            |

| (0x64)                                                                                                               | PRR                                                  | PRTWI         | PRTIM2                | PRTIM0               | -                                                             | PRTIM1                                                                                  | PRSPI     | PRUSART0      | PRADC         | 42                         |

| (0x63)                                                                                                               | Reserved                                             | _             | _                     | _                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x62)                                                                                                               | Reserved                                             | _             | _                     | _                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| (0x61)                                                                                                               | CLKPR                                                | CLKPCE        | _                     | _                    | -                                                             | CLKPS3                                                                                  | CLKPS2    | CLKPS1        | CLKPS0        | 37                         |

| (0x60)                                                                                                               | WDTCSR                                               | WDIF          | WDIE                  | WDP3                 | WDCE                                                          | WDE                                                                                     | WDP2      | WDP1          | WDP0          | 54                         |

| 0x3F (0x5F)                                                                                                          | SREG                                                 | I             | Т                     | Н                    | S                                                             | V                                                                                       | N         | Z             | С             | 10                         |

| 0x3E (0x5E)                                                                                                          | SPH                                                  | _             | _                     | _                    | -                                                             | _                                                                                       | (SP10) 5. | SP9           | SP8           | 13                         |

| 0x3D (0x5D)                                                                                                          | SPL                                                  | SP7           | SP6                   | SP5                  | SP4                                                           | SP3                                                                                     | SP2       | SP1           | SP0           | 13                         |

| 0x3C (0x5C)                                                                                                          | Reserved                                             | -             | _                     | _                    | _                                                             | _                                                                                       | _         | -             | _             |                            |

| 0x3B (0x5B)                                                                                                          | Reserved                                             | -             | -                     | -                    | -                                                             | -                                                                                       | _         | -             | _             |                            |

| 0x3A (0x5A)                                                                                                          | Reserved                                             | -             | -                     | -                    | -                                                             | -                                                                                       | -         | -             | -             |                            |

| 0x39 (0x59)                                                                                                          | Reserved                                             | -             | -                     | -                    | -                                                             | -                                                                                       | -         | -             | _             |                            |

| 0x38 (0x58)                                                                                                          | Reserved                                             | -             | -                     | -                    | -                                                             | -                                                                                       | -         | -             | -             |                            |

| 0x37 (0x57)                                                                                                          | SPMCSR                                               | SPMIE         | (RWWSB) <sup>5.</sup> | SIGRD                | (RWWSRE)5.                                                    | BLBSET                                                                                  | PGWRT     | PGERS         | SPMEN         | 278                        |

| 0x36 (0x56)                                                                                                          | Reserved                                             | -             | _                     | -                    | _                                                             | _                                                                                       | _         | -             | _             |                            |

| 0x35 (0x55)                                                                                                          | MCUCR                                                | -             | BODS <sup>(6)</sup>   | BODSE <sup>(6)</sup> | PUD                                                           | _                                                                                       | -         | IVSEL         | IVCE          | 45/68/91                   |

| 0x34 (0x54)                                                                                                          | MCUSR                                                | -             | -                     | -                    | -                                                             | WDRF                                                                                    | BORF      | EXTRF         | PORF          | 54                         |

| 0x33 (0x53)                                                                                                          | SMCR                                                 | -             | -                     | -                    | -                                                             | SM2                                                                                     | SM1       | SM0           | SE            | 40                         |

| 0x32 (0x52)                                                                                                          | Reserved                                             | -             | _                     | -                    | _                                                             | _                                                                                       | _         | _             | _             |                            |

| 0x31 (0x51)                                                                                                          | Reserved                                             | -             | -                     | -                    | -                                                             | -                                                                                       | -         | -             | -             |                            |

| 0x30 (0x50)                                                                                                          | ACSR                                                 | ACD           | ACBG                  | ACO                  | ACI                                                           | ACIE                                                                                    | ACIC      | ACIS1         | ACIS0         | 235                        |

| 0x2F (0x4F)                                                                                                          | Reserved                                             | -             | -                     | -                    | -                                                             | -                                                                                       | -         | -             | _             |                            |

| 0x2E (0x4E)                                                                                                          | SPDR                                                 |               | _                     |                      | SPI Data                                                      | Register                                                                                |           |               |               | 169                        |

| 0x2D (0x4D)                                                                                                          | SPSR                                                 | SPIF          | WCOL                  | -                    | -                                                             | -                                                                                       | -         | -             | SPI2X         | 168                        |

| 0x2C (0x4C)                                                                                                          | SPCR                                                 | SPIE          | SPE                   | DORD                 | MSTR                                                          | CPOL                                                                                    | CPHA      | SPR1          | SPR0          | 167                        |

| 0x2B (0x4B)                                                                                                          | GPIOR2                                               |               |                       |                      | General Purpos                                                | se I/O Register 2                                                                       |           |               |               | 26                         |

| 0x2A (0x4A)                                                                                                          | GPIOR1                                               |               |                       |                      | General Purpos                                                | se I/O Register 1                                                                       |           |               |               | 26                         |

| 0x29 (0x49)                                                                                                          | Reserved                                             | -             | _                     | -                    | -                                                             | -                                                                                       | _         | -             | -             |                            |

| 0x28 (0x48)                                                                                                          | OCR0B                                                |               |                       |                      | mer/Counter0 Outpo                                            |                                                                                         |           |               |               |                            |

| 0x27 (0x47)                                                                                                          | OCR0A                                                |               |                       | Tir                  | mer/Counter0 Outpo                                            | ut Compare Regi                                                                         | ster A    |               |               |                            |

| 0x26 (0x46)                                                                                                          | TCNT0                                                |               | 1                     |                      | Timer/Cou                                                     | nter0 (8-bit)                                                                           | 1         | 1             | ,             |                            |

| 0x25 (0x45)                                                                                                          | TCCDOD                                               | FOC0A         | FOC0B                 | -                    | -                                                             | WGM02                                                                                   | CS02      | CS01          | CS00          |                            |

|                                                                                                                      | TCCR0B                                               |               | 0011010               | COM0B1               | COM0B0                                                        | -                                                                                       | -         | WGM01         | WGM00         |                            |

| 0x24 (0x44)                                                                                                          | TCCR0A                                               | COM0A1        | COM0A0                |                      |                                                               | _                                                                                       | _         | PSRASY        | PSRSYNC       | 140/159                    |

| 0x23 (0x43)                                                                                                          | TCCR0A<br>GTCCR                                      | COM0A1<br>TSM | - COMUAU              | -                    | -                                                             |                                                                                         | _         |               |               |                            |

| 0x23 (0x43)<br>0x22 (0x42)                                                                                           | TCCR0A<br>GTCCR<br>EEARH                             |               |                       |                      | EEPROM Address I                                              | L<br>Register High Byt                                                                  | -         |               |               | 22                         |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)                                                                            | TCCR0A<br>GTCCR<br>EEARH<br>EEARL                    |               |                       |                      | EEPROM Address I<br>EEPROM Address                            | r<br>Register High Byt<br>Register Low By                                               | -         |               |               | 22                         |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)<br>0x20 (0x40)                                                             | TCCR0A<br>GTCCR<br>EEARH<br>EEARL<br>EEDR            |               |                       | (I                   | EEPROM Address I<br>EEPROM Address<br>EEPROM D                | Register High Byt<br>Register Low By<br>Pata Register                                   | rte       |               |               | 22<br>22                   |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)                                              | TCCR0A GTCCR EEARH EEARL EEDR EECR                   |               |                       |                      | EEPROM Address I EEPROM Address EEPROM D EEPM0                | Register High Byt<br>Register Low By<br>lata Register<br>EERIE                          | -         | EEPE          | EERE          | 22                         |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)<br>0x20 (0x40)                                                             | TCCR0A<br>GTCCR<br>EEARH<br>EEARL<br>EEDR            | TSM           | -                     | (I                   | EEPROM Address I EEPROM Address EEPROM D EEPM0                | Register High Byt<br>Register Low By<br>Pata Register                                   | rte       | EEPE          | EERE          | 22<br>22                   |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)                                              | TCCR0A GTCCR EEARH EEARL EEDR EECR                   | TSM           | -                     | (I                   | EEPROM Address I EEPROM Address EEPROM D EEPM0                | Register High Byt<br>Register Low By<br>lata Register<br>EERIE                          | rte       | EEPE<br>INT1  | EERE INTO     | 22<br>22<br>22             |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)<br>0x1E (0x3E)                               | TCCR0A GTCCR EEARH EEARL EEDR EECR GPIOR0            | TSM<br>-      | -                     | (I<br>EEPM1          | EEPROM Address I EEPROM Address EEPROM D EEPM0 General Purpos | Register High Byt<br>Register Low Byteta Register<br>EERIE<br>EE I/O Register 0         | EEMPE     | ·<br>·        |               | 22<br>22<br>22<br>26       |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)<br>0x1E (0x3E)<br>0x1D (0x3D)                | TCCR0A GTCCR EEARH EEARL EEDR EECR GPIOR0 EIMSK      | TSM<br>-<br>- | -                     | (I<br>EEPM1          | EEPROM Address I EEPROM Address EEPROM D EEPMO General Purpos | Register High Byts Register Low Byts Retar Register EERIE See I/O Register 0            | EEMPE -   | INT1          | INT0          | 22<br>22<br>22<br>26<br>72 |

| 0x23 (0x43)<br>0x22 (0x42)<br>0x21 (0x41)<br>0x20 (0x40)<br>0x1F (0x3F)<br>0x1E (0x3E)<br>0x1D (0x3D)<br>0x1C (0x3C) | TCCR0A GTCCR EEARH EEARL EEDR EECR GPIOR0 EIMSK EIFR |               | -                     | (I<br>EEPM1          | EEPROM Address I EEPROM Address EEPROM D EEPMO General Purpos | Register High Byte Register Low Byte Register Low Byte Register EERIE Re I/O Register 0 | EEMPE -   | INT1<br>INTF1 | INTO<br>INTFO | 22<br>22<br>22<br>26<br>72 |

| Address     | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Page |

|-------------|----------|--------|--------|--------|--------|--------|--------|--------|--------|------|

| 0x18 (0x38) | Reserved | _      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x17 (0x37) | TIFR2    | -      | -      | -      | -      | -      | OCF2B  | OCF2A  | TOV2   | 158  |

| 0x16 (0x36) | TIFR1    | -      | -      | ICF1   | -      | -      | OCF1B  | OCF1A  | TOV1   | 136  |

| 0x15 (0x35) | TIFR0    | _      | _      | _      | _      | _      | OCF0B  | OCF0A  | TOV0   |      |

| 0x14 (0x34) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x13 (0x33) | Reserved | 1      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x12 (0x32) | Reserved | _      | _      | _      | _      | _      | _      | _      | -      |      |

| 0x11 (0x31) | Reserved | -      | -      | _      | _      | -      | -      | _      | -      |      |

| 0x10 (0x30) | Reserved | 1      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0F (0x2F) | Reserved | _      | _      | _      | _      | _      | _      | _      | -      |      |

| 0x0E (0x2E) | Reserved | -      | -      | _      | _      | -      | -      | _      | -      |      |

| 0x0D (0x2D) | Reserved | _      | -      | -      | -      | _      | -      | _      | -      |      |

| 0x0C (0x2C) | Reserved | -      | _      | _      | _      | -      | _      | _      | -      |      |

| 0x0B (0x2B) | PORTD    | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | 92   |

| 0x0A (0x2A) | DDRD     | DDD7   | DDD6   | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | 92   |

| 0x09 (0x29) | PIND     | PIND7  | PIND6  | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  | 92   |

| 0x08 (0x28) | PORTC    | _      | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | 91   |

| 0x07 (0x27) | DDRC     | _      | DDC6   | DDC5   | DDC4   | DDC3   | DDC2   | DDC1   | DDC0   | 91   |

| 0x06 (0x26) | PINC     | _      | PINC6  | PINC5  | PINC4  | PINC3  | PINC2  | PINC1  | PINC0  | 92   |

| 0x05 (0x25) | PORTB    | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | 91   |

| 0x04 (0x24) | DDRB     | DDB7   | DDB6   | DDB5   | DDB4   | DDB3   | DDB2   | DDB1   | DDB0   | 91   |

| 0x03 (0x23) | PINB     | PINB7  | PINB6  | PINB5  | PINB4  | PINB3  | PINB2  | PINB1  | PINB0  | 91   |

| 0x02 (0x22) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x01 (0x21) | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

| 0x0 (0x20)  | Reserved | -      | -      | -      | -      | -      | -      | -      | -      |      |

- 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O Registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the Status Flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such Status Flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega48A/PA/88A/PA/168A/PA/328/P is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- 5. Only valid for ATmega88A/88PA/168A/168PA/328/328P.

- 6. BODS and BODSE only available for picoPower devices ATmega48PA/88PA/168PA/328P

# 8. Instruction Set Summary

| Mnemonics           | Operands          | Description                              | Operation                                             | Flags          | #Clocks    |

|---------------------|-------------------|------------------------------------------|-------------------------------------------------------|----------------|------------|

| ARITHMETIC AND L    | OGIC INSTRUCTIONS | · · · · · · · · · · · · · · · · · · ·    |                                                       |                |            |

| ADD                 | Rd, Rr            | Add two Registers                        | $Rd \leftarrow Rd + Rr$                               | Z,C,N,V,H      | 1          |

| ADC                 | Rd, Rr            | Add with Carry two Registers             | $Rd \leftarrow Rd + Rr + C$                           | Z,C,N,V,H      | 1          |

| ADIW                | RdI,K             | Add Immediate to Word                    | Rdh:Rdl ← Rdh:Rdl + K                                 | Z,C,N,V,S      | 2          |

| SUB                 | Rd, Rr            | Subtract two Registers                   | Rd ← Rd - Rr                                          | Z,C,N,V,H      | 1          |

| SUBI                | Rd, K             | Subtract Constant from Register          | Rd ← Rd - K                                           | Z,C,N,V,H      | 1          |

| SBC                 | Rd, Rr            | Subtract with Carry two Registers        | Rd ← Rd - Rr - C                                      | Z,C,N,V,H      | 1          |

| SBCI                | Rd, K             | Subtract with Carry Constant from Reg.   | Rd ← Rd - K - C                                       | Z,C,N,V,H      | 1          |

| SBIW                | RdI,K             | Subtract Immediate from Word             | Rdh:Rdl ← Rdh:Rdl - K                                 | Z,C,N,V,S      | 2          |

| AND                 | Rd, Rr            | Logical AND Registers                    | Rd ← Rd • Rr                                          | Z,N,V          | 1          |

| ANDI                | Rd, K             | Logical AND Register and Constant        | Rd ← Rd • K                                           | Z,N,V          | 1          |

| OR                  | Rd, Rr            | Logical OR Registers                     | Rd ← Rd v Rr                                          | Z,N,V          | 1          |

| ORI                 | Rd, K             | Logical OR Register and Constant         | Rd ← Rd v K                                           | Z,N,V          | 1          |

| EOR                 | Rd, Rr            | Exclusive OR Registers                   | $Rd \leftarrow Rd \oplus Rr$                          | Z,N,V          | 1          |

| COM                 | Rd                | One's Complement                         | Rd ← 0xFF – Rd                                        | Z,C,N,V        | 1          |

| NEG                 | Rd                | Two's Complement                         | $Rd \leftarrow 0x00 - Rd$                             | Z,C,N,V,H      | 1          |

| SBR                 | Rd,K              | Set Bit(s) in Register                   | Rd ← Rd v K                                           | Z,N,V          | 1          |

| CBR                 | Rd,K              | Clear Bit(s) in Register                 | $Rd \leftarrow Rd \bullet (0xFF - K)$                 | Z,N,V          | 1          |

| INC                 | Rd                | Increment                                | Rd ← Rd + 1                                           | Z,N,V          | 1          |

| DEC                 | Rd                | Decrement Decrement                      | Rd ← Rd + 1<br>Rd ← Rd − 1                            | Z,N,V<br>Z,N,V | 1          |

|                     |                   |                                          |                                                       |                |            |

| TST                 | Rd                | Test for Zero or Minus                   | $Rd \leftarrow Rd \bullet Rd$                         | Z,N,V          | 1          |

| CLR                 | Rd                | Clear Register                           | Rd ← Rd ⊕ Rd                                          | Z,N,V          | 1          |