# Ultralow Input Bias Current Operational Amplifier

Data Sheet AD549

### **FEATURES**

Ultralow input bias current

60 fA maximum (AD549L)

100 fA maximum (AD549K)

250 fA maximum (AD549J)

Input bias current guaranteed over the common-mode voltage range

Low offset voltage

0.50 mV maximum (AD549K)

1.00 mV maximum (AD549J)

Low offset drift

15 μV/°C maximum (AD549K)

20 μV/°C maximum (AD549J)

Low power

700 µA maximum supply current

Low input voltage noise

4 μV (typ) p-p over 0.1 Hz to 10 Hz

MIL-STD-883B parts available

### **APPLICATIONS**

Electrometer amplifier Photodiode preamp pH electrode buffer

### **GENERAL DESCRIPTION**

The AD549 is a monolithic electrometer operational amplifier with very low input bias current. Input offset voltage and input offset voltage drift are laser trimmed for precision performance. The ultralow input current of the part is achieved with Topgate IFET technology, a process development exclusive to Analog Devices, Inc. This technology allows fabrication of extremely low input current JFETs compatible with a standard junction isolated bipolar process. The  $10^{15}\,\Omega$  common-mode impedance, which results from the bootstrapped input stage, ensures that the input current is essentially independent of the common-mode voltage.

The AD549 is suited for applications requiring very low input current and low input offset voltage. It excels as a preamp for a wide variety of current output transducers, such as photodiodes, photomultiplier tubes, or oxygen sensors. The AD549 can also be used as a precision integrator or low droop sample-and-hold. The AD549 is pin compatible with standard FET and electrometer op amps, allowing designers to upgrade the performance of present systems at little additional cost.

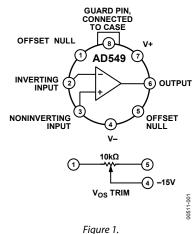

The AD549 is available in a TO-99 hermetic package. The case is connected to Pin 8, thus, the metal case can be independently

Rev. K

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

### **CONNECTION DIAGRAM**

connected to a point at the same potential as the input terminals, minimizing stray leakage to the case. The AD549 is available in four performance grades. The J, K, and L versions are rated over the commercial temperature range of  $0^{\circ}$ C to  $+70^{\circ}$ C. The S grade is specified over the military temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C and is available processed to MIL-STD-883B, Rev. C. Extended reliability plus screening is also available. Plus screening includes 168 hour burn-in, as well as other environmental and physical tests derived from MIL-STD-883B, Rev. C.

### **PRODUCT HIGHLIGHTS**

- The AD549 input currents are specified, 100% tested, and guaranteed after the device is warmed up. They are guaranteed over the entire common-mode input voltage range.

- 2. The AD549 input offset voltage and drift are laser trimmed to 0.50 mV and 15  $\mu$ V/°C (AD549K), and to 1 mV and 20  $\mu$ V/°C (AD549J).

- 3. A maximum quiescent supply current of 700 μA minimizes heating effects on input current and offset voltage.

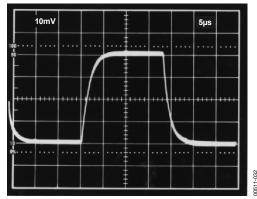

- 4. AC specifications include 1 MHz unity-gain bandwidth and 3 V/ $\mu$ s slew rate. Settling time for a 10 V input step is 5  $\mu$ s to 0.01%.

| TABLE OF CONTENTS                                           |                                                    |          |

|-------------------------------------------------------------|----------------------------------------------------|----------|

| Features1                                                   | Offset Nulling                                     | 1        |

| Applications1                                               | AC Response with High Value Source and Feedback    |          |

| Connection Diagram1                                         | Resistance                                         | 12       |

| General Description1                                        | Common-Mode Input Voltage Overload                 | 12       |

| Product Highlights 1                                        | Differential Input Voltage Overload                | 13       |

| Revision History                                            | Input Protection                                   | 13       |

| Specifications                                              | Sample-and-Difference Circuit to Measure Electrome | eter     |

| Absolute Maximum Ratings                                    | Leakage Currents                                   | 13       |

| ESD Caution                                                 | Photodiode Interface                               | 14       |

|                                                             | Log Ratio Amplifier                                | 15       |

| Typical Performance Characteristics                         | Temperature Compensated pH Probe Amplifier         | 16       |

| Functional Description                                      | Outline Dimensions                                 |          |

| Minimizing Input Current                                    | Ordering Guide                                     |          |

| Circuit Board Notes                                         | 0 0                                                |          |

| REVISION HISTORY                                            |                                                    |          |

| 2/15—Rev. J to Rev. K                                       | 7/07—Rev. F to Rev. G                              |          |

| Updated Outline Dimensions                                  | Changes to Figure 45                               | 16       |

| 12/14—Rev. I to Rev. J                                      | Changes to Temperature Compensated pH Probe        | 1.5      |

| Added L ModelUniversal                                      | Amplifier Section                                  |          |

| Changes to Features Section and Applications Section 1      | Changes to Ordering Guide                          |          |

| Changes to Table 1                                          | 5/06—Rev. E to Rev. F                              |          |

| Changes to Table 2                                          |                                                    | ,        |

| Changes to Log Ratio Amplifier Section                      | Removed ESD Caution                                |          |

| Amplifier Section                                           | 8/05—Rev. D to Rev. E                              |          |

| Changes to Ordering Guide                                   | Change to Figure 22                                |          |

| 6/14—Rev. H to Rev. I                                       | 5/04—Rev. C to Rev. D                              |          |

| Deleted L ModelThroughout                                   | Updated FormatU                                    | Jniversa |

| Change to Features Section                                  | Changes to Features                                |          |

| Changes to Input Offset Voltage Parameter and Input Voltage | Updated Outline Dimensions                         |          |

| Noise Parameter, Table 1                                    | Added Ordering Guide                               | 18       |

| Changes to Ordering Guide                                   | 10/02—Rev. B to Rev. C                             |          |

| 3/08—Rev. G to Rev. H                                       | Deleted Product Highlights #5                      | ]        |

| Changes to Features                                         | Edits to Specifications                            |          |

| Changes to Figure 1                                         | Deleted Metallization Photograph                   | 3        |

| Deleted Package Option Parameter                            | Updated Outline Dimensions                         | 13       |

| Inserted ESD Caution                                        | 7/02—Rev. A to Rev. B                              |          |

| Changes to Figure 2, Figure 3, and Figure 7                 |                                                    | ,        |

| Changes to Figure 11                                        | Edits to Specifications                            |          |

| Changes to Figure 17                                        |                                                    |          |

| Changes to Figure 41                                        |                                                    |          |

## **SPECIFICATIONS**

At 25°C and  $V_S = \pm 15$  V dc, unless otherwise noted; all minimum and maximum specifications are guaranteed; specifications in **boldface** are tested on all production units at final electrical test, and results from those tests are used to calculate outgoing quality levels.

Table 1.

|                                                                                                             |     | AD549J    |     |     | AD549K    |     |     | AD549L    |     |     | AD549S    |     |          |

|-------------------------------------------------------------------------------------------------------------|-----|-----------|-----|-----|-----------|-----|-----|-----------|-----|-----|-----------|-----|----------|

| Parameter                                                                                                   | Min | Тур       | Max | Unit     |

| INPUT BIAS CURRENT <sup>1</sup>                                                                             |     |           |     |     |           |     |     |           |     |     |           |     |          |

| Either Input, $V_{CM} = 0 \text{ V}$                                                                        |     | 150       | 250 |     | 75        | 100 |     | 40        | 60  |     | 75        | 100 | fA       |

| Either Input, $V_{CM} = \pm 10 \text{ V}$                                                                   |     | 150       | 250 |     | 75        | 100 |     | 40        | 60  |     | 75        | 100 | fA       |

| Either Input at $T_{MAX}$ , $V_{CM} = 0 \text{ V}$                                                          |     | 11        |     |     | 4.2       |     |     | 2.8       |     |     | 420       |     | pA       |

| Offset Current                                                                                              |     | 50        |     |     | 30        |     |     | 20        |     |     | 30        |     | fA       |

| Offset Current at T <sub>MAX</sub>                                                                          |     | 2.2       |     |     | 1.3       |     |     | 0.85      |     |     | 125       |     | рА       |

| INPUT OFFSET VOLTAGE <sup>2</sup>                                                                           |     |           |     |     |           |     |     |           |     |     |           |     |          |

| Initial Offset                                                                                              |     | 0.5       | 1.0 |     | 0.15      | 0.5 |     | 0.3       | 0.5 |     | 0.3       | 0.5 | mV       |

| Offset at T <sub>MAX</sub>                                                                                  |     |           | 1.9 |     |           | 0.9 |     |           | 0.9 |     |           | 2.0 | mV       |

| vs. Temperature                                                                                             |     | 10        | 20  |     | 10        | 15  |     | 5         | 10  |     | 10        | 15  | μV/°C    |

| vs. Supply                                                                                                  |     | 32        | 100 |     | 10        | 32  |     | 10        | 32  |     | 10        | 32  | μV/V     |

| vs. Supply, $T_{MIN}$ to $T_{MAX}$                                                                          |     | 32        | 100 |     | 10        | 32  |     | 10        | 32  |     | 32        | 50  | μV/V     |

| Long-Term Offset Stability                                                                                  |     | 15        |     |     | 15        |     |     | 15        |     |     | 15        |     | μV/month |

| INPUT VOLTAGE NOISE                                                                                         |     |           |     |     |           |     |     |           |     |     |           |     |          |

| f = 0.1 Hz to 10 Hz                                                                                         |     | 4         |     |     | 4         | 6   |     | 4         |     |     | 4         |     | μV p-p   |

| f = 10 Hz                                                                                                   |     | 90        |     |     | 90        |     |     | 90        |     |     | 90        |     | nV/√Hz   |

| f = 100 Hz                                                                                                  |     | 60        |     |     | 60        |     |     | 60        |     |     | 60        |     | nV/√Hz   |

| f = 1 kHz                                                                                                   |     | 35        |     |     | 35        |     |     | 35        |     |     | 35        |     | nV/√Hz   |

| f = 10 kHz                                                                                                  |     | 35        |     |     | 35        |     |     | 35        |     |     | 35        |     | nV/√Hz   |

| INPUT CURRENT NOISE                                                                                         |     |           |     |     |           |     |     |           |     |     |           |     |          |

| f = 0.1 Hz to 10 Hz                                                                                         |     | 0.7       |     |     | 0.5       |     |     | 0.36      |     |     | 0.5       |     | fA rms   |

| f = 1 kHz                                                                                                   |     | 0.22      |     |     | 0.16      |     |     | 0.11      |     |     | 0.16      |     | fA/√Hz   |

| INPUT IMPEDANCE                                                                                             |     |           |     |     |           |     |     |           |     |     |           |     |          |

| Differential                                                                                                |     |           |     |     |           |     |     |           |     |     |           |     |          |

| $V_{\text{DIFF}} = \pm 1$                                                                                   |     | 1013  1   |     |     | 1013  1   |     |     | 1013  1   |     |     | 1013  1   |     | Ω  pF    |

| Common Mode                                                                                                 |     | - 11      |     |     | - 11      |     |     | - 11      |     |     | - 11      |     | 1111     |

| $V_{CM} = \pm 10 \text{ V}$                                                                                 |     | 1015  0.8 |     |     | 1015  0.8 |     |     | 1015  0.8 |     |     | 1015  0.8 |     | Ω  pF    |

| OPEN-LOOP GAIN                                                                                              |     | 1111111   |     |     |           |     |     | - 11      |     |     | 1111111   |     | 1111     |

| $V_{OUT}$ at $\pm 10$ V, $R_L = 10$ k $\Omega$                                                              | 300 | 1000      |     | 300 | 1000      |     | 300 | 1000      |     | 300 | 1000      |     | V/mV     |

| $V_{OUT}$ at $\pm 10$ V, $R_L = 10$ k $\Omega$ , $T_{MIN}$ to $T_{MAX}$                                     | 300 | 800       |     | 300 | 800       |     | 300 | 800       |     | 300 | 800       |     | V/mV     |

| $V_{OUT} = \pm 10 \text{ V}, R_L = 2 \text{ k}\Omega$                                                       | 100 | 250       |     | 100 | 250       |     | 100 | 250       |     | 100 | 250       |     | V/mV     |

| $V_{\text{OUT}} = \pm 10 \text{ V}, R_{\text{L}} = 2 \text{ k}\Omega,$ $T_{\text{MIN}}$ to $T_{\text{MAX}}$ | 80  | 200       |     | 80  | 200       |     | 80  | 200       |     | 25  | 150       |     | V/mV     |

| INPUT VOLTAGE RANGE                                                                                         |     |           |     |     |           |     |     |           |     |     |           |     |          |

| Differential <sup>3</sup>                                                                                   |     |           | ±20 |     |           | ±20 |     |           | ±20 |     |           | ±20 | V        |

| Common-Mode Voltage                                                                                         | -10 |           | +10 | -10 |           | +10 | -10 |           | +10 | -10 |           | +10 | V        |

| Common-Mode Rejection<br>Ratio                                                                              |     |           |     |     |           |     |     |           |     |     |           |     |          |

| $-10~V \leq V_{CM} \leq +10~V$                                                                              | 80  | 90        |     | 90  | 100       |     | 90  | 100       |     | 90  | 100       |     | dB       |

| $T_{MIN}$ to $T_{MAX}$                                                                                      | 76  | 80        |     | 80  | 90        |     | 80  | 90        |     | 80  | 90        |     | dB       |

| OUTPUT CHARACTERISTICS                                                                                      |     |           |     |     |           |     |     |           |     |     |           |     |          |

| $V_{OUT}$ at $R_L = 10 \text{ k}\Omega$ , $T_{MIN}$ to $T_{MAX}$                                            | -12 |           | +12 | -12 |           | +12 | -12 |           | +12 | -12 |           | +12 | V        |

| $V_{OUT}$ at $R_L = 2 k\Omega$ , $T_{MIN}$ to $T_{MAX}$                                                     | -10 |           | +10 | -10 |           | +10 | -10 |           | +10 | -10 |           | +10 | ٧        |

| Short-Circuit Current                                                                                       | 15  | 20        | 35  | 15  | 20        | 35  | 15  | 20        | 35  | 15  | 20        | 35  | mA       |

| T <sub>MIN</sub> to T <sub>MAX</sub>                                                                        | 9   |           |     | 9   |           |     | 9   |           |     | 6   |           |     | mA       |

| Load Capacitance Stability,                                                                                 |     | 4000      |     |     | 4000      |     |     | 4000      |     |     | 4000      |     | pF       |

Rev. K | Page 3 of 18

|                                               |     | AD549. | J    |     | AD549 | K    |     | AD549 | L    |     | AD549 | S    |      |

|-----------------------------------------------|-----|--------|------|-----|-------|------|-----|-------|------|-----|-------|------|------|

| Parameter                                     | Min | Тур    | Max  | Min | Тур   | Max  | Min | Тур   | Max  | Min | Тур   | Max  | Unit |

| FREQUENCY RESPONSE                            |     |        |      |     |       |      |     |       |      |     |       |      |      |

| Unity Gain, Small Signal                      | 0.7 | 1.0    |      | 0.7 | 1.0   |      | 0.7 | 1.0   |      | 0.7 | 1.0   |      | MHz  |

| Full Power Response                           |     | 50     |      |     | 50    |      |     | 50    |      |     | 50    |      | kHz  |

| Slew Rate                                     | 2   | 3      |      | 2   | 3     |      | 2   | 3     |      | 2   | 3     |      | V/µs |

| Settling Time, 0.1%                           |     | 4.5    |      |     | 4.5   |      |     | 4.5   |      |     | 4.5   |      | μs   |

| Settling Time, 0.01%                          |     | 5      |      |     | 5     |      |     | 5     |      |     | 5     |      | μs   |

| Overload Recovery, 50%<br>Overdrive, $G = -1$ |     | 2      |      |     | 2     |      |     | 2     |      |     | 2     |      | μs   |

| POWER SUPPLY                                  |     |        |      |     |       |      |     |       |      |     |       |      |      |

| Rated Performance                             |     | ±15    |      |     | ±15   |      |     | ±15   |      |     | ±15   |      | V    |

| Operating                                     | ±5  |        | ±18  | ±5  |       | ±18  | ±5  |       | ±18  | ±5  |       | ±18  | ٧    |

| Quiescent Current                             |     | 0.60   | 0.70 |     | 0.60  | 0.70 |     | 0.60  | 0.70 |     | 0.60  | 0.70 | mA   |

| TEMPERATURE RANGE                             |     |        |      |     |       |      |     |       |      |     |       |      |      |

| Operating, Rated<br>Performance               | 0   |        | 70   | 0   |       | 70   | 0   |       | 70   | -55 |       | +125 | °C   |

| Storage                                       | -65 |        | +150 | -65 |       | +150 | -65 |       | +150 | -65 |       | +150 | °C   |

<sup>&</sup>lt;sup>1</sup> Bias current specifications are guaranteed after five minutes of operation at  $T_A = 25^{\circ}$ C. Bias current increases by a factor of 2.3 for every 10°C rise in temperature. <sup>2</sup> Input offset voltage specifications are guaranteed after five minutes of operation at  $T_A = 25^{\circ}$ C. <sup>3</sup> Defined as maximum continuous voltage between the inputs, such that neither input exceeds  $\pm 10$  V from ground.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating            |

|--------------------------------------|-------------------|

| Supply Voltage                       | ±18 V             |

| Internal Power Dissipation           | 500 mW            |

| Input Voltage <sup>1</sup>           | ±18 V             |

| Output Short-Circuit Duration        | Indefinite        |

| Differential Input Voltage           | $+V_S$ and $-V_S$ |

| Storage Temperature Range            | −65°C to +125°C   |

| Operating Temperature Range          |                   |

| AD549J, AD549K, AD549L               | 0°C to +70°C      |

| AD549S                               | −55°C to +125°C   |

| Lead Temperature (Soldering, 60 sec) | 300°C             |

$<sup>^1</sup>$  For supply voltages less than  $\pm 18$  V, the absolute maximum input voltage is equal to the supply voltage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

## TYPICAL PERFORMANCE CHARACTERISTICS

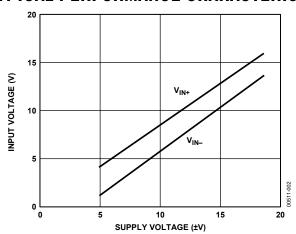

Figure 2. Input Voltage Range vs. Supply Voltage

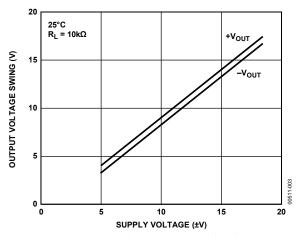

Figure 3. Output Voltage Swing vs. Supply Voltage

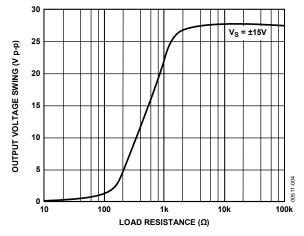

Figure 4. Output Voltage Swing vs. Load Resistance

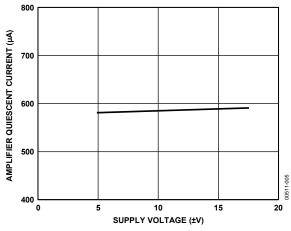

Figure 5. Quiescent Current vs. Supply Voltage

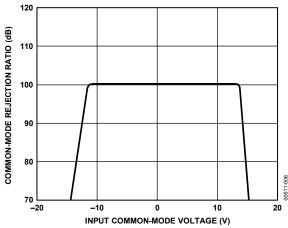

Figure 6. CMRR vs. Input Common-Mode Voltage

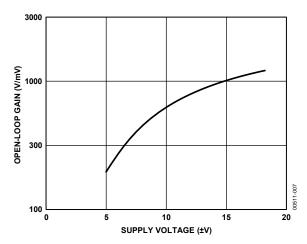

Figure 7. Open-Loop Gain vs. Supply Voltage

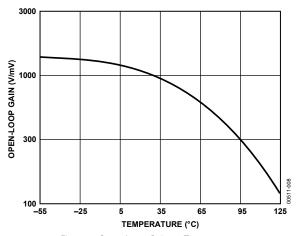

Figure 8. Open-Loop Gain vs. Temperature

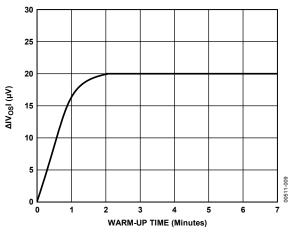

Figure 9. Change in Offset Voltage vs. Warm-Up Time

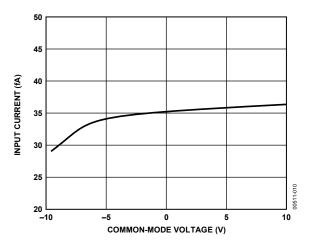

Figure 10. Input Bias Current vs. Common-Mode Voltage

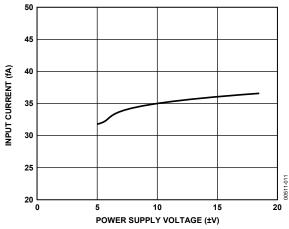

Figure 11. Input Bias Current vs. Power Supply Voltage

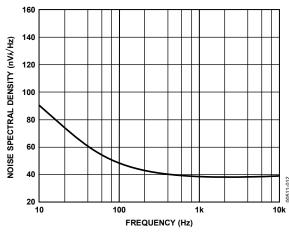

Figure 12. Input Voltage Noise Spectral Density

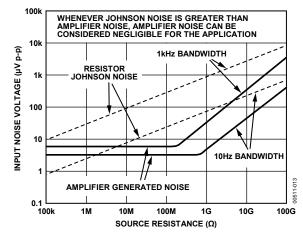

Figure 13. Noise vs. Source Resistance

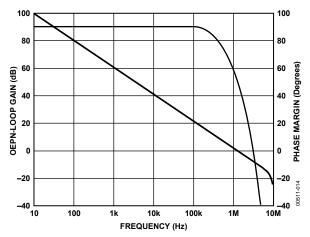

Figure 14. Open-Loop Frequency Response

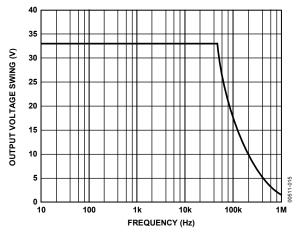

Figure 15. Large Signal Frequency Response

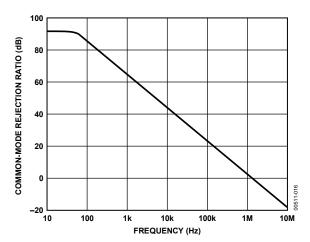

Figure 16. CMRR vs. Frequency

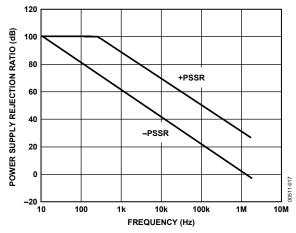

Figure 17. PSRR vs. Frequency Response

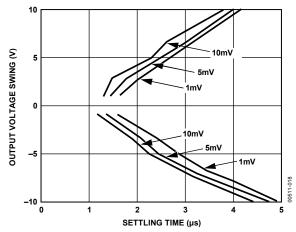

Figure 18. Output Voltage Swing and Error vs. Settling Time

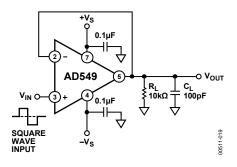

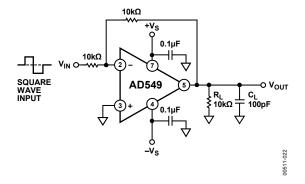

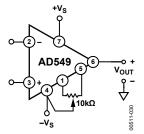

Figure 19. Unity-Gain Follower

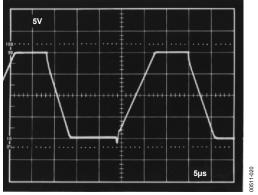

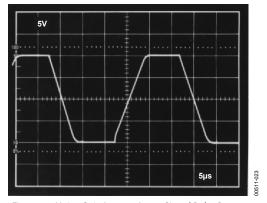

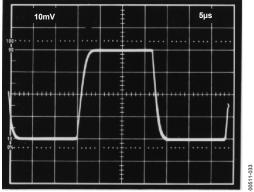

Figure 20. Unity-Gain Follower Large Signal Pulse Response

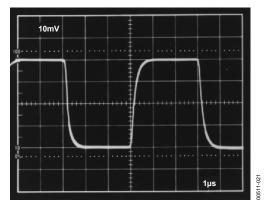

Figure 21. Unity-Gain Follower Small Signal Pulse Response

Figure 22. Unity-Gain Inverter

Figure 23. Unity-Gain Inverter Large Signal Pulse Response

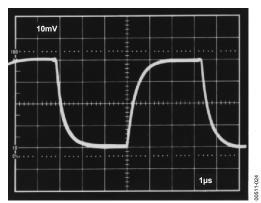

Figure 24. Unity-Gain Inverter Small Signal Pulse Response

# FUNCTIONAL DESCRIPTION MINIMIZING INPUT CURRENT

The AD549 is optimized for low input current and offset voltage. Careful attention to how the amplifier is used reduces input currents in actual applications.

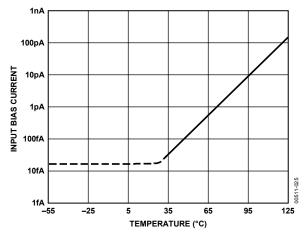

Keep the amplifier operating temperature as low as possible to minimize input current. Like other JFET input amplifiers, the AD549 input current is sensitive to chip temperature, rising by a factor of 2.3 for every 10°C. Figure 25 is a plot of the AD549 input current vs. ambient temperature.

Figure 25. Input Bias Current vs. Ambient Temperature

On-chip power dissipation raises the chip operating temperature, causing an increase in input bias current. Due to the low quiescent supply current of the AD549, the chip temperature is less than 3°C higher than its ambient temperature when the (unloaded) amplifier is operating with 15 V supplies. The difference in the input current is negligible.

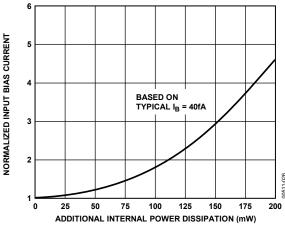

However, heavy output loads can cause a significant increase in chip temperature and a corresponding increase in the input current. Maintaining a minimum load resistance of 10  $\Omega$  is recommended. Input current vs. additional power dissipation due to output drive current is plotted in Figure 26.

Figure 26. Input Bias Current vs. Additional Power Dissipation

### **CIRCUIT BOARD NOTES**

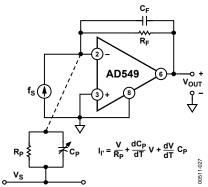

A number of physical phenomena generate spurious currents that degrade the accuracy of low current measurements. Figure 27 is a schematic of a current to voltage (I-to-V) converter with these parasitic currents modeled.

Figure 27. Sources of Parasitic Leakage Currents

Finite resistance from input lines to voltages on the board, modeled by Resistor  $R_{\text{P}}$ , results in parasitic leakage. Insulation resistance of more than  $10^{15}\,\Omega$  must be maintained between the amplifier signal and supply lines to capitalize on the low input currents of the AD549. Standard PCB material does not have high enough insulation resistance; therefore, connect the input leads of the AD549 to standoffs made of insulating material with adequate volume resistivity (that is, Teflon\*). The surface of the insulator must be kept clean to preserve surface resistivity. For Teflon, an effective cleaning procedure consists of swabbing the surface with high grade isopropyl alcohol, rinsing with deionized water, and baking the board at 80°C for 10 minutes.

In addition to high volume and surface resistivity, other properties are desirable in the insulating material chosen. Resistance to water absorption is important because surface water films drastically reduce surface resistivity. The insulator chosen should also exhibit minimal piezoelectric effects (charge emission due to mechanical stress) and triboelectric effects (charge generated by friction). Charge imbalances generated by these mechanisms can appear as parasitic leakage currents. These effects are modeled by Variable Capacitor  $C_P$  in Figure 27. Table 3 lists various insulators and their properties.<sup>2</sup>

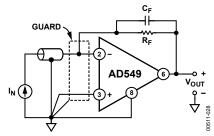

Guarding the input lines by completely surrounding them with a metal conductor biased near the potential of the input lines has two major benefits. First, parasitic leakage from the signal line is reduced because the voltage between the input line and the guard is very low. Second, stray capacitance at the input node is minimized. Input capacitance can substantially degrade signal bandwidth and the stability of the I-to-V converter.

<sup>&</sup>lt;sup>2</sup> Electronic Measurements, pp. 15–17, Keithley Instruments, Inc., Cleveland, Ohio, 1977.

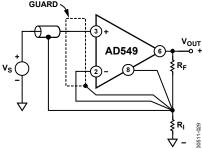

The case of the AD549 is connected to Pin 8 so that it can be bootstrapped near the input potential. This minimizes pin leakage and input common-mode capacitance due to the case. Guard schemes for inverting and noninverting amplifier topologies are illustrated in Figure 28 and Figure 29.

Figure 28. Inverting Amplifier with Guard

Figure 29. Noninverting Amplifier with Guard

Other guidelines include keeping the circuit layout as compact as possible and keeping the input lines short. Keeping the assembly rigid and minimizing sources of vibration reduces triboelectric and piezoelectric effects. All precision, high impedance circuitry requires shielding against interference noise. Use low noise coaxial or triaxial cables for remote connections to the input signal lines.

#### OFFSET NULLING

The AD549 input offset voltage can be nulled by using balance Pin 1 and Pin 5, as shown in Figure 30. Nulling the input offset voltage in this fashion introduces an added input offset voltage drift component of 2.4  $\mu$ V/°C per mV of nulled offset (a maximum additional drift of 1.2  $\mu$ V/°C for the AD549K and AD549L, and 2.4  $\mu$ V/°C for the AD549J).

Figure 30. Standard Offset Null Circuit

The approach in Figure 31 can be used when the amplifier is used as an inverter. This method introduces a small voltage referenced to the power supplies in series with the positive input terminal of the amplifier. The amplifier input offset voltage drift with temperature is not affected. However, variation of the power supply voltages causes offset shifts.

Figure 31. Alternate Offset Null Circuit for Inverter

Table 3. Insulating Materials and Characteristics

| Material     | Volume Resistivity<br>(V to CM)      | Minimal<br>Triboelectric Effect <sup>1</sup> | Minimal<br>Piezoelectric Effect <sup>1</sup> | Resistance to<br>Water Absorption <sup>1</sup> |

|--------------|--------------------------------------|----------------------------------------------|----------------------------------------------|------------------------------------------------|

| Teflon       | 10 <sup>17</sup> to 10 <sup>18</sup> | W                                            | W                                            | G                                              |

| Kel-F®       | 10 <sup>17</sup> to 10 <sup>18</sup> | W                                            | M                                            | G                                              |

| Sapphire     | 10 <sup>16</sup> to 10 <sup>18</sup> | M                                            | G                                            | G                                              |

| Polyethylene | 10 <sup>14</sup> to 10 <sup>18</sup> | M                                            | G                                            | М                                              |

| Polystyrene  | 10 <sup>12</sup> to 10 <sup>18</sup> | W                                            | M                                            | M                                              |

| Ceramic      | 10 <sup>12</sup> to 10 <sup>14</sup> | W                                            | M                                            | W                                              |

| Glass Epoxy  | 10 <sup>10</sup> to 10 <sup>17</sup> | W                                            | M                                            | W                                              |

| PVC          | 10 <sup>10</sup> to 10 <sup>15</sup> | G                                            | М                                            | G                                              |

| Phenolic     | 10 <sup>5</sup> to 10 <sup>12</sup>  | W                                            | G                                            | W                                              |

<sup>&</sup>lt;sup>1</sup> G: good with regard to property; M: moderate with regard to property; W: weak with regard to property.

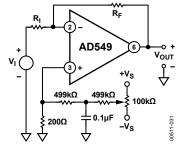

# AC RESPONSE WITH HIGH VALUE SOURCE AND FEEDBACK RESISTANCE

Source and feedback resistances greater than 100  $k\Omega$  magnify the effect of the input capacitances (stray and inherent to the AD549) on the ac behavior of the circuit. The effects of common-mode and differential input capacitances should be taken into account because the circuit bandwidth and stability can be adversely affected.

Figure 32. Follower Pulse Response from 1  $M\Omega$  Source Resistance, Case Not Bootstrapped

Figure 33. Follower Pulse Response from 1 MΩ Source Resistance, Case Bootstrapped

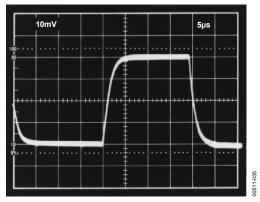

In a follower, the source resistance and input common-mode capacitance form a pole that limits the bandwidth to  $\frac{1}{2}\pi R_s C_s$ . Bootstrapping the metal case by connecting Pin 8 to the output minimizes capacitance due to the package. Figure 32 and Figure 33 show the follower pulse response from a 1 M $\Omega$  source resistance with and without the package connected to the output. Typical common-mode input capacitance for the AD549 is 0.8 pF.

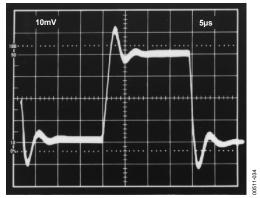

In an inverting configuration, the differential input capacitance forms a pole in the loop transmission of the circuit. This can create peaking in the ac response and possible instability. A feedback capacitance can be used to stabilize the circuit. The inverter pulse response with  $R_{\rm F}$  and  $R_{\rm S}$  equal to 1  $M\Omega$  appears in Figure 34. Figure 35 shows the response of the same circuit with a 1 pF feedback capacitance. Typical differential input capacitance for the AD549 is 1 pF.

Figure 34. Inverter Pulse Response with 1 MΩ Source and Feedback Resistance

Figure 35. Inverter Pulse Response with 1 M $\Omega$  Source and Feedback Resistance, 1 pF Feedback Capacitance

### **COMMON-MODE INPUT VOLTAGE OVERLOAD**

The rated common-mode input voltage range of the AD549 is from 3 V less than the positive supply voltage to 5 V greater than the negative supply voltage. Exceeding this range degrades the CMRR of the amplifier. Driving the common-mode voltage above the positive supply causes the amplifier output to saturate at the upper limit of the output voltage. Recovery time is typically 2  $\mu$ s after the input has been returned to within the normal operating range. Driving the input common-mode voltage within 1 V of the negative supply causes phase reversal of the output signal. In this case, normal operation typically resumes within 0.5  $\mu$ s of the input voltage returning within range.

#### DIFFERENTIAL INPUT VOLTAGE OVERLOAD

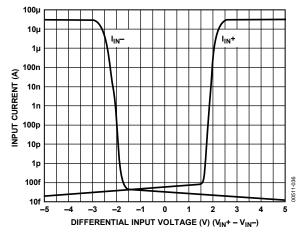

A plot of the AD549 input currents vs. differential input voltage (defined as  $V_{\rm IN+}-V_{\rm IN-}$ ) appears in Figure 36. The input current at either terminal stays below a few hundred femtoamps until one input terminal is forced higher than 1 V to 1.5 V above the other terminal. Under these conditions, the input current limits at 30  $\mu$ A.

Figure 36. Input Current vs. Differential Input Voltage

#### INPUT PROTECTION

The AD549 safely handles any input voltage within the supply voltage range. Subjecting the input terminals to voltages beyond the power supply can destroy the device or cause shifts in input current or offset voltage if the amplifier is not protected.

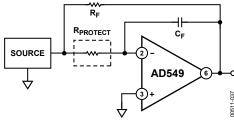

A protection scheme for the amplifier as an inverter is shown in Figure 37.  $R_P$  is chosen to limit the current through the inverting input to 1 mA for expected transient (less than 1 sec) overvoltage conditions, or to 100  $\mu A$  for a continuous overload. Because  $R_P$  is inside the feedback loop and is much lower in value than the amplifier input resistance, it does not affect the dc gain of the inverter. However, the Johnson noise of the resistor adds root sum of squares to the amplifier input noise.

Figure 37. Inverter with Input Current Limit

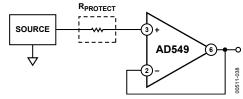

In the corresponding version of this scheme for a follower, shown in Figure 38,  $R_P$  and the capacitance at the positive input terminal produce a pole in the signal frequency response at a  $f=\frac{1}{2}\pi RC$ . Again, the Johnson noise,  $R_P$ , adds to the input voltage noise of the amplifier.

Figure 38. Follower with Input Current Limit

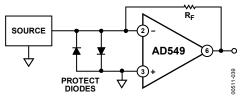

Figure 39 is a schematic of the AD549 as an inverter with an input voltage clamp. Bootstrapping the clamp diodes at the inverting input minimizes the voltage across the clamps and keeps the leakage due to the diodes low. Use low leakage diodes, such as the FD333s, and shield them from light to prevent photocurrents from being generated. Even with these precautions, the diodes measurably increase input current and capacitance.

Figure 39. Input Voltage Clamp with Diodes

# SAMPLE-AND-DIFFERENCE CIRCUIT TO MEASURE ELECTROMETER LEAKAGE CURRENTS

There are a number of methods used to test electrometer leakage currents, including current integration and direct I-to-V conversion. Regardless of the method used, board and interconnect cleanliness, proper choice of insulating materials (such as Teflon or Kel-F), correct guarding and shielding techniques, and care in physical layout are essential to making accurate leakage measurements.

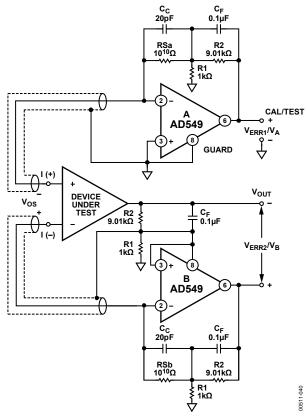

Figure 40 is a schematic of the sample-and-difference circuit. It uses two AD549 electrometer amplifiers (A and B) as I-to-V converters with high value ( $10^{10}~\Omega$ ) sense resistors (RSa and RSb). R1 and R2 provide for an overall circuit sensitivity of 10 fA/mV (10~pA full scale).  $C_{\text{C}}$  and  $C_{\text{F}}$  provide noise suppression and loop compensation.  $C_{\text{C}}$  should be a low leakage polystyrene capacitor. An ultralow leakage Kel-F test socket is used for contacting the device under test. Rigid Teflon coaxial cable is used to make connections to all high impedance nodes. The use of rigid coaxial cable affords immunity to error induced by mechanical vibration and provides an outer conductor for shielding. The entire circuit is enclosed in a grounded metal box.

The test apparatus is calibrated without a device under test present. After power is turned on, a 5 minute stabilization period is required. First,  $V_{\text{ERR1}}$  and  $V_{\text{ERR2}}$  are measured. These voltages are the errors caused by the offset voltages and leakage currents of the I-to-V converters.

$$V_{ERRI} = 10 (V_{OS}A - I_BA \times RSa)$$

$$V_{ERR2} = 10 (V_{OS}B - I_BB \times RSb)$$

Figure 40. Sample and Difference Circuit for Measuring Electrometer Leakage Currents

Once measured, these errors are subtracted from the readings taken with a device under test present. Amplifier B closes the feedback loop to the device under testing in addition to providing the I-to-V conversion. The offset error of the device under testing appears as a common-mode signal and does not affect the test measurement. As a result, only the leakage current of the device under testing is measured.

$$V_A - V_{ERR1} = 10[RSa \times I_B(+)]$$

$$V_X - V_{ERR2} = 10[RSb \times I_B(-)]$$

Although a series of devices can be tested after only one calibration measurement, calibration should be updated periodically to compensate for any thermal drift of the I-to-V converters or changes in the ambient environment. Laboratory results have shown that repeatable measurements within 10 fA can be realized when this apparatus is properly implemented. These results are achieved in part by the design of the circuit, which eliminates relays and other parasitic leakage paths in the high impedance signal lines, and in part by the inherent cancellation of errors through the calibration and measurement procedure.

### **PHOTODIODE INTERFACE**

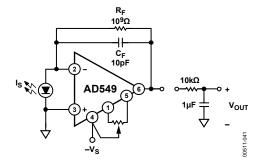

The low input current and low input offset voltage of the AD549 make it an excellent choice for very sensitive photodiode preamps (see Figure 41). The photodiode develops a signal current, Is, equal to

$$I_S = R \times P$$

where P is light power incident on the diode surface, in watts, and R is the photodiode responsivity in amps/watt.  $R_F$  converts the signal current to an output voltage

$$V_{OUT} = R_F \times I_S$$

Figure 41. Photodiode Preamp

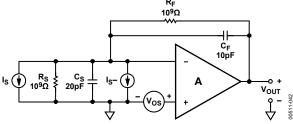

The dc error sources and an equivalent circuit for a small area (0.2 mm square) photodiode are indicated in Figure 42.

Figure 42. Photodiode Preamp DC Error Sources

Input current,  $I_B$ , contributes an output voltage error,  $V_{E1}$ , proportional to the feedback resistance

$$V_{E1} = I_B \times R_F$$

The input voltage offset of the op amp causes an error current through the photodiode shunt resistance, R<sub>S</sub>

$$I = V_{OS}/R_S$$

The error current results in an error voltage  $(V_{\text{E2}})$  at the amplifier output equal to

$$V_{E2} = (1 + R_F/R_S)V_{OS}$$

Given typical values of photodiode shunt resistance (on the order of  $10^9~\Omega$ ),  $R_F/R_S$  can easily be greater than 1, especially if a large feedback resistance is used. Also,  $R_F/R_S$  increases with temperature because photodiode shunt resistance typically drops by a factor of 2 for every  $10^\circ C$  rise in temperature. An op amp with low offset voltage and low drift must be used to maintain accuracy. The AD549K offers a guaranteed maximum 0.50 mV offset voltage and 15 mV/ $^\circ C$  drift for very sensitive applications.

### **Photodiode Preamp Noise**

Noise limits the signal resolution obtainable with the preamp. The output voltage noise divided by the feedback resistance is the minimum current signal that can be detected. This minimum detectable current divided by the responsivity of the photodiode represents the lowest light power that is detectable by the preamp.

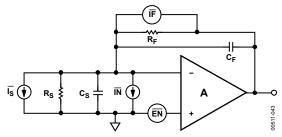

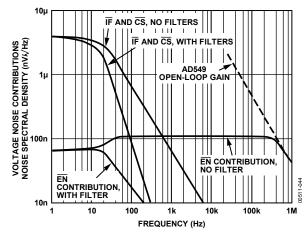

Noise sources associated with the photodiode, amplifier, and feedback resistance are shown in Figure 43; Figure 44 is the spectral density vs. frequency plot of the contribution of each of the noise sources to the output voltage noise (circuit parameters in Figure 42 are assumed). The rms contribution of each noise source to the total output voltage noise is obtained by integrating the square of its spectral density function over frequency. The rms value of the output voltage noise is the square root of the sum of all contributions. Minimizing the total area under these curves optimizes the resolution of the preamplifier for a given bandwidth.

Figure 43. Photodiode Preamp Noise Sources

The photodiode preamp in Figure 41 can detect a signal current of 26 fA rms at a bandwidth of 16 Hz, which, assuming a photodiode responsivity of 0.5 A/W, translates to a 52 fW rms minimum detectable power. The photodiode used has a high source resistance and low junction capacitance.  $C_F$  sets the signal bandwidth with  $R_F$  and also limits the peak in the noise

gain that multiplies the op amp input voltage noise contribution. A single-pole filter at the output of the amplifier limits the op amp output voltage noise bandwidth to 26 Hz, comparable to the signal bandwidth. This greatly improves the signal-to-noise ratio of the preamplifier (in this case, by a factor of 3).

Figure 44. Spectral Density of the Photodiode Preamp Noise Sources vs. Frequency

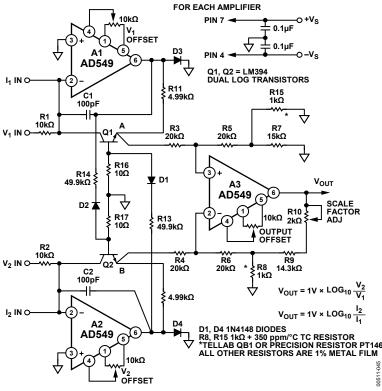

#### **LOG RATIO AMPLIFIER**

Logarithmic ratio circuits are useful for processing signals with wide dynamic range. The 60 fA maximum input current of the AD549L makes it possible to build a log ratio amplifier with 1% log conformance for input currents ranging from 10 pA to 1 mA, a dynamic range of 160 dB.

The log ratio amplifier in Figure 45 provides an output voltage proportional to the log base 10 of the ratio of Input Current  $I_1$  and Input Current  $I_2$ . Resistor R1 and Resistor R2 are provided for voltage inputs. Because NPN devices are used in the feedback loop of the front-end amplifiers that provide the log transfer function, the output is valid only for positive input voltages and input currents. The input currents set the Collector Current IC1 and Collector Current IC2 of a matched pair of log transistors, Q1 and Q2, to develop Voltage  $V_A$  and Voltage  $V_B$

$$V_A$$

,  $V_B = -(kT/q) \ln IC/IES$

where *IES* is the saturation current of the transistor.

The difference of  $V_{\text{A}}$  and  $V_{\text{B}}$  is taken by the subtractor section to obtain

$$V_C = (kT/q)\ln(IC2/IC1)$$

$V_{\rm C}$  is scaled up by the ratio of (R9 + R10)/R8, which is equal to approximately 16 at room temperature, resulting in the output voltage

$$V_{OUT} = 1 \text{ V} \times \log(IC2/IC1)$$

R8 is a resistor with a positive 3500 ppm/°C temperature coefficient to provide the necessary temperature compensation. The parallel combination of R15 and R7 is provided to keep the gain of the subtractor section for positive and negative inputs matched over temperature.

Frequency compensation is provided by R11, R12, C1, and C2. The bandwidth of the circuit is 300 kHz at input signals greater than 50  $\mu$ A; bandwidth decreases smoothly with decreasing signal levels.

To trim the circuit, set the input currents to 10  $\mu A$  and trim the A3 offset using the trim potentiometer of the amplifier for the output to equal 0. Next, set  $I_1$  to 1  $\mu A$  and adjust the output to equal 1 V by trimming R10. Additional offset trims on Amplifier A1 and Amplifier A2 can be used to increase the voltage input accuracy and dynamic range.

The very low input current of the AD549 makes this circuit useful over a very wide range of signal currents. The total input current (which determines the low level accuracy of the circuit) is the sum of the amplifier input current, the leakage across the compensating capacitor (negligible if a polystyrene or Teflon capacitor is used), and the collector-to-collector and collector-to-base leakages of one side of the dual log transistors. The magnitudes of these last two leakages depend on the amplifier input offset voltage and are typically less than 10 fA with 1 mV offsets. The low level accuracy is limited primarily by the amplifier input current, only 60 fA maximum when the AD549L is used.

The effects of the emitter resistance of Q1 and Q2 can degrade circuit accuracy at input currents above 100  $\mu$ A. The networks

composed of R13, D1, R16, R14, D2, and R17 compensate for these errors, so that this circuit has less than a 1% log conformance error at 1 mA input currents. The correct value for R13 and R14 depends on the type of log transistors used. The 49.9 k $\Omega$  resistors were chosen for use with LM394 transistors. Smaller resistance values are needed for smaller log transistors.

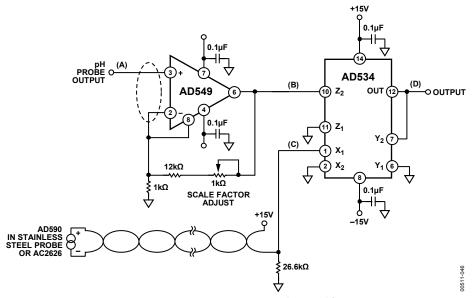

# TEMPERATURE COMPENSATED pH PROBE AMPLIFIER

A pH probe can be modeled as an mV-level voltage source with a series source resistance dependent on the electrode composition and configuration. The glass bulb resistance of a typical pH electrode pair falls between  $10^6\,\Omega$  and  $10^9\,\Omega$ . It is therefore important to select an amplifier with low enough input currents such that the voltage drop produced by the amplifier input bias current and the electrode resistance does not become an appreciable percentage of a pH unit.

The circuit in Figure 46 illustrates the use of the AD549 as a pH probe amplifier. As with other electrometer applications, the use of guarding, shielding, and Teflon standoffs is necessary to capitalize on the AD549 low input current. If an AD549L (60 fA maximum input current) is used, the error contributed by the input current is held below 60  $\mu V$  for pH electrode source impedances up to  $10^9\,\Omega.$  Input offset voltages (which can be trimmed) are below 0.5 mV.

Figure 45. Log Ratio Amplifier

The pH probe output is ideally 0 V at a pH of 7, independent of temperature. The slope of the transfer function of the probe, though predictable, is temperature dependent (-54.2 mV/pH at 0°C and -74.04 mV/pH at 100°C). By using an AD590 temperature sensor and an AD534 analog divider, an accurate temperature compensation network can be added to the basic pH probe amplifier. Table 4 shows voltages at various points, thereby illustrating

the compensation. The AD549 is set for a noninverting gain of 13.51. The output of the AD590 circuitry (Point C) is equal to 10 V at 100°C and decreases by 26.8 mV/°C. The output of the AD534 analog divider (Point D) is a temperature-compensated output voltage centered at 0 V for a pH of 7 and has a transfer function of -1.00 V/pH unit. The output range spans from -7.00 V (pH = 14) to +7.00 V (pH = 0).

Figure 46. Temperature Compensated pH Amplifier

**Table 4. Illustration of Temperature Compensation**

|                        |                       | Point             |                      |                      |  |  |  |  |  |

|------------------------|-----------------------|-------------------|----------------------|----------------------|--|--|--|--|--|

| Probe Temperature (°C) | A (Probe Output) (mV) | B (A × 13.51) (V) | C (AD590 Output) (V) | D (10 × (B ÷ C)) (V) |  |  |  |  |  |

| 0                      | 54.20                 | 0.732             | 7.32                 | 1.00                 |  |  |  |  |  |

| 25                     | 59.16                 | 0.799             | 7.99                 | 1.00                 |  |  |  |  |  |

| 37                     | 61.54                 | 0.831             | 8.31                 | 1.00                 |  |  |  |  |  |

| 60                     | 66.10                 | 0.893             | 8.93                 | 1.00                 |  |  |  |  |  |

| 100                    | 74.04                 | 1.000             | 10.00                | 1.00                 |  |  |  |  |  |

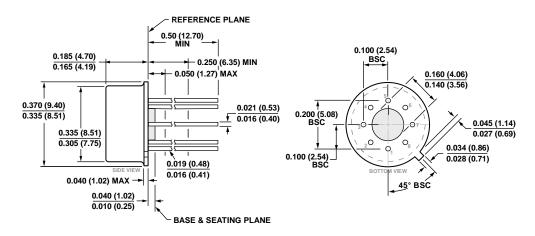

### **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-002-AK

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 47. 8-Lead Metal Can [TO-99] (H-08) Dimensions shown in inches and (millimeters)

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description      | Package Option |

|--------------------|-------------------|--------------------------|----------------|

| AD549JHZ           | 0°C to +70°C      | 8-Lead Metal Can (TO-99) | H-08           |

| AD549KHZ           | 0°C to +70°C      | 8-Lead Metal Can (TO-99) | H-08           |

| AD549LHZ           | 0°C to +70°C      | 8-Lead Metal Can (TO-99) | H-08           |

| AD549SH/883B       | −55°C to +125°C   | 8-Lead Metal Can (TO-99) | H-08           |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Precision Amplifiers category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below:

OPA4187IRUMT

OPA202IDGKT

514327X

561681F

647876R

5962-9080901MCA\*

MAX410CPA

MAX44241AUK+T

LT6230IS6#TR

LT1112S8#TR

OP227GN#PBF

LT6020IDD-1#PBF

LT6023IDD#PBF

LT6013AIDD#PBF

LT6237IMS8#PBF

LT1124CS8#TR

LT1215CS8#TRPBF

ADA4622-1ARZ-R7

NCS21871SQ3T2G

NCS21871SN2T1G

NCV21871SQ3T2G

NCV21871SN2T1G

AD8538WAUJZ-R7

NCS21912DMR2G

MCP6V82-EMS

MCP6V92-EMS

TLC27L7CP

TLE2022MD

TLV2473CDR

MCP6V34-E/ST

MCP6V84-EST

MCP6V94-EST

LT1014DDWR

5962-89641012A

5962-8859301M2A

5962-89801012A

5962-9452101M2A

LMC6064IN

LT1013DDR

TL034ACDR

TLC2201AMDG4

TLC274MDRG4

TLE2021QDRG4Q1

TLE2024BMDWG4

AD8691WAUJZ-R7

AD8629TRZ-EP-R7

AD8604ARQZ

TS507IYLT

MAX4239ATT+T

MAX4238AUT+T