Address: Midas Components Ltd, Electra House, 32 Southtown Road, Great Yarmouth, Norfolk, England, NR31 ODU Email:sales@midascomponents.co.uk

Website:www.midascomponents.co.uk Tel:+44(0)1493 602602 Fax:+44(0)1493 665111

DOC.

#### DATASHEET STATEMENT

- 1. The following icons are absolutely designed by Midas independently in 2007-SEP. They are not in common use in the LCD industry yet but just used for marking out Midasproducts' characteristics quickly and simply without any special meaning. Midas reserves the composing right and copyright. No one else is allowed to adopt these icons without Midas approval.

- 2. The ISO9001 logo used in this document is authorized by SGS (www.sgs.com). Midas had already successfully passed the strict and professional ISO9001:2000 Quality Management System Certification and got the certificate (No.: CN07/00404)

- 3. The technologies/techniques/crafts which denoted by the following icons are not exclusively owned by Midas, but also shared by Midas LCD strategic cooperators, however all these technologies/techniques/crafts have been finally confirmed by Midas professional engineers and QC department.

- **4.** As the difference in test standard and test conditions, also Midas insufficient familiarity with the actual LCD using environment, all the referred information in this DATASHEET (including the icons) only have two functions:

- 4.1: providing quick reference when you are judging whether or not the product meets your requirements.

- 4.2: listing out definitely the tolerance.

SAMPLE APPROVAL document rather than consider this DATASHEET as the standard for judging whether or not the LCD meets your requirements. Once you instruct Midas to a mass-production without definite demand for providing sample before, Midas will disclaim all responsibility if the mass-production is proved not meeting with your requirements.

- **5.** The sequence of the icons is random and doesn't indicate the importance grade.

- 6. Icons explanation

Midas 2006 version logo. Midas is an integrated manufacturer of flat panel display (FPD). Midas supplies TN, HTN, STN, FSTN monochrome LCD panel; COB, COG, TAB LCD module; and all kinds of LED backlight.

#### **FAST RESPONSE TIME**

This icon on the cover indicates the product is with high response speed; Otherwise not.

#### PROTECTION CIRCUIT

This icon on the cover indicates the product is with protection circuit; Otherwise not.

#### **HIGH CONTRAST**

This icon on the cover indicates the product is with high contrast; Otherwise not.

#### LONG LIFE VERSION

This icon on the cover indicates the product is long life version (over 9K hours guaranteed); Otherwise not.

#### WIDE VIEWING SCOPE

This icon on the cover indicates the product is with wide viewing scope; Otherwise not.

#### **Anti UV VERSION**

This icon on the cover indicates the product is against UV line. Otherwise not.

#### **RoHS COMPLIANCE**

This icon on the cover indicates the product meets ROHS requirements; Otherwise not.

## **OPERATION TEMPERATURE RANGE**

This icon on the cover indicates the operating temperature range (X-Y).

#### **3TIMEs 100% QC EXAMINATION**

This icon on the cover indicates the product has passed Midas thrice 100% QC.

Otherwise not.

#### TWICE SELECTION OF LED MATERIALS

This icon on the cover indicates the LED had passed Midas twice strict selection which promises the product's identical color and brightness; Otherwise not.

#### Vlcm = 3.0V

This icon on the cover indicates the product can work at 3.0V exactly; otherwise not.

#### N SERIES TECHNOLOGY (2008 developed)

New structure, new craft, new technology and new materials inside both LCD module and LCD panel to improve the "RainBow"

| BOOKBINDING AREA |               |                 |      |      |  |

|------------------|---------------|-----------------|------|------|--|

|                  | STANDARD DOC. | REVISION RECORD | PAGE | 1/19 |  |

|     |         |                | OC.  |        |         |

|-----|---------|----------------|------|--------|---------|

| NO. | DATE    | DESCRIPTION    | ITEN | I PAGE | APPROVE |

| 1   | 2011.04 | INITIAL ISSUED | ALL  | ALL    | State   |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

|     |         |                |      |        |         |

## **BOOKBINDING AREA**

STANDARD DOC.

**CONTENTS**

PAGE 2/19

| 1.  | GENERAL SPECIFICATIONS Page 4                |

|-----|----------------------------------------------|

| 2.  | MECHANICAL SPECIFICATIONS Page 4             |

| 3.  | ABSOLUTE MAXIMUM RATINGS Page 4              |

| 4.  | ELECTRONICAL CHARACTERISTIC Page 4           |

| 5.  | OPTICAL CHARACTERISTICSPage 5                |

| 6.  | ELECTRICAL SPECIFICATIONS Page 6             |

| 7.  | EXTERNAL DIMENSION Page 8                    |

|     | PIN ASSIGNMENT Page 9                        |

| 9.  | POWER SUPPLY Page 9                          |

| 10. | REFLECTOR OF SCREEN AND DDRAM ADDRESS Page 9 |

| 11. | INSTRUCTION TABLEPage 10                     |

| 12. | INSTRUCTION DESCRIPTIONPage 11               |

| 13. | CGRAM Page 15                                |

| 14. | DDRAM Page 15                                |

| 15. | INITIALIZATION Page 16                       |

| 16. | INTERFACE TO MPUPage 18                      |

| 17. | FONT MAP Page 19                             |

| 18. | PACKING DETAIL Page 20                       |

| BOOKBINDING AREA |         |                  |      |      |  |  |

|------------------|---------|------------------|------|------|--|--|

|                  | PRODUCT | MODE NO.         | PAGE | 2/40 |  |  |

|                  | SPEC.   | MC20805A6W-GPTLY | PAGE | 3/19 |  |  |

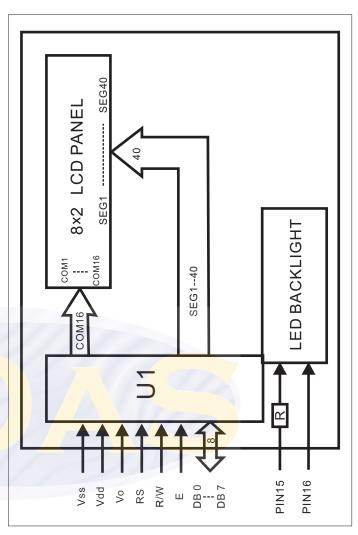

## 1. GENERAL SPECIFICATIONS

| ITEM                      | NOMINAL DIMENSIONS / AVAILABLE OPTIONS        |

|---------------------------|-----------------------------------------------|

| DISPLAY FORMAT            | 8 Characters by 2 Lines                       |

| LCD PANEL OPTIONS         | STN (Graycolor)                               |

| POLARIZER OPTIONS         | Positive, Transflective                       |

| BACKLIGHT OPTIONS         | Array type LED backlight (Yellow-green color) |

| VIEWING DIRECTION OPTIONS | 6:00 ( Bottom )                               |

| TEMPERATURE RANGE OPTIONS | Wide temp. range ( -20°C ~ 70°C )             |

| CONTROLLERIC              | SUNPLUS                                       |

| DISPLAY DUTY              | 1/16                                          |

| DRIVING BIAS              | 1/5                                           |

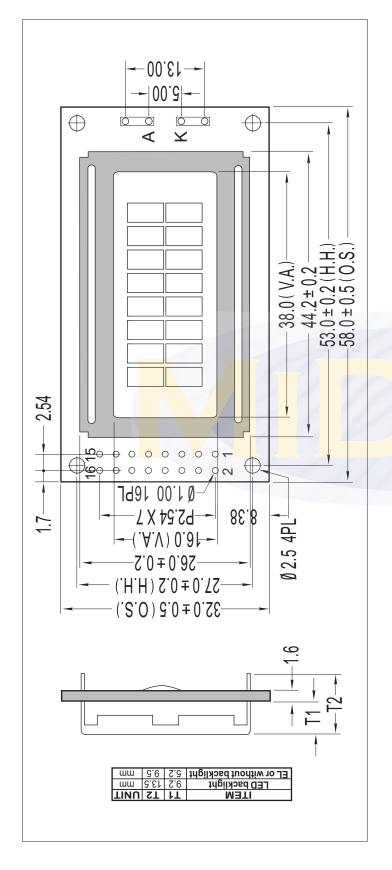

### 2. MECHANICAL SPECIFICATIONS

| OVERALL SIZE   | LED backlight version: 58.0 x 32.0 x max 13.5 |    |                 |               | mm |

|----------------|-----------------------------------------------|----|-----------------|---------------|----|

| VIEWING AREA   | 38.0W x 16.0H                                 | mm | HOLE-HOLE       | 53.0W x 27.0H | mm |

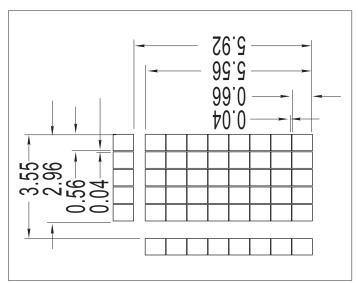

| CHARACTER SIZE | 2.96W x 5.56H                                 | mm | CHARACTER PITCH | 0.59W x 0.36H | mm |

| DOT SIZE       | 0.56W x 0.66H                                 | mm | DOT PITCH       | 0.04W x 0.04H | mm |

### 3. ABSOLUTE MAXIMUM RATINGS

| ITEM                                | SYMBOL | CONDITION | MIN       | MAX      | UNIT |

|-------------------------------------|--------|-----------|-----------|----------|------|

| POWER SUPPL <mark>Y (</mark> LOGIC) | Vdd    | 25°C      | -0.3      | 7.0      | ٧    |

| POWER SUPPLY (LCD)                  | V0     | 25°C      | Vdd -13.5 | Vdd +0.3 | ٧    |

| INPUT VOLTAGE                       | Vin    | 25°C      | -0.3      | Vdd +0.3 | V    |

| OPERATING TEMPERATURE               | Vopr   |           | -20       | 70       | °C   |

| STORAGE TEMPERATURE                 | Vstg   |           | -30       | 80       | °C   |

#### 4. ELECTRONICAL CHARACTERISTIC\*

| IT E M                        | CVMDOL   | SYMBOL CONDITION | S    | STANDARD |      |       |

|-------------------------------|----------|------------------|------|----------|------|-------|

| ITEM                          | SYMBOL   | CONDITION        | MIN  | TYP      | MAX  | UNIT  |

| Input voltage                 | Vdd      | +5V              | 4.7  | 5.0      | 5.5  | V     |

| Supply current                | ldd      | Vdd=5V           |      | 1.3      |      | mA    |

| Recommended LCD driving       |          | -20°C            | 4.35 |          | 4.90 |       |

|                               |          | 0°C              | 4.25 |          | 4.85 |       |

| voltage for normal temp.      | Vdd - V0 | 25°C             | 4.20 | 4.50     | 4.80 | V     |

| Version module                |          | 50°C             | 4.10 |          | 4.70 |       |

|                               |          | 70°C             | 4.00 |          | 4.60 |       |

| LED forward voltage           | Vf       | 25°C             | 3.8  |          | 4.4  | V     |

| LED forward current           | lf       | 25°C             |      | 60       |      | mA    |

| LED reverse Current           | lr       | 25°C             |      |          | 60   | μA    |

| LED Peak wave length          | λр       | 25°C If = 60mA   | 568  |          | 575  | nm    |

| LED illuminance (Without LCD) | Lv       | 25°C If = 60mA   |      | 100      |      | cd/m² |

| LED life time                 |          | 25°C If = 60mA   | 9K** |          |      | Hours |

<sup>\*</sup> The above data are for reference only.

<sup>\*\*</sup> The warranty period of FORDATA LCD module is 1YEAR counted from the date shown on the label of products.

| BOOKBINDING AREA |                  |      |      |

|------------------|------------------|------|------|

| PRODUCT          | MODE NO.         | PAGE | 4/19 |

| SPEC.            | MC20805A6W-GPTLY | PAGE | 4/19 |

## 5. OPTICAL CHARACTERISTIC

| FOR TN TYPE LCD MODULE (TA=25°C, Vdd=5.0V ± 0.25V) |            |           |     |     |     |      |  |

|----------------------------------------------------|------------|-----------|-----|-----|-----|------|--|

| ITEM                                               | SYMBOL     | CONDITION | MIN | TYP | MAX | UNIT |  |

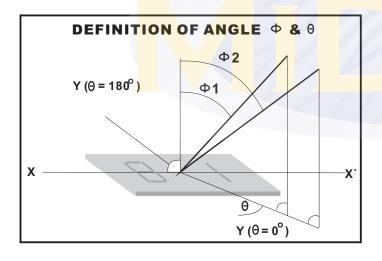

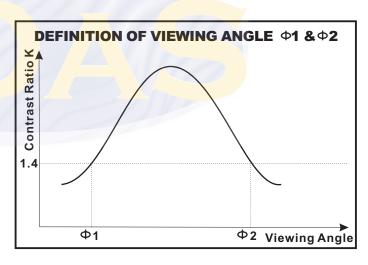

| VIEWING ANGLE                                      | Ф2-Ф 1     | K=4       | 30  |     |     | deg  |  |

| VIEWING ANGLE                                      | Θ          |           | 25  |     |     | ueg  |  |

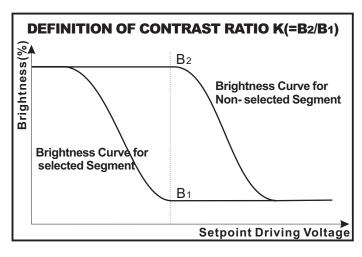

| CONTRAST RATIO                                     | K          |           |     | 2   |     |      |  |

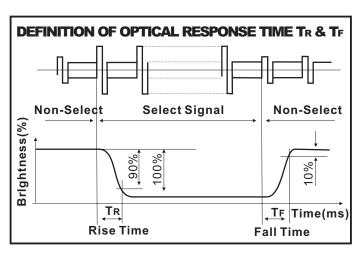

| RESPONSE TIME(RISE)                                | <b>T</b> R |           |     | 120 | 150 | ms   |  |

| RESPONSE TIME(FALL)                                | <b>T</b> F |           |     | 120 | 150 | ms   |  |

| FOR STN TYPE LCD MODULE (TA=25 °C, Vdd=5.0V ± 0.25V) |        |           |     |     |     |      |  |

|------------------------------------------------------|--------|-----------|-----|-----|-----|------|--|

| ITEM                                                 | SYMBOL | CONDITION | MIN | TYP | MAX | UNIT |  |

| VIEWING ANGLE                                        | Ф2-Ф 1 | K=4       | 40  |     |     | dog  |  |

| VIEWING ANGLE                                        | Θ      |           | 60  |     |     | deg  |  |

| CONTRAST RATIO                                       | K      |           |     | 6   |     |      |  |

| RESPONSE TIME(RISE)                                  | TR     |           |     | 150 | 250 | ms   |  |

| RESPONSE TIME(FALL)                                  | TF     |           |     | 150 | 250 | ms   |  |

| BOOKBINDING AREA |         |                  |      |      |  |  |

|------------------|---------|------------------|------|------|--|--|

|                  | PRODUCT | MODE NO.         | PAGE | E/40 |  |  |

|                  | SPEC.   | MC20805A6W-GPTLY | PAGE | 5/19 |  |  |

## **6. ELECTRICAL SPECIFICATIONS**

# 6.1 DC CHARACTERISTICS ( VDD = 4.5V to 5.5V, TA = 25 $^{\circ}$ C )

| CHARACTERISTICS              | CAMBOI  |      | LIMIT |      | UNIT | TEST CONDITION                   |  |  |

|------------------------------|---------|------|-------|------|------|----------------------------------|--|--|

| CHARACTERISTICS              | STWIBUL | MIN. | TYP.  | MAX. | UNII | TEST CONDITION                   |  |  |

| INPUT HIGH VOLTAGE           | VIH1    | 2.2  |       | Vdd  | V    | Pins ( E. RS. R/W. DB0 - DB7 )   |  |  |

| INPUT LOW VOLTAGE            | VIL1    | -0.3 |       | 0.6  | V    | Fills ( E. N.S. N.W. DD0 - DD1 ) |  |  |

| INPUT HIGH CURRENT           | Іін     | -2.0 |       | 2.0  | μΑ   | Pins ( RS. R/W. DB0 - DB7 )      |  |  |

| INPUT LOW CURRENT            | lıL     | -20  | -50   | -100 | μΑ   | Vdd = 5.0V                       |  |  |

| OUTPUT HIGH<br>VOLTAGE (TTL) | Vон1    | 2.4  |       | Vdd  | V    | Iон = - 0.1mA<br>Pins: DB0 - DB7 |  |  |

| OUTPUT LOW<br>VOLTAGE (TTL)  | Vol1    |      |       | 0.4  | V    | IoL = 0.1mA<br>Pins: DB0 - DB7   |  |  |

# 6.2 AC CHARACTERISTICS ( VDD = 4.5V to 5.5V, TA = 25 °C )

## Write mode

| CHARACTERISTICS        | SYMPOL   |                  | LIMIT | 7/5  | LINUT | TEST CONDITION  |

|------------------------|----------|------------------|-------|------|-------|-----------------|

| CHARACTERISTICS        | STIVIBUL | MIN.             | TYP.  | MAX. | UNIT  | TEST CONDITION  |

| ENABLE CYCLE TIME      | tc       | <mark>500</mark> |       | /_// | ns    | Pin E           |

| ENABLE PULSE WIDTH     | tpw      | 230              |       |      | ns    | Pin E           |

| ENABLE RISE/ FALL TIME | tr, tr   |                  |       | 20   | ns    | Pin E           |

| ADDRESS SETUP TIME     | tsp1     | 40               |       |      | ns    | Pins RS, R/W, E |

| ADDRESS HOLD TIME      | tHD1     | 10               |       |      | ns    | Pins RS, R/W, E |

| DATA SETUP TIME        | tsp2     | 80               |       |      | ns    | Pins: DB0 - DB7 |

| DATA HOLD TIME         | tHD2     | 10               |       |      | ns    | Pins: DB0 - DB7 |

## Read mode

| CHARACTERISTICS        | CVMDOL  |      | LIMIT |      | LINUT | TEST CONDITION  |

|------------------------|---------|------|-------|------|-------|-----------------|

| CHARACTERISTICS        | STWIBUL | MIN. | TYP.  | MAX. | UNIT  | 1E31 CONDITION  |

| ENABLE CYCLE TIME      | tc      | 500  |       |      | ns    | Pin E           |

| ENABLE PULSE WIDTH     | tpw     | 230  |       |      | ns    | Pin E           |

| ENABLE RISE/ FALL TIME | tr, tr  |      |       | 20   | ns    | Pin E           |

| ADDRESS SETUP TIME     | tsp1    | 40   |       |      | ns    | Pins RS, R/W, E |

| ADDRESS HOLD TIME      | tHD1    | 10   |       |      | ns    | Pins RS, R/W, E |

| DATA OUTPUT DELAY TIME | to      |      |       | 120  | ns    | Pins: DB0 - DB7 |

| DATA HOLD TIME         | tHD2    | 5    |       |      | ns    | Pins: DB0 - DB7 |

| BOOKBINDING AREA |         |                  |      |      |  |  |  |

|------------------|---------|------------------|------|------|--|--|--|

|                  | PRODUCT | MODE NO.         | PAGE | 6/10 |  |  |  |

|                  | SPEC.   | MC20805A6W-GPTLY | PAGE | 6/19 |  |  |  |

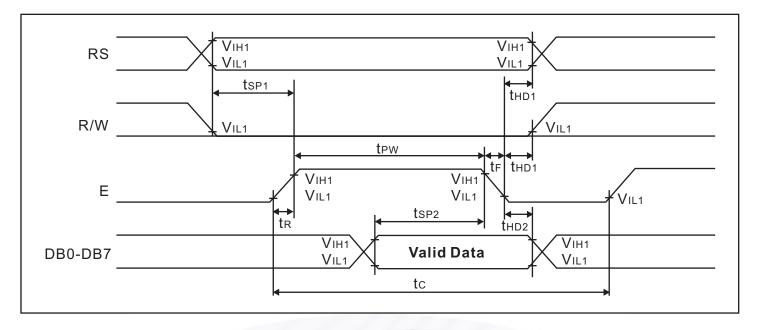

### **6.3.1 WRITE MODE TIMING DIAGRAM**

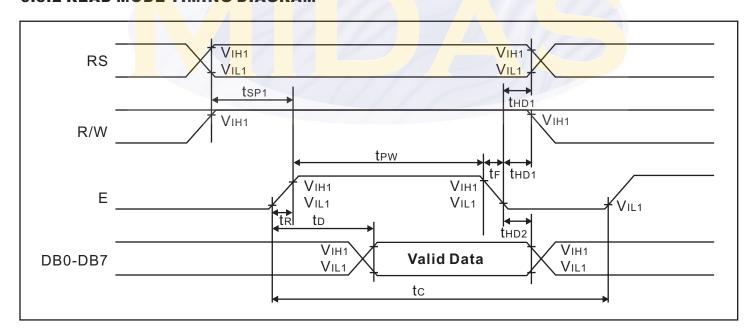

### 6.3.2 READ MODE TIMING DIAGRAM

| BOOKBINDING AREA |         |                  |      |      |  |  |  |

|------------------|---------|------------------|------|------|--|--|--|

|                  | PRODUCT | MODE NO.         | PAGE | 7/40 |  |  |  |

|                  | SPEC.   | MC20805A6W-GPTLY | PAGE | 7/19 |  |  |  |

#### 7. EXTERNAL DIMENSIONS

| BOOKBINDING AREA |         |                  |      |      |  |  |  |

|------------------|---------|------------------|------|------|--|--|--|

|                  | PRODUCT | MODE NO.         | PAGE | 8/19 |  |  |  |

|                  | SPEC.   | MC20805A6W-GPTLY | PAGE | 0/19 |  |  |  |

## **8.PIN ASSIGNMENT**

| PIN  | SYMBOL    | FUNCTION                     |

|------|-----------|------------------------------|

| 1    | Vss       | GND                          |

| 2    | Vdd       | Power supply for LCM (+5.0V) |

| 3    | V0        | Contrast Adjust              |

| 4    | RS        | Register Select Signal       |

| 5    | R/W       | Data Read / Write            |

| 6    | E         | Enable Signal                |

| 7-14 | DB0 - DB7 | Data bus line                |

| 15   | LED+      | Power supply for BKL (+5.0V) |

| 16   | LED-      | Power supply for BKL (0V)    |

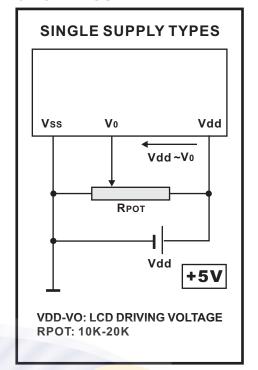

## **9.POWER SUPPLY**

### 10. REFLECTOR OF SCREEN AND DDRAM ADDRESS

| Display position         1-1         1-2         1-3         1-4         1-5         1-6         1-7         1-8           DDRAM address         00         01         02         03         04         05         06         07         08         09           Display position         0A         0B         0C         0D         0E         0F         10         11         12         13           Display position         0B         0C         0D         0E         0F         10         11         12         13           DDRAM address         14         15         16         17         18         19         1A         1B         1C         1D           DDRAM address         1E         1F         20         21         22         23         24         25         26         27           DDRAM address         40         41         42         43         44         45         46         47         48         49           Display position         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         <                                                                                                                                                                                                                                                                                                                                                                                             |                                                                             |          |          |          |          |             |          | _        |          |             |             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------|----------|----------|----------|-------------|----------|----------|----------|-------------|-------------|

| Display position         OR                                                                                                                                                                                                                                                                                                                                                                           | Display p <mark>osi</mark> tion                                             | 1-1      | 1-2      | 1-3      | 1-4      | 1-5         | 1-6      | 1-7      | 1-8      |             | 1           |

| DDRAM address         0A         0B         0C         0D         0E         0F         10         11         12         13           Display position         DDRAM address         14         15         16         17         18         19         1A         1B         1C         1D           Display position         DDRAM address         1E         1F         20         21         22         23         24         25         26         27           Display position         2-1         2-2         2-3         2-4         2-5         2-6         2-7         2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DDRAM address                                                               | 00       | 01       | 02       | 03       | 04          | 05       | 06       | 07       | 08          | 09          |

| Display position         14         15         16         17         18         19         1A         1B         1C         1D           Display position         1E         1F         20         21         22         23         24         25         26         27           Display position         2-1         2-2         2-3         2-4         2-5         2-6         2-7         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8         2-8                                                                                                                                                                                                                                                                                                                                                 | Display position                                                            |          |          |          |          |             |          |          | <br>     | i<br>i      |             |

| DDRAM address         14         15         16         17         18         19         1A         1B         1C         1D           Display position         1E         1F         20         21         22         23         24         25         26         27           Display position         2-1         2-2         2-3         2-4         2-5         2-6         2-7         2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DDRAM address                                                               | 0A       | 0B       | 0C       | 0D       | 0E          | 0F       | 10       | 11       | 12          | 13          |

| Display position         1E         1F         20         21         22         23         24         25         26         27           Display position         2-1         2-2         2-3         2-4         2-5         2-6         2-7         2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Display position                                                            |          |          |          |          | ;<br>!<br>! | <br>     | <br>     | <br>     | ;<br>!<br>! | ;<br>!<br>! |

| DDRAM address         1E         1F         20         21         22         23         24         25         26         27           Display position         2-1         2-2         2-3         2-4         2-5         2-6         2-7         2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DDRAM address                                                               | 14       | 15       | 16       | 17       | 18          | 19       | 1A       | 1B       | 1C          | 1D          |

| Display position         2-1         2-2         2-3         2-4         2-5         2-6         2-7         2-8           DDRAM address         40         41         42         43         44         45         46         47         48         49           Display position         DDRAM address         4A         4B         4C         4D         4E         4F         50         51         52         53           Display position         DDRAM address         54         55         56         57         58         59         5A         5B         5C         5D           Display position         Display position <t< td=""><td>Display position</td><td></td><td> <br/> </td><td></td><td> <br/> </td><td>i<br/>i</td><td> <br/> </td><td> <br/> </td><td> <br/> </td><td> <br/> </td><td>i<br/>!</td></t<> | Display position                                                            |          | <br>     |          | <br>     | i<br>i      | <br>     | <br>     | <br>     | <br>        | i<br>!      |

| DDRAM address         40         41         42         43         44         45         46         47         48         49           Display position         DDRAM address         4A         4B         4C         4D         4E         4F         50         51         52         53           Display position         DDRAM address         54         55         56         57         58         59         5A         5B         5C         5D           Display position         Display positio                                                                                                                                         | DDRAM address                                                               | 1E       | 1F       | 20       | 21       | 22          | 23       | 24       | 25       | 26          | 27          |

| Display position         A         A         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                             |          |          |          |          |             |          |          |          | 1           | 1           |

| DDRAM address         4A         4B         4C         4D         4E         4F         50         51         52         53           Display position         54         55         56         57         58         59         5A         5B         5C         5D           Display position         54         55         56         57         58         59         5A         5B         5C         5D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Display position                                                            | 2-1      | 2-2      | 2-3      | 2-4      | 2-5         | 2-6      | 2-7      | 2-8      |             | !<br>!      |

| Display position  DDRAM address 54 55 56 57 58 59 5A 5B 5C 5D  Display position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |          |          |          |          |             |          |          |          | 48          | 49          |

| DDRAM address         54         55         56         57         58         59         5A         5B         5C         5D           Display position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DDRAM address                                                               |          |          |          |          |             |          |          |          | 48          | 49          |

| Display position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DDRAM address Display position                                              | 40       | 41       | 42       | 43       | 44          | 45       | 46       | 47       |             |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DDRAM address Display position DDRAM address                                | 40       | 41       | 42       | 43       | 44          | 45       | 46       | 47       |             |             |

| DDRAM address 5E 5F 60 61 62 63 64 65 66 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DDRAM address Display position DDRAM address Display position               | 40<br>4A | 41<br>4B | 42<br>4C | 43<br>4D | 44<br>4E    | 45<br>4F | 46<br>50 | 47<br>51 | 52          | 53          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DDRAM address Display position DDRAM address Display position DDRAM address | 40<br>4A | 41<br>4B | 42<br>4C | 43<br>4D | 44<br>4E    | 45<br>4F | 46<br>50 | 47<br>51 | 52          | 53          |

<sup>1-1</sup> means first character of line 1 on screen

| BOOKBINDING AREA |         |                  |      |      |  |  |  |

|------------------|---------|------------------|------|------|--|--|--|

|                  | PRODUCT | MODE NO.         | PAGE | 0/40 |  |  |  |

|                  | SPEC.   | MC20805A6W-GPTLY | PAGE | 9/19 |  |  |  |

## 11. INSTRUCTION TABLE

|                                  |    |     |     | Inst | ructio | on Co | de  |     |     |     |                                                                                                                                               | Execution             |

|----------------------------------|----|-----|-----|------|--------|-------|-----|-----|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Instruction                      | RS | R/W | DB7 | DB6  | DB5    | DB4   | DB3 | DB2 | DB1 | DB0 | Description                                                                                                                                   | Time(fosc=<br>270kHz) |

| Clear Display                    | 0  | 0   | 0   | 0    | 0      | 0     | 0   | 0   | 0   | 1   | Write 20H to DDRAM set DDRAM address to 00H from AC                                                                                           | 1.52ms                |

| Return Home                      | 0  | 0   | 0   | 0    | 0      | 0     | 0   | 0   | 1   | -   | Set DDRAM address to<br>00H from AC and return<br>cursor to its original<br>position if shifted. The<br>contents of DDRAM are<br>not changed. | 1.52ms                |

| Entry Mode<br>Set                | 0  | 0   | 0   | 0    | 0      | 0     | 0   | 1   | I/D | SH  | Assign cursor moving direction and enable the shift of entire display                                                                         | 38 µs                 |

| Display<br>ON/OFF<br>Control     | 0  | 0   | 0   | 0    | 0      | 0     | 1   | D   | С   | В   | Set display(D) cursor(C) and blinking of cursor(B) on/off                                                                                     | 38 µs                 |

| Cursor or<br>Display Shift       | 0  | 0   | 0   | 0    | 0      | 1     | S/C | R/L |     | -/  | Set cursor moving and display shift control bit, and the direction, without changing DDRAM data                                               | 38 µs                 |

| Function Set                     | 0  | 0   | 0   | 0    | 1      | DL    | N   | F   | -   | -   | Set interface data length(DL:8bit/4bit), number of display line (N:2line/1line) and,display font type F:5X11dots / 5X8dots                    | 38 µs                 |

| Set CGRAM<br>Address             | 0  | 0   | 0   | 1    | AC5    | AC4   | AC3 | AC2 | AC1 | AC0 | Set CGRAM address in address counter                                                                                                          | 38 µs                 |

| Set DDRAM<br>Address             | 0  | 0   | 1   | AC6  | AC5    | AC4   | AC3 | AC2 | AC1 | AC0 | Set DDRAM address in address counter                                                                                                          | 38 µs                 |

| Read Busy<br>Flag and<br>Address | 0  | 1   | BF  | AC6  | AC5    | AC4   | AC3 | AC2 | AC1 | AC0 | Whether during internal operation or not can be known by reading BF The contents of address counter can also be read                          | 0 µs                  |

| Write Data to RAM                | 1  | 0   | D7  | D6   | D5     | D4    | D3  | D2  | D1  | D0  | Write data into internal RAM (DDRAM/CGRAM)                                                                                                    | 38 µs                 |

| Read data<br>from RAM            | 1  | 1   | D7  | D6   | D5     | D4    | D3  | D2  | D1  | D0  | Read data from internal RAM (DDRAM/CGRAM)                                                                                                     | 38 µs                 |

# PRODUCT MODE NO. SPEC. MC20805A6W-GPTLY PAGE 10/19

#### 12. INSTRUCTION DESCRIPTION

## A. Clear Display

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing 20H (space code) to all DDRAM address, and set DDRAM address to 00H into AC (address counter).

Return cursor to the original status, namely, bring the cursor to the left edge on the first line of the display.

Make the entry mode increment (I/D = HIGH)

## B. Return Home

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 4   |

Set DDRAM address to 00H into the address counter.

Return cursor to its original site and return display to its original status,if shifted. Contents of DDRAM does not change.

## C. Entry Mode Set

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | SH  |

Set the moving direction of cursor and display.

## I/D:Increment /decrement of DDRAM address(cursor or blink)

I/D=High,cursor/blink moves to right and DDRAM address is increased by 1.

I/D=low,cursor/blink moves to left and DDRAM address is decreased by 1.

\*CGRAM operates the same way as DDRAM, when reading from or writing to CGRAM.

### SH:Shift of entire display

When DDRAM read (CGRAM read/write) operation or SH=Low,shifting of entire display is not performed.if SH=High, and DDRAM write operation,shift of entire display is performed according to I/D value(I/D=High,shift left, I/D=Low, shift right).

#### **BOOKBINDING AREA**

| PRODUCT | MODE NO.         | DAGE | 11/19 |

|---------|------------------|------|-------|

| SPEC.   | MC20805A6W-GPTLY | PAGE | 11/19 |

# D. Display ON/OFF Control

| F | RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|---|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|   | 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В   |

## D:Display ON/OFF control bit

When D=High, entire display is turned on.

When D=Low, display is turned off, but display data remains in DDRAM.

#### C:Cursor ON/OFF control bit

When C=High, cursor is turned on.

When C=Low, cursor is disappeared in current display ,but I/D register preserves its data.

### **B:Cursor Blink ON/OFF control bit**

When B=High, cursor blink is on, which performs alternately between all the High data and display characters at the cursor position.

When B=Low ,blink is off.

# E. Cursor or Display Shift

| RS | R/W | DB7 | DB6 | D <mark>B5</mark> | DB4 | DB3 | DB2 | DB1  | DB0 |

|----|-----|-----|-----|-------------------|-----|-----|-----|------|-----|

| 0  | 0   | 0   | 0   | 0                 | 1   | S/C | R/L | 1.11 | -   |

Shifting of right/left cursor position or display without writing or reading of display data.

This instruction is used to correct or search display data.

During 2-line mode display, cursor moves to the 2<sup>nd</sup> line after the 40<sup>th</sup> digit of the 1<sup>st</sup> line.

Note that display shift is performed simultaneously in all the lines.

When displayed data is shifted repeatedly, each line is shifted individually.

When display shift is performed, the contents of the address counter are not changed.

| S/C | R/L | Operation                                                                 |

|-----|-----|---------------------------------------------------------------------------|

| 0   | 0   | Shift cursor to the left, AC is decreased by 1                            |

| 0   | 1   | Shift cursor to the right, AC is increased by 1                           |

| 1   | 0   | Shift all the display to the left,cursor moves according to the display   |

| 1   | 1   | Shift all the display to the right, cursor moves according to the display |

#### **BOOKBINDING AREA**

| PRODUCT | MODE NO.         | PAGE | 42/40 |

|---------|------------------|------|-------|

| SPEC.   | MC20805A6W-GPTLY | PAGE | 12/19 |

## F. Function set

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 0   | 1   | DL  | N   | F   | -   | -   |

## DL:Interface data length control bit

When DL=High, it means 8-bit bus mode with MPU.

When DL=Low, it means 4-bit bus mode with MPU.

When 4-bit bus mode, it needs to transfer 4-bit data twice.

## N:Display line number control bit

When N=Low, 1-line display mode is set.

When N=High, 2-line display mode is set.

## F:Display font type control bit

When F=Low, 5x8 dots format display mode is set.

When F=High, 5x11 dots format display mode.

## G. Set CGRAM Address

| RS | R/W | DB7 | DB6 | D <mark>B5</mark> | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-------------------|-----|-----|-----|-----|-----|

| 0  | 0   | 0   | 1   | AC5               | AC4 | AC3 | AC2 | AC1 | AC0 |

Set CGRAM address to AC.

This instruction makes CGRAM data available from MPU.

## H. Set DDRAM Address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set DDRAM address to AC.

This instruction makes DDRAM data available from MPU.

When 1-line display mode (N=Low), DDRAM address is from 00H to 4FH In 2-line display mode(N=High), DDRAM address in the 1<sup>st</sup> line is from 00H to 27H and DDRAM address in the 2<sup>nd</sup> line is from 40H to 67H

# PRODUCT MODE NO. SPEC. MC20805A6W-GPTLY PAGE 13/19

## I. Read Busy Flag & Address

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0  | 1   | BF  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

This instruction shows whether IC is in internal operation or not.

If BF is High, internal operation is in progress and shall wait until BF is to be Low, which by then the next instruction can be performed. In this instruction you and also read the value of the address counter.

## J. Write data to RAM

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Write binary 8-bit data to DDRAM/CGRAM.

The selection of RAM from DDRAM, and CGRAM, is set by the previous address set instruction (DDRAM address set, CGRAM address set).

RAM set instruction can also determine the AC direction to RAM.

After write operation, the address is automatically increased /decreased by 1,according the entry mode.

## K. Read data from RAM

| RS | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 1  | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Read binary 8-bit data from DDRAM/CGRAM.

The selection of RAM is set by the previous address set instruction. If the address set instruction of RAM is not performed before this instruction, the data that has been read first is invalid, as the direction of AC is not yet determined. If RAM data is read several times without RAM address instructions set before read operation, the correct RAM data can be obtained from the second. But the first data would be incorrect, as there is no time margin to transfer RAM data.

|   | BOOKBINDING AREA | 1                |      |       |

|---|------------------|------------------|------|-------|

|   | PRODUCT          | MODE NO.         | DAGE | 14/19 |

| 1 | SPEC.            | MC20805A6W-GPTLY | PAGE | 14/19 |

In case of DDRAM read operation, cursor shift instruction plays the same role as DDRAM address set instruction, it also transfers RAM data to output data register.

After read operation, address counter is automatically increased/decreased by 1 according to the entry mode.

After CGRAM read operation, display shift may not be executed correctly.

Note:In case of RAM write operation,AC is increased/decreased by 1 as in read operation.

At this time,AC indicates the next address position, but only the previous data can be read by the read instruction.

#### 13. RELATIONSHIP BETWEEN CHARACTER CODE AND CGRAM

|    | С  | haı | act | ter ( | COC | de   |    | C  | GR | AM | Ad | dre | SS |    |    | CG | RAI | M D | ata |    |    | Pattern   |

|----|----|-----|-----|-------|-----|------|----|----|----|----|----|-----|----|----|----|----|-----|-----|-----|----|----|-----------|

| D7 | D6 | D5  | D4  | D3    | D2  | 2 D1 | D0 | A5 | A4 | А3 | A2 | A1  | A0 | P7 | P6 | P5 | P4  | P3  | P2  | P1 | P0 | number    |

| 0  | 0  | 0   | 0   | Х     | 0   | 0    | 0  | 0  | 0  | 0  | 0  | 0   | 0  | Х  | Χ  | Х  | 0   | 1   | 1   | 1  | 0  | pattern 1 |

|    |    |     |     |       |     |      |    |    |    |    | 0  | 0   | 1  | Χ  | Χ  | Χ  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     | :     |     |      |    |    |    |    | 0  | 1   | 0  | Χ  | Χ  | Χ  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 0  | 1   | 1  | X  | X  | Х  | 1   | 1   | 1   | 1  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 1  | 0   | 0  | X  | X  | Χ  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 1  | 0   | 1  | Х  | Χ  | Х  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 1  | 1   | 0  | X  | X  | X  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     |       |     | V .  |    |    |    |    | 1  | 1   | 1  | Х  | X  | X  | 0   | 0   | 0   | 0  | 0  |           |

|    |    |     |     |       |     | V    |    |    |    |    |    |     |    |    |    |    |     |     |     |    |    |           |

|    |    |     |     |       |     |      |    |    |    |    |    |     |    |    |    |    |     |     |     |    |    |           |

| 0  | 0  | 0   | 0   | Х     | 1   | 1    | 1  | 0  | 0  | 0  | 0  | 0   | 0  | Х  | Х  | Х  | 1   | 0   | 0   | 0  | 1  | pattern8  |

|    |    |     | Ū   | ,     | •   | ·    | •  |    |    | Ū  | 0  | 0   | 1  | X  | Х  | X  | 1   | 0   | 0   | 0  | 1  | pattorno  |

|    |    |     |     |       |     |      |    |    |    |    | 0  | 1   | 0  | Х  | Χ  | х  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 0  | 1   | 1  | Х  | Χ  | Х  | 1   | 1   | 1   | 1  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 1  | 0   | 0  | Х  | Χ  | Х  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 1  | 0   | 1  | Х  | Χ  | Х  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     | •     |     |      |    |    | •  |    | 1  | 1   | 0  | Х  | Χ  | Х  | 1   | 0   | 0   | 0  | 1  |           |

|    |    |     |     |       |     |      |    |    |    |    | 1  | 1   | 1  | Х  | Х  | Χ  | 0   | 0   | 0   | 0  | 0  |           |

## 14. DISPLAY DATA RAM(DDRAM)

DDRAM stores display data of maximum 80x8 bits(80 characters). DDRAM address is set in the address counter(AC) as a hexadecimal number

| MSB |     |     |     |     |     | LSB |

|-----|-----|-----|-----|-----|-----|-----|

| AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

| BOOKBIN | IDING AREA |                  |      |       |

|---------|------------|------------------|------|-------|

|         | PRODUCT    | MODE NO.         | DAGE | 15/19 |

|         | SPEC.      | MC20805A6W-GPTLY | PAGE | 15/19 |

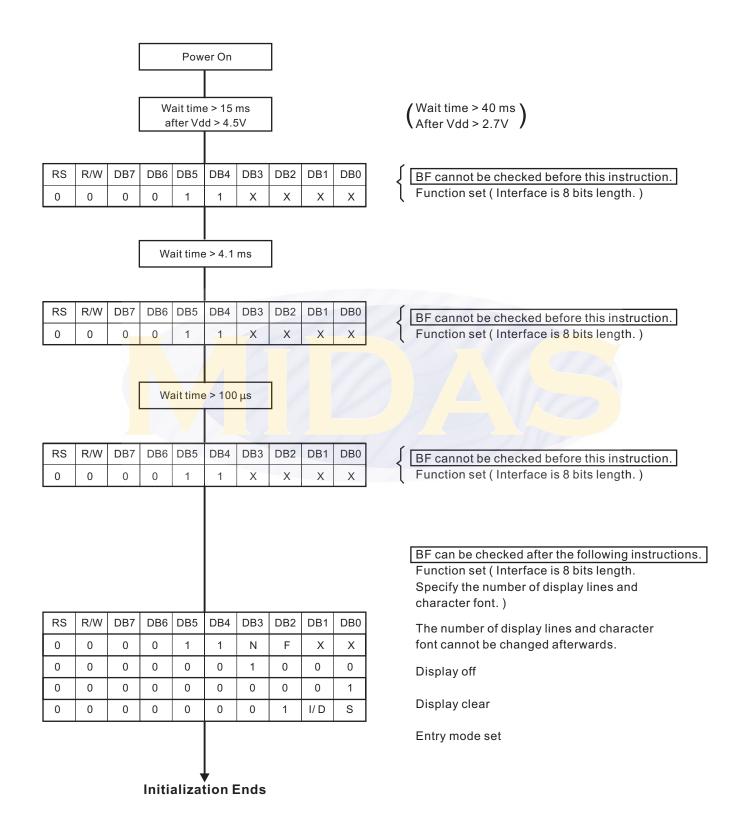

#### 15. INITIALIZATION

## 15.1 8-bit interface mode (Condition: fosc = 270KHZ)

| воок | BINDING AREA |                  |      |       |

|------|--------------|------------------|------|-------|

|      | PRODUCT      | MODE NO.         | PAGE | 16/10 |

|      | SPEC.        | MC20805A6W-GPTLY | PAGE | 10/19 |

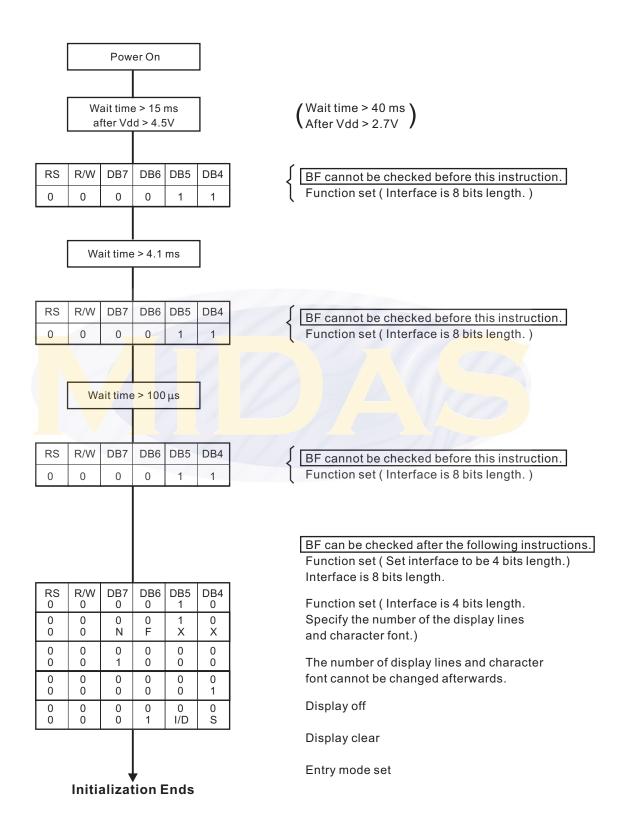

## 15.2 4-bit interface mode (Condition: fosc = 270KHZ)

| BOOKBINDING AREA | 1                |      |       |

|------------------|------------------|------|-------|

| PRODUCT          | MODE NO.         | DAGE | 17/19 |

| SPEC.            | MC20805A6W-GPTLY | PAGE | 17/19 |

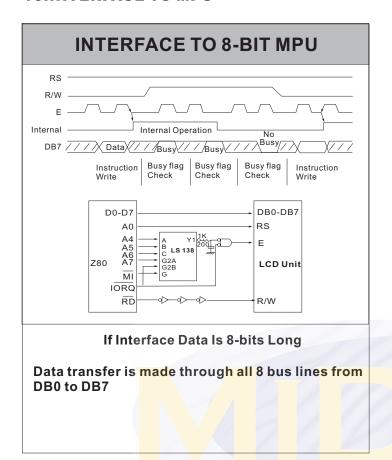

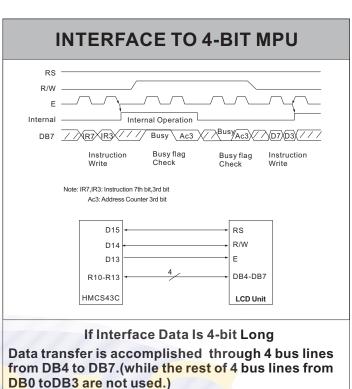

#### **16.INTERFACE TO MPU**

Data transfer is completed when 4-bits of data is transferred twice.(upper 4-bits of data, then lower

#### **Features**

- 1. Interface to an 8-bit or 4-bit MPU is available.

- 2. 192 types of alphanumeric, symbols and special characters can be displayed with the built in character generator (ROM).

4-bits of data.)

- 3. Other preferred characters can be displayed by character generator (RAM).

- 4. Various instructions may be programmed.

- Clear display

- Cursor at home

- On/Off cursor

- Blink character

- Shift display

- Shift cursor

- Read/Write display data .etc.

- 5. Compact and light weight design which can easily be integrated into end products.

- 6. Single power supply +5V drive (except for extended temperature type).

- 7. Low power consumption.

| BOOKBIN | DING AREA |                  |      |       |

|---------|-----------|------------------|------|-------|

|         | PRODUCT   | MODE NO.         | DAGE | 18/19 |

|         | SPEC.     | MC20805A6W-GPTLY | PAGE | 10/19 |

## **17. STANDARD FONT MAP**

| Upper<br>4bit<br>Lower | LLLL             | LLLH | LLHL | LLHH | LHLL | LHLH | LHHL | LHHH | HLLL | HLLH | HLHL | НЬНН | HHLL | ннгн | HHHL | нннн |

|------------------------|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 4bit LLLL              | CG<br>RAM<br>(1) |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLLH                   | (2)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLHL                   | (3)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LLHH                   | (4)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHLL                   | (5)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHLH                   | (6)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHHL                   | (7)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| LHHH                   | (8)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLLL                   | (1)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLLH                   | (2)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HLHL                   | (3)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| НГНН                   | (4)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHLL                   | (5)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHLH                   | (6)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| HHHL                   | (7)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| нннн                   | (8)              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| воок | BINDING AREA |                  |      |       |

|------|--------------|------------------|------|-------|

|      | PRODUCT      | MODE NO.         | DAGE | 19/19 |

|      | SPEC.        | MC20805A6W-GPTLY | PAGE | 19/19 |

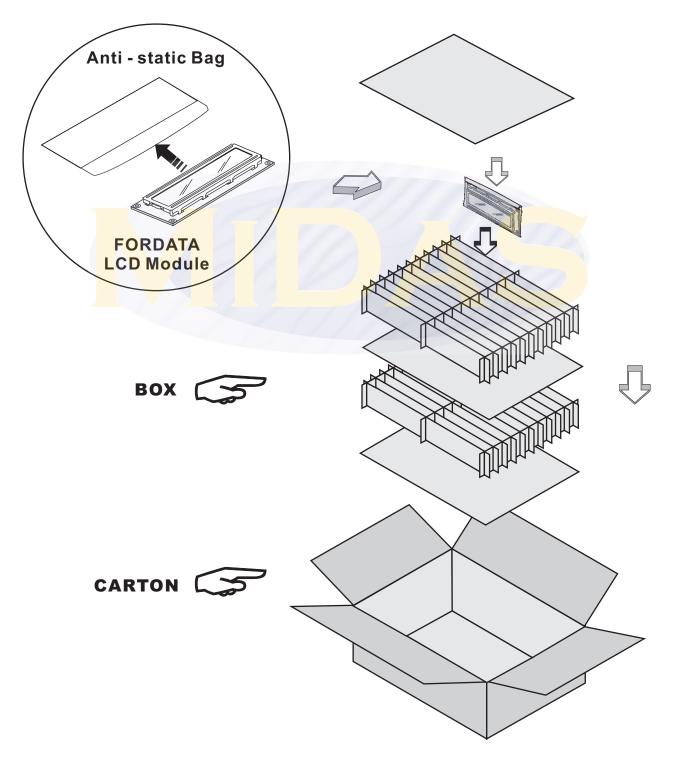

## **18. PACKING DETAIL**

| WITH LED BKL                | WI  |

|-----------------------------|-----|

| 45 PCS/BOX                  | 45  |

| 10 BOXES/CARTON             | 10  |

| 450 PCS/CARTON              | 450 |

| 18.00 KGS/CTN(G.W.)         | 16. |

| 0.07 M <sup>3</sup> /CARTON | 0.0 |

| WITHOUT LED BKL     |

|---------------------|

| 45 PCS/BOX          |

| 10 BOXES/CARTON     |

| 450 PCS/CARTON      |

| 16.00 KGS/CTN(G.W.) |

| 0.07 M³/CARTON      |

## NOTE

- 1. The weight is estimated for reference only.

- 2. Packing detail may be changed without notice.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

## Click to view similar products for midas manufacturer:

Other Similar products are found below:

MCT070LA12W1024600LML MCOT128064BY-WM MCOB21609AV-EWP MC42004A6W-SPTLY MC22008B6W-SPR

MCT035G12W320240LML MC11605A6WR-SPTLY-V2 MC21605H6W-BNMLW-V2 MCOT048064A1V-YI

MCT101E0CW1280800LMLIPS MCT104A0W1024768LML MCT070Z0W800480LML MCT0144C6W128128PML MCIB-16-LVDSCABLE MC41605A6W-FPTLA-V2 MCOT128064UA1V-WM MCT101E0TW1280800LMLIPS MCT150B0W1024768LML

MCT050HDMI-A-RTP MCT050HDMI-A-CTP MCT070Z0TW1W800480LML MCT050ACA0CW800480LML MC42008A6W-SPTLY

MC42005A12W-VNMLY MC42005A12W-VNMLG MCT052A6W480128LML MC21605A6WK-BNMLW-V2 MCOT256064A1A-BM

MCOT22005A1V-EYM MC20805A12W-VNMLG MC21605B6WD-BNMLW-V2 MC22405A6WK-BNMLW-V2 MC41605A6WKFPTLW-V2 MCT101HDMI-A-RTP MCT024L6W240320PML MCCOG21605D6W-FPTLWI MC21605A6WD-SPTLY-V2

MC22005A6WK-BNMLW-V2 MC24005AA6W9-BNMLW-V2 MC42004A6WK-SPTLY-V2 MC11609A6W-SPTLY-V2

MC07064048A1V-YM MCOT128064BY-BM MCCOG128064B12W-FPTLRGB MC11609A6W-SPR-V2 MC21605H6WK-BNMLW-V2

MCOT128064E1V-BM MCT070HDMI-B-RTP MDT5000C MCCOG42005A6W-BNMLWI