#

# Dual, 10-Bit, 80Msps, Current-Output DAC

### **General Description**

The MAX5853 dual, 10-bit, 80Msps digital-to-analog converter (DAC) provides superior dynamic performance in wideband communication systems. The device integrates two 10-bit DAC cores, and a 1.24V reference. The converter supports single-ended and differential modes of operation. The MAX5853 dynamic performance is maintained over the entire 2.7V to 3.6V power-supply operating range. The analog outputs support a -1.0V to +1.25V compliance voltage.

The MAX5853 can also operate in interleave data mode to reduce the I/O pin count. This allows the converter to be updated on a single, 10-bit bus.

The MAX5853 features digital control of channel gain matching to within ±0.4dB in sixteen 0.05dB steps. Channel matching improves sideband suppression in analog quadrature modulation applications. The onchip 1.24V bandgap reference includes a control amplifier that allows external full-scale adjustments of both channels through a single resistor. The internal reference can be disabled and an external reference may be applied for high-accuracy applications.

The MAX5853 features full-scale current outputs of 2mA to 20mA and operates from a 2.7V to 3.6V single supply. The DAC supports three modes of power-control operation: normal, low-power standby, and complete powerdown. In power-down mode, the operating current is reduced to 1µA.

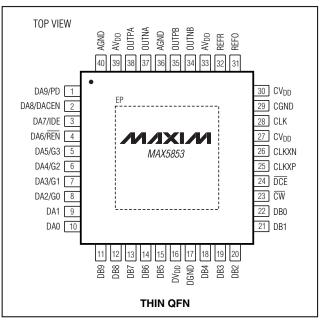

The MAX5853 is packaged in a 40-pin thin QFN with exposed paddle (EP) and is specified for the extended (-40°C to +85°C) temperature range.

Pin-compatible, higher speed, and lower resolution versions are also available. Refer to the MAX5854 (10-bit, 165Msps), the MAX5852\*\* (8-bit, 165Msps), and the MAX5851\*\* (8-bit, 80Msps) data sheets for more information. See Table 4 at the end of the data sheet.

### **Applications**

Communications SatCom, LMDS, MMDS, HFC, DSL, WLAN, Point-to-Point Microwave Links

Wireless Base Stations Quadrature Modulation Direct Digital Synthesis (DDS) Instrumentation/ATE

\*\*Future product—contact factory for availability.

### **Features**

- ♦ 10-Bit, 80Msps Dual DAC

- **♦ Low Power** 77mW with IFS = 5mA at fCLK = 80MHz

- ♦ 2.7V to 3.6V Single Supply

- ◆ Full Output Swing and Dynamic Performance at 2.7V Supply

- **♦** Superior Dynamic Performance 78dBc SFDR at four = 20MHz

- Programmable Channel Gain Matching

- ♦ Integrated 1.24V Low-Noise Bandgap Reference

- **♦ Single-Resistor Gain Control**

- ♦ Interleaved Data Mode

- ♦ Single-Ended and Differential Clock Input Modes

- ♦ Miniature 40-Pin Thin QFN Package, 6mm x 6mm

- ♦ EV Kit Available—MAX5854 EV Kit

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE     |

|------------|----------------|-----------------|

| MAX5853ETL | -40°C to +85°C | 40 Thin QFN-EP* |

<sup>\*</sup>EP = Exposed paddle.

### Pin Configuration

#### **ABSOLUTE MAXIMUM RATINGS**

| AVDD to AGND0.3V to +4V DVDD to DGND0.3V to +4V CVDD to CGND0.3V to +4V AVDD to DVDD4V to +4V AGND to DGND0.3V to +0.3V AGND to CGND0.3V to +0.3V DGND to CGND0.3V to +0.3V DA9-DA0, DB9-DB0, CW, DCE to DGND0.3V to +4V CLK to CGND0.3V to (CVDD + 0.3V) CLKXN, CLKXP to CGND0.3V to (AVDD + 0.3V) REFR, REFO to AGND0.3V to (AVDD + 0.3V) | OUTPA, OUTNA to AGND(AVDD - 4.8V) to (AVDD + 0.3V) OUTPB, OUTNB to AGND(AVDD - 4.8V) to (AVDD + 0.3V) Maximum Current into Any Pin (excluding power supplies) |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(AV_{DD} = DV_{DD} = 3V, AGND = DGND = CGND = 0, f_{DAC} = 80Msps, differential clock, external reference, V_{REF} = 1.2V, I_{FS} = 20mA$ , differential output, output amplitude = 0dBFS,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $T_A \ge +25^{\circ}C$ , guaranteed by production test.  $T_A < +25^{\circ}C$  guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                      | SYMBOL | CONI                                                                                           | DITIONS                                   | MIN   | TYP   | MAX   | UNITS  |

|------------------------------------------------|--------|------------------------------------------------------------------------------------------------|-------------------------------------------|-------|-------|-------|--------|

| STATIC PERFORMANCE                             |        |                                                                                                |                                           |       |       |       |        |

| Resolution                                     | N      |                                                                                                |                                           | 10    |       |       | Bits   |

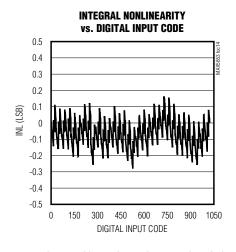

| Integral Nonlinearity                          | INL    | $R_L = 0$                                                                                      |                                           | -1.0  | ±0.25 | +1.0  | LSB    |

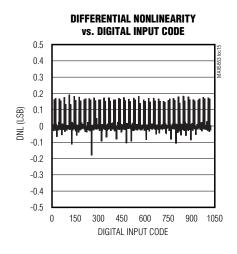

| Differential Nonlinearity                      | DNL    | Guaranteed monotor                                                                             | nic, R <sub>L</sub> = 0                   | -0.5  | ±0.2  | +0.5  | LSB    |

| Offset Error                                   | Vos    |                                                                                                |                                           | -0.5  | ±0.1  | +0.5  | LSB    |

| Gain Error (See Also Gain Error                | GE     | Internal reference (N                                                                          | ote1)                                     | -11.0 | ±1.5  | +6.8  | %FSR   |

| Definition Section)                            | GE     | ` ,                                                                                            |                                           | -6.25 | ±0.7  | +4.10 | %F5R   |

| Cain Funay Tananawatu ya Duift                 |        | Internal reference                                                                             |                                           |       | ±150  |       | 0.07   |

| Gain-Error Temperature Drift                   |        | External reference                                                                             |                                           |       | ±100  |       | ppm/°C |

| DYNAMIC PERFORMANCE                            |        |                                                                                                |                                           |       |       |       |        |

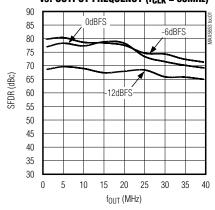

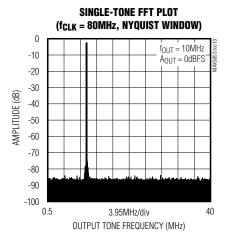

|                                                |        | f <sub>CLK</sub> = 80MHz,<br>A <sub>OUT</sub> = -1dBFS                                         | f <sub>OUT</sub> = 10MHz                  | 69.5  | 78    |       |        |

|                                                |        |                                                                                                | f <sub>OUT</sub> = 20MHz                  |       | 78    |       |        |

|                                                | SFDR   |                                                                                                | fout = 30MHz                              |       | 72    |       |        |

| Spurious-Free Dynamic Range to Nyquist         |        | f <sub>CLK</sub> = 44MHz,<br>A <sub>OUT</sub> = -1dBFS                                         | f <sub>OUT</sub> = 10MHz                  | 78    |       |       | dBc    |

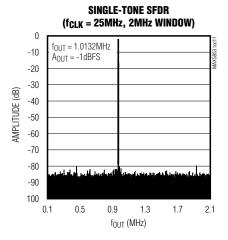

|                                                |        | f <sub>CLK</sub> = 25MHz,<br>A <sub>OUT</sub> = -1dBFS                                         | f <sub>OUT</sub> = 1MHz                   | 79    |       |       |        |

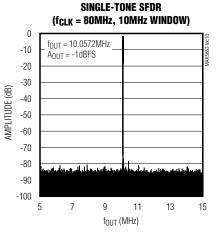

|                                                |        | f <sub>CLK</sub> = 80MHz, f <sub>OUT</sub> = 10MHz,<br>A <sub>OUT</sub> = -1dBFS, span = 10MHz |                                           |       | 85    |       |        |

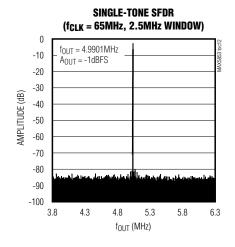

| Spurious-Free Dynamic Range<br>Within a Window | SFDR   | f <sub>CLK</sub> = 65MHz, f <sub>OUT</sub> = 5MHz,<br>A <sub>OUT</sub> = -1dBFS, span = 2.5MHz |                                           |       | 82    |       | dBc    |

|                                                |        | f <sub>CLK</sub> = 25MHz, f <sub>OUT</sub> = 1MHz,<br>A <sub>OUT</sub> = -1dBFS, span = 2MHz   |                                           |       | 82    |       |        |

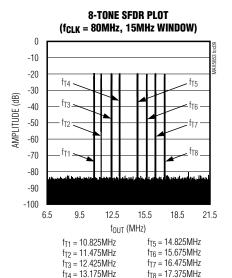

| Multitone Power Ratio to Nyquist               | MTPR   | 8 tones at 400kHz sp<br>f <sub>OUT</sub> = 15MHz to 18.                                        | pacing, f <sub>CLK</sub> = 78MHz,<br>2MHz |       | 74    |       | dBc    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = DVDD = CVDD = 3V, AGND = DGND = CGND = 0,  $f_{DAC}$  = 80Msps, differential clock, external reference,  $V_{REF}$  = 1.2V,  $I_{FS}$  = 20mA, differential output, output amplitude = 0dBFS,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $T_A \ge +25^{\circ}\text{C}$ , guaranteed by production test.  $T_A < +25^{\circ}\text{C}$  guaranteed by design and characterization. Typical values are at  $T_A$  =  $+25^{\circ}\text{C}$ .)

| PARAMETER                                                | SYMBOL              | CONDITIONS                                             |                                                                                            | MIN   | TYP   | MAX   | UNITS   |

|----------------------------------------------------------|---------------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------|-------|-------|-------|---------|

| Multitone Spurious-Free Dynamic<br>Range Within a Window |                     |                                                        | 8 tones at 811kHz spacing, $f_{CLK}$ = 80MHz, $f_{OUT}$ = 10.8MHz to 17.2MHz, span = 15MHz |       | 76    |       | dBc     |

|                                                          |                     |                                                        | f <sub>OUT</sub> = 10MHz                                                                   |       | -76   |       |         |

|                                                          |                     | f <sub>CLK</sub> = 80MHz,<br>A <sub>OUT</sub> = -1dBFS | f <sub>OUT</sub> = 20MHz                                                                   |       | -75   |       |         |

| Total Harmonic Distortion to                             |                     | A001 = -1dbi 3                                         | f <sub>OUT</sub> = 30MHz                                                                   |       | -70   |       |         |

| Nyquist (2nd- Through 8th-Order<br>Harmonics Included)   | THD                 | f <sub>CLK</sub> = 44MHz,<br>A <sub>OUT</sub> = -1dBFS | f <sub>OUT</sub> = 10MHz                                                                   |       | -76   |       | dBc     |

|                                                          |                     | f <sub>CLK</sub> = 25MHz,<br>A <sub>OUT</sub> = -1dBFS | f <sub>OUT</sub> = 1MHz                                                                    |       | -76   |       |         |

| Output Channel-to-Channel Isolation                      |                     | f <sub>OUT</sub> = 10MHz                               |                                                                                            |       | 90    |       | dB      |

| Channel-to-Channel Gain<br>Mismatch                      |                     | f <sub>OUT</sub> = 10MHz, G[3:                         | 0] = 1000                                                                                  |       | 0.025 |       | dB      |

| Channel-to-Channel Phase<br>Mismatch                     |                     | fout = 10MHz                                           |                                                                                            |       | 0.05  |       | Degrees |

| Circulto Naisa Datia ta Niversiat                        | CNID                | $f_{CLK} = 80MHz$ , $f_{OUT} = 5MHz$ , $I_{FS} = 20mA$ |                                                                                            |       | 62    |       | ٩D      |

| Signal-to-Noise Ratio to Nyquist                         | SNR                 | $f_{CLK} = 80MHz$ , $f_{OUT} = 5MHz$ , $I_{FS} = 5mA$  |                                                                                            |       | 62    |       | dB      |

| Maximum DAC Conversion Rate                              | fores               | Interleaved mode di                                    | Interleaved mode disabled, IDE = 0                                                         |       |       |       | Msps    |

| Maximum DAC Conversion hate                              | †DAC                | Interleaved mode er                                    | nabled, IDE = 1                                                                            | 80    |       |       | IVISPS  |

| Glitch Impulse                                           |                     |                                                        |                                                                                            |       | 5     |       | pV-s    |

| Output Settling Time                                     | ts                  | To ±0.1% error band                                    | d (Note 3)                                                                                 |       | 12    |       | ns      |

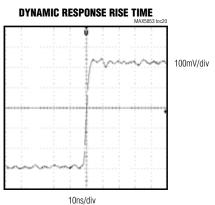

| Output Rise Time                                         |                     | 10% to 90% (Note 3                                     | )                                                                                          |       | 2.2   |       | ns      |

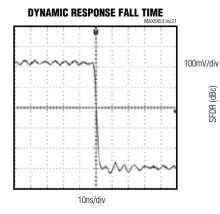

| Output Fall Time                                         |                     | 90% to 10% (Note 3                                     | 3)                                                                                         |       | 2.2   |       | ns      |

| ANALOG OUTPUT                                            |                     |                                                        |                                                                                            |       |       |       |         |

| Full-Scale Output Current Range                          | I <sub>FS</sub>     |                                                        |                                                                                            | 2     |       | 20    | mA      |

| Output Voltage Compliance<br>Range                       |                     |                                                        |                                                                                            | -1.00 |       | +1.25 | V       |

| Output Leakage Current                                   |                     | Shutdown or standby mode                               |                                                                                            | -5    |       | +5    | μΑ      |

| REFERENCE                                                | l.                  | 1                                                      |                                                                                            | •     |       |       |         |

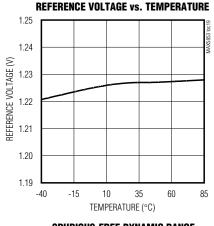

| Internal-Reference Output<br>Voltage                     | VREFO               | REN = 0                                                |                                                                                            | 1.13  | 1.24  | 1.32  | V       |

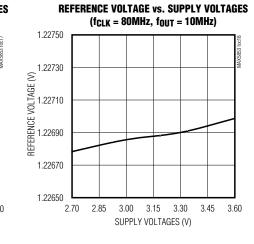

| Internal-Reference Supply<br>Rejection                   |                     | AV <sub>DD</sub> varied from 2.7V to 3.6V              |                                                                                            |       | 0.5   |       | mV/V    |

| Internal-Reference Output-<br>Voltage Temperature Drift  | TCV <sub>REFO</sub> | REN = 0                                                |                                                                                            |       | ±50   |       | ppm/°C  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = CV_{DD} = 3V, AGND = DGND = CGND = 0, f_{DAC} = 80Msps, differential clock, external reference, V_{REF} = 1.2V, I_{FS} = 20mA$ , differential output, output amplitude = 0dBFS,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $T_A \ge +25^{\circ}C$ , guaranteed by production test.  $T_A < +25^{\circ}C$  guaranteed by design and characterization. Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                                  | SYMBOL                            | CONDITIONS                                   | MIN                        | TYP                 | MAX                       | UNITS |

|--------------------------------------------|-----------------------------------|----------------------------------------------|----------------------------|---------------------|---------------------------|-------|

| Internal-Reference Output Drive Capability |                                   | REN = 0                                      |                            | 50                  |                           | μΑ    |

| External-Reference Input Voltage Range     |                                   | REN = 1                                      | 0.10                       | 1.2                 | 1.32                      | V     |

| Current Gain                               | I <sub>FS</sub> /I <sub>REF</sub> |                                              |                            | 32                  |                           | mA/mA |

| LOGIC INPUTS (DA9-DA0, DB9-                | DB0, $\overline{\text{CW}}$ )     |                                              |                            |                     |                           |       |

| Digital Input-Voltage High                 | VIH                               |                                              | 0.65 x<br>DV <sub>DD</sub> |                     |                           | V     |

| Digital Input-Voltage Low                  | V <sub>IL</sub>                   |                                              |                            |                     | $0.3 \times DV_{DD}$      | V     |

| Digital Input Current                      | I <sub>IN</sub>                   |                                              | -1                         |                     | +1                        | μΑ    |

| Digital Input Capacitance                  | CIN                               |                                              |                            | 3                   |                           | рF    |

| SINGLE-ENDED CLOCK INPUT/0                 | OUTPUT AND                        | DEE INPUT (CLK, DEE)                         |                            |                     |                           |       |

| Digital Input-Voltage High                 | VIH                               | DCE = 1                                      | 0.65 x<br>CV <sub>DD</sub> |                     |                           | ٧     |

| Digital Input-Voltage Low                  | VIL                               | DCE = 1                                      |                            |                     | 0.3 x<br>CV <sub>DD</sub> | V     |

| Digital Input Current                      | I <sub>IN</sub>                   | DCE = 1                                      | -1                         |                     | +1                        | μΑ    |

| Digital Input Capacitance                  | CIN                               | DCE = 1                                      |                            | 3                   |                           | рF    |

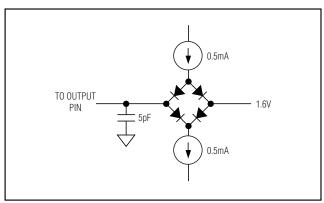

| Digital Output-Voltage High                | Voн                               | DCE = 0, ISOURCE = 0.5mA, Figure 1           | 0.9 x<br>CV <sub>DD</sub>  |                     |                           | V     |

| Digital Output-Voltage Low                 | V <sub>OL</sub>                   | DCE = 0, I <sub>SINK</sub> = 0.5mA, Figure 1 |                            |                     | 0.1 x<br>CV <sub>DD</sub> | V     |

| DIFFERENTIAL CLOCK INPUTS                  | (CLKXP/CLK)                       | (N)                                          |                            |                     |                           |       |

| Differential Clock Input Internal Bias     |                                   |                                              |                            | CV <sub>DD</sub> /2 |                           | V     |

| Differential Clock Input Swing             |                                   |                                              | 0.5                        |                     |                           | V     |

| Clock Input Impedance                      |                                   | Measured single ended                        |                            | 5                   |                           | kΩ    |

| POWER REQUIREMENTS                         |                                   |                                              |                            |                     |                           |       |

| Analog Power-Supply Voltage                | $AV_{DD}$                         |                                              | 2.7                        | 3                   | 3.6                       | V     |

| Digital Power-Supply Voltage               | DV <sub>DD</sub>                  |                                              | 2.7                        | 3                   | 3.6                       | V     |

| Clock Power-Supply Voltage                 | CV <sub>DD</sub>                  |                                              | 2.7                        | 3                   | 3.6                       | V     |

|                                            |                                   | IFS = 20mA (Note 2), single-ended clock mode |                            | 43.2                | 46                        |       |

| Analog Supply Current                      | lavdd                             | IFS = 20mA (Note 2), differential clock mode |                            | 43.2                |                           | mA    |

| Analog Supply Culterit                     | IAVDD                             | IFS = 2mA (Note 2), single-ended clock mode  |                            | 5                   |                           | IIIA  |

|                                            |                                   | IFS = 2mA (Note 2), differential clock mode  |                            | 5                   |                           |       |

### **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = DVDD = CVDD = 3V, AGND = DGND = CGND = 0,  $f_{DAC}$  = 80Msps, differential clock, external reference,  $V_{REF}$  = 1.2V,  $I_{FS}$  = 20mA, differential output, output amplitude = 0dBFS,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.  $T_A \ge +25^{\circ}\text{C}$ , guaranteed by production test.  $T_A < +25^{\circ}\text{C}$  guaranteed by design and characterization. Typical values are at  $T_A$  =  $+25^{\circ}\text{C}$ .)

| PARAMETER                                                 | SYMBOL            | COND                                                     | ITIONS                                                   | MIN   | TYP  | MAX  | UNITS           |

|-----------------------------------------------------------|-------------------|----------------------------------------------------------|----------------------------------------------------------|-------|------|------|-----------------|

| Digital Supply Current                                    | I <sub>DVDD</sub> | I <sub>FS</sub> = 20mA (Note 2), single-ended clock mode |                                                          |       | 3.4  | 4    | mA              |

|                                                           |                   | I <sub>FS</sub> = 20mA (Note 2),                         | differential clock mode                                  |       | 3.4  |      |                 |

| Clock Supply Current                                      | ICVDD             | Single-ended clock m<br>(Note 2)                         | node (DCE = 1)                                           |       | 11.1 | 13.5 | mA              |

|                                                           |                   | Differential clock mod                                   | le ( $\overline{DCE} = 0$ ) (Note 2)                     |       | 16.7 |      |                 |

| Total Standby Current                                     | ISTANDBY          | IAVDD + IDVDD + ICVD                                     | D                                                        |       | 3.1  | 3.7  | mA              |

| Total Shutdown Current                                    | ISHDN             | IAVDD + IDVDD + ICVD                                     | D                                                        |       | 1    |      | μΑ              |

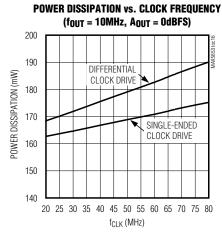

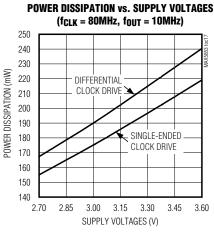

|                                                           |                   | Single-ended clock                                       | I <sub>FS</sub> = 20mA (Note 2)                          |       | 173  | 191  |                 |

|                                                           |                   | mode ( $\overline{DCE} = 1$ )                            | I <sub>FS</sub> = 2mA (Note 2)                           |       | 58   |      |                 |

| Total Dawer Dissipation                                   | Dene              | Differential clock<br>mode (DCE = 0)                     | I <sub>FS</sub> = 20mA (Note 2)                          |       | 190  |      | mW              |

| Total Power Dissipation                                   | P <sub>TOT</sub>  |                                                          | I <sub>FS</sub> = 2mA (Note 2)                           |       | 75   |      |                 |

|                                                           |                   | Standby                                                  |                                                          | 9.3   | 11.1 |      |                 |

|                                                           |                   | Shutdown                                                 |                                                          | 0.003 |      |      |                 |

| TIMING CHARACTERISTICS (F                                 | Figures 5 and 6)  |                                                          |                                                          |       |      |      |                 |

| Propagation Delay                                         |                   |                                                          |                                                          |       | 1    |      | Clock<br>cycles |

| DAC Data to CLK Rise/Fall                                 |                   | Single-ended clock ma                                    | ingle-ended clock mode ( $\overline{DCE} = 1$ ) (Note 4) |       |      |      |                 |

| Setup Time                                                | tDCS              | Differential clock mod                                   | le (DCE = 0) (Note 4)                                    | 2.7   |      |      | ns              |

| DAC Data to CLK Rise/Fall                                 |                   | Single-ended clock ma                                    | 0.8                                                      |       |      |      |                 |

| Hold Time                                                 | tDCH              | Differential clock mod                                   | le (DCE = 0) (Note 4)                                    | -0.5  |      |      | ns              |

| Control Word to $\overline{\text{CW}}$ Rise<br>Setup Time | tcs               |                                                          |                                                          | 2.5   |      |      | ns              |

| Control Word to $\overline{\text{CW}}$ Rise<br>Hold Time  | tcw               |                                                          |                                                          | 2.5   |      |      | ns              |

| CW High Time                                              | tcwH              |                                                          |                                                          | 5     |      |      | ns              |

| <del>CW</del> Low Time                                    | tcwL              |                                                          |                                                          | 5     |      |      | ns              |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(AV_{DD} = DV_{DD} = 3V, AGND = DGND = CGND = 0, f_{DAC} = 80Msps, differential clock, external reference, V_{REF} = 1.2V, I_{FS} = 20mA, differential output, output amplitude = 0dBFS, T_A = T_{MIN} to T_{MAX}, unless otherwise noted. T_A <math>\geq$  +25°C, guaranteed by production test. T\_A < +25°C guaranteed by design and characterization. Typical values are at T\_A = +25°C.)

| PARAMETER                                                         | SYMBOL | CONDITIONS           | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------------|--------|----------------------|-----|-----|-----|-------|

| DACEN = 1 to V <sub>OUT</sub> Stable Time (Coming Out of Standby) | tstb   |                      |     | 3   |     | μs    |

| PD = 0 to V <sub>OUT</sub> Stable Time (Coming Out of Power-Down) | tshdn  |                      |     | 500 |     | μs    |

| Maximum Clock Frequency at CLKXP/CLKXN Input                      | fCLK   |                      | 80  |     |     | MHz   |

| Clock High Time                                                   | tcxH   | CLKXP or CLKXN input |     | 3   |     | ns    |

| Clock Low Time                                                    | tCXL   | CLKXP or CLKXN input |     | 3   |     | ns    |

| CLKXP Rise to CLK Output<br>Rise Delay                            | tCDH   | DCE = 0              |     | 2.7 |     | ns    |

| CLKXP Fall to CLK Output<br>Fall Delay                            | tCDL   | DCE = 0              |     | 2.7 |     | ns    |

Note 1: Including the internal reference voltage tolerance and reference amplifier offset.

**Note 2:**  $f_{DAC} = 80Msps$ ,  $f_{OUT} = 10MHz$ .

**Note 3:** Measured single ended with  $50\Omega$  load and complementary output connected to ground.

Note 4: Guaranteed by design, not production tested.

Figure 1. Load Test Circuit for CLK Outputs

### Typical Operating Characteristics

$(AV_{DD} = DV_{DD} = CV_{DD} = 3V$ , AGND = DGND = CGND = 0, external reference, IFS = 20mA, differential output, differential clock (unless otherwise noted),  $T_A = +25$ °C.)

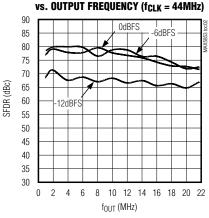

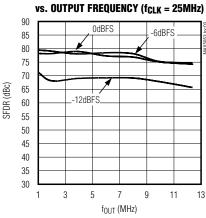

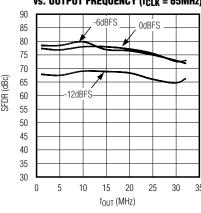

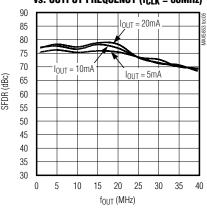

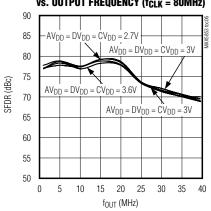

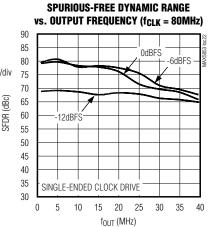

### SPURIOUS-FREE DYNAMIC RANGE

# SPURIOUS-FREE DYNAMIC RANGE vs. OUTPUT FREQUENCY (f<sub>CLK</sub> = 65MHz)

# SPURIOUS-FREE DYNAMIC RANGE vs. OUTPUT FREQUENCY (f<sub>CLK</sub> = 80MHz)

# SPURIOUS-FREE DYNAMIC RANGE vs. OUTPUT FREQUENCY (f<sub>CLK</sub> = 80MHz)

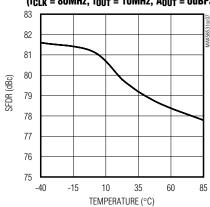

# SPURIOUS-FREE DYNAMIC RANGE vs. TEMPERATURE (fclk = 80MHz, fout = 10MHz, Aout = 0dBFs)

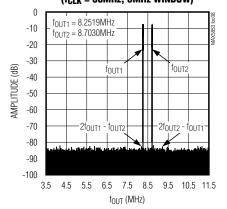

# TWO-TONE INTERMODULATION DISTORTION (fclk = 80MHz, 8MHz WINDOW)

### \_Typical Operating Characteristics (continued)

$(AV_{DD} = DV_{DD} = CV_{DD} = 3V$ , AGND = DGND = CGND = 0, external reference, IFS = 20mA, differential output, differential clock (unless otherwise noted),  $T_A = +25$ °C.)

### Typical Operating Characteristics (continued)

$(AV_{DD} = DV_{DD} = CV_{DD} = 3V, AGND = DGND = CGND = 0, external reference, I_{FS} = 20mA, differential output, differential clock (unless otherwise noted), T_A = +25°C.)$

### **Pin Description**

| PIN    | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DA9/PD           | Channel A Input Data Bit 9 (MSB)/Power-Down                                                                                                                                                                                                                                                                                                                               |

| 2      | DA8/DACEN        | Channel A Input Data Bit 8/DAC Enable Control                                                                                                                                                                                                                                                                                                                             |

| 3      | DA7/IDE          | Channel A Input Data Bit 7/Interleaved Data Enable                                                                                                                                                                                                                                                                                                                        |

| 4      | DA6/REN          | Channel A Input Data Bit 6/Reference Enable. Setting REN = 0 enables the internal reference. Setting REN = 1 disables the internal reference.                                                                                                                                                                                                                             |

| 5      | DA5/G3           | Channel A Input Data Bit 5/Channel A Gain Adjustment Bit 3                                                                                                                                                                                                                                                                                                                |

| 6      | DA4/G2           | Channel A Input Data Bit 4/Channel A Gain Adjustment Bit 2                                                                                                                                                                                                                                                                                                                |

| 7      | DA3/G1           | Channel A Input Data Bit 3/Channel A Gain Adjustment Bit 1                                                                                                                                                                                                                                                                                                                |

| 8      | DA2/G0           | Channel A Input Data Bit 2/Channel A Gain Adjustment Bit 0                                                                                                                                                                                                                                                                                                                |

| 9      | DA1              | Channel A Input Data Bit 1                                                                                                                                                                                                                                                                                                                                                |

| 10     | DA0              | Channel A Input Data Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                          |

| 11     | DB9              | Channel B Input Data Bit 9 (MSB)                                                                                                                                                                                                                                                                                                                                          |

| 12     | DB8              | Channel B Input Data Bit 8                                                                                                                                                                                                                                                                                                                                                |

| 13     | DB7              | Channel B Input Data Bit 7                                                                                                                                                                                                                                                                                                                                                |

| 14     | DB6              | Channel B Input Data Bit 6                                                                                                                                                                                                                                                                                                                                                |

| 15     | DB5              | Channel B Input Data Bit 5                                                                                                                                                                                                                                                                                                                                                |

| 16     | DV <sub>DD</sub> | Digital Power Input. See the Power Supplies, Bypassing, Decoupling, and Layout section for more details.                                                                                                                                                                                                                                                                  |

| 17     | DGND             | Digital Ground                                                                                                                                                                                                                                                                                                                                                            |

| 18     | DB4              | Channel B Input Data Bit 4                                                                                                                                                                                                                                                                                                                                                |

| 19     | DB3              | Channel B Input Data Bit 3                                                                                                                                                                                                                                                                                                                                                |

| 20     | DB2              | Channel B Input Data Bit 2                                                                                                                                                                                                                                                                                                                                                |

| 21     | DB1              | Channel B Input Data Bit 1                                                                                                                                                                                                                                                                                                                                                |

| 22     | DB0              | Channel B Input Data Bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                          |

| 23     | CW               | Active-Low Control Word Write Pulse. The control word is latched on the rising edge of $\overline{\text{CW}}$ .                                                                                                                                                                                                                                                           |

| 24     | DCE              | Active-Low Differential Clock Enable Input. Drive $\overline{DCE}$ low to enable the differential clock inputs CLKXP and CLKXN. Drive $\overline{DCE}$ high to disable the differential clock inputs and enable the single-ended CLK input.                                                                                                                               |

| 25     | CLKXP            | Positive Differential Clock Input. With $\overline{DCE} = 0$ , CLKXP and CLKXN are enabled. With $\overline{DCE} = 1$ , CLKXP and CLKXN are disabled. Connect CLKXP to CGND when the differential clock is disabled.                                                                                                                                                      |

| 26     | CLKXN            | Negative Differential Clock Input. With $\overline{DCE} = 0$ , CLKXP and CLKXN are enabled. With $\overline{DCE} = 1$ , CLKXP and CLKXN are disabled. Connect CLKXN to CV <sub>DD</sub> when the differential clock is disabled.                                                                                                                                          |

| 27, 30 | CV <sub>DD</sub> | Clock Power Input. See the Power Supplies, Bypassing, Decoupling, and Layout section for more                                                                                                                                                                                                                                                                             |

| 28     | CLK              | Single-Ended Clock Input/Output. With the differential clock disabled ( $\overline{DCE} = 1$ ), CLK becomes a single-ended conversion clock input. With the differential clock enabled ( $\overline{DCE} = 0$ ), CLK is a single-ended output that mirrors the differential clock inputs CLKXP and CLKXN. See the <i>Clock Modes</i> section for more information on CLK. |

| 29     | CGND             | Clock Ground                                                                                                                                                                                                                                                                                                                                                              |

| 31     | REFO             | Reference Input/Output. REFO serves as a reference input when the internal reference is disabled. If the internal 1.24V reference is enabled, REFO serves as an output for the internal reference. When the internal reference is enabled, bypass REFO to AGND with a 0.1µF capacitor                                                                                     |

### Pin Description (continued)

| PIN                                                                                                                               | NAME  | FUNCTION                                                                                                                                                                                                           |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 32                                                                                                                                | REFR  | Full-Scale Current Adjustment. To set the output full-scale current, connect an external resistor RSET between REFR and AGND. The output full-scale current is equal to 32 x V <sub>REFO</sub> /R <sub>SET</sub> . |  |  |

| 33, 39 AV <sub>DD</sub> Analog Power Input. See the <i>Power Supplies, Bypassing, Decoupling, and Layout</i> section for more def |       |                                                                                                                                                                                                                    |  |  |

| 34                                                                                                                                | OUTNB | Channel B Negative Analog Current Output                                                                                                                                                                           |  |  |

| 35                                                                                                                                | OUTPB | Channel B Positive Analog Current Output                                                                                                                                                                           |  |  |

| 36, 40                                                                                                                            | AGND  | Analog Ground                                                                                                                                                                                                      |  |  |

| 37                                                                                                                                | OUTNA | Channel A Negative Analog Current Output                                                                                                                                                                           |  |  |

| 38                                                                                                                                | OUTPA | Channel A Positive Analog Current Output                                                                                                                                                                           |  |  |

|                                                                                                                                   | EP    | Exposed Paddle. Connect EP to the common point of all ground planes.                                                                                                                                               |  |  |

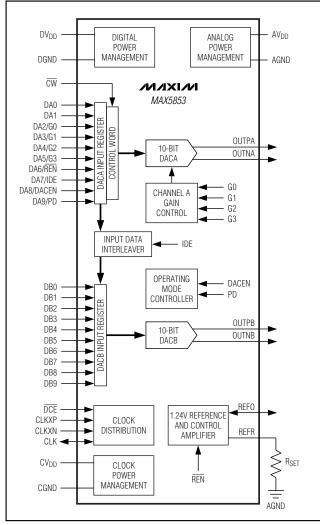

Figure 2. Simplified Diagram

### **Detailed Description**

The MAX5853 dual, high-speed, 10-bit, current-output DAC provides superior performance in communication systems requiring low-distortion analog-signal reconstruction. The MAX5853 combines two DACs and an onchip 1.24V reference (Figure 2). The current outputs of the DACs can be configured for differential or single-ended operation. The full-scale output current range is adjustable from 2mA to 20mA to optimize power dissipation and gain control.

The MAX5853 accepts an input data and a DAC conversion rate of 80MHz. The inputs are latched on the rising edge of the clock whereas the output latches on the following rising edge.

The MAX5853 features three modes of operation: normal, standby, and power-down (Table 2). These modes allow efficient power management. In power-down, the MAX5853 consumes only  $1\mu A$  of supply current. Wakeup time from standby mode to normal DAC operation is  $3\mu s$ .

#### **Programming the DAC**

An 8-bit control word routed through channel A's data port programs the gain matching, reference, and the operational mode of the MAX5853. The control word is latched on the rising edge of  $\overline{\text{CW}}$ .  $\overline{\text{CW}}$  is independent of the DAC clock. The DAC clock can always remain running when the control word is written to the DAC. Table 1 and Table 2 represent the control word format and function.

The gain on channel A can be adjusted to achieve gain matching between two channels in a user's system. The gain on channel A can be adjusted from -0.4dB to 0.35dB in steps of 0.05dB by using bits G3 to G0 (see Table 3).

#### **Table 1. Control Word Format and Function**

| ĺ | MSB |       |     |     |    |    |    |    |   | LSB |

|---|-----|-------|-----|-----|----|----|----|----|---|-----|

|   | PD  | DACEN | IDE | REN | G3 | G2 | G1 | G0 | Χ | X   |

| CONTROL WORD                                                                                                                                                                                                                                                                                     | FUNCTION                                                                                                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PD Power-Down. The part enters power-down mode if PD = 1.                                                                                                                                                                                                                                        |                                                                                                                                                                                     |  |  |  |  |

| DACEN                                                                                                                                                                                                                                                                                            | DAC Enable. When DACEN = 0 and PD = 0, the part enters standby mode.                                                                                                                |  |  |  |  |

| Interleaved Data Mode. IDE = 1 enables the interleaved data mode. In this mode, digital data for channels is applied through channel A in a multiplexed fashion. Channel B data is written on the form of the clock signal and channel A data is written on the rising edge of the clock signal. |                                                                                                                                                                                     |  |  |  |  |

| REN                                                                                                                                                                                                                                                                                              | Reference Enable Bit. REN = 0 activates the internal reference. REN = 1 disables the internal reference and requires the user to apply an external reference between 0.1V to 1.32V. |  |  |  |  |

| G3                                                                                                                                                                                                                                                                                               | Bit 3 (MSB) of Gain Adjust Word                                                                                                                                                     |  |  |  |  |

| G2 Bit 2 of Gain Adjust Word                                                                                                                                                                                                                                                                     |                                                                                                                                                                                     |  |  |  |  |

| G1                                                                                                                                                                                                                                                                                               | Bit 1 of Gain Adjust Word                                                                                                                                                           |  |  |  |  |

| G0                                                                                                                                                                                                                                                                                               | Bit 0 (LSB) of Gain Adjust Word                                                                                                                                                     |  |  |  |  |

### **Table 2. Configuration Modes**

| MODE                                                                       | PD | DACEN | IDE | REN |

|----------------------------------------------------------------------------|----|-------|-----|-----|

| Normal operation;<br>noninterleaved inputs;<br>internal reference active   | 0  | 1     | 0   | 0   |

| Normal operation;<br>noninterleaved inputs;<br>internal reference disabled | 0  | 1     | 0   | 1   |

| Normal operation;<br>interleaved inputs;<br>internal reference disabled    | 0  | 1     | 1   | 1   |

| Standby                                                                    | 0  | 0     | Χ   | Χ   |

| Power-down                                                                 | 1  | X     | Χ   | Χ   |

| Power-up                                                                   | 0  | 1     | Χ   | Χ   |

X = Don't care.

**Table 3. Gain Difference Setting**

| GAIN ADJUSTMENT ON<br>CHANNEL A (dB) | G3 | G2 | G1 | G0 |

|--------------------------------------|----|----|----|----|

| +0.4                                 | 0  | 0  | 0  | 0  |

| 0                                    | 1  | 0  | 0  | 0  |

| -0.35                                | 1  | 1  | 1  | 1  |

#### Device Power-Up and States of Operation

At power-up, the MAX5853's default configuration is internal reference, noninterleaved input mode with a gain of OdB and a fully operational converter. In shutdown, the MAX5853 consumes only  $1\mu A$  of supply current, and in standby the current consumption is 3.1mA. Wake-up time from standby mode to normal operation is  $3\mu s$ .

#### **Clock Modes**

The MAX5853 allows both single-ended CMOS and differential clock mode operation, and supports update rates of up to 80Msps. These modes are selected through an active-low control line called  $\overline{DCE}$ . In single-ended clock mode ( $\overline{DCE}$  = 1), the CLK pin functions as an input, which accepts a user-provided single-ended clock signal. Data is written to the converter on the rising edge of the clock. The DAC outputs (previous data) are updated simultaneously on the same edge.

If the  $\overline{DCE}$  pin is pulled low, the MAX5853 operates in differential clock mode. In this mode, the clock signal has to be applied to the differential clock input pins CLKXP/CLKXN. The differential input accepts an input range of  $\geq 0.5 \text{Vp-p}$  and a common-mode range of 1V to (CVDD - 0.5V), making the part ideal for low-input amplitude clock drives. CLKXP/CLKXN also help to minimize the jitter, and allow the user to connect a crystal oscillator directly to the MAX5853.

The CLK pin now becomes an output, and provides a single-ended replica of the differential clock signal, which may be used to synchronize the input data. Data is written to the device on the rising edge of the CLK signal.

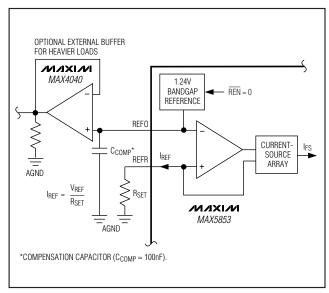

Figure 3. Setting I<sub>FS</sub> with the Internal 1.24V Reference and the Control Amplifier

#### $AV_{DD}$ AGND 1.24V $\mathsf{AV}_\mathsf{DD}$ MIXIM BANDGAP MAX6520 REFERENCE EXTERNAL REFO REFERENCE CURRENT-IREE RFFR ARRAY RSET AGND MIXIM MAX5853

Figure 4. MAX5853 with External Reference

#### **Internal Reference and Control Amplifier**

The MAX5853 provides an integrated 50ppm/°C, 1.24V, low-noise bandgap reference that can be disabled and overridden with an external reference voltage. REFO serves either as an external reference input or an integrated reference output. If  $\overline{\text{REN}} = 0$ , the internal reference is selected and REFO provides a 1.24V (50µA) output. Buffer REFO with an external amplifier, when driving a heavy load.

The MAX5853 also employs a control amplifier designed to simultaneously regulate the full-scale output current (IFS) for both outputs of the devices. Calculate the output current as:

$$IFS = 32 \times IREF$$

where IREF is the reference output current (IREF =  $V_{REFO} / R_{SET}$ ) and IFS is the full-scale output current. RSET is the reference resistor that determines the amplifier output current of the MAX5853 (Figure 3). This current is mirrored into the current-source array where IFS is equally distributed between matched current segments and summed to valid output current readings for the DACs.

#### **External Reference**

To disable the internal reference of the MAX5853, set  $\overline{\text{REN}} = 1$ . Apply a temperature-stable, external reference to drive the REFO pin and set the full-scale output (Figure 4). For improved accuracy and drift performance, choose a fixed output voltage reference such as the 1.2V, 25ppm/°C MAX6520 bandgap reference.

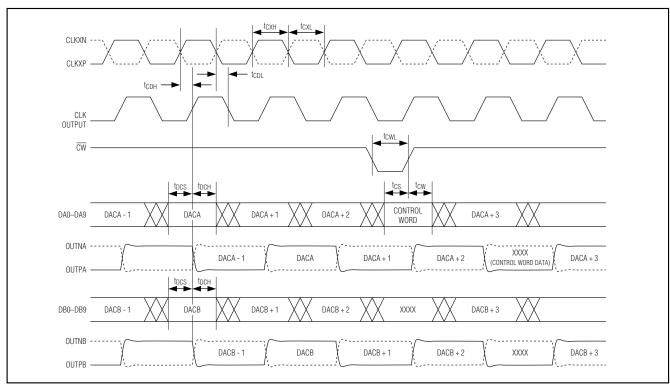

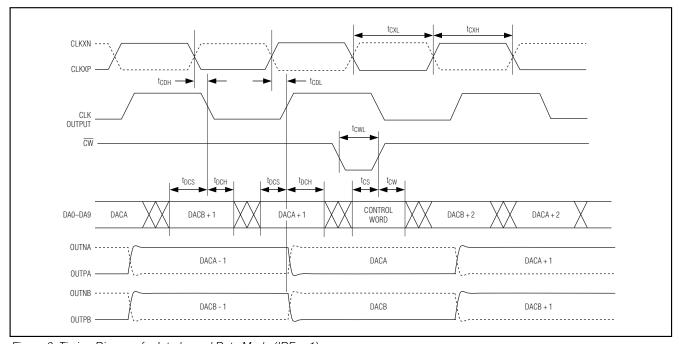

### **Detailed Timing**

The MAX5853 accepts an input data and DAC conversion rate of up to 80Msps. The input latches on the rising edge of the clock, whereas the output latches on the following rising edge.

Figure 5 depicts the write cycle of the two DACs in non-interleaved mode.

The MAX5853 can also operate in an interleaved data mode. Programming the IDE bit with a high level activates this mode (Tables 1 and 2). In interleaved mode, data for both DAC channels is written through input port A. Channel B data is written on the falling edge of the clock signal and then channel A data is written on the following rising edge of the clock signal. Both DAC outputs (channel A and B) are updated simultaneously on the next following rising edge of the clock. The interleaved data mode is attractive for applications where lower data rates are acceptable and interfacing on a single 10-bit bus is desired (Figure 6).

Figure 5. Timing Diagram for Noninterleaved Data Mode (IDE = 0)

Figure 6. Timing Diagram for Interleaved Data Mode (IDE = 1)

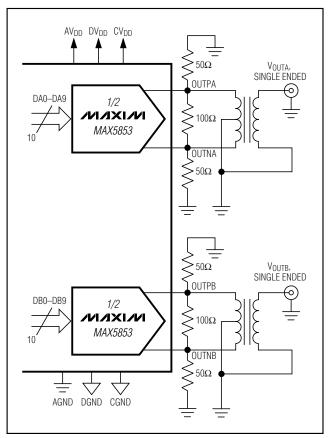

Figure 7. Application with Output Transformer Performing Differential-to-Single-Ended Conversion

#

Figure 8. Application with DC-Coupled Differential Outputs

### Applications Information

#### **Differential-to-Single-Ended Conversion**

The MAX5853 exhibits excellent dynamic performance to synthesize a wide variety of modulation schemes, including high-order QAM modulation with OFDM.

Figure 7 shows a typical application circuit with output transformers performing the required differential-to-single-ended signal conversion. In this configuration, the MAX5853 operates in differential mode, which reduces even-order harmonics, and increases the available output power.

#### **Differential DC-Coupled Configuration**

Figure 8 shows the MAX5853 output operating in differential, DC-coupled mode. This configuration can be used in communication systems employing analog quadrature upconverters and requiring a baseband sampling, dual-channel, high-speed DAC for I/Q syn-

thesis. In these applications, information bandwidth can extend from 10MHz down to several hundred kilohertz. DC-coupling is desirable to eliminate long discharge time constants that are problematic with large, expensive coupling capacitors. Analog quadrature upconverters have a DC common-mode input requirement of typically 0.7V to 1.0V. The MAX5853 differential I/Q outputs can maintain the desired full-scale level at the required 0.7V to 1.0V DC common-mode level when powered from a single 2.85V (±5%) supply. The MAX5853 meets this low-power requirement with minimal reduction in dynamic range while eliminating the need for level-shifting resistor networks.

#### Power Supplies, Bypassing, Decoupling, and Layout

Grounding and power-supply decoupling strongly influence the MAX5853 performance. Unwanted digital crosstalk can couple through the input, reference,

power-supply, and ground connections, which can affect dynamic specifications, like signal-to-noise ratio or spurious-free dynamic range. In addition, electromagnetic interference (EMI) can either couple into or be generated by the MAX5853. Observe the grounding and power-supply decoupling guidelines for high-speed, high-frequency applications. Follow the power supply and filter configuration to realize optimum dynamic performance.

Use of a multilayer printed circuit (PC) board with separate ground and power-supply planes is recommended. Run high-speed signals on lines directly above the ground plane. The MAX5853 has separate analog and digital ground buses (AGND, CGND, and DGND, respectively). Provide separate analog, digital, and clock ground sections on the PC board with only one point connecting the three planes. The ground connection points should be located underneath the device and connected to the exposed paddle. Run digital signals above the digital ground plane and analog/clock signals above the analog/clock ground plane. Digital signals should be kept away from sensitive analog, clock, and reference inputs. Keep digital signal paths short and metal trace lengths matched to avoid propagation delay and data skew mismatch.

The MAX5853 includes three separate power-supply inputs: analog (AVDD), digital (DVDD), and clock (CVDD). Use a single linear regulator power source to branch out to three separate power-supply lines (AVDD, DVDD, CVDD) and returns (AGND, DGND, CGND). Filter each power-supply line to the respective return line using LC filters comprising ferrite beads and  $10\mu F$  capacitors. Filter each supply input locally with  $0.1\mu F$  ceramic capacitors to the respective return lines.

Note: To maintain the dynamic performance of the *Electrical Characteristics*, ensure the voltage difference between DV<sub>DD</sub>, AV<sub>DD</sub>, and CV<sub>DD</sub> does not exceed 150mV.

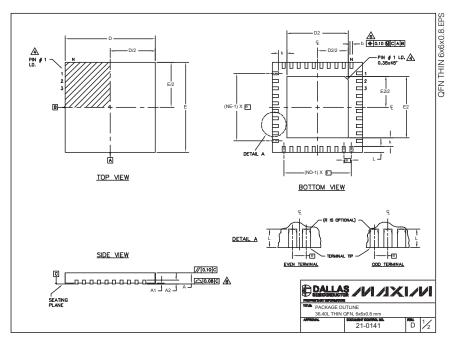

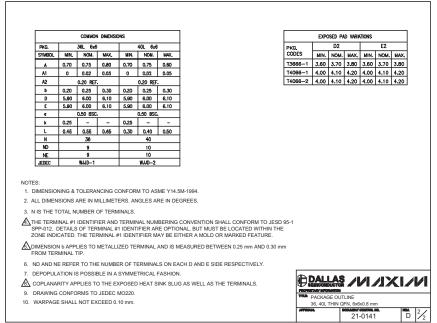

# Thermal Characteristics and Packaging Thermal Resistance

40-lead thin QFN-EP:

$$\theta_{\text{JA}} = 38^{\circ}\text{C/W}$$

The MAX5853 is packaged in a 40-pin thin QFN-EP package, providing greater design flexibility, increased thermal efficiency, and optimized AC performance of the DAC. The EP enables the implementation of grounding techniques, which are necessary to ensure highest performance operation.

In this package, the data converter die is attached to an EP leadframe with the back of this frame exposed at the package bottom surface, facing the PC board side of the package. This allows a solid attachment of the package to the PC board with standard infrared (IR) flow soldering techniques. A specially created land pattern on the PC board, matching the size of the EP (4.1mm  $\times$  4.1mm), ensures the proper attachment and grounding of the DAC. Designing vias\* into the land area and implementing large ground planes in the PC board design allows for highest performance operation of the DAC. Use an array of 3  $\times$  3 vias ( $\leq$ 0.3mm diameter per via hole and 1.2mm pitch between via holes) for this 40-pin thin QFN-EP package (package code: T4066-1).

# **Dynamic Performance Parameter Definitions**

#### Total Harmonic Distortion (THD)

THD is the ratio of the RMS sum of all essential harmonics (within a Nyquist window) of the input signal to the fundamental itself. This can be expressed as:

THD=

$$20 \times log \left( \frac{\sqrt{(V_2^2 + V_3^2 + V_4^2 ... + ... V_N^2)}}{V_1} \right)$$

where  $V_1$  is the fundamental amplitude, and  $V_2$  through  $V_N$  are the amplitudes of the 2nd through Nth order harmonics. The MAX5853 uses the first seven harmonics for this calculation.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the ratio of RMS amplitude of the carrier frequency (maximum signal component) to the RMS value of their next-largest spectral component. SFDR is usually measured in dBc with respect to the carrier frequency amplitude or in dBFS with respect to the DAC's full-scale range. Depending on its test condition, SFDR is observed within a predefined window or to Nyquist.

#### Multitone Power Ratio (MTPR)

A series of equally spaced tones are applied to the DAC with one tone removed from the center of the range. MTPR is defined as the worst-case distortion (usually a 3rd-order harmonic product of the fundamental frequencies), which appears as the largest spur at the frequency of the missing tone in the sequence. This test can be performed with any number of input tones; however, four and eight tones are among the most common test conditions for CDMA- and GSM/EDGE-type applications.

<sup>\*</sup>Vias connect the land pattern to internal or external copper planes.

#### Intermodulation Distortion (IMD)

The two-tone IMD is the ratio expressed in dBc of either output tone to the worst 3rd-order (or higher) IMD products.

### Static Performance Parameter Definitions

#### Integral Nonlinearity (INL)

Integral nonlinearity (INL) is the deviation of the values on an actual transfer function from a line drawn between the end points of the transfer function, once offset and gain errors have been nullified. For a DAC, the deviations are measured at every individual step.

#### Differential Nonlinearity (DNL)

Differential nonlinearity (DNL) is the difference between an actual step height and the ideal value of 1 LSB. A DNL error specification no more negative than -1 LSB guarantees monotonic transfer function.

#### Offset Error

Offset error is the current flowing from positive DAC output when the digital input code is set to zero. Offset error is expressed in LSBs.

#### Gain Error

A gain error is the difference between the ideal and the actual full-scale output current on the transfer curve, after nullifying the offset error. This error alters the slope of the transfer function and corresponds to the same percentage error in each step. The ideal current is defined by reference voltage at V<sub>REFO</sub> / I<sub>REF</sub> x 32.

#### Settling Time

The settling time is the amount of time required from the start of a transition until the DAC output settles to its new output value to within the converter's specified accuracy.

#### Glitch Impulse

A glitch is generated when a DAC switches between two codes. The largest glitch is usually generated around the midscale transition, when the input pattern transitions from 011...111 to 100...000. This occurs due to timing variations between the bits. The glitch impulse is found by integrating the voltage of the glitch at the midscale transition over time. The glitch impulse is usually specified in pV-s.

#### **Table 4. Part Selection Table**

| PART    | SPEED (Msps) | RESOLUTION   |

|---------|--------------|--------------|

| MAX5851 | 80           | 8-bit, dual  |

| MAX5852 | 165          | 8-bit, dual  |

| MAX5853 | 80           | 10-bit, dual |

| MAX5854 | 165          | 10-bit, dual |

### Chip Information

TRANSISTOR COUNT: 9,035

PROCESS: CMOS

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

18 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Digital to Analog Converters - DAC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

5962-8871903MYA 5962-8876601LA 5962-89697013A 5962-89932012A 5962-9176404M3A PM7545FPCZ AD5311BRMZ-REEL7

AD5311RBRMZ-RL7 AD558SE/883B AD5681RBCPZ-1RL7 AD664TE/883B AD667SE AD7845SE/883B AD9115BCPZRL7

AD9162BBCA DAC08RC/883C JM38510/11302BEA AD5449YRUZ-REEL7 AD664AJ AD664BJ AD667SE/883B AD7534JPZ TCC

103A-RT 057536E 5962-87700012A 5962-87700032A 5962-87789022A 5962-89657023A 702423BB AD664BE MAX5853ETL+T

MAX5801AUB+ AD9116BCPZRL7 MAX5110GTJ+ MAX5702BAUB+ DS4412U+T&R MAX5364EUT+T MAX5858AECM+D

AD5821ABCBZ-REEL7 MX7528KP+ MAX5858ECM+D MAX5138BGTE+T MAX5856AECM+D AD9164BBCA AD7545AUE

MX7528JP+ TCC-303A-RT MAX5112GTJ+ DS3911T+T MAX5805BAUB+T