# **Specification**

BT45213

BTHQ128064AVD1-SRE-12-COG

Doc. No.: COG-BTD12864-40

**Version October 2010**

#### **DOCUMENT REVISION HISTORY:**

| REVISION FROM TO  A 2010.10.11 First Release.  Based on: a.) VL-QUA-012B REV.Y 2010.12.10  According to VL-QUA-012B, LCD size is small because Unit Per Laminate=24 which is more than 6pcs/Laminate. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A 2010.10.11 First Release.  Based on: a.) VL-QUA-012B REV.Y 2010.12.10  According to VL-QUA-012B, LCD size is small because Unit Per Laminate=24 which is more                                       |

| Based on: a.) VL-QUA-012B REV.Y 2010.12.10  According to VL-QUA-012B, LCD size is small because Unit Per Laminate=24 which is more                                                                    |

|                                                                                                                                                                                                       |

## **CONTENTS**

|     |                                           | <u>Page No.</u> |

|-----|-------------------------------------------|-----------------|

| 1.  | GENERAL DESCRIPTION                       | 4               |

| 2.  | MECHANICAL SPECIFICATIONS                 | 4               |

| 3.  | INTERFACE SIGNALS                         | 7               |

| 4.  | ABSOLUTE MAXIMUM RATINGS                  | 9               |

| 4.1 | ELECTRICAL MAXIMUM RATINGS – FOR IC ONLY  | 9               |

| 4.2 | ENVIRONMENTAL CONDITION                   | 10              |

| 5.  | ELECTRICAL SPECIFICATIONS                 | 11              |

| 5.1 | TYPICAL ELECTRICAL CHARACTERISTICS        | 11              |

| 5.2 | TIMING SPECIFICATIONS                     | 12              |

| 5.3 | COMMAND TABLE                             | 15              |

| 5.4 | INITIAL CODE SETTING (FOR REFERENCE ONLY) | 16              |

| 5.5 | REFERENCE CIRCUIT                         | 16              |

| 6.  | ELECTRO-OPTICAL CHARACTERISTICS           | 17              |

| 6.1 | ISO PLOT                                  | 17              |

| 6.2 | OPTICAL CHARACTERISTICS DEFINITION        | 18              |

| 7.  | LCD COSMETIC CONDITIONS                   | 19              |

| 8.  | REMARK                                    | 19              |

# Specification of LCD Module Type Model No.: COG-BTD12864-40

#### 1. General Description

• 128 x 64 Dots STN Positive Yellow Reflective Dot Matrix LCD Module.

• Viewing Angle: 12 o'clock direction.

• Driving duty: 1/65 Duty, 1/7 bias.

• 'SITRONIX' ST7565P (COG) LCD controller/Driver or equivalent.

• Logic voltage: 3.3V.

• FPC connection.

• "RoHS" compliance.

#### 2. Mechanical Specifications

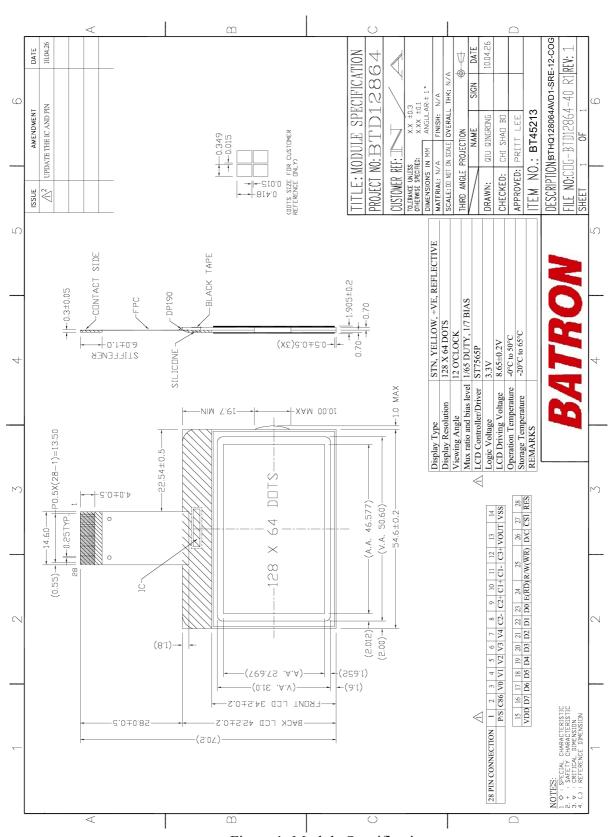

The mechanical detail is shown in Fig. 1 and summarized in Table 1 below.

Table 1

| Parameter          | Specifications                                     | Unit  |

|--------------------|----------------------------------------------------|-------|

| Outline dimensions | 55.6(W) x 70.2(H) x 4.48(D) (Included FPC. Exclude | mm    |

|                    | terminals of backlight)                            |       |

| Viewing area       | 50.60(W) x 31.0(H)                                 | mm    |

| Active area        | 46.577(W) x 27.697(H)                              | mm    |

| Display format     | 128(W) x 64(H)                                     | dots  |

| Dot size           | 0.349(W) x 0.418(H)                                | mm    |

| Dot spacing        | 0.015(W) x 0.015(H)                                | mm    |

| Dot pitch          | 0.364(W) x 0.433(H)                                | mm    |

| Weight             | Approx: 9                                          | grams |

Figure 1: Module Specification

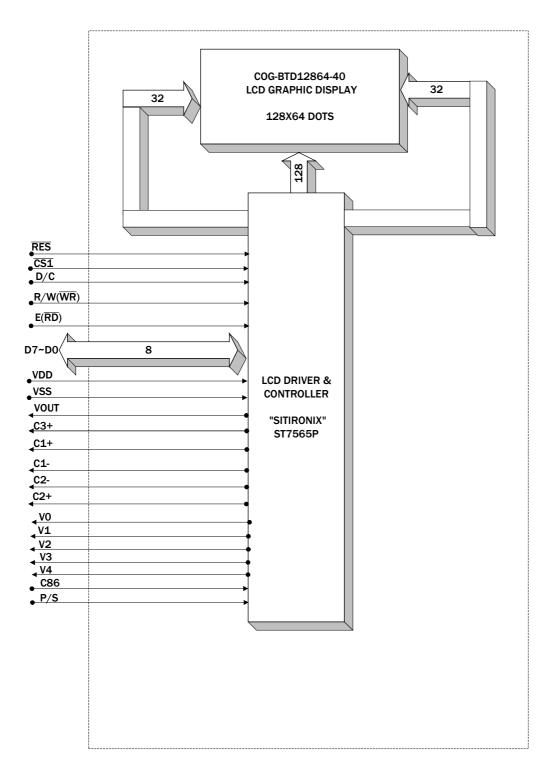

Figure2: Block Diagram.

#### 3. Interface signals

Table 2(a): Pin Assignment

| Pin No. | Symbol | Description                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|         |        | This pin configures the interface to be parallel mode or serial mode.  P/S = "H": Parallel data input/output.  P/S = "L": Serial data input.  The following applies depending on the P/S status:  P/S   Data/Command   Data   Read/Write   Serial Clock                         |  |  |  |  |  |  |  |  |  |  |

| 1       | P/S    | $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| 2       | C86    | This is the MPU interface selection pin.  C86 = "H": 6800 Series MPU interface.  C86 = "L": 8080 Series MPU interface.                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

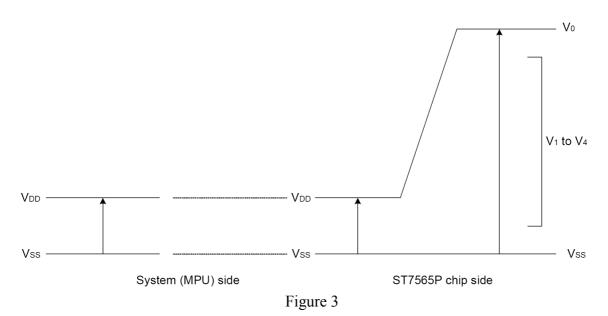

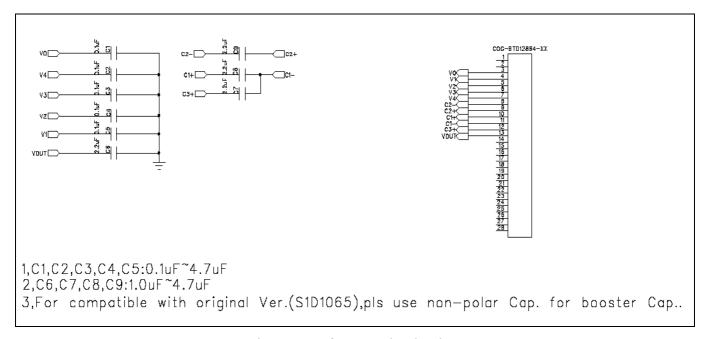

| 3       | V0     | This is a multi-level power supply for the liquid crystal drive. The voltage                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

| 4       | V1     | supply applied is determined by the liquid crystal cell, and is changed                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| 5       | V2     | through the use of a resistive voltage divided or through changing the                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |  |

| 6       | V3     | impedance using an op. amp. Voltage levels are determined based on VSS,                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| 7       | V4     | and must maintain the relative magnitudes shown below. $V0 \ge V1 \ge V2 \ge V3 \ge V4 \ge VSS$ When the power supply turns ON, the internal power supply circuits produce the V1 to V4 voltages shown below. The voltage settings are selected using the LCD bias set command. |  |  |  |  |  |  |  |  |  |  |

| 8       | C2-    | For 1/7 bias: V1= 6/7 * V0, V2=5/7 * V0, V3=2/7 *V0, V4=1/7 * V0.  DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2P terminal.                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| 9       | C2+    | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2N terminal.                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| 10      | C1+    | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1N terminal.                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| 11      | C1-    | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1P terminal.                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| 12      | C3+    | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1N terminal.                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| 13      | VOUT   | DC/DC voltage converter. Connect a capacitor between this terminal and VSS or VDD.                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| 14      | VSS    | Ground.                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| 15      | VDD    | Power supply pins for logic.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |  |

Table 2(b): Pin Assignment

| Pin No. | Symbol  | Description                                                                                                                                                                                                                                                                                                                                               |

|---------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16      | D7      |                                                                                                                                                                                                                                                                                                                                                           |

| 17      | D6      | This is an 8-bit bi-directional data bus that connects to an 8-bit standard MPU                                                                                                                                                                                                                                                                           |

| 18      | D5      | data bus.                                                                                                                                                                                                                                                                                                                                                 |

| 19      | D4      | When the serial interface is selected (P/S = LOW), then D7 serves as the serial                                                                                                                                                                                                                                                                           |

| 20      | D3      | data input terminal (SI) and D6 serves as the serial clock input terminal (SCL). At this time, D0 to D5 are set to high impedance.                                                                                                                                                                                                                        |

| 21      | D2      | When the chip select is inactive, D0 to D7 are set to high impedance.                                                                                                                                                                                                                                                                                     |

| 22      | D1      | when the emp select is mactive, bo to by are set to high impedance.                                                                                                                                                                                                                                                                                       |

| 23      | D0      |                                                                                                                                                                                                                                                                                                                                                           |

| 24      | E(RD)   | When connected to 8080 series MPU, this pin is treated as the "RD" signal of the 8080 MPU and is LOW-active.  The data bus is in an output status when this signal is "L".  When connected to 6800 series MPU, this pin is treated as the "E" signal of the 6800 MPU and is HIGH-active.  This is the enable clock input terminal of the 6800 Series MPU. |

|         |         | When connected to 8080 series MPU, this pin is treated as the "WR" signal of the 8080 MPU and is LOW-active.                                                                                                                                                                                                                                              |

| 25      | R/W(WR) | The signals on the data bus are latched at the rising edge of the $\overline{WR}$ signal. When connected to 6800 series MPU, this pin is treated as the "R/W" signal of the 6800 MPU and decides the access type: When R/W = "H": Read. When R/W = "L": Write.                                                                                            |

| 26      | D/C     | This is connect to the least significant bit of the normal MPU address bus, and it determines whether the data bits are data or command.  D/C = "H": Indicates that D0 to D7 are display data.  D/C= "L": Indicates that D0 to D7 are control data.                                                                                                       |

| 27      | CS1     | This is the chip select signal. When /CS1 = "L", then the chip select becomes active, and data/command I/O is enabled.                                                                                                                                                                                                                                    |

| 28      | RES     | When RES is set to "L", the register settings are initialized (cleared). The reset operation is performed by the /RES signal level.                                                                                                                                                                                                                       |

#### 4. Absolute Maximum Ratings

#### 4.1 Electrical Maximum Ratings – for IC Only

Table 3

| Parameter                             | Symbol         | Min. | Max.  | Unit |

|---------------------------------------|----------------|------|-------|------|

| Power Supply voltage (Logic)          | VDD            | +0.3 | +3.6  | V    |

| Power Supply voltage (VDD2)           | VDD2           | +0.3 | +3.6  | V    |

| Power Supply voltage (V0, VOUT)       | V0, VOUT       | +0.3 | +14.5 | V    |

| Power Supply voltage (V1, V2, V3, V4) | V1, V2, V3, V4 | V0   | +0.3  | V    |

#### Note:

- 1. The VDD2, V0 to V4 and VOUT are relative to the VSS = 0V reference.

- 2. Insure that the voltage levels of V1, V2, V3, and V4 are always such that VOUT  $\geq$  V0  $\geq$  V1  $\geq$  V2  $\geq$  V3  $\geq$  V4.

- 3. Permanent damage to the LSI may result if the LSI is used outside of the absolute maximum ratings. Moreover, it is recommended that in normal operation the chip be used at the electrical characteristic conditions, and use of the LSI outside of these conditions may not only result in malfunctions of the LSI, but may have a negative impact on the LSI reliability as well.

#### 4.2 Environmental Condition

Table 4

|                          | Oper                  | ating                        | Stor         | age |  |  |  |  |

|--------------------------|-----------------------|------------------------------|--------------|-----|--|--|--|--|

| Item                     | Tempe                 | Temperature Temperature Rema |              |     |  |  |  |  |

|                          | (To                   |                              |              |     |  |  |  |  |

|                          |                       |                              |              |     |  |  |  |  |

|                          | Min.                  |                              |              |     |  |  |  |  |

| Ambient Temperature      | 0°C                   | Dry                          |              |     |  |  |  |  |

|                          | 90% max. RI           | H for Ta $\leq 40$           | )°C          |     |  |  |  |  |

| Humidity (Note 1)        | < 50% RH fo           | No condensation              |              |     |  |  |  |  |

|                          | temperature           |                              |              |     |  |  |  |  |

| Vibration (IEC 68-2-6)   | Frequency:            |                              |              |     |  |  |  |  |

| cells must be mounted on | Amplitude:            |                              | 3 directions |     |  |  |  |  |

| a suitable connector     | Duration: 20          |                              |              |     |  |  |  |  |

|                          | Pulse duration: 11 ms |                              |              |     |  |  |  |  |

| Shock (IEC 68-2-27)      | Peak accelera         | 3 directions                 |              |     |  |  |  |  |

| Half-sine pulse shape    | У                     | 3 unections                  |              |     |  |  |  |  |

|                          | perpendicula          |                              |              |     |  |  |  |  |

Note 1: Product cannot sustain at extreme storage conditions for long time.

#### 5. Electrical Specifications

#### **5.1** Typical Electrical Characteristics

At

$$Ta = +25$$

°C,  $VDD = +3.3\pm5\%$ ,  $VSS = 0V$ .

Table 5

| Parameter        | Symbol    | Conditions           | Min.    | Тур. | Max.    | Unit |

|------------------|-----------|----------------------|---------|------|---------|------|

| Supply voltage   | VDD-VSS   |                      | 3.14    | 3.3  | 3.47    | V    |

| (Logic)          |           |                      |         |      |         |      |

| Supply voltage   | VLCD      | Ta = 0 °C,           | -       | 8.9  | -       | V    |

| (LCD) (built-in) | =V0-VSS   | Character mode       |         |      |         |      |

|                  |           | VDD = +3.3V, Note 1  |         |      |         |      |

|                  |           | $Ta = 25  ^{\circ}C$ | 8.6     | 8.8  | 9.0     | V    |

|                  |           | Character mode       |         |      |         |      |

|                  |           | VDD = +3.3V, Note 1  |         |      |         |      |

|                  |           | $Ta = 50  ^{\circ}C$ | -       | 8.6  | -       | V    |

|                  |           | Character mode       |         |      |         |      |

|                  |           | VDD = +3.3V, Note 1  |         |      |         |      |

| Low-level input  | $V_{ILC}$ | Note 2               | VSS     | -    | 0.2xVDD | V    |

| signal voltage   |           |                      |         |      |         |      |

| High-level input | $V_{IHC}$ | Note 2               | 0.8xVDD | -    | VDD     | V    |

| signal voltage   |           |                      |         |      |         |      |

| Supply Current   | IDD       | VDD = +3.3V, Note 1, | -       | 0.46 | 0.69    | mA   |

| (Logic & LCD)    |           | Character mode       |         |      |         |      |

|                  |           | VDD = +3.3V, Note 1, | _       | 0.78 | 1.2     | mA   |

|                  |           | Checker board mode   |         |      |         |      |

Note 1: There is tolerance in optimum LCD driving voltage during production and it will be within the specified range.

Note 2: D/C, D0 to D5, D6, D7,  $E(\overline{RD})$ ,  $R/W(\overline{WR})$ ,  $\overline{CS1}$ , C86, P/S,  $\overline{RES}$  terminals.

Note 3: Do not display a fixed pattern for more than 30 min. because it may cause image sticking due to LCD characteristics. It is recommended to change display pattern frequently. If customer must fix display pattern on the screen, please consider to activate screen saver.

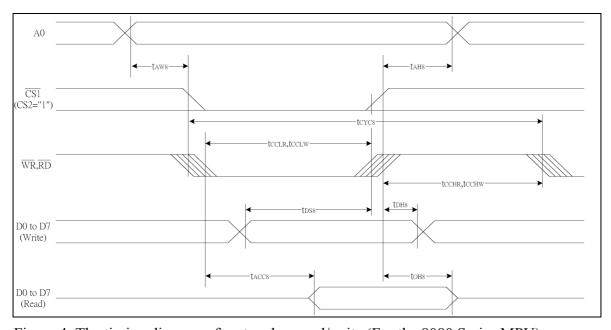

#### 5.2 Timing Specifications

System Bus read/Write Characteristics 1 (For the 8080 Series MPU)

At Ta = 0 °C to +50 °C,  $VDD = +3.3V\pm5\%$ , VSS = 0V.

Table 6

| Item                         | Signal      | Symbol        | Condition   | Rat  | Units |        |

|------------------------------|-------------|---------------|-------------|------|-------|--------|

| item                         | Signal      | Syllibol      | Condition   | Min. | Max.  | Ullits |

| Address hold time            |             | tAH8          |             | 0    | –     |        |

| Address setup time           | A0          | tAW8          |             | 0    | _     |        |

| System cycle time            |             | tcyc8         |             | 240  | _     | ]      |

| Enable L pulse width (WRITE) | WR          | tcclw         |             | 80   | _     | ]      |

| Enable H pulse width (WRITE) | 1 VVK       | <b>t</b> CCHW |             | 80   | _     | ]      |

| Enable L pulse width (READ)  | RD          | tCCLR         |             | 140  | _     | Ns     |

| Enable H pulse width (READ)  | ן אט        | tCCHR         |             | 80   |       | ]      |

| WRITE Data setup time        |             | tDS8          |             | 40   | _     | ]      |

| WRITE Address hold time      | D0 to D7    | tDH8          |             | 0    | _     | ]      |

| READ access time             | י וט וט טלי | tACC8         | CL = 100 pF | _    | 70    | ]      |

| READ Output disable time     |             | <b>t</b> OH8  | CL = 100 pF | 5    | 50    | ]      |

<sup>\*1</sup> The input signal rise time and fall time (tr, tr) is specified at 15 ns or less. When the system cycle time is extremely fast,  $(tr + tr) \le (tcycs - tcchw - tcchw)$  for  $(tr + tr) \le (tcycs - tcchw - tcchw)$  are specified.

<sup>\*3</sup> tcclw and tcclR are specified as the overlap between /CS1 being "L" (CS2 = "H") and /WR and /RD being at the "L" level.

Figure 4: The timing diagram of system bus read/write (For the 8080 Series MPU)

<sup>\*2</sup> All timing is specified using 20% and 80% of VDD as the reference.

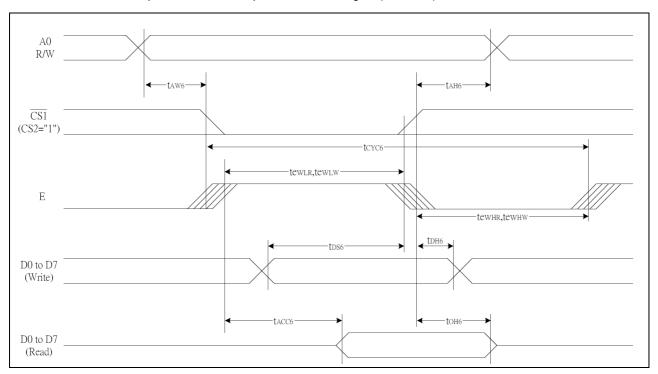

#### System Bus read/Write Characteristics 2 (For the 6800 Series MPU)

At Ta =0 °C to +50 °C, VDD =  $+3.3V\pm5\%$ , VSS = 0V.

#### Table 7

| Itama                        | Cianal   | Cumahal      | Condition   | Rat  | ing  | Linita |

|------------------------------|----------|--------------|-------------|------|------|--------|

| Item                         | Signal   | Symbol       | Condition   | Min. | Max. | Units  |

| Address hold time            |          | tAH6         |             | 0    | _    |        |

| Address setup time           | A0       | tAW6         |             | 0    | _    |        |

| System cycle time            |          | tcyc6        |             | 240  | _    |        |

| Enable L pulse width (WRITE) | WR       | tewlw        |             | 80   | _    |        |

| Enable H pulse width (WRITE) | VVK      | tewhw        |             | 80   | _    |        |

| Enable L pulse width (READ)  | RD       | tewlr        |             | 80   | _    | ns     |

| Enable H pulse width (READ)  | ן אט     | tEWHR        |             | 140  |      |        |

| WRITE Data setup time        |          | tDS6         |             | 40   | _    |        |

| WRITE Address hold time      | D0 to D7 | tDH6         |             | 0    | _    |        |

| READ access time             | D0 to D7 | tACC6        | CL = 100 pF | _    | 70   |        |

| READ Output disable time     |          | <b>t</b> OH6 | CL = 100 pF | 5    | 50   |        |

<sup>\*1</sup> The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast, (tr +tf) ≤ (tcγc6 - tewlw - tewhw) for (tr + tf) ≤ (tcγc6 - tewlr - tewhr) are specified.

<sup>\*3</sup> tewlw and tewlr are specified as the overlap between CS1 being "L" (CS2 = "H") and E.

Figure 5: The timing diagram of system bus read/write (For the 6800 Series MPU)

<sup>\*2</sup> All timing is specified using 20% and 80% of VDD as the reference.

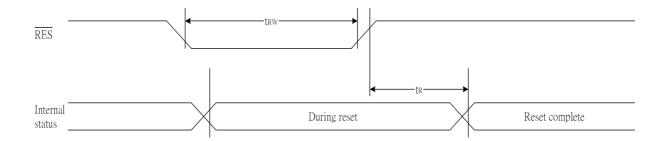

#### **Reset Timing**

At Ta =0 °C to +50 °C, VDD = +3.3 $V\pm5\%$ , VSS = 0V.

Table 8

| Item                  | Signal  | Symbol   | Condition | ,    | Units |      |        |

|-----------------------|---------|----------|-----------|------|-------|------|--------|

| item                  | Sigilal | Syllibol | Condition | Min. | Тур.  | Max. | Ullits |

| Reset time            |         | tr       |           | _    | _     | 1.0  | us     |

| Reset "L" pulse width | /RES    | trw      |           | 1.0  | _     | _    | us     |

<sup>\*1</sup> All timing is specified with 20% and 80% of  $\mbox{\em VDD}$  as the standard.

Figure 6: Reset Timing

#### **5.3.** Command Table

Table 9

| Command                                                                 |    |     |     | Cor    | nma    | nd C     | Code      | <del></del> |              |               |                                  | Function                                                                                                                                          |

|-------------------------------------------------------------------------|----|-----|-----|--------|--------|----------|-----------|-------------|--------------|---------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Command                                                                 | A0 | /RD | /WR | D7     |        |          |           | D3          |              |               |                                  |                                                                                                                                                   |

| (1) Display ON/OFF                                                      | 0  | 1   | 0   | 1      | 0      | 1        | 0         | 1           | 1            | 1             | 0<br>1                           | LCD display ON/OFF<br>0: OFF, 1: ON                                                                                                               |

| (2) Display start line set                                              | 0  | 1   | 0   | 0      | 1      | Di       | spla      | ay st       | art a        | ddre          | ess                              | Sets the display RAM display start line address                                                                                                   |

| (3) Page address set                                                    | 0  | 1   | 0   | 1      | 0      | 1        | 1         | Pa          | ige a        | addr          | ess                              | Sets the display RAM page address                                                                                                                 |

| (4) Column address set<br>upper bit<br>Column address set<br>lower bit  | 0  | 1   | 0   | 0      | 0      | 0        | 1         | col:<br>Lea | umn<br>ast s | add<br>ignif  | cant<br>lress<br>licant<br>lress | Sets the most significant 4 bits of<br>the display RAM column address.<br>Sets the least significant 4 bits of<br>the display RAM column address. |

| (5) Status read                                                         | 0  | 0   | 1   |        | St     | atus     |           | 0           | 0            |               | 0                                | Reads the status data                                                                                                                             |

| (6) Display data write                                                  | 1  | 1   | 0   |        |        | \        | Nrit      | e da        | ta           |               |                                  | Writes to the display RAM                                                                                                                         |

| (7) Display data read                                                   | 1  | 0   | 1   |        |        | F        | Rea       | d da        | ta           |               |                                  | Reads from the display RAM                                                                                                                        |

| (8) ADC select                                                          | 0  | 1   | 0   | 1      | 0      | 1        | 0         | 0           | 0            | 0             | 0<br>1                           | Sets the display RAM address<br>SEG output correspondence<br>0: normal, 1: reverse                                                                |

| (9) Display normal/<br>reverse                                          | 0  | 1   | 0   | 1      | 0      | 1        | 0         | 0           | 1            | 1             | 0<br>1                           | Sets the LCD display normal/<br>reverse<br>0: normal, 1: reverse                                                                                  |

| (10) Display all points<br>ON/OFF                                       | 0  | 1   | 0   | 1      | 0      | 1        | 0         | 0           | 1            | 0             | 0<br>1                           | Display all points 0: normal display 1: all points ON                                                                                             |

| (11) LCD bias set                                                       | 0  | 1   | 0   | 1      | 0      | 1        | 0         | 0           | 0            | 1             | 0<br>1                           | Sets the LCD drive voltage bias ratio<br>0: 1/9 bias, 1: 1/7 bias (ST7565P)                                                                       |

| (12) Read/modify/write                                                  | 0  | 1   | 0   | 1      | 1      | 1        | 0         | 0           | 0            | 0             | 0                                | Column address increment<br>At write: +1<br>At read: 0                                                                                            |

| (13) End                                                                | 0  | 1   | 0   | 1      | 1      | 1        | 0         | 1           | 1            | 1             | 0                                | Clear read/modify/write                                                                                                                           |

| (14) Reset                                                              | 0  | 1   | 0   | 1      | 1      | 1        | 0         | 0           | 0            | 1             | 0                                | Internal reset                                                                                                                                    |

| (15) Common output<br>mode select                                       | 0  | 1   | 0   | 1      | 1      | 0        | 0         | 0<br>1      | *            | *             | *                                | Select COM output scan direction 0: normal direction 1: reverse direction                                                                         |

| (16) Power control set                                                  | 0  | 1   | 0   | 0      | 0      | 1        | 0         | 1           |              | oera<br>ode   | ting                             | Select internal power supply operating mode                                                                                                       |

| (17) V0 voltage regulator internal resistor ratio set                   | 0  | 1   | 0   | 0      | 0      | 1        | 0         | 0           |              | esist<br>atio | or                               | Select internal resistor ratio(Rb/Ra) mode                                                                                                        |

| (18) Electronic volume<br>mode set<br>Electronic volume<br>register set | 0  | 1   | 0   | 1<br>0 | 0      | 0<br>Ele | 0<br>ctro | 0<br>nic v  | 0<br>olur/   | 0<br>ne v     | 1<br>alue                        | Set the V0 output voltage electronic volume register                                                                                              |

| (19) Static indicator<br>ON/OFF<br>Static indicator                     | 0  | 1   | 0   | 1      | 0      | 1        |           | 1           | 1            |               | 0                                | 0: OFF, 1: ON                                                                                                                                     |

| register set                                                            |    |     |     | 0      | 0      | 0        | 0         | 0           | 0            | 0             | Mode                             | Set the flashing mode                                                                                                                             |

| (20) Booster ratio set                                                  | 0  | 1   | 0   | 1<br>0 | 1<br>0 | 1<br>0   | 1<br>0    | 1<br>0      | 0            |               | 0<br>p-up<br>ilue                | select booster ratio<br>00: 2x,3x,4x<br>01: 5x<br>11: 6x                                                                                          |

| (21) Power saver                                                        |    |     |     |        |        |          |           |             |              |               |                                  | Display OFF and display all points ON compound command                                                                                            |

| (22) NOP                                                                | 0  | 1   | 0   | 1      | 1      | 1        | 0         | 0           | 0            | 1             | 1                                | Command for non-operation                                                                                                                         |

| (23) Test                                                               | 0  | 1   | 0   | 1      | 1      | 1        | 1         | *           | *            | *             | *                                | Command for IC test. Do not use this command                                                                                                      |

#### 5.4 Initial code setting (for reference only)

Table 10

| Description                                      | Setting data |  |  |  |

|--------------------------------------------------|--------------|--|--|--|

| Reset                                            | 0xe2         |  |  |  |

| LCD bias set                                     | 0xa3         |  |  |  |

| ADC select                                       | 0xa0         |  |  |  |

| Common output mode select                        | 0xc8         |  |  |  |

| V5 voltage regulator internal resistor ratio set | 0x25         |  |  |  |

| Electronic volume mode set                       | 0x81         |  |  |  |

| Electronic volume                                | 0x13         |  |  |  |

| Power control set                                | 0x25         |  |  |  |

| Display start line set                           | 0x40         |  |  |  |

| Page address set                                 | 0xb0         |  |  |  |

| Column address upper bit set                     | 0x10         |  |  |  |

| Column address lower bit set                     | 0x04         |  |  |  |

| Display all point ON/OFF                         | 0xa4         |  |  |  |

| Display normal or reverse                        | 0xa6         |  |  |  |

#### **5.5** Reference circuit

Figure 7: Reference Circuit Diagram

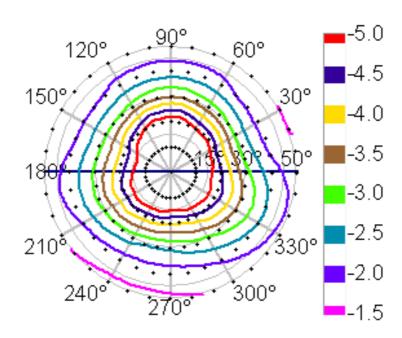

#### 6. Electro-Optical Characteristics

Table 11

| Item                        | Cymbol              | Temp. | Value |      |      | Unit | Condition                                                      |                                       |

|-----------------------------|---------------------|-------|-------|------|------|------|----------------------------------------------------------------|---------------------------------------|

| nem                         | Symbol              | °C    | Min.  | Typ. | Max. | Omi  | Condition                                                      |                                       |

| Driving voltage             | Vop                 | +25   | -     | 8.8  | -    | V    | Vop= optimum voltage                                           |                                       |

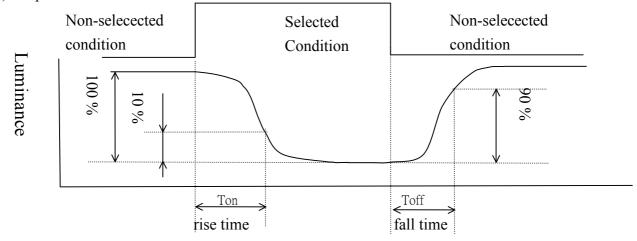

| Response time               | Ton                 | +25   | ı     | 5737 | 7458 | msec | Vop= Optimum voltage $\theta = 0^{\circ}, \phi = 0^{\circ}$    |                                       |

|                             | Toff                |       | -     | 5371 | 6982 |      |                                                                |                                       |

| Optimum viewing area Cr ≥ 2 | θ1(6 o'clock)       | +25   | 27    | 38   | -    | DEG  | φ=0°                                                           | Vop= Optimum<br>voltage<br>(Remark 1) |

|                             | θ2(12 o'clock)      |       | 30    | 44   | -    |      |                                                                |                                       |

|                             | \$\phi 1(3 o'clock) |       | 31    | 45   | -    |      | $\theta = 0$ °                                                 |                                       |

|                             | \$\phi 2(9 o'clock) |       | 30    | 44   | -    |      |                                                                |                                       |

| Contrast ratio              | Cr                  | +25   | 5     | 7    | -    | -    | Vop = Optimum voltage $\theta = 0^{\circ}, \ \phi = 0^{\circ}$ |                                       |

Remark 1: Due to hardware limitation, the maximum measurable angle is 50  $^{\rm O}$

#### 6.1 ISO plot

#### **6.2** Optical Characteristics Definition

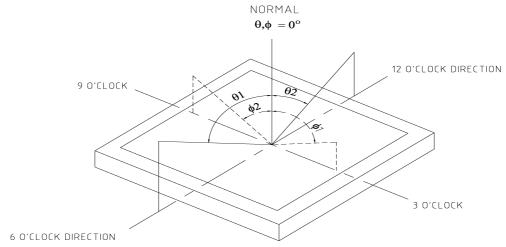

#### a.) Viewing Angle

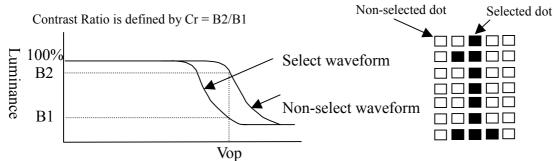

#### b.) Contrast Ratio

B1 = segments luminance in case of non-selected waveform

B2 = segments luminance in case of selected waveform

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for batron manufacturer:

Other Similar products are found below:

BTHQ42005VSS-FSTF-LED WHITE BT22008VSMNLEDRED BT96040AV2-COG-FSTF-12-I2C BTHQ21605V-COG-FSRE-I2C