## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

## Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- 2. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## H8/3048B Group

Hardware Manual

Renesas 8-Bit Single-Chip Microcomputer H8 Family/H8/300H Series

H8/3048B HD6433048B

HD6433048BV

H8/3048F-ONE HD64F3048B

HD64F3048BV

- Technology Corp. product best suited to the customer's application; they do not convey any under any intellectual property rights, or any other rights, belonging to Renesas Technology

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of a party's rights, originating in the use of any product data, diagrams, charts, programs, algoriti circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, progra algorithms represents information on products at the time of publication of these materials, subject to change by Renesas Technology Corp. without notice due to product improvemen other reasons. It is therefore recommended that customers contact Renesas Technology C

- an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein. The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corp. by various including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.co

- 4. When using any or all of the information contained in these materials, including product data diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a system before making a final decision on the applicability of the information and products. F Technology Corp. assumes no responsibility for any damage, liability or other loss resulting information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a system that is used under circumstances in which human life is potentially at stake. Please Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor

- considering the use of a product contained herein for any specific purposes, such as appara systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater us 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduc-

- whole or in part these materials. 7. If these products or technologies are subject to the Japanese export control restrictions, the be exported under a license from the Japanese government and cannot be imported into a

- other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/o country of destination is prohibited. 8. Please contact Renesas Technology Corp. for further details on these materials or the production

- contained therein.

Rev. 3.00 Sep 27, 2006 page ii of xxvi

2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. In

are in their open states, intermediate levels are induced by noise in the vicinity through current flows internally, and a malfunction may occur.

## 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throug chip and a low level is input on the reset pin. During the period where the stat undefined, the register settings and the output state of each pin are also undefined your system so that it does not malfunction because of processing while it is in undefined state. For those products which have a reset function, reset the LSI

1 Prohibition of Access to Undefined or Deserved Addresses

after the power supply has been turned on.

4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test may have been be allocated to these addresses. Do not access these registers; operation is not guaranteed if they are accessed.

Rev. 3.00 Sep 27, 2006 p

Rev. 3.00 Sep 27, 2006 page iv of xxvi

RENESAS

The on-chip emulator (E10T)\*2 has functions that allow it to emulate directly a micromounted on the user board. This makes possible on-board program debugging.

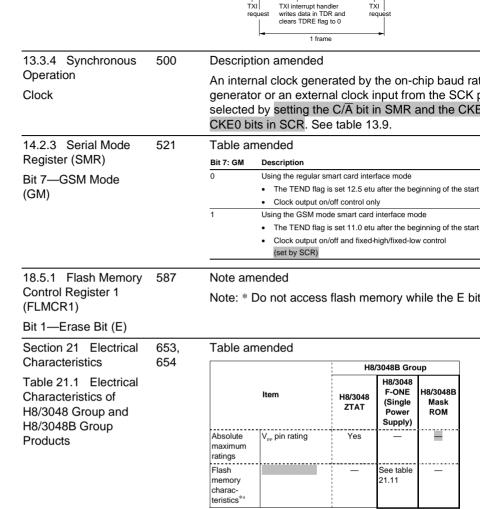

The on-chip supporting functions include ROM, RAM, a 16-bit integrated timer unit (programmable timing pattern controller (TPC), a watchdog timer (WDT), a serial continterface (SCI), an A/D converter, a D/A converter, I/O ports, a direct memory access (DMAC), a refresh controller, and other facilities. Of the two SCI channels, one has be expanded to support the ISO/IEC7816-3 smart card interface. Functions have also been reduce power consumption in battery-powered applications: individual modules can be

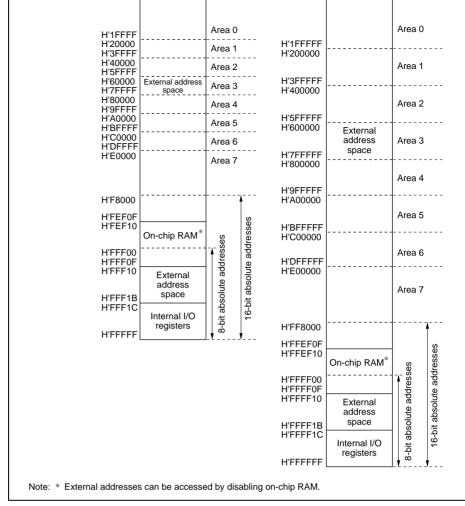

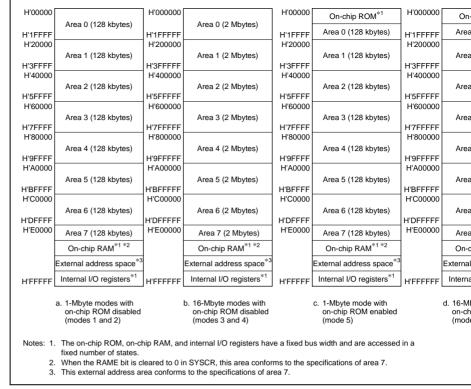

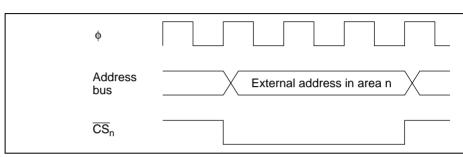

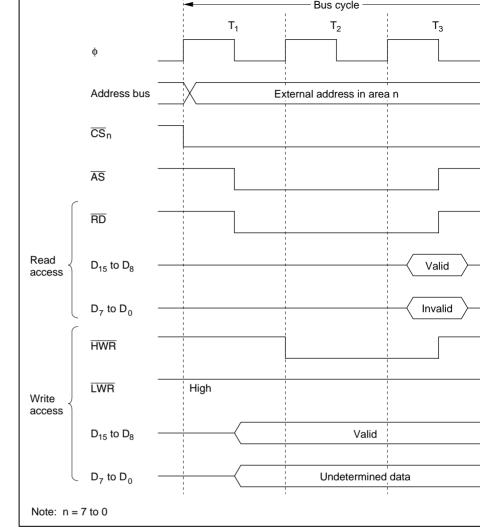

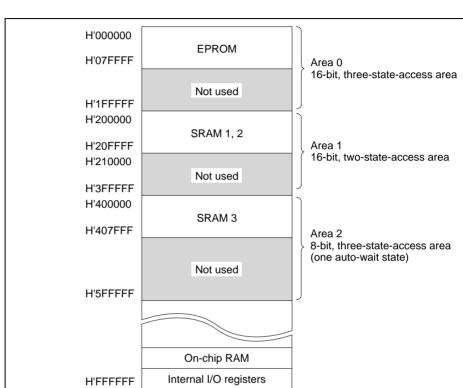

The address space is divided into eight areas. The data bus width and access cycle len selected independently in each area, simplifying the connection of different types of n Seven operating modes (modes 1 to 7) are provided, offering a choice of data bus wid address space size.

standby, and the frequency of the system clock supplied to the chip can be divided do

With these features, the H8/3048B Group can be used to implement compact, high-pe systems easily.

Versions with either flash memory (F-ZTAT<sup>TM\*1</sup>) or mask ROM as the on-chip ROM

available. This enables users to respond quickly and flexibly to changing application s from the initial production stage through full-scale volume production.

software control.

products, please refer to the H8/3048 Group Hardware Manual. For details of the instreefer to the H8/300H Series Programming Manual.

Notes: 1. F-ZTAT (Flexible ZTAT) is a trademark of Renesas Technology Corp.

This manual describes the H8/3048B Group hardware. For information on H8/3048 G

2. An on-chip emulator (E10T) is not provided in the mask ROM version.

Rev. 3.00 Sep 27, 2006 p

- 1. Only programs in the on-chip flash memory can be developed and debugged. Conse emulation is not possible for programs in external memory or in the no-ROM mode

- emulation is not possible for programs in external memory or in the no-ROM mode 2. Refresh controller and DMAC operation are not supported, so settings should not b

- 3. During break mode of on-chip emulation, the watchdog timer stops counting. Acco counter value may be invalid after resuming from the break mode.

- 4. The FWE (BRK) pin and pins P91, P93, and P95 are reserved for the E10T, and caused.

- 5. Area H'F7000 to H'F7FFF in 1-M address mode (area H'FF7000 to H'FF77FF in 16 mode) is used by the E10T, and is not available to the user.6. The initial program instructions following a reset should be initialize stack pointer (area H'FF7000 to H'FF77FF in 16 mode).

- read mode register (MDCR). (After initializing SP using the MOV.L instruction, us MOV.B instruction to read the MDCR register.)

the registers for these modules.

7. Emulation of the hardware standby mode is not supported.

Rev. 3.00 Sep 27, 2006 page vi of xxvi

RENESAS

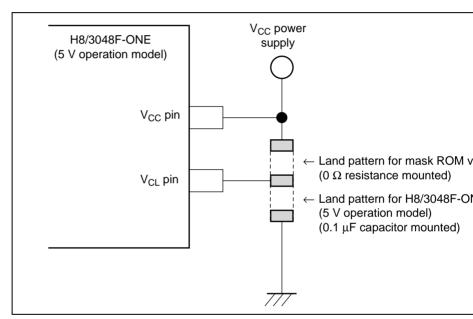

2. H8/3048F-ONE has single power supply with flash memory and E10T ins

H8/3048 Group

(Rev. 7.0)

Mask ROM

H8/3048 mask ROM

H8/3047 mask ROM

H8/3045 mask ROM

H8/3044 mask ROM

Mask ROM model

version

version

version

version

H8/3048B

F-ZTAT

H8/3048F

**Dual power**

H8/3048F-ONE

Single power

(Rev. 3

Н

R

M

Hardware

**ROM Type**

Model Type

Model Spec

**ZTAT**

PROM model

H8/3048

Manual

| ·                 |                                                   |                                                                         | supply, flash<br>memory is<br>installed                                  | supply, flash<br>memory installed,<br>internal step-<br>down (5 V<br>operation model),<br>high-speed<br>operation model | me            |

|-------------------|---------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------|

|                   |                                                   |                                                                         | Refer to 1.4,<br>Differences<br>between<br>H8/3048F and<br>H8/3048F-ONE. | Refer to 1.4.3,<br>Differences<br>between<br>H8/3048F and<br>H8/3048F-ONE.                                              | 1             |

| Model Type<br>No. | HD6473048                                         | HD6433048<br>HD6433047<br>HD6433045<br>HD6433044                        | HD64F3048                                                                | HD64F3048B<br>(5 V operation<br>model)                                                                                  | HI<br>(5<br>m |

|                   |                                                   | 1100433044                                                              |                                                                          | HD64F3048BV<br>(3 V operation<br>model)                                                                                 | (3<br>m       |

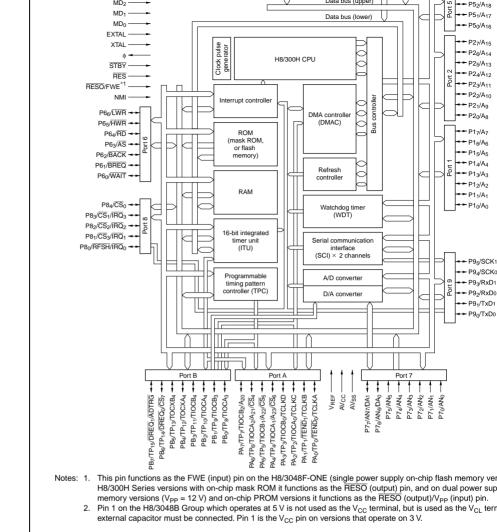

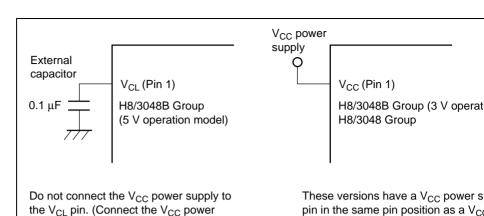

| Pin<br>Assignment | Refer to figure<br>H8/3048 Mask<br>Version, H8/30 | 5-V operation models and an external capa connected.                    |                                                                          |                                                                                                                         |               |

|                   | ROM Version,<br>View), in section                 | Refer to figure 1.3, He<br>Pin Arrangement (FP<br>100B, Top View), in s |                                                                          |                                                                                                                         |               |

|                   | <u>,</u>                                          |                                                                         | Rev. 3.0                                                                 | 00 Sep 27, 2006                                                                                                         | ра            |

|                                               |                                     | H8/3044: 32 kbytes                                                             |                            |              |                                                                                                           |      |

|-----------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------|----------------------------|--------------|-----------------------------------------------------------------------------------------------------------|------|

| Flash Memory                                  | _                                   | _                                                                              | 19, Fla<br>Memoi<br>(H8/30 |              | Refer to section<br>18, ROM<br>(H8/3048F-ONE:<br>Single Power<br>Supply, H8/3048B<br>Mask ROM<br>Version) |      |

| Clock Pulse<br>Generator                      | Refer to section                    | Refer to section 19<br>Generator.                                              | , Cl                       |              |                                                                                                           |      |

| Power-Down<br>State                           | Refer to section                    | Refer to section 20 State.                                                     | , Po                       |              |                                                                                                           |      |

|                                               | Clock oscillator states             | Clock oscillator settling time of up to 262144 s                               |                            |              |                                                                                                           |      |

| Electrical<br>Characteristics<br>(Clock Rate) | Refer to table 22<br>Group Products | Refer to table 21.1<br>Characteristics of H<br>and H8/3048B Gro<br>section 21. | -<br>18/3                  |              |                                                                                                           |      |

|                                               | 1 to 18 MHz                         | 5 V operation mode<br>2 to 25 MHz,<br>3 V operation mode<br>2 to 25 MHz.       |                            |              |                                                                                                           |      |

| List of<br>Registers                          | Refer to table B appendix B.        | .1, Comparison of H8/304                                                       | 18 Grou                    | p Internal I | /O Register Specific                                                                                      | atic |

|                                               | Refer to append                     | dix B.1, Addresses.                                                            |                            |              |                                                                                                           |      |

| Notes on<br>Usage                             | _                                   | _                                                                              |                            | _            | Refer to section<br>1.4, Notes on<br>H8/3048F-ONE<br>(Single Power                                        |      |

Rev. 3.00 Sep 27, 2006 page viii of xxvi

On-chip Emulator (E10T)

Supply)

On-chip emulator (E10T)

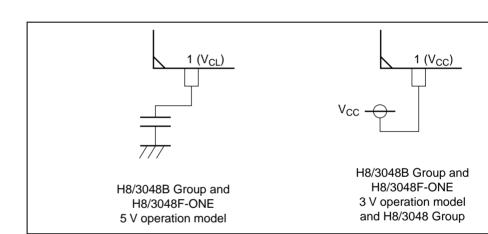

| Arrangement Figure 1.3 H8/3048B Group Pin Arrangement (FP- 100B or TFP-100B, Top View) |        | Note: 1. F             | or the 5                    | or the 3 | V opera  | tion mod                                                              | els, this                              |

|----------------------------------------------------------------------------------------|--------|------------------------|-----------------------------|----------|----------|-----------------------------------------------------------------------|----------------------------------------|

| 1.3.3 Pin Functions                                                                    | 18, 19 | Table am               | ended                       |          |          |                                                                       |                                        |

| Table 1.4 Pin                                                                          |        | Туре                   | Symbol                      | Pin No.  | I/O      | Name and I                                                            | Function                               |

| Functions                                                                              |        | A/D and D/A converters | AV <sub>cc</sub>            | 76       | Input    | Power supp<br>converters.<br>supply (V <sub>cc</sub> )<br>D/A convert | Connect to the<br>when not us          |

|                                                                                        |        |                        | AV <sub>ss</sub>            | 86       | Input    | Ground pin                                                            |                                        |

|                                                                                        |        |                        | V <sub>REF</sub>            | 77       | Input    | Reference v<br>D/A convert<br>power suppl<br>and D/A cor              | ers. Connectly (V <sub>cc</sub> ) when |

| 1.4.2 Product Type                                                                     | 21     | Sample m               | narkings                    | amende   | d        |                                                                       |                                        |

| Names and Markings                                                                     |        |                        | Dual Powe<br>Model: H8/     |          | Single I | Power Supply                                                          | Model: H8/                             |

| Table 1.5 Differences in H8/3048F and H8/3048F-ONE                                     |        | Sample<br>markings     | H8/3<br>3J1<br>HD<br>64F304 |          |          |                                                                       | 64F<br>H8/<br>PGM<br>BK80              |

RENESAS

Rev. 3.00 Sep 27, 2006 p

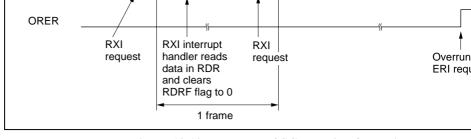

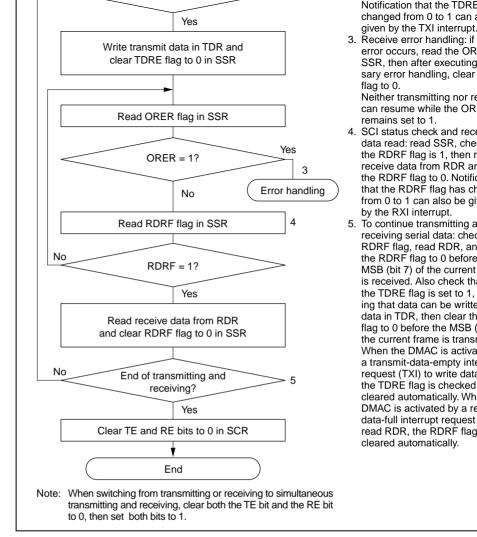

Read Write IRQb Execution

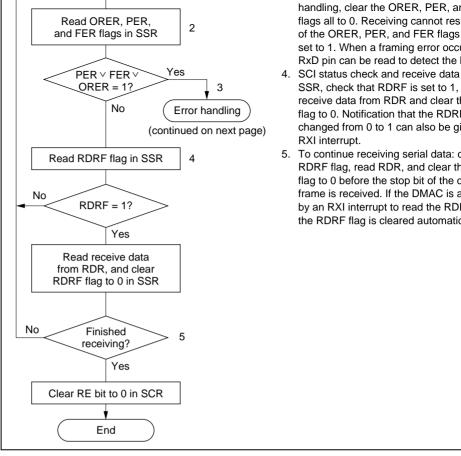

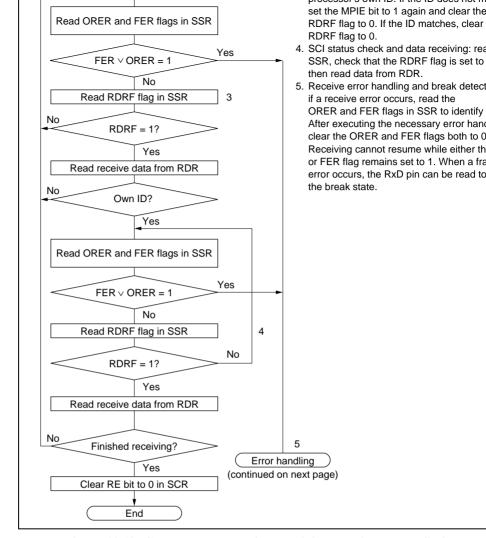

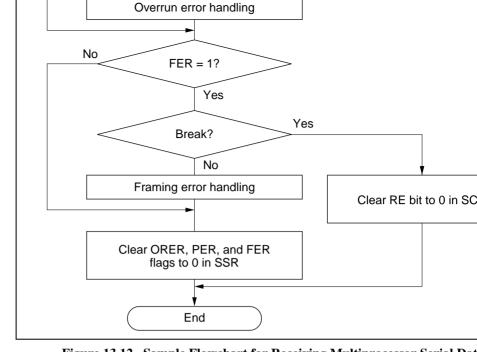

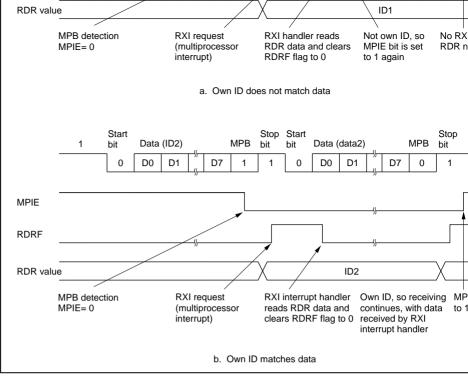

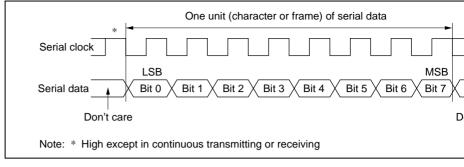

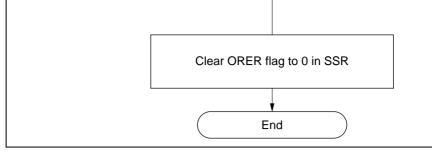

RXI interrupt handler reads data in RDR and clears RDRF flag to 0

RXI request Read

| Occurrence | condition | 1 |

|------------|-----------|---|

|------------|-----------|---|

|                                       |      |                   |        |       |              |          |            |                   |          |         | Clear         |

|---------------------------------------|------|-------------------|--------|-------|--------------|----------|------------|-------------------|----------|---------|---------------|

|                                       |      |                   |        | Occur | rrence cond  | lition 1 | ]          |                   |          | С       | Occurren      |

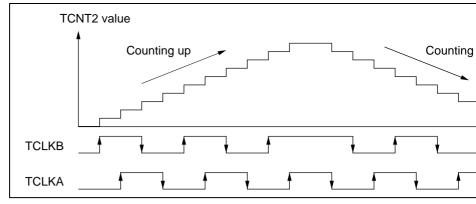

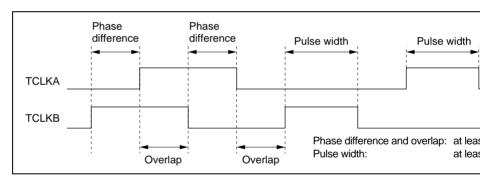

| 10.2.3 Timer Mode                     | 335  | Table a           | mei    | nded  |              |          |            |                   |          |         |               |

| Register (TMDR)                       |      | Counting [        | Direct | ion   | Down-Cou     | unting   | g          |                   | Up-      | -Counti | ng            |

| Bit 6—Phase Counting                  |      | TCLKA pin         |        |       | ↑ F          | High     | ↓          | Low               | <u> </u> | Lo      | ow .          |

| Mode Flag (MDF)                       |      | TCLKB pin         |        |       | Low ↑        | 1        | High       | <b>\</b>          | Hig      | h ↑     |               |

| 13.2.8 Bit Rate                       | 473, | Table a           | mer    | nded  |              |          |            |                   |          |         |               |

| Register (BRR)                        | 475  |                   | _      |       |              |          | φ (MI      | Hz)               | 1        |         |               |

| Table 13.3 Examples                   |      |                   |        | 3     | ,            |          | 3.68       | 64                | T        | 25      |               |

| of Bit Rates and BRR<br>Settings in   |      | Bit Rate (bits/s) | n      | N     | Error<br>(%) | n        | N          | Error<br>(%)      | n        | N       | Erro<br>(%)   |

| Asynchronous Mode                     |      | 110               | 1      | 212   | 0.03         | 2        | 64         | 0.70              | 3        | 110     | -0.02         |

| Asylicilionous Mouc                   |      | 150               | 1      | 155   | 0.16         | 1        | 191        | 0.00              | 3        | 80      | 0.47          |

|                                       |      | 300               | 1      | 77    | 0.16         | 1        | 95         | 0.00              | 2        | 162     | -0.1          |

|                                       |      | 600               | 0      | 155   | 0.16         | 0        | 191        | 0.00              | 2        | 80      | 0.47          |

|                                       |      | 1200              | 0      | 77    | 0.16         | 0        | 95         | 0.00              | 1        | 162     | -0.1          |

|                                       |      | 2400              | 0      | 38    | 0.16         | 0        | 47         | 0.00              | 1        | 80      | 0.47          |

|                                       |      | 4800              | 0      | 19    | -2.34        | 0        | 23         | 0.00              | 0        | 162     | -0.1          |

|                                       |      | 9600              | 0      | 9     | -2.34        | 0        | 11         | 0.00              | 0        | 80      | 0.47          |

|                                       |      | 19200             | 0      | 4     | -2.34        | 0        | 5          | 0.00              | 0        | 40      | -0.7          |

|                                       |      | 31250             | 0      | 2     | 0.00         | 0        | 3          | <del>-</del> 7.84 | 0        | 24      | 0.00          |

|                                       |      | 38400             | 0      | 1     | 22.07        | 0        | 2          | 0.00              | 0        | 19      | 1.73          |

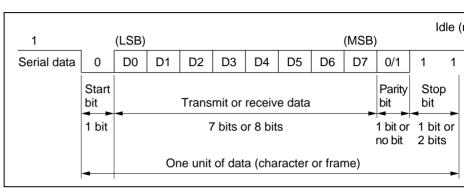

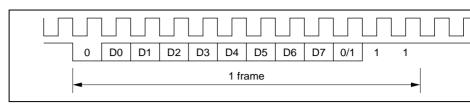

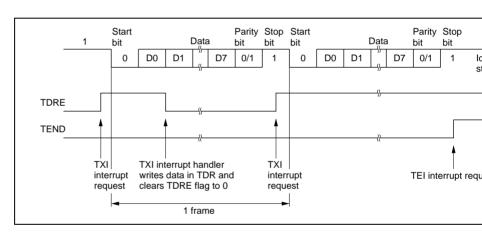

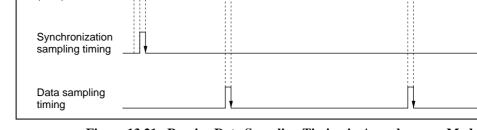

| 13.3.2 Operation in Asynchronous Mode | 492  | Figure a          | Sta    | art   |              |          | arity Stop |                   |          | Dete    | Parity        |

| Figure 13.8 Example of SCI Receive    |      | 1_                | bit    |       | Data<br>D1 % |          | 0/1 1      | bit 0 Di          | 0 D1     | Data    | bit<br>07 0/1 |

RDRF

Rev. 3.00 Sep 27, 2006 page x of xxvi

Operation (8-Bit Data

with Parity and One

Stop Bit)

1 frame

Rev. 3.00 Sep 27, 2006 p

|                                    |     | spec                                                                     | шса                                            | แบทธ                             | )                                                            |                                    |              |                                        |

|------------------------------------|-----|--------------------------------------------------------------------------|------------------------------------------------|----------------------------------|--------------------------------------------------------------|------------------------------------|--------------|----------------------------------------|

| B.1 Addresses (For                 | 742 | Note amended                                                             |                                                |                                  |                                                              |                                    |              |                                        |

| H8/3048F-ONE,<br>H8/3048B Mask ROM |     | Note: 4. Byte data must be used to access FLMCR1 FLMCR2, EBR, and RAMCR. |                                                |                                  |                                                              |                                    |              |                                        |

| Version)                           |     |                                                                          |                                                |                                  |                                                              | MCR2, EB                           |              |                                        |

|                                    |     |                                                                          |                                                |                                  |                                                              | sh memory                          |              |                                        |

|                                    |     | RON                                                                      | /I ver                                         | sion                             | does not                                                     | have these                         | registe      | ers.                                   |

| B.3 Function                       | 829 | Tabl                                                                     | e am                                           | ende                             | ed                                                           |                                    |              |                                        |

| ADCR                               |     | H8/30                                                                    | )48F-C                                         | NE                               |                                                              | Not include the                    | is register  |                                        |

|                                    |     | H8/30<br>H8/30<br>H8/30<br>H8/30                                         | 048B m<br>048ZT/<br>048 ma<br>047 ma<br>045 ma | AT<br>ask RO<br>ask RO<br>ask RO | OM version M version M version M version M version M version | Include this re                    | gister       |                                        |

| ADCR                               | 829 | Tabl                                                                     | e am                                           | ende                             | ed                                                           |                                    |              |                                        |

|                                    |     | H8/30                                                                    | )48F-C                                         | NE                               |                                                              | Include this re                    | gister       |                                        |

|                                    |     | H8/30<br>H8/30<br>H8/30<br>H8/30                                         | 048B m<br>048ZTA<br>048 ma<br>047 ma<br>045 ma | AT<br>ask RO<br>ask RO<br>ask RO | OM version M version M version M version M version M version | Not include thi                    | s register   |                                        |

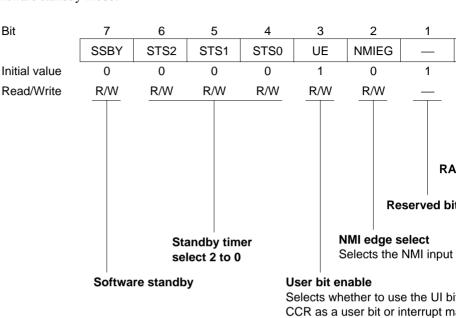

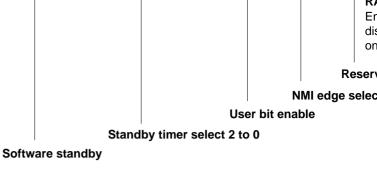

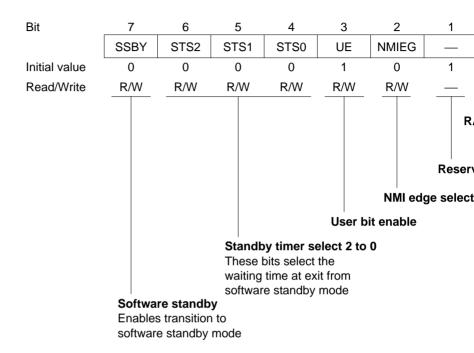

| SYSCR                              | 833 | Tabl                                                                     | e am                                           | ende                             | ed                                                           |                                    |              |                                        |

|                                    |     |                                                                          |                                                | r select                         | 2 to 0                                                       |                                    |              |                                        |

|                                    |     | Bit 6                                                                    | Bit 5                                          | Bit 4                            | H9/20                                                        | Standb<br>048F-ONE                 | y Timer      |                                        |

|                                    |     |                                                                          | STS1                                           | STS0                             | H8/3048B ma                                                  | ask ROM version                    |              | *                                      |

|                                    |     | 0                                                                        | 0                                              | 1                                |                                                              | = 8,192 states<br>= 16,384 states  |              | ne = 8,192 states                      |

|                                    |     |                                                                          | 1                                              | 0                                |                                                              | = 10,364 states<br>= 32,768 states |              | ne = 16,384 state<br>ne = 32,768 state |

|                                    |     |                                                                          |                                                | 1                                | Waiting time :                                               | = 65,536 states                    | Waiting tin  | ne = 65,536 state                      |

|                                    |     | 1                                                                        | 0                                              | 0                                |                                                              | = 131,072 states                   |              | ne = 131,072 stat                      |

|                                    |     |                                                                          | 1                                              | 1                                |                                                              | = 262,144 states<br>= 1,024 states | Waiting tin  | ne = 1,024 states                      |

|                                    |     |                                                                          | '                                              | 1                                | Illegal setting                                              |                                    | Illegal sett | -                                      |

|                                    |     | L .                                                                      |                                                |                                  |                                                              |                                    | 1 094. 301   | 5                                      |

Rev. 3.00 Sep 27, 2006 page xii of xxvi

Note: \* H8/3048F H8/3048ZTAT H8/3048 mask ROM version H8/3047 mask ROM version H8/3045 mask ROM version H8/3044 mask ROM version

| 1       | 4.2 Product Type Names and Markings                      |         |

|---------|----------------------------------------------------------|---------|

| 1       | 4.3 Differences between H8/3048F and H8/3048F-ONE        |         |

| 1       | 4.4 V <sub>CL</sub> Pin                                  |         |

| 1       | 4.5 Note on Changeover to H8/3048 Group Mask ROM Version |         |

| 1.5 S   | etting Oscillation Settling Wait Time                    |         |

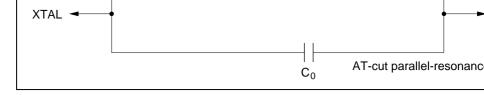

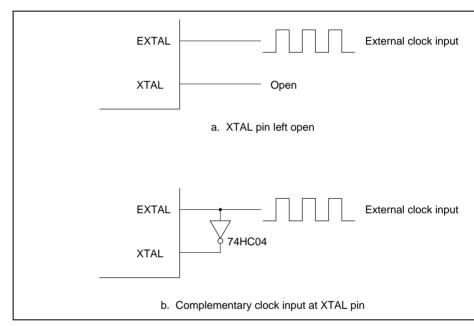

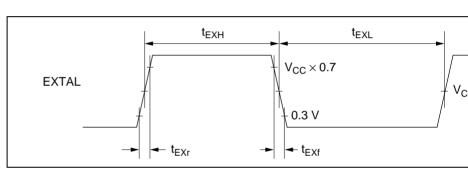

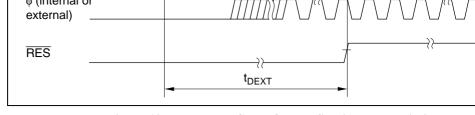

|         | otes on Crystal Resonator Connection                     |         |

| Section | 2 CPU                                                    |         |

|         | verview                                                  |         |

| 2       | 1.1 Features                                             |         |

| 2       | 1.2 Differences from H8/300 CPU                          |         |

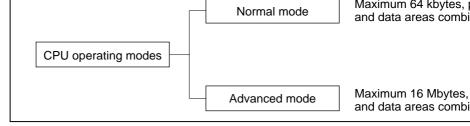

| 2.2     | PU Operating Modes                                       |         |

| 2.3 A   | ddress Space                                             |         |

| 2.4 F   | egister Configuration                                    |         |

|         | 4.1 Overview                                             |         |

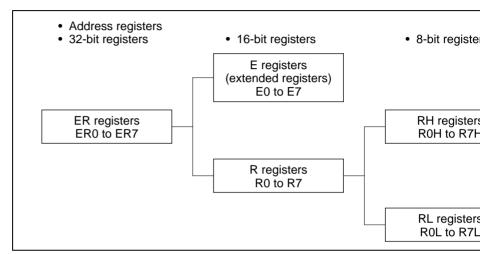

| 2       | 4.2 General Registers                                    |         |

| 2       | 4.3 Control Registers                                    | •••••   |

| 2       | 4.4 Initial CPU Register Values                          |         |

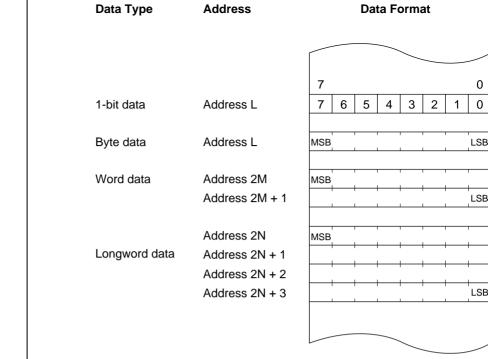

| 2.5 I   | ata Formats                                              |         |

| 2       | 5.1 General Register Data Formats                        |         |

| 2       | 5.2 Memory Data Formats                                  |         |

| 2.6 I   | struction Set                                            |         |

|         | 6.1 Instruction Set Overview                             |         |

| 2       | 6.2 Instructions and Addressing Modes                    |         |

| 2       | 6.3 Tables of Instructions Classified by Function        |         |

| 2       | 6.4 Basic Instruction Formats                            |         |

| 2       | 6.5 Notes on Use of Bit Manipulation Instructions        |         |

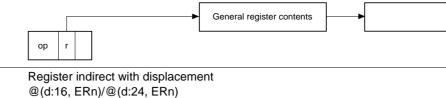

| 2.7 A   | ddressing Modes and Effective Address Calculation        |         |

|         | 7.1 Addressing Modes                                     |         |

|         | Rev. 3.00 Sep 27,                                        | 2006 pa |

|         | RENESAS                                                  |         |

1.3.3

1.4.1

1.4

Pin Functions .....

Voltage Application.....

Notes on H8/3048F-ONE (Single Power Supply) .....

|      | 3.1.1                        | Operating Mode Selection              |  |  |  |  |  |  |  |

|------|------------------------------|---------------------------------------|--|--|--|--|--|--|--|

|      | 3.1.2                        | Register Configuration                |  |  |  |  |  |  |  |

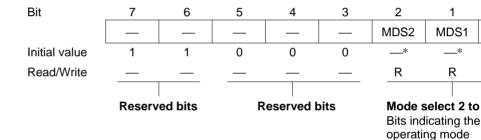

| 3.2  | Mode Control Register (MDCR) |                                       |  |  |  |  |  |  |  |

| 3.3  |                              | n Control Register (SYSCR)            |  |  |  |  |  |  |  |

| 3.4  | Operating Mode Descriptions  |                                       |  |  |  |  |  |  |  |

|      | 3.4.1                        | Mode 1                                |  |  |  |  |  |  |  |

|      | 3.4.2                        | Mode 2                                |  |  |  |  |  |  |  |

|      | 3.4.3                        | Mode 3                                |  |  |  |  |  |  |  |

|      | 3.4.4                        | Mode 4                                |  |  |  |  |  |  |  |

|      | 3.4.5                        | Mode 5                                |  |  |  |  |  |  |  |

|      | 3.4.6                        | Mode 6                                |  |  |  |  |  |  |  |

|      | 3.4.7                        | Mode 7                                |  |  |  |  |  |  |  |

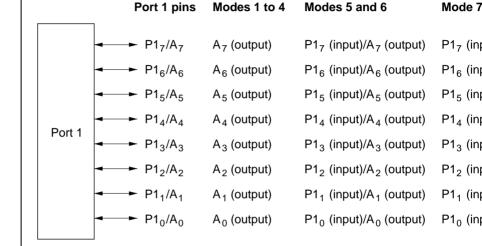

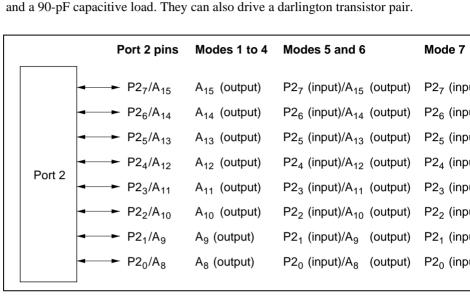

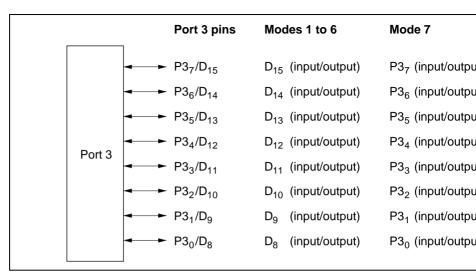

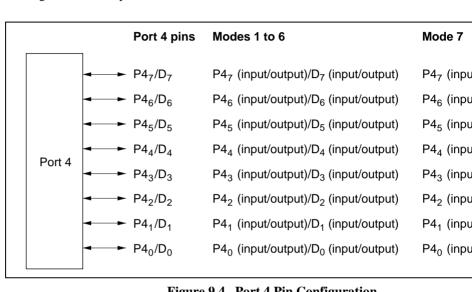

| 3.5  | Pin Fu                       | nctions in Each Operating Mode        |  |  |  |  |  |  |  |

| 3.6  | Memo                         | ry Map in Each Operating Mode         |  |  |  |  |  |  |  |

|      |                              |                                       |  |  |  |  |  |  |  |

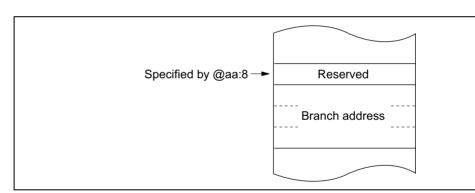

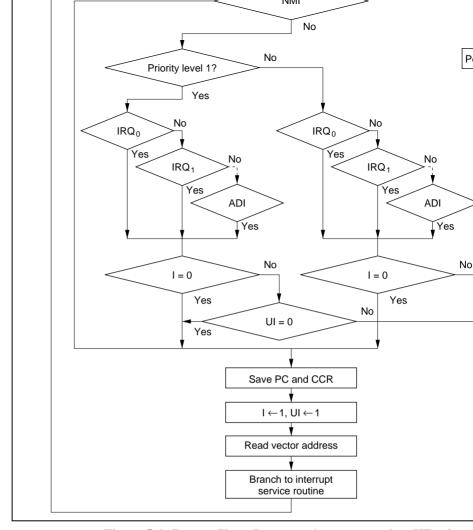

| Sect |                              | Exception Handling                    |  |  |  |  |  |  |  |

| 4.1  | Overv                        | iew                                   |  |  |  |  |  |  |  |

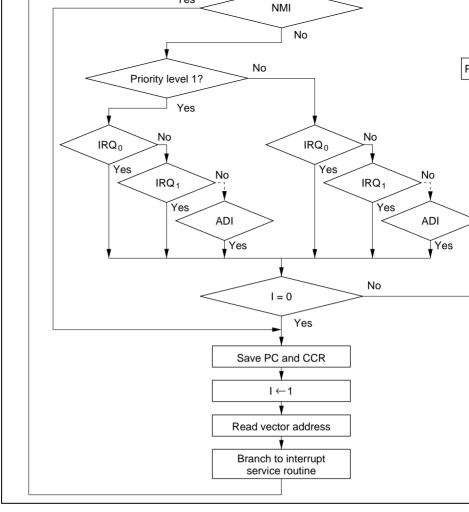

|      | 4.1.1                        | Exception Handling Types and Priority |  |  |  |  |  |  |  |

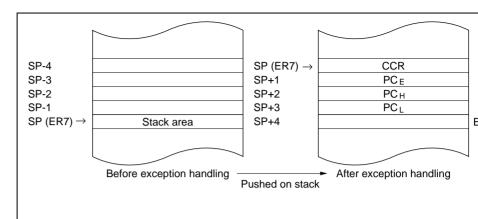

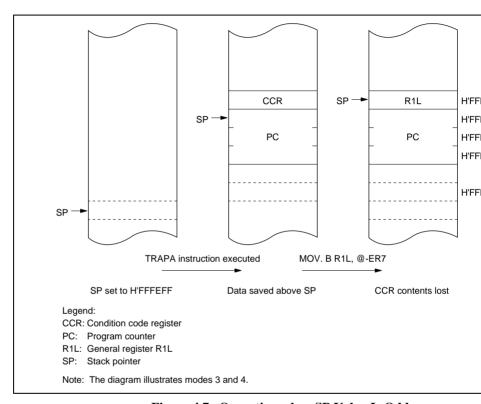

|      | 4.1.2                        | Exception Handling Operation          |  |  |  |  |  |  |  |

|      | 4.1.3                        | Exception Vector Table                |  |  |  |  |  |  |  |

| 4.2  | Reset.                       |                                       |  |  |  |  |  |  |  |

|      | 4.2.1                        | Overview                              |  |  |  |  |  |  |  |

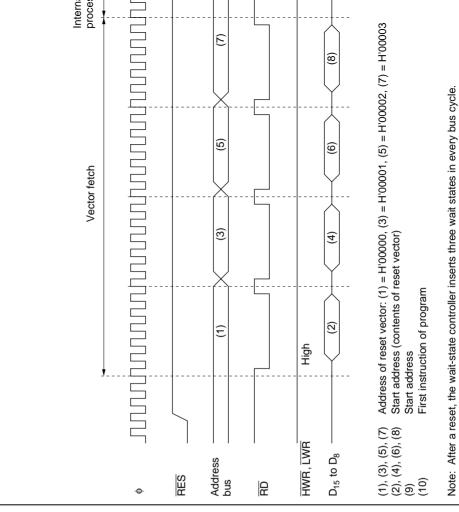

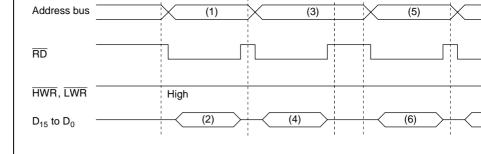

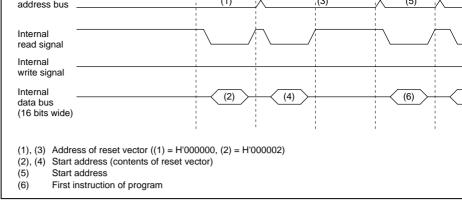

|      | 4.2.2                        | Reset Sequence                        |  |  |  |  |  |  |  |

|      | 4.2.3                        | Interrupts after Reset                |  |  |  |  |  |  |  |

| _    |                              |                                       |  |  |  |  |  |  |  |

| Rev. | 3.00 Se                      | ep 27, 2006 page xiv of xxvi          |  |  |  |  |  |  |  |

|      |                              |                                       |  |  |  |  |  |  |  |

2.9

2.9.1

2.9.2 2.9.3

2.9.4

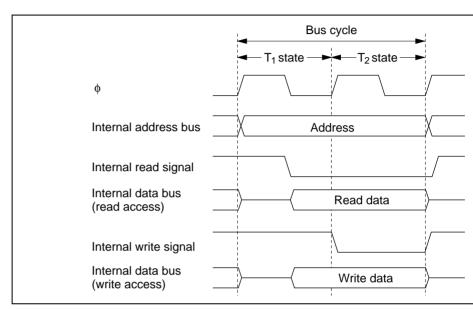

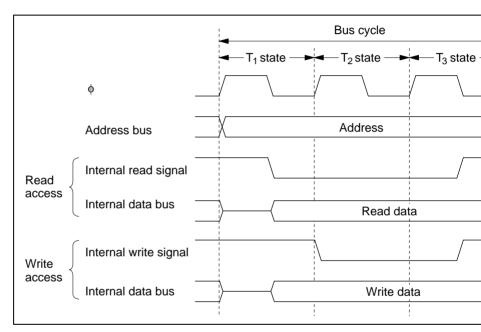

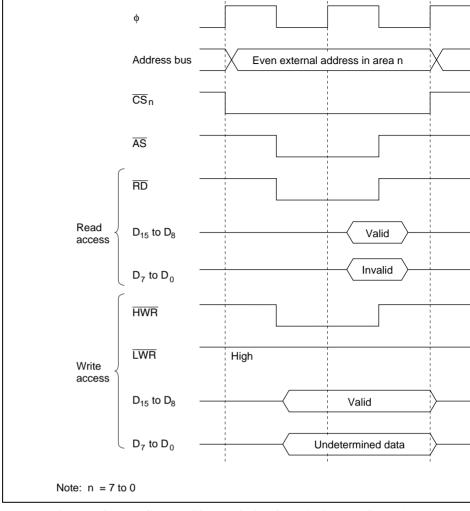

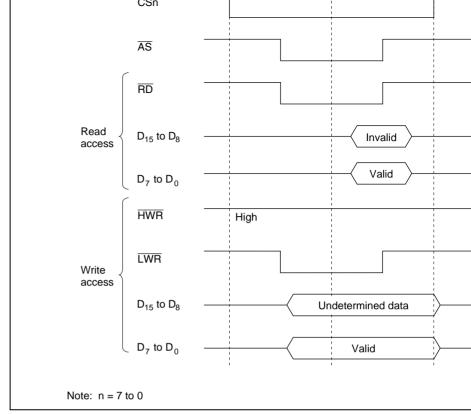

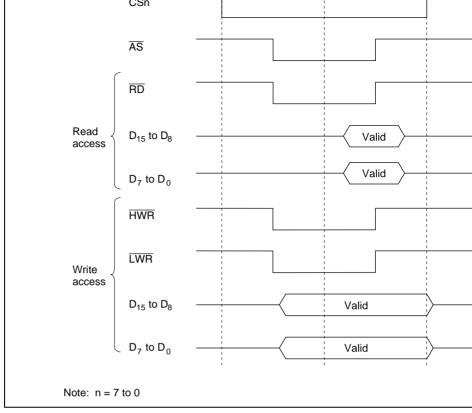

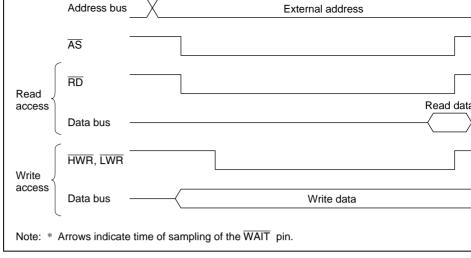

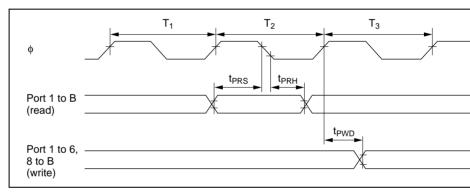

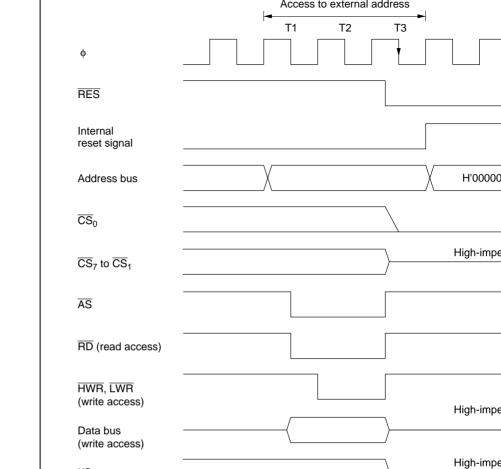

Basic Operational Timing .....

Section 3 MCU Operating Modes ..... Overview.....

Overview..... On-Chip Memory Access Timing.....

On-Chip Supporting Module Access Timing .....

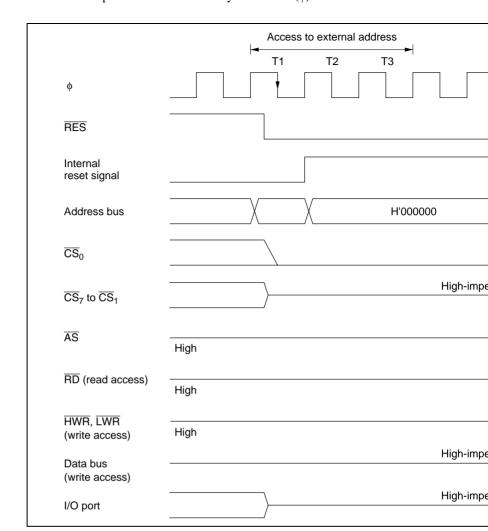

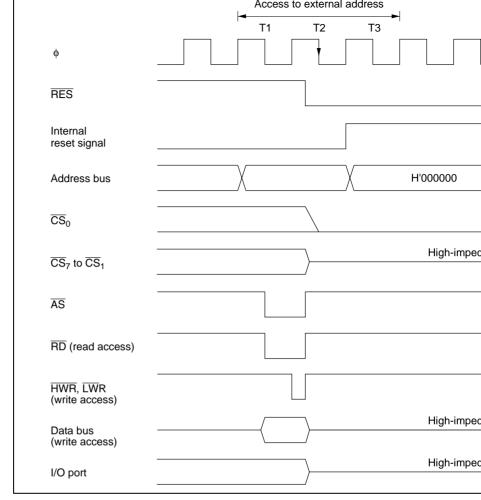

Access to External Address Space.....

RENESAS

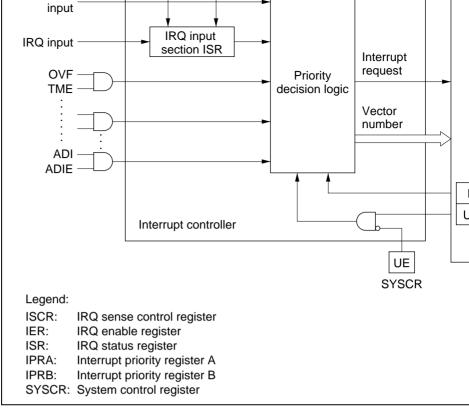

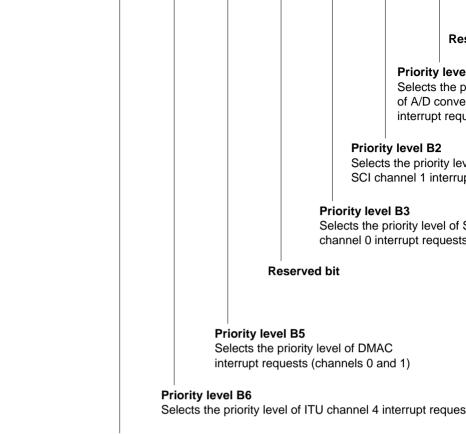

|          | 5.2.2   | Interrupt Priority Registers A and B (IPRA, IPRB)                |

|----------|---------|------------------------------------------------------------------|

|          | 5.2.3   | IRQ Status Register (ISR)                                        |

|          | 5.2.4   | IRQ Enable Register (IER)                                        |

|          | 5.2.5   | IRQ Sense Control Register (ISCR)                                |

| 5.3      | Interru | ipt Sources                                                      |

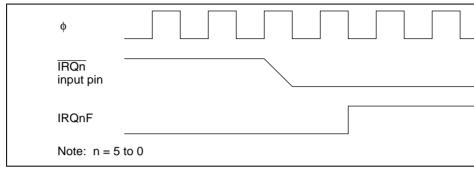

|          | 5.3.1   | External Interrupts                                              |

|          | 5.3.2   | Internal Interrupts                                              |

|          | 5.3.3   | Interrupt Vector Table                                           |

| 5.4      | Interru | pt Operation                                                     |

|          | 5.4.1   | Interrupt Handling Process                                       |

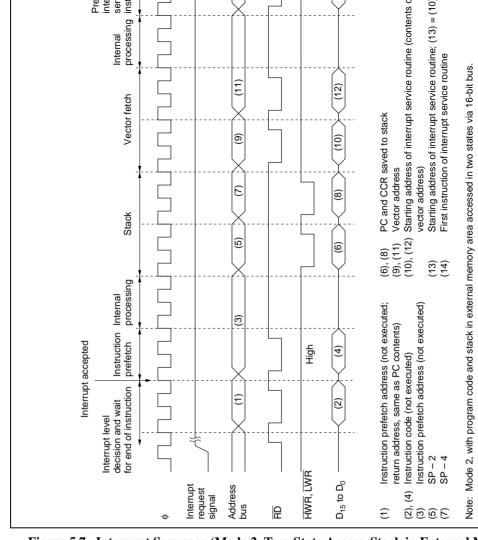

|          | 5.4.2   | Interrupt Sequence                                               |

|          | 5.4.3   | Interrupt Response Time                                          |

| 5.5      | Usage   | Notes                                                            |

|          | 5.5.1   | Contention between Interrupt and Interrupt-Disabling Instruction |

|          | 5.5.2   | Instructions That Inhibit Interrupts                             |

|          | 5.5.3   | Interrupts during EEPMOV Instruction Execution                   |

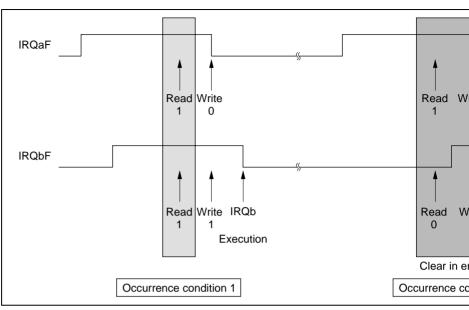

|          | 5.5.4   | Usage Notes on External Interrupts                               |

|          | 5.5.5   | Notes on Non-Maskable Interrupts (NMI)                           |

| <b>a</b> |         | D. G II                                                          |

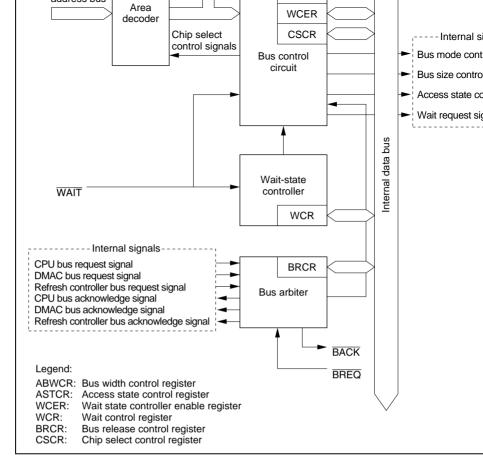

|          |         | Bus Controller                                                   |

| 6.1      |         | iew                                                              |

|          | 6.1.1   | Features                                                         |

|          | 6.1.2   | Block Diagram                                                    |

|          | 6.1.3   | Input/Output Pins                                                |

|          | 6.1.4   | Register Configuration                                           |

| 6.2      | _       | er Descriptions                                                  |

|          | 6.2.1   | Bus Width Control Register (ABWCR)                               |

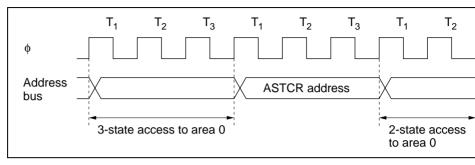

|          | 6.2.2   | Access State Control Register (ASTCR)                            |

|          |         | Rev. 3.00 Sep 27, 2006 p                                         |

|          |         | RENESAS                                                          |

|          |         | -(2.423/23                                                       |

|          |         |                                                                  |

|          |         |                                                                  |

Pin Configuration.....

Register Configuration.....

System Control Register (SYSCR)

Register Descriptions

5.1.3

5.1.4

5.2.1

5.2

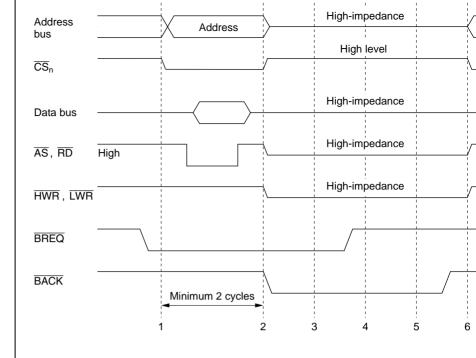

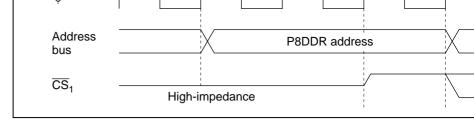

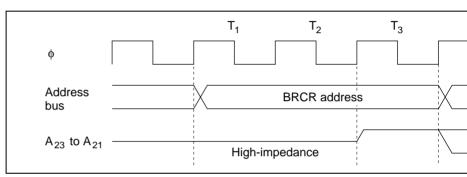

|      | 6.3.7   | Bus Arbiter Operation                           |

|------|---------|-------------------------------------------------|

| 6.4  | Usage   | Notes                                           |

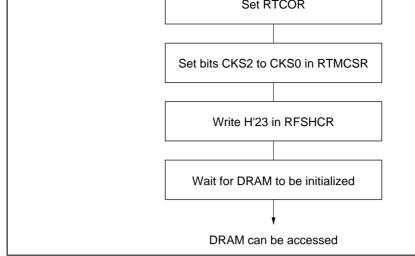

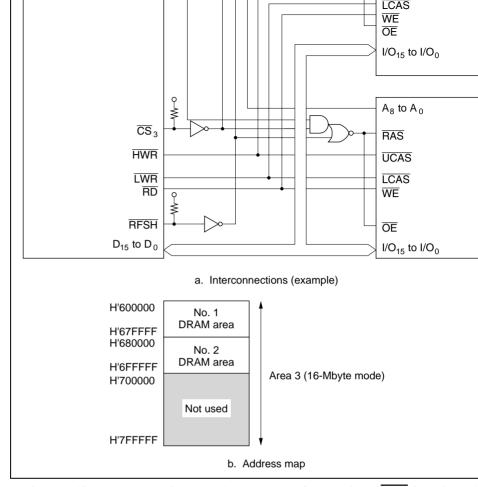

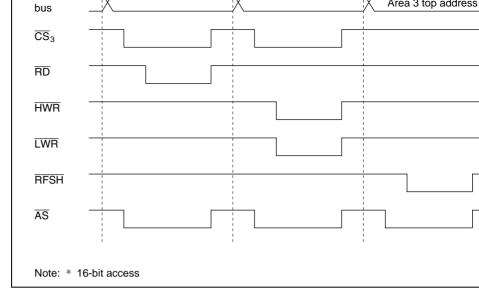

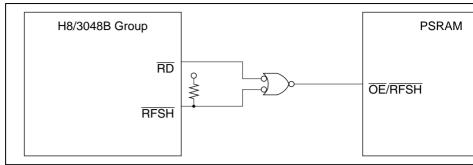

|      | 6.4.1   | Connection to Dynamic RAM and Pseudo-Static RAM |

|      | 6.4.2   | Register Write Timing                           |

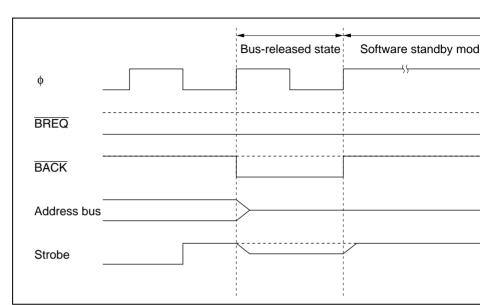

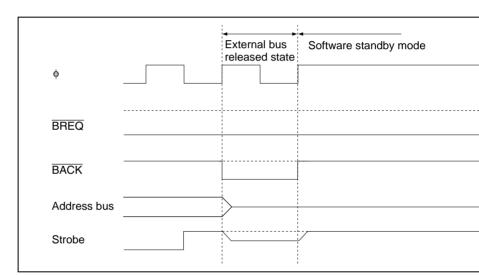

|      | 6.4.3   | BREQ Input Timing                               |

|      | 6.4.4   | Transition To Software Standby Mode             |

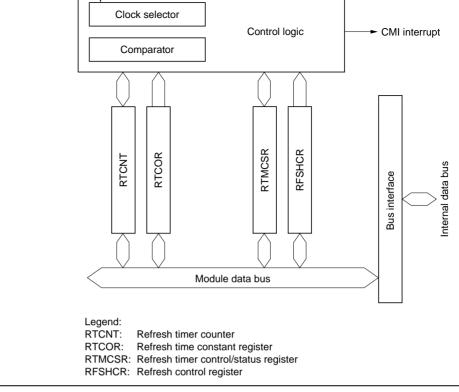

| Sect | ion 7   | Refresh Controller                              |

| 7.1  |         |                                                 |

| 7.1  |         | ew                                              |

|      | 7.1.1   | Features                                        |

|      | 7.1.2   | Block Diagram                                   |

|      | 7.1.3   | Input/Output Pins                               |

|      | 7.1.4   | Register Configuration                          |

| 7.2  | Regist  | er Descriptions                                 |

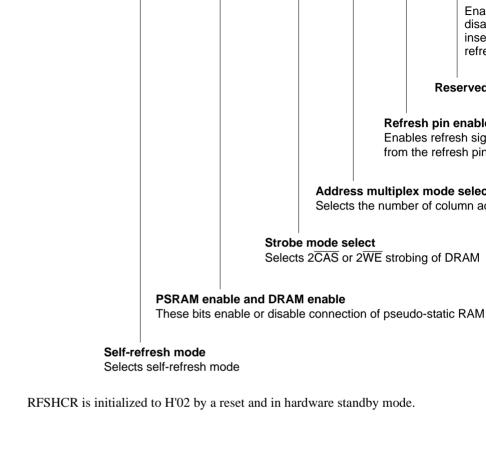

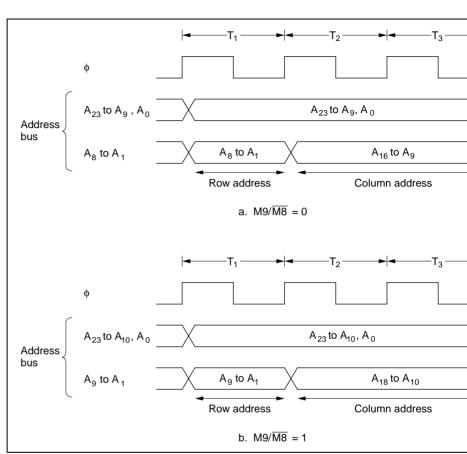

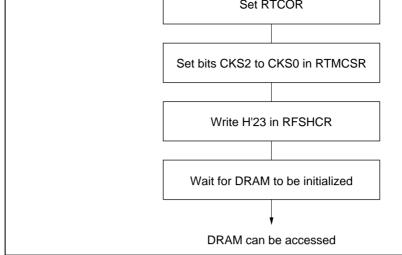

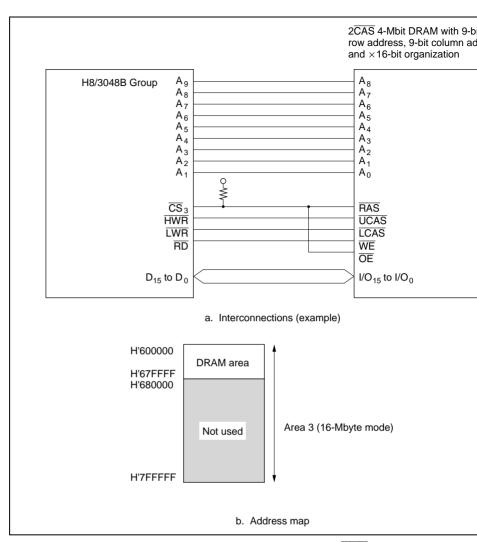

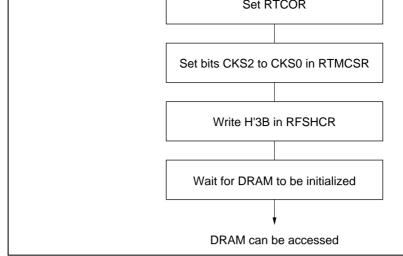

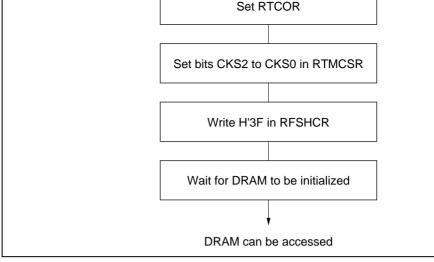

|      | 7.2.1   | Refresh Control Register (RFSHCR)               |

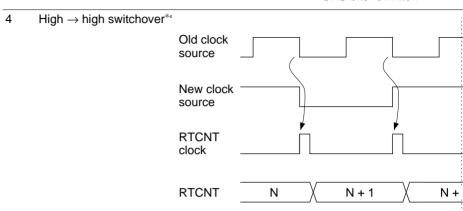

|      | 7.2.2   | Refresh Timer Control/Status Register (RTMCSR)  |

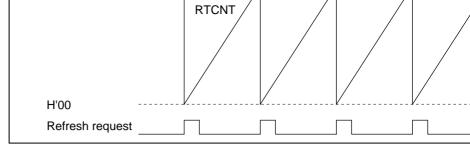

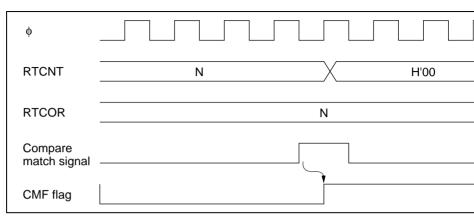

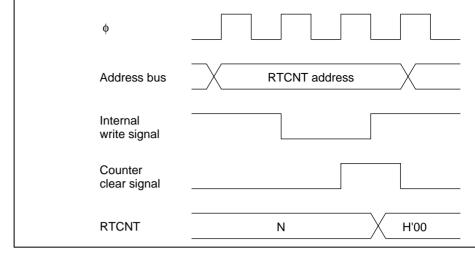

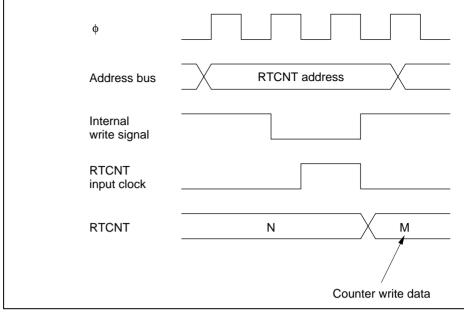

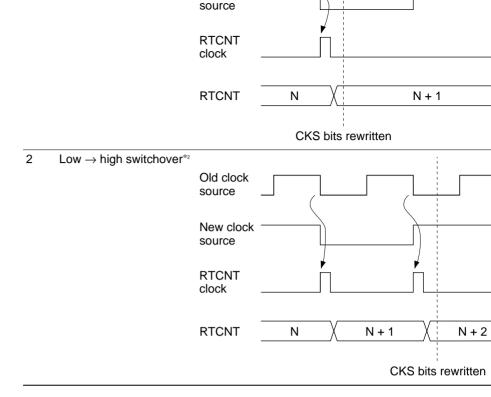

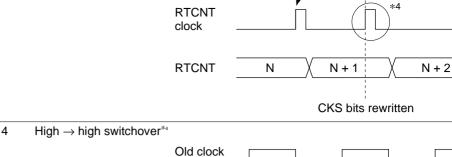

|      | 7.2.3   | Refresh Timer Counter (RTCNT)                   |

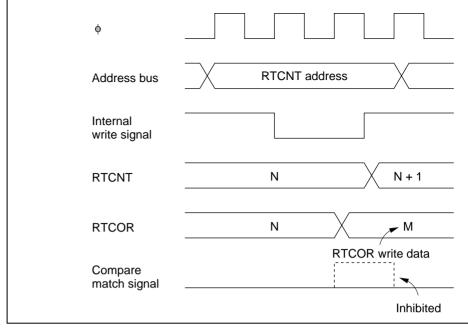

|      | 7.2.4   | Refresh Time Constant Register (RTCOR)          |

| 7.3  | Operat  | ion                                             |

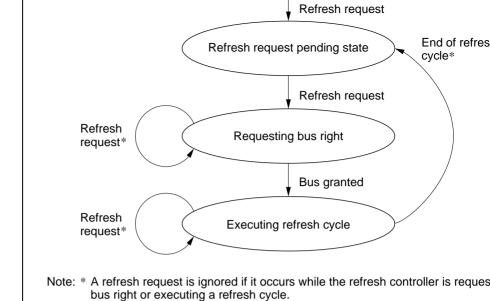

|      | 7.3.1   | Overview                                        |

|      | 7.3.2   | DRAM Refresh Control                            |

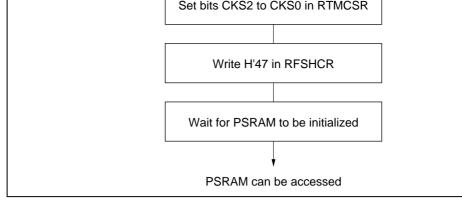

|      | 7.3.3   | Pseudo-Static RAM Refresh Control               |

|      | 7.3.4   | Interval Timer                                  |

| 7.4  | Interru | pt Source                                       |

| 7.5  |         | Notes                                           |

|      |         |                                                 |

6.3.5 6.3.6

8.1.1

8.1.2

Wait Modes.....

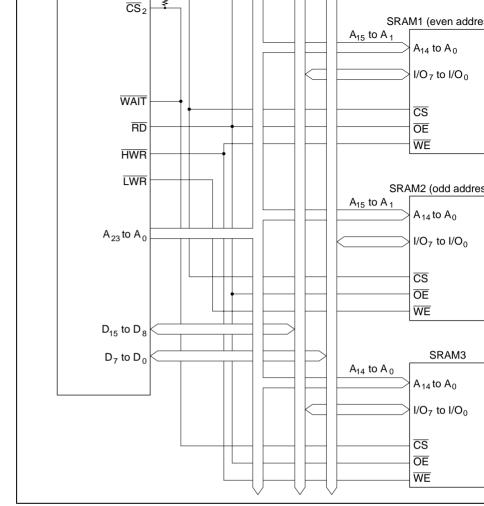

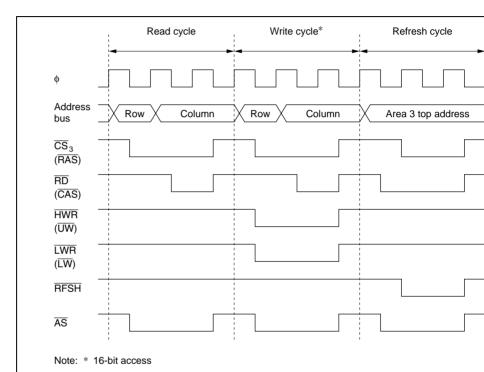

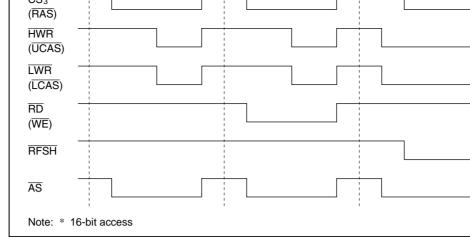

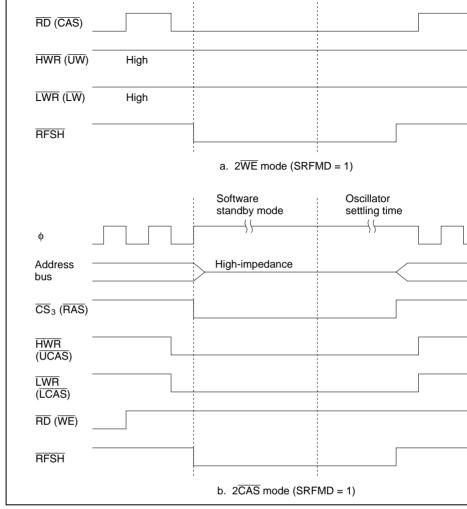

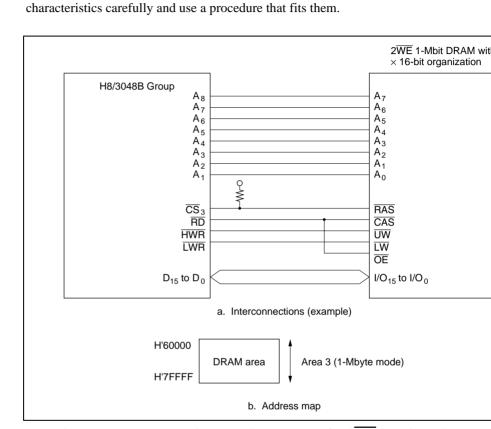

Interconnections with Memory (Example) .....

Rev. 3.00 Sep 27, 2006 page xvi of xxvi

RENESAS

Features.....

Block Diagram.....

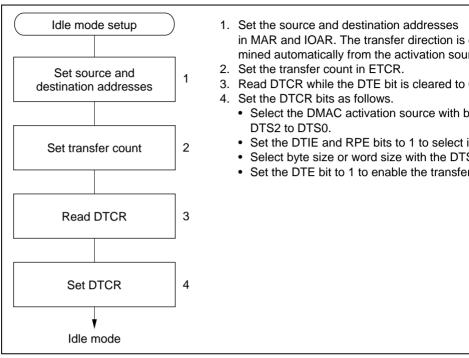

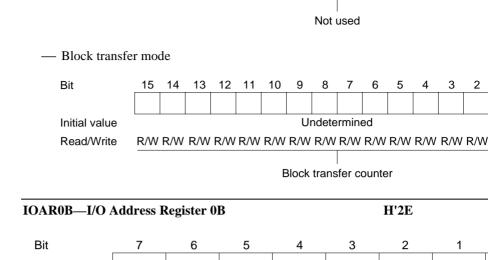

|      | 8.4.1   | Overview                                                  |

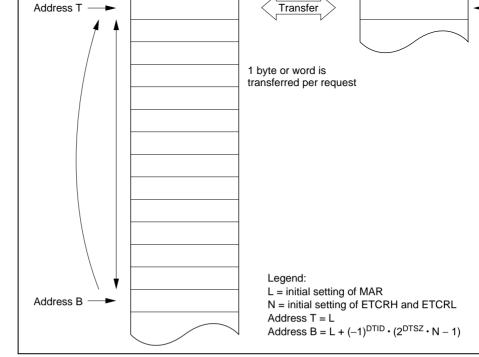

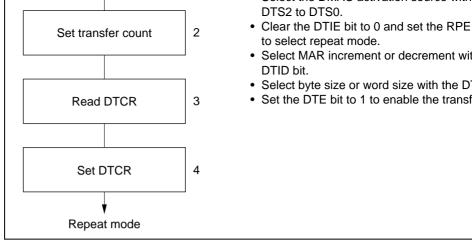

|------|---------|-----------------------------------------------------------|

|      | 8.4.2   | I/O Mode                                                  |

|      | 8.4.3   | Idle Mode                                                 |

|      | 8.4.4   | Repeat Mode                                               |

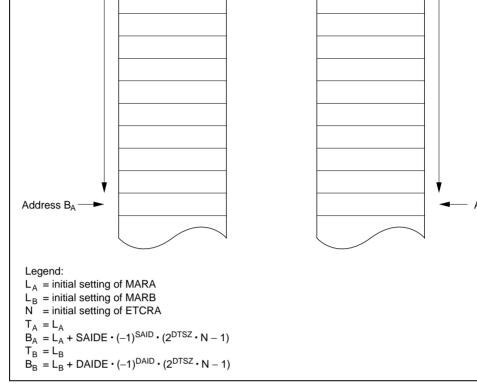

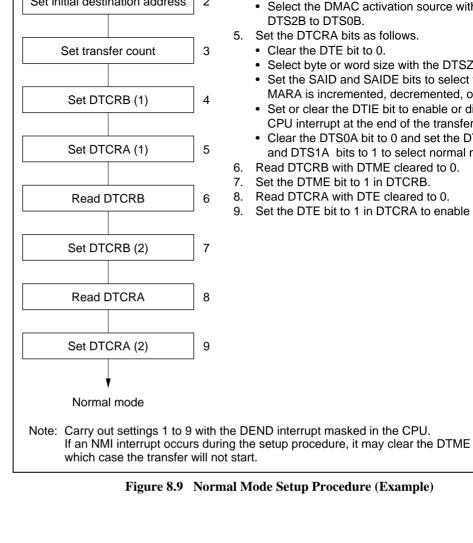

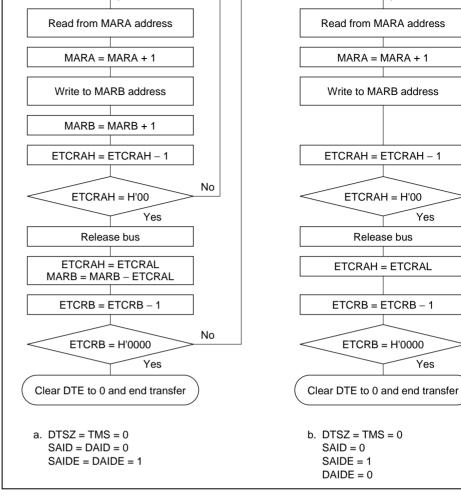

|      | 8.4.5   | Normal Mode                                               |

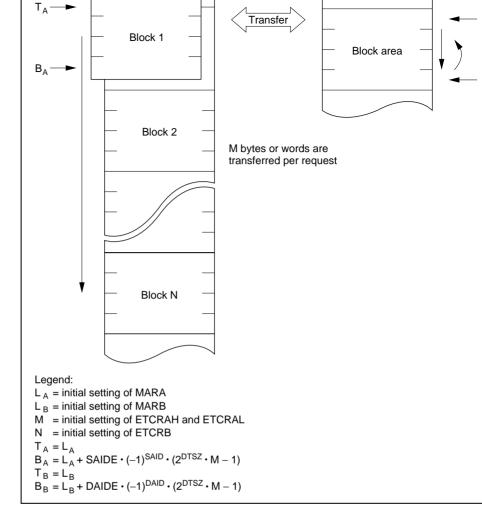

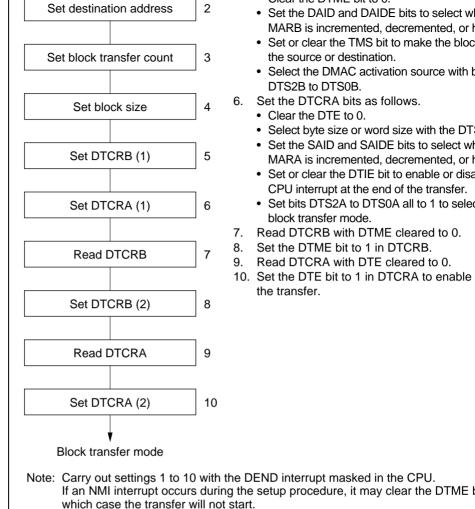

|      | 8.4.6   | Block Transfer Mode                                       |

|      | 8.4.7   | DMAC Activation                                           |

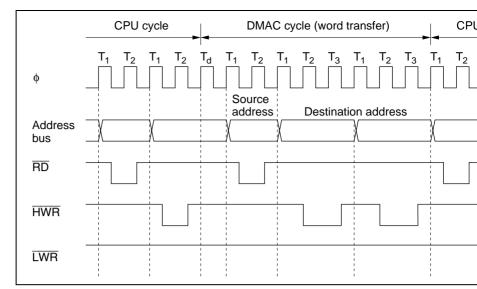

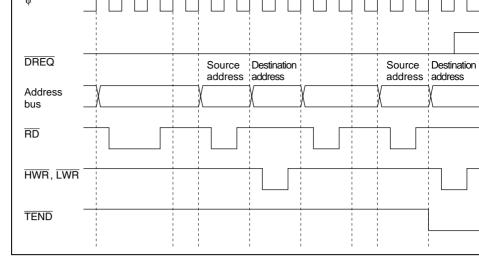

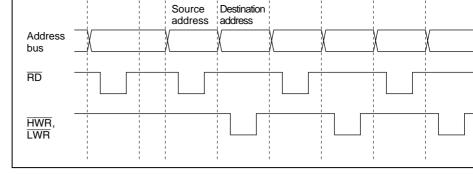

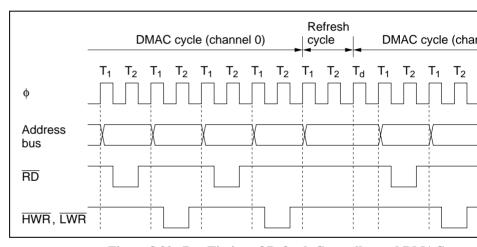

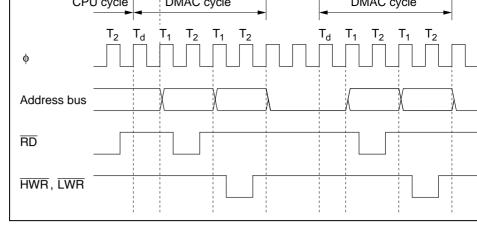

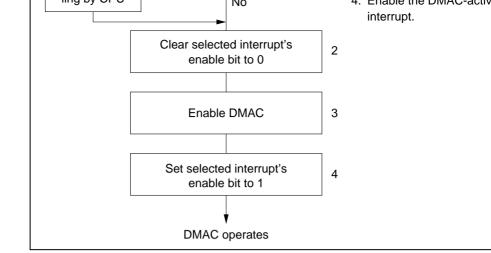

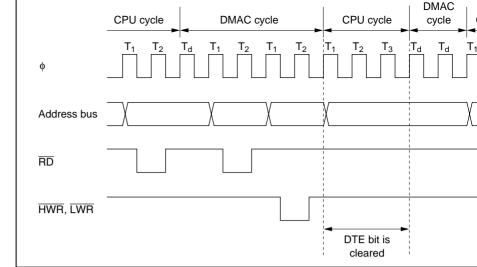

|      | 8.4.8   | DMAC Bus Cycle                                            |

|      | 8.4.9   | DMAC Multiple-Channel Operation                           |

|      | 8.4.10  | External Bus Requests, Refresh Controller, and DMAC       |

|      | 8.4.11  | NMI Interrupts and DMAC                                   |

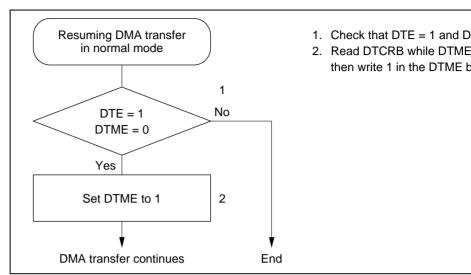

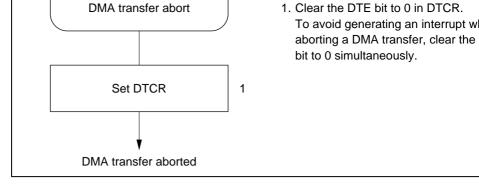

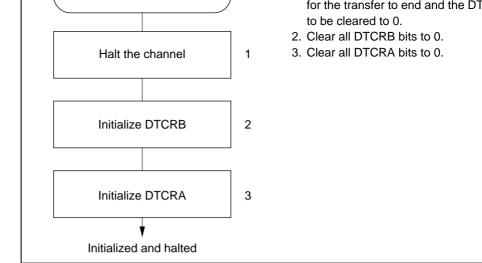

|      | 8.4.12  | Aborting a DMA Transfer                                   |

|      | 8.4.13  | Exiting Full Address Mode                                 |

|      | 8.4.14  | DMAC States in Reset State, Standby Modes, and Sleep Mode |

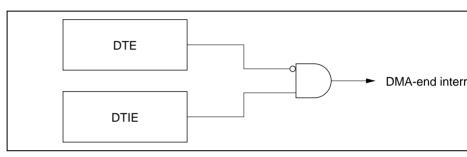

| 8.5  | Interru | pts                                                       |

| 8.6  | Usage   | Notes                                                     |

|      | 8.6.1   | Note on Word Data Transfer                                |

|      | 8.6.2   | DMAC Self-Access                                          |

|      | 8.6.3   | Longword Access to Memory Address Registers               |

|      | 8.6.4   | Note on Full Address Mode Setup                           |

|      | 8.6.5   | Note on Activating DMAC by Internal Interrupts            |

|      | 8.6.6   | NMI Interrupts and Block Transfer Mode                    |

|      | 8.6.7   | Memory and I/O Address Register Values                    |

|      | 8.6.8   | Bus Cycle when Transfer Is Aborted                        |

| Sect | ion 9   | I/O Ports                                                 |

| 9.1  |         | ew.                                                       |

| 7.1  | OVCIVI  | CW                                                        |

|      |         | Rev. 3.00 Sep 27, 2006 par                                |

|      |         | RENESAS                                                   |

8.3.1

8.3.2

8.3.3 8.3.4

8.4

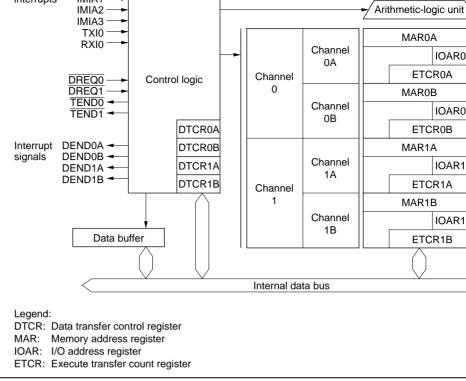

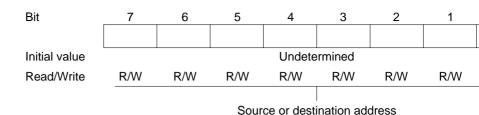

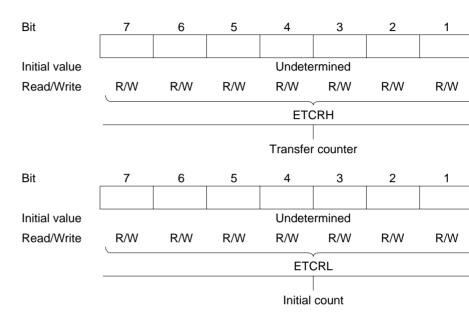

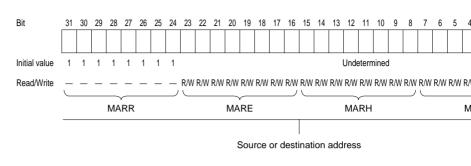

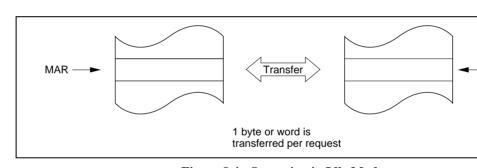

Memory Address Registers (MAR).....

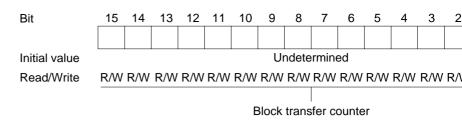

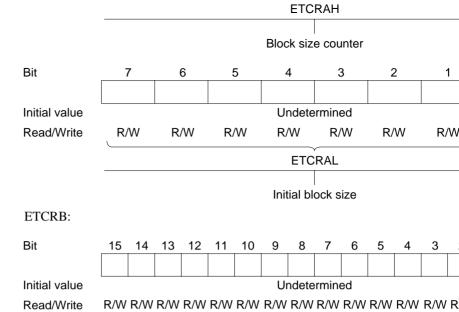

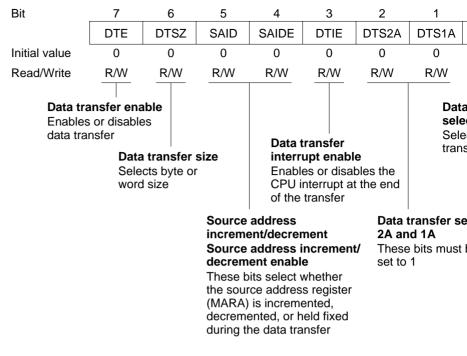

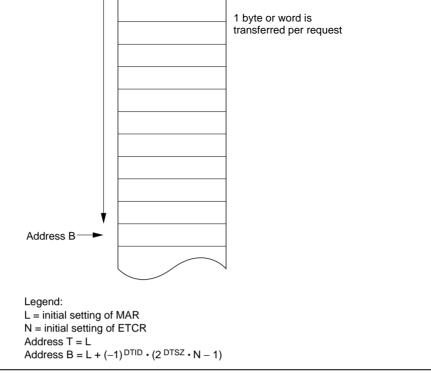

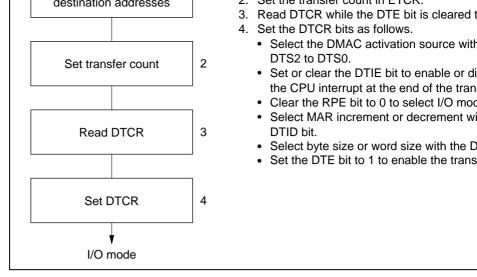

I/O Address Registers (IOAR)..... Execute Transfer Count Registers (ETCR).....

Data Transfer Control Registers (DTCR)

Operation .....

|        | 9.7.2   | Register Descriptions              |

|--------|---------|------------------------------------|

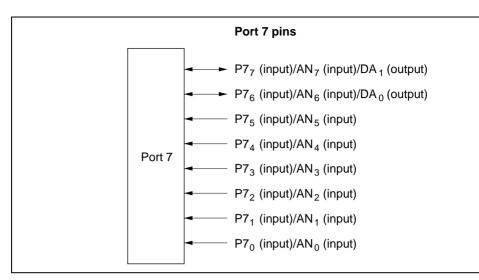

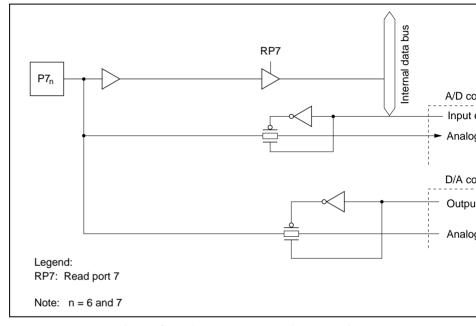

| 9.8    | Port 7. |                                    |

|        | 9.8.1   | Overview                           |

|        | 9.8.2   | Register Description.              |

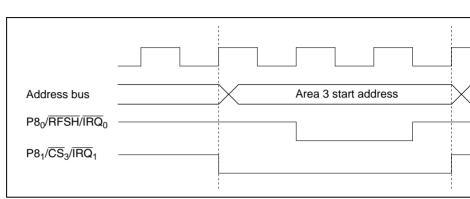

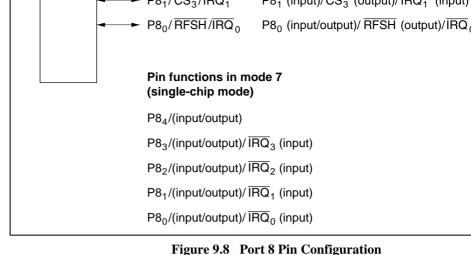

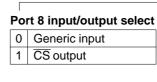

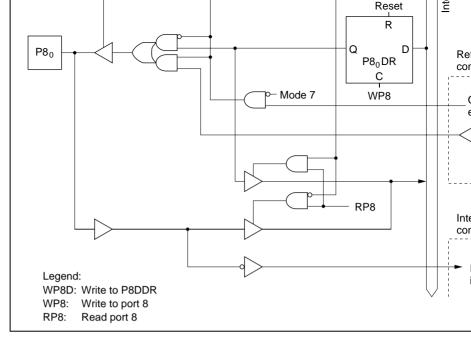

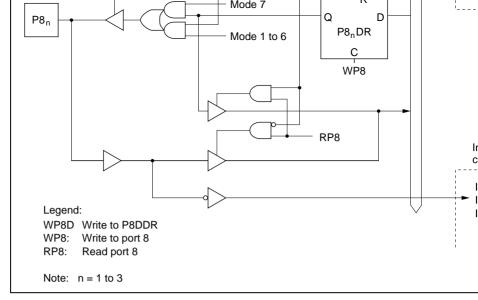

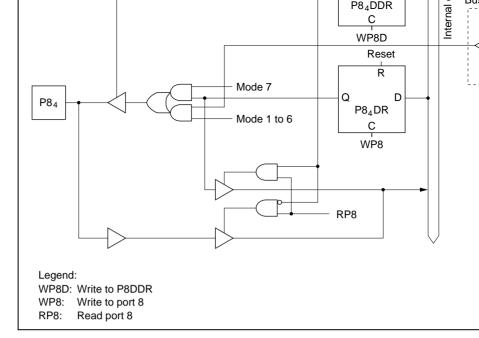

| 9.9    | Port 8. |                                    |

|        | 9.9.1   | Overview                           |

|        | 9.9.2   | Register Descriptions              |

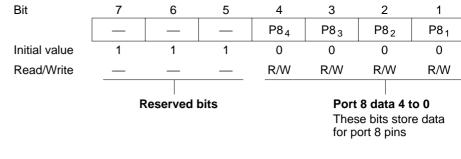

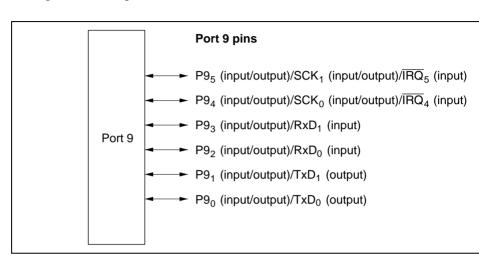

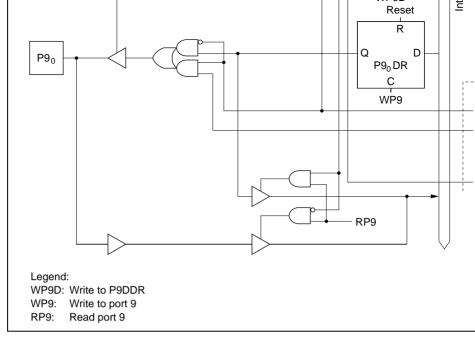

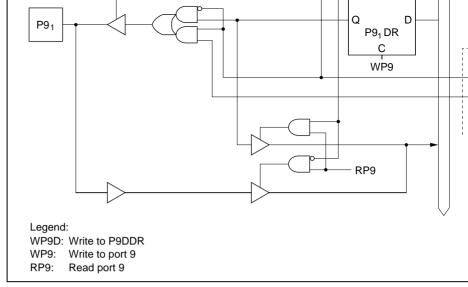

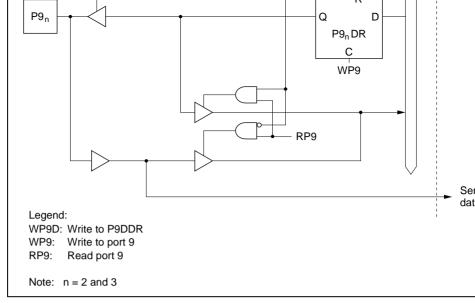

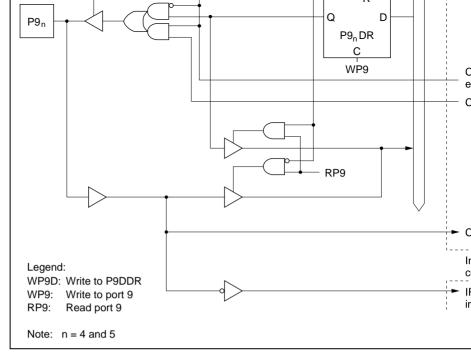

| 9.10   | Port 9  |                                    |

|        | 9.10.1  | Overview                           |

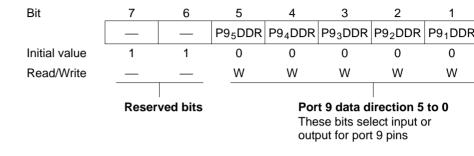

|        | 9.10.2  | Register Descriptions              |

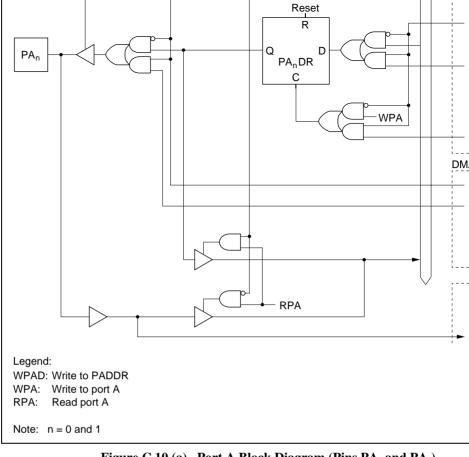

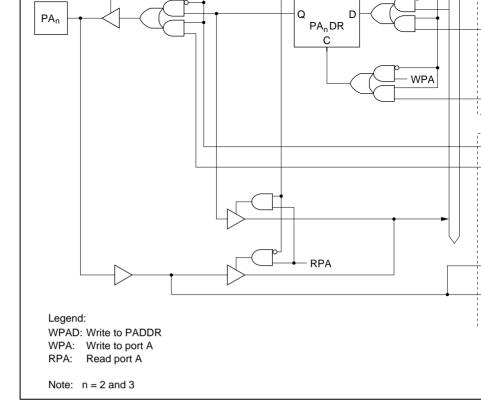

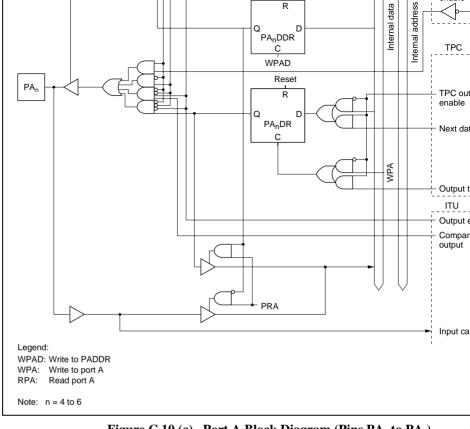

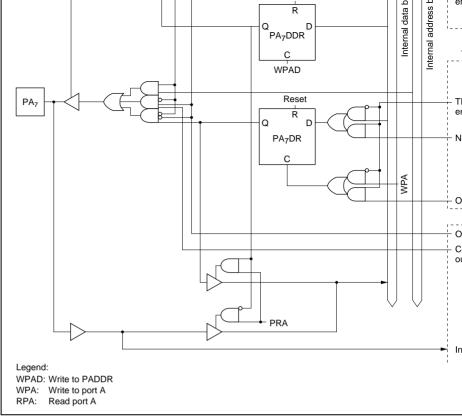

| 9.11   | Port A  |                                    |

|        | 9.11.1  | Overview                           |

|        | 9.11.2  | Register Descriptions              |

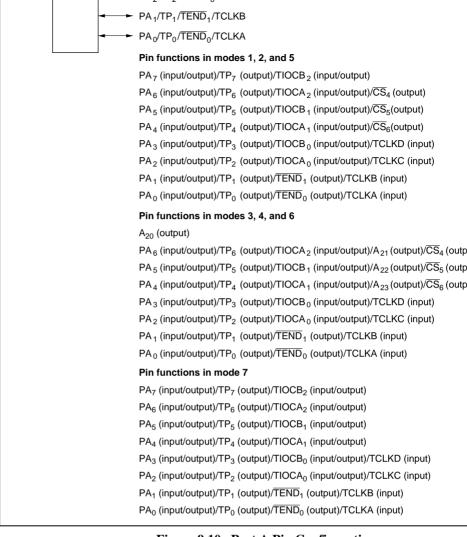

|        | 9.11.3  | Pin Functions                      |

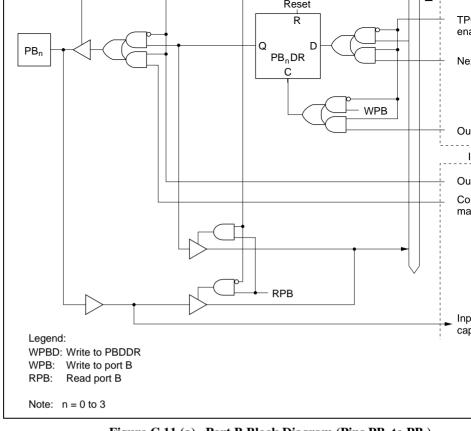

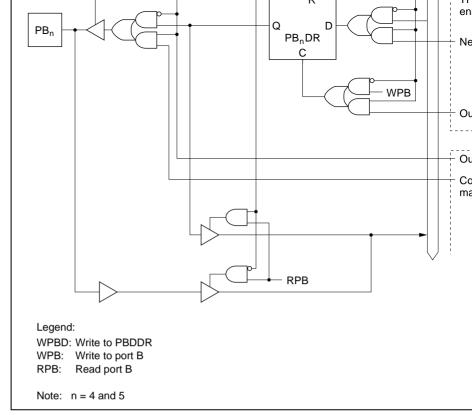

| 9.12   | Port B  |                                    |

|        | 9.12.1  | Overview                           |

|        | 9.12.2  | Register Descriptions              |

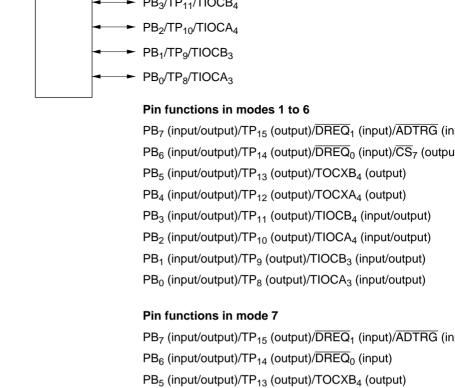

|        | 9.12.3  | Pin Functions                      |

|        |         |                                    |

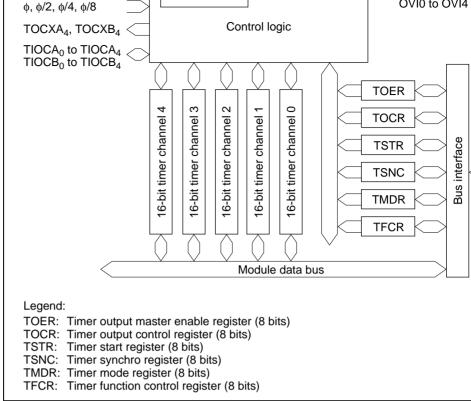

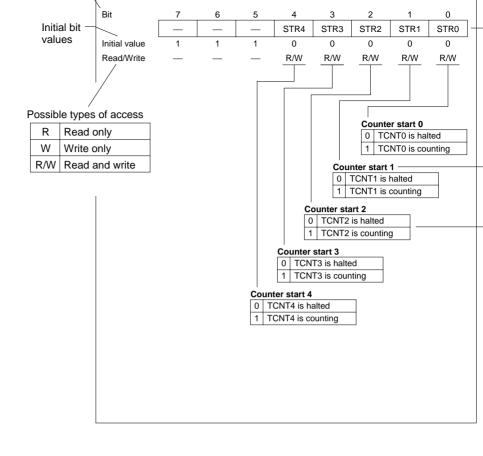

| Secti  | on 10   | 16-Bit Integrated Timer Unit (ITU) |

| 10.1   | Overvi  | ew                                 |

|        | 10.1.1  | Features                           |

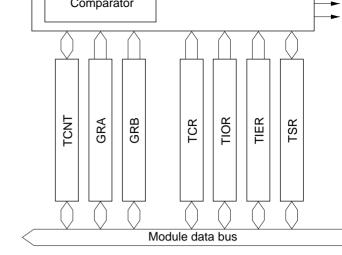

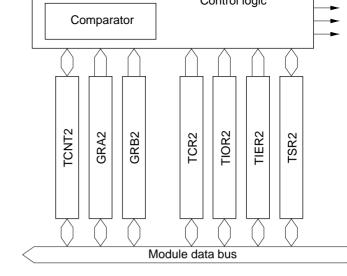

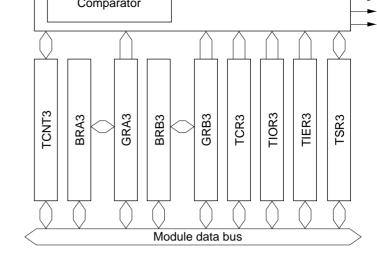

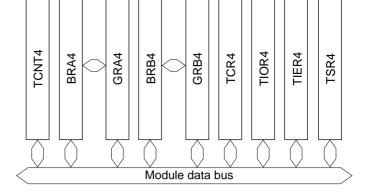

|        | 10.1.2  | Block Diagrams                     |

|        | 10.1.3  | Input/Output Pins                  |

|        | _       |                                    |

| Rev. 3 | 3.00 Se | p 27, 2006 page xviii of xxvi      |

|        |         | RENESAS                            |

|        |         |                                    |

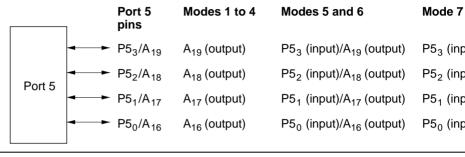

Port 4

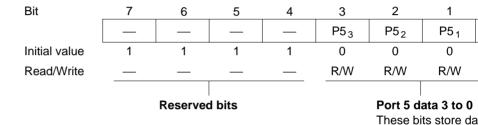

Port 5.....

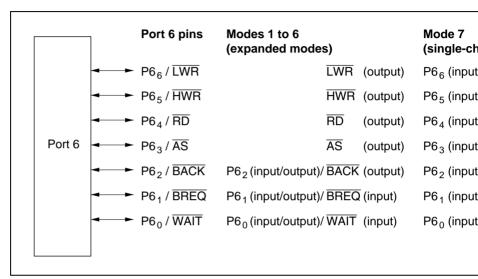

Port 6.....

Overview.....

Register Descriptions

Overview.....

9.5

9.6

9.7

9.5.1

9.5.2

9.6.1

9.6.2

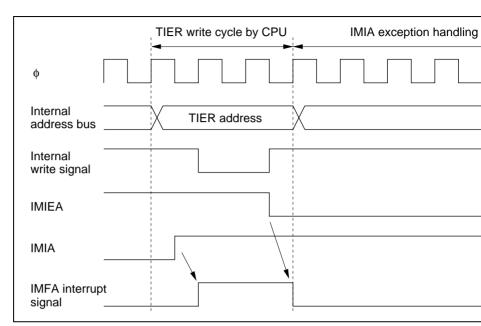

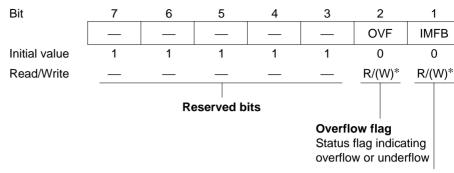

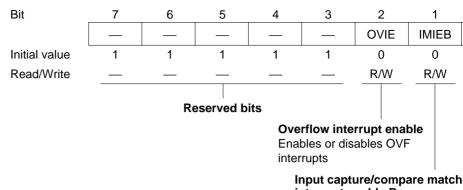

|       | 10.2.12   | Timer Status Register (TSR)                     |

|-------|-----------|-------------------------------------------------|

|       |           | Timer Interrupt Enable Register (TIER)          |

| 10.3  |           | terface                                         |

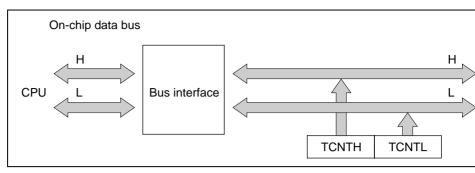

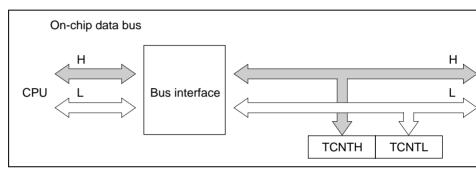

|       |           | 16-Bit Accessible Registers                     |

|       | 10.3.2    | 8-Bit Accessible Registers                      |

| 10.4  | Operation | on                                              |

|       | 10.4.1    | Overview                                        |

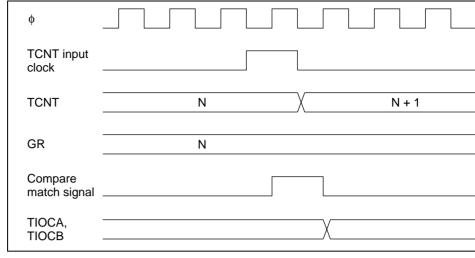

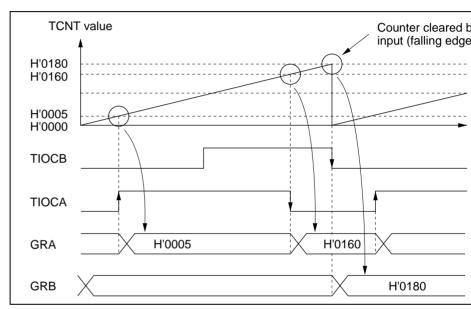

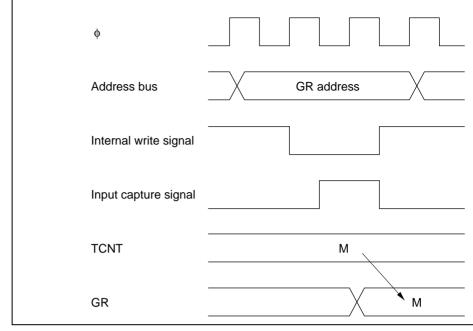

|       | 10.4.2    | Basic Functions                                 |

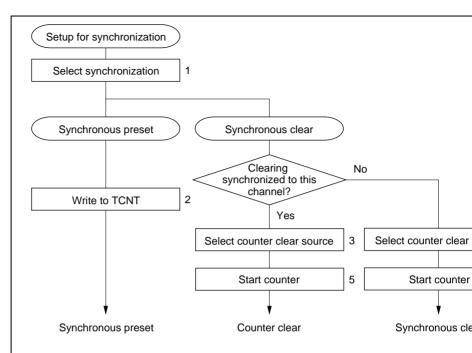

|       | 10.4.3    | Synchronization                                 |

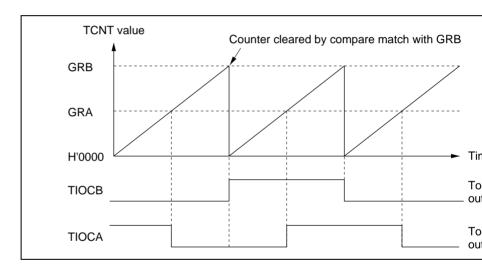

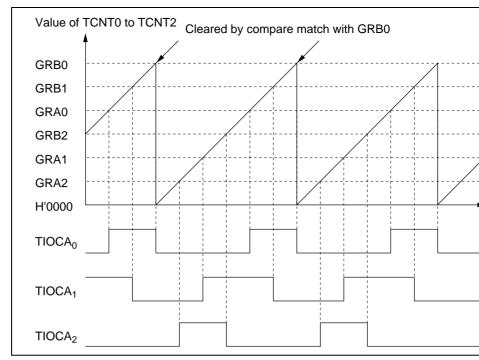

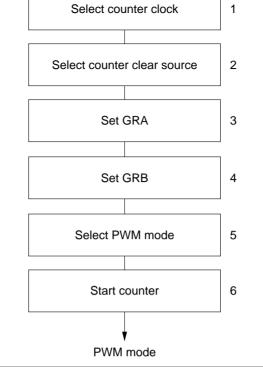

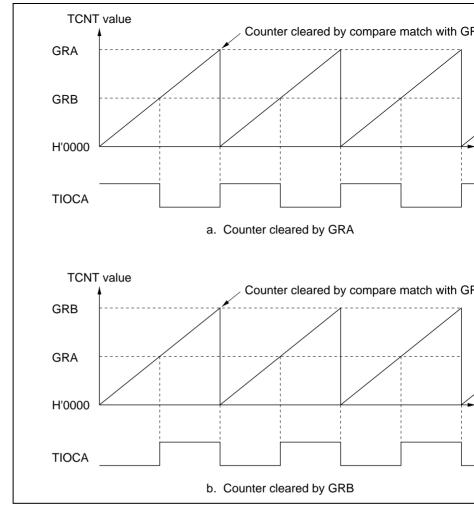

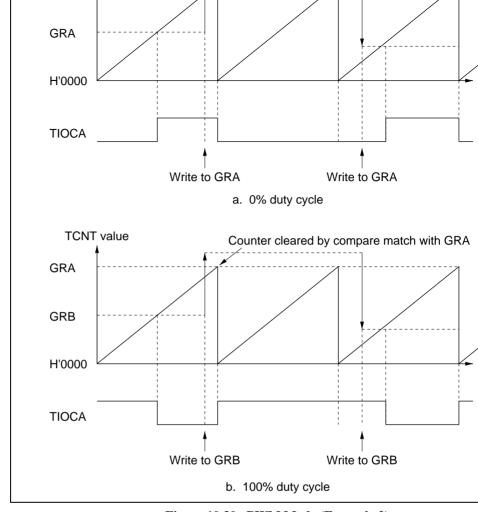

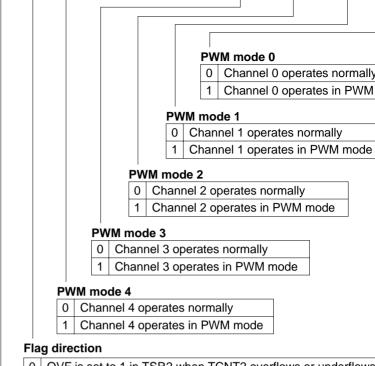

|       | 10.4.4    | PWM Mode                                        |

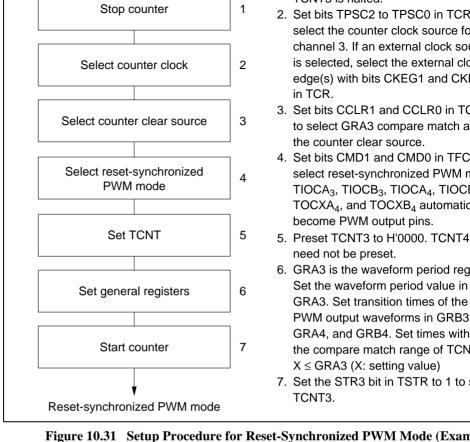

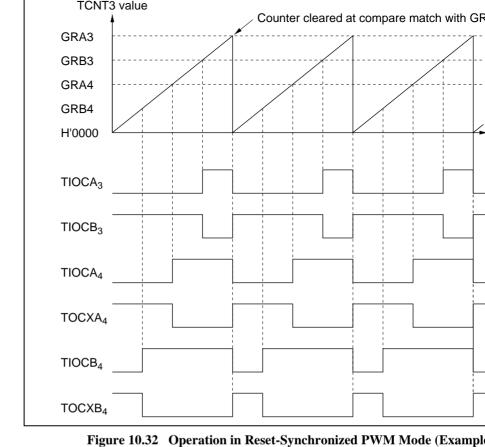

|       |           | Reset-Synchronized PWM Mode                     |

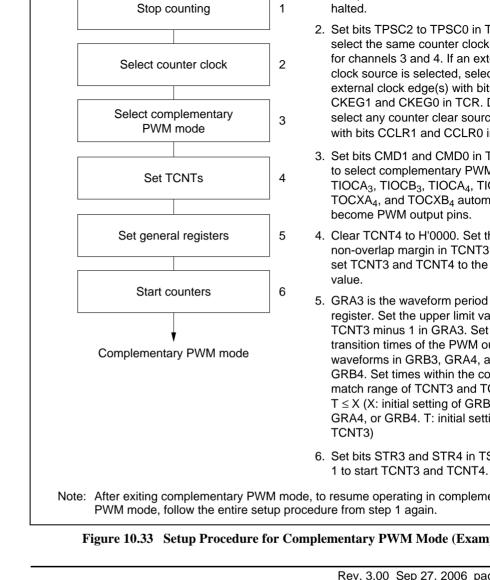

|       | 10.4.6    | Complementary PWM Mode                          |

|       |           | Phase Counting Mode                             |

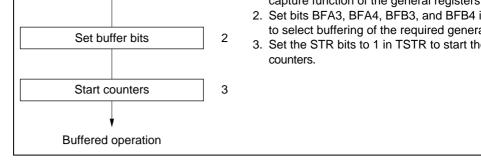

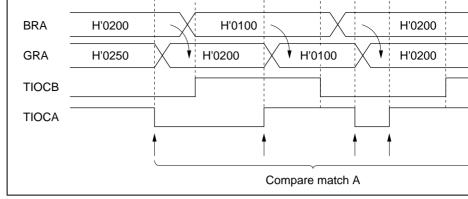

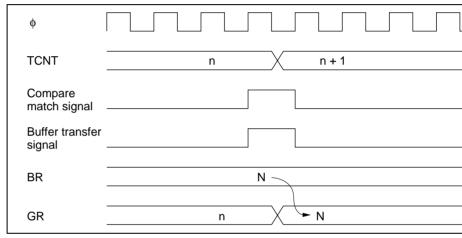

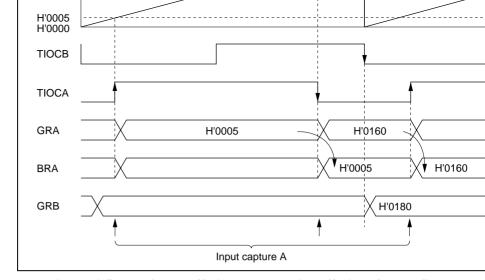

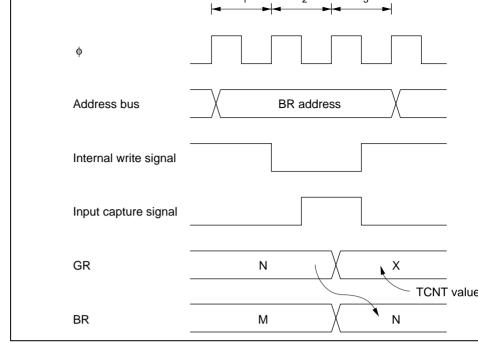

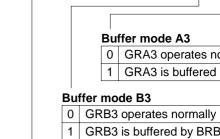

|       | 10.4.8    | Buffering                                       |

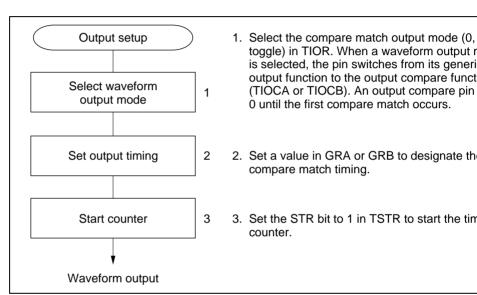

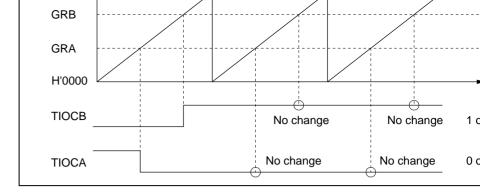

|       |           | ITU Output Timing                               |

| 10.5  | Interrup  | ts                                              |

|       |           | Setting of Status Flags                         |

|       |           | Timing of Clearing of Status Flags              |

|       |           | Interrupt Sources and DMA Controller Activation |

| 10.6  | Usage N   | Notes                                           |

|       |           |                                                 |

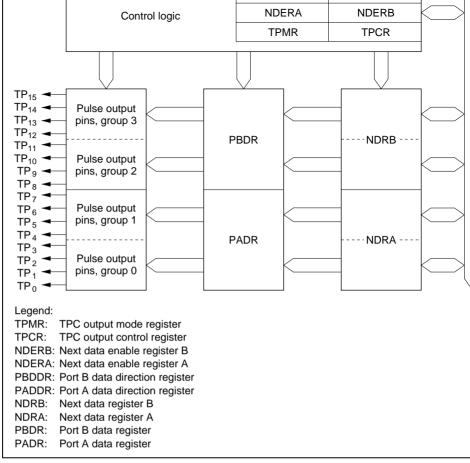

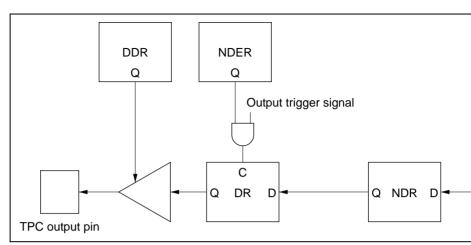

| Secti | ion 11    | Programmable Timing Pattern Controller          |

| 11.1  | Overvie   | w                                               |

|       | 11.1.1    | Features                                        |

|       | 11.1.2    | Block Diagram                                   |

|       | 11.1.3    | TPC Pins                                        |

|       | 11.1.4    | Registers                                       |

| 11.2  | Register  | r Descriptions                                  |

|       |           |                                                 |

|       |           | Rev. 3.00 Sep 27, 2006 pa                       |

|       |           | RENESAS                                         |

|       |           | - (2.1423.23                                    |

|       |           |                                                 |

|       |           |                                                 |

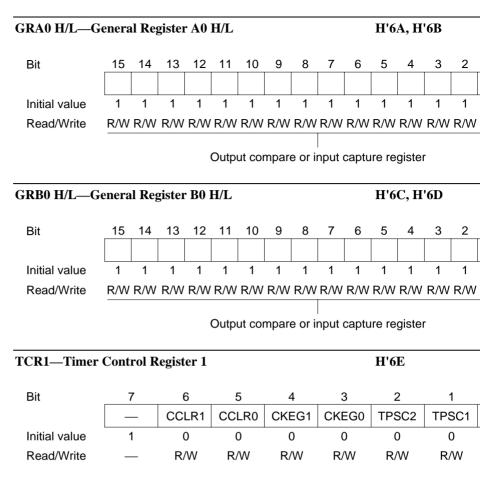

10.2.8 General Registers A, B (GRA, GRB)

10.2.9 Buffer Registers A, B (BRA, BRB)

10.2.10 Timer Control Registers (TCR)

10.2.11 Timer I/O Control Register (TIOR)

| 11.4  | Usage   | Notes                                                |

|-------|---------|------------------------------------------------------|

|       |         | Operation of TPC Output Pins                         |

|       |         | Note on Non-Overlapping Output                       |

|       |         |                                                      |

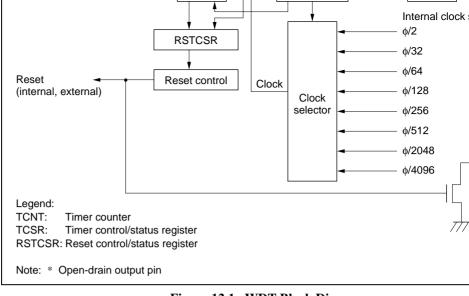

| Secti | ion 12  | Watchdog Timer                                       |

| 12.1  | Overvi  | ew                                                   |

|       | 12.1.1  | Features                                             |

|       | 12.1.2  | Block Diagram                                        |

|       |         | Pin Configuration                                    |

|       |         | Register Configuration                               |

| 12.2  |         | er Descriptions                                      |

|       |         | Timer Counter (TCNT)                                 |

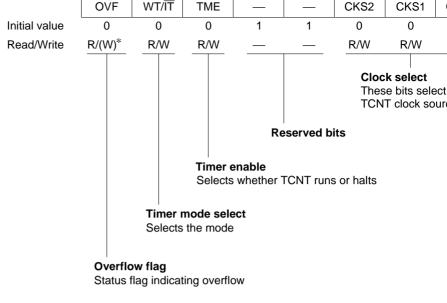

|       |         | Timer Control/Status Register (TCSR)                 |

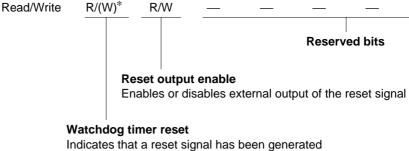

|       |         | Reset Control/Status Register (RSTCSR)               |

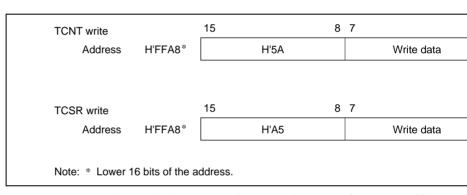

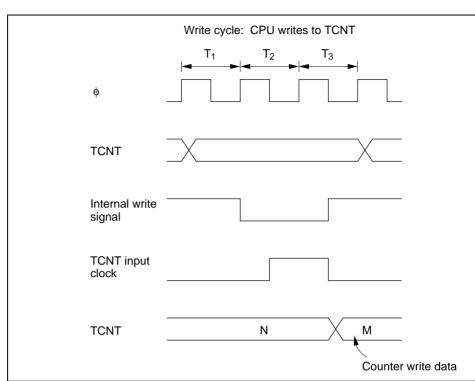

|       |         | Notes on Register Rewriting                          |

| 12.3  |         | ion                                                  |

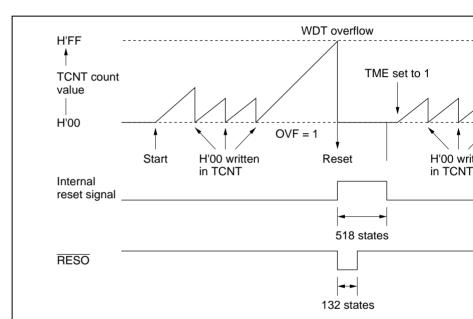

|       | 12.3.1  | Watchdog Timer Operation                             |

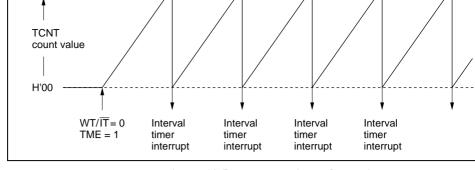

|       |         | Interval Timer Operation                             |

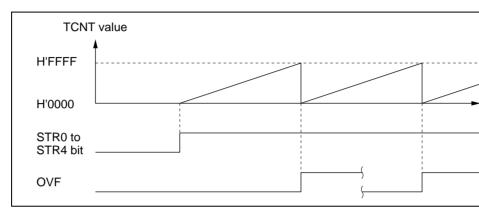

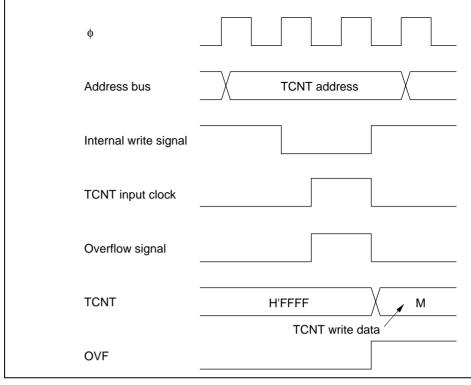

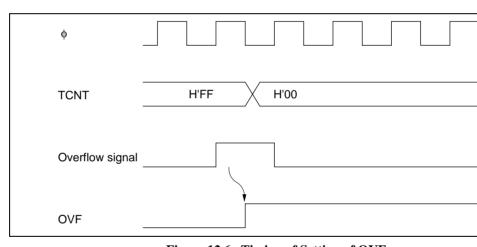

|       |         | Timing of Setting of Overflow Flag (OVF)             |

|       |         | Timing of Setting of Watchdog Timer Reset Bit (WRST) |

| 12.4  | Interru | pts                                                  |

| 12.5  |         | Notes                                                |

| 12.6  | _       |                                                      |

|       |         |                                                      |

|       |         |                                                      |

|       |         |                                                      |

| Rev.  | 3.00 Se | p 27, 2006 page xx of xxvi                           |

|       |         |                                                      |

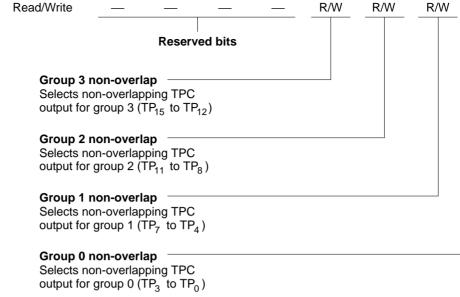

11.2.10 TPC Output Mode Register (TPMR)

Operation

11.3.1 Overview

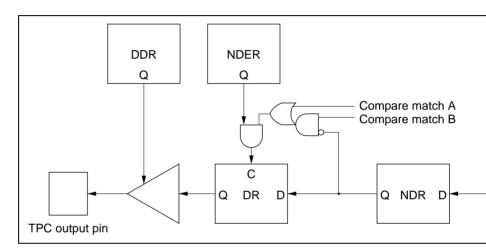

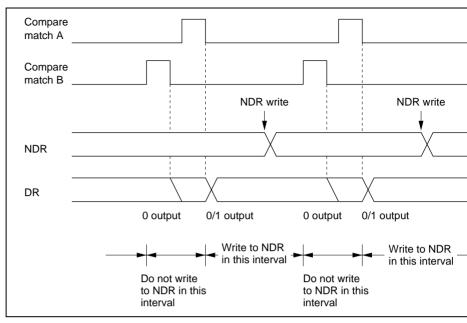

11.3.2 Output Timing

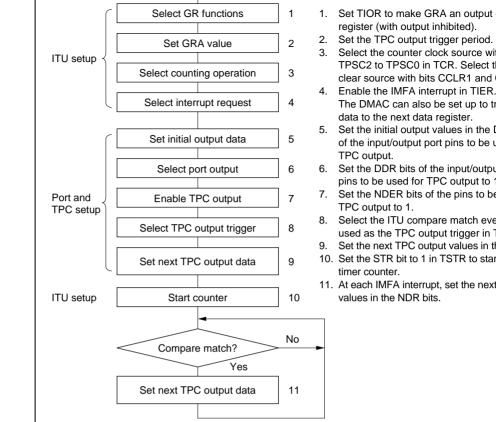

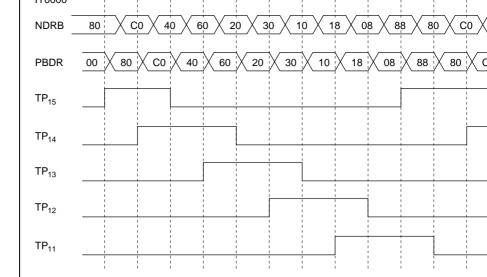

11.3.3 Normal TPC Output

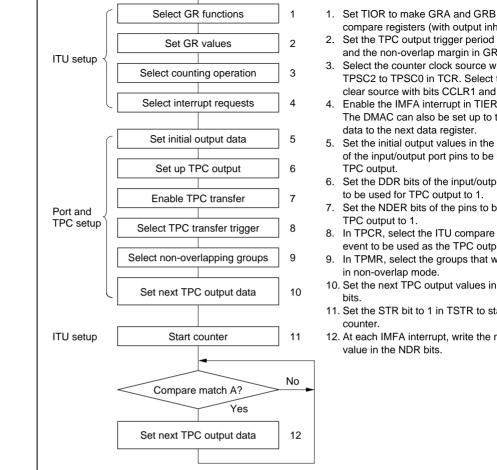

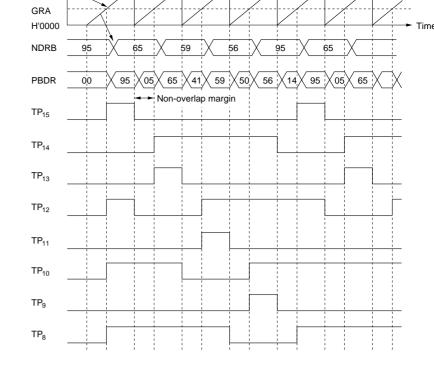

11.3.4 Non-Overlapping TPC Output

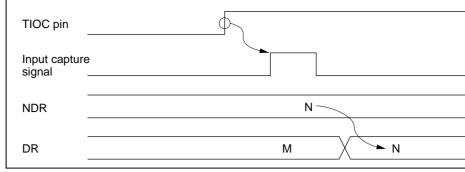

11.3.5 TPC Output Triggering by Input Capture

RENESAS

|       | 13.2.8  | Bit Rate Register (BRR)         |                           |

|-------|---------|---------------------------------|---------------------------|

| 13.3  |         | on                              |                           |

|       | _       | Overview                        |                           |

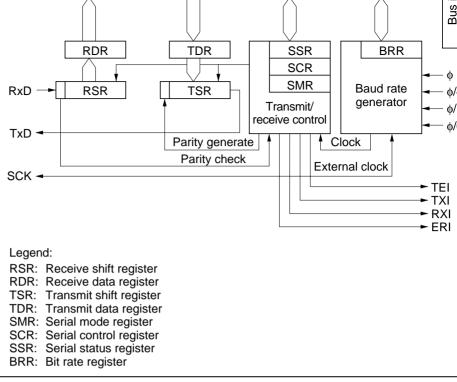

|       |         | Operation in Asynchronous Mode  |                           |

|       | 13.3.3  | •                               |                           |

|       | 13.3.4  | Synchronous Operation           |                           |

| 13.4  |         | errupts                         |                           |

| 13.5  |         | Notes                           |                           |

|       | Č       |                                 |                           |

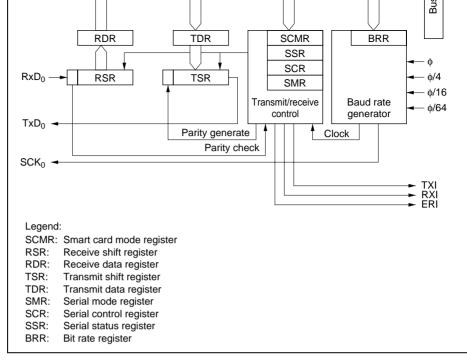

| Secti | ion 14  | Smart Card Interface            |                           |

| 14.1  |         | ew                              |                           |

|       | 14.1.1  | Features                        |                           |

|       | 14.1.2  | Block Diagram                   |                           |

|       | 14.1.3  | Input/Output Pins               |                           |

|       | 14.1.4  | Register Configuration          |                           |

| 14.2  | Registe | r Descriptions                  |                           |

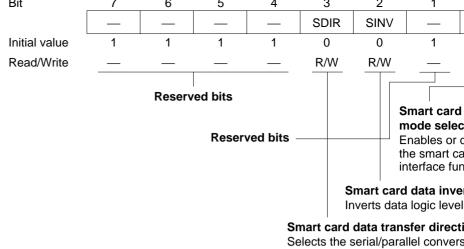

|       | 14.2.1  | Smart Card Mode Register (SCMR) |                           |

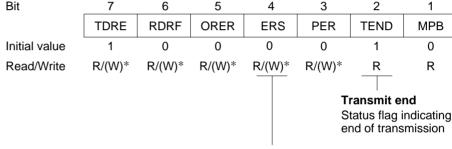

|       | 14.2.2  | Serial Status Register (SSR)    |                           |

|       | 14.2.3  | Serial Mode Register (SMR)      |                           |

|       | 14.2.4  | Serial Control Register (SCR)   |                           |

| 14.3  | Operati | on                              |                           |

|       | 14.3.1  | Overview                        |                           |

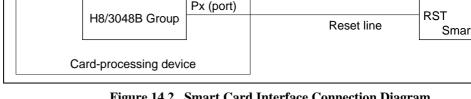

|       | 14.3.2  | Pin Connections                 |                           |

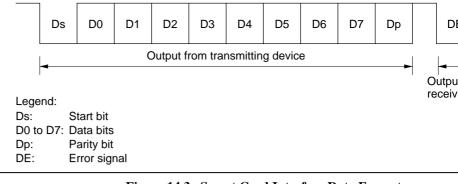

|       | 14.3.3  | Data Format                     |                           |

|       | 14.3.4  | Register Settings               |                           |

|       | 14.3.5  | Clock                           |                           |

|       | 14.3.6  | Transmitting and Receiving Data |                           |

|       |         |                                 |                           |

|       |         |                                 | Rev. 3.00 Sep 27, 2006 pa |

|       |         | RENESA                          | 5                         |

|       |         |                                 |                           |

13.2.3 Transmit Shift Register (TSR)

13.2.4 Transmit Data Register (TDR)

13.2.5 Serial Mode Register (SMR)

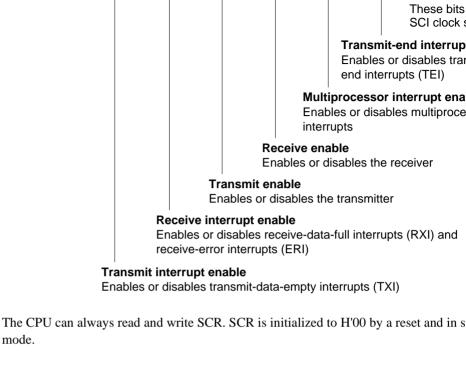

13.2.6 Serial Control Register (SCR)

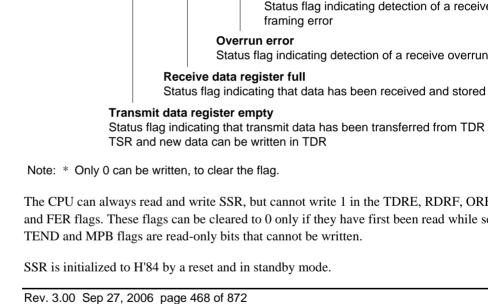

13.2.7 Serial Status Register (SSR)

| 15.5 | Interrupts                                       |

|------|--------------------------------------------------|

| 15.6 | Usage Notes                                      |

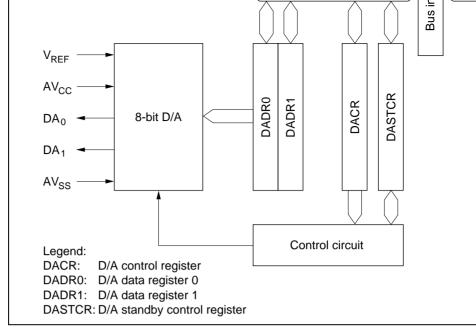

| Sec  | tion 16 D/A Converter                            |

| 16.1 | Overview                                         |

|      | 16.1.1 Features                                  |

|      | 16.1.2 Block Diagram                             |

|      | 16.1.3 Input/Output Pins                         |

|      | 16.1.4 Register Configuration                    |

| 16.2 |                                                  |

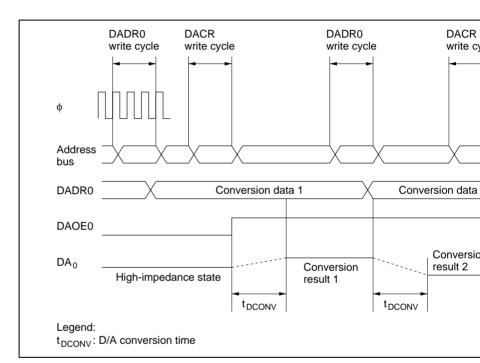

|      | 16.2.1 D/A Data Registers 0 and 1 (DADR0, DADR1) |

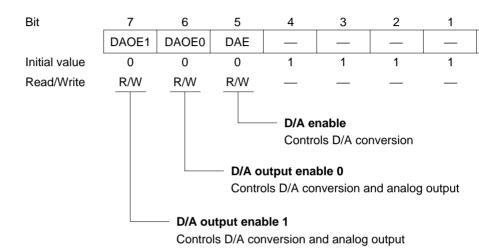

|      | 16.2.2 D/A Control Register (DACR)               |

|      | 16.2.3 D/A Standby Control Register (DASTCR)     |

| 16.3 |                                                  |

|      | D/A Output Control                               |

|      | 1                                                |

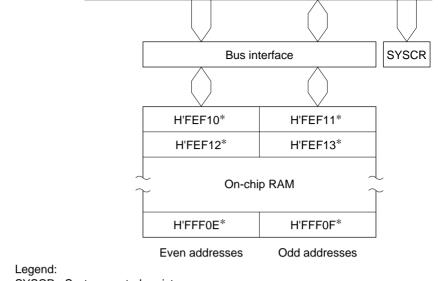

| Sec  | tion 17 RAM                                      |

| 17.1 |                                                  |

|      | 17.1.1 Block Diagram                             |

|      | 17.1.2 Register Configuration                    |

| 17.2 |                                                  |

| 17.3 | •                                                |

|      |                                                  |

|      |                                                  |

| Rev  | . 3.00 Sep 27, 2006 page xxii of xxvi            |

|      | 2chice ve                                        |

|      | RENESAS                                          |

|      |                                                  |

|      |                                                  |

15.3

15.4

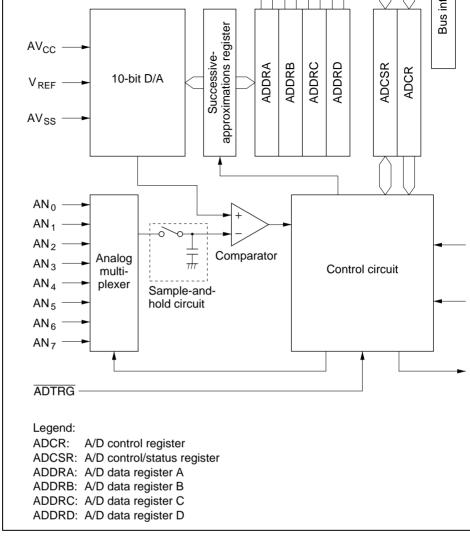

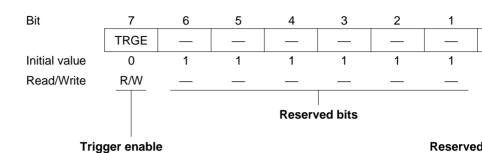

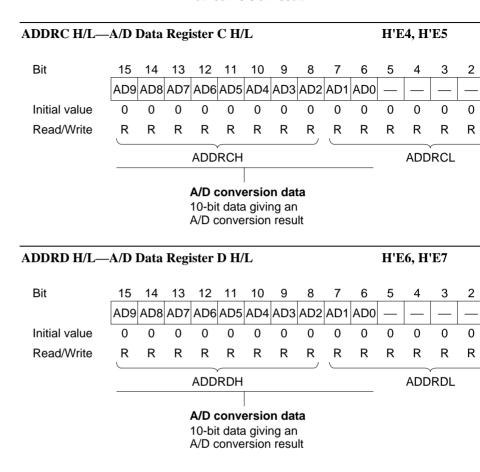

15.2.1 A/D Data Registers A to D (ADDRA to ADDRD)..... 15.2.2 A/D Control/Status Register (ADCSR) 15.2.3 A/D Control Register (ADCR) .....

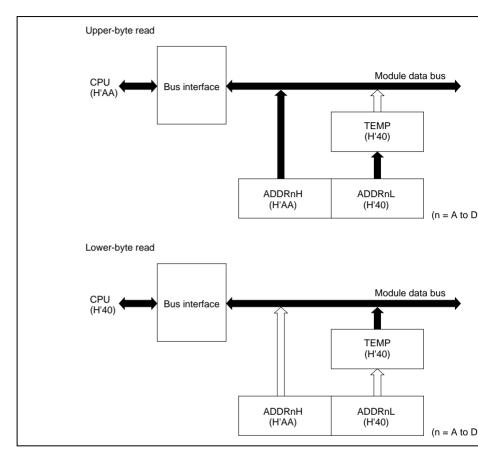

CPU Interface.....

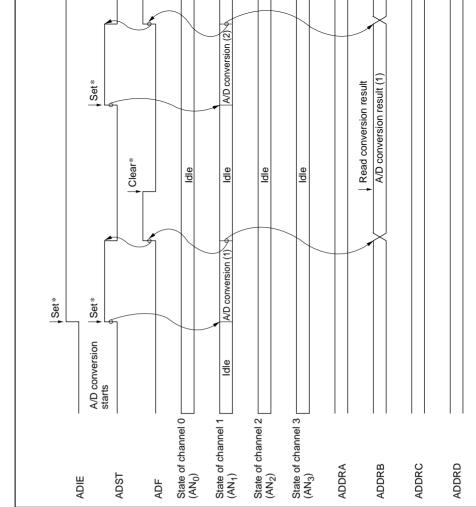

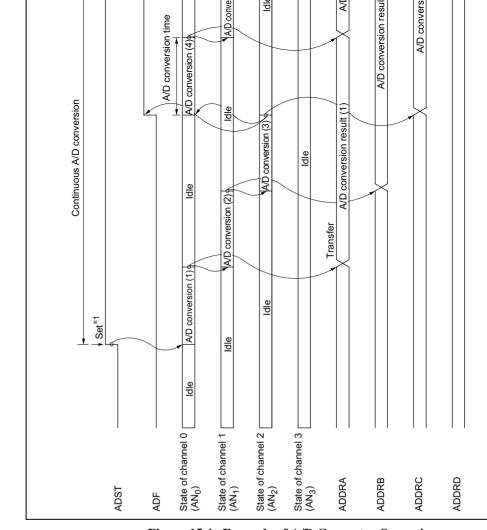

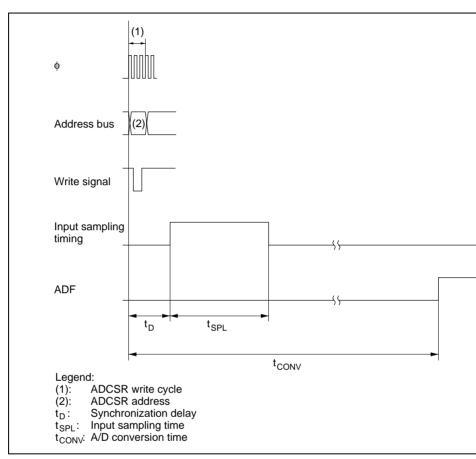

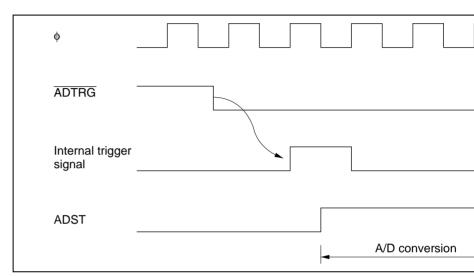

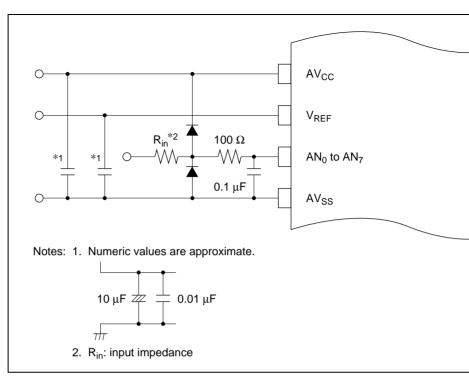

Operation ..... 15.4.1 Single Mode (SCAN = 0) ...... 15.4.2 Scan Mode (SCAN = 1)..... 15.4.3 Input Sampling and A/D Conversion Time ...... 15.4.4 External Trigger Input Timing.....

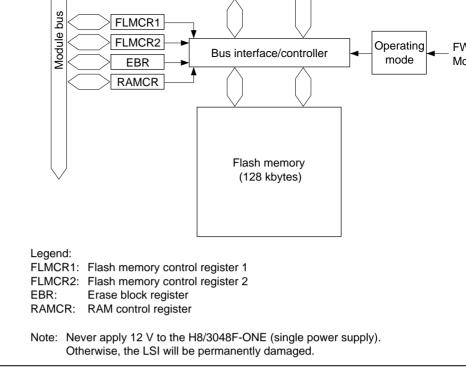

| 18.5  | Flash N  | Memory Register Descriptions              |

|-------|----------|-------------------------------------------|

|       | 18.5.1   | Flash Memory Control Register 1 (FLMCR1)  |

|       | 18.5.2   | Flash Memory Control Register 2 (FLMCR2)  |

|       | 18.5.3   | Erase Block Register (EBR)                |

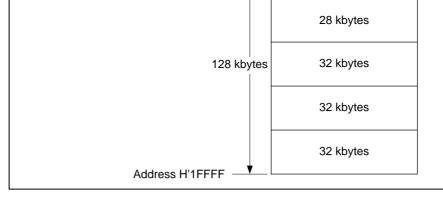

|       |          | RAM Control Register (RAMCR)              |

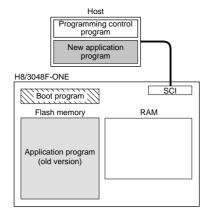

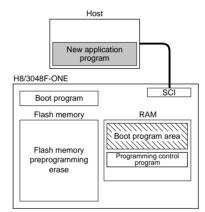

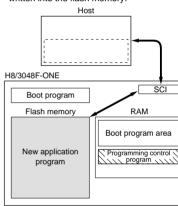

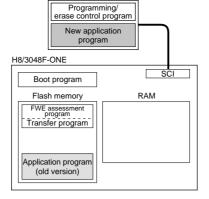

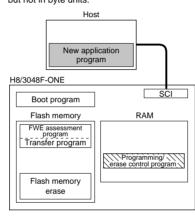

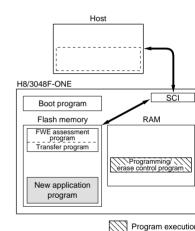

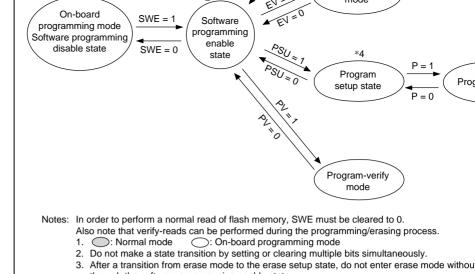

| 18.6  | Flash N  | Memory On-Board Programming Modes         |

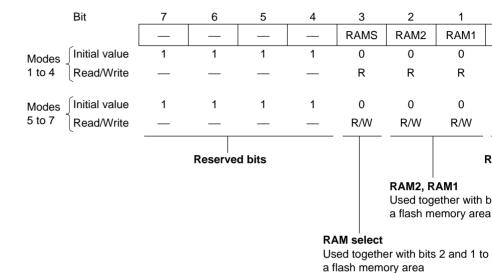

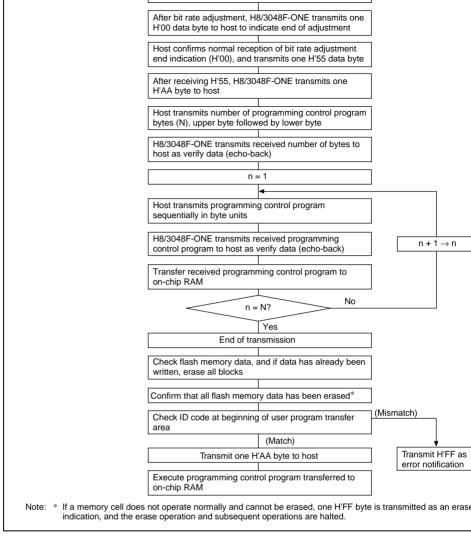

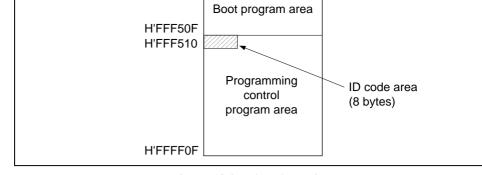

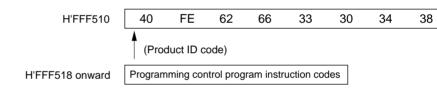

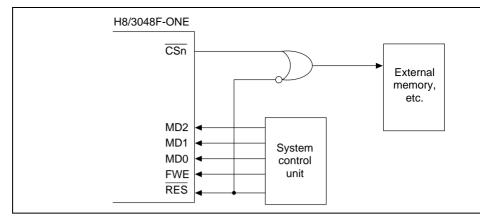

|       | 18.6.1   | Boot Mode                                 |

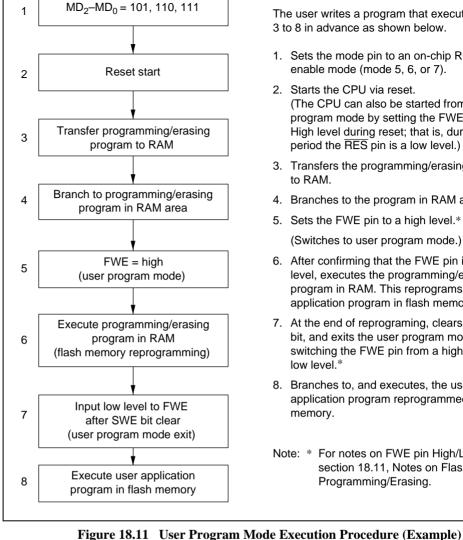

|       | 18.6.2   | User Program Mode                         |

| 18.7  |          | mming/Erasing Flash Memory                |

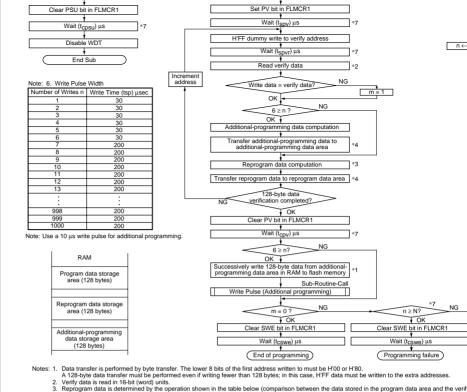

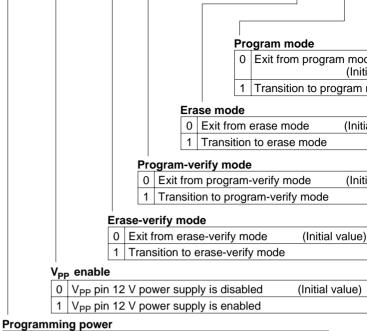

|       | 18.7.1   | Program Mode                              |

|       |          | Program-Verify Mode                       |

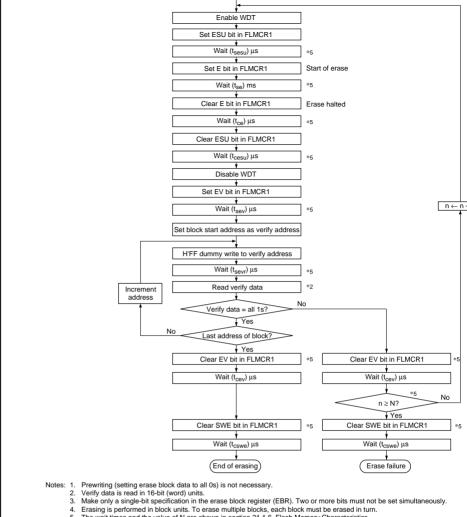

|       | 18.7.3   | Erase Mode                                |

|       | 18.7.4   | Erase-Verify Mode                         |

| 18.8  | Flash N  | Memory Protection                         |

|       |          | Hardware Protection                       |

|       | 18.8.2   | Software Protection                       |

|       | 18.8.3   | Error Protection                          |

|       | 18.8.4   | NMI Input Disable Conditions              |

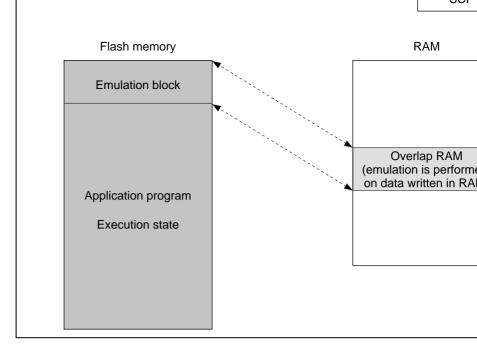

| 18.9  | Flash N  | Memory Emulation in RAM                   |

| 18.10 | Flash N  | Memory PROM Mode                          |

|       |          | Socket Adapters and Memory Map            |

|       | 18.10.2  | 2 Notes on Use of PROM Mode               |

| 18.11 | Notes of | on Flash Memory Programming/Erasing       |

| 18.12 | Mask I   | ROM (H8/3048B Mask ROM Version) Overviews |

|       | 18.12.1  | Block Diagram                             |

| 18.13 | Notes o  | on Ordering Mask ROM Version Chips        |

|       |          |                                           |

|       |          |                                           |

|       |          | Rev. 3.00 Sep 27, 2006 pa                 |

|       |          | RENESAS                                   |

|       |          |                                           |

18.3 18.4

Flash Memory Register Configuration.....

| 20.2   | Registe              | r Configuration                                               |

|--------|----------------------|---------------------------------------------------------------|

|        | 20.2.1               | System Control Register (SYSCR)                               |

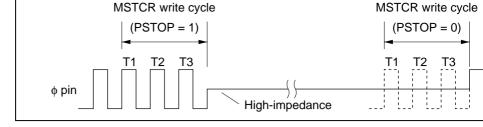

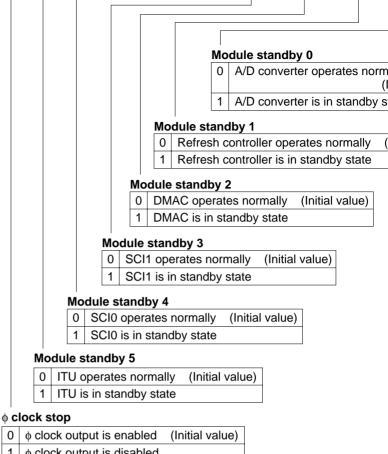

|        | 20.2.2               | Module Standby Control Register (MSTCR)                       |

| 20.3   | Sleep N              | Mode                                                          |

|        | 20.3.1               | Transition to Sleep Mode                                      |

|        | 20.3.2               | Exit from Sleep Mode                                          |

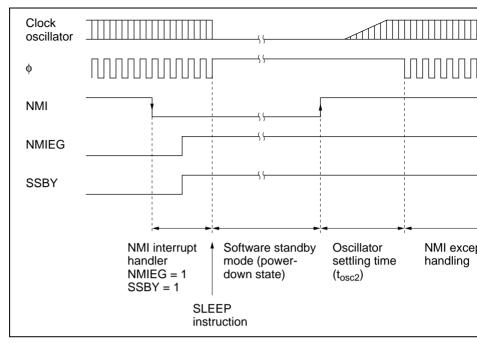

| 20.4   | Softwa               | re Standby Mode                                               |

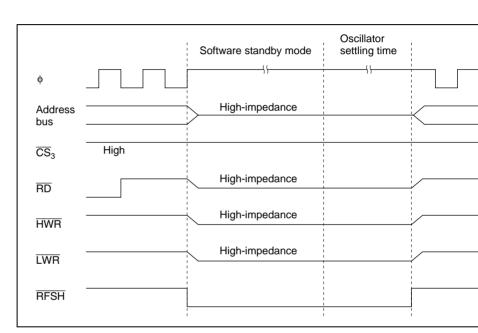

|        | 20.4.1               | Transition to Software Standby Mode                           |

|        | 20.4.2               | Exit from Software Standby Mode                               |

|        | 20.4.3               | Selection of Waiting Time for Exit from Software Standby Mode |

|        | 20.4.4               | Sample Application of Software Standby Mode                   |

|        | 20.4.5               | Note                                                          |

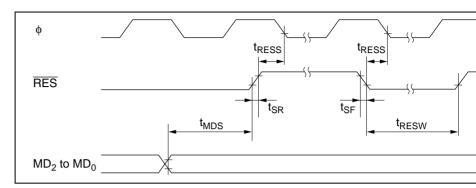

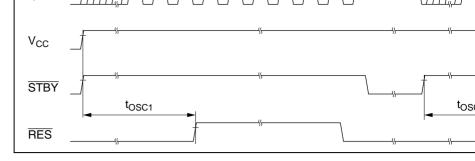

| 20.5   | Hardwa               | are Standby Mode                                              |

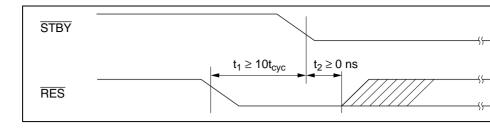

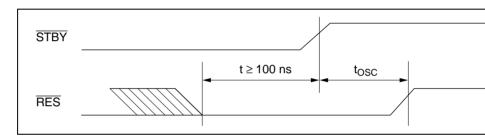

|        | 20.5.1               | Transition to Hardware Standby Mode                           |

|        | 20.5.2               | Exit from Hardware Standby Mode                               |

|        | 20.5.3               | Timing for Hardware Standby Mode                              |

| 20.6   | Module               | e Standby Function                                            |

|        | 20.6.1               | Module Standby Timing                                         |

|        | 20.6.2               | Read/Write in Module Standby                                  |

|        | 20.6.3               | Usage Notes                                                   |

| 20.7   | System               | Clock Output Disabling Function                               |

|        |                      |                                                               |

|        |                      |                                                               |

|        | _                    |                                                               |

| Rev. 3 | 3.00 Se <sub>l</sub> | p 27, 2006 page xxiv of xxvi                                  |

|        |                      | RENESAS                                                       |

|        |                      |                                                               |

|        |                      |                                                               |

|        |                      |                                                               |

19.3

19.5

Duty Adjustment Circuit.....

Prescalers .....

| 2. | 1.3 Operational Timing                                               |

|----|----------------------------------------------------------------------|

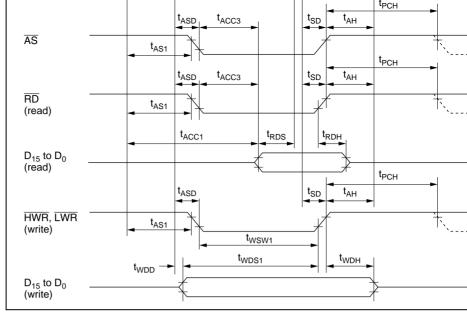

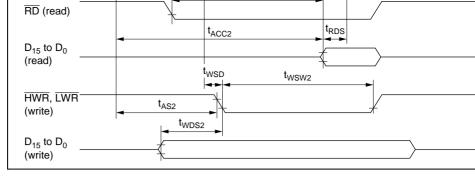

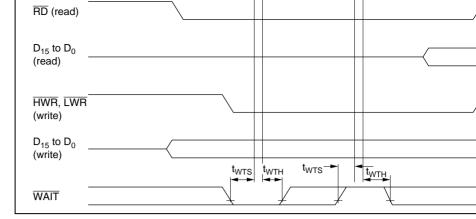

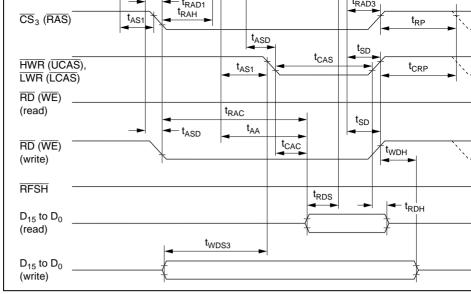

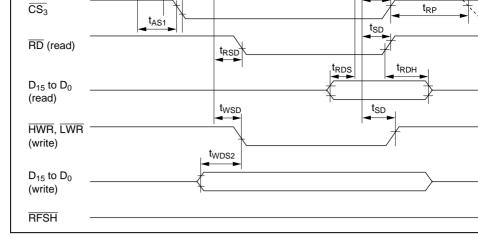

|    | 21.3.1 Bus Timing                                                    |

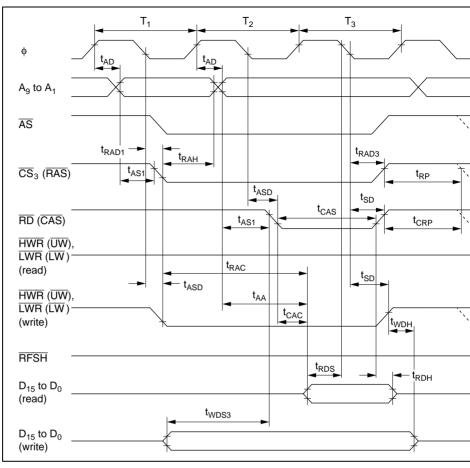

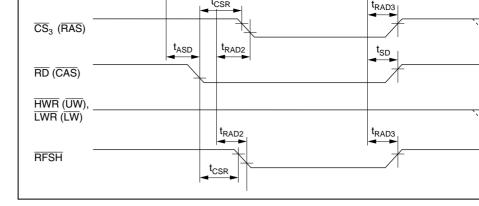

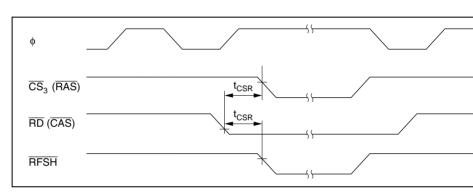

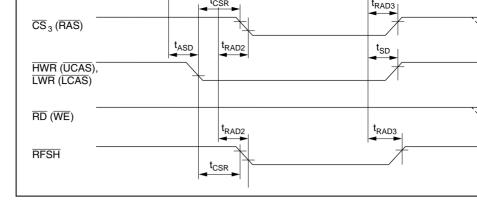

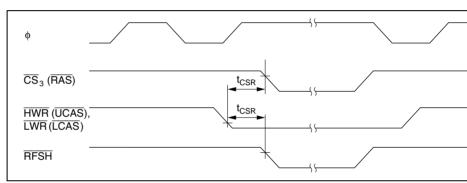

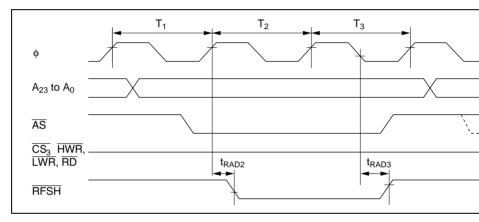

|    | 21.3.2 Refresh Controller Bus Timing                                 |

|    | 21.3.3 Control Signal Timing                                         |

|    | 21.3.4 Clock Timing                                                  |

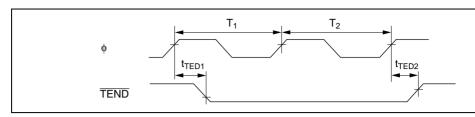

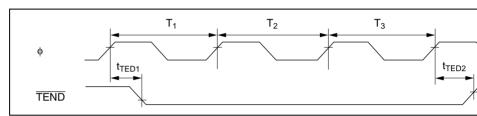

|    | 21.3.5 TPC and I/O Port Timing                                       |

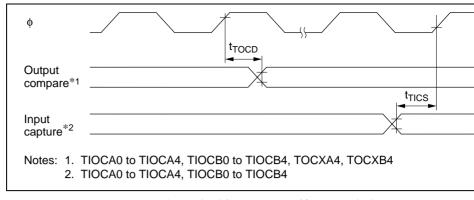

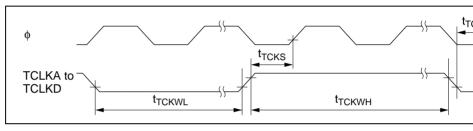

|    | 21.3.6 ITU Timing                                                    |

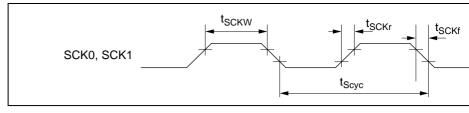

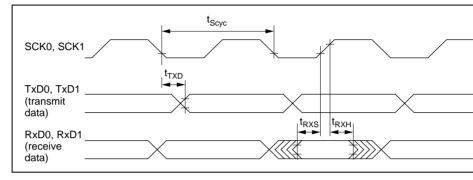

|    | 21.3.7 SCI Input/Output Timing                                       |

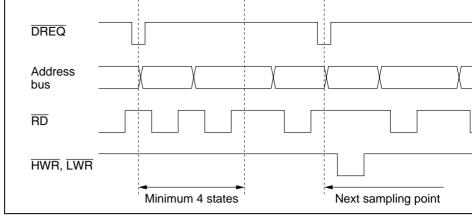

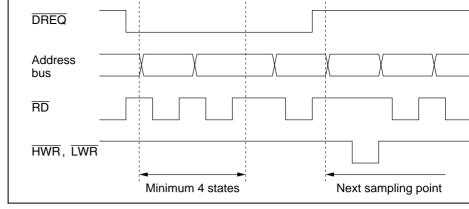

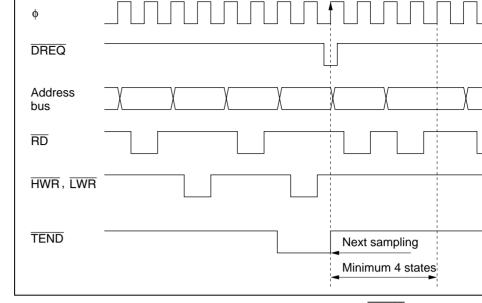

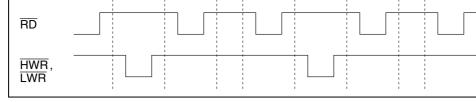

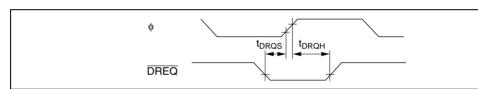

|    | 21.3.8 DMAC Timing                                                   |

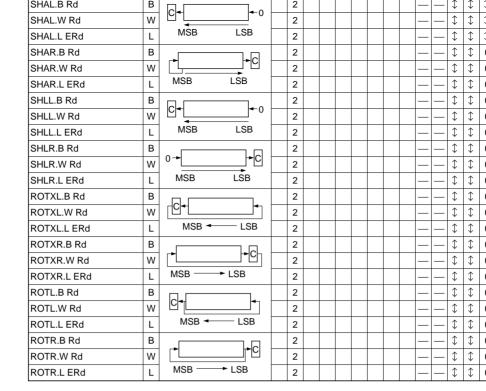

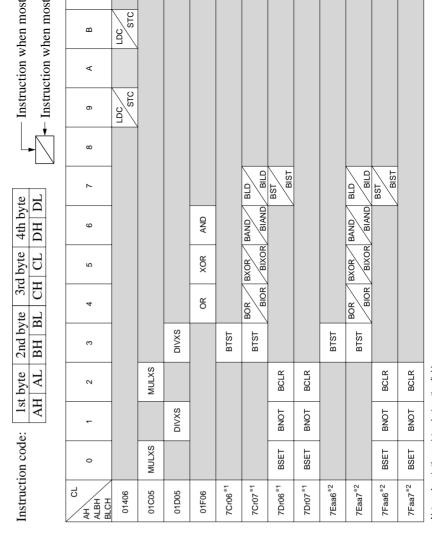

| A  | ppendix A Instruction Set                                            |

| A  |                                                                      |

| A  |                                                                      |

|    | 3 Number of States Required for Execution                            |

|    |                                                                      |

| A  | ppendix B Internal I/O Register                                      |

| В  | .1 Addresses (For H8/3048F-ONE, H8/3048B Mask ROM Version)           |

| В  | 2 Addresses (For H8/3048F, H8/3048ZTAT, H8/3048 Mask-ROM, H8/3047 Ma |

|    | H8/3045 Mask-ROM, and H8/3044 Mask-ROM Versions)                     |

| В  | 3 Function                                                           |

|    | 11 6 7/0 5 51 1 51                                                   |

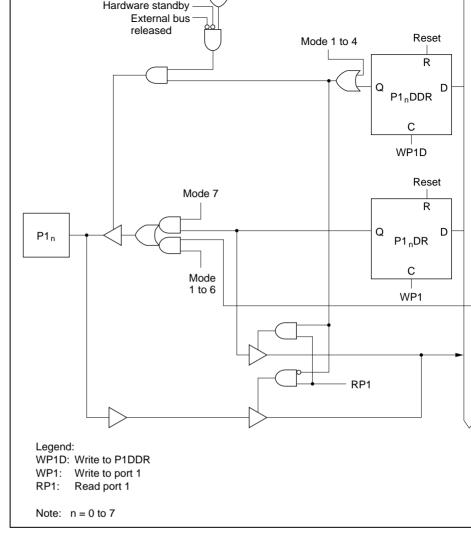

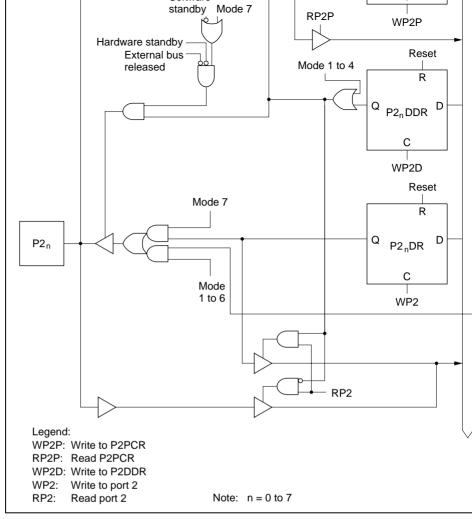

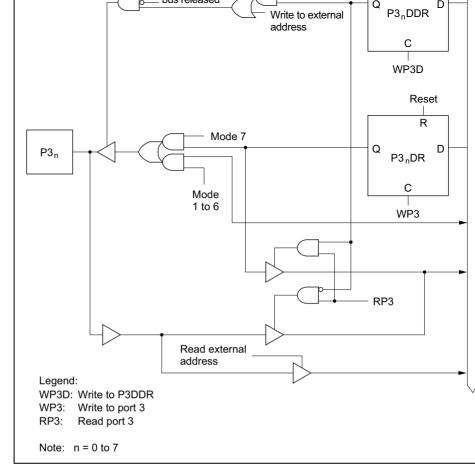

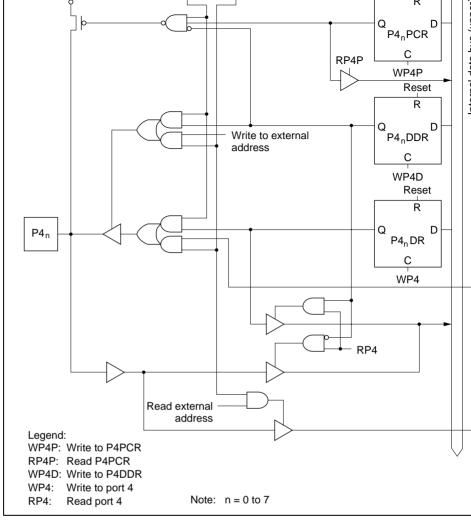

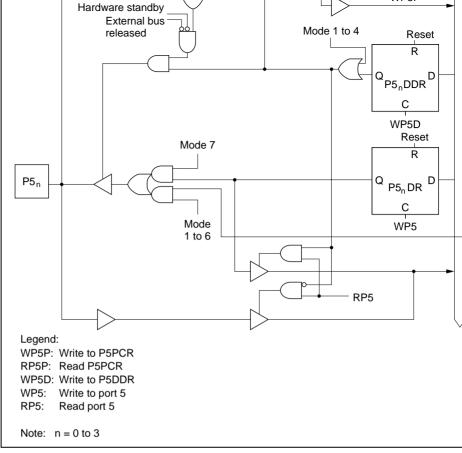

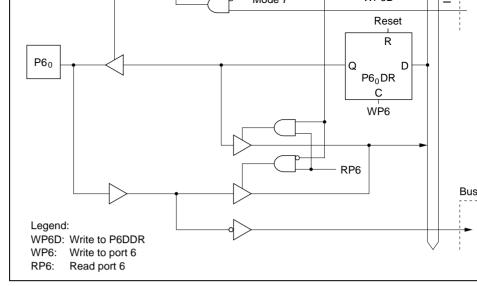

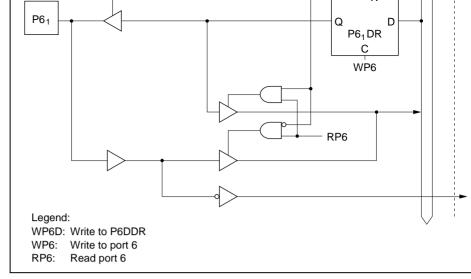

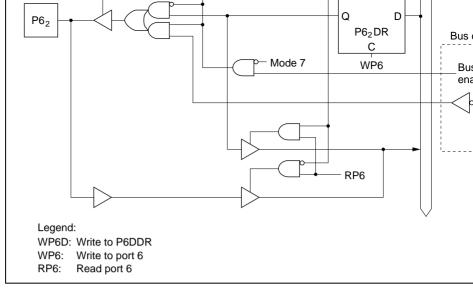

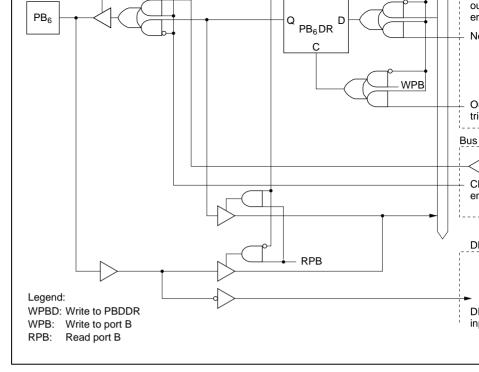

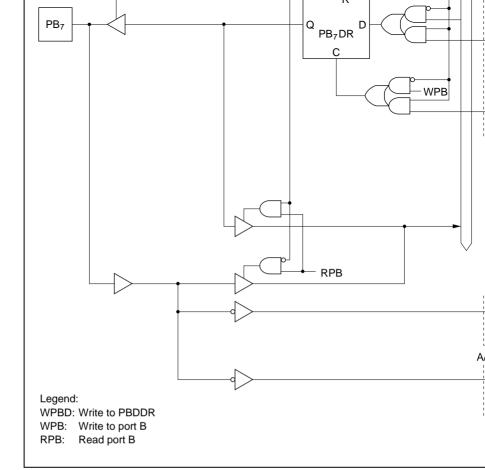

|    | ppendix C I/O Port Block Diagrams                                    |

| C  |                                                                      |

| C  |                                                                      |

| C  |                                                                      |

| C  |                                                                      |

| C  | 5 Port 5 Block Diagram                                               |

|    | Rev. 3.00 Sep 27, 2006 pa                                            |

|    | RENESAS                                                              |

|    | - (CINCSIAS                                                          |

|    |                                                                      |

21.2.1 Absolute Maximum Ratings

21.2.2 DC Characteristics

21.2.3 AC Characteristics

21.2.4 A/D Conversion Characteristics

21.2.5 D/A Conversion Characteristics

| Appendix E | Timing of Transition to and Recovery from Hardware Standby Mode |

|------------|-----------------------------------------------------------------|

| Appendix F | Product Code Lineup                                             |

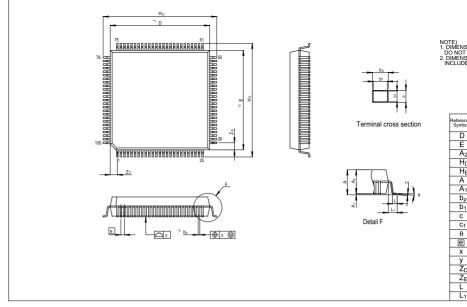

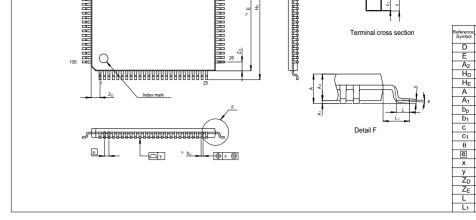

| Appendix G | Package Dimensions                                              |

Pin States at Reset.....

Rev. 3.00 Sep 27, 2006 page xxvi of xxvi

D.2

RENESAS

The H8/300H CPU has a 32-bit internal architecture with sixteen 16-bit general regist space. Its instruction set is upward-compatible at the object-code level with the H8/30

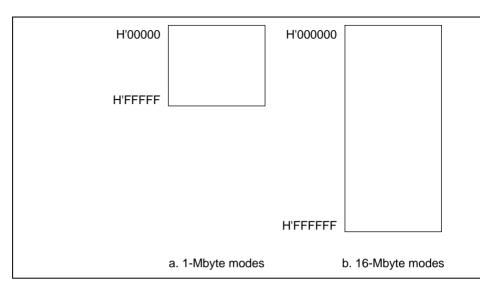

concise, optimized instruction set designed for speed. It can address a 16-Mbyte linear

enabling easy porting of software from the H8/300 Series.

The on-chip system supporting functions include ROM, RAM, a 16-bit integrated tim (ITU), a programmable timing pattern controller (TPC), a watchdog timer (WDT), a s communication interface (SCI), an A/D converter, a D/A converter, I/O ports, a direct access controller (DMAC), a refresh controller, and other facilities.

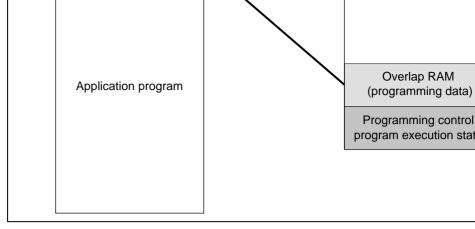

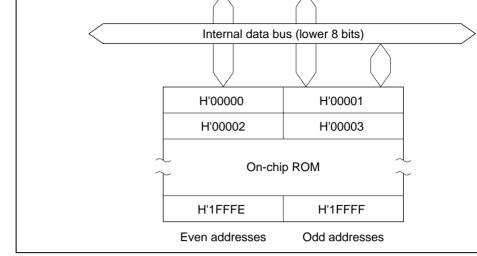

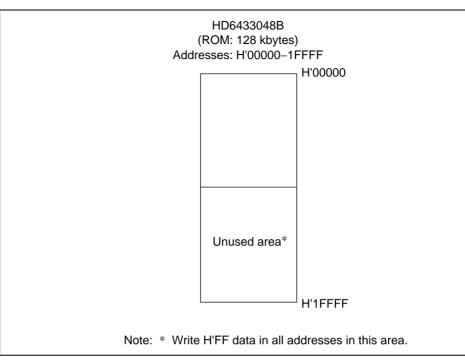

The H8/3048B Group has 128 kbytes of on-chip ROM and 4 kbytes of on-chip RAM.

Seven MCU operating modes offer a choice of data bus width and address space size. (modes 1 to 7) include one single-chip mode and six expanded modes.

In addition to mask ROM products, the H8/3048B Group includes F-ZTAT<sup>TM\*1</sup> version with on-chip user-programmable flash memory. It enables users to respond quickly ar changing application specifications as well as to conditions when ramping up from in volume production. The on-chip emulator (E10T)\*2 is capable of direct emulation of t microcontroller when mounted in the user's system, thereby making possible on-board debugging.

Table 1.1 summarizes the features of the H8/3048B Group.

Notes: 1. F-ZTAT (Flexible ZTAT<sup>TM</sup>) is a trademark of Renesas Technology Corp.

2. An on-chip emulator (E10T) is not provided in the mask ROM version.

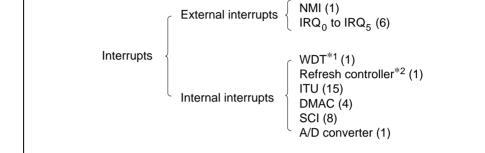

bits) Signed and unsigned divide instructions (16 bits ÷ 8 bits, 32 b bits) - Bit accumulator function Bit manipulation instructions with register-indirect specification positions Memory ROM: 128 kbytes RAM: 4 kbytes Seven external interrupt pins: NMI, IRQ to IRQ Interrupt controller 30 internal interrupts Three selectable interrupt priority levels Bus controller Address space can be partitioned into eight areas, with independ specifications in each area Chip select output available for areas 0 to 7 8-bit access or 16-bit access selectable for each area Two-state or three-state access selectable for each area Selection of four wait modes

High-speed operation (flash memory version)

8/16/32-bit data transfer, arithmetic, and logic instructions

Signed and unsigned multiply instructions (8 bits × 8 bits, 16 bits)

Maximum clock rate: 25 MHz

— Add/subtract: 80 ns— Multiply/divide: 560 ns— 16-Mbyte address space

Instruction features

Bus arbitration function

Rev. 3.00 Sep 27, 2006 page 2 of 872

| (DMAC)                             |   | Maximum four channels available                                                                                                                                                          |

|------------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |   | <ul> <li>Selection of I/O mode, idle mode, or repeat mode</li> </ul>                                                                                                                     |

|                                    |   | <ul> <li>Can be activated by compare match/input capture A interrup<br/>channels 0 to 3, transmit-data-empty and receive-data-full in<br/>SCI channel 0, or external requests</li> </ul> |

|                                    | • | Full address mode                                                                                                                                                                        |

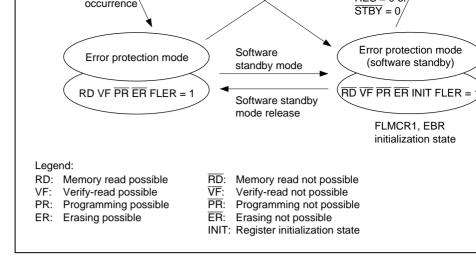

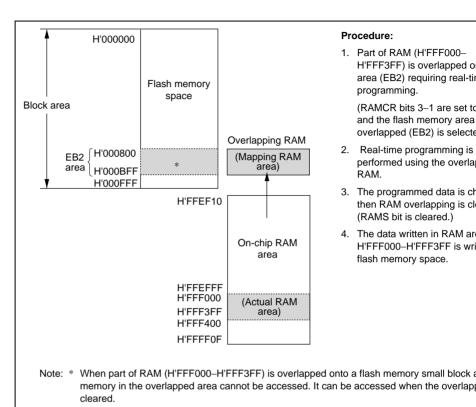

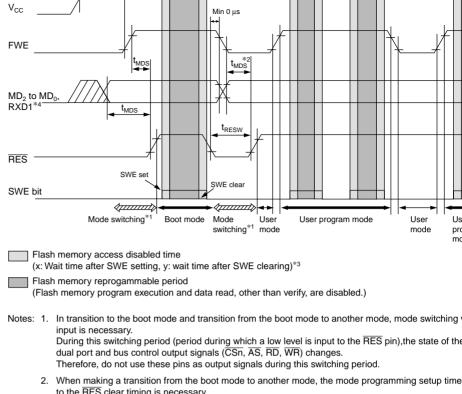

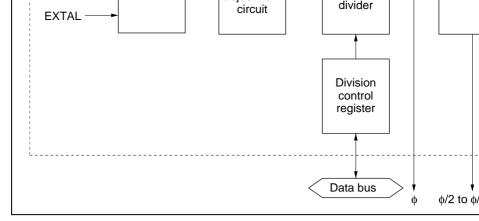

|                                    |   | <ul> <li>Maximum two channels available</li> </ul>                                                                                                                                       |