TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC74ACT299P,TC74ACT299F

#### 8-Bit PIPO Shift Register with Asynchronous Clear

The TC74ACT299 is an advanced high speed CMOS 8-BIT PIPO SHIFT REGISTER fabricated with silicon gate and double-layer metal wiring C<sup>2</sup>MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

This device may be used as a level converter for interfacing TLL or NMOS to High Speed CMOS. The inputs are compatible with TTL, NMOS and CMOS output voltage levels.

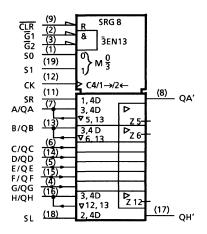

It has a four modes (HOLD, SHIFT LEFT, SHIFT RIGHT and LOAD DATA) controlled by the two selection inputs (S0, S1).

When one or both enable  $(\overline{G1}, \overline{G2})$  are high, the eight I/O outputs are forced to the high-impedance state; however, sequential operation or clearing of the register is not affected.

All inputs are equipped with protection circuits against static discharge or transient excess voltage.

#### Features (Note 1)(Note 2)

- High speed:  $f_{max} = 130 \text{ MHz}$  (typ.) at  $V_{CC} = 5 \text{ V}$

- Low power dissipation:  $I_{CC} = 8 \mu A (max)$  at  $Ta = 25^{\circ}C$

- Compatible with TTL outputs:  $V_{IL} = 0.8 V (max)$

$V_{IH} = 2.0 V (min)$

- Symmetrical output impedance:  $|I_{OH}| = I_{OL} = 24$  mA (min) Capability of driving 50  $\Omega$ transmission lines.

- Balanced propagation delays:  $t_{pLH} \simeq t_{pHL}$

- Pin and function compatible with 74F299

Note 1: Do not apply a signal to any bus terminal when it is in the output mode. Damage may result.

Note 2: All floating (high impedance) bus terminals must have their input levels fixed by means of pull up or pull down resistors.

#### **Pin Assignment**

| S0<br>G1<br>G2<br>G/QG<br>E/QE<br>C/QC<br>A/QA<br>QA'<br>CLR<br>GND | 6<br>7<br>8<br>9 |      | 19<br>18<br>17<br>16 | V <sub>cc</sub><br>S1<br>SL<br>H/QH<br>F/QF<br>D/QD<br>B/QB<br>CK<br>SR |

|---------------------------------------------------------------------|------------------|------|----------------------|-------------------------------------------------------------------------|

|                                                                     |                  | (TOP | VIEW)                |                                                                         |

DIP20-P-300-2.54A SOP20-P-300-1.27A

: 1.30 g (typ.) : 0.22 g (typ.)

#### **IEC Logic Symbol**

### Truth Table

|       |        | Inputs |    |                 |      |      |        |     |       | Inputs/<br>Outputs |     | puts |

|-------|--------|--------|----|-----------------|------|------|--------|-----|-------|--------------------|-----|------|

| Mode  | Select |        |    | Outputs Control |      | СК   | Serial |     | A/O A |                    |     | 0.1  |

|       |        | CK     | SL | SR              | A/QA | H/QH | QA'    | QH' |       |                    |     |      |

| Z     | L      | Н      | Н  | Х               | Х    | Х    | Х      | х   | Z     | Z                  | L   | L    |

| Clear | L      | L      | Х  | L               | L    | Х    | Х      | Х   | L     | L                  | L   | L    |

| Clear | L      | х      | L  | L               | L    | х    | Х      | х   | L     | L                  | L   | L    |

| Hold  | Н      | L      | L  | L               | L    | Х    | Х      | х   | QA0   | QH0                | QA0 | QH0  |

| Shift | Н      | L      | Н  | L               | L    |      | Х      | Н   | Н     | QGn                | Н   | QGn  |

| Right | Н      | L      | Н  | L               | L    |      | х      | L   | L     | QGn                | L   | QGn  |

| Shift | Н      | Н      | L  | L               | L    |      | Н      | х   | QBn   | Н                  | QBn | Н    |

| Left  | Н      | Н      | L  | L               | L    |      | L      | х   | QBn   | L                  | QBn | L    |

| Load  | Н      | Н      | Н  | Х               | Х    |      | Х      | Х   | а     | h                  | а   | h    |

Note: When one or both output controls are high, the eight input/output terminals are in the high-impedance state; however sequential or clearing of the register is not affected.

Z: High impedance

Qn0: The level of Qn before the indicated steady-state input conditions were established.

Qnn: The level of Qn before the most recent active transition indicated by  $\downarrow$  or  $\uparrow$ .

a, h: The level of the steady-state inputs A, H, respectively.

X: Don't care

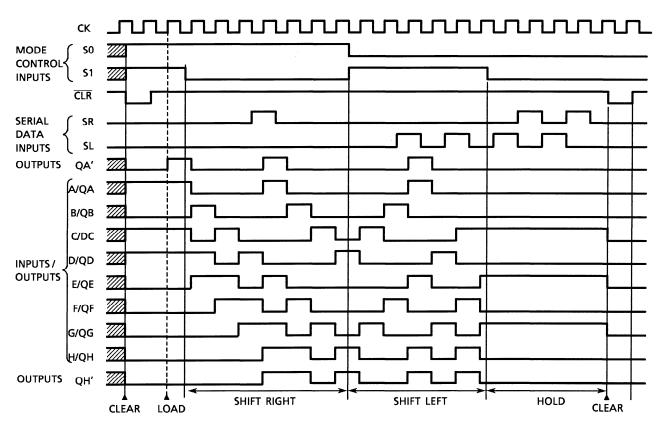

#### **Timing Chart**

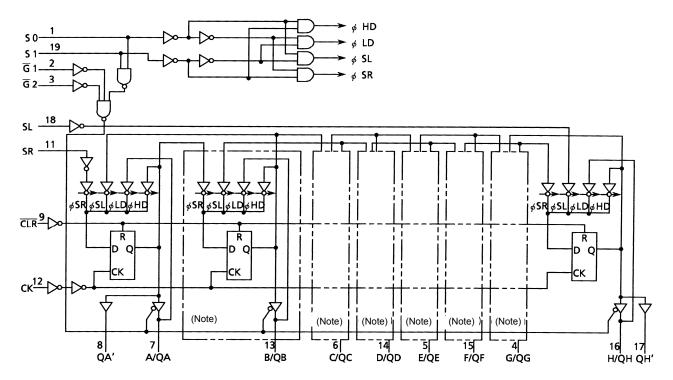

#### System Diagram

### Absolute Maximum Ratings (Note 1)

| Characteristics                    | Symbol           | Rating                        | Unit |

|------------------------------------|------------------|-------------------------------|------|

| Supply voltage range               | V <sub>CC</sub>  | –0.5 to 7.0                   | V    |

| DC input voltage                   | V <sub>IN</sub>  | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| DC output voltage                  | V <sub>OUT</sub> | -0.5 to V <sub>CC</sub> + 0.5 | V    |

| Input diode current                | I <sub>IK</sub>  | ±20                           | mA   |

| Output diode current               | IOK              | ±50                           | mA   |

| DC output current                  | IOUT             | ±50                           | mA   |

| DC V <sub>CC</sub> /ground current | ICC              | ±250                          | mA   |

| Power dissipation                  | PD               | 500 (DIP) (Note 2)/180 (SOP)  | mW   |

| Storage temperature                | T <sub>stg</sub> | –65 to 150                    | °C   |

Note 1: Exceeding any of the absolute maximum ratings, even briefly, lead to deterioration in IC performance or even destruction.

Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

Note 2: 500 mW in the range of Ta = -40 to  $65^{\circ}$ C. From Ta = 65 to  $85^{\circ}$ C a derating factor of -10 mW/°C should be applied up to 300 mW.

| Characteristics          | Symbol           | Rating               | Unit |

|--------------------------|------------------|----------------------|------|

| Supply voltage           | V <sub>CC</sub>  | 4.5 to 5.5           | V    |

| Input voltage            | V <sub>IN</sub>  | 0 to V <sub>CC</sub> | V    |

| Output voltage           | V <sub>OUT</sub> | 0 to V <sub>CC</sub> | V    |

| Operating temperature    | T <sub>opr</sub> | -40 to 85            | °C   |

| Input rise and fall time | dt/dV            | 0 to 10              | ns/V |

#### **Operating Ranges (Note)**

Note: The operating ranges must be maintained to ensure the normal operation of the device. Unused inputs must be tied to either VCC or GND.

### **Electrical Characteristics**

#### **DC Characteristics**

| Characteristics                     | Symbol          |                                                            | Test Condition                                              |        |     | -    | Ta = 25°C | )    | Ta = -40 to<br>85°C |      | Unit |  |

|-------------------------------------|-----------------|------------------------------------------------------------|-------------------------------------------------------------|--------|-----|------|-----------|------|---------------------|------|------|--|

| Characteriolico                     |                 |                                                            | V <sub>C</sub><br>(V                                        |        |     | Min  | Тур.      | Max  | Min                 | Max  |      |  |

| High-level input voltage            | V <sub>IH</sub> |                                                            | _                                                           |        |     | 2.0  | _         |      | 2.0                 | _    | V    |  |

| Low-level input voltage             | VIL             |                                                            | _                                                           |        |     | _    | _         | 0.8  | _                   | 0.8  | V    |  |

|                                     |                 | VIN                                                        | I <sub>OH</sub> = -50 μA                                    |        | 4.5 | 4.4  | 4.5       | _    | 4.4                 | _    |      |  |

| High-level output<br>voltage        | V <sub>OH</sub> | = V <sub>IN</sub><br>V <sub>IL</sub>                       | I <sub>OH</sub> = -24 mA                                    |        | 4.5 | 3.94 | —         | —    | 3.80                | —    | V    |  |

| 5                                   |                 |                                                            | I <sub>OH</sub> = -75 mA                                    | (Note) | 5.5 | —    | —         | —    | 3.85                | —    |      |  |

|                                     | V <sub>OL</sub> | V <sub>IN</sub><br>= V <sub>IH</sub> or<br>V <sub>IL</sub> | $I_{OL} = 50 \ \mu A$                                       |        | 4.5 | —    | 0.0       | 0.1  | —                   | 0.1  |      |  |

| Low-level output<br>voltage         |                 |                                                            | I <sub>OL</sub> = 24 mA                                     |        | 4.5 | —    | —         | 0.36 | —                   | 0.44 | V    |  |

| 5                                   |                 |                                                            | I <sub>OL</sub> = 75 mA                                     | (Note) | 5.5 |      |           |      | —                   | 1.65 |      |  |

| 3-state output<br>off-state current | I <sub>OZ</sub> |                                                            | $V_{IN} = V_{IH}$ or $V_{IL}$<br>$V_{OUT} = V_{CC}$ or GND  |        | 5.5 | _    | _         | ±0.5 | _                   | ±5.0 | μΑ   |  |

| Input leakage<br>current            | I <sub>IN</sub> | $V_{IN} = V_C$                                             | $V_{IN} = V_{CC}$ or GND                                    |        | 5.5 | _    | _         | ±0.1 | _                   | ±1.0 | μA   |  |

|                                     | ICC             | $V_{IN} = V_C$                                             | $V_{IN} = V_{CC}$ or GND                                    |        |     | —    | _         | 8.0  | _                   | 80.0 | μA   |  |

| Quiescent supply current            | IC              |                                                            | Per input: $V_{IN} = 3.4 V$<br>Other input: $V_{CC}$ or GND |        | 5.5 | _    | _         | 1.35 | _                   | 1.5  | mA   |  |

Note: This spec indicates the capability of driving 50  $\Omega$  transmission lines.

One output should be tested at a time for a 10 ms maximum duration.

#### Timing Requirements (input: $t_r = t_f = 3 \text{ ns}$ )

| Characteristics                                 | Symbol             | Test Condition | Test Condition      |            |     | Ta =<br>40 to<br>85°C | Unit |  |

|-------------------------------------------------|--------------------|----------------|---------------------|------------|-----|-----------------------|------|--|

|                                                 |                    |                | V <sub>CC</sub> (V) | Typ. Limit |     | Limit                 |      |  |

| Minimum pulse width                             | t <sub>W (L)</sub> |                | 5.0 ± 0.5           |            | 5.0 | 5.0                   | ns   |  |

| (CK)                                            | t <sub>W (H)</sub> |                | 5.0 ± 0.5           |            | 5.0 | 5.0                   | 115  |  |

| Minimum pulse width ( $\overline{\text{CLR}}$ ) | <sup>t</sup> W (L) | _              | $5.0\pm0.5$         | _          | 5.0 | 5.0                   | ns   |  |

| Minimum set-up time<br>(SL, SR, A~H)            | ts                 | _              | $5.0\pm0.5$         | _          | 3.5 | 3.5                   | ns   |  |

| Minimum set-up time<br>(S0, S1)                 | ts                 | _              | $5.0\pm0.5$         | _          | 6.0 | 6.5                   | ns   |  |

| Minimum hold time<br>(SL, SR, A~H)              | t <sub>h</sub>     | _              | $5.0\pm0.5$         |            | 2.0 | 2.0                   | ns   |  |

| Minimum hold time<br>(S0, S1)                   | t <sub>h</sub>     | _              | $5.0\pm0.5$         |            | 0.0 | 0.0                   | ns   |  |

| Minimum removal time<br>( CLR )                 | t <sub>rem</sub>   | _              | $5.0\pm0.5$         |            | 2.0 | 2.0                   | ns   |  |

## AC Characteristics (C<sub>L</sub> = 50 pF, R<sub>L</sub> = 500 $\Omega$ , input: t<sub>r</sub> = t<sub>f</sub> = 3 ns)

| Characteristics            | Symbol           | Test Condition |                     | -   | Ta = 25°0 | )    | Ta = -<br>85 | Unit |     |

|----------------------------|------------------|----------------|---------------------|-----|-----------|------|--------------|------|-----|

|                            |                  |                | V <sub>CC</sub> (V) | Min | Тур.      | Max  | Min          | Max  |     |

| Propagation delay time     | t <sub>pLH</sub> | _              | 5.0 ± 0.5           |     | 7.2       | 10.5 | 1.0          | 12.0 | ns  |

| (CK-QA', QH')              | tpHL             |                |                     |     |           |      |              |      |     |

| Propagation delay time     | t <sub>pHL</sub> |                | 5.0 ± 0.5           |     | 6.0       | 10.0 | 1.0          | 11.5 | ns  |

| ( CLR -QA', QH')           |                  |                |                     |     |           |      |              |      |     |

| Propagation delay time     | t <sub>pLH</sub> | _              | 5.0 ± 0.5           | _   | 7.4       | 11.4 | 1.0          | 13.0 | ns  |

| (CK-QA~QH)                 | t <sub>pHL</sub> |                |                     |     |           |      | -            |      |     |

| Propagation delay time     | t <sub>pHL</sub> | _              | 5.0 ± 0.5           | _   | 6.3       | 10.5 | 1.0          | 12.0 | ns  |

| ( CLR -QA~QH)              |                  |                |                     |     |           |      |              |      |     |

| Output enable time         | t <sub>pZL</sub> | _              | 5.0 ± 0.5           |     | 7.4       | 11.4 | 1.0          | 13.0 | ns  |

|                            | t <sub>pZH</sub> |                |                     |     |           |      |              |      |     |

| Output disable time        | t <sub>pLZ</sub> | _              | 5.0 ± 0.5           |     | 7.2       | 9.6  | 1.0          | 11.0 | ns  |

|                            | t <sub>pHZ</sub> |                | 0.0 ± 0.0           |     | 1.2       | 0.0  | 1.0          | 11.0 | 110 |

| Maximum clock<br>frequency | f <sub>max</sub> | —              | $5.0\pm0.5$         | 80  | 120       |      | 80           | _    | MHz |

| Input capacitance          | C <sub>IN</sub>  | _              |                     | _   | 5         | 10   | _            | 10   | pF  |

| Bus input capacitance      | C <sub>I/O</sub> | _              |                     | _   | 13        |      |              |      | pF  |

| Power dissipation          | C <sub>PD</sub>  |                |                     |     |           |      |              |      | pF  |

| capacitance                | (Note)           | —              |                     |     | 100       |      |              |      | μг  |

Note: C<sub>PD</sub> is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

Average operating current can be obtained by the equation:

$I_{CC}$  (opr) =  $C_{PD} \cdot V_{CC} \cdot f_{IN} + I_{CC}$

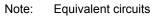

### Package Dimensions

DIP20-P-300-2.54A

Unit : mm

Weight: 1.30 g (typ.)

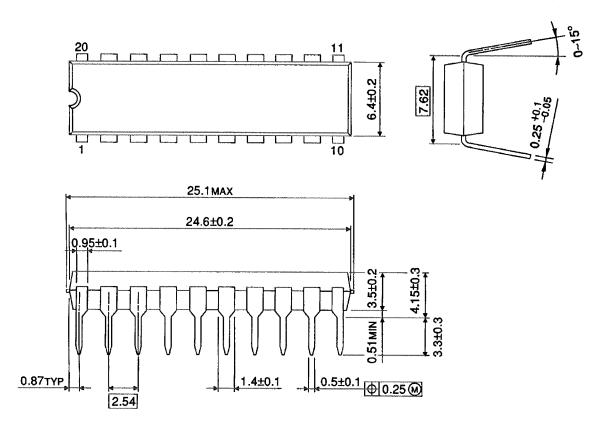

#### **Package Dimensions**

SOP20-P-300-1.27A

Unit: mm

Weight: 0.22 g (typ.)

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Logic Comparators category:

Click to view products by Toshiba manufacturer:

Other Similar products are found below :

742450X

74FCT521ATQG

LMC7221BIM5X/NOPB

SC2903NG

M38510/10301BHA

74HC85D.652

74HCT4046AD.112

HEF4046BT.652

HEF4541BT.512

SN74ALS520NSR

SN74LS682NSR

ADCMP393ARUZ-RL7

74HC280D.652

74HC85DB.118

74HCT9046AD.112

74HC688DB.118

74HCT85D.652

74HC4046AD.652

74HC4046ADB.112

74HC4088PW.112

74HC785DB.118

74HC688DB.118

74HCT85D.652

74HC4046AD.652

74HC4046ADB.112

74HC4046APW.112

74HC785DB.112

AS339GTR-E1

MC33298

74FCT521ATSOG

74FCT521ATSOG8

74FCT521CTQG

74FCT521CTSOG8

74HC7688N

004592X

74HC785D

74HC688D,652

74HC688DB,118

74HC688PW,112

74HC688PW,112

74HC85DB,652

74HC785DB,112

74HC785D

74HC688D,652

74HC688DB,118

74HC688PW,112

74HC688PW,118

74HC85DB,112

74HC85DB,118

74HC85PW,118

74HC688D

74HC785D,652

74HC785D,653

MC14585BDG

MC14585BDR2G

MC14585BD

HA17903APS-E

MC3363DW

LM239DG4

CD74HC7688MG4

SN74HC688DWRG4

SN74HC688DWRG4

SN74HC688DWRG4