# SY89200U

Ultra-Precision 1:8 LVDS Fanout Buffer with Three ÷1/÷2/÷4 Clock Divider Output Banks

Revision 6.0

### **General Description**

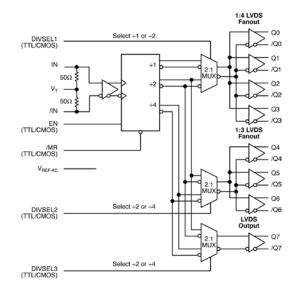

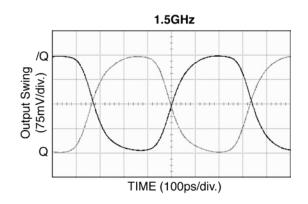

The SY89200U is a 2.5V precision, high-speed, integrated clock divider and LVDS fanout buffer capable of handling clocks up to 1.5GHz. Optimized for communications applications, the three independently controlled output banks are phase matched and can be configured for pass through  $(\div 1)$ ,  $\div 2$  or  $\div 4$  divider ratios.

The differential input includes Micrel's unique, 3-pin input termination architecture that allows the user to interface to any differential signal path. The low-skew, low-jitter outputs are LVDS-compatible with extremely fast rise/fall times guaranteed to be less than 150ps.

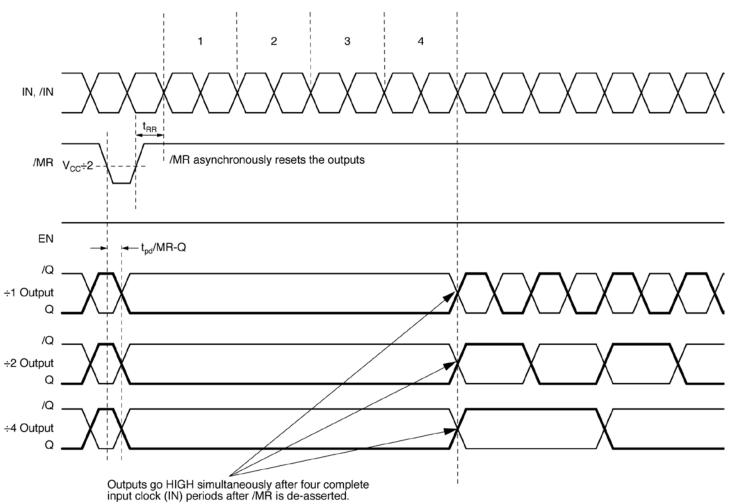

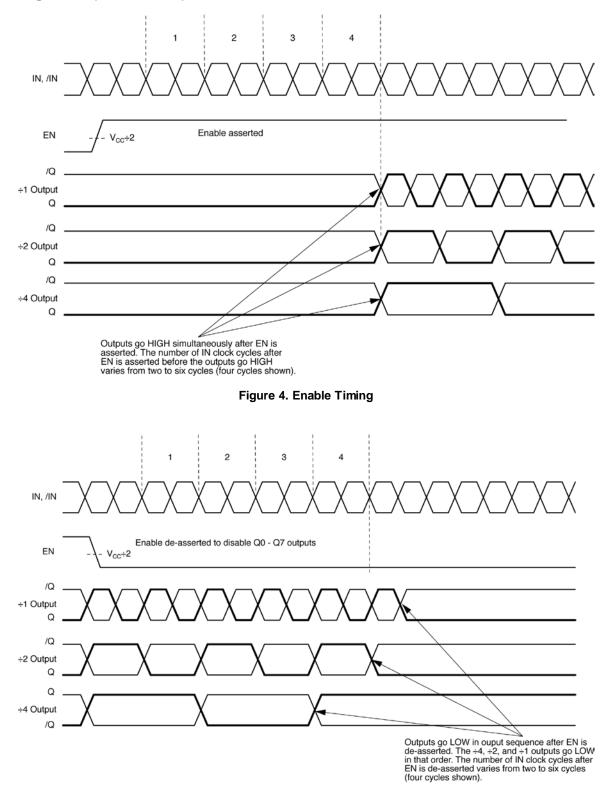

The EN (enable) input guarantees that the  $\div$ 1,  $\div$ 2 and  $\div$ 4 outputs will start from the same state without any runt pulse after an asynchronous master rest (MR) is asserted. This is accomplished by enabling the outputs after a four-clock delay to allow the counters to synchronize.

The SY89200U is part of Micrel's Precision Edge<sup>®</sup> product family.

Datasheets and support documentation are available on Micrel's web site at: <u>www.micrel.com</u>.

## **Functional Block Diagram**

Precision Edge is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

### Features

- Three low-skew LVDS output banks with programmable ÷1, ÷2 and ÷4 divider options

- Three independently programmable output banks

- Guaranteed AC performance over temperature and voltage:

- Accepts a clock frequency up to 1.5GHz

- <900ps IN-to-OUT propagation delay

- <150ps rise/fall time

- <50ps bank-to-bank phase offset

- Ultra-low jitter design:

- <1ps<sub>RMS</sub> random jitter

- <10ps<sub>PP</sub> total jitter (clock)

- Patent-pending input termination and VT pin accepts DC- and AC-coupled inputs (CML, PECL, LVDS)

- LVDS-compatible outputs

- CMOS/TTL-compatible output enable (EN) and divider select control

- 2.5V ±5% power supply

- -40°C to +85°C temperature range

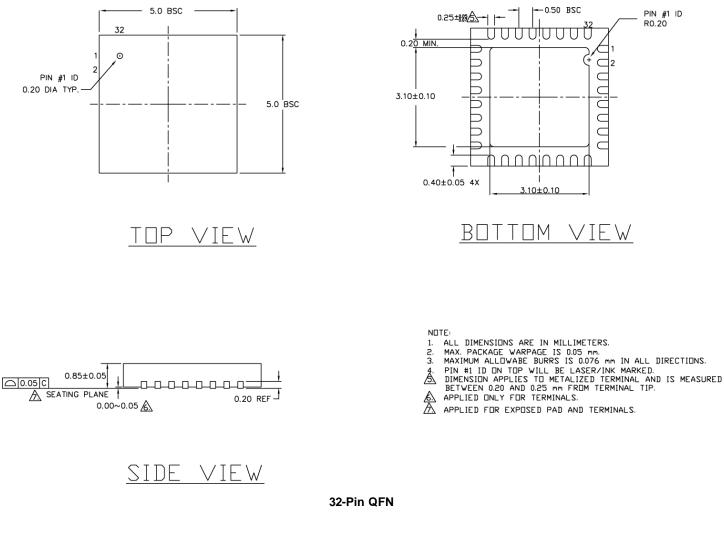

- Available in 32-pin (5mm × 5mm) QFN package

### Applications

- All SONET/SD applications

- All Fibre Channel applications

- All Gigabit Ethernet applications

# Ordering Information<sup>(1)</sup>

| Part Number                 | Package | Temperature Range | Package Marking                             | Package           |

|-----------------------------|---------|-------------------|---------------------------------------------|-------------------|

| SY89200UMG                  | QFN-32  | Industrial        | SY89200U with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

| SY89200UMGTR <sup>(2)</sup> | QFN-32  | Industrial        | SY89200U with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

Note:

1. Other voltages are available. Contact Micrel for details.

2. Tape and Reel

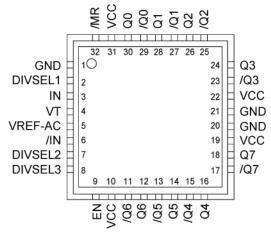

# **Pin Configuration**

#### 32-Pin QFN

## **Pin Description**

| Pin Number                         | Pin Name                                | Pin Function                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

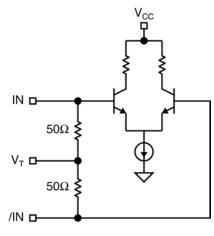

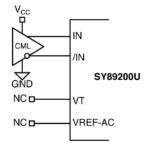

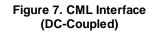

| 3, 6                               | IN, /IN                                 | Differential Input: This input pair is the differential signal input to the device. This input accepts AC- or DC-coupled signals as small as 100mV. The input pair internally terminates to a VT pin through $50\Omega$ . Note that these inputs will default to an indeterminate state if left open. Please refer to the "Input Interface Applications" section for more details. |

| 2<br>7<br>8                        | DIVSEL1<br>DIVSEL2<br>DIVSEL3           | Single-Ended Inputs: These TTL/CMOS inputs select the device ratio for each of the three banks of outputs. Note that each of these inputs is internally connected to a $25k\Omega$ pull-up resistor and will default to logic HIGH state if left open. The input-switching threshold is V <sub>CC</sub> /2.                                                                        |

| 4                                  | VT                                      | Input Termination Center-Tap: Each side of the differential input pair terminates to the VT pin.<br>The VT pin provides a center-tap to a termination network for maximum interface flexibility. See<br>"Input Interface Applications" section for more details.                                                                                                                   |

| 5                                  | VREF-AC                                 | Reference Voltage: This output biases to V <sub>CC</sub> -1.2V. It is used for AC-coupling inputs IN and /IN. For AC-coupled applications, connect VREF-AC directly to the VT pin. Bypass with $0.01\mu$ F low ESR capacitor to VCC. Maximum sink/source capability is 0.5mA.                                                                                                      |

| 9                                  | EN                                      | Single-Ended Input: This TTL/CMOS input disable and enable the Q0 – Q7 outputs. This input is internally connected to a $25k\Omega$ pull-up resistor and will default to logic HIGH state if left open. The input-switching threshold is V <sub>CC</sub> /2. For the input enable and disable functional description, refer to Figures 2a through 2c.                              |

| 30, 29, 28<br>27, 26, 25<br>24, 23 | Q0, /Q0, /Q1<br>/Q1, Q2, /Q2<br>Q3, /Q3 | Bank 1 LVDS differential output pairs controlled by DIVSEL1: LOW Q0 – Q3 = $\div$ 1 HIGH, Q0 – Q3 = $\div$ 2. Unused output pairs should be terminated with 100 $\Omega$ across the differential pair.                                                                                                                                                                             |

| 16, 15, 14<br>13, 12, 11           | Q4, /Q4, Q5<br>/Q5, Q6, /Q6             | Bank 2 LVDS differential output pairs controlled by DIVSEL2: LOW Q4 – Q6 = $\div$ 2 HIGH, Q4 – Q6 = $\div$ 4. Unused output pairs should be terminated with 100 $\Omega$ across the differential pair.                                                                                                                                                                             |

| 18, 17                             | Q7, /Q7                                 | Bank 3 LVDS differential output pairs controlled by DIVSEL3: LOW Q7 = $\div$ 2 HIGH. Q7 = $\div$ 4. Unused output pairs should be terminated with 100 $\Omega$ across the differential pair.                                                                                                                                                                                       |

| 32                                 | /MR                                     | Single-Ended Input: This TTL/CMOS-compatible master reset function asynchronously sets Q0 – Q7 outputs LOW, /Q0 – /Q7 outputs HIGH, and holds them in that state as long as /MR remains LOW. This input is internally connected to a $25k\Omega$ pull-up resistor and will default to a logic HIGH state if left open. The input-switching threshold is V <sub>CC</sub> /2.        |

| 10, 19, 22, 31                     | VCC                                     | Positive power supply. Bypass with 0.1µF∥0.01µF low ESR capacitors.                                                                                                                                                                                                                                                                                                                |

| 1, 20, 21                          | GND<br>Exposed                          | Ground and exposed pad must be connected to the same GND plane on the board.                                                                                                                                                                                                                                                                                                       |

## Truth Table

| /MR <sup>(3)</sup> | EN <sup>(4, 5)</sup> | DIVSEL1 | DIVSEL2 | DIVSEL3 | Q0 – Q3 | Q4 – Q6 | Q7 |

|--------------------|----------------------|---------|---------|---------|---------|---------|----|

| 0                  | Х                    | Х       | Х       | Х       | 0       | 0       | 0  |

| 1                  | 0                    | х       | Х       | Х       | 0       | 0       | 0  |

| 1                  | 1                    | 0       | 0       | 0       | ÷1      | ÷2      | ÷2 |

| 1                  | 1                    | 1       | 1       | 1       | ÷2      | ÷4      | ÷4 |

#### Notes:

3. /MR asynchronously forces Q0 - Q7 LOW (/Q0 - /Q7 HIGH).

4. EN forces Q0 – Q7 LOW between 2 and 6 input clock cycles after the falling edge of EN. Refer to Timing Diagram section.

5. EN synchronously enables the outputs between two and six input clock cycles after the rising edge of EN. Refer to Timing Diagram section.

# Absolute Maximum Ratings<sup>(6)</sup>

| Supply Voltage (V <sub>CC</sub> )–0.5V to +4.0V Input Voltage (V <sub>IN</sub> )–0.5V to V <sub>CC</sub> |

|----------------------------------------------------------------------------------------------------------|

| Termination Current <sup>(8)</sup>                                                                       |

| Source or sink current on V <sub>T</sub> ±100mA                                                          |

| Output Current <sup>(8)</sup>                                                                            |

| Source or sink current on IN, /IN±50mA                                                                   |

| V <sub>REF-AC</sub> Current <sup>(8)</sup>                                                               |

| Source or sink current on V <sub>REF-AC</sub> ±2mA                                                       |

| Lead Temperature (soldering, 20s)                                                                        |

| Storage Temperature (Ts)65°C to +150°C                                                                   |

# Operating Ratings<sup>(7)</sup>

| Supply Voltage (V <sub>CC</sub> )            | +2.375V to +2.625V |

|----------------------------------------------|--------------------|

| Ambient Temperature (T <sub>A</sub> )        | –40°C to +85°C     |

| Package Thermal Resistance <sup>(9)</sup>    |                    |

| QFN (θ <sub>JA</sub> ) Still-Air             | 35°C/W             |

| $QFN\left(\Psi_{JB} ight)$ Junction-to-Board | 20°C/W             |

# DC Electrical Characteristics<sup>(10)</sup>

$T_{\text{A}} = -40^{\circ}\text{C}$  to +85°C, unless otherwise stated.

| Symbol                       | Parameter                                                           | Condition                               | Min.                 | Тур.                 | Max.                 | Units |

|------------------------------|---------------------------------------------------------------------|-----------------------------------------|----------------------|----------------------|----------------------|-------|

| V <sub>CC</sub>              | Power Supply                                                        |                                         | 2.375                | 2.5                  | 2.625                | V     |

| lcc                          | Power Supply Current                                                | No load, max. V <sub>CC</sub> , Note 11 |                      |                      | 350                  | mA    |

| $R_{\text{DIFF}\_\text{IN}}$ | Differential Input Resistance<br>(IN-to-/IN)                        |                                         | 80                   | 100                  | 120                  | Ω     |

| R <sub>IN</sub>              | Input Resistance<br>(IN-to-V <sub>T</sub> , /IN-to-V <sub>T</sub> ) |                                         | 40                   | 50                   | 60                   | Ω     |

| V <sub>IH</sub>              | Input High Voltage; (IN, /IN)                                       |                                         | 1.2                  |                      | V <sub>CC</sub>      | V     |

| V <sub>IL</sub>              | Input Low Voltage; (IN, /IN)                                        |                                         | 0                    |                      | V <sub>IH</sub> -0.1 | V     |

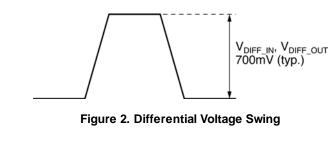

| V <sub>IN</sub>              | Input Voltage Swing; (IN, /IN)                                      | See Figure 1                            | 0.1                  |                      | V <sub>cc</sub>      | V     |

| $V_{DIFF\_IN}$               | Differential Input Voltage Swing                                    | See Figure 2                            | 0.2                  |                      |                      | V     |

| $V_{\text{REF-AC}}$          | Reference Voltage                                                   |                                         | V <sub>CC</sub> -1.3 | V <sub>CC</sub> -1.2 | V <sub>CC</sub> -1.1 | V     |

| IN-to-V <sub>T</sub>         | Voltage from Input to $V_T$                                         |                                         |                      |                      | 1.8                  | V     |

Notes:

6. Exceeding the absolute maximum ratings may damage the device.

7. The device is not guaranteed to function outside its operating ratings.

8. Due to the limited drive capability use for input of the same package only.

9. Package thermal resistance assumes exposed pad is soldered (or equivalent) to the device's most negative potential on the PCB.  $\Psi_{JB}$  uses 4-layer  $\theta_{JA}$  in still-air, unless otherwise stated.

10. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

11. Includes current through internal 50  $\ensuremath{\Omega}$  pull-up.

# LVTTL/CMOS DC Electrical Characteristics<sup>(10)</sup>

$V_{CC}$  = 2.5V ±5%;  $T_{A}$  = –40°C to +85°C, unless otherwise stated.

| Symbol | Parameter          | Condition | Min. | Тур. | Max. | Units |

|--------|--------------------|-----------|------|------|------|-------|

| VIH    | Input HIGH Voltage |           | 2.0  |      |      | V     |

| VIL    | Input LOW Voltage  |           |      |      | 0.8  | V     |

| կո     | Input HIGH Current |           | -125 |      | 30   | μA    |

| μL     | Input Low Current  |           |      |      | -300 | μA    |

# LVDS Output DC Electrical Characteristics<sup>(12)</sup>

$V_{CC}$  = 2.5V ±5%;  $T_A$  = –40°C to +85°C;  $R_L$  = 100 $\Omega$  across Q and /Q, unless otherwise stated.

| Symbol                | Parameter                                 | Condition | Min.  | Тур. | Max.  | Units |

|-----------------------|-------------------------------------------|-----------|-------|------|-------|-------|

| V <sub>OH</sub>       | Output HIGH Voltage; (Q, /Q)              |           |       |      | 1.475 | V     |

| V <sub>OL</sub>       | Output LOW Voltage; (Q, /Q)               |           | 0.925 |      |       | V     |

| V <sub>OUT</sub>      | Output Voltage Swing; (Q, /Q)             |           | 250   | 350  |       | mV    |

| V <sub>DIFF_OUT</sub> | Differential Output Voltage Swing  Q - /Q |           | 500   | 700  |       | mV    |

| V <sub>OCM</sub>      | Output Common Mode Voltage<br>(Q, /Q)     |           | 1.125 |      | 1.275 | V     |

| $\Delta V_{OCM}$      | Change in Common Mode Voltage (Q, /Q)     |           | -50   |      | +50   | mV    |

Note:

12. The circuit is designed to meet the DC specifications shown in the above table after thermal equilibrium has been established.

# AC Electrical Characteristics<sup>(13)</sup>

|                                    | 00 1 0500 D 1000                                                  |                              | · · · · · · · · · · · · · · · · · · · |

|------------------------------------|-------------------------------------------------------------------|------------------------------|---------------------------------------|

| $V_{CC} = 2.5V \pm 5\%; T_A = -40$ | $^{\circ}$ C to +85 $^{\circ}$ C; R <sub>L</sub> = 100 $\Omega$ a | icross all outputs (Q and /Q | ), unless otherwise stated.           |

| Symbol                          | Parameter                                                 | Condition                                                                                                                                                                                                                                                                                                                                                                                                                         | Min. | Тур. | Max. | Units             |

|---------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------------|

| f <sub>MAX</sub>                | Maximum Operating Frequency                               | V <sub>OUT</sub> >200mV Clock                                                                                                                                                                                                                                                                                                                                                                                                     | 1.5  |      |      | GHz               |

|                                 |                                                           | IN-to-Q                                                                                                                                                                                                                                                                                                                                                                                                                           | 500  | 700  | 900  | ps                |

| t <sub>PD</sub>                 | Differential Propagation Delay                            | /MR-to-Q                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      | 900  | ps                |

| t <sub>RR</sub>                 | Reset Recovery Time                                       | /MR(L-H)-to-(L-H)                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      | 900  | ps                |

| t <sub>PD</sub><br>Tempco       | Differential Propagation Delay<br>Temperature Coefficient |                                                                                                                                                                                                                                                                                                                                                                                                                                   |      | 115  |      | fs/°C             |

|                                 | Within-Bank Skew                                          | Within same fanout bank, Note 14                                                                                                                                                                                                                                                                                                                                                                                                  |      | 10   | 25   | ps                |

|                                 | Bank-to-Bank Skew                                         | Same divide setting, Note 15                                                                                                                                                                                                                                                                                                                                                                                                      |      | 15   | 35   | ps                |

| ISKEW                           | Bank-to-Bank Skew                                         | Delay         MR-to-Q         900           /MR(L-H)-to-(L-H)         900           Delay         115           Within same fanout bank, Note 14         10         25           Same divide setting, Note 15         15         35           Differential divide setting, Note 15         25         50           Note 16         200         200           Note 17         1         10           Note 18         10         10 | 50   | ps   |      |                   |

|                                 | Part-to-Park Skew                                         | Note 16                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      | 200  | ps                |

|                                 | Random Jitter (RJ)                                        | Note 17                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      | 1    | ps <sub>RMS</sub> |

| t <sub>JITTER</sub>             | Total Jitter (TJ)                                         | Note 18                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      | 10   | ps <sub>PP</sub>  |

| tskew                           | Cycle-to-Cycle Jitter                                     | Note 19                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      | 1    | ps <sub>RMS</sub> |

| t <sub>f</sub> ,/t <sub>f</sub> | Rise/Fall Time                                            | 20% to 80% at full output swing                                                                                                                                                                                                                                                                                                                                                                                                   | 40   | 80   | 150  | ps                |

#### Notes:

13. Measured with 100mV input swing. See Timing Diagram section for definition of parameters. High-frequency AC-parameters are guaranteed by design and characterization.

14. Within-bank is the difference in propagation delays among the outputs within the same bank.

- 15. Bank-to-bank skew is the difference in propagation delays between outputs from difference banks. Bank-to-bank skew is also the phase offset between each bank after MR is applied.

- 16. Part-to-part skew is defined for two parts with identical power supply voltages at the same temperature and with no skew of the edges at the respective inputs.

- 17. RJ is measured with a K28.7 comma detect character pattern.

- 18. Total jitter definition: With an ideal clock input of frequency ≤fMAX, no more than one output edge in 1012 output edges will deviate by more than the specified peak-to-peak jitter value.

- 19. Cycle-to-cycle jitter definition: The variation of periods between adjacent cycles, Tn Tn-1 where T is the time between rising edges of the output signal.

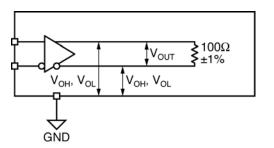

# Single-Ended Differential Swings

# **Timing Diagrams**

Figure 3. Reset with Output Enabled

## **Timing Diagrams (Continued)**

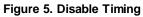

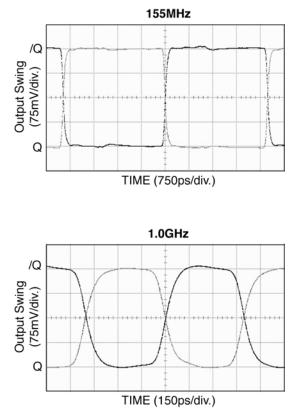

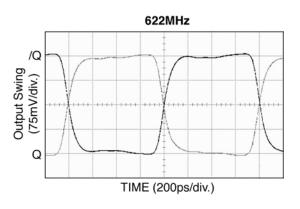

# **Typical Operating Characteristics**

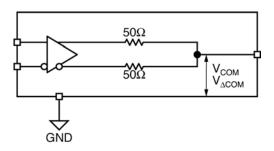

## Input Stage Internal Termination

Figure 6. Simplified Differential Input Stage

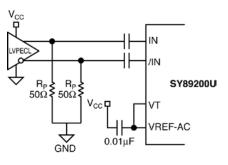

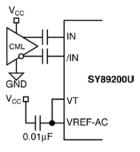

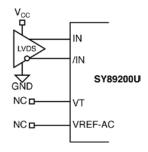

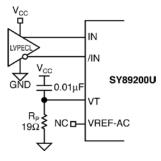

# Input Interface Applications

Option: May connect to  $V_{\rm T}$  and  $V_{\rm CC}$

Figure 10. LVPECL Interface (AC-Coupled)

Figure 8. CML Interface (AC-Coupled)

Figure 11. LVDS Interface

Figure 9. LVPECL Interface (DC-Coupled)

## **Output Interface Applications**

LVDS specifies a small swing of 350mV typical, on a nominal 1.25V common mode above ground. The common mode voltage has tight limits to permit large variations in ground between an LVDS driver and receiver. Also, change in common mode voltage, as a function of data input, is kept to a minimum to keep EMI low.

Figure 12. LVDS Differential Measurement

Figure 13. LVDS Common Mode Measurement

# Package Information<sup>(20)</sup>

#### Note:

20. Package information is correct as of the publication date. For updates and most current information, go to <u>www.micrel.com</u>.

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2013 Micrel, Incorporated.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Drivers & Distribution category:

Click to view products by Microchip manufacturer:

Other Similar products are found below :

8501BYLF

854\$015CKI-01LF

8T33F\$6221EPGI

NB7V72MMNHTBG

\$i53314-B-GMR

4RCD0124KC0ATG

P9090-0NLGI8

SY100EP33VKG

850\$1201BGILF

8004AC-13-33E-125.00000X

ISPPAC-CLK5520V-01T100C8P

4RCD0124KC0ATG8

854110AKILF

PI6C4931504-04LIE

\$I53305-B-GMR

83210AYLF

NB6VQ572MMNG

4RCD0229KB1ATG

PI6C4931502-04LIEX

8SLVD1212ANLGI

PI6C4931504-04LIEX

AD9508BCPZ-REEL7

NBA3N200SDR2G

8T79S308NLGI

\$I53315-B-GMR

NB7NQ621MMUTWG

49FCT3805DPYGI8

49FCT805BTPYG

49FCT805PYGI

RS232-S5

542MILFT

6ES7390-1AF30-0AA0

74FCT3807PYGI

\$Y89873LMG

SY89875UMG-TR

853S011BGILFT

853S9252BKILF

8P34\$1102NLGI8

8T53\$111NLGI

CDCVF2505IDRQ1

CDCUA877ZQLT

CDCE913QPWRQ1

CDC2516DGGR

8SLVP2104ANBGI/W

8S73034AGILF

LV5609LP-E

5T9950PFGI

STCD2400F35F

74FCT3807PYG18

74FCT3807PYG18

74FCT3807PYG18

8ST3034AGILF

LV5609LP-E

5T9950PFGI

STCD2400F35F