# **PR533**

### **Contactless Interface Controller**

Rev. 3.3 — 20 October 2012 206433

Product short data sheet COMPANY PUBLIC

### 1. General description

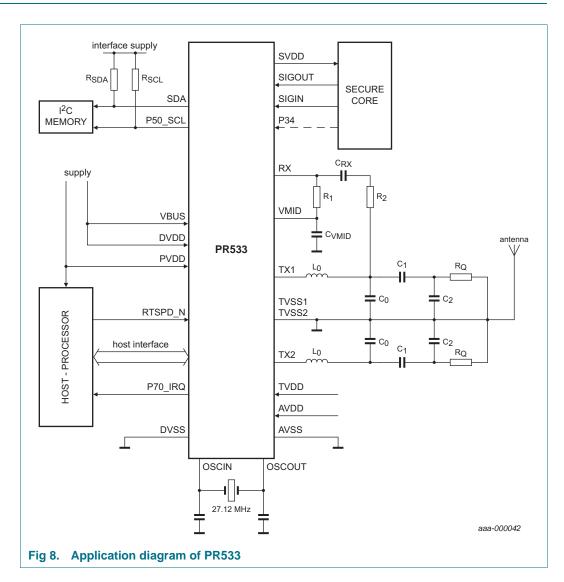

The PR5331C3HN is a highly integrated transceiver module for contactless reader/writer communication at 13.56 MHz.

A dedicated ROM code is implemented to handle different RF protocols by an integrated microcontroller. The system host controller communicates with the PR5331C3HN by using the USB or the HSU link.

The protocol between the host controller and the PR5331C3HN, on top of this physical link is the CCID protocol.

#### 1.1 RF protocols

PR5331C3HN supports the PCD mode for FeliCa (212 kbps and 424 kbps), ISO/IEC14443 Type A and B (from 106 kbps to 848 kbps), MIFARE (106 kbps), B' cards (106 kbps), picoPass tag (106 kbps) and Innovision Jewel cards (106 kbps)

The Initiator passive mode (from 106 kbps to 424 kbps) can be supported through the PC/SC transparent mode.

#### 1.2 Interfaces

The PR5331C3HN supports a USB 2.0 full speed interface (bus powered or host powered mode).

Alternatively to the USB interface, a High Speed UART (from 9600b up to 1.2 Mb) can be used to connect the PR533 to a host.

The R5331C3HN has also a master I<sup>2</sup>C-bus interface that allows to connect one of the following peripherals:

- An external EEPROM: in this case the PR5331C3HN is configured as master and is able to communicate with external EEPROM (address A0h) which can store configuration data like PID, UID and RF parameters

- A TDA8029 contact smart card reader

#### 1.3 Standards compliancy

PR5331C3HN offers commands in order for applications to be compliant with "EMV Contactless Communication Protocol Specification V2.0.1".

PR5331C3HN supports RF protocols ISO/IEC 14443A and B such as compliancy with Smart eID standard can be achieved at application level.

#### **Contactless Interface Controller**

Support of USB 2.0 full speed, interoperable with USB 3.0 hubs

The PR533C3HN in PCD mode is compliant with EMV contactless specification V2.0.1.

#### 1.4 Supported operating systems

- Microsoft Windows 2000

- Microsoft Windows XP (32 and 64 bits)

- Microsoft Windows 2003 Server (32 and 64 bits)

- Microsoft Windows 2008 Server (32 and 64 bits)

- Microsoft Windows Vista (32 and 64 bits)

- Microsoft Windows 7 (32 and 64 bits)

The PR533 is supported by the following OS through the PCSC-Lite driver:

- GNU/Linux using libusb 1.0.x and later

- Mac OS Leopard (1.5.6 and newer)

- Mac OS Snow Leopard (1.6.X)

- Solaris

- FreeBSD

#### 2. Features and benefits

- USB 2.0 full speed host interface and CCID protocol support

- Integrated microcontroller implements high-level RF protocols

- Buffered output drivers to connect an antenna with minimum number of external components

- Integrated RF level detector

- Integrated data mode detector

- Supports ISO/IEC 14443A Reader/Writer mode up to 848 kbit/s

- Supports ISO/IEC 14443B Reader/Writer mode up to 848 kbit/s

- Supports contactless communication according to the FeliCa protocol at 212 kbit/s and 424 kbit/s

- Supports MIFARE encryption

- Typical operating distance in Read/Write mode for communication to ISO/IEC 14443A/MIFARE, ISO/IEC 14443B or FeliCa cards up to 50 mm depending on antenna size and tuning

- I<sup>2</sup>C-bus master interface allows to connect an external I<sup>2</sup>C EEPROM for configuration data storage or to control a TDA8029 contact smart card reader

- Low-power modes

- Hard power-down mode

- Soft power-down mode

- Only one external oscillator required (27.12 MHz Crystal oscillator)

- Power modes

- USB bus power mode

- ◆ 2.5 V to 3.6 V power supply operating range in non-USB bus power mode

PR533\_SDS

#### **Contactless Interface Controller**

### ■ Dedicated I/O ports for external device control

### 3. Quick reference data

Table 1. Quick reference data

| Symbol                | Parameter                                 | Conditions                                                                                | Min                     | Тур       | Max        | Unit |

|-----------------------|-------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|-----------|------------|------|

| $V_{BUS}$             | bus supply voltage                        |                                                                                           | 4.02                    | 5         | 5.25       | V    |

|                       |                                           | (non-USB mode);<br>$V_{BUS} = V_{DDD}$ ; $V_{SSD} = 0 V$                                  | 2.5                     | 3.3       | 3.6        | V    |

| $V_{DDA}$             | analog supply voltage                     | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} =$                                                      | [1] 2.5                 | 3.3       | 3.6        | V    |

| $V_{DDD}$             | digital supply voltage                    | $V_{DD(PVDD)}$ ; $V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$                  | [1] 2.5                 | 3.3       | 3.6        | V    |

| V <sub>DD(TVDD)</sub> | TVDD supply voltage                       | VSS(PVSS) - VSS(TVSS) - U V                                                               | [1] 2.5                 | 3.3       | 3.6        | V    |

| V <sub>DD(PVDD)</sub> | PVDD supply voltage                       |                                                                                           | 1.6                     | -         | 3.6        | V    |

| V <sub>DD(SVDD)</sub> | SVDD supply voltage                       | $V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 \text{ V}$ ; reserved for future use | V <sub>DDD</sub> – 0.1  | -         | $V_{DDD}$  | V    |

| I <sub>BUS</sub>      | bus supply current                        | maximum load current (USB mode); measured on V <sub>BUS</sub>                             |                         |           | 150        | mA   |

|                       |                                           | maximum inrush current limitation; at power-up (curlimoff = 0)                            |                         |           | 100        | mA   |

| I <sub>pd</sub>       | power-down current                        | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD}$                                               | DD(PVDD) = 3  V;  notes | ot powere | d from USB |      |

|                       |                                           | hard power-down;<br>RF level detector off                                                 |                         |           | 10         | μΑ   |

|                       |                                           | soft power-down; RF level detector on                                                     |                         |           | 30         | μА   |

| I <sub>CCSL</sub>     | suspended low-power device supply current | RF level detector on, (with-<br>out resistor on DP/DM)                                    | -                       | -         | 250        | μΑ   |

| I <sub>DDD</sub>      | digital supply current                    | RF level detector on, V <sub>DD(SVDD)</sub> switch off                                    | [1] -                   | 15        | -          | mA   |

| I <sub>DD(SVDD)</sub> | SVDD supply current                       | $V_{DDS} = 3 V$                                                                           | -                       | -         | 30         | mA   |

| I <sub>DDA</sub>      | analog supply current                     | RF level detector on                                                                      | -                       | 6         | -          | mA   |

| $I_{DD(TVDD)}$        | TVDD supply current                       | during RF transmission;<br>V <sub>DD(TVDD)</sub> = 3 V                                    | -                       | 60        | 100        | mA   |

| P <sub>tot</sub>      | total power dissipation                   | $T_{amb} = -30 \text{ to } +85 ^{\circ}\text{C}$                                          | -                       | -         | 0.55       | W    |

| T <sub>amb</sub>      | ambient temperature                       |                                                                                           | -30                     | -         | +85        | °C   |

<sup>[1]</sup>  $V_{DDD}$ ,  $V_{DDA}$  and  $V_{DD(TVDD)}$  must always be at the same supply voltage.

#### **Contactless Interface Controller**

# 4. Ordering information

Table 2. Ordering information

| Type number              | Package |                                                                 |          |

|--------------------------|---------|-----------------------------------------------------------------|----------|

|                          | Name    | Description                                                     | Version  |

| PR5331C3HN/C350[1][2][3] | HVQFN40 | plastic thermal enhanced very thin quad flat package; no leads; | SOT618-1 |

| PR5331C3HN/C360[1][2][3] |         | 40 terminals; body $6 \times 6 \times 0.85$ mm                  |          |

- [1] 50 or 60 refers to the ROM code version described in the User Manual. For differences of romcode versions refer to the release note of the product.

- [2] Refer to Section 14.4 "Licenses".

- [3] MSL 2 (Moisture Sensitivity Level).

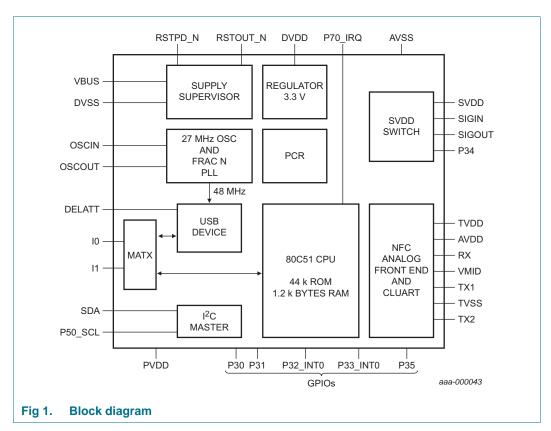

### 5. Block diagram

The following block diagram describes hardware blocks controlled by PR5331C3HN firmware or which can be accessible for data transaction by a host baseband.

**Contactless Interface Controller**

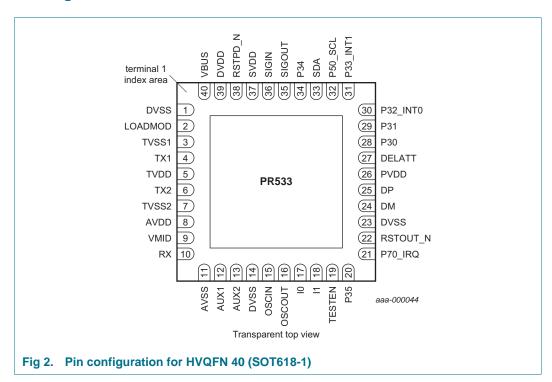

# 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

Table 3. PR533 pin description

| Symbol  | Pin | Type | Pad ref | Description                                                                                                                       |

|---------|-----|------|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| D) (00  |     | _    | voltage |                                                                                                                                   |

| DVSS    | 1   | G    |         | digital ground                                                                                                                    |

| LOADMOD | 2   | 0    | DVDD    | load modulation output provides digital signal for FeliCa and MIFARE card operating mode                                          |

| TVSS1   | 3   | G    |         | transmitter ground: supplies the output stage of TX1                                                                              |

| TX1     | 4   | 0    | TVDD    | transmitter 1: transmits modulated 13.56 MHz energy carrier                                                                       |

| TVDD    | 5   | Р    |         | transmitter power supply: supplies the output stage of TX1 and TX2                                                                |

| TX2     | 6   | 0    | TVDD    | transmitter 2: delivers the modulated 13.56 MHz energy carrier                                                                    |

| TVSS2   | 7   | G    |         | transmitter ground: supplies the output stage of TX2                                                                              |

| AVDD    | 8   | Р    |         | analog power supply                                                                                                               |

| VMID    | 9   | Р    | AVDD    | internal reference voltage: This pin delivers the internal reference voltage.                                                     |

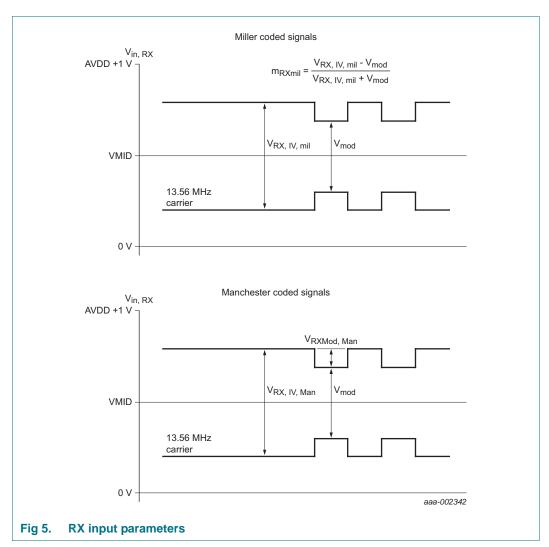

| RX      | 10  | I    | AVDD    | receiver input: Input pin for the reception signal, which is the load modulated 13.56 MHz energy carrier from the antenna circuit |

| AVSS    | 11  | G    |         | analog ground                                                                                                                     |

| AUX1    | 12  | 0    | DVDD    | auxiliary output 1: This pin delivers analog and digital test signals                                                             |

| AUX2    | 13  | 0    | DVDD    | auxiliary output 2: This pin delivers analog and digital test signals                                                             |

| DVSS    | 14  | G    |         | digital ground                                                                                                                    |

PR533\_SDS

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2012. All rights reserved.

#### **Contactless Interface Controller**

Table 3. PR533 pin description ... continued

| Symbol   | Pin | Type | Pad ref voltage | Description                                                                                                                                                                                                         |

|----------|-----|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCIN    | 15  | I    | AVDD            | crystal oscillator input: input to the inverting amplifier of the oscillator. This pin is also the input for an externally generated clock ( $f_{clk} = 27.12$ MHz).                                                |

| OSCOUT   | 16  | 0    | AVDD            | crystal oscillator output: output of the inverting amplifier of the oscillator.                                                                                                                                     |

| 10       | 17  | I    | DVDD            | interface mode lines: selects the used host interface; in test mode I0 is used                                                                                                                                      |

| l1       | 18  | I    | DVDD            | as test signals.                                                                                                                                                                                                    |

| TESTEN   | 19  | I    | DVDD            | test enable pin:                                                                                                                                                                                                    |

|          |     |      |                 | when set to 1 enable the test mode.                                                                                                                                                                                 |

|          |     |      |                 | when set to 0 reset the TCB and disable the access to the test mode.                                                                                                                                                |

| P35      | 20  | I/O  | DVDD            | general purpose I/O signal                                                                                                                                                                                          |

| P70_IRQ  | 21  | I/O  | PVDD            | interrupt request: output to signal an interrupt event to the host (Port 7 bit 0)                                                                                                                                   |

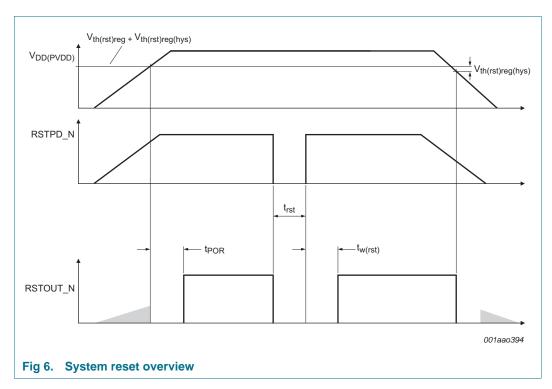

| RSTOUT_N | 22  | 0    | PVDD            | output reset signal; when LOW it indicates that the circuit is in reset state.                                                                                                                                      |

| DVSS     | 23  | G    |                 | digital ground                                                                                                                                                                                                      |

| DM       | 24  | I/O  | PVDD            | USB D- data line in USB mode or TX in HSU mode; in test mode this signal is used as input and output test signal                                                                                                    |

| DP       | 25  | I/O  | PVDD            | USB D+ data line in USB mode or RX in HSU mode; in test mode this signal is used as input and output test signal.                                                                                                   |

| PVDD     | 26  | Р    |                 | I/O pad power supply                                                                                                                                                                                                |

| DELATT   | 27  | 0    | PVDD            | optional output for an external 1.5 k $\Omega$ resistor connection on D+.                                                                                                                                           |

| P30      | 28  | I/O  | PVDD            | general purpose I/O signal. Can be configured to act either as RX line of the second serial interface UART or general purpose I/O.                                                                                  |

|          |     |      |                 | In test mode this signal is used as input and output test signal.                                                                                                                                                   |

| P31      | 29  | I/O  | PVDD            | general purpose I/O signal. Can be configured to act either as TX line of the second serial interface UART or general purpose I/O.                                                                                  |

|          |     |      |                 | In test mode this signal is used as input and output test signal.                                                                                                                                                   |

| P32_INT0 | 30  | I/O  | PVDD            | general purpose I/O signal. Can also be used as an interrupt source In test mode this signal is used as input and output test signal.                                                                               |

| P33_INT1 | 31  | I/O  | PVDD            | general purpose I/O signal. Can be used to generate an HZ state on the output of the selected interface for the Host communication and to enter into power-down mode without resetting the internal state of PR533. |

|          |     |      |                 | In test mode this signal is used as input and output test signal.                                                                                                                                                   |

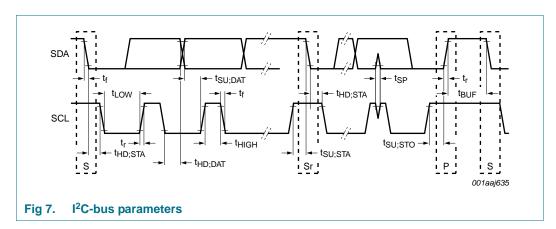

| P50_SCL  | 32  | I/O  | DVDD            | I <sup>2</sup> C-bus clock line - open-drain in output mode                                                                                                                                                         |

| SDA      | 33  | I/O  | DVDD            | I <sup>2</sup> C-bus data line - open-drain in output mode                                                                                                                                                          |

| P34      | 34  | I/O  | SVDD            | general purpose I/O signal or clock signal for the SAM                                                                                                                                                              |

| SIGOUT   | 35  | 0    | SVDD            | contactless communication interface output: delivers a serial data stream according to NFCIP-1 and output signal for the SAM.                                                                                       |

|          |     |      |                 | In test mode this signal is used as test signal output.                                                                                                                                                             |

| SIGIN    | 36  | I    | SVDD            | contactless communication interface input: accepts a digital, serial data stream according to NFCIP-1 and input signal from the SAM.                                                                                |

|          |     |      |                 | In test mode this signal is used as test signal input.                                                                                                                                                              |

| SVDD     | 37  | Р    |                 | output power for SAM power supply. Switched on by Firmware with an overload detection. Used as a reference voltage for SAM communication.                                                                           |

#### **Contactless Interface Controller**

Table 3. PR533 pin description ...continued

| Symbol  | Pin | Туре | Pad ref<br>voltage | Description                                                                                                                                                                                                                            |

|---------|-----|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTPD_N | 38  | I    | PVDD               | reset and power-down: When LOW, internal current sources are switched off, the oscillator is inhibited, and the input pads are disconnected from the outside world.  With a negative edge on this pin the internal reset phase starts. |

| DVDD    | 39  | Р    |                    | digital power supply                                                                                                                                                                                                                   |

| VBUS    | 40  | Р    |                    | USB power supply.                                                                                                                                                                                                                      |

<sup>[1]</sup> Pin types: I= Input, O = Output, I/O = Input/Output, P = Power and G = Ground.

# 7. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                | Parameter                        | Conditions                                 | Min        | Max                  | Unit |

|-----------------------|----------------------------------|--------------------------------------------|------------|----------------------|------|

| $V_{DDA}$             | analog supply voltage            |                                            | -0.5       | +4                   | V    |

| $V_{DDD}$             | digital supply voltage           |                                            | -0.5       | +4                   | V    |

| $V_{DD(TVDD)}$        | TVDD supply voltage              |                                            | -0.5       | +4                   | V    |

| $V_{DD(PVDD)}$        | PVDD supply voltage              |                                            | -0.5       | +4                   | V    |

| $V_{DD(SVDD)}$        | SVDD supply voltage              |                                            | -0.5       | +4                   | V    |

| $V_{BUS}$             | bus supply voltage               |                                            | -0.5       | +5.5                 | V    |

| P <sub>tot</sub>      | total power dissipation          |                                            | -          | 500                  | mW   |

| I <sub>DD(SVDD)</sub> | SVDD supply current              | maximum current in V <sub>DDS</sub> switch | -          | 30                   | mA   |

| $V_i$                 | input voltage                    | TX1, TX2, RX pins                          | -0.5       | +4                   | V    |

| $V_{ESD}$             | electrostatic discharge voltage  | HBM                                        | <u>[1]</u> | ±2.0                 | kV   |

|                       |                                  | MM                                         | [2] _      | 200                  | V    |

|                       |                                  | CDM                                        | [3] _      | ±1                   | kV   |

| T <sub>stg</sub>      | storage temperature              |                                            | <b>–55</b> | +150                 | °C   |

| T <sub>j</sub>        | junction temperature             |                                            | -40        | +125                 | °C   |

| $V_{i(dyn)(RX)}$      | dynamic input voltage on pin RX  | input signal at 13.56 MHz                  | -0.7       | $V_{DD(AVDD)} + 1.0$ | V    |

| $V_{i(dyn)(TX1)}$     | dynamic input voltage on pin TX1 | input signal at 13.56 MHz                  | -1.2       | $V_{DD(TVDD)} + 1.3$ | V    |

| $V_{i(dyn)(TX2)}$     | dynamic input voltage on pin TX2 | input signal at 13.56 MHz                  | -1.2       | $V_{DD(TVDD)} + 1.3$ | V    |

| I <sub>TX1</sub>      | current on pin TX1               | output signal at 13.56 MHz                 | -300       | +300                 | mA   |

| I <sub>TX2</sub>      | current on pin TX2               | output signal at 13.56 MHz                 | -300       | +300                 | mA   |

<sup>[1]</sup>  $1500 \Omega$ , 100 pF; EIA/JESD22-A114-A

<sup>[2] 0.75</sup> mH, 200 pF; EIA/JESD22-A115-A

<sup>[3]</sup> Field induced model; EIA/JESC22-C101-C

#### **Contactless Interface Controller**

### 8. Recommended operating conditions

Table 5. Operating conditions

| Symbol           | Parameter                | Conditions                                                                                                                                              |        | Min  | Тур        | Max  | Unit |

|------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------------|------|------|

| $V_{BUS}$        | bus supply voltage       | $V_{SSA} = V_{SSD = VSS(PVSS)} = V_{SS(TVSS)} = 0 \text{ V}$                                                                                            |        | 4.02 | 5          | 5.25 | V    |

|                  |                          | supply voltage (non-USB mode); $V_{BUS} = V_{DDD}$ ; $V_{SSA} = V_{SSD} = v_{SS(PVSS)} = V_{SS(TVSS)} = 0 \text{ V}$                                    |        | 2.5  | 3.3        | 3.6  | V    |

| $V_{DDA}$        | analog supply voltage    | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)};$<br>$V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$                                           | [1][2] | 2.5  | 3.3        | 3.6  | V    |

| $V_{DDD}$        | digital supply voltage   | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)};$<br>$V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$                                           | [1][2] | 2.5  | 3.3        | 3.6  | V    |

| $V_{DD(TVDD)}$   | TVDD supply voltage      | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)};$<br>$V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 V$                                           | [1][2] | 2.5  | 3.3        | 3.6  | V    |

| $V_{DD(PVDD)}$   | PVDD supply voltage      | supply pad for host interface;<br>$V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)};$<br>$V_{SSA} = V_{SSD} = V_{SS(PVSS)} = V_{SS(TVSS)} = 0 \text{ V}$ | [2]    | 1.6  | 1.8 to 3.3 | 3.6  | V    |

| T <sub>amb</sub> | ambient tempera-<br>ture |                                                                                                                                                         |        | -30  | +25        | +85  | °C   |

<sup>[1]</sup>  $V_{SSA}$ ,  $V_{DDD}$  and  $V_{DD(TVDD)}$  shall always be on the same voltage level.

### 9. Thermal characteristics

Table 6. Thermal characteristics

| Symbol        | Parameter                                   | Conditions                                                             | Min | Тур | Max  | Unit |

|---------------|---------------------------------------------|------------------------------------------------------------------------|-----|-----|------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air with exposed pad<br>soldered on a 4 layer Jedec<br>PCB-0.5 | -   | 37  | 41.1 | K/W  |

### 10. Characteristics

Unless otherwise specified, the limits are given for the full operating conditions. The typical value is given for 25 °C,  $V_{DDD}$  = 3.4 V and  $V_{DD(PVDD)}$  = 3 V in non-USB bus power mode,  $V_{BUS}$  = 5 V in USB power mode.

Timings are only given from characterization results.

#### 10.1 Power management characteristics

#### 10.1.1 Current consumption characteristics

Typical value using a complementary driver configuration and an antenna matched to 40  $\Omega$  between TX1 and TX2 at 13.56 MHz.

<sup>[2]</sup> Supply voltages below 3 V reduces the performance (e.g. the achievable operating distance).

#### **Contactless Interface Controller**

Table 7. Current consumption characteristics

|                       | •                                            |                                                                                                                                                                        |              |         |     |      |

|-----------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------|-----|------|

| Symbol                | Parameter                                    | Conditions                                                                                                                                                             | Min          | Тур     | Max | Unit |

| I <sub>pd</sub>       | power-down current                           | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)} = 3$                                                                                                                  | V; not power | ed from | USB |      |

|                       |                                              | hard power-down current; not powered from USB; RF level detector off                                                                                                   | <u>[1]</u> - | 1.3     | 10  | μА   |

|                       |                                              | soft power-down current; not powered from USB; RF level detector on                                                                                                    | <u>[1]</u> - | 9       | 30  | μА   |

| I <sub>CCSL</sub>     | suspended low-power device<br>supply current | $V_{BUS} = 5 \text{ V}; V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)} = 3 \text{ V}; V_{DDS} = 0 \text{ V}; RF level detector on (without resistor on pin DP (D+))}$ | [1] -        | 120     | 250 | μΑ   |

| I <sub>DDD</sub>      | digital supply current                       | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)}$<br>= 3 V; RF level detector on                                                                                       | -            | 12      | -   | mA   |

| I <sub>DDA</sub>      | analog supply current                        | $V_{DDA} = V_{DDD} = V_{DD(TVDD)} = V_{DD(PVDD)} = 3$                                                                                                                  | <b>V</b> ;   |         |     |      |

|                       |                                              | RF level detector on                                                                                                                                                   | -            | 3       | 6   | mΑ   |

|                       |                                              | RF level detector off                                                                                                                                                  | -            | 1.5     | 5   | mA   |

| I <sub>DD(PVDD)</sub> | PVDD supply current                          |                                                                                                                                                                        | [2] _        | -       | 30  | mA   |

| I <sub>DD(SVDD)</sub> | SVDD supply current                          | sam_switch_en set to 1                                                                                                                                                 | [3] _        | -       | 30  | mA   |

| I <sub>DD(TVDD)</sub> | TVDD supply current                          | continuous wave; V <sub>DD(TVDD)</sub> = 3 V                                                                                                                           | [4][5]       | 60      | 100 | mΑ   |

<sup>[1]</sup> I<sub>pd</sub> is the total currents over all supplies.

### 10.1.2 Voltage regulator characteristics

Table 8. Voltage regulator characteristics[1]

| Symbol                       | Parameter                                    | Conditions                                                                                | Min  | Тур  | Max  | Unit |

|------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| $V_{BUS}$                    | bus supply voltage                           | USB mode; V <sub>SS</sub> = 0 V                                                           | 4.02 | 5    | 5.25 | V    |

| $V_{DDD}$                    | digital supply voltage                       | after inrush current limitation (USB mode); from $I_{VDDD} = 0$ mA to $I_{VDDD} = 150$ mA | 2.95 | 3.3  | 3.6  | V    |

| I <sub>BUS</sub>             | bus supply current                           | USB mode; measure on V <sub>BUS</sub>                                                     | -    | -    | 150  | mΑ   |

| I <sub>inrush(lim)</sub>     | inrush current limit                         | at power-up (curlimofff = 0)                                                              | -    | -    | 100  | mΑ   |

| V <sub>th(rst)reg</sub>      | regulator reset threshold voltage            | regulator reset                                                                           | 1.90 | 2.15 | 2.40 | V    |

| V <sub>th(rst)reg(hys)</sub> | regulator reset threshold voltage hysteresis |                                                                                           | 35   | 60   | 85   | mV   |

|                              | V <sub>DDD</sub> decoupling capacitor        |                                                                                           | 8    | 10   | -    | μF   |

|                              |                                              |                                                                                           |      |      |      |      |

<sup>[1]</sup> The internal regulator is only enabled when the USB interface is selected by I0 and I1.

#### 10.2 Antenna presence self test thresholds

The values in  $\underline{\text{Table 9}}$  are guaranteed by design. Only functional is done in production for cases andet\_ithl[1:0]=10b and for andet\_ithh[2:0]=011b.

<sup>[2]</sup> I<sub>DD(PVDD)</sub> depends on the overall load at the digital pins.

<sup>[3]</sup>  $I_{DD(SVDD)}$  depends on the overall load on  $V_{DD(SVDD)}$  pad.

<sup>[4]</sup>  $I_{DD(TVDD)}$  depends on  $V_{DD(TVDD)}$  and the external circuitry connected to TX1 and TX2.

<sup>[5]</sup> During operation with a typical circuitry the overall current is below 100 mA.

#### **Contactless Interface Controller**

Table 9. Antenna presence detection

| Parameter                            | Conditions                 | Min         | Тур | Max | Unit |

|--------------------------------------|----------------------------|-------------|-----|-----|------|

| I <sub>VDDD</sub> lower current thre | shold for antenna presence | e detection |     |     |      |

| andet_ithl[1:0]                      | 00b                        | -           | 5   | -   | mA   |

|                                      | 01b                        | -           | 15  | -   | mA   |

|                                      | 10b                        | -           | 25  | -   | mA   |

|                                      | 11b                        | -           | 35  | -   | mA   |

| I <sub>VDDD</sub> upper current thre | eshold for antenna presenc | e detection |     |     |      |

| andet_ithh[2:0]                      | 000b                       | -           | 45  | -   | mA   |

|                                      | 001b                       | -           | 60  | -   | mA   |

|                                      | 010b                       | -           | 75  | -   | mA   |

|                                      | 011b                       | -           | 90  | -   | mA   |

|                                      | 100b                       | -           | 105 | -   | mA   |

|                                      | 101b                       | -           | 120 | -   | mA   |

|                                      | 110b                       | -           | 135 | -   | mA   |

|                                      | 111b                       | -           | 150 | -   | mA   |

#### **Contactless Interface Controller**

### 10.3 Typical 27.12 MHz Crystal requirements

Table 10. Crystal requirements

| Symbol            | Parameter                    | Conditions | Min    | Тур   | Max    | Unit |

|-------------------|------------------------------|------------|--------|-------|--------|------|

| f <sub>xtal</sub> | crystal frequency            |            | 27.107 | 27.12 | 27.133 | MHz  |

| ESR               | equivalent series resistance |            | -      | -     | 100    | Ω    |

| C <sub>L</sub>    | load capacitance             |            | -      | 10    | -      | pF   |

| P <sub>xtal</sub> | crystal power dissipation    |            | 100    | -     | -      | μW   |

### 10.4 Pin characteristics for 27.12 MHz XTAL Oscillator (OSCIN, OSCOUT)

Table 11. Pin characteristics for 27.12 MHz XTAL Oscillator (OSCIN, OSCOUT)

| Symbol             | Parameter                       | Conditions                                                                            |     | Min                  | Тур   | Max                  | Unit   |

|--------------------|---------------------------------|---------------------------------------------------------------------------------------|-----|----------------------|-------|----------------------|--------|

| I <sub>LI</sub>    | input leakage current           | RSTPD_N = 0 V                                                                         |     | -1                   | -     | +1                   | mA     |

| $V_{IH}$           | HIGH-level input voltage        |                                                                                       |     | $0.7 \times V_{DDA}$ | -     | $V_{DDA}$            | V      |

| $V_{IL}$           | LOW-level input voltage         |                                                                                       |     | 0                    | -     | $0.3 \times V_{DDA}$ | V      |

| V <sub>OH</sub>    | HIGH-level output voltage       |                                                                                       |     | -                    | 1.1   | -                    | V      |

| V <sub>OL</sub>    | LOW-level output voltage        |                                                                                       |     | -                    | 0.2   | -                    | V      |

| f <sub>clk</sub>   | clock frequency                 |                                                                                       |     | -0.05 %              | 27.12 | +0.05 %              | MHz    |

| δ                  | duty cycle                      |                                                                                       |     | 40                   | 50    | 60                   | %      |

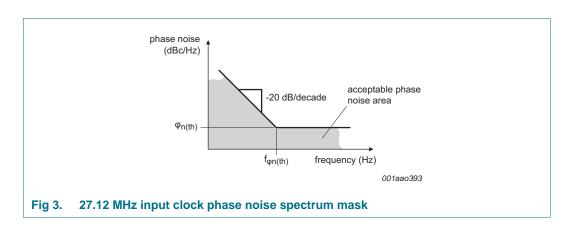

| φ <sub>n(th)</sub> | phase noise threshold           |                                                                                       | [1] | -                    | -     | -140                 | dBc/Hz |

| $f_{\phi n(th)}$   | phase noise threshold frequency | $\phi_{n(th)} = -140 dBc/Hz;$<br>-20dB/decade slope                                   | [1] | -                    | -     | 50                   | kHz    |

| OSCIN              |                                 |                                                                                       |     |                      |       |                      |        |

| Vi                 | input voltage                   | DC                                                                                    |     | -                    | 0.65  | -                    | V      |

| C <sub>i</sub>     | input capacitance               | $V_{DDA} = 2.8 \text{ V}; V_i (DC) = 0.65 \text{ V};$<br>$V_i (AC) = 1 \text{ V p-p}$ |     | -                    | 2     | -                    | pF     |

| OSCOUT             |                                 |                                                                                       |     |                      |       |                      |        |

| Ci                 | input capacitance               |                                                                                       |     | -                    | 2     | -                    | pF     |

<sup>[1]</sup>  $\phi_{n(th)}$  and  $f_{\phi n(th)}$  define the mask for maximum acceptable phase noise of the clock signal at the OSCIN, OSCOUT inputs. See Figure 3 "27.12 MHz input clock phase noise spectrum mask".

#### **Contactless Interface Controller**

### 10.5 RSTPD\_N input pin characteristics

Table 12. RSTPD\_N input pin characteristics

| Symbol          | Parameter                     | Conditions           | Min                   | Тур | Max            | Unit |

|-----------------|-------------------------------|----------------------|-----------------------|-----|----------------|------|

| $V_{IH}$        | HIGH-level input voltage      |                      | $V_{DD(PVDD)}$ $-0.4$ | -   | $V_{DD(PVDD)}$ | V    |

| $V_{IL}$        | LOW-level input voltage       |                      | 0                     | -   | 0.4            | V    |

| I <sub>IH</sub> | HIGH-level input cur-<br>rent | $V_I = V_{DD(PVDD)}$ | <b>–1</b>             | -   | 1              | μΑ   |

| I <sub>IL</sub> | LOW-level input current       | $V_I = 0 V$          | -1                    | -   | 1              | μΑ   |

| C <sub>i</sub>  | input capacitance             |                      | -                     | 2.5 | -              | pF   |

### 10.6 Input pin characteristics for I0, I1 and TESTEN

Table 13. Input pin characteristics for I0, I1 and TESTEN

| Symbol          | Parameter                | Conditions                 | Min                       | Тур | Max                  | Unit |

|-----------------|--------------------------|----------------------------|---------------------------|-----|----------------------|------|

| $V_{IH}$        | HIGH-level input voltage |                            | $[1]  0.7 \times V_{DDD}$ | -   | $V_{DDD}$            | V    |

| V <sub>IL</sub> | LOW-level input voltage  |                            | [2] 0                     |     | $0.3 \times V_{DDD}$ | V    |

| I <sub>IH</sub> | HIGH-level input current | I0 and I1; $V_I = V_{DDD}$ | [ <u>3</u> ] –1           | -   | 1                    | μΑ   |

| I <sub>IL</sub> | LOW-level input current  | $V_I = 0 V$                | <b>–1</b>                 | -   | 1                    | μΑ   |

| Ci              | input capacitance        |                            | -                         | 2.5 | -                    | pF   |

<sup>[1]</sup> To minimize power consumption when in soft power-down mode, the limit is  $V_{DDD} - 0.4 \ V.$

<sup>[2]</sup> To minimize power consumption when in soft power-down mode, the limit is 0.4  $\rm V.$

<sup>[3]</sup> TESTEN should never be set to high level in the application. It is used for production test purpose only. It is recommended to connect TESTEN to ground although there is a pull-down included.

#### **Contactless Interface Controller**

### 10.7 RSTOUT\_N output pin characteristics

Table 14. RSTOUT\_N output pin characteristics

| Symbol          | Parameter                                                        | Conditions                                                                                 |     | Min                       | Тур | Max                       | Unit |

|-----------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|---------------------------|-----|---------------------------|------|

| $V_{OH}$        | HIGH-level output                                                | $V_{DD(PVDD)} = 3 \text{ V}; I_{OH} = -4 \text{ mA}$                                       |     | $0.7 \times V_{DD(PVDD)}$ | -   | $V_{DD(PVDD)}$            | V    |

|                 | voltage                                                          | $V_{DD(PVDD)} = 1.8 \text{ V}; I_{OH} = -2 \text{ mA}$                                     | [1] | $0.7 \times V_{DD(PVDD)}$ | -   | $V_{DD(PVDD)}$            | V    |

| $V_{OL}$        | LOW-level output                                                 | $V_{DD(PVDD)} = 3 \text{ V}; I_{OL} = 4 \text{ mA}$                                        |     | 0                         | -   | $0.3 \times V_{DD(PVDD)}$ | V    |

|                 | voltage                                                          | $V_{DD(PVDD)} = 1.8 \text{ V}; I_{OL} = 2 \text{ mA}$                                      | [1] | 0                         | -   | $0.3 \times V_{DD(PVDD)}$ | V    |

| I <sub>OH</sub> | HIGH-level output current                                        | $V_{DD(PVDD)} = 3 \text{ V}; V_{OH} = 0.8 \times V_{DD(PVDD)}$                             | [2] | -4                        | -   | -                         | mA   |

|                 | $V_{DD(PVDD)} = 1.8 \text{ V}; V_{OH} = 0.7 \times V_{DD(PVDD)}$ |                                                                                            | -2  | -                         | -   | mA                        |      |

| I <sub>OL</sub> | LOW-level output current                                         | $V_{DD(PVDD)} = 3 \text{ V}; V_{OL} = 0.2 \times V_{DD(PVDD)}$                             | [2] | 4                         | -   | -                         | mA   |

|                 |                                                                  | $V_{DD(PVDD)} = 1.8 \text{ V}; V_{OL} = 0.3 \times V_{DD(PVDD)}$                           |     | 2                         | -   | -                         | mA   |

| C <sub>L</sub>  | load capacitance                                                 |                                                                                            |     |                           | -   | 30                        | pF   |

| t <sub>r</sub>  | rise time                                                        | $V_{DD(PVDD)} = 3 \text{ V};$<br>$V_{OH} = 0.8 \times V_{DD(PVDD)}; C_L = 30 \text{ pF}$   |     | -                         | -   | 13.5                      | ns   |

|                 |                                                                  | $V_{DDP} = 1.8 \text{ V};$<br>$V_{OH} = 0.7 \times V_{DD(PVDD)}; C_L = 30 \text{ pF}$      |     | -                         | -   | 10.8                      | ns   |

| t <sub>f</sub>  | fall time                                                        | $V_{DD(PVDD)} = 3 \text{ V};$<br>$V_{OL} = 0.2 \times V_{DD(PVDD)}; C_L = 30 \text{ pF}$   |     | -                         | -   | 13.5                      | ns   |

|                 |                                                                  | $V_{DD(PVDD)} = 1.8 \text{ V};$<br>$V_{OL} = 0.3 \times V_{DD(PVDD)}; C_L = 30 \text{ pF}$ |     | -                         | -   | 10.8                      | ns   |

<sup>[1]</sup> Data at  $V_{DD(PVDD)} = 1.8V$  are only given from characterization results.

<sup>[2]</sup> I<sub>OH</sub> and I<sub>OL</sub> give the output drive capability from which the rise and fall times may be calculated as a function of the load capacitance.

#### **Contactless Interface Controller**

### 10.8 Input/output characteristics for pin P70\_IRQ

Table 15. Input/output pin characteristics for pin P70\_IRQ

| Symbol          | Parameter                      | Conditions                                                                                                               |            | Min                       | Тур | Max                       | Unit |

|-----------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|-----|---------------------------|------|

| $V_{IH}$        | HIGH-level input voltage       |                                                                                                                          | [1]        | $0.7 \times V_{DD(PVDD)}$ | -   | $V_{DD(PVDD)}$            | V    |

| $V_{IL}$        | LOW-level input voltage        |                                                                                                                          | [2]        | 0                         | -   | $0.3 \times V_{DD(PVDD)}$ | V    |

| V <sub>OH</sub> | HIGH-level output voltage      | push-pull mode;<br>$V_{DD(PVDD)} = 3 \text{ V; } I_{OH} = -4 \text{ mA}$                                                 |            | $0.7 \times V_{DD(PVDD)}$ | -   | $V_{DD(PVDD)}$            | V    |

|                 |                                | push-pull mode;<br>V <sub>DD(PVDD)</sub> = 1.8 V; I <sub>OH</sub> = -2 mA                                                | [3]        | $0.7 \times V_{DD(PVDD)}$ | -   | $V_{DD(PVDD)}$            | V    |

| V <sub>OL</sub> | LOW-level output voltage       | push-pull mode;<br>$V_{DD(PVDD)} = 3 \text{ V; } I_{OL} = 4 \text{ mA}$                                                  |            | 0                         | -   | $0.3 \times V_{DD(PVDD)}$ | V    |

|                 |                                | push-pull mode;<br>$V_{DD(PVDD)} = 1.8 \text{ V}; I_{OL} = 2 \text{ mA}$                                                 | [3]        | 0                         | -   | $0.3 \times V_{DD(PVDD)}$ | V    |

| I <sub>IH</sub> | HIGH-level input current       | input mode; $V_I = V_{DDD}$                                                                                              |            | <b>–1</b>                 | -   | 1                         | μΑ   |

| I <sub>IL</sub> | LOW-level input current        | input mode; $V_1 = 0 V$                                                                                                  |            | -1                        | -   | 1                         | μΑ   |

| I <sub>OH</sub> | HIGH-level output cur-<br>rent | $V_{DD(PVDD)} = 3 \text{ V};$<br>$V_{OH} = 0.8 \times V_{DD(PVDD)}$                                                      | <u>[5]</u> | -4                        | -   | -                         | mA   |

| I <sub>OL</sub> | LOW-level output cur-<br>rent  | $V_{DD(PVDD)} = 3 \text{ V};$<br>$V_{OL} = 0.2 \times V_{DD(PVDD)}$                                                      | <u>[5]</u> | 4                         | -   | -                         | mA   |

| ILI             | input leakage current          | RSTPD_N = 0.4 V                                                                                                          |            | -1                        | -   | 1                         | μΑ   |

| Ci              | input capacitance              |                                                                                                                          |            | -                         | 2.5 |                           | pF   |

| C <sub>L</sub>  | load capacitance               |                                                                                                                          |            | -                         | -   | 30                        | pF   |

| t <sub>r</sub>  | rise time                      | $\begin{split} &V_{DD(PVDD)} = 3 \text{ V;} \\ &V_{OH} = 0.8 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$   |            | -                         | -   | 13.5                      | ns   |

|                 |                                | $\begin{split} &V_{DD(PVDD)} = 1.8 \text{ V;} \\ &V_{OH} = 0.7 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$ |            | -                         | -   | 10.8                      | ns   |

| t <sub>f</sub>  | fall time                      | $\begin{split} &V_{DD(PVDD)} = 3 \text{ V;} \\ &V_{OL} = 0.2 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$   |            | -                         | -   | 13.5                      | ns   |

|                 |                                | $\begin{split} &V_{DD(PVDD)} = 1.8 \text{ V;} \\ &V_{OL} = 0.3 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$ |            | -                         | -   | 10.8                      | ns   |

<sup>[1]</sup> To minimize power consumption when in soft power-down mode, the limit is  $V_{DD(PVDD)}-0.4\ V.$

<sup>[2]</sup> To minimize power consumption when in soft power-down mode, the limit is 0.4 V.

<sup>[3]</sup> Data at  $V_{DD(PVDD)} = 1.8 \text{ V}$  are only given from characterization results.

<sup>[4]</sup> The I<sub>OH</sub> and I<sub>OL</sub> give the output driving capability and allow to calculate directly the rise and fall time as function of the load capacitance.

**Contactless Interface Controller**

# 10.9 Input/output pin characteristics for P30 / UART\_RX, P31 / UART\_TX, P32\_INT0, P33\_INT1

Table 16. Input/output pin characteristics for P30 / UART\_RX, P31 / UART\_TX, P32\_INT0, P33\_INT1

| Symbol            | Parameter                      | Conditions                                                                                                               |            | Min                        | Тур | Max                       | Unit |

|-------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|----------------------------|-----|---------------------------|------|

| V <sub>IH</sub>   | HIGH-level input voltage       |                                                                                                                          | <u>[1]</u> | $0.7 \times V_{DD(PVDD)}$  | -   | $V_{DD(PVDD)}$            | V    |

| $V_{IL}$          | LOW-level input voltage        |                                                                                                                          | [2]        | 0                          | -   | $0.3 \times V_{DD(PVDD)}$ | V    |

| V <sub>OH</sub>   | HIGH-level output voltage      | push-pull mode;<br>$V_{DD(PVDD)} = 3 \text{ V};$<br>$I_{OH} = -4 \text{ mA}$                                             |            | V <sub>DD(PVDD)</sub> -0.4 | -   | $V_{DD(PVDD)}$            | V    |

|                   |                                | $V_{DD(PVDD)} = 1.8 \text{ V};$<br>$I_{OH} = -2 \text{ mA}$                                                              | [3]        | V <sub>DD(PVDD)</sub> –0.4 | -   | $V_{DD(PVDD)}$            | V    |

| V <sub>OL</sub>   | LOW-level output voltage       | push-pull mode;<br>$V_{DD(PVDD)} = 3 \text{ V};$<br>$I_{OL} = 4 \text{ mA}$                                              |            | 0                          | -   | 0.4                       | V    |

|                   |                                | $V_{DD(PVDD)} = 1.8 \text{ V};$<br>$I_{OL} = 2 \text{ mA}$                                                               | [3]        | 0                          | -   | 0.4                       | V    |

| I <sub>IH</sub>   | HIGH-level input current       | input mode;<br>$V_I = V_{DD(PVDD)}$                                                                                      |            | <b>-1</b>                  | -   | 1                         | μА   |

| I <sub>IL</sub>   | LOW-level input current        | input mode; $V_I = 0 V$                                                                                                  |            | -1                         | -   | 1                         | μΑ   |

| I <sub>OH</sub>   | HIGH-level output cur-<br>rent | $V_{DD(PVDD)} = 3 \text{ V};$<br>$V_{OH} = 0.8 \times V_{DD(PVDD)}$                                                      | <u>[4]</u> | -4                         | -   | -                         | mA   |

| I <sub>OL</sub>   | LOW-level output current       | $V_{DD(PVDD)} = 3 \text{ V};$<br>$V_{OL} = 0.2 \times V_{DD(PVDD)}$                                                      | <u>[4]</u> | 4                          | -   | -                         | mA   |

| ILI               | input leakage current          | RSTPD_N = 0.4 V                                                                                                          |            | -1                         | -   | 1                         | μΑ   |

| Ci                | input capacitance              |                                                                                                                          |            | -                          | 2.5 | -                         | рF   |

| C <sub>L</sub>    | load capacitance               |                                                                                                                          |            | -                          | -   | 30                        | pF   |

| t <sub>r</sub>    | rise time                      | $\begin{split} &V_{DD(PVDD)} = 3 \text{ V;} \\ &V_{OH} = 0.8 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$   |            | -                          | -   | 13.5                      | ns   |

|                   |                                | $\begin{split} &V_{DD(PVDD)} = 1.8 \text{ V;} \\ &V_{OH} = 0.7 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$ |            | -                          | -   | 10.8                      | ns   |

| t <sub>f</sub> fa | fall time                      | $\begin{split} &V_{DD(PVDD)} = 3 \text{ V;} \\ &V_{OL} = 0.2 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$   |            | -                          | -   | 13.5                      | ns   |

|                   |                                | $\begin{split} &V_{DD(PVDD)} = 1.8 \text{ V;} \\ &V_{OL} = 0.3 \times V_{DD(PVDD)}; \\ &C_L = 30 \text{ pF} \end{split}$ |            | -                          | -   | 10.8                      | ns   |

<sup>[1]</sup> To minimize power consumption when in soft power-down mode, the limit is  $V_{DD(PVDD)}-0.4\ V.$

<sup>[2]</sup> To minimize power consumption when in soft power-down mode, the limit is 0.4 V

<sup>[3]</sup> Data at  $V_{DD(PVDD)} = 1.8 \text{ V}$  are only given from characterization results.

<sup>[4]</sup> The I<sub>OH</sub> and I<sub>OL</sub> give the output driving capability and allow to calculate directly the rise and fall time as function of the load capacitance.

#### **Contactless Interface Controller**

### 10.10 Input/output pin characteristics for P35

Table 17. Input/output pin characteristics for P35

| Symbol          | Parameter                 | Conditions                                                                                                  |            | Min                  | Тур | Max                  | Unit |

|-----------------|---------------------------|-------------------------------------------------------------------------------------------------------------|------------|----------------------|-----|----------------------|------|

| V <sub>IH</sub> | HIGH-level input voltage  |                                                                                                             | <u>[1]</u> | $0.7 \times V_{DDD}$ | -   | $V_{DDD}$            | V    |

| V <sub>IL</sub> | LOW-level input voltage   |                                                                                                             | [2]        | 0                    | -   | $0.3 \times V_{DDD}$ | V    |

| V <sub>OH</sub> | HIGH-level output voltage | $V_{DDD} = 3 \text{ V}; I_{OH} = -4 \text{ mA}$                                                             |            | $V_{DDD}-0.4$        | -   | $V_{DDD}$            | V    |

| V <sub>OL</sub> | LOW-level output voltage  | $V_{DDD} = 3 \text{ V}; I_{OL} = 4 \text{ mA}$                                                              |            | 0                    | -   | 0.4                  | V    |

| I <sub>IH</sub> | HIGH-level input current  | $V_I = V_{DDD}$                                                                                             |            | -1                   | -   | 1                    | μΑ   |

| I <sub>IL</sub> | LOW-level input current   | $V_I = 0 V$                                                                                                 |            | -1                   | -   | 1                    | μΑ   |

| Гон             | HIGH-level output current | $V_{DDD} = 3 \text{ V};$<br>$V_{OH} = 0.8 \times V_{DD(PVDD)}$                                              | [3]        | -4                   | -   | -                    | mA   |

| OL              | LOW-level output current  | $V_{DDD} = 3 \text{ V};$<br>$V_{OL} = 0.2 \times V_{DD(PVDD)}$                                              | [3]        | 4                    | -   | -                    | mA   |

| I <sub>LI</sub> | input leakage current     | $RSTPD_N = 0.4 V$                                                                                           |            | -1                   | -   | 1                    | μΑ   |

| Ci              | input capacitance         |                                                                                                             |            | -                    | 2.5 | -                    | pF   |

| CL              | load capacitance          |                                                                                                             |            | -                    | -   | 30                   | pF   |

| t <sub>r</sub>  | rise time                 | $\begin{split} V_{DDD} &= 3 \text{ V};  V_{OH} = 0.8 \times V_{DDD}; \\ C_L &= 30 \text{ pF} \end{split}$   |            | -                    | -   | 13.5                 | ns   |

|                 |                           | $\begin{split} V_{DDD} &= 1.8 \text{ V; } V_{OH} = 0.7 \times V_{DDD}; \\ C_L &= 30 \text{ pF} \end{split}$ |            | -                    | -   | 10.8                 | ns   |

| t <sub>f</sub>  | fall time                 | $V_{DDD}$ = 3 V; $V_{OL}$ = 0.2 × $V_{DDD}$ ; $C_L$ = 30 pF                                                 |            | -                    | -   | 13.5                 | ns   |

|                 |                           | $V_{DDD} = 1.8 \text{ V}; V_{OL} = 0.3 \times V_{DDD};$ $C_L = 30 \text{ pF}$                               |            | -                    | -   | 10.8                 | ns   |

<sup>[1]</sup> To minimize power consumption when in soft power-down mode, the limit is  $V_{DDD}$  – 0.4 V.

<sup>[2]</sup> To minimize power consumption when in soft power-down mode, the limit is 0.4 V.

<sup>[3]</sup> The I<sub>OH</sub> and I<sub>OL</sub> give the output driving capability and allow to calculate directly the rise and fall time as function of the load capacitance.

#### **Contactless Interface Controller**

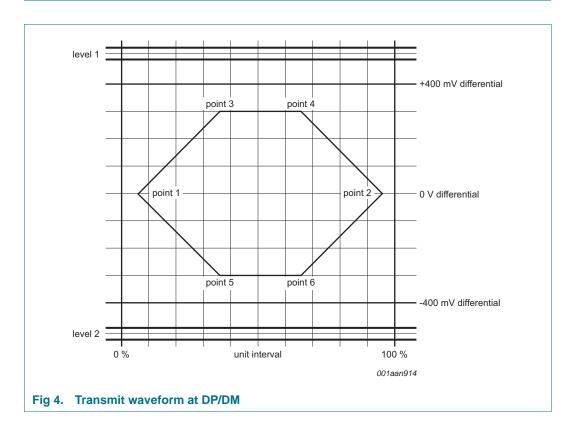

### 10.11 Input/output pin characteristics for DP and DM

Table 18. Input/output pin characteristics for DP and DM for USB interface

| Symbol              | Parameter                                                                  | Conditions                                                                     |            | Min   | Тур | Max            | Unit |

|---------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------|-------|-----|----------------|------|

| V <sub>IH</sub>     | HIGH-level input voltage                                                   | $V_{DD(PVDD)} = 3.3 \text{ V}$                                                 |            | 2     | -   | 3.6            | V    |

| V <sub>IL</sub>     | LOW-level input voltage                                                    |                                                                                | <u>[1]</u> | 0     | -   | 0.8            | V    |

| V <sub>OH</sub>     | HIGH-level output voltage                                                  | $V_{DD(PVDD)} = 3.3 \text{ V};$ $R_{PD} = 1.5 \Omega \text{ to V}_{SS}$        |            | 2.8   | -   | $V_{DD(PVDD)}$ | V    |

| V <sub>OL</sub>     | LOW-level output voltage                                                   | $V_{DD(PVDD)} = 3.3 \text{ V};$ $R_{PD} = 1.5 \Omega \text{ to } V_{DD(PVDD)}$ |            | 0     | -   | 0.3            | V    |

| I <sub>OH</sub>     | HIGH-level output current                                                  | $V_{DD(PVDD)} = 3.3 \text{ V};$<br>$V_{OH} = 0.8 \times V_{DD(PVDD)}$          | [2]        | -4    | -   | -              | mA   |

|                     |                                                                            | $V_{DD(PVDD)} = 1.8 \text{ V};$<br>$V_{OH} = 0.7 \times V_{DD(PVDD)}$          |            | -2    | -   | -              | mA   |

| l <sub>OL</sub>     | LOW-level output current                                                   | $V_{DD(PVDD)} = 3.3 \text{ V};$<br>$V_{OL} = 0.2 \times V_{DD(PVDD)}$          | [2]        | 4     | -   | -              | mΑ   |

|                     |                                                                            | $V_{DD(PVDD)} = 1.8 \text{ V};$<br>$V_{OL} = 0.3 \times V_{DD(PVDD)}$          |            | 2     | -   | -              | mA   |

| I <sub>IH</sub>     | HIGH-level input current                                                   | $V_{I} = V_{DD(PVDD)}$                                                         |            | -     | -   | 1              | μΑ   |

| I <sub>IL</sub>     | LOW-level input current                                                    | $V_I = 0 V$                                                                    |            | -     | -   | 1              | μΑ   |

| ILI                 | input leakage current                                                      | RSTPD_N = 0 V                                                                  |            | -1    | -   | +1             | μΑ   |

| Ci                  | input capacitance                                                          |                                                                                |            | -     | 2.5 | 3.5            | pF   |

| Z <sub>INP</sub>    | input impedance exclusive of pull-up/pull-down (for low-/full speed)       |                                                                                |            | 300   | -   | -              | kΩ   |

| $Z_{DRV}$           | driver output impedance for driver which is not high-speed capable         |                                                                                |            | 28    | -   | 44             | Ω    |

| t <sub>FDRATE</sub> | full-speed data rate for devices which are not high-speed capable          |                                                                                |            | 11.97 | -   | 12.03          | Mb/s |

| t <sub>DJ1</sub>    | source jitter total (including frequency tolerance) to next transition     |                                                                                |            | -3.5  | -   | +3.5           | ns   |

| t <sub>DJ2</sub>    | source jitter total (including frequency tolerance) for paired transitions |                                                                                |            | -4    | -   | +4             | ns   |

| t <sub>FDEOP</sub>  | source jitter for differential transition to SE0 transition                |                                                                                |            | -2    | -   | +5             | ns   |

| t <sub>JR1</sub>    | receiver jitter to next transition                                         |                                                                                |            | -18.5 | -   | +18.5          | ns   |

| t <sub>JR2</sub>    | receiver jitter for paired transitions                                     |                                                                                |            | -9    | -   | +9             | ns   |

| t <sub>FEOPT</sub>  | source SE0 interval of EOP                                                 |                                                                                |            | 160   | -   | 175            | ns   |

| t <sub>FEOPR</sub>  | receiver SE0 interval of EOP                                               |                                                                                |            | 82    | -   | -              | ns   |

| t <sub>FST</sub>    | width of SE0 interval during differential transition                       |                                                                                |            | -     | -   | 14             | ns   |

|                     |                                                                            |                                                                                |            |       |     |                |      |

<sup>[1]</sup> The value does not guarantee the power-down consumptions. To reach the specified power-down consumptions, the limit is 0.4 V.

<sup>[2]</sup> The I<sub>OH</sub> and I<sub>OL</sub> give the output driving capability and allow to calculate directly the rise and fall time as function of the load capacitance.

#### **Contactless Interface Controller**

Table 19. USB DP/DM differential receiver input levels

| Symbol   | Parameter                                   | Conditions | Min | Тур | Max | Unit |

|----------|---------------------------------------------|------------|-----|-----|-----|------|

| $V_{DI}$ | differential input sen-<br>sitivity voltage | -          | 0.2 | -   | -   | V    |

| $V_{CM}$ | differential common mode voltage range      | -          | 0.8 | -   | 2.5 | V    |

Table 20. USB DP/DM driver characteristics

| Symbol            | Parameter                                | Conditions                                                                                | Min | Тур | Max   | Unit |

|-------------------|------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-------|------|

| t <sub>r</sub>    | rise time                                | $C_L = 50 \text{ pF};$<br>10 % to 90 %<br>of (V <sub>OH</sub> - V <sub>OL</sub> )         | 4   | -   | 20    | ns   |

| t <sub>f</sub>    | fall time                                | $C_L = 50 \text{ pF};$<br>10 % to 90 %<br>of $(V_{OH} - V_{OL})$                          | 4   | -   | 20    | ns   |

| t <sub>FRFM</sub> | differential rise and fall time matching | (t <sub>FR</sub> /t <sub>FF</sub> ); excluding<br>the first transition<br>from Idle state | 90  | -   | 111.1 | %    |

| V <sub>CRS</sub>  | output signal cross-<br>over voltage     | excluding the first transition from Idle state                                            | 1.3 | -   | 2.0   | V    |

#### **Contactless Interface Controller**

Table 21. Input Pin characteristics for DP for HSU interface

| Symbol          | Parameter                | Conditions           |     | Min                       | Тур | Max                       | Unit |

|-----------------|--------------------------|----------------------|-----|---------------------------|-----|---------------------------|------|

| $V_{IH}$        | HIGH-level input voltage |                      | [1] | $0.7 \times V_{DD(PVDD)}$ | -   | $V_{DD(PVDD)}$            | V    |

| V <sub>IL</sub> | LOW-level input voltage  |                      | [2] | 0                         | -   | $0.3 \times V_{DD(PVDD)}$ | V    |

| I <sub>IH</sub> | HIGH-level input current | $V_i = V_{DD(PVDD)}$ |     | -                         | -   | 1                         | mA   |

| I <sub>IL</sub> | LOW-level input current  | $V_i = 0 V$          |     | -                         | -   | 1                         | mA   |

| ILI             | input leakage current    | RSTPD_N = 0 V        |     | <b>–1</b>                 |     | 1                         | mA   |

| C <sub>i</sub>  | input capacitance        |                      |     | -                         | 2.5 | 3.5                       | pF   |

<sup>[1]</sup> The value does not guarantee the power-down consumptions. To reach the specified power-down consumptions, the limit is  $V_{DD(PVDD)} = 0.4 \text{ V}$ .

Table 22. Output Pin characteristics for DM for HSU interface

| Table 22.               | Output i ili characteri                                               | ISLICS for DIVITOR HSO INTERFACE                                                                                         |            |                      |     |                |      |

|-------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|----------------------|-----|----------------|------|

| Symbol                  | Parameter                                                             | Conditions                                                                                                               |            | Min                  | Тур | Max            | Unit |

| V <sub>OH</sub>         | HIGH-level output                                                     | $V_{DD(PVDD)} = 3 \text{ V}; I_{OH} = -4 \text{ mA}$                                                                     |            | $V_{DD(PVDD)} - 0.4$ | -   | $V_{DD(PVDD)}$ | V    |

|                         | voltage                                                               | $V_{DD(PVDD)} = 1.8 \text{ V}; I_{OH} = -2 \text{ mA}$                                                                   |            | $V_{DD(PVDD)} - 0.4$ | -   | $V_{DD(PVDD)}$ | V    |

| $V_{OL}$                | LOW-level output volt-                                                | $V_{DD(PVDD)} = 3 \text{ V}; I_{OL} = -4 \text{ mA}$                                                                     |            | 0                    | -   | 0.4            | V    |

|                         | age                                                                   | $V_{DD(PVDD)} = 1.8 \text{ V}; I_{OL} = -2 \text{ mA}$                                                                   |            | 0                    | -   | 0.4            | V    |

| ОН                      | HIGH-level output current                                             | $V_{DD(PVDD)} = 3 \text{ V};$<br>$V_{OH} = 0.8 \times V_{DD(PVDD)}$                                                      | [1]        | -4                   | -   | -              | mA   |