### MIC2782

# Dual-Input Push Button Reset IC with Immediate and Delayed Outputs

### **General Description**

The MIC2782 is a two input, two output push button reset IC. It will generate a reset pulse for a factory programmed reset timeout period after both manual reset inputs have been held to a logic-low for the factory programmed setup period. The MIC2782 also has an ANDOUT logic output which will activate if both inputs are held low for longer than a debounce time (1.5ms), and deactivate if one or both inputs are released for longer than a debounce time (1.5ms). The RESET and ANDOUT outputs are active-low, open-drain NMOS outputs.

The MIC2782 operates over the 1.5V to 5.5V supply voltage range, consuming  $2.2\mu A$  of supply current at 3.3V. The device features  $65k\Omega$  internal pull-up resistors on both of the inputs (/MR1 and /MR2). The device offers factory programmed setup periods of 6s, 8s, 10s, or 12s and reset timeout periods of 0.5s, 1s or 2s. It is available in a space saving, 6-bump, 0.4mm pitch, 0.8mm x 1.2mm Wafer Level Chip Scale Package.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

- 1.5V to 5.5V Operating Supply Voltage Range

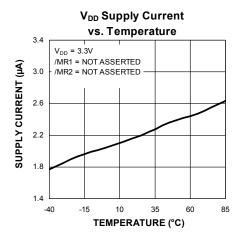

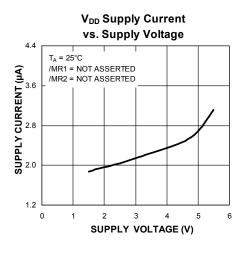

- 2.2μA Supply Current with /MR1, /MR2 not asserted

- Factory programmed setup periods of 6s, 8s, 10s or 12s

- Factory programmed reset timeout periods of 0.5s, 1s or 2s

- Integrated 65kΩ /MR1 and /MR2 Pull-Up Resistors

- Supports single push button reset with /MR1 tied to /MR2

- RESET asserts after /MR1 and /MR2 are asserted low for a setup period

- ANDOUT asserts after /MR1 and /MR2 are asserted low for a debounce time (1.5ms)

- Open-Drain RESET and ANDOUT Outputs

- 6-bump, 0.4mm pitch, 0.8mm x 1.2mm Wafer Level Chip Scale Package (WLCSP)

### **Applications**

- Smart Phones

- Tablets

- eBooks

- Portable Games

- Portable Navigation Device

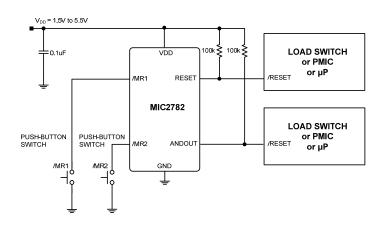

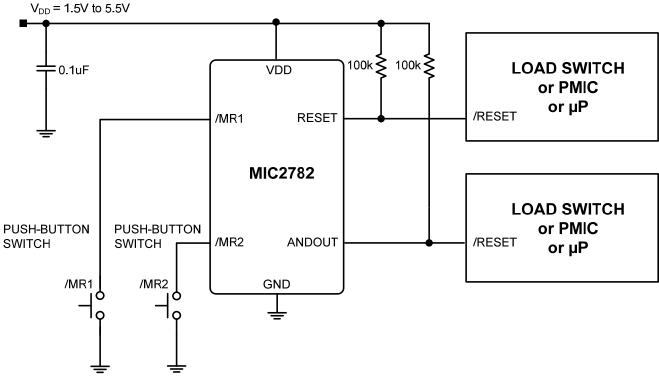

# **Typical Application**

January 2012 M9999-010912-A

### **Ordering Information**

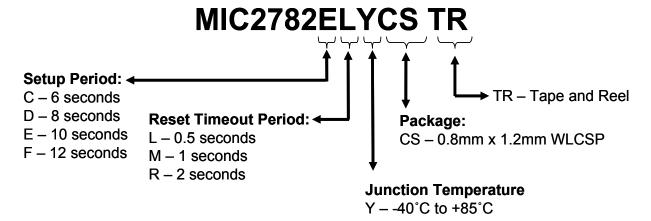

|                             |              | Setup Period          | Reset Timeout Period  |                                          |

|-----------------------------|--------------|-----------------------|-----------------------|------------------------------------------|

| Part Number                 | Part Marking | (t <sub>SETUP</sub> ) | (t <sub>reset</sub> ) | Package                                  |

|                             |              | (s)                   | (s)                   |                                          |

| MIC2782CLYCS <sup>(1)</sup> | -            | 6                     | 0.5                   | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782CMYCS <sup>(1)</sup> | -            | 6                     | 1                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782CRYCS <sup>(1)</sup> | -            | 6                     | 2                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782DLYCS                | UKU          | 8                     | 0.5                   | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782DMYCS <sup>(1)</sup> | -            | 8                     | 1                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782DRYCS <sup>(1)</sup> | -            | 8                     | 2                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782ELYCS                | UKW          | 10                    | 0.5                   | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782EMYCS <sup>(1)</sup> | -            | 10                    | 1                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782ERYCS <sup>(1)</sup> | -            | 10                    | 2                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782FLYCS <sup>(1)</sup> | -            | 12                    | 0.5                   | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782FMYCS <sup>(1)</sup> | -            | 12                    | 1                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

| MIC2782FRYCS <sup>(1)</sup> | -            | 12                    | 2                     | 6-bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP |

#### Notes:

1. Contact Factory for availability.

### **Ordering Guide**

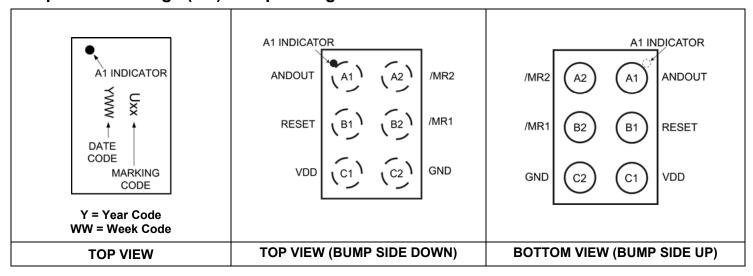

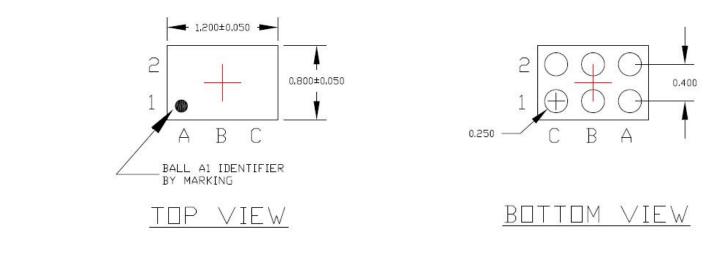

### Chip Scale Package (CS) Bump Configuration

6-Bump, 0.4mm pitch, 0.8mm x 1.2mm WLCSP Package

| Bump<br>Designation | Bump<br>Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                  | ANDOUT       | NMOS Open-Drain output, Active-Low. Asserts low 1.5ms after /MR1 and /MR2 are both asserted low. Connect a resistor greater than $5k\Omega$ from the ANDOUT pin to VDD in order to pull up the ANDOUT output voltage when inactive. No ESD diode from ANDOUT to VDD. Please see the Functional Description and Timing Diagram sections for further details of how the ANDOUT output functions.                     |

| A2                  | /MR2         | Manual Reset Input 2, Active-Low. Internal $65k\Omega$ (typical) Pull-Up Resistor to VDD. Pulling both manual reset inputs low for longer than the setup period causes one RESET output pulse for the reset timeout delay period.                                                                                                                                                                                  |

| B1                  | RESET        | NMOS Open-Drain output, Active-Low. Asserts low after /MR1 and /MR2 have both asserted low for longer than setup period. Connect a resistor greater than $5k\Omega$ from the RESET pin to VDD in order to pull up the RESET output voltage when inactive. No ESD diode from RESET to VDD. Please see the Functional Description and Timing Diagram sections for further details of how the RESET output functions. |

| B2                  | /MR1         | Manual Reset Input 1, Active-Low. Internal $65k\Omega$ (typical) Pull-Up Resistor to VDD. Pulling both manual reset inputs low for longer than the setup period causes one RESET output pulse for the reset timeout delay period.                                                                                                                                                                                  |

| C1                  | VDD          | Supply Voltage. Bypass to ground with minimum 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                     |

| C2                  | GND          | Supply Ground.                                                                                                                                                                                                                                                                                                                                                                                                     |

# Absolute Maximum Ratings (1)

| GND to +6.0V           |

|------------------------|

| .3V to $V_{DD} + 0.3V$ |

| GND - 0.3V to          |

|                        |

| 260°C                  |

| 55°C to +150°C         |

| 2kV                    |

| 200V                   |

|                        |

# Operating Ratings (2)

| Supply Voltage (V <sub>DD</sub> )                               | +1.5V to +5.5V        |

|-----------------------------------------------------------------|-----------------------|

| Input Voltage (V <sub>/MR1</sub> , V <sub>/MR2</sub> )          | 0V to V <sub>DD</sub> |

| NMOS Output Voltage (V <sub>RESET</sub> , V <sub>ANDOUT</sub> ) | 0V to +5.5V           |

| Junction Temperature (T <sub>J</sub> )                          | 40°C to +85°C         |

| Package Thermal Resistance                                      |                       |

| 6-Bump, 0.4mm Pitch WLCSP (θ <sub>JA</sub> )                    | 125°C/W               |

# **Electrical Characteristics** (4)

For typical values,  $V_{DD}$  = 3.3V, /MR1 = /MR2 = Open,  $T_J$  = 25°C, **bold** values indicate -40°C  $\leq T_J \leq +85$ °C; unless noted.

| Parameter                                          | Conditions                                        | Min. | Тур. | Max. | Units |  |

|----------------------------------------------------|---------------------------------------------------|------|------|------|-------|--|

| Power Supply Input                                 |                                                   |      |      |      |       |  |

| Supply Voltage (V <sub>DD</sub> )                  | Reset Output Valid                                | 1.5  |      | 5.5  | V     |  |

|                                                    | V <sub>DD</sub> = 3.3V, /MR1 = /MR2 = VDD         |      | 2.2  | 4.0  |       |  |

| Supply Current (I <sub>DD</sub> )                  | V <sub>DD</sub> = 5.0V, /MR1 = /MR2 = VDD         |      | 3.2  | 5.0  | μΑ    |  |

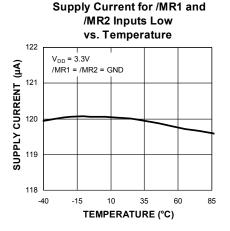

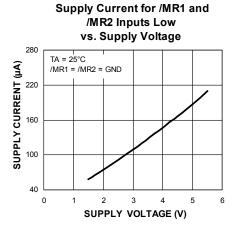

|                                                    | V <sub>DD</sub> = 3.3V, /MR1 = /MR2 = GND         |      | 120  |      |       |  |

| Reset Time                                         |                                                   |      |      |      |       |  |

|                                                    | Ordering Option: C                                | 5.4  | 6    | 6.6  |       |  |

| Setup Period (t <sub>SETUP</sub> )                 | Ordering Option: D                                | 7.2  | 8    | 8.8  | 1 _   |  |

| Setup Feriod (ISETUP)                              | Ordering Option: E                                | 9.0  | 10   | 11   | S     |  |

|                                                    | Ordering Option: F                                | 10.8 | 12   | 13.2 | 1     |  |

|                                                    | Ordering Option: L                                | 0.4  | 0.5  | 0.6  | s     |  |

| Reset Timeout Period (t <sub>RESET</sub> )         | Ordering Option: M                                | 0.9  | 1    | 1.1  |       |  |

|                                                    | Ordering Option: R                                | 1.8  | 2    | 2.2  |       |  |

| ANDOUT Debounce Time (t <sub>DB</sub> )            | $V_{/MR1,2} < (V_{IL} - 100mV)$                   | 1    | 1.5  | 2    | ms    |  |

|                                                    | V <sub>DD</sub> = 4.5V, I <sub>SINK</sub> = 1.6mA |      |      | 0.3  |       |  |

| Output Low Voltage (V <sub>OL</sub> )              | $V_{DD} = 3.3V$ , $I_{SINK} = 1.2mA$              |      |      | 0.3  | V     |  |

|                                                    | $V_{DD} = 1.5V, I_{SINK} = 0.5mA$                 |      |      | 0.3  |       |  |

| Open-Drain Leakage Current (I <sub>LEAKAGE</sub> ) | RESET, ANDOUT Inactive                            | 300  |      | nA   |       |  |

| Open-Drain Leakage Current (ILEAKAGE)              | V <sub>RESET</sub> , V <sub>ANDOUT</sub> = 5.5V   |      |      | 300  |       |  |

| /MR1, /MR2 Input                                   |                                                   |      |      |      |       |  |

| Input High Voltage (V <sub>IH</sub> )              |                                                   | 1.2  |      |      | V     |  |

| Input Low Voltage (V <sub>IL</sub> )               |                                                   |      |      | 0.4  | V     |  |

| Internal Pull-Up Resistance (R <sub>PU</sub> )     | For /MR1, /MR2                                    | 55   | 65   | 75   | kΩ    |  |

#### Notes:

- 1. Exceeding the absolute maximum rating may damage the device.

- 2. The device is not guaranteed to function outside its operating rating.

- 3. Devices are ESD sensitive. Handling precautions recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

- Specification for packaged product only.

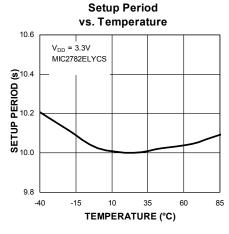

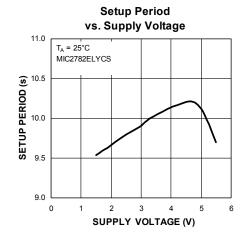

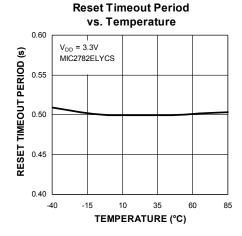

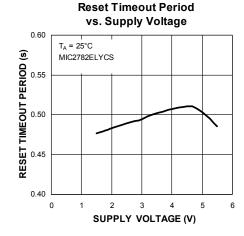

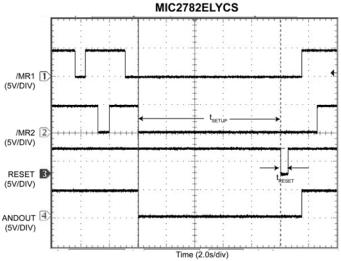

### **Typical Characteristics**

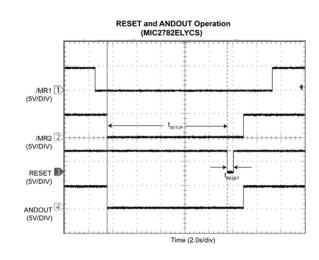

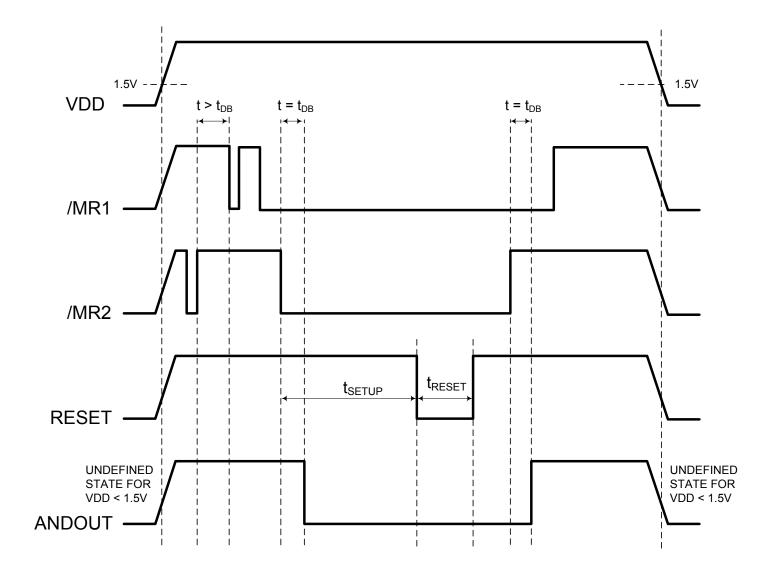

# **Timing Diagram**

# **Functional Diagram**

### **Functional Description**

#### **Design and Product Advantages**

The MIC2782 is a dual push-button input reset IC with extended setup delay times. It is used for generating a hard reset for microcontrollers, PMICs or load disconnect switches. The dual manual reset inputs and long setup delay times help protect against accidental system resets. The fixed Reset Timeout period allows for more predictable phone or Tablet operation during hardware resets. It is used in applications such as smart phones, tablets, personal navigation devices, MP3 players and Set-Top Boxes (STB).

#### **General Functionality**

As shown in Figure 1, if both /MR1 and /MR2 are asserted low for longer than the Setup Period ( $t_{\text{SETUP}}$ ), the RESET output will be asserted (logic-level low) for a Reset Timeout Period ( $t_{\text{RESET}}$ ). During the Setup Period, if either of the /MR1 or /MR2 inputs are de-asserted high, then the Setup Period timer will be reset. To assert the RESET output low again, both the /MR1 and /MR2 inputs will have to be asserted low together for the full duration of the Setup period.

If both /MR1 and /MR2 are asserted low for longer than the Debounce Time ( $t_{DB}$ ), then the ANDOUT output will be asserted, (logic-level low). ANDOUT will remain asserted low as long as both the /MR1 and /MR2 inputs are asserted low. If either the /MR1 or /MR2 are deasserted for longer that the Debounce Time ( $t_{DB}$ ), then the ANDOUT output will de-assert high.

Figure 1. Manual Reset Function

Keeping both manual reset inputs low for a longer time does not generate additional RESET output pulses. Deasserting either manual reset input during the RESET pulse duration, will not reset the Setup Timer. After the RESET pin has de-asserted high, both the manual reset inputs must be held high for more than a Debounce Time to reset the Setup Timer.

**ANDOUT Debounce Time** is a de-glitch time, typically 1.5ms, that senses the asserting of both manual reset inputs low together. A de-glitch time is needed if the manual reset inputs come from noisy push-button sources. If either manual reset inputs are asserted (or de-asserted) for less than a Debounce Time, the ANDOUT output will not respond.

#### **Dual Manual Reset Inputs (/MR1, /MR2)**

The /MR1, /MR2 are active-low manual inputs that have integrated  $65k\Omega$  pull-up resistors to the VDD power supply. If both inputs are asserted (logic-level low) for a Setup Period ( $t_{SETUP}$ ), only one reset pulse, of width  $t_{RESET}$ , is generated. The behavior of the RESET and ANDOUT outputs is independent of the order in which the /MR1, /MR2 inputs are driven low. The MIC2782 consumes only  $2\mu A$  when /MR1 and /MR2 manual inputs are de-asserted (logic-level high) together. Current consumption is typically  $120\mu A$  when both manual inputs are asserted low together and  $55\mu A$  when only one of the manual inputs is asserted low while the other manual input is de-asserted high.

#### **Outputs (RESET and ANDOUT)**

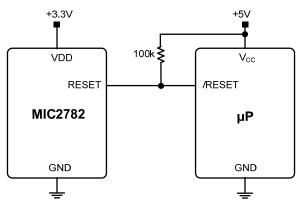

The RESET and ANDOUT outputs are simple opendrain N-channel MOSFET structures that require a pull-up resistor. For most applications, the pull-up voltage will be the same as the power supply that supplies  $V_{DD}$  to the MIC2782. As shown in Figure 2, it is possible to tie this resistor to some other voltage, other than  $V_{DD}$ , thus enabling level-shifting of the RESET or ANDOUT outputs. The pull-up voltage must be limited to 5.5V to avoid damaging the MIC2782. The pull-up resistor must be small enough to supply current to the inputs and leakage paths that are driven by the RESET or ANDOUT outputs. A recommended value is 100k $\Omega$ .

Since the RESET and ANDOUT outputs are open-drain, several reset sources can be wire-ORed, in parallel, to allow resets from multiple sources.

Figure 2. MIC2782 Used in Multiple Supply System

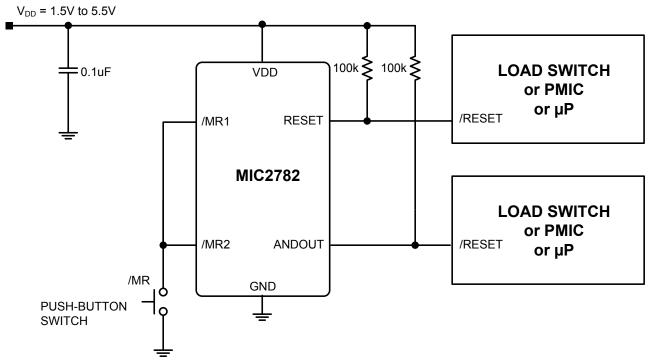

#### **Bypass Capacitor from VDD to GND**

A  $0.1\mu F$  input bypass capacitor must be placed from VDD (Pin C1) to GND (Pin C2).

### **Typical Applications**

Figure 3. Single Button application for MIC2782 used for Microcontroller Reset

Figure 4. Dual Button application for MIC2782 used for Microcontroller Reset

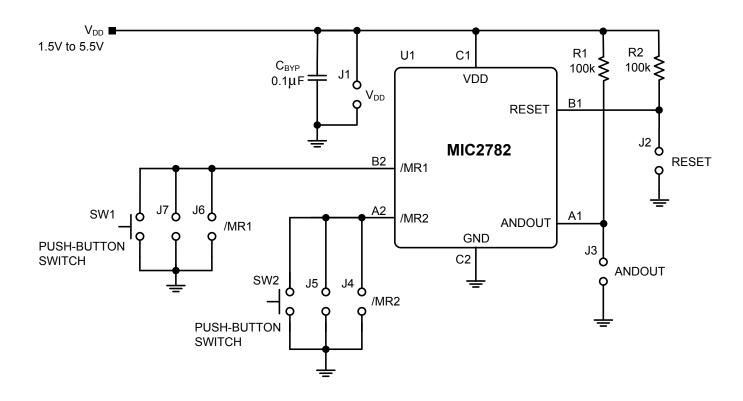

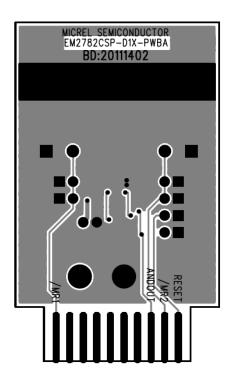

# **Evaluation Board Schematic**

#### **Bill of Materials**

| Item   | Part Number                       | Manufacturer | Description                     | Qty. |

|--------|-----------------------------------|--------------|---------------------------------|------|

| C1     | GRM188R71C104KA01D <sup>(1)</sup> | Murata       | 0.1μF, 16V capacitor, X7R, 0603 | 1    |

| R1, R2 | CRCW0603100KJNEA <sup>(2)</sup>   | Vishay       | 100k, 5% resistor, 0603         | 2    |

| U1     | MIC2782ELYCS <sup>(3)</sup>       | Micrel, Inc. | Dual-Input Push Button Reset IC | 1    |

#### Notes:

1. Murata Tel: www.murata.com.

2. Vishay Tel: www.vishay.com.

3. Micrel, Inc.: www.micrel.com.

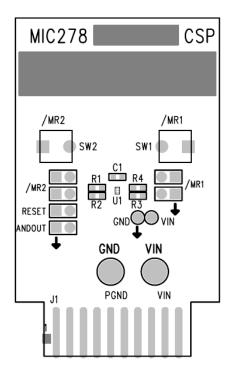

# **PCB Layout Recommendations**

**Top Silkscreen**

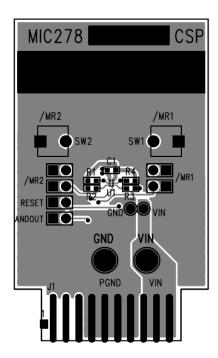

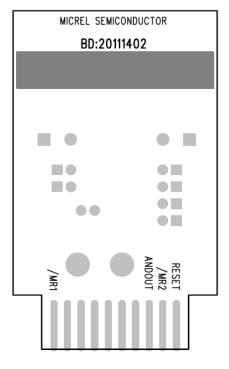

# **PCB Layout Recommendations (Continued)**

Copper Layer 1 (Top Layer)

Copper Layer 2 (Bottom Layer)

# **PCB Layout Recommendations (Continued)**

**Bottom Silkscreen**

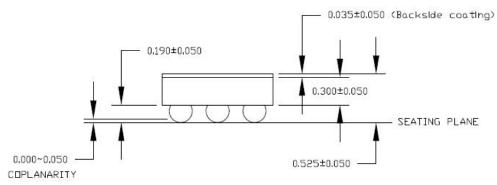

# **Package Information**

SIDE VIEW

6-Bump, 0.4mm Pitch 0.8mm x 1.2mm WLCSP (CS) Package Drawing

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2012 Micrel, Incorporated.

January 2012 16 M9999-010912-A

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

# Click to view similar products for micrel manufacturer:

Other Similar products are found below:

MIC2544A-1YMM MIC2774N-23YM5 TR MIC2920A-12WT MIC4423YWM DSC1103BI2-150.0000 MIC2544A-2YMM MIC2551AYTS

MIC4605-2YM EV MICUSB DONGLE EV KSZ8842-16MVL DSC1001BE1-025.0000 MIC2580A-1.0YTS MIC3172YN DSC-PROGTIMEFLASH-2520 SY10ELT22LZG KSZ9692PB-EVAL KSZ8721BI KSZ8873MLL-EVAL KSZ8993 KSZ9031MNX-EVAL

SY100ELT22LZG MIC2039-1AYM6 EV MIC23050-SYML TR MIC24055YJL EV MIC49200WR SY69952ZH SY88982LMG

SY58019UMG MIC29150-5.0WU MIC29752WWT KSZ8081RNB-EVAL KSZ8852HLE-EVAL KSZ8863FLL-EVAL KSZ8873MML

MIC2076A-2YM MIC2207YML EV MIC24051YJL EV MIC45212-1YMP EV SY89840UMG MIC4605-1YMT EV MICRF219A-315 EV

DSC1001DL5-027.0000T MIC2941AWU TR KSZ8041NL-EVAL KSZ8091RNB-EVAL KSZ8863MLLI MIC5365-3.0YC5 TR MIC21762YMM 5A EV KSZ8995FQI MIC23250-S4YMT EV