#### General Description

The MAX3325 integrates a two-transmitter, two-receiver RS-232 transceiver with an LCD supply plus temperature-compensated contrast control. It is intended for small 3V instruments requiring a 5V supply for either logic or an LCD display, an adjustable bias signal for contrast, LCD temperature compensation, and an RS-232 interface for serial communications.

The 5V supply is a regulated charge pump followed by a low-dropout (LDO) linear regulator capable of supplying 11mA for the 5V LCD power.

The MAX3325 has an internal 6-bit digital-to-analog converter (DAC) providing 64 contrast levels, plus an internal temperature sensor that compensates the LCD's contrast for changes in ambient temperature. The LCD contrast can be designed for any voltage range from -5V to +2V.

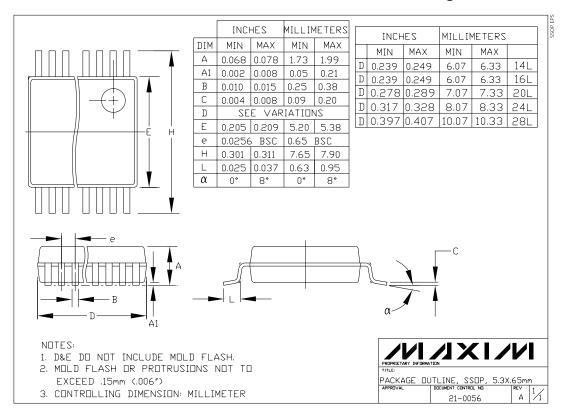

The MAX3325's 250kbps RS-232 transceiver meets all EIA-232E specifications with input voltages from +3.0V to +3.6V. Both the RS-232 section and the LCD supply circuitry can be independently placed in shutdown, tailoring power consumption for battery-powered equipment. The MAX3325 is available in 28-pin SSOP and narrow DIP packages.

| PART       | TEMP. RANGE    | PIN-PACKAGE           |

|------------|----------------|-----------------------|

| MAX3325CAI | 0°C to +70°C   | 28 SSOP               |

| MAX3325CNI | 0°C to +70°C   | 28 Narrow Plastic DIP |

| MAX3325EAI | -40°C to +85°C | 28 SSOP               |

| MAX3325ENI | -40°C to +85°C | 28 Narrow Plastic DIP |

### **Applications**

PDAs and Palmtop Computers Handy Terminals **GPS** Receivers Hand-Held Medical Equipment Industrial Test Equipment

## **Features**

- ♦ +3.0V to +3.6V Single-Supply Operation

- ♦ Provides 5.0V Regulated Output at 11mA in 3V Systems

- ♦ 6-Bit DAC with Up/Down Interface for LCD **Contrast Adjustment**

- ♦ Selectable Positive or Negative LCD Bias

- Meets EIA-232E Specifications at 250kbps— Guaranteed

- ♦ 1µA Shutdown Mode

- ♦ Uses Small 0.22µF Capacitors—No Inductors Required

- Temperature Sensor for LCD Contrast Compensation

- ♦ Simple, Flexible Design Procedure for a Broad Range of LCD Displays

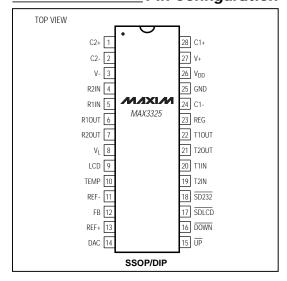

### Pin Configuration

Ordering Information

Typical Operating Circuit appears at end of data sheet.

Maxim Integrated Products

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> , V <sub>L</sub> to GND |                                 |

|-----------------------------------------|---------------------------------|

| LCD, REF-, TEMP to GND                  | 6V to (V <sub>DD</sub> + 0.3V)  |

| V+ to GND (Note 1)                      | 0.3V to +7V                     |

| V- to GND (Note 1)                      | +0.3V to -7V                    |

| V+ to  V-  (Note 1)                     | +13V                            |

| REF+, FB, R_OUT to GND                  | 0.3V to (V <sub>L</sub> + 0.3V) |

| Input Voltages                          |                                 |

| T_OUT, SDLCD, SD232, UP, DOWN to        | GND0.3V to +6V                  |

| R_IN to GND                             | ±25V                            |

| Output Voltages                         |                                 |

| T OUT to GND                            | ±13V                            |

| R_OUT to GND                            | $0.3V$ to $(V_1 + 0.3V)$        |

| REG to GND                              | 0.3V to +6V                     |

|                                         |                                 |

| Short-Circuit Duration (T_OUT, REF+, REF-)Continuous Continuous Output Current |

|--------------------------------------------------------------------------------|

| REG                                                                            |

| LCD40mA                                                                        |

| Continuous Power Dissipation                                                   |

| 28-Pin SSOP (derate 9.52mW/°C above +70°C)762mW                                |

| 28-Pin NDIP (derate 14.3mW/°C above +70°C)1143mW                               |

| Operating Temperature Range                                                    |

| MAX3325C_I0°C to +70°C                                                         |

| MAX3325E_I40°C to +85°C                                                        |

| Storage Temperature Range65°C to +150°C                                        |

| Lead Temperature (soldering, 10sec)+300°C                                      |

|                                                                                |

Note 1: V+ and V- can have maximum magnitudes of +7V, but their absolute difference cannot exceed 13V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

( $V_{DD}$  = +3.0V to +3.6V,  $V_{L}$  = +3.3V, circuit and components of Figure 1,  $T_{A}$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $V_{DD}$  = +3.3V,  $T_{A}$  = +25°C.)

| PARAMETER                               | COND                                                          | CONDITIONS                                                                                                               |      |      | MAX  | UNITS |

|-----------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| DC CHARACTERISTICS                      |                                                               |                                                                                                                          | l    |      |      |       |

| V <sub>DD</sub> Supply Current          | No load, V <sub>DD</sub> = V <sub>L</sub> = 3.3V,             | T <sub>A</sub> = +25°C                                                                                                   |      | 2    | 4    | mA    |

| V <sub>L</sub> Supply Current           | No load, V <sub>DD</sub> = V <sub>L</sub> = 3.3V,             | T <sub>A</sub> = +25°C                                                                                                   |      | 0.5  | 10   | μΑ    |

| V <sub>DD</sub> Shutdown Supply Current |                                                               | $\overline{SD232}$ , $\overline{SDLCD}$ = GND; all input pins = GND or $V_{DD}$ ; $V_{DD}$ = $V_L$ = 3.3V; $T_A$ = +25°C |      |      | 10   | μA    |

| DIGITAL-TO-ANALOG CONVER                | TER                                                           |                                                                                                                          |      |      |      |       |

| Resolution                              | Guaranteed monotonic                                          |                                                                                                                          |      | 6    |      | Bits  |

| Full-Scale Voltage                      | No load                                                       |                                                                                                                          | 1.13 | 1.2  | 1.27 | V     |

| Zero-Scale Voltage                      | No load                                                       |                                                                                                                          | -15  | 0    | 10   | mV    |

| Output Impedance                        | 0 < V <sub>DAC</sub> < V <sub>REF</sub> +, I <sub>DAC</sub> s | ≤ 10µA                                                                                                                   | 35   | 50   | 65   | kΩ    |

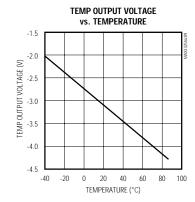

| TEMPERATURE SENSOR                      |                                                               |                                                                                                                          |      |      |      |       |

| TEMP Output                             | T <sub>A</sub> = +25°C                                        | TA = +25°C                                                                                                               |      | -3.2 |      | V     |

| TEMP Voltage Temperature<br>Coefficient | I <sub>TEMP</sub> < 22μA                                      |                                                                                                                          |      | -18  |      | mV/°C |

| POSITIVE LINEAR REGULATOR               | \<br>\                                                        |                                                                                                                          | l    |      |      |       |

| REG Output Voltage                      | 1 transmitter loaded with                                     | V <sub>CC</sub> ≥ 3.15V, I <sub>REG</sub> = 0 to 11mA                                                                    | 4.7  | 5    | 5.3  | V     |

| REG Output voltage                      | 5kΩ, TA = +25°C                                               | V <sub>CC</sub> ≥ 3.0V, I <sub>REG</sub> = 0 to 7mA                                                                      |      | 5    |      | V     |

| Line Regulation                         | 3V < V <sub>DD</sub> < 3.6V                                   |                                                                                                                          |      | 6    | 50   | mV    |

| Short-Circuit Current                   |                                                               |                                                                                                                          |      | 50   |      | mA    |

| NEGATIVE LINEAR REGULATO                | R—LCD BIAS                                                    |                                                                                                                          | •    |      |      |       |

| Feedback Regulation Point               |                                                               |                                                                                                                          | -20  | 0    | 20   | mV    |

| Input Leakage Current (Note 2)          | V <sub>FB</sub> = 0, CMOS input                               | V <sub>FB</sub> = 0, CMOS input                                                                                          |      | 0    | 10   | nA    |

| LCD Load Regulation (Note 3)            | V <sub>LCD</sub> = -4.0V, load = 0 to                         | V <sub>LCD</sub> = -4.0V, load = 0 to -3mA                                                                               |      | 20   |      | mV    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +3.0V \text{ to } +3.6V, V_L = +3.3V, \text{ circuit and components of Figure 1, T}_A = T_{MIN} \text{ to T}_{MAX}, \text{ unless otherwise noted. Typical values are at V}_{DD} = +3.3V, T}_A = +25^{\circ}\text{C.})$

| PARAMETER                 | CONDITIONS                                                              | MIN                  | TYP   | MAX   | UNITS |

|---------------------------|-------------------------------------------------------------------------|----------------------|-------|-------|-------|

| LCD Line Regulation       | $3V < V_{DD} < 3.6V, V_{LCD} = -4.0V$                                   |                      | 10    |       | mV    |

| LCD Adjustment Range      | Load = -3mA                                                             | -5                   |       | +2    | V     |

| POSITIVE REFERENCE VOLT   | TAGE                                                                    | '                    |       |       |       |

| Output Voltage            | $R_{REF}+=10k\Omega$                                                    | 1.16                 | 1.21  | 1.26  | V     |

| Load Regulation           | Load = 12µA to 62µA (sourcing current)                                  |                      | 4     |       | mV    |

| Short-Circuit Current     |                                                                         |                      | 5     |       | mA    |

| NEGATIVE REFERENCE VOL    | TAGE                                                                    | <u>'</u>             |       |       |       |

| Output Voltage            | No load                                                                 | -1.14                | -1.21 | -1.28 | V     |

| Load Regulation           | Load = 0 to 50µA (sinking current)                                      |                      | 35    |       | mV    |

| Short-Circuit Current     |                                                                         |                      | 0.125 |       | mA    |

| LOGIC INPUTS (SD232, SDLC | D, T1IN, T2IN, UP, DOWN)                                                | •                    |       |       |       |

| Logic Threshold High      |                                                                         | 2                    |       |       | V     |

| Logic Threshold Low       |                                                                         |                      |       | 0.8   | V     |

| Input Current             | V <sub>IN</sub> = GND or V <sub>DD</sub>                                | -1                   |       | 1     | μΑ    |

| RECEIVER OUTPUTS          |                                                                         | '                    |       |       |       |

| Output Voltage Low        | ISINK = 1.6mA                                                           |                      |       | 0.4   | V     |

| Output Voltage High       | ISOURCE = 1.0mA                                                         | 0.8 • V <sub>L</sub> |       |       | V     |

| RECEIVER INPUTS           |                                                                         | •                    |       |       |       |

| Input Voltage Range       |                                                                         | -25                  |       | +25   | V     |

| Input Threshold Low       | $T_A = +25^{\circ}C$ , $V_{DD} = 3.3V$                                  | 0.6                  |       |       | V     |

| Input Threshold High      | $T_A = +25^{\circ}C$ , $V_{DD} = 3.3V$                                  |                      |       | 2.4   | V     |

| Input Hysteresis          |                                                                         |                      | 0.3   |       | V     |

| Input Resistance          | -15V < V <sub>R_IN</sub> < +15V, T <sub>A</sub> = +25°C                 | 3                    | 5     | 7     | kΩ    |

| TRANSMITTER OUTPUTS       |                                                                         | '                    |       |       |       |

| Output Voltage Swing      | All outputs loaded with 3kΩ to ground                                   | ±5                   | ±5.4  |       | V     |

| Output Resistance         | $V_{DD} = V_{L} = V_{+} = V_{-} = 0$ , $V_{OUT} = \pm 2V$               | 300                  | 10M   |       | Ω     |

| Short-Circuit Current     |                                                                         |                      | ±35   | ±60   | mA    |

| Output Leakage Current    | $V_{DD} = 0$ or 3V to 3.6V, $V_{OUT} = \pm 12V$ , transmitters disabled |                      |       | ±25   | μΑ    |

#### **TIMING CHARACTERISTICS**

$(V_{DD} = +3.0 V \text{ to } +3.6 V, V_{L} = +3.3 V, \text{ circuit and components of Figure 1, } T_{A} = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = +3.3 V, T_{A} = +25 ^{\circ} C.)$

| PARAMETER                   | SYMBOL           | CONDITIONS                                                                                                                           | MIN | TYP | MAX | UNITS |

|-----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Maximum Data Rate           |                  | $R_L = 3k\Omega$ , $C_L = 1000pF$ , one transmitter switching                                                                        | 250 |     |     | kbps  |

| Receiver Propagation Delay  | tphl             | Receiver input to receiver output,                                                                                                   |     | 300 |     | ns    |

| Receiver Fropagation Delay  | t <sub>PLH</sub> | C <sub>L</sub> = 150pF                                                                                                               |     | 300 |     | 1 115 |

| Receiver Skew               | tplh -tphl       |                                                                                                                                      |     | 300 |     | ns    |

| Transmitter Skew            | tplh -tphl       |                                                                                                                                      |     | 200 |     | ns    |

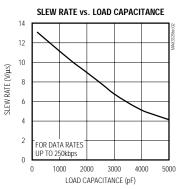

| Transition-Region Slew Rate |                  | $V_{DD}$ = 3.3V, $T_A$ = +25°C, $R_L$ = 3k $\Omega$ to 7k $\Omega$ , $C_L$ = 150pF to 1000pF, measured from +3V to -3V or -3V to +3V | 6   |     | 30  | V/µs  |

Note 2: Guaranteed by design and not production tested.

Note 3: No load on REG or transmitter outputs.

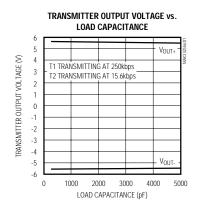

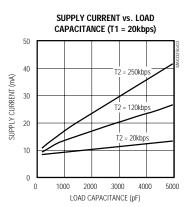

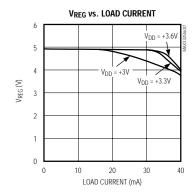

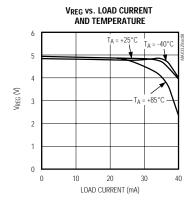

### Typical Operating Characteristics

$(V_{DD} = V_L = +3.3V, \text{ circuit and components of Figure 1, all transmitters loaded with <math>3k\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### Typical Operating Characteristics (continued)

$(V_{DD} = V_L = +3.3V, \text{ circuit and components of Figure 1}, \text{ all transmitters loaded with } 3k\Omega \text{ and } C_L, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

### Pin Description

| PIN    | NAME            | FUNCTION                                                                                                                                                                                     |

|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | C2+             | Positive Terminal of Voltage-Inverting Charge-Pump Capacitor. Connect C2+ to C2- with a 0.22µF capacitor.                                                                                    |

| 2      | C2-             | Negative Terminal of Voltage-Inverting Charge-Pump Capacitor. Connect C2- to C2+ with a 0.22µF capacitor.                                                                                    |

| 3      | V-              | Output of Negative Charge Pump. Bypass V- to GND with a 0.22µF capacitor.                                                                                                                    |

| 4, 5   | R_IN            | RS-232 Receiver Inputs                                                                                                                                                                       |

| 6, 7   | R_OUT           | TTL/CMOS Receiver Outputs                                                                                                                                                                    |

| 8      | VL              | Supply Input for Receiver Outputs. Connect V <sub>L</sub> to the system logic supply voltage.                                                                                                |

| 9      | LCD             | Output of Negative Regulator. Connect LCD to FB with a series resistor. Bypass with a 0.47µF capacitor to GND.                                                                               |

| 10     | TEMP            | Output of Temperature Sensor. Connect TEMP to FB with a series resistor to compensate LCD contrast for changing temperature. Bypass TEMP with a 0.22µF capacitor to GND.                     |

| 11     | REF-            | Output of Negative Reference, -1.2V. Bypass REF- with a 0.22µF capacitor to GND.                                                                                                             |

| 12     | FB              | Feedback Input for Negative Regulator. Regulates when FB is at zero (0).                                                                                                                     |

| 13     | REF+            | Output of Positive Reference, +1.2V. Bypass REF+ with a 0.22µF capacitor to GND.                                                                                                             |

| 14     | DAC             | Output of Internal 6-Bit DAC. Connect DAC to FB with a series resistor to adjust LCD voltage.                                                                                                |

| 15     | ŪP              | DAC Adjust Input. A falling edge on UP increments the internal 6-bit DAC counter.                                                                                                            |

| 16     | DOWN            | DAC Adjust Input. A falling edge on DOWN decrements the internal 6-bit DAC counter.                                                                                                          |

| 17     | SDLCD           | Active-Low Shutdown-Control Input for Both Regulators, References, DAC, and Temperature Sensors. Drive SDLCD low to disable all analog circuitry. Drive high to enable the analog circuitry. |

| 18     | SD232           | Active-Low Shutdown-Control Input for Transmitter Outputs. Drive \$\overline{\text{SD232}}\$ low to disable the RS-232 transmitters. Drive high to enable the transmitters.                  |

| 19, 20 | T_IN            | TTL/CMOS Transmitter Inputs                                                                                                                                                                  |

| 21, 22 | T_OUT           | RS-232 Transmitter Outputs                                                                                                                                                                   |

| 23     | REG             | Output of Positive Regulator. Bypass REG with a 4.7µF capacitor to GND.                                                                                                                      |

| 24     | C1-             | Negative Terminal of Voltage-Doubling Charge-Pump Capacitor. Connect C1- to C1+ with a 0.22μF capacitor.                                                                                     |

| 25     | GND             | Ground                                                                                                                                                                                       |

| 26     | V <sub>DD</sub> | +3.0V to +3.6V Supply Voltage. Bypass V <sub>DD</sub> with a 0.22µF capacitor to GND.                                                                                                        |

| 27     | V+              | Output of Positive Charge Pump. Bypass V+ to V <sub>DD</sub> with a 0.22µF capacitor.                                                                                                        |

| 28     | C1+             | Positive Terminal of Voltage-Doubling Charge-Pump Capacitor. Connect C1+ to C1- with a 0.22µF capacitor.                                                                                     |

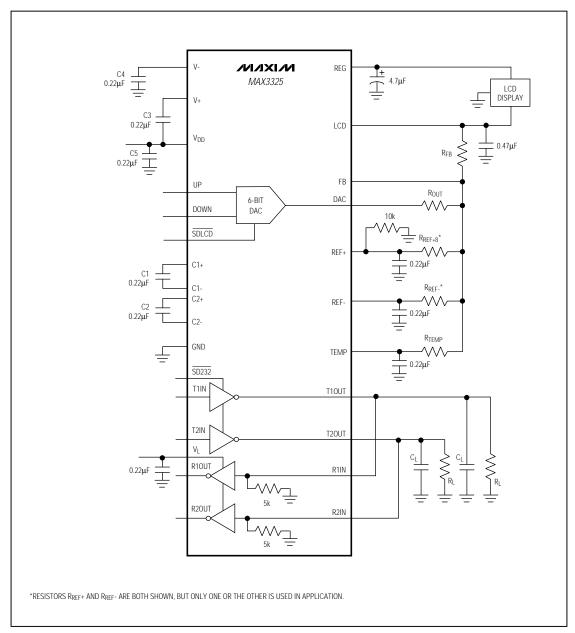

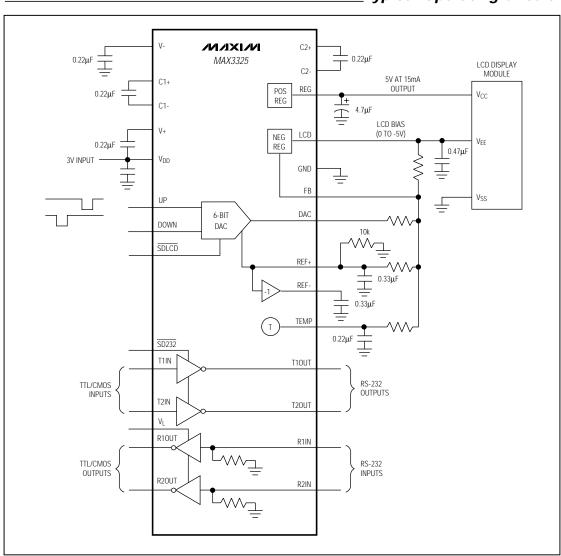

Figure 1. Application Circuit

NIXIN

#### **Detailed Description**

#### **Dual Charge-Pump Voltage Converter**

The MAX3325's internal power supply consists of a regulated dual charge pump that provides output voltages of +5.5V (doubling charge pump) and -5.5V (inverting charge pump) over the 3.0V to 3.6V Vpp range. The charge pump operates in discontinuous mode; if the output voltages are less than 5.5V, the charge pump is enabled; if the output voltages exceed 5.5V, the charge pump is disabled. Each charge pump requires a flying capacitor (C1, C2) and a reservoir capacitor (C3, C4) to generate the V+ and V- supplies (Figure 1).

#### **RS-232 Transmitters**

The transmitters are inverting level translators that convert logic levels to  $\pm 5.0 V$  EIA/TIA-232 levels. The MAX3325 transmitters guarantee a 250kbps data rate with worst-case loads of 3k $\Omega$  in parallel with 1000pF, providing compatibility with PC-to-PC communication software (such as LapLink^TM).

The MAX3325's transmitters are disabled and the outputs are forced into a high-impedance state when the RS-232 circuitry is in shutdown ( $\overline{\text{SD232}}$  = low). The MAX3325 permits the outputs to be driven up to ±13V in shutdown.

The transmitter inputs do not have pull-up resistors. Connect unused inputs to GND or VDD.

#### **RS-232 Receivers**

The receivers convert RS-232 signals to logic output levels. The  $V_L$  pin controls the logic output high voltage. The receiver outputs are always active, regardless of the shutdown state.

#### Positive Voltage Regulator

The MAX3325 has a regulated +5V output suitable for powering +5V LCD modules or other circuits. The output of the boost charge pump is regulated with an LDO linear regulator. The REG output sources up to 11mA of current to external circuitry.

#### Adjustable LCD Supply

The LCD output provides a flexible output voltage to adjust the contrast of LCD modules. The output voltage range is determined by the external circuitry connected to LCD, FB, DAC, REF+ (or REF-, depending on contrast polarity). Additionally, the TEMP output can be used to automatically compensate the contrast adjustment for temperature variance.

The LCD output is a linear regulator powered by the negative charge pump. It is capable of sinking up to 3mA of current. Although the LCD regulator can be adjusted to LapLink is a trademark of Traveling Software.

positive voltages, it is not capable of sourcing current. A minimum output current of 100µA is required.

#### 6-Rit DAC

The MAX3325's DAC output is an unbuffered inverted R2R structure with an output voltage range of 0 to  $\pm 1.2V$ . The DAC output impedance is typically  $50k\Omega$ , and can be connected through a series resistor to the FB input of the LCD regulator. An internal power-on reset circuit sets the DAC to midscale on power-up.

#### **DAC Control Inputs**

The DAC code is controlled by  $\overline{\text{UP}}$  and  $\overline{\text{DOWN}}$  to adjust the contrast of the LCD module. These inputs are intended to interface to digital signals, but do not include debounce circuitry. See the *Applications* section. See Table 1 for the truth table.

#### Temperature Compensation

The MAX3325's TEMP output is used to minimize deviation in LCD contrast level due to temperature changes. The TEMP output is capable of sinking or sourcing up to  $22\mu A$  to the external resistor network.

#### Shutdown Mode

Supply current falls below  $1\mu A$  in shutdown mode (SDLCD = SD232 = low). When shut down, the device's charge pumps are shut off, V+ is pulled down to VDD, V- is pulled to ground, and the transmitter outputs are disabled (high impedance). The LCD section is also powered down. The REG, LCD, and both reference outputs become high impedance. The time required to exit shutdown is typically  $100\mu s$ , as shown in the *Typical Operating Characteristics*. However, the TEMP output requires 50ms to fully stabilize. Connect SDLCD and SD232 to VDD if the shutdown mode is not used. See Table 2.

Table 1. DAC Truth Table

| ŪP           | DOWN     | FUNCTION                        |

|--------------|----------|---------------------------------|

| 0            | 0        | DAC set to midscale             |

| 1            | <b>\</b> | DAC register decrements 1 count |

| $\downarrow$ | 1        | DAC register increments 1 count |

#### **Table 2. Shutdown Truth Table**

| SDLCD | SD232 | FUNCTION                         |

|-------|-------|----------------------------------|

| 0     | 0     | Low-power shutdown mode          |

| 1     | Х     | LCD bias and REG outputs enabled |

| Х     | 1     | RS-232 transmitters enabled      |

X = Don't care

3 \_\_\_\_\_\_ MAXIM

### Applications Information

#### **Capacitor Selection**

The capacitor type used for C1-C4 is not critical for proper operation; polarized or nonpolarized capacitors can be used. Ceramic chip capacitors with an X7R dielectric provide the best combination of performance, cost, and size. The charge pump requires 0.22µF capacitors for 3.3V operation. Do not use values smaller than those listed in Figure 1. Increasing the capacitor values (e.g., by a factor of 2) reduces ripple on the transmitter outputs, slightly reduces power consumption, and increases the available output current from VREG and VLCD. C2, C3, and C4 can be increased without changing C1's value. However, do not increase C1 without also increasing the values of C2, C3, C4, and C5 to maintain the proper ratios.

When using the minimum required capacitor values, make sure the capacitor value does not degrade excessively with temperature or voltage. This is typical of Y5V and Z5U dielectric ceramic capacitors. If in doubt, use capacitors with a larger nominal value, or specify X7R dielectric. The capacitor's equivalent series resistance (ESR), which usually rises at low temperatures, influences the amount of ripple on V+ and V-.

#### **Power-Supply Decoupling**

In most circumstances, a 0.22µF VDD bypass capacitor (C5) is adequate. Choosing larger values for C5 increases performance and decreases the induced ripple on the VDD supply line. Note that capacitor C2, connected to V+, is returned to C5. This connection also improves the performance of the MAX3325. Locate all bypass capacitors as close as possible to the IC. Keep metal traces as wide as possible. Return all capacitor ground connections directly to a solid-copper ground plane.

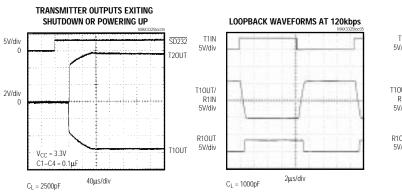

## Transmitter Outputs when Exiting Shutdown

The Typical Operating Characteristics show the MAX3325 transmitter outputs when exiting shutdown mode. As they become active, the two transmitter outputs are shown going to opposite RS-232 levels (one transmitter input is high, the other is low). Each transmitter is loaded with  $3k\Omega$  in parallel with 2500pF. The transmitter outputs display no ringing or undesirable transients as they come out of shutdown. Note that the transmitters are enabled only when the magnitude of V-exceeds approximately -3V.

#### High Data Rates

The MAX3325 maintains the RS-232 ±5.0V minimum transmitter output voltage even at high data rates.

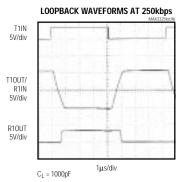

Figure 1 shows a transmitter loopback test circuit. The *Typical Operating Characteristics* show loopback test results at 120kbps and 250kbps. For 120kbps, all transmitters were driven simultaneously at 120kbps into RS-232 loads in parallel with 1000pF. For 250kbps, a single transmitter was driven at 250kbps, and all transmitters were loaded with an RS-232 receiver in parallel with 1000pF.

#### Interconnection with Lower Logic Voltages

The MAX3325 provides a separate supply for the logic interface to optimize input and output levels. Connect V<sub>L</sub> to the system's logic supply voltage, and bypass it with a 0.1µF capacitor to GND. If the logic supply is the same as V<sub>DD</sub>, connect V<sub>L</sub> to V<sub>DD</sub>. The V<sub>L</sub> pin can be operated from +1.8V to +5.0V to accommodate various logic levels.

#### Setting V<sub>LCD</sub> Output Voltage

The LCD output can be configured in a variety of ways to suit the requirements of the LCD display. First, determine the nominal voltage range that the LCD will require for adequate contrast adjustment. If the display requires temperature compensation for contrast, include the TEMP output in all calculations. The output voltage is defined by:

$$V_{LCD} = -R_{FB} \left( \frac{\text{code} \cdot V_{DAC}}{\left(R_{O} + R_{DAC}\right)} + \frac{V_{REF+}}{R_{REF+}} + \frac{V_{REF-}}{R_{REF-}} + \frac{-3.3V \cdot V_{TEMP} \cdot (T \cdot 25^{\circ}C)}{R_{TEMP}} \right)$$

where code is the current digital code in the DAC, and Ro is the nominal DAC output impedance ( $50k\Omega$ ). The other terms in the equation are due to external resistances connected to the indicated pins. A spreadsheet program is an excellent tool for helping to select components and evaluate their effect on the output voltage range.

Although the above equation has terms for both REF+ and REF- offset resistors, only one or the other is used.

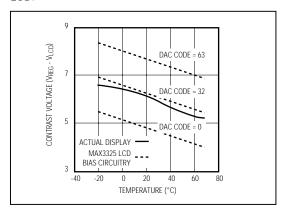

#### Design Example

The first step in designing for a particular display is to obtain the manufacturer's device specifications for the nominal values as well as the temperature characteristics. For example, consider the Optrex DMC series of dot matrix LCD modules. The manufacturer specifies a nominal contrast bias voltage of 6V at +25°C, where bias voltage is VREG - VLCD. The temperature coefficient needed

to maintain the nominal contrast is  $-16\text{mV}/^{\circ}\text{C}$ . In this case, data for a spread of nominal bias voltages is not available, so a range of  $\pm 1\text{V}$  is chosen by experimentation.

#### Feedback Resistor (RFB)

The first step in designing the MAX3325 LCD bias is to select a feedback resistor. This can be arbitrary, but values between  $220k\Omega$  to  $1M\Omega$  are a good starting point. We will choose  $330k\Omega$ . If the design can't reach its target range in later calculations, the feedback resistor can be adjusted accordingly.

#### DAC Output Resistor (ROUT)

Given the above criterion of a  $\pm 1V$  output range, the DAC's output should be multiplied by the ratio of the desired output swing ( $\pm 1V$ ) divided by the available output from the DAC (0 to 1.2V). Assuming that we've used a  $330k\Omega$  feedback resistor, this corresponds to a total DAC resistance of  $200k\Omega$ . Because the DAC has an intrinsic output impedance of  $50k\Omega$ , set ROUT to  $200k\Omega - 50k\Omega = 150k\Omega$ .

#### Temperature Compensation Resistor (RTEMP)

Next, the temperature compensation resistor is selected. Because the MAX3325 regulates FB to virtual ground, adding or removing the remaining resistors in this design does not affect the transfer function set in the previous section. The TEMP output has a temperature coefficient of -17.5mV per °C, and the LCD's is -16mV/°C. To scale these two values, multiply the feedback resistor (330k $\Omega$ ) by the ratio of the TEMP coefficient divided by the display's coefficient. For this example, the result is 360k $\Omega$ .

#### Reference Resistance (RREF )

To complete the design, the DC output is biased to the final desired value at DAC midscale. Because the previous steps concentrated on the transfer function only, we now have a large offset of +1.94V. This is calculated from the entire equation, where the reference resistors are assumed to be infinite, the DAC voltage is +0.6V, and VTEMP is -3.2V. Connecting a 130k $\Omega$  resistor from REF+ to FB forces VLCD to -1.1V, resulting in a nominal contrast voltage (VREG - VLCD) of +6.1V. This is close to the target value of +6V.

#### Actual Performance

The graph in Figure 2 shows the actual LCD display's data curve, along with the MAX3325's performance with various DAC codes. Note that changing the DAC code does not affect the slope of the temperature compensation. If a wider scale of contrast adjustments is desired, change the DAC output resistor, and readjust the offset voltage.

#### Interfacing to the UP and DOWN Inputs

The \$\overline{UP}\$ and \$\overline{DOWN}\$ inputs to the MAX3325 are edge-triggered digital inputs. For proper operation, the signals must be standard logic signals. Mechanical switch outputs, (toggle or membrane types) are unsuitable and require proper debouncing before connecting to the MAX3325. The best solution is to use the MAX6817 dual switch debouncer. This sends the correct signal levels to the \$\overline{UP}\$ and \$\overline{DOWN}\$ inputs, and provides a robust interface to the switch inputs. The \$\overline{UP}\$ and \$\overline{DOWN}\$ inputs can be driven directly from a microprocessor.

### System Considerations

Because the MAX3325 is the temperature transducer for the LCD bias compensation, optimal performance is obtained by placing the IC as close as possible to the ICD.

Figure 2. Design Example for Optrex DMC Display

#### \_Chip Information

**TRANSISTOR COUNT: 1957**

### Typical Operating Circuit

#### Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RS-232 Interface IC category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

062191EB 713266CB MAX3250EAIT MAX250ESD+T MAX13223EEUP+T SP508EEF-L MAX3218EAP+T MAX561CAI+T

MAX3218CAP+T MAX218EAP+T MAX3232ECUP+G071 MAX3228AEEWV+T LT1180AISW#TRPBF MAX3386ECPWR

TRSF3223ECPWR ADM202EARWZ-REEL ICL3232IVZ-T7A ICL3232IBZ-T ICL3222EIBZ-T LMS202EIMX/NOPB 5962-89877012C

AZ75232GTR-G1 AZ75232GSTR-G1 TRS222IDWR TRS3223ECDWR MAX563CPN+ MAX491EESD+ MAX489ESD+ MAX489CPD+

MAX491ECSD+ MAX487EESA+ MAX3389ECUG MAX3318EEAP MAX3244EEUI+ MAX3232ECUE+ MAX3225EETP+

MAX3223EAPT MAX3222ECUP+T MAX3221EUE+T MAX3221EUE+ MAX3190EEUTT MAX251CSD+T MAX248CQH+D

MAX3245CWI+ MAX3241CUI+T MAX221EEUE+ MAX3232EEWET MAX3232EEUET MAX3232ECPE+ MAX3232CPW