| 1 70                                                                               |                                                             |                                                      |                                                                                                                                                                                                                            |                                  |                                     |                                                              |                                                                |              | REVISI |                        |                              |                                           |                                                     |                                  |                              |                              |                                          |                                   |          |         |

|------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|--------------|--------|------------------------|------------------------------|-------------------------------------------|-----------------------------------------------------|----------------------------------|------------------------------|------------------------------|------------------------------------------|-----------------------------------|----------|---------|

| LTR                                                                                |                                                             | DESCRIPTION                                          |                                                                                                                                                                                                                            |                                  |                                     |                                                              |                                                                |              |        |                        |                              |                                           | DA                                                  | TE (YI                           | R-MO-I                       | DA)                          |                                          | APPF                              | ROVED    |         |

| A                                                                                  | table<br>parar                                              | I, anal                                              | ed document to new boilerplate; corrected table I footnotes; corrected<br>analog input voltage maximum value; added footnote to clocking<br>ers; corrected figures 3, 6, and 7, timing diagrams; editorial changes<br>but. |                                  |                                     |                                                              |                                                                |              |        |                        | 92-12-07                     |                                           |                                                     | M. L. Poelking                   |                              |                              |                                          |                                   |          |         |

| В                                                                                  | Char                                                        | iges in                                              | accord                                                                                                                                                                                                                     | lance w                          | nce with NOR 5962-R064-94.          |                                                              |                                                                |              |        |                        |                              |                                           |                                                     | 93-12-07                         |                              |                              | М                                        | Monica L. Poelking                |          |         |

| С                                                                                  | Upda                                                        | Update boilerplate to MIL-PRF-38535 requirements CFS |                                                                                                                                                                                                                            |                                  |                                     |                                                              |                                                                |              |        |                        |                              | 06-06-15                                  |                                                     |                                  | 1                            | Thomas M. Hess               |                                          |                                   |          |         |

|                                                                                    |                                                             |                                                      |                                                                                                                                                                                                                            |                                  |                                     |                                                              |                                                                |              |        |                        |                              |                                           |                                                     |                                  |                              |                              |                                          |                                   |          |         |

| REV                                                                                |                                                             |                                                      |                                                                                                                                                                                                                            |                                  |                                     |                                                              |                                                                |              |        |                        |                              |                                           |                                                     |                                  |                              |                              |                                          |                                   |          | 1       |

| SHEET                                                                              |                                                             |                                                      |                                                                                                                                                                                                                            |                                  |                                     |                                                              |                                                                |              |        |                        |                              |                                           |                                                     |                                  |                              |                              |                                          |                                   |          |         |

| REV                                                                                | С                                                           | С                                                    | С                                                                                                                                                                                                                          | С                                | С                                   |                                                              | -                                                              |              |        |                        |                              |                                           |                                                     |                                  |                              |                              |                                          |                                   |          |         |

| SHEET                                                                              | 15                                                          | 16                                                   |                                                                                                                                                                                                                            |                                  | C                                   | С                                                            | С                                                              | С            |        |                        |                              |                                           |                                                     |                                  |                              |                              |                                          |                                   |          |         |

| REV STATUS                                                                         | 6                                                           |                                                      | 17                                                                                                                                                                                                                         | 18                               | 19                                  | C<br>20                                                      | C<br>21                                                        | C<br>22      |        |                        |                              |                                           |                                                     |                                  |                              |                              |                                          |                                   |          |         |

|                                                                                    |                                                             |                                                      | 17                                                                                                                                                                                                                         | 18<br>REV                        | 19                                  |                                                              |                                                                |              | C      | C                      | С                            | C                                         | C                                                   | C                                | C                            | С                            | C                                        | C                                 | C        | C       |

| OF SHEETS                                                                          |                                                             |                                                      | 17                                                                                                                                                                                                                         |                                  | 19<br>,                             |                                                              | 21                                                             | 22           | C<br>3 | C 4                    | C<br>5                       | C<br>6                                    | C<br>7                                              | C<br>8                           | C<br>9                       | C 10                         | C 11                                     | C 12                              | C<br>13  | C<br>14 |

| PMIC N/A                                                                           |                                                             |                                                      | 17                                                                                                                                                                                                                         | REV<br>SHE                       | 19<br>,                             | 20                                                           | 21<br>C                                                        | 22<br>C      | -      | -                      |                              | -                                         |                                                     | _                                | -                            |                              | -                                        |                                   |          | _       |

|                                                                                    |                                                             |                                                      | 17                                                                                                                                                                                                                         | REV<br>SHE                       | 19<br>,<br>ET                       | 20                                                           | 21<br>C                                                        | 22<br>C      | -      | -                      | 5                            | 6                                         | 7                                                   | 8                                | 9                            | 10                           | 11                                       | 12                                | 13       | -       |

| PMIC N/A                                                                           |                                                             | RD                                                   | 17                                                                                                                                                                                                                         | REV<br>SHE<br>PRE                | 19<br>,<br>ET                       | 20<br>D<br>Tim F                                             | 21<br>C<br>1                                                   | 22<br>C      | -      | -                      | 5                            | 6<br>EFEN                                 | 7<br>SE SI                                          | 8<br>JPPL                        | 9<br>Y CE                    |                              |                                          | 12<br>-UMB                        | 13       | -       |

| PMIC N/A<br>STA<br>MICR                                                            | OCIRC                                                       | CUIT                                                 | 17                                                                                                                                                                                                                         | REV<br>SHE<br>PRE                | 19<br>'<br>ET<br>PAREE              | 20<br>)<br>Tim H<br>BY                                       | 21<br>C<br>1                                                   | 22<br>C      | -      | -                      | 5                            | 6<br>EFEN                                 | 7<br>SE SI<br>DLUM                                  | 8<br>UPPL<br>BUS                 | 9<br>Y CE<br>, OHI0          | 10<br>NTEF                   | 11<br>R COL<br>218-3                     | 12<br>-UMB                        | 13       | -       |

| PMIC N/A<br>STA<br>MICR                                                            |                                                             | CUIT                                                 | 17                                                                                                                                                                                                                         | REV<br>SHE<br>PRE                | 19<br>ET<br>PAREL                   | 20<br>Tim H<br>BY<br>Tim H                                   | 21<br>C<br>1                                                   | 22<br>C      | -      | -                      | 5                            | 6<br>EFEN                                 | 7<br>SE SI<br>DLUM                                  | 8<br>UPPL<br>BUS                 | 9<br>Y CE<br>, OHI0          | 10<br>NTEF<br>O 432          | 11<br>R COL<br>218-3                     | 12<br>-UMB                        | 13       | -       |

| PMIC N/A<br>STA<br>MICR<br>DR                                                      |                                                             | CUIT<br>G                                            |                                                                                                                                                                                                                            | REV<br>SHE<br>PRE                | 19<br>'<br>ET<br>PAREE              | 20<br>Tim F<br>BY<br>Tim F                                   | 21<br>C<br>1<br>I. Noh                                         | 22<br>C      | -      | 4                      | 5<br>DI                      | 6<br>EFEN<br>CC                           | 7<br>SE SI<br>DLUM<br>http                          | 8<br>UPPL<br>BUS                 | 9<br>Y CE<br>, OHI0<br>/w.ds | 10<br>NTEF<br>O 432<br>cc.dl | 11<br>R COL<br>218-39<br>a.mil           | 12<br>-UMB<br>990                 | 13       | -       |

| PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR                                  |                                                             | CUIT<br>G<br>VAILAI<br>ALL                           |                                                                                                                                                                                                                            | REV<br>SHE<br>PRE                | 19<br>ET<br>PAREL                   | 20<br>Tim F<br>BY<br>Tim F                                   | 21<br>C<br>1                                                   | 22<br>C      | -      | 4<br>MIC               | 5<br>DI                      | 6<br>EFEN<br>CC                           | 7<br>SE SI<br>DLUM<br>http                          | 8<br>UPPL<br>BUS<br>:://ww       | 9<br>Y CE<br>, OHI<br>w.ds   | NTER<br>D 432<br>cc.dl       | 11<br>218-33<br>a.mil                    | 12<br>-UMB<br>990<br>BIT          | 13<br>US | -       |

| PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR<br>DEP/<br>AND AGE               | OCIRO<br>AWIN<br>ING IS A<br>USE BY A<br>ARTMEN<br>ENCIES ( | CUIT<br>G<br>VAILAI<br>ALL<br>TS<br>DF THE           | BLE                                                                                                                                                                                                                        | REV<br>SHE<br>PRE<br>CHE         | 19<br>ET<br>PARED<br>CKED           | 20<br>Tim F<br>BY<br>Tim F<br>D BY<br>Don M                  | 21<br>C<br>1<br>I. Noh                                         | 22<br>C<br>2 | -      | 4<br>MIC<br>MIC        | 5<br>DI<br>CROC              | 6<br>EFEN<br>CC<br>CIRCI                  | 7<br>SE SI<br>DLUM<br>http<br>JIT, [<br>ROL         | 8<br>BUS<br>DIGIT<br>LER         | 9<br>Y CE<br>, OHIO<br>w.ds  | 10<br>NTEF<br>D 432<br>cc.dl | 11<br>218-39<br>a.mil<br>S, 8-10<br>, PW | 12<br>-UMB<br>990<br>BIT          | 13<br>US | -       |

| PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR<br>DEP                           | OCIRO<br>AWIN<br>ING IS A<br>USE BY A<br>ARTMEN<br>ENCIES ( | CUIT<br>G<br>VAILAI<br>ALL<br>TS<br>DF THE           | BLE                                                                                                                                                                                                                        | REV<br>SHE<br>PRE<br>CHE         | 19<br>ET<br>PARED<br>CKED           | 20<br>Tim F<br>BY<br>Tim F<br>D BY<br>Don N<br>APPR(         | 21<br>C<br>1<br>I. Noh<br>I. Noh                               | 22<br>C<br>2 | -      | 4<br>MIC<br>MIC        | 5<br>DI<br>CROC              | 6<br>EFEN<br>CC<br>CIRCI                  | 7<br>SE SI<br>DLUM<br>http<br>JIT, [<br>ROL         | 8<br>BUS<br>DIGIT<br>LER         | 9<br>Y CE<br>, OHIO<br>w.ds  | NTER<br>D 432<br>cc.dl       | 11<br>218-39<br>a.mil<br>S, 8-10<br>, PW | 12<br>-UMB<br>990<br>BIT          | 13<br>US | -       |

| PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR I<br>DEP/<br>AND AGE<br>DEPARTME | OCIRC<br>AWIN<br>USE BY<br>ARTMEN<br>ENCIES (<br>ENT OF E   | CUIT<br>G<br>VAILAF<br>ALL<br>TS<br>DF THE<br>DEFEN  | BLE                                                                                                                                                                                                                        | REV<br>SHE<br>PRE<br>CHE<br>APPI | 19<br>FET<br>PARED<br>CKED<br>ROVED | 20<br>Tim F<br>BY<br>Tim F<br>D BY<br>Don M<br>APPR(<br>91-0 | 21<br>C<br>1<br>I. Noh<br>I. Noh<br>I. Cool<br>DVAL E          | 22<br>C<br>2 | -      | 4<br>MIC<br>MIC<br>EPF | 5<br>DI<br>ROC<br>ROC<br>ROM | 6<br>EFEN<br>CC<br>CIRCI<br>CONT<br>, MOI | 7<br>SE SI<br>DLUM<br>http<br>JIT, I<br>ROL         | 8<br>BUS<br>DIGIT<br>LER<br>THIC | 9<br>Y CE<br>, OHIO<br>w.ds  | 10<br>NTEF<br>D 432<br>cc.dl | 11<br>218-39<br>a.mil<br>S, 8-10<br>, PW | 12<br>-UMB<br>990<br>BIT          | 13<br>US | _       |

| PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR I<br>DEP/<br>AND AGE<br>DEPARTME | OCIRO<br>AWIN<br>ING IS A<br>USE BY A<br>ARTMEN<br>ENCIES ( | CUIT<br>G<br>VAILAF<br>ALL<br>TS<br>DF THE<br>DEFEN  | BLE                                                                                                                                                                                                                        | REV<br>SHE<br>PRE<br>CHE<br>APPI | 19<br>FET<br>PARED<br>CKED<br>ROVED | 20<br>Tim F<br>BY<br>Tim F<br>Don M<br>APPR(<br>91-C         | 21<br>C<br>1<br>I. Noh<br>I. Noh<br>I. Cool<br>DVAL D<br>99-11 | 22<br>C<br>2 | -      | 4<br>MIC<br>MIC<br>EPF | 5<br>DI<br>ROC<br>ROC<br>ROM | 6<br>EFEN<br>CC<br>CIRCI<br>CONT<br>, MOI | 7<br>SE SI<br>DLUM<br>http<br>JIT, I<br>ROL<br>NOLI | 8<br>BUS<br>DIGIT<br>LER<br>THIC | 9<br>Y CE<br>, OHIO<br>w.ds  | 10<br>NTEF<br>D 432<br>cc.dl | 11<br>218-33<br>a.mil<br>S, 8-I<br>0, PW | 12<br>-UMB<br>990<br>BIT          | 13<br>US | _       |

| PMIC N/A<br>STA<br>MICR<br>DR<br>THIS DRAW<br>FOR<br>DEP/<br>AND AGE<br>DEPARTME   | OCIRC<br>AWIN<br>USE BY<br>ARTMEN<br>ENCIES (<br>ENT OF E   | CUIT<br>G<br>VAILAF<br>ALL<br>TS<br>DF THE<br>DEFEN  | BLE                                                                                                                                                                                                                        | REV<br>SHE<br>PRE<br>CHE<br>APPI | 19<br>FET<br>PARED<br>CKED<br>ROVED | 20<br>Tim F<br>BY<br>Tim F<br>Don M<br>APPR(<br>91-C         | 21<br>C<br>1<br>I. Noh<br>I. Noh<br>I. Cool<br>DVAL E          | 22<br>C<br>2 | -      | 4<br>MIC<br>MIC<br>EPF |                              | 6<br>EFEN<br>CC<br>CIRCI<br>CONT<br>, MOI | 7<br>SE SI<br>DLUM<br>http<br>JIT, I<br>ROL         | 8<br>BUS<br>DIGIT<br>LER<br>THIC | 9<br>Y CE<br>, OHIO<br>w.ds  | 10<br>NTEF<br>D 432<br>cc.dl | 11<br>218-33<br>a.mil<br>S, 8-I<br>0, PW | 12<br>-UMB<br>990<br>BIT<br>/M AN | 13<br>US | -       |

# 1. SCOPE

1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels is reflected in the PIN.

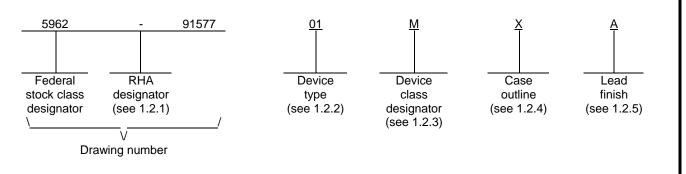

1.2 <u>PIN</u>. The PIN is as shown in the following example:

1.2.1 <u>RHA designator</u>. Device classes Q, and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function                                                                                 |

|-------------|----------------|--------------------------------------------------------------------------------------------------|

| 01          | 87C752         | CMOS, 8-bit microcontroller with A/D, PWM, 2k<br>EPROM memory (3.5 to 12 MHz)                    |

| 02          | 87C752-16      | CMOS, 8-bit microcontroller with A/D, PWM, 2k<br>EPROM memory (3.5 to 16 MHz)                    |

| 03          | 87C752         | CMOS, 8-bit microcontroller with A/D, PWM, 2k one time programmable EPROM memory (3.5 to 12 MHz) |

| 04          | 87C752-16      | CMOS, 8-bit microcontroller with A/D, PWM, 2k one time programmable EPROM memory (3.5 to 16 MHz) |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as follows:

| Device class     | Device requirements documentation                                                                                                                             |                          |                        |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|--|--|--|--|--|--|

| М                | Vendor self-certification to the requirements for MIL-STD-883 compliant, non-<br>JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A |                          |                        |  |  |  |  |  |  |

| Q or V           | Certifi                                                                                                                                                       | cation and qualification | on to MIL-PRF-38535    |  |  |  |  |  |  |

| Case outline(s). | The case outline(s) are as de                                                                                                                                 | esignated in MIL-ST      | 0-1835 and as follows: |  |  |  |  |  |  |

| Outline letter   | Descriptive designator                                                                                                                                        | <u>Terminals</u>         | Package style          |  |  |  |  |  |  |

X GDIP1-T28 or CDIP2-T28 28 Dual-in-line <u>1</u>/

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q, and V or MIL-PRF-38535, appendix A for device class M.

1/ For device types 01 and 02, the lid shall be transparent to permit ultraviolet light erasure.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-91577 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>C | SHEET 2    |

1.2.4

# 1.3 Absolute maximum ratings. 1/

| Supply voltage V <sub>CC</sub> to V <sub>SS</sub> range | -0.5 V dc to +6.5 V dc           |

|---------------------------------------------------------|----------------------------------|

| Voltage (any pin) to V <sub>SS</sub> range              | -0.5 V dc to $V_{CC}$ + 0.5 V dc |

| Storage temperature range                               | -65°C to +150°C                  |

| Maximum power dissipation (P <sub>D</sub> )             | 1.0 W                            |

| Lead temperature (soldering, 5 seconds)                 | +300°C                           |

| Thermal resistance, junction-to-case ( $\theta_{JC}$ )  | See MIL-STD-1835                 |

# 1.4 Recommended operating conditions.

| Supply voltage range (V <sub>CC</sub> )            | +4.5 V dc to +5.5 V dc         |

|----------------------------------------------------|--------------------------------|

| Maximum low level input voltage (except SDA, SCL)  | 0.2V <sub>CC</sub> – 0.25 V dc |

| Maximum low level input voltage (SDA, SCL)         | 0.3V <sub>CC</sub>             |

| Minimum high level input voltage (SDA, SCL)        | 0.7V <sub>CC</sub>             |

| Minimum high level input voltage (except X1, RST)  | 0.2V <sub>CC</sub> + 0.9 V dc  |

| Minimum high level input voltage (X1, RST)         | 0.7V <sub>CC</sub>             |

| Case operating temperature range (T <sub>c</sub> ) | -55°C to +125°C                |

| Oscillator frequency                               | 3.5 MHz to 16 MHz              |

# 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

# DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

# DEPARTMENT OF DEFENSE STANDARDS

| MIL-STD-883 | - | Tes | t Met | hod | Stan | dard | Mic | roo | circuits. |   |  |

|-------------|---|-----|-------|-----|------|------|-----|-----|-----------|---|--|

|             |   |     |       | -   |      |      |     |     | -         | _ |  |

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

# DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at http://assist.daps.dla.mil/quicksearch/ or http://assist.daps.dla.mil or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

1/ Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91577 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | C              | 3          |

#### 3. REQUIREMENTS

3.1 <u>Item requirements</u>. The individual item requirements for device classes Q, and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.4 herein.

3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

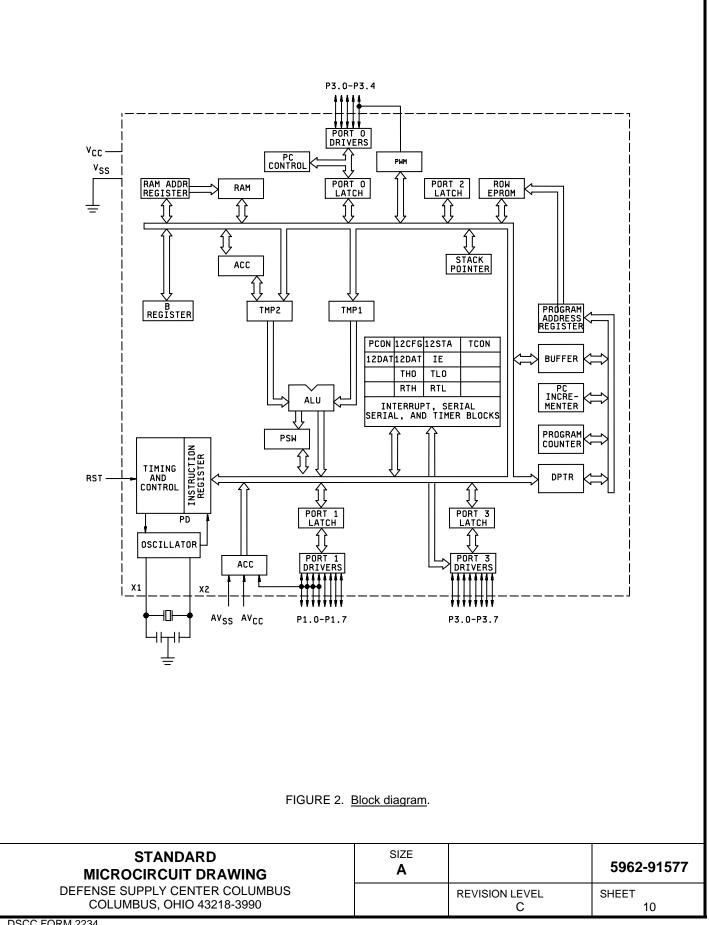

3.2.3 <u>Block diagram</u>. The block diagram shall be as specified on figure 2.

3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change that affects this drawing.

3.9 <u>Verification and review for device class M</u>. For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 105 (see MIL-PRF-38535, appendix A).

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91577 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | C              | 4          |

3.11 <u>Processing EPROM's</u>. All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

3.11.1 <u>Erasure of EPROM's</u>. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.5.

3.11.2 <u>Programmability of EPROM's</u>. When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.6 and table III.

3.11.3 <u>Verification of erasure of programmability of EPROM's</u>. When specified, devices shall be verified as either programmed to the specified pattern or erased. As a minimum, verification shall consist of performing a functional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-91577 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>C | SHEET<br>5 |

| DOCO FORM 0004                                              |           |                     |            |

| Test                                                                    | Symbol           | -55°C ≤ T                                | ditions <u>1/</u><br><sup>·</sup> <sub>C</sub> ≤ +125°C<br>/ <sub>CC</sub> ≤ 5.5 V | Group A   | Device | Lim                 | Limits |    |

|-------------------------------------------------------------------------|------------------|------------------------------------------|------------------------------------------------------------------------------------|-----------|--------|---------------------|--------|----|

|                                                                         |                  |                                          | wise specified                                                                     | subgroups | types  | Min                 | Max    | 1  |

| Output low voltage,<br>Ports 1, 3, 0.3, and 0.4<br>(PWM disabled)       | V <sub>OL</sub>  | I <sub>OL</sub> = 1.6 mA                 | $V_{CC} = 4.5 V$ $V_{IN} = V_{IL} max,$ $V_{IH} min$                               | 1, 2, 3   | All    |                     | 0.45   | V  |

| Output low voltage,<br>Port 0.2                                         | V <sub>OL1</sub> | I <sub>OL</sub> = 3.2 mA                 |                                                                                    |           |        |                     | 0.45   | V  |

| Ports 0.0 and 0.1<br>(I <sup>2</sup> C) - Drivers output<br>low voltage | V <sub>OL2</sub> | I <sub>OL</sub> = 3.2 mA                 |                                                                                    |           |        |                     | 0.45   | V  |

| Output high voltage,<br>Ports 1, 3, 0.3 and 0.4                         | V <sub>OH</sub>  | I <sub>OH</sub> = -60 μA                 |                                                                                    |           |        | 2.4                 |        | V  |

| (PWM disabled)                                                          |                  | I <sub>OH</sub> = -25 μA                 | 1                                                                                  |           |        | 0.75V <sub>CC</sub> |        |    |

|                                                                         |                  | I <sub>OH</sub> = -10 μA                 | 1                                                                                  |           |        | 0.9V <sub>CC</sub>  |        |    |

| Output high voltage,<br>Port 0.4                                        | V <sub>OH1</sub> | I <sub>OH</sub> = -400 μA                | 1                                                                                  |           |        | 2.4                 |        | V  |

| (PWM disabled)                                                          |                  | I <sub>OH</sub> = -40 μA                 | ]                                                                                  |           |        | 0.9V <sub>CC</sub>  |        |    |

| Logic 0 input current,<br>ports 1, 3, 0.3, and 0.4<br>(PWM disabled)    | IIL              | V <sub>IN</sub> = 0.45 V, V <sub>C</sub> | <sub>c</sub> = 5.5 V                                                               |           |        | 0                   | -50    | μA |

| Logic 1 to 0 transition<br>current, ports 1, 3, 0.3,<br>and 0.4         | I <sub>TL</sub>  | $V_{IN} = 2.0 \text{ V}, \text{ V}_{CC}$ | ; = 5.5 V                                                                          | ]         |        | 0                   | -650   | μA |

| Input leakage current,                                                  | ILI              | $V_{IN} = V_{CC}$                        | $V_{CC} = 5.5 V$                                                                   | ]         |        | 0                   | 10     | μA |

| port 0.0, 0.1, and 0.2                                                  |                  | V <sub>IN</sub> = 0.45 V                 | <u> </u>                                                                           |           |        | 0                   | -10    |    |

| Reset pull-down resistor                                                | R <sub>RST</sub> |                                          |                                                                                    |           |        | 25                  | 175    | kΩ |

| Driver, receiver<br>combined capacitance                                | С                | See 4.4.1.b                              |                                                                                    | 4         | All    |                     | 10     | pF |

| Pin capacitance                                                         | C <sub>I/O</sub> | See 4.4.1.b                              |                                                                                    |           |        |                     | 10     | pF |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91577 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | C              | 6          |

| Test                            | Symbol           | $\begin{array}{c} \mbox{Conditions}  \underline{1}/\\ -55^{\circ}\mbox{C} \leq \mbox{T}_{\mbox{C}} \leq +125^{\circ}\mbox{C}\\ 4.5\ \mbox{V} \leq \mbox{V}_{\mbox{CC}} \leq 5.5\ \mbox{V} \end{array}$ | Group A<br>subgroups |        |                           | nits                   | Unit |

|---------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|---------------------------|------------------------|------|

|                                 |                  | $4.5 \text{ V} \leq \text{V}_{CC} \leq 5.5 \text{ V}$<br>unless otherwise specified                                                                                                                    | subgroups            | types  | Min                       | Max                    |      |

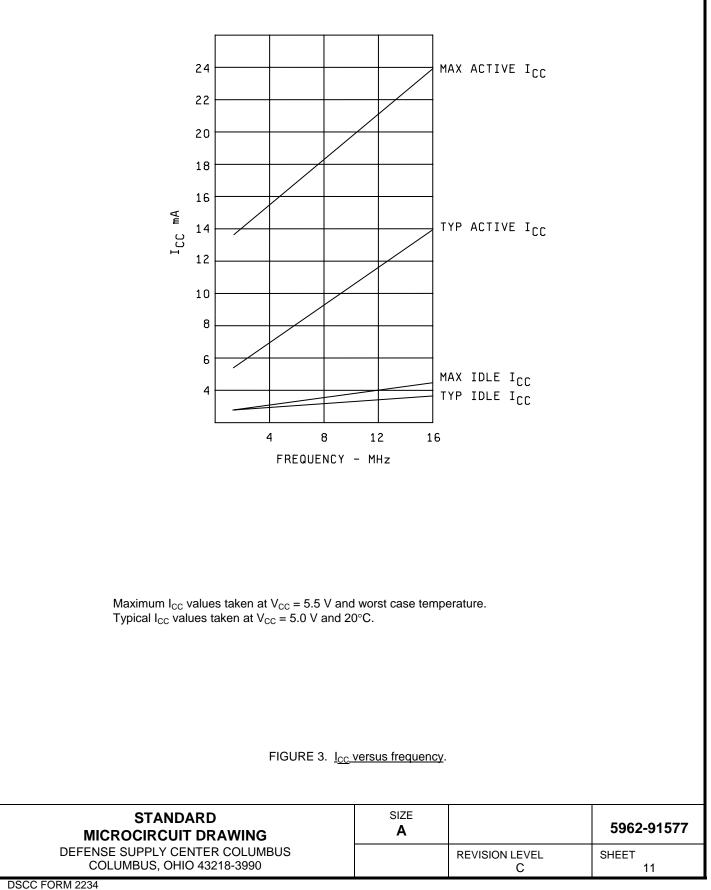

| Supply current,                 | I <sub>cc</sub>  | $V_{CC} = 5.5 \text{ V},  \underline{2}/ \ \underline{3}/$                                                                                                                                             | 1, 2, 3              | 01, 03 |                           | 21                     | mA   |

| active                          |                  | See figure 3.                                                                                                                                                                                          |                      | 02, 04 |                           | 24                     |      |

| Supply current,                 | I <sub>CC1</sub> | $V_{CC} = 5.5 \text{ V},  \underline{3}/ \ \underline{4}/$                                                                                                                                             |                      | 01, 03 |                           | 4                      | mA   |

| idle                            |                  | See figure 3.                                                                                                                                                                                          |                      | 02, 04 |                           | 5                      |      |

| Power down current              | I <sub>PD</sub>  | $V_{CC} = 2 V, 5.5 V \underline{5}/$                                                                                                                                                                   | 1, 2, 3              | All    |                           | 50                     | μA   |

| V <sub>PP</sub> program voltage | V <sub>PP</sub>  | V <sub>CC</sub> = 4.5 V, 5.5 V<br>V <sub>SS</sub> = 0 V                                                                                                                                                | 1                    | All    | 12.5                      | 13.0                   | V    |

| Program current                 | I <sub>PP</sub>  | V <sub>PP</sub> = 13.0 V                                                                                                                                                                               |                      |        |                           | 50                     | mA   |

| Analog supply voltage           | AV <sub>CC</sub> | $AV_{CC} = V_{CC} \pm 0.2 V $ <u>7</u> /                                                                                                                                                               | 1, 2, 3              | All    | 4.5                       | 5.5                    | V    |

| A/D converter parameters        | <u>6</u> /       |                                                                                                                                                                                                        |                      |        |                           |                        |      |

| Analog input voltage            | AV <sub>IN</sub> | AV <sub>CC</sub> = 5.12 V                                                                                                                                                                              |                      |        | AV <sub>SS</sub> –<br>0.2 | AV <sub>CC</sub> + 0.2 | V    |

| Analog input<br>capacitance     | C <sub>IA</sub>  | See 4.4.1b                                                                                                                                                                                             | 4                    | All    |                           | 15                     | pF   |

| Sampling time                   | T <sub>ADS</sub> | <u>8</u> /                                                                                                                                                                                             | 9, 10, 11            | All    |                           | 8t <sub>CY</sub>       | S    |

| Conversion time                 | T <sub>ADS</sub> | <u>8</u> /                                                                                                                                                                                             |                      |        |                           | 40t <sub>CY</sub>      | s    |

| Resolution                      | R                |                                                                                                                                                                                                        | 4, 5, 6              | All    |                           | 8                      | bits |

| Differential<br>non-linearity   | D <sub>NL</sub>  | <u>8</u> /                                                                                                                                                                                             |                      |        |                           | ±1                     | LSE  |

| Zero scale offset               | OS <sub>e</sub>  |                                                                                                                                                                                                        |                      |        |                           | ±1                     | LSE  |

| Full scale gain error           | G <sub>e</sub>   |                                                                                                                                                                                                        |                      |        |                           | 0.4                    | %    |

| Channel to channel              | M <sub>CTC</sub> | <u>9</u> /                                                                                                                                                                                             |                      |        |                           | ±1                     | LSE  |

| matching                        | -1               | 0 – 100 kHz <u>7</u> / <u>8</u> /                                                                                                                                                                      |                      |        |                           | -60                    | dB   |

STANDARDSIZEMICROCIRCUIT DRAWINGADEFENSE SUPPLY CENTER COLUMBUS<br/>COLUMBUS, OHIO 43218-3990

| 4 |                     | 5962-91577 |

|---|---------------------|------------|

|   | REVISION LEVEL<br>C | SHEET<br>7 |

| Test                                                        | Symbol              | $\begin{array}{c} \mbox{Conditions}  \underline{1}/ \\ -55^{\circ}\mbox{C} \leq \mbox{T}_{\mbox{C}} \leq +125^{\circ}\mbox{C} \\ 4.5 \ \mbox{V} \leq \mbox{V}_{\mbox{CC}} \leq 5.5 \ \mbox{V} \end{array}$ | Group A   | Device | Lir      | nits | Unit     |

|-------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|----------|------|----------|

|                                                             |                     | unless otherwise specified                                                                                                                                                                                 | subgroups | types  | Min      | Max  |          |

| Functional test                                             |                     | See 4.4.1c                                                                                                                                                                                                 | 7, 8      | All    |          |      |          |

| Oscillator frequency                                        | 1/t <sub>CLCL</sub> |                                                                                                                                                                                                            | 9, 10, 11 | 01, 03 | 3.5      | 12   | MHz      |

| variable clock                                              |                     |                                                                                                                                                                                                            |           | 02, 04 | 3.5      | 16   |          |

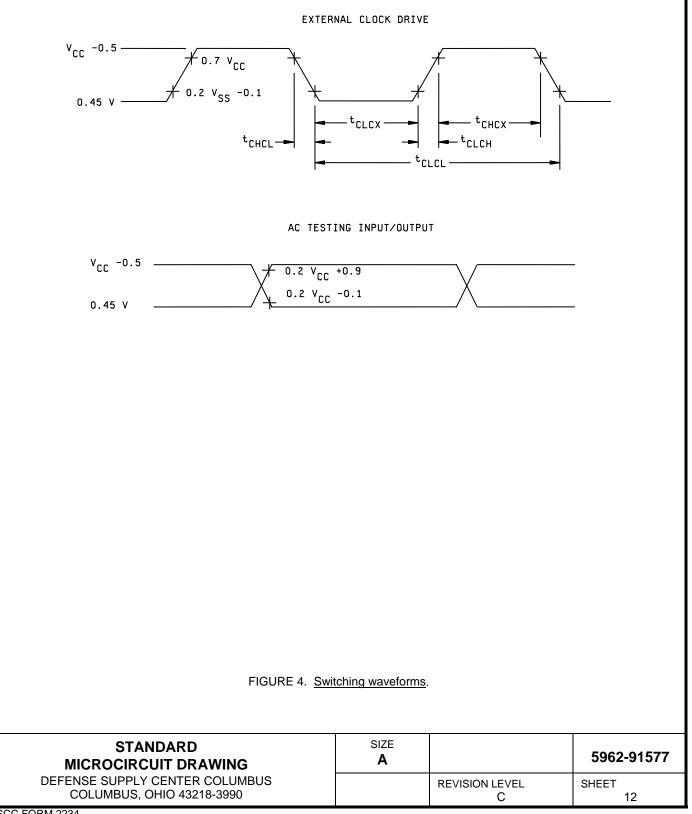

| External clock (See figu                                    | re 4)               |                                                                                                                                                                                                            |           |        |          |      |          |

| External clock (See figu                                    | re 4)               |                                                                                                                                                                                                            |           |        |          |      |          |

| High time,<br>variable clock                                | t <sub>CHCX</sub>   | <u>9</u> /                                                                                                                                                                                                 | 9, 10, 11 | All    | 20       |      | ns       |

| High time,<br>variable clock<br>Low time,<br>variable clock |                     | <u>9</u> /                                                                                                                                                                                                 | 9, 10, 11 | All    | 20<br>20 |      | ns<br>ns |

| High time,<br>variable clock<br>Low time,                   | t <sub>CHCX</sub>   |                                                                                                                                                                                                            | 9, 10, 11 | All    |          | 20   |          |

- 1/ Unless otherwise specified, parameters are valid over operating temperature range. All parameters must be tested by using the worst case forcing condition unless otherwise noted.

- $\frac{2}{V}$  I<sub>CC</sub> is measured with all output pins disconnected; X1 driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V, V<sub>IH</sub> = V<sub>CC</sub> 0.5 V; X2 = NC; RST = port 0 = V<sub>CC</sub>. I<sub>CC</sub> will be slightly higher if a crystal oscillator is used.

- 3/ The resistor ladder network is not disconnected in the power down or idle modes. Thus, to conserve power the user may remove AV<sub>CC</sub>.

- $\frac{4}{V}$  Idle I<sub>CC</sub> is measured with all output pins disconnected; X1 driven with t<sub>CLCH</sub>, t<sub>CHCL</sub> = 5 ns, V<sub>IL</sub> = V<sub>SS</sub> + 0.5 V, V<sub>IH</sub> = V<sub>CC</sub> 0.5 V; X2 = NC; port 0 = V<sub>CC</sub>; RST = V<sub>SS</sub>.

- 5/ Power-down  $I_{CC}$  is measured with all output pins disconnected; port 0 =  $V_{CC}$ ; X2, X1 = NC; RST =  $V_{SS}$ .

- 6/ Analog inputs (A/D guaranteed only with quartz window covered).

- <u>7</u>/ If the A/D function is not required, or if the A/D function is only needed periodically, then AV<sub>CC</sub> may be removed without affecting the operation of the digital circuitry. Contents of ADCON and ADAT are not guaranteed to be valid. Digital inputs on P1.0 P1.4 will not function normally.

- 8/ Tested, initially and after any design changes that affect the parameters.

- <u>9/</u> If not tested, guaranteed to the limit specified in table I.

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 C SHEET<br>COLUMBUS, OHIO 43218-3990 C 8 | STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                     | 5962-91577 |

|------------------------------------------------------------------------------------------------------|----------------------------------|------------------|---------------------|------------|

|                                                                                                      |                                  |                  | REVISION LEVEL<br>C | SHEET<br>8 |

| Device types:   | All                  |

|-----------------|----------------------|

| Case outline:   | Х                    |

| Terminal number | Terminal symbol      |

| 1               | P3.4/A4              |

| 2               | P3.3/A3              |

| 3               | P3.2/A2/A10          |

| 4               | P3.1/A1/A9           |

| 5               | P3.0/A0/A8           |

| 6               | P0.2/V <sub>PP</sub> |

| 7               | P0.1/SDA/OE-PGM      |

| 8               | P0.0/SCL/ASEL        |

| 9               | RST                  |

| 10              | X2                   |

| 11              | X1                   |

| 12              | V <sub>SS</sub>      |

| 13              | P1.0/ADC0/D0         |

| 14              | P1.1/ADC1/D1         |

| 15              | P1.2/ADC2/D2         |

| 16              | P1.3/ADC3/D3         |

| 17              | P1.4/ADC4/D4         |

| 18              | AV <sub>SS</sub>     |

| 19              | AV <sub>CC</sub>     |

| 20              | P1.5/INT0            |

| 21              | P1.6/INT1/D6         |

| 22              | P1.7/T0/D7           |

| 23              | P0.3                 |

| 24              | P0.4/PWM OUT         |

| 25              | P3.7/A7              |

| 26              | P3.6/A6              |

| 27              | P3.5/A5              |

| 28              | V <sub>cc</sub>      |

FIGURE 1. Terminal connections.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91577 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | C              | 9          |

# 4. VERIFICATION

4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. For device class M, sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection.

#### 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- c. A data retention stress test shall be included as part of the screening procedure and shall consist of the following steps:

#### Margin test method A

- (1) Program greater than 95 percent of the bit locations, including the slowest programming cell (see 3.11.2). The remaining cells shall provide a worst case speed pattern.

- (2) Bake, unbiased for 72 hours at +140°C to screen for data retention lifetime.

- (3) Perform a margin test using  $V_m = +5.9 \text{ V}$  at +25°C using loose timing (i.e.,  $T_{ACC} > 1 \mu s$ ).

- (4) Perform dynamic burn-in (see 4.2.1a).

- (5) Margin at  $V_m = +5.9 V$ .

- (6) Perform electrical tests (see 4.2).

- (7) Erase (see 3.11.1), except devices submitted for groups A, B, C, and D testing.

- (8) Verify erasure (see 3.11.3).

|                                                                     | 2-91577 |

|---------------------------------------------------------------------|---------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 C SHEET | 13      |

# Margin test method B

- (1) Program at 25°C, 100 percent of the bits.

- (2) Bake, unbiased for 24 hours at +250°C.

- (3) Perform margin test at  $V_m = +5.9$  V.

- (4) Erase (see 3.11.1).

- (5) Perform interim electrical tests in accordance with table II.

- (6) For device types 01 and 02, program 100 percent of the bits and verify (see 3.11.2).

- (7) Perform burn-in (see 4.2.1a).

- (8) One-hundred percent test at 25°C (group A, subgroups 1 and 7). V<sub>m</sub> = 5.9 V with loose timing, apply PDA. For device types 03 and 04, the virgin state of the devices must be verified.

- (9) Perform remaining final electrical subgroups and group A testing.

- (10) For device types 01 and 02, erase, devices may be submitted for groups B, C, and D at this time.

- (11) For device types 01 and 02, verify erasure (see 3.11.3).

- (12) Steps 1 through 4 are performed at wafer level.

- 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

4.4 <u>Conformance inspection</u>. Technology conformance inspection for classes Q and V shall be in accordance with MIL-PRF-38535 including groups A, B, C, D, and E inspections and as specified herein. Quality conformance inspection for device class M shall be in accordance with MIL-PRF-38535, appendix A and as specified herein. Inspections to be performed for device class M shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br><b>A</b> |                | 5962-91577 |

|----------------------------------|------------------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |                  | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |                  | C              | 14         |

# 4.4.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroup 4 (C, C<sub>I/O</sub>, and C<sub>IA</sub>) shall be measured only for the initial test and after process or design changes which may affect capacitance. A minimum sample size of five devices with zero rejects shall be required.

- c. For device class M, subgroups 7 and 8 tests shall be sufficient to verify the truth table. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device.

- d. For device types 01 and 02, all devices selected for testing shall have the EPROM programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified (except devices submitted for groups C and D testing).

- e. For device types 03 and 04, unprogrammed devices shall be tested for programmability and functionality compliance to the requirements of group A, subgroups 7 and 8. Either of two techniques is acceptable:

- (1) Testing the entire lot using additional built in test circuitry which allows the manufacturer to verify programmability and functionality without programming the user array. If this is done, the resulting test patterns shall be verified on all devices during subgroups 7 and 8, group A testing per the sampling plan specified in MIL-STD-883, method 5005.

- (2) If such compliance cannot be tested on an unprogrammed device, a sample shall be selected to satisfy programmability requirements prior to performing subgroups 7 and 8. Twelve devices shall be submitted to programming. If more than 2 devices fail to program, the lot shall be rejected. At the manufacturer's option, the sample may be increased to 24 total devices with no more than 4 total device failures allowable. (Ten devices from the programmability sample shall be submitted to the requirements of group A, subgroup 7 and 8. If more than 2 total devices fail, the lot shall be rejected. At the manufacturer's option, the sample with no more than 4 total devices fail, the lot shall be rejected. At the manufacturer's option, the sample may be increased to 20 total devices with no more than 4 total device failures allowable.)

| Test requirements                                    | Subgroups<br>(in accordance with<br>MIL-STD-883,<br>method 5005, table I) | (in accord           | roups<br>Jance with<br>535, table III) |

|------------------------------------------------------|---------------------------------------------------------------------------|----------------------|----------------------------------------|

|                                                      | Device                                                                    | Device               | Device                                 |

|                                                      | class M                                                                   | class Q              | class V                                |

| Interim electrical                                   |                                                                           |                      |                                        |

| parameters (see 4.2)                                 |                                                                           |                      |                                        |

| Final electrical                                     | 1, 2, 3, 5, 6, 7, 8,                                                      | 1, 2, 3, 5, 6, 7, 8, | 1, 2, 3, 5, 6, 7, 8,                   |

| parameters (see 4.2)                                 | 9, 10, 11 <u>1</u> /                                                      | 9, 10, 11 <u>1</u> / | 9, 10, 11 <u>2</u> /                   |

| Group A test                                         | 1, 2, 3, 4, 5, 6,                                                         | 1, 2, 3, 4, 5, 6,    | 1, 2, 3, 4, 5, 6,                      |

| requirements (see 4.4)                               | 7, 8, 9, 10, 11                                                           | 7, 8, 9, 10, 11      | 7, 8, 9, 10, 11                        |

| Group C end-point electrical<br>parameters (see 4.4) | 2, 5, 8a, 10                                                              | 2, 5, 8a, 10         | 2, 5, 8a, 10                           |

| Group D end-point electrical<br>parameters (see 4.4) | 2, 5, 8a, 10                                                              | 2, 5, 8a, 10         | 2, 5, 8a, 10                           |

| Group E end-point electrical parameters (see 4.4)    | 1, 5, 7, 9                                                                | 1, 5, 7, 9           | 1, 5, 7, 9                             |

# TABLE II. Electrical test requirements.

<u>1</u>/ PDA applies to subgroup 1.

2/ PDA applies to subgroups 1 and 7.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91577 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | C              | 15         |

- 4.4.2 <u>Group C inspection</u>. The group C inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.2.1 Additional criteria for device class M. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

- b.  $T_A = +125^{\circ}C$ , minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- d. For device types 01 and 02, all devices selected for testing shall be programmed with a checkerboard pattern or equivalent. After completion of all testing, the devices shall be erased and verified.

- e. For device types 03 and 04, the virgin state of the device must be verified.

4.4.2.2 Additional criteria for device classes Q and V. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

4.4.3 <u>Group D inspection</u>. The group D inspection end-point electrical parameters shall be as specified in table II herein.

4.4.4 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein).

- a. End-point electrical parameters shall be as specified in table II herein.

- b. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535 for the RHA level being tested. For device class M, the devices shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535, appendix A for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table I at T<sub>A</sub> = +25°C ±5°C, after exposure, to the subgroups specified in table II herein.

4.5 <u>Erasing procedure</u>. The recommended erasure procedure is exposure to ultraviolet light (at 2537 Angstroms) to an integrated dose of at least 15 W-s/cm<sup>2</sup>. Exposing the EPROM to an ultraviolet lamp of 12,000  $\mu$ W/cm<sup>2</sup> rating for 20 to 30 minutes, at a distance of about one inch, should be sufficient.

4.6 <u>Programming procedures</u>. The programming characteristics in table III and the following procedures shall be used for programming the device:

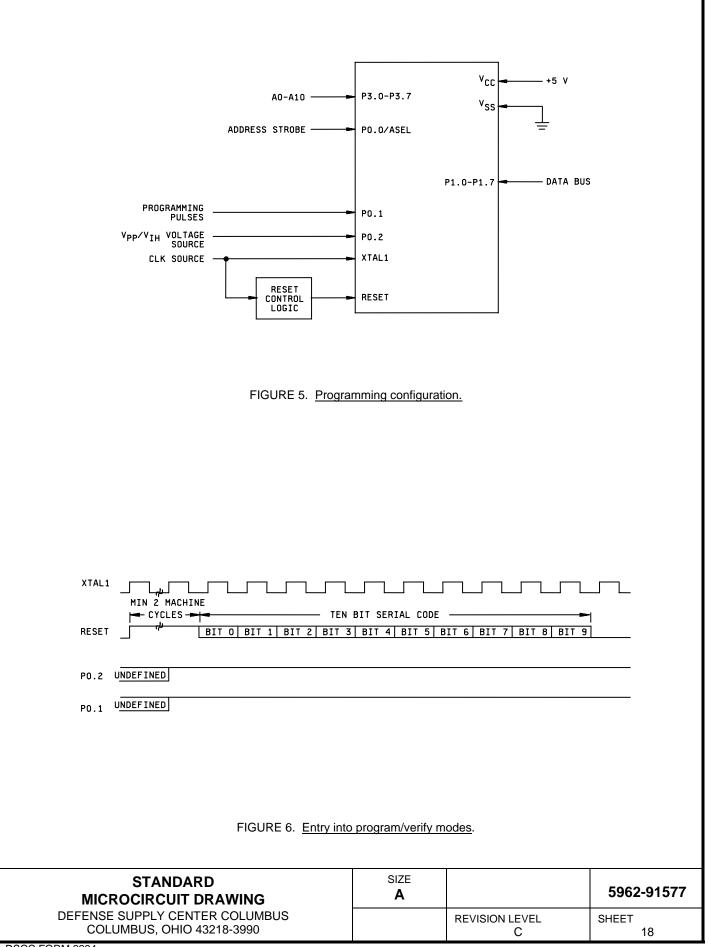

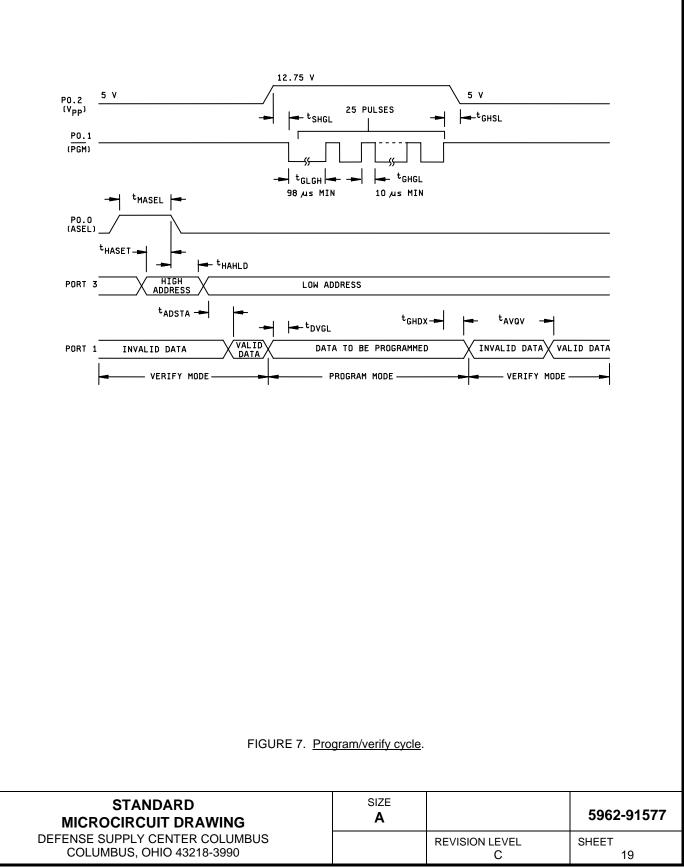

- a. Connect the device in the electrical configuration (see figure 5) for programming. The waveforms of figure 6 and programming characteristics of table III shall apply.

- b. Initially and after each erasure, all bits are in the high "H" state. Information is introduced by selectively programming "L" into the desired bit locations. A programmed "L" can be changed to an "H" by ultraviolet light erasure (see 4.5).

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91577 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | C              | 16         |

| Parameter                               | Symbol                  | Conditions                  | Limit                       | S                   | Units |

|-----------------------------------------|-------------------------|-----------------------------|-----------------------------|---------------------|-------|

|                                         |                         |                             | Min                         | Max                 |       |

| Oscillator frequency                    | 1/t <sub>CLCL</sub>     | <u>1</u> /<br>See figure 7. | 1.2                         | 6                   | MHz   |

| Address setup to<br>PROG low            | t <sub>AVGL</sub>       |                             | 10 μs + 24t <sub>CLCL</sub> |                     | ns    |

| Address hold after<br>PROG              | t <sub>GHAX</sub>       |                             | 48t <sub>CLCL</sub>         |                     | ns    |

| Data setup to<br>PROG low               | t <sub>DVGL</sub>       |                             | 38t <sub>CLCL</sub>         |                     | ns    |

| Data hold after<br>PROG                 | t <sub>GHDX</sub>       |                             | 36t <sub>CLCL</sub>         |                     | ns    |

| $V_{PP}$ setup to $\overline{PROG}$ low | t <sub>SHGL</sub>       |                             | 10                          |                     | μs    |

| V <sub>PP</sub> hold after PROG         | t <sub>GHSL</sub>       |                             | 10                          |                     | μS    |

| PROG width                              | t <sub>GLGH</sub>       |                             | 90                          | 110                 | μS    |

| $V_{\text{PP}}$ low to data valid       | t <sub>AVQV</sub><br>3/ |                             |                             | 48t <sub>CLCL</sub> | ns    |

| PROG high to PROG low                   | t <sub>GHGL</sub>       |                             | 10                          |                     | μs    |

| P0.0 (sync pulse) low                   | t <sub>SYNL</sub>       |                             | 4t <sub>CLCL</sub>          |                     | ns    |

| P0.0 (sync pulse) high                  | t <sub>SYNH</sub>       |                             | 8t <sub>CLCL</sub>          |                     | ns    |

| ASEL high time                          | t <sub>MASEL</sub>      |                             | 13t <sub>CLCL</sub>         |                     | ns    |

| Address hold time                       | t <sub>HAHLD</sub>      |                             | 2t <sub>CLCL</sub>          |                     | ns    |

| Address setup to ASEL                   | t <sub>HASET</sub>      |                             | 13t <sub>CLCL</sub>         |                     | ns    |

| Low address to<br>address stable        | t <sub>ADSTA</sub>      |                             | 13t <sub>CLCL</sub>         |                     | ns    |

# TABLE III. EPROM Programming and verification characteristics.

$\begin{array}{ll} \underline{1}' & \mbox{For programming specifications, } T_A = 21^\circ\mbox{C to } 27^\circ\mbox{C}, \ V_{CC} = 5\ V \pm 10\ \mbox{percent, } V_{SS} = 0\ V. \\ \underline{2}' & \mbox{Address should be valid at least } 24t_{CLCL} \ \mbox{before rising edge of } P0.2(V_{PP}). \\ \underline{3}' & \mbox{For a pure verify mode, i.e., no program mode in between, } t_{AVQV} \ \mbox{is } 14t_{CLCL} \ \mbox{maximum.} \end{array}$

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-91577 |