# **EcoSpeed<sup>®</sup> DC-DC Buck Controller** with Integrated LDO

#### **POWER MANAGEMENT**

## **Features**

- Power system

- Input voltage 4.5V to 46V

- Output voltage 0.6V to >85% x VIN

- Integrated bootstrap switch

- Fixed 5V LDO output 200mA

- 1% reference

- Selectable internal/external bias power supply

- EcoSpeed® architecture with pseudo-fixed frequency adaptive on-time control

- Logic input and output control

- Independent control EN for LDO and switcher

- Programmable soft-start time

- Programmable V<sub>IN</sub> UVLO threshold

- Power Good output

- Selectable power-save mode for >80% efficiency under light load

- Programmable ultrasonic power-save mode

- SmartDriveTM for reduced EMI

- Protections

- Automatic restart on fault shutdown

- Over-voltage and under-voltage

- TC compensated R<sub>DS(ON)</sub> sensed current limit

- Thermal shutdown

- Smart power-save

- Pre-bias start-up

- Capacitor types: SP, POSCAP, OSCON, and ceramic

- Package 3 x 3(mm), 20-pin MLPQ

- Lead-free and halogen-free

- RoHS and WEEE compliant

- AEC-Q100 Qualified available in SC508A

# **Applications**

- Office automation and computing

- Networking and telecommunication equipment

- Point-of-load power supplies and module replacement

- Automotive applications

# **Description**

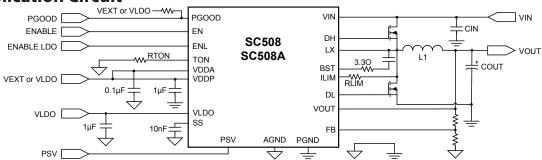

The SC508/SC508A is a synchronous EcoSpeed® buck regulator which incorporates Semtech's advanced, patented adaptive on-time control architecture to provide excellent light-load efficiency and fast transient response. It features an integrated bootstrap switch and a fixed 5V LDO in a 3 x 3(mm) package. The device is highly efficient and uses minimal PCB area. The SC508A is available for automotive applications and is qualified to AEC-Q100.

The SC508 supports using standard capacitor types such as electrolytic or special polymer, in addition to ceramic, at switching frequencies up to 1MHz. The programmable frequency, synchronous operation, and programmable power-save provide high efficiency operation over a wide load range.

Additional features include cycle-by-cycle current limit, programmable soft-start, under and over-voltage protection, programmable over-current protection, start-up into pre-biased output, automatic fault recovery (hiccup restart), soft-shutdown, selectable power-save modes, and programmable ultrasonic power-save. The device also provides separate enable inputs for the PWM controller and LDO as well as a power good output for the PWM controller. Output voltage range is 0.6 to 5V, with output voltages greater than 5V supported using additional components.

The input voltage can range from 4.5V to 46V. The wide input voltage range, programmable frequency, and integrated 5V LDO make the device extremely flexible and easy to use in a broad range of applications. Support is provided for multi-cell battery systems in addition to traditional DC power supply applications.

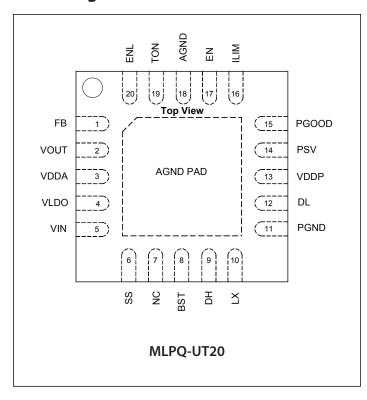

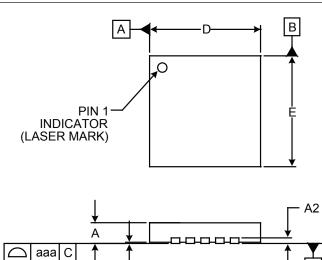

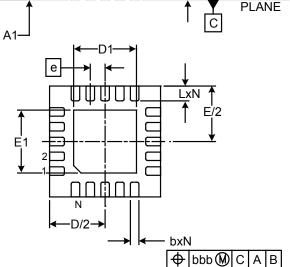

# **Pin Configuration**

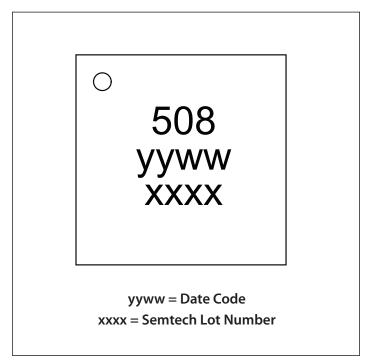

# **Ordering Information**

| Device                           | Package          |

|----------------------------------|------------------|

| SC508ULTRT <sup>(1)(2)</sup>     | MLPQ-UT20        |

| SC508AULTRT <sup>(1)(2)(3)</sup> | MLPQ-UT20        |

| SC508EVB                         | Evaluation Board |

| SC508AEVB                        | Evaluation Board |

#### Notes:

- 1) Available in tape and reel only. A reel contains 3000 devices.

- 2) Lead-free packaging only. Device is WEEE and RoHS compliant and halogen-free.

- 3) AEC-Q100 Qualified.

# **Marking Information**

# **Absolute Maximum Ratings**

| LX to PGND (V)0.3 to +50                                                        |

|---------------------------------------------------------------------------------|

| LX to PGND (V) (transient — 100ns)2 to $+50$                                    |

| DH, BST to PGND (V)0.3 to +55                                                   |

| DH, BST to LX (V)0.3 to +6                                                      |

| DL to PGND (V)0.3 to +6                                                         |

| VIN to PGND (V)0.3 to +50                                                       |

| EN, FB, ILIM, PGOOD to AGND (V)0.3 to +(VDDA + 0.3)                             |

| PSV, SS, TON to AGND (V)0.3 to +(VDDA + 0.3)                                    |

| VLDO, VOUT to AGND (V)0.3 to +(VDDA + 0.3)                                      |

| TON to AGND (V)0.3 to +(VDDA -1.5)                                              |

| ENL to AGND (V)0.3 to VIN                                                       |

| VDDP to PGND, VDDA to AGND (V) $\ \ldots \ 0.3$ to $\ +6$                       |

| VDDA to VDDP (V)                                                                |

| AGND to PGND (V)                                                                |

| $ESDProtectionLevel^{\scriptscriptstyle{(1)}}(kV)\;\ldots\qquad\qquad \qquad 2$ |

|                                                                                 |

# **Recommended Operating Conditions**

| Input Voltage (V)4.5                             | to | 46  |

|--------------------------------------------------|----|-----|

| VDDA to AGND, VDDP to PGND (V) 4.5               | to | 5.5 |

| VOUT to PGND (V) <sup>(2)</sup>                  | to | 5.5 |

| Supports output voltages greater than 5.5V using |    |     |

| external components                              |    |     |

# **Thermal Information**

| St | torage Temperature (°C) $\dots$ -60 to $\dashv$               | -150 |

|----|---------------------------------------------------------------|------|

| Μ  | laximum Junction Temperature (°C) $\dots$                     | 150  |

| 0  | perating Junction Temperature (°C) $\dots$ -40 to $+$         | -125 |

| Tł | hermal resistance, junction to ambient $^{	ext{	iny (°C/W)}}$ | .50  |

| Pe | eak IR Reflow Temperature (°C)                                | 260  |

Exceeding the above specifications may result in permanent damage to the device or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not recommended.

#### NOTES:

- (1) Tested according to JEDEC standard JESD22-A114.

- (2) VOUT pin must not exceed (VDDA pin + 0.3V).

- (3) Calculated from package in still air, mounted to 3 x 4.5 (in), 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

## **Electrical Characteristics** —

Unless specified:  $V_{IN} = 12V$ , VDDA = VDDP = 5V,  $T_{A} = +25^{\circ}C$  for Typ, -40 to  $+85^{\circ}C$  for Min and Max,  $T_{I} < 125^{\circ}C$ , Typical Application Circuit

| Parameter                                     | Conditions                                                                                 |      | Тур  | Max  | Units                                 |

|-----------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|---------------------------------------|

| Input Supplies                                |                                                                                            |      |      |      |                                       |

| Input Supply Voltage (V <sub>IN</sub> )       | VDDA = 5V                                                                                  | 4.5  |      | 46   | V                                     |

| V INIO Three hold(1)                          | Sensed at ENL pin, rising edge                                                             | 1.50 | 1.56 | 1.70 | V                                     |

| V <sub>IN</sub> UVLO Threshold <sup>(1)</sup> | Sensed at ENL pin, falling edge                                                            |      | 1.52 | 1.65 | V                                     |

| V <sub>IN</sub> UVLO Hysteresis               | Sensed at ENL pin; EN = 5V                                                                 |      | 0.04 |      | V                                     |

| VDDA UVLO Threshold                           | Measured at VDDA pin, rising edge                                                          |      | 3.9  | 4.1  | V                                     |

| VDDA OVEO Mireshold                           | Measured at VDDA pin, falling edge                                                         |      | 3.7  | 3.9  | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| VDDA UVLO Hysteresis                          |                                                                                            |      | 0.2  |      | V                                     |

| V Comply Covered                              | Shutdown mode; ENL, EN = 0V, $V_{IN} = 46V$<br>Standby mode; VDDA, VDDP, ENL = 5V, EN = 0V |      | 20   | 35   |                                       |

| V <sub>IN</sub> Supply Current                |                                                                                            |      | 130  |      | μΑ                                    |

# **Electrical Characteristics (continued)**

| Parameter                                 | Conditions                                                                                                              | Min    | Тур   | Max    | Units |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------|

| Input Supplies (continued)                |                                                                                                                         |        |       |        |       |

|                                           | ENL, EN = 0V                                                                                                            |        | 3     | 7      | μΑ    |

|                                           | Power-save operation<br>EN = 5V, PSV = open (float), V <sub>FB</sub> > 600mV                                            |        | 0.4   |        |       |

| VDDA + VDDP Supply Current <sup>(2)</sup> | Ultrasonic Power-save operation<br>$EN = 5V$ , $R_{PSV} = 115k\Omega$ , $V_{FB} > 600 \text{mV}$                        |        | 2.4   |        | mA    |

|                                           | Forced Continuous Mode operation $Operating \ f_{sw} = 220 kHz, \ PSV = VDDA, \ no \ load$                              |        | 13    |        |       |

| FB Comparator Threshold                   | Static $V_{_{\rm IN}}$ and load, 0 to +85 $^{\circ}{\rm C}$                                                             | 0.5952 | 0.600 | 0.6048 | V     |

| To Comparator Tilleshold                  | Static V <sub>IN</sub> and load, -40 to +85 °C                                                                          | 0.594  |       | 0.606  | V     |

| Frequency Range                           | Continuous mode operation                                                                                               |        |       | 1000   | kHz   |

| Timing                                    |                                                                                                                         |        |       |        |       |

| On-Time                                   | Forced Continuous Mode operation $V_{IN} = 30V, V_{OUT} = 3 V, R_{TON} = 600 k\Omega, VDDA = 5V$                        | 1530   | 1700  | 1870   | ns    |

| On-nine                                   | On-time Accuracy; Forced Continuous Mode $V_{IN} = 4.5$ to 10V, $V_{OUT} = 3$ V, $R_{TON} = 600$ k $\Omega$ , VDDA = 5V |        | ±15   |        | %     |

| Minimum On-Time                           |                                                                                                                         |        | 80    |        | ns    |

| Minimum Off-Time                          |                                                                                                                         |        | 250   |        | ns    |

| Ultrasonic Frequency                      | Minimum switching frequency, $R_{psv} = 115kΩ$                                                                          |        | 25    |        | kHz   |

| Soft-Start                                |                                                                                                                         |        |       |        |       |

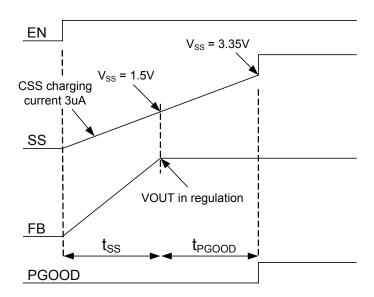

| Soft-Start Charge Current                 |                                                                                                                         |        | 3.0   |        | μΑ    |

| Analog Inputs/Outputs                     |                                                                                                                         |        |       |        |       |

| VOUT Input Resistance                     |                                                                                                                         |        | 500   |        | kΩ    |

| Current Sense                             |                                                                                                                         | ,      |       |        |       |

| Zero Cross Detector Threshold             | LX with respect to PGND                                                                                                 | -3     | 0     | +3     | mV    |

| Power Good                                | ,                                                                                                                       |        |       | 1      |       |

| Power Good Threshold                      | Upper limit, V <sub>FB</sub> > internal 600mV reference                                                                 |        | +20   |        | - %   |

| Power Good Tilleshold                     | Lower limit, V <sub>FB</sub> < internal 600mV reference                                                                 |        | -10   |        | 90    |

| Startup Delay Time                        | EN rising edge to PGOOD rising edge, CSS = 10nF                                                                         |        | 11    |        | ms    |

| Fault (noise immunity) Delay Time         |                                                                                                                         |        | 5     |        | μs    |

| Leakage                                   | PGOOD = high impedance (open)                                                                                           |        |       | 1      | μΑ    |

| Power Good On-Resistance                  | PGOOD = pulled low to AGND                                                                                              |        | 10    |        | Ω     |

# **Electrical Characteristics (continued)**

| Parameter                                               | Conditions                                                                        | Min   | Тур  | Max   | Units |

|---------------------------------------------------------|-----------------------------------------------------------------------------------|-------|------|-------|-------|

| Fault Protection                                        |                                                                                   |       |      |       |       |

| I <sub>LIM</sub> Source Current                         |                                                                                   | 9     | 10   | 11    | μΑ    |

| I <sub>LIM</sub> Source Current Temperature Coefficient |                                                                                   |       | 0.41 |       | %/°C  |

| I <sub>LIM</sub> Comparator Offset                      | With respect to AGND                                                              | -8    | 0    | +8    | mV    |

| Output Under-Voltage Threshold                          | V <sub>FB</sub> with respect to internal 600mV reference,<br>8 consecutive cycles |       | -25  |       | %     |

| Smart Power-Save Protection Threshold                   | V <sub>FB</sub> with respect to internal 600mV reference                          |       | +10  |       | %     |

| Over-Voltage Protection Threshold                       | V <sub>FB</sub> with respect to internal 600mV reference                          |       | +20  |       | %     |

| Over-Voltage Fault Delay                                |                                                                                   |       | 5    |       | μs    |

| Over-Temperature Shutdown                               | 10°C hysteresis                                                                   |       | 165  |       | °C    |

| Logic Inputs/Outputs                                    |                                                                                   |       |      |       |       |

| Logic Input High Voltage — EN                           |                                                                                   | 1.4   |      |       | V     |

| Logic Input High Voltage — PSV                          | Forced Continuous Mode operation; PSV pin with respect to VDDA                    | -0.4  |      |       | V     |

| Logic Input Low Voltage — EN, ENL(3)                    | With respect to AGND                                                              |       |      | 0.4   | V     |

| EN Input Bias Current                                   | EN = VDDA or AGND                                                                 | -10   |      | +10   | μΑ    |

| ENL Input Bias Current                                  | V <sub>IN</sub> = 46V                                                             |       | +11  |       | μΑ    |

| FB Input Bias Current                                   | FB = VDDA or AGND                                                                 | -1    |      | +1    | μΑ    |

| DCV lanut Diag Courant                                  | PSV = VDDA                                                                        |       | 5    | 16    | μΑ    |

| PSV Input Bias Current                                  | PSV ≤ 1.5V                                                                        |       | 1    |       | μΑ    |

| Linear Regulator                                        |                                                                                   |       |      |       |       |

| VLDO Accuracy                                           | VLDO load = 10mA                                                                  | 4.875 | 5.0  | 5.125 | V     |

|                                                         | VLDO < 1V start-up                                                                |       | 13   |       |       |

| Current Limit                                           | 1V < VLDO < 4.5V (typ)                                                            |       | 90   |       | mA    |

|                                                         | Operating, VLDO > 4.5V (typ)                                                      |       | 200  |       |       |

| VLDO to VOUT Switch-over Threshold (4)                  |                                                                                   | -130  |      | +130  | mV    |

| VLDO to VOUT Non-switch-over Threshold (4)              |                                                                                   | -500  |      | +500  | mV    |

| VLDO to VOUT Switch-over Resistance                     | VLDO = VOUT = 5V                                                                  |       | 2.0  |       | Ω     |

| VLDO Drop Out Voltage                                   | V <sub>IN</sub> to VLDO, LDO load = 50mA                                          |       | 1.2  |       | V     |

# **Electrical Characteristics (continued)**

| Parameter                                            | Conditions                              | Min                             | Тур  | Max  | Units |  |  |  |

|------------------------------------------------------|-----------------------------------------|---------------------------------|------|------|-------|--|--|--|

| High-Side Driver (DH, BST, LX)                       | ·                                       | •                               |      |      |       |  |  |  |

| Peak Current VDDP = 5V, DH pin sourcing or sinking 2 |                                         |                                 |      |      |       |  |  |  |

|                                                      | $R_{DH\_PULL-UP,}$ LX < 0.5V, VDDP = 5V |                                 | 3.0  | 6.0  | Ω     |  |  |  |

| On Resistance                                        | $R_{DH\_PULL\_UP}$ LX > 0.5V, VDDP = 5V |                                 | 1.0  | 2.0  | Ω     |  |  |  |

|                                                      | R <sub>DH_PULL-DOWN</sub> , VDDP = 5V   |                                 | 0.6  | 1.2  | Ω     |  |  |  |

| Rise Time                                            | $C_{DH-LX} = 3nF, VDDP = 5V$            |                                 | 22   |      | ns    |  |  |  |

| Fall Time                                            | C <sub>DH-LX</sub> = 3nF, VDDP = 5V     |                                 | 12   |      | ns    |  |  |  |

| Propagation Delay                                    | From FB Input to DH                     |                                 | 45   |      | ns    |  |  |  |

| Shoot-thru Protection Delay                          |                                         |                                 | 45   |      | ns    |  |  |  |

| Bootstrap Switch Resistance                          |                                         |                                 | 16   |      | Ω     |  |  |  |

| Low-Side Driver (DL, VDDP, PGND)                     | ·                                       | '                               | '    | '    |       |  |  |  |

| D. I.C                                               | VDDP = 5V, DL sourcing                  |                                 | 2    |      | А     |  |  |  |

| Peak Current                                         | VDDP = 5V, DL sinking                   |                                 | 4    |      |       |  |  |  |

|                                                      | $R_{DL\_PULL\_UP}$ , $VDDP = 5V$        | $R_{DL\_PULL-UP_{i}} VDDP = 5V$ |      | 2.1  | Ω     |  |  |  |

| On Resistance                                        | $R_{DL\_PULL\_DOWN,} VDDP = 5V$         |                                 | 0.50 | 0.86 | Ω     |  |  |  |

| Rise Time                                            | $C_{DL} = 3nF, VDDP = 5V$               |                                 | 7    |      | ns    |  |  |  |

| Fall Time                                            | $C_{DL} = 3nF, VDDP = 5V$               |                                 | 3.5  |      | ns    |  |  |  |

#### Notes:

- (1)  $V_{IN}$  UVLO is programmable using a resistor divider from VIN to ENL to AGND. The ENL voltage is compared to an internal reference.

- (2) For UPSV and FCM operation, the VDDA and VDDP supply current includes the DH/DL current required to drive the external MOSFETS.

- (3) The ENL pin will enable the LDO with 0.8V typical. The ENL pin  $V_{IN}$  ULVO function will disable the switcher unless the ENL pin exceeds the  $V_{IN}$  UVLO Threshold which is typically 1.56V.

- (4) The switch-over threshold is the maximum voltage differential between the VLDO and VOUT pins which ensures that VLDO will internally switch-over to VOUT. The non-switch-over threshold is the minimum voltage differential between the VLDO and VOUT pins which ensures that VLDO will not switch-over to VOUT.

# **Typical Characteristics (continued)**

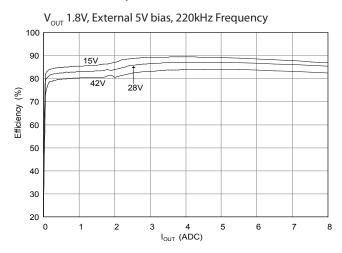

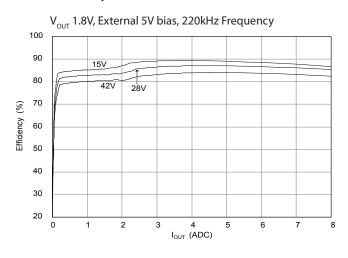

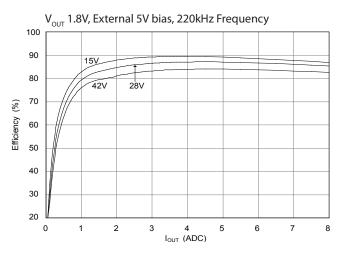

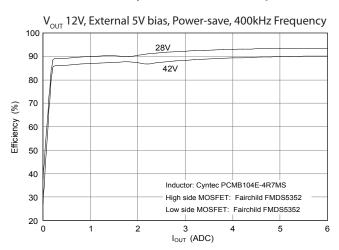

# Efficiency vs Load — PSAVE Mode

## Efficiency vs Load — Ultrasonic PSAVE Mode

## Efficiency vs Load — Forced Continuous Mode

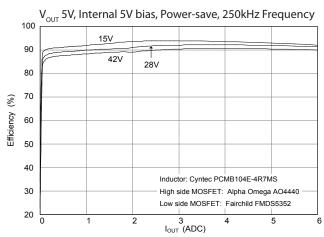

## Efficiency vs Load — 5V output

## Efficiency vs Load — 12V output

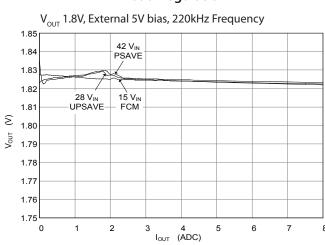

# **Load Regulation**

# **Typical Characteristics (continued)**

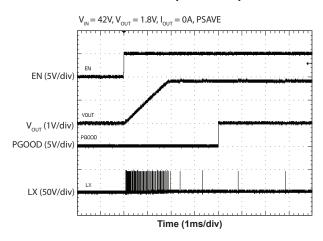

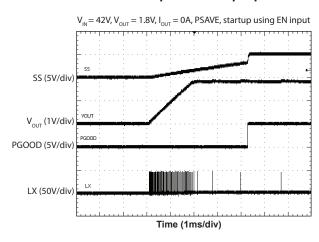

#### Start-up — EN Input

## Start-up — SS ramp-up

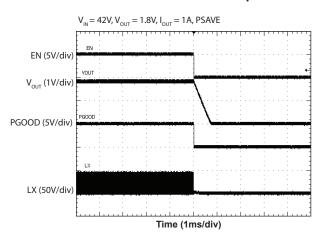

#### Shutdown — EN Input

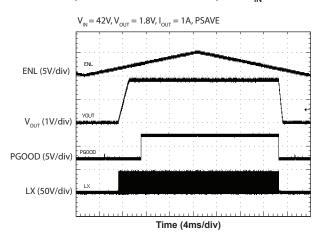

## Start-up, Shutdown — ENL Input (V<sub>IN</sub> UVLO)

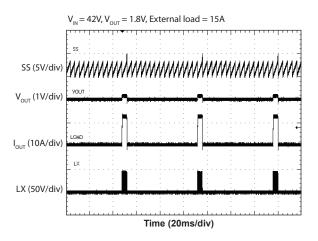

#### **Over-current** — Automatic Restart

# **Typical Characteristics (continued)**

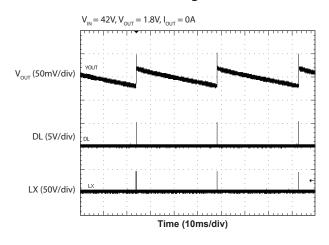

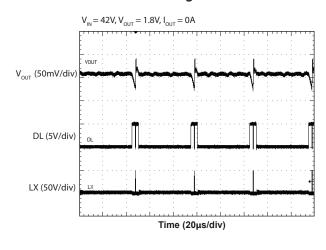

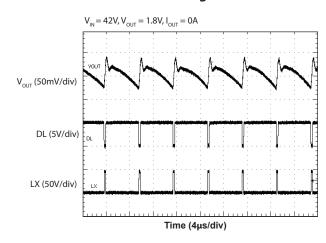

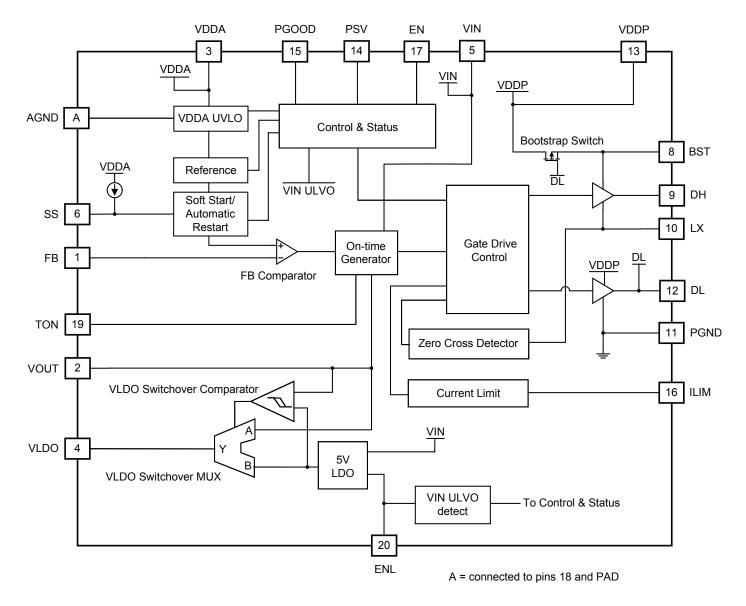

## Switching — PSAVE

# Transient Response — PSAVE

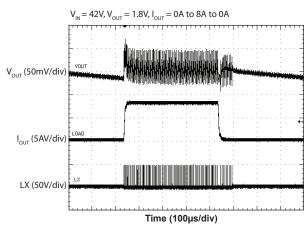

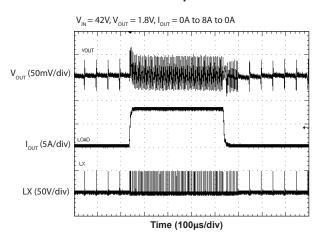

## Switching — UPSAVE

## Transient Response — UPSAVE

## Switching — FCM

#### Transient Response — FCM

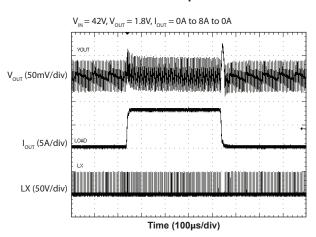

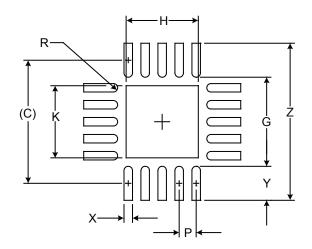

# **Detailed Application Circuit**

## **Key Components**

| Component  | mponent Value |             | Part Number        | Web                   |

|------------|---------------|-------------|--------------------|-----------------------|

| CIN1, CIN2 | 10μF/50V      | Murata      | UMK325BJ106MM-T    | www.murata.com        |

| COUT       | 330μF/6mΩ     | Sanyo       | 2TPF330M6          | edc.sanyo.com         |

| L1         | 1.8µH         | Vishay      | IHLP4040EZER1R8M01 | www.vishay.com        |

| Q1         | AO4440        | Alpha Omega | AO4440             | www.aosmd.com         |

| Q2         | FDMS5352      | Fairchild   | FDMS5352           | www.fairchildsemi.com |

Notes:

(1) 5V: Connect VDDA and VDDP to external 5V supply for external bias. Connect VDDA and VDDP to VLDO for self -biased operation.

(2) RPSV: Use  $115k\Omega$  for Ultrasonic operation.

Remove RPSV for Power-Save operation.

Connect PSV pin to VDDA for Forced Continuous Mode operation.

# **Pin Descriptions**

| Pin # | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                           |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | FB       | Feedback input for switching regulator — connect to an external resistor divider from output — used to program the output voltage.                                                                                                                                                                                                                     |

| 2     | VOUT     | Switcher output voltage sense pin — also the input to the internal switch-over MOSFET between VOUT and VLDO. The voltage at this pin must not exceed the VDDA pin. For output voltages up to 5V connect this pin directly to the switcher output. For output voltages exceeding 5V connect this pin to the switcher output through a resistor divider. |

| 3     | VDDA     | 5V supply input for internal analog circuits — connect to external 5V supply or connect to VLDO — also the sense input for VDDA Under Voltage Lockout (VDDA UVLO).                                                                                                                                                                                     |

| 4     | VLDO     | Output of the 5V LDO — The voltage at this pin must not exceed the voltage at the VDDA pin.                                                                                                                                                                                                                                                            |

| 5     | VIN      | Input supply voltage — connect to the same supply used for the high-side MOSFET. Connect a 100nF capacitor from this pin to AGND to filter high frequency noise.                                                                                                                                                                                       |

| 6     | SS       | Soft-Start — connect an external capacitor to AGND to program the soft start and automatic recovery time.                                                                                                                                                                                                                                              |

| 7     | NC       | No Connection                                                                                                                                                                                                                                                                                                                                          |

| 8     | BST      | Bootstrap pin — connect a 100nF minimum capacitor and series resistor from BST to LX to develop the floating voltage for the high-side gate drive. A 3.3 ohm resistor is recommended.                                                                                                                                                                  |

| 9     | DH       | High-side gate drive output                                                                                                                                                                                                                                                                                                                            |

| 10    | LX       | Switching (phase) node                                                                                                                                                                                                                                                                                                                                 |

| 11    | PGND     | Power ground for the DL and DH drivers and the low-side external MOSFET.                                                                                                                                                                                                                                                                               |

| 12    | DL       | Low-side gate drive output                                                                                                                                                                                                                                                                                                                             |

| 13    | VDDP     | 5V supply input for the DH and DL gate drives — connect to the same 5V supply used for VDDA.                                                                                                                                                                                                                                                           |

| 14    | PSV      | Power-save programming input — connect a resistor to AGND to set a minimum (ultrasonic) power-save frequency — float pin to select power-save with no minimum frequency — pull up to VDDA to disable power-save and select forced continuous mode.                                                                                                     |

| 15    | PGOOD    | Open-drain Power Good indicator — high impedance indicates the switching regulator output is good. An external pull-up resistor is required when connecting the PGOOD signal to external logic.                                                                                                                                                        |

| 16    | ILIM     | Current limit sense pin — used to program the current limit by connecting a resistor from ILIM to LX.                                                                                                                                                                                                                                                  |

| 17    | EN       | Enable input for switching regulator — logic low disables the switching regulator — logic high enables the switching regulator.                                                                                                                                                                                                                        |

| 18    | AGND     | Analog ground                                                                                                                                                                                                                                                                                                                                          |

| 19    | TON      | ON time programming input — set the on-time by connecting through a resistor to AGND.                                                                                                                                                                                                                                                                  |

| 20    | ENL      | Enable input for the LDO and VIN UVLO input for the switching regulator — connect ENL to AGND to disable the LDO — drive to logic high (>1.7V) to enable the LDO and inhibit $V_{\rm IN}$ UVLO — connect to resistor divider from VIN to AGND to program the $V_{\rm IN}$ UVLO threshold.                                                              |

| PAD   | AGND     | Analog ground                                                                                                                                                                                                                                                                                                                                          |

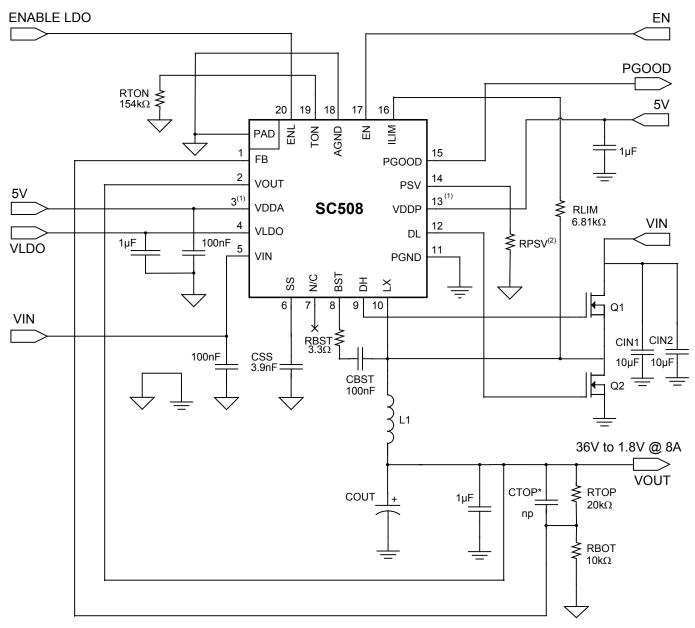

# **Block Diagram**

# **Applications Information**

## **Synchronous Buck Converter**

The SC508 is a step down synchronous DC-DC buck controller with an internal 5V LDO. It provides efficient operation in a space saving 3x3 (mm) 20-pin package. The programmable operating frequency range up to 1MHz enables optimizing the configuration for PCB area and efficiency. For automotive applications, the SC508A is qualified to AEC-Q100.

The controller uses a pseudo-fixed frequency adaptive on-time control. This allows fast transient response which permits the use of smaller output capacitors.

## **Input Voltage Requirements**

The SC508 requires two input supplies for normal operation:  $V_{IN}$  and VDDA/VDDP.  $V_{IN}$  operates over the wide range of 5V to 46V. VDDA and VDDP require a 5V supply which can be from an external source or from the internal LDO. VDDA and VDDP must be derived from the same source voltage.

# **Psuedo-fixed Frequency Adaptive On-time Control**

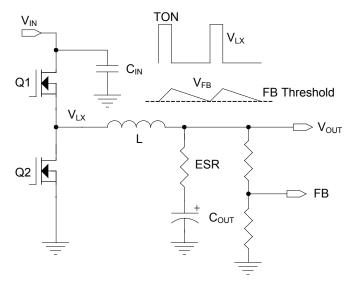

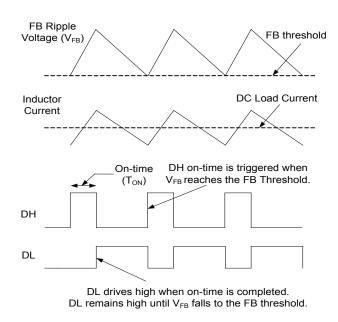

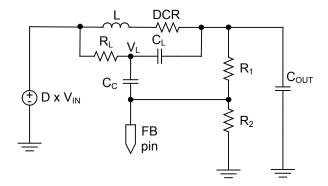

The PWM control method used by the SC508 is pseudo-fixed frequency, adaptive on-time, as shown in Figure 1. The ripple voltage generated at the output capacitor ESR is used as a PWM ramp signal. This ripple is used to trigger the on-time of the controller.

Figure 1 — PWM Control Method, Vour Ripple

The adaptive on-time is determined by an internal one-shot timer. When the one-shot is triggered by the output ripple, the device sends a single on-time pulse to the high-side MOSFET. The pulse period is determined by  $V_{\text{OUT}}$  and  $V_{\text{IN}}$ . The period is proportional to output voltage and inversely proportional to input voltage. With this adaptive on-time configuration, the device automatically anticipates the on-time needed to regulate  $V_{\text{OUT}}$  for the present  $V_{\text{IN}}$  condition and at the selected frequency.

The advantages of adaptive on-time control are:

- Predictable operating frequency compared to other variable frequency methods.

- Reduced component count by eliminating the error amplifier and compensation components.

- Reduced component count by removing the need to sense and control inductor current.

- Fast transient response the response time is controlled by a fast comparator instead of a typically slow error amplifier.

- Reduced output capacitance due to fast transient response.

## **One-Shot Timer and Operating Frequency**

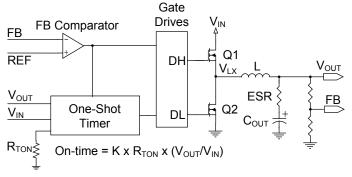

One-shot timer operation is shown in Figure 2. The FB comparator output goes high when  $V_{FB}$  is less than the internal 600mV reference. This feeds into the DH gate drive and turns on the high-side MOSFET, and also starts the one-shot timer. The one-shot timer uses an internal comparator and a capacitor. One comparator input is connected to  $V_{OUT'}$  the other input is connected to the capacitor. When the on-time begins, the capacitor charges from zero volts through a current which is proportional to  $V_{IN}$ . When the capacitor voltage reaches  $V_{OUT'}$  the on-time is completed and the high-side MOSFET turns off.

Figure 2 — On-Time Generation

This method automatically produces an on-time that is proportional to  $V_{\rm OUT}$  and inversely proportional to  $V_{\rm IN}$ . Under steady-state conditions, the switching frequency can be determined from the on-time by the following equation.

$$f_{\text{SW}} = \frac{V_{\text{OUT}}}{T_{\text{ON}} \times V_{\text{IN}}}$$

The SC508 uses an external resistor to set the on-time which indirectly sets the frequency. The on-time can be programmed to provide an operating frequency of up to 1MHz using a resistor between the TON pin and ground. The resistor value is selected by the following equation.

$$R_{TON} = \frac{(T_{ON} - 10ns) \times V_{IN}}{28pF \times V_{OUT}} = \frac{\left(\frac{V_{OUT}}{V_{IN} \times f_{SW}} - 10ns\right) \times V_{IN}}{28pF \times V_{OUT}}$$

The maximum recommended  $R_{TON}$  value is shown by the following equation.

$$R_{\text{TON\_MAX}} = \frac{V_{\text{IN\_MIN}}}{20 \times 1.5 \mu A}$$

Immediately after the on-time, the DL output drives high to energize the low-side MOSFET. DL has a minimum high time of ~250ns, after which DL continues to stay high until one of the following occurs:

- The FB input falls below the 600mV reference

- The Zero Cross Detector trips if power-save is active

Note that the on-time variation increases to typically 15% at input voltages from 4.5 to 10V. In most applications this does not significantly affect overall performance.

# **V**<sub>out</sub> **Voltage Selection**

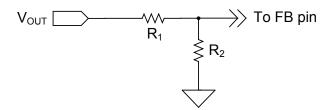

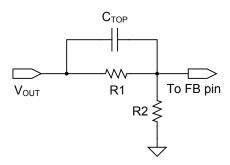

The switcher output voltage is regulated by comparing  $V_{\text{OUT}}$  as seen through a resistor divider at the FB pin to the internal 600mV reference voltage (see Figure 3).

Figure 3 — Output Voltage Selection

Note that this control method regulates the valley of the output ripple voltage, not the DC value. The DC value of  $V_{\text{OUT}}$  is offset by the output ripple according to the following equation.

$$V_{\text{OUT}} = 0.6 \times \left(1 + \frac{R_1}{R_2}\right) + \left(\frac{V_{\text{RIPPLE}}}{2}\right)$$

In some applications a small capacitor CTOP is placed in parallel with R1 to provide a larger ripple signal from VOUT to the FB pin. In these applications, the output voltage VOUT is calculated according to the following equation in which  $\omega$  represents the switching frequency.

$$V_{\text{OUT}} = 0.6 \times \left(1 + \frac{R_1}{R_2}\right) + \left(\frac{V_{\text{RIPPLE}}}{2}\right) \times \sqrt{\frac{1 + \left(R_1 \omega C_{\text{TOP}}\right)^2}{1 + \left(\frac{R_2 \times R_1}{R_2 + R_1} \omega C_{\text{TOP}}\right)^2}}$$

# Configuring V<sub>out</sub> Greater Than 5V

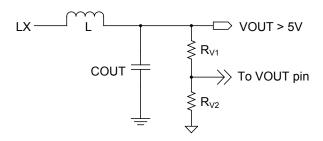

The switcher output voltage can be programmed higher than 5V with careful attention to the VOUT and RTON pins. In these applications the VOUT pin cannot connect directly to the switcher output due to its maximum voltage rating. An additional resistor divider network is required to connect from the switcher output to the VOUT pin as shown in Figure 4.

Figure 4 — Resistor Divider For V<sub>OUT</sub> Exceeding 5V

If the internal LDO is used for bias power, the LDO switch-over function must be inhibited by selecting the resistor divider so that the voltage at the VOUT pin does not exceed 4V; this will inhibit the VLDO switch-over function. If the SC508 bias power is from an external 5V supply and the LDO is disabled by grounding the ENL pin, the voltage at the VOUT pin is not limited to 4V and can be as high as the VDDA supply voltage.

Note that the VOUT pin has an internal  $500k\Omega$  resistor connected to AGND. To minimize the effect of this resistor on the resistor divider ratio, the maximum recommend value for resistor  $R_{v_2}$  in Figure 4 is  $10k\Omega$ .

In addition to the resistor divider, the RTON resistor value must be adjusted. The on-time is generated according to the voltage at the VOUT pin. In order to select the desired on-time and operating frequency, the RTON resistor should be adjusted to a higher value to compensate for the reduced voltage at the VOUT pin. For output voltages exceeding 5V, the required RTON value can be determined by the following equation. The desired operating frequency is f<sub>sw</sub>.

$$R_{TON} = \frac{\left(\frac{V_{OUT}}{V_{IN} \times f_{SW}} - 10ns\right) \times V_{IN}}{28pF \times V_{OUT}} \times \left(1 + \frac{R_{V1}}{R_{V2}}\right)$$

For applications where  $V_{\text{OUT}}$  exceeds 5V, FCM operation is recommended.

## **Forced Continuous Mode Operation**

The SC508 operates the switcher in Forced Continuous Mode (FCM) by connecting the PSV pin to VDDA. The PSV pin should never exceed the VDDA supply. See Figure 5 for FCM waveforms. In this mode one of the power MOSFETs is always on, with no intentional dead time other than to avoid cross-conduction. This results in more uniform frequency across the full load range with the trade-off being reduced efficiency at light loads due to the high-frequency switching of the MOSFETs.

The PSV pin contains a  $5\mu A$  current sink to prevent stray leakage current from pulling the PSV pin up to the VDDA

supply when the PSV pin is floated to select Power-Save operation. To select Forced Continuous Mode operation, the maximum recommended resistance between the VDDA supply and the PSV pin is  $40k\Omega$ .

Figure 5 — Forced Continuous Mode Operation

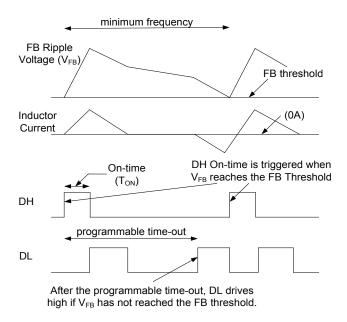

## **Programmable Ultrasonic Power-Save Operation**

The device provides programmable ultrasonic power-save operation at light loads; the minimum operating frequency is programmed by connecting a resistor from PSV to AGND. The SC508 uses the PSV resistor to set an internal timer that monitors the time between consecutive high-side gate pulses. If the time exceeds the programmed timer, DL drives high to turn the low-side MOSFET on. This draws current from  $\boldsymbol{V}_{\text{OUT}}$  through the inductor, forcing both  $V_{OUT}$  and  $V_{FR}$  to fall. When  $V_{FR}$  drops to the 600mV threshold, the next DH on-time is triggered. After the on-time is completed the high-side MOSFET is turned off and the low-side MOSFET turns on, and the internal timer is restarted. The low-side MOSFET remains on until the inductor current ramps down to zero, at which point the low-side MOSFET is turned off. This ends the cycle until  $V_{ER}$ again falls below the 600mV threshold, or the internal timer forces another DL turn-on.

Because the period between on-times is limited to a maximum value, a minimum operating frequency is maintained. Figure 6 shows ultrasonic power-save operation.

Figure 6 — Ultrasonic Power-Save Operation

The equation for determining the  $R_{PSV}$  resistor value is shown next. The desired minimum frequency is  $f_{SWMIN}$ .

$$R_{\text{PSV}} = \frac{1}{350 \text{pF} \times f_{\text{SWMIN}}}$$

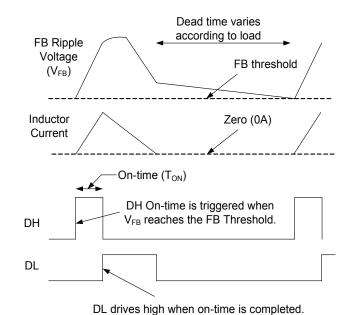

#### **Power-Save Mode Operation**

The device provides power-save operation at light loads with no minimum operating frequency, selected by floating the PSV pin (no connection). In this mode of operation, the zero cross comparator monitors inductor current via the voltage across the low-side MOSFET during the off-time. If the inductor current falls to zero for 8 consecutive switching cycles, the controller enters power-save operation. It will then turn off the low-side MOSFET on each subsequent cycle, provided that the current falls to zero. After the low-side MOSFET is off, both high-side and low-sides MOSFETs remain off until  $V_{\rm FB}$  drops to the 600mV threshold. While the MOSFETs are off the load is supplied by the output capacitor. If the inductor current does not reach zero on any switching cycle, the controller immedi-

ately exits power-save and returns to forced continuous mode. Figure 7 shows power-save operation at light loads.

Figure 7 — Power-Save Operation

DL remains high until inductor current reaches zero.

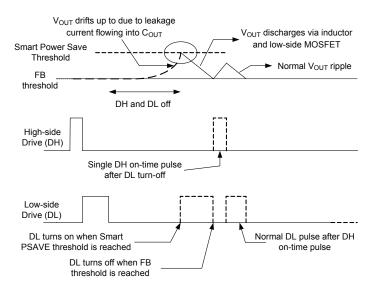

#### **Smart Power-Save Protection**

Active loads may leak current from a higher voltage into the switcher output. Under light load conditions with power-save enabled, this can force  $V_{\text{OUT}}$  to slowly rise and reach the over-voltage threshold, resulting in an over-voltage shutdown. Smart power-save prevents this condition. When the FB voltage exceeds 10% above nominal (exceeds 660mV), the device immediately disables power-save and DL drives high to turn on the low-side MOSFET. This draws current from  $V_{\text{OUT}}$  through the inductor and causes  $V_{\text{OUT}}$  to fall. When  $V_{\text{FB}}$  drops back to the 600mV trip point, a normal  $T_{\text{ON}}$  switching cycle begins. This method prevents over-voltage shutdown by cycling energy from  $V_{\text{OUT}}$  back to  $V_{\text{IN}}$ . It also minimizes operating power under light load conditions by avoiding forced continuous mode operation.

Figure 8 shows typical waveforms for the Smart Powersave feature.

Figure 8 — Smart Power-Save

#### **SmartDrive**<sup>™</sup>

For each DH pulse, the DH driver initially turns on the high-side MOSFET at a slower speed. This produces a softer, controlled turn off and reverse recovery of the low-side diode. Once the low-side diode is off and the LX voltage has risen 0.8V above PGND, the SmartDrive circuit automatically drives the high-side MOSFET on at a rapid rate. This two stage technique reduces switching noise and EMI while maintaining high efficiency and reducing the need for external snubbers.

## **Enable Input for Switching Regulator**

The EN input is a logic level input. When EN is low (grounded), the switching regulator is off and in its lowest power state. When EN is low and VDDA is above the VDDA UVLO threshold, the output of the switching regulator soft-discharges into the VOUT pin through an internal  $2k\Omega$  resistor. When EN is a logic high ( $\geq 1V$ ) the switching regulator is enabled.

The EN input has internal resistors —  $2M\Omega$  pullup to VDDA, and a  $1M\Omega$  pulldown to AGND. These resistors will normally cause the EN voltage to be near the logic high trip point as VDDA reaches the VDDA UVLO threshold. To prevent undesired toggling of EN and erratic start-up performance, the EN pin should not be allowed to float as open-circuit.

Note that the LDO enable pin (ENL) can also disable the switching regulator through the  $V_{\rm IN}$  UVLO function. Refer to the ENL Pin and  $V_{\rm IN}$  UVLO section.

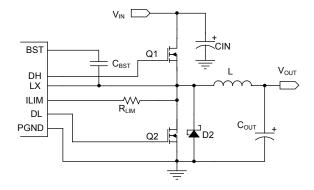

#### **Current Limit Protection**

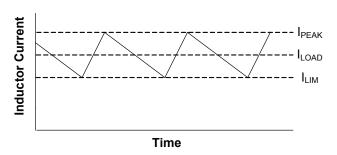

The SC508 features programmable current limiting, which is accomplished using the  $RDS_{(ON)}$  of the lower MOSFET for current sensing. The current limit is set by R<sub>IIM</sub> resistor which connects from the ILIM pin to the drain of the lowside MOSFET. When the low-side MOSFET is on, an internal 10µA current flows from the ILIM pin and through the R resistor, creating a voltage drop across the resistor. While the low-side MOSFET is on, the inductor current flows through it and creates a voltage across the RDS<sub>(ON)</sub>. The voltage across the MOSFET is negative with respect to PGND. If this MOSFET voltage drop exceeds the voltage across R<sub>IM</sub>, the voltage at the ILIM pin will be negative and current limit will activate. The current limit then keeps the low-side MOSFET on and prevents another high-side ontime, until the current in the low-side MOSFET reduces enough to bring the ILIM pin voltage up to zero. This method regulates the inductor valley current at the level shown by  $I_{\text{IIM}}$  in Figure 9.

Figure 9 — Valley Current Limit

The current limit schematic with the  $R_{LIM}$  resistor is shown in Figure 10.

Figure 10 — Valley Current Limit

Setting the valley current limit to 10A results in a peak inductor current of 10A plus peak ripple current. In this situation the average current through the inductor is 10A plus one-half the peak-to-peak ripple current.

The R<sub>LIM</sub> value is calculated by the next equation.

$$R_{\text{LIM}} = \frac{RDS_{\text{ON}} \times I_{\text{LIM}}}{10 \mu A}$$

The internal 10 $\mu$ A current source is temperature compensated at 4100ppm in order to provide tracking with the RDS<sub>ON</sub>.

## **Soft-Start of PWM Regulator**

The SC508 has a programmable soft-start time that is controlled by an external capacitor at the SS pin. During the soft-start time, the controller sources  $3\mu A$  from the SS pin to charge the capacitor. During the start-up process (Figure 11), 40% of the voltage ramp at the SS pin is used as the reference for the FB comparator. The PWM comparator issues an on-time pulse when the FB voltage is less than 40% of the SS voltage, which forces the output voltage to follow the SS ramp. The output voltage reaches regulation when the SS pin voltage exceeds 1.5V and the FB reaches the 600mV threshold. The time between the first LX pulse and VOUT reaching the regulation point is the soft-start time ( $t_{ss}$ ). The calculation for the soft-start time is shown by the following equation.

$$t_{\text{SS}} = \frac{C_{\text{SS}} \times 1.5V}{3\mu\text{A}}$$

After the SS capacitor voltage reaches 1.5V, the SS capacitor continues to charge until the SS voltage is equal to 67% of VDDA. At this time the Power Good monitor compares the FB pin to the 600mV reference and sets the PGOOD output high (open drain) if VOUT is in regulation. The time between VOUT reaching the regulation point and the PGOOD output going high is shown by the following equation.

$$t_{PGOOD} = \frac{C_{SS}}{3\mu A} \times \left(\frac{2 \times VDDA}{3} - 1.5V\right)$$

The time from the rising edge of the EN pin to the PGOOD output going high is shown by the following equation.

$$t_{\text{EN\_GOOD}} = \frac{C_{\text{SS}}}{3\mu\text{A}} \times \left(\frac{2 \times \text{VDDA}}{3}\right)$$

After the Power Good Start-up Delay Time is completed, the SS pin is internally pulled up to the VDDA supply.

The soft-start cycle and Power Good timing can be seen in the Figure 11.

Figure 11 — Soft-start Cycle and Power Good timing

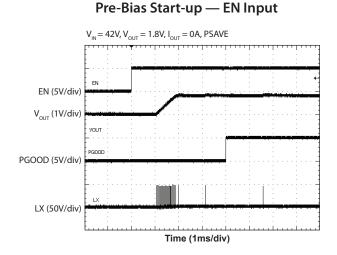

## **Pre-Bias Start-up**

SC508 can support soft-start with an output pre-bias. The SS ramp time is the same as a normal start-up when the output voltage starts from zero. Under a pre-bias start-up, the DH and DL drivers inhibit switching until 40% of the

ramp at the SS pin equals the pre-bias FB voltage level. Pre-bias start-up is achieved by turning off the lower MOSFET when the inductor current reaches zero during the soft-start cycle. This method prevents the output voltage from decreasing.

## **Power Good Output**

The PGOOD (power good) output is an open-drain output which requires an external pull-up resistor. During start-up, PGOOD is held low and is not allowed to transition high until the FB pin is in regulation and the SS pin has reached 67% of VDDA. The time from EN going high to PGOOD going high is typically 11ms for CSS = 10nF.

When the voltage at the FB pin is 10% below the nominal voltage, PGOOD is pulled low. Once PGOOD pulls low there is typically 2% hysteresis to prevent chatter on the PGOOD output.

PGOOD will transition low if the FB voltage exceeds +20% of nominal (720mV), which is also the over-voltage shutdown threshold. PGOOD also pulls low if the EN pin is low and VDDA is present.

## **Output Over-Voltage Protection**

Over-voltage protection (OVP) becomes active as soon as the device is enabled. The OVP threshold is set at 600mV +20% (720mV). There is a 5µs delay built into the OVP detector to prevent false transitions. When  $V_{FB}$  exceeds the OVP threshold, DL is driven high and the low-side MOSFET is turned on. DL remains high and the controller remains off while the device goes through the automatic fault recovery cycle. When the automatic recovery cycle is completed, the device will attempt a new soft-start cycle. At the start of the soft-start cycle, the DL output will go low for typically 30usec while the controller initializes the soft-start sequence. PGOOD is also low after an OVP event.

#### **Output Under-Voltage Protection**

When  $V_{FB}$  falls 25% below its nominal voltage (falls to 450mV) for eight consecutive clock cycles, the switcher is shut off and the DH and DL drives are pulled low to tristate the MOSFETs. The controller stays off while the device goes through the automatic fault recovery cycle.

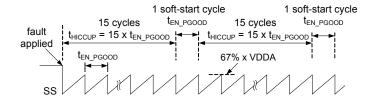

#### **Automatic Fault Recovery**

The SC508 includes an automatic recovery feature (hiccup mode upon fault). If the switcher output is shut down due to a fault condition, the device uses the SS capacitor as a timer. Upon fault detection the SS pin is pulled low and then begins charging through the internal 3µA current source. When the SS capacitor reaches 67% of VDDA, the SS pin is again pulled low, after which the SS capacitor begins another charging cycle. The SS capacitor will be used for 15 cycles of charging from 0 to 67% of VDDA. (For Over-voltage and Over-Temperature faults, the count will be 16 cycles instead of 15.) During these cycles the switcher is off and there is no MOSFET switching.

During the next charging cycle, the normal soft-start routine is implemented and the MOSFETs begin switching. Switching continues until the Power Good Start-up Delay Time is reached. If the switcher output is still in a fault condition, the switcher will again shut down and force 15 cycles of SS charging (16 cycles in the case of an Over-voltage or Over-Temperature fault) before attempting another soft-start. The long delay between soft-start cycles reduces the average power loss in the power components.

The automatic recovery timing is shown in Figure 12.

Figure 12 — Automatic Recovery Timing

The control of the low-side MOSFET during an Overvoltage fault is handled differently from other faults. If the fault was due to an over-voltage condition, the DL output will remain high during 16 SS charging cycles. For all other faults, the DL output will remain low. However, if the FB pin exceeds the Over-voltage threshold, the charging of the SS capacitor will not occur, and the DL output will remain high. If the FB pin falls below the OVP threshold, 16 SS charging cycles will occur while DL remains high. When the next start-up cycle commences, DL will drive

low for typically 30us as the controller re-initializes the internal soft-start routine.

Note that LDO faults will not be automatically recovered by the hiccup restart feature, refer to the LDO Thermal Limitations section.

#### **VDDA UVLO and POR**

The VDDA Under-Voltage Lock-Out (UVLO) circuitry inhibits switching and tri-states the DH/DL drivers until VDDA rises above 3.9V. When VDDA exceeds 3.9V, an internal POR (Power-On Reset) resets the fault latch and the soft-start circuitry and then the SC508 is ready to begin a soft-start cycle. The switcher will shut off if VDDA falls below 3.6V. VDDP does not have UVLO protection.

## **LDO Regulator**

When the LDO is providing bias power to the device, a minimum  $0.1\mu F$  capacitor referenced to AGND is required, along with a minimum  $1\mu F$  capacitor referenced to PGND to filter the gate drive pulses. Refer to the PCB Layout Guidelines section.

# ENL Pin and $V_{IN}$ UVLO

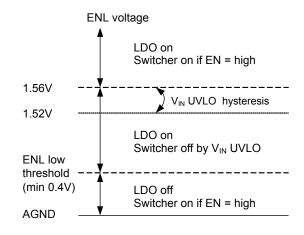

The ENL pin is also used for the  $V_{\rm IN}$  under-voltage lockout ( $V_{\rm IN}$  UVLO) for the switcher. The  $V_{\rm IN}$  UVLO voltage is programmable via a resistor divider at the  $V_{\rm IN}$  ENL and AGND pins. The  $V_{\rm IN}$  UVLO function has a typical threshold of 1.56V on the  $V_{\rm IN}$  rising edge. The falling edge threshold is 1.52V.

Timing is important when driving ENL with logic and not using the  $V_{\rm IN}$  UVLO capability. The ENL pin must transition from high to low within 2 switching cycles to avoid the PWM output turning off. If ENL goes below the  $V_{\rm IN}$  UVLO threshold and stays above 1V, then the switcher will turn off but the LDO will remain on.

Note that it is possible to operate the switcher with the LDO disabled, but the ENL pin must be below the logic low threshold (0.4V maximum), otherwise the  $V_{\rm IN}$  UVLO function will disable the switcher.

The next table summarizes the function of the ENL and EN pins, with respect to the rising edge of ENL.

| EN   | ENL           | LDO status | Switcher status |

|------|---------------|------------|-----------------|

| low  | low, < 0.4V   | off        | off             |

| high | low, < 0.4V   | off        | on              |

| low  | high, < 1.52V | on         | off             |

| high | high, < 1.52V | on         | off             |

| low  | high, > 1.56V | on         | off             |

| high | high, > 1.56V | on         | on              |

Figure 13 shows the ENL voltage thresholds and their effect on LDO and Switcher operation.

Figure 13 — ENL Thresholds

## **ENL Logic Control of PWM Operation**

When the ENL input exceeds the  $V_{\rm IN}$  UVLO threshold of 1.56V, internal logic checks the PGOOD signal. If PGOOD is high, the switcher is already running and the LDO will start without affecting the switcher. If PGOOD is low, the device disables PWM switching until the LDO output has reached 90% of its final value. This delay prevents the additional current needed by the DH and DL gate drives from overloading the LDO at start-up.

#### **LDO Start-up**

Before LDO start-up, the device checks the status of the following signals to ensure proper operation can be maintained.

- 1. ENL pin

- 2. VLDO output

- 3. V<sub>IN</sub> input voltage

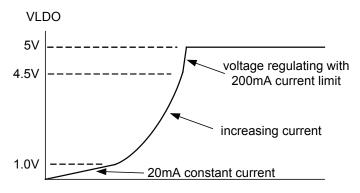

When the ENL pin is high and  $V_{\rm IN}$  voltage is available, the LDO will begin start-up. During the initial phase when  $V_{\rm LDO}$  is below 1V, the LDO initiates a current-limited start-up (typically 20mA). This protects the LDO from thermal damage if the VLDO pin is shorted to ground. As  $V_{\rm LDO}$  exceeds 1V, the start-up current gradually increases to 80mA. When  $V_{\rm LDO}$  reaches 4.5V, the LDO current limit increases to 200mA and the LDO output rises quickly to 5.0V. The LDO start-up profile is shown in Figure 14.

Figure 14 — LDO Start-Up

## **LDO Thermal Limitations**

The LDO is not protected by the Over-Temperature shutdown feature. If the LDO output is loaded externally, the resulting power loss can cause overheating and failure of the LDO.

In typical applications where the LDO is used to power only the SC508 and the external MOSFETs, the current supplied by the LDO is typically below 30mA and temperature rise is acceptable.

The LDO output is protected against heavy overloading or short circuits as shown in Figure 14. When the LDO load is enough to keep the LDO output below 1V, the available-current from the LDO is typically 20mA, which limits the power loss and prevents LDO overheating.

## **LDO Switch-Over Operation**

The SC508 includes a switch-over function for the LDO. The switch-over function is designed to increase efficiency

by using the more efficient DC-DC converter to power the IC, avoiding the less efficient LDO regulator when possible. The switch-over function connects the VLDO pin directly to the VOUT pin through an internal switch. When the switch-over is complete the LDO is turned off, which reduces operating power loss. If the LDO output is used to bias the SC508, then after switch-over the device is self-powered from the switching regulator with the LDO turned off.

After the switcher completes soft-start and the PGOOD delay, the switch-over logic waits for 32 switching cycles before it starts the switch-over. There are two methods of completing the switch-over of  $V_{\rm LDO}$  to  $V_{\rm OLIT}$ .

In the first method, the LDO is already in regulation when the DC-DC converter is enabled. As soon as the PGOOD output goes high, the 32 cycle count is started. The voltages at the VLDO and VOUT pins are then compared; if the two voltages are within ±300mV of each other, the VLDO pin connects to the VOUT pin using an internal switch, and the LDO is turned off.

In the second method, the DC-DC converter is already running and the LDO is enabled. In this case the 32 cycle count is started as soon as the LDO reaches 90% of its final value. At this time, the VLDO and VOUT pins are compared, and if within  $\pm 300$ mV the switch-over occurs and the LDO is turned off.

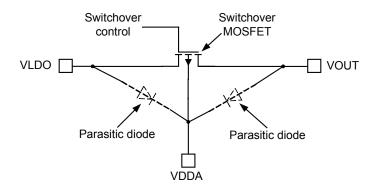

#### **Switch-over MOSFET Parasitic Diodes**

The switch-over MOSFET contains parasitic diodes that are inherent to its construction, as shown in Figure 15.

Figure 15— Switch-over MOSFET Parasitic Diodes

It is important to prevent forward bias of these diodes. The following two conditions must be satisfied in order for the parasitic diodes to stay off.

- $VDDA \ge V_{LDO}$

- $VDDA \ge V_{OUT}^{EDO}$

If either  $V_{LDO}$  or  $V_{OUT}$  is higher than VDDA, the respective diode will turn on and the SC508 operating current will then flow through this diode. This has the potential of damaging the device.

## Using the Internal LDO to Bias the SC508

The following steps must be followed when using the internal LDO to bias the device.

- Connect VDDA and VDDP to VLDO before enabling the LDO.

- During the initial start-up the LDO, when the LDO output is less than 1V, the external load should not exceed 10mA. Above 1V, any external load on VLDO should not exceed 40mA until the LDO voltage has reached 4.5V.

- Review any external loads connected to the LDOoutput to prevent overheating of the LDO.

When the switch-over feature is used and the VDDA/VDDP power comes from the VOUT pin, the EN and ENL inputs must be used carefully. Do not connect the EN pin directly to VDDA or another supply voltage. If this is done, driving the ENL pin low (to AGND) will turn off the LDO and the LDO switch-over MOSFET, but the switcher will continue operating. V<sub>OUT</sub> will feed into the LDO output and the VDDA/VDDP supplies through the internal parasitic diode. This can potentially damage the device, and also prevents the switcher from shutting off until the VDDA supply drops below the VDDA UVLO threshold. For these applications a dedicated logic signal is required to drive EN low and disable the switcher. This signal can be combined with the ENL signal if needed, as long as the EN pin does not exceed Absolute Maximum Ratings.

#### **LDO Usage at Low Input Voltage**

Applications requiring steady-state or transient operation at low input voltages ( $V_{IN}$  below 6.5V) may use the internal LDO to bias the VDDA/VDDP pins within limitations. There

are limitations to both startup and normal operation as explained below.

When starting up using the internal LDO, switcher operation is inhibited until the LDO output reaches 4.5V. During this time, the LDO start-up is implemented using a current source. At low  $V_{\rm IN}$  it is important to not apply an external load to the LDO, in order to allow the LDO output to reach the 4.5V threshold and allow switching to begin.

Once switching begins, LDO operation transitions from current-source operation to voltage regulation. The minimum operating  $V_{\rm IN}$  is then limited by the RDS<sub>ON</sub> of the internal LDO MOSFET. The current required to power the SC508 and external MOSFET gates causes a voltage drop from the  $V_{\rm IN}$  pin to the VLDO pin. The VLDO pin must stay above 4.5V, otherwise the LDO control will revert back to current-source operation, causing more voltage drop at the LDO output. The RDS<sub>ON</sub> of the LDO mosfet at low  $V_{\rm IN}$  is typically 24 ohms at 25°C.

## **Design Procedure**

When designing a switch mode supply the input voltage range, load current, switching frequency, and inductor ripple current must be specified.

The maximum input voltage ( $V_{INMAX}$ ) is the highest specified input voltage. The minimum input voltage ( $V_{INMIN}$ ) is determined by the lowest input voltage including the voltage drops due to connectors, fuses, switches, and PCB traces. The following parameters define the design.

- Nominal output voltage (V<sub>OUT</sub>)

- Static or DC output tolerance

- Transient response

- Maximum load current (I<sub>OUT</sub>)

There are two values of load current to evaluate — continuous load current and peak load current. Continuous load current relates to thermal stresses which drive the selection of the inductor and input capacitors. Peak load current determines instantaneous component stresses and filtering requirements such as inductor saturation, output capacitors, and design of the current limit circuit.

The following values are used in this design.

- $V_{IN} = 28V \pm 10\%$

- $V_{OUT} = 1.8V \pm 4\%$

- $f_{SW} = 220 \text{kHz}$

- Load = 8A maximum

#### **Frequency Selection**

Selection of the switching frequency requires making a trade-off between the size and cost of the external filter components (inductor and output capacitor) and the power conversion efficiency.

The desired switching frequency is 220kHz.

A resistor,  $R_{TON}$  is used to program the on-time (indirectly setting the frequency) using the following equation.

$$R_{TON} = \frac{(T_{ON} - 10ns) \times V_{IN}}{28pF \times V_{OUT}}$$

To select  $R_{TON}$ , use the maximum value for  $V_{IN}$ , and for  $T_{ON}$  use the value associated with maximum  $V_{IN}$ .

$$T_{ON} = \frac{V_{OUT}}{V_{INMAX} \times f_{SW}}$$

$$T_{ON} = 266 \text{ ns at } 30.8 V_{IN}, 1.8 V_{OUT}, 220 \text{kHz}$$

Substituting for  $\rm R_{TON}$  results in the following solution.

$$R_{TON} = 156k\Omega$$

, use  $R_{TON} = 154k\Omega$

#### **Inductor Selection**

In order to determine the inductance, the ripple current must first be defined. Low inductor values result in smaller size but create higher ripple current which can reduce efficiency. Higher inductor values will reduce the ripple current/voltage and for a given DC resistance are more efficient. However, larger inductance translates directly into larger packages and higher cost. Cost, size, output ripple, and efficiency are all used in the selection process.

The ripple current will also set the boundary for powersave operation. The switching will typically enter powersave mode when the load current decreases to 1/2 of the ripple current. For example, if ripple current is 4A then Power-save operation will typically start for loads less than 2A. If ripple current is set at 40% of maximum load current, then power-save will start for loads less than 20% of maximum current.

The inductor value is typically selected to provide a ripple current that is between 25% to 60% of the maximum load current. This provides an optimal trade-off between cost, efficiency, and transient performance.

During the DH on-time, voltage across the inductor is  $(V_{IN} - V_{OUT})$ . The following equation for determining inductance is shown.

$$L = \frac{(V_{IN} - V_{OUT}) \times T_{ON}}{I_{RIPPLE}}$$

In this example the inductor ripple current is set approximately equal to 50% of the maximum load current. Thus ripple current target will be 50% x 8A or 4A.

To find the minimum inductance needed, use the  $V_{IN}$  and  $T_{ON}$  values that correspond to  $V_{INMAX}$ .

$$L = \frac{(30.8 - 1.8) \times 266 \text{ns}}{4A} = 1.93 \mu H$$

A slightly smaller value of  $1.8\mu H$  is selected. This will increase the maximum  $I_{RIPPIF}$  to 4.3A.

Note that the inductor must be rated for the maximum DC load current plus 1/2 of the ripple current.

The ripple current under minimum  $V_{IN}$  conditions is also checked using the following equations.

$$T_{ON\_VINMIN} = \frac{28pF \times R_{TON} \times V_{OUT}}{V_{INMIN}} + 10ns = 318ns$$

$$I_{RIPPLE} = \frac{(V_{IN} - V_{OUT}) \times T_{ON}}{I}$$

$$I_{\text{RIPPLE\_VINMIN}} = \frac{(25.2 - 1.8) \times 318 ns}{1.8 \mu H} = 4.13 A$$

#### **Capacitor Selection**

The output capacitors are chosen based on required ESR and capacitance. The maximum ESR requirement is controlled by the output ripple requirement and the DC tolerance. The output voltage has a DC value that is equal to the valley of the output ripple plus 1/2 of the peak-to-peak ripple. Change in the output ripple voltage will lead to a change in DC voltage at the output.

The design goal is for the output voltage regulation to be  $\pm 4\%$  under static conditions. The internal 600mV reference tolerance is 1%. Allowing 1% tolerance from the FB resistor divider, this allows 2% tolerance due to  $V_{OUT}$  ripple. Since this 2% error comes from 1/2 of the ripple voltage, the allowable ripple is 4%, or 72mV for a 1.8V output.

The maximum ripple current of 4.3A creates a ripple voltage across the ESR. The maximum ESR value allowed is shown by the following equations.

$$ESR_{MAX} = \frac{V_{RIPPLE}}{I_{RIPPLEMAX}} = \frac{72mV}{4.3A}$$

$$ESR_{MAX} = 16.7 \text{ m}\Omega$$

The output capacitance is chosen to meet transient requirements. A worst-case load release, from maximum load to no load at the exact moment when inductor current is at the peak, determines the required capacitance. If the load release is instantaneous (load changes from maximum to zero in < 1 $\mu$ s), the output capacitor must absorb all the inductor's stored energy. This will cause a peak voltage on the capacitor according to the following equation.

$$COUT_{MIN} = \frac{L\left(I_{OUT} + \frac{1}{2} \times I_{RIPPLEMAX}\right)^{2}}{\left(V_{PEAK}\right)^{2} - \left(V_{OUT}\right)^{2}}$$

Assuming a peak voltage  $V_{\text{peak}}$  of 1.98 (180mV rise upon load release), and a 8A load release, the required capacitance is shown by the next equation.

$$COUT_{MIN} = \frac{1.8\mu H \left(8 + \frac{1}{2} \times 4.3\right)^{2}}{\left(1.98\right)^{2} - \left(1.80\right)^{2}}$$

$$COUT_{MIN} = 272\mu F$$

If the load release is relatively slow, the output capacitance can be reduced. At heavy loads during normal switching, when the FB pin is above the 600mV reference, the DL output is high and the low-side MOSFET is on. During this time, the voltage across the inductor is approximately -V<sub>OUT</sub>. This causes a down-slope or falling di/dt in the inductor. If the load di/dt is not faster than the -di/dt in the inductor, then the inductor current will tend to track the falling load current. This will reduce the excess inductive energy that must be absorbed by the output capacitor, therefore a smaller capacitance can be used.

The following can be used to calculate the needed capacitance for a given  $dl_{LOAD}/dt$ . Peak inductor current is shown by the next equation.

$$I_{LPK} = I_{MAX} + 1/2 \times I_{RIPPLEMAX}$$

$$I_{LPK} = 8 + 1/2 \times 4.3 = 10.2A$$

Rate of change of Load Current =  $\frac{dI_{LOAD}}{dt}$

I<sub>MAX</sub> = maximum load release = 8A

$$C_{\text{OUT}} = I_{\text{LPK}} \times \frac{I_{\text{LPK}}}{V_{\text{OUT}}} - \frac{I_{\text{MAX}}}{dI_{\text{LOAD}}} \times dt$$

$$2(V_{\text{PK}} - V_{\text{OUT}})$$

#### Example

$$\frac{dI_{LOAD}}{dt} = \frac{2.5A}{\mu s}$$

The preceding rate of load change would cause the output current to move from 8A to zero in 3.2µs.

$$C_{\text{OUT}} = 10.2 \times \frac{1.8 \mu H \times \frac{10.2}{1.8} - \frac{8}{2.5} \times 1 \mu s}{2 \times \left(1.98 - 1.8\right)}$$

$$C_{out} = 198 \mu F$$

Note that  $C_{OUT}$  is much smaller in this example,  $198\mu F$  compared to  $272\mu F$  based on a worst-case load release. To meet the two design criteria of minimum  $272\mu F$  and

maximum 16.7m $\Omega$  ESR, select a capacitor rated at 330 $\mu$ F and 6m $\Omega$  ESR.

It is recommended that an additional small capacitor with a value of 1 to  $10\mu F$  be placed in parallel with  $C_{\text{OUT}}$  in order to filter high frequency switching noise.

# **Stability Considerations**

Unstable operation is possible with adaptive on-time controllers, and usually takes the form of double-pulsing or ESR loop instability.

Double-pulsing occurs due to switching noise seen at the FB input or because the FB ripple voltage is too low. This causes the FB comparator to trigger prematurely after the 250ns minimum off-time has expired. In extreme cases the noise can cause three or more successive on-times. Double-pulsing will result in higher ripple voltage at the output, but in most applications it will not affect operation. This form of instability can usually be avoided by providing the FB pin with a smooth, clean ripple signal that is at least 10mVp-p, which may dictate the need to increase the ESR of the output capacitors. It is also imperative to provide a proper PCB layout as discussed in the Layout Guidelines section.

Another way to eliminate doubling-pulsing is to add a small capacitor across the upper feedback resistor, as shown in Figure 16. This capacitor should be left unpopulated unless it can be confirmed that double-pulsing exists. Adding the  $C_{\text{TOP}}$  capacitor will couple more ripple into FB to help eliminate the problem. An optional connection on the PCB should be available for this capacitor.

Figure 16 — Capacitor Coupling to FB Pin

NOTE: The  $C_{TOP}$  capacitor can moderately affect the DC output voltage, refer to the section on  $V_{OUT}$  voltage selection.

ESR loop instability is caused by insufficient ESR. The details of this stability issue are discussed in the ESR Requirements section. The best method for checking stability is to apply a zero-to-full load transient and observe the output voltage ripple envelope for overshoot and ringing. Ringing for more than one cycle after the initial step is an indication that the ESR should be increased.

One simple way to solve this problem is to add trace resistance in the high current output path. A side effect of adding trace resistance is decreased load regulation.

#### **ESR Requirements**

A minimum ESR is required for two reasons. One reason is to generate enough output ripple voltage to provide 10mVp-p at the FB pin (after the resistor divider) to avoid double-pulsing.

The second reason is to prevent instability due to insufficient ESR. The on-time control regulates the valley of the output ripple voltage. This ripple voltage is the sum of the two voltages. One is the ripple generated by the ESR, the other is the ripple due to capacitive charging and discharging during the switching cycle. For most applications the minimum ESR ripple voltage is dominated by the output capacitors, typically SP or POSCAP devices. For stability the ESR zero of the output capacitor should be lower than approximately one-third the switching frequency. The formula for minimum ESR is shown by the following equation.

$$\text{ESR}_{\text{MIN}} = \frac{3}{2 \times \pi \times C_{\text{QUT}} \times f_{\text{sw}}}$$

#### **Using Ceramic Output Capacitors**

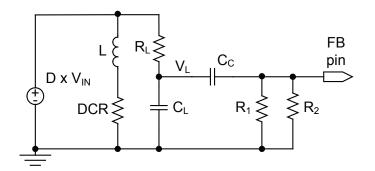

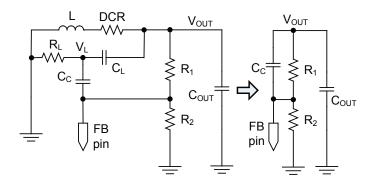

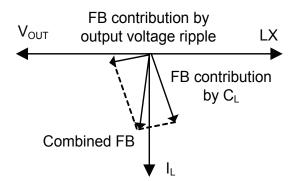

When using high ESR value capacitors, the feedback voltage ripple lags the phase node voltage by 90 degrees and the converter is easily stabilized. When using ceramic output capacitors, the ESR value is normally too small to meet the above ESR criteria. As a result, the feedback voltage ripple is 180 degrees from the phase node leading to unstable operation. In this application it is necessary to add a small virtual ESR network that is composed of two capacitors and one resistor, as shown by  $\rm R_L$ ,  $\rm C_L$ , and  $\rm C_C$  in Figure 17.

Figure 17 — Virtual ESR Ramp Circuit

The ripple voltage at FB is a superposition of two voltage sources: the voltage across  $C_L$  and the output ripple voltage. They are defined in the following equations.

$$Vc_{L} = \frac{I_{L} \times DCR(s \times L / DCR + 1)}{S \times R_{L}C_{L} + 1}$$

$$\Delta V_{\text{OUT}} = \frac{\Delta I_{L}}{8C \times f_{\text{SW}}}$$

Figure 18 shows the equivalent circuit for calculating the magnitude of the ripple contribution at the FB pin due to C<sub>1</sub>.

Figure 18 — FB Voltage by CL Voltage

The magnitude of the FB ripple contribution due to  $C_L$  is shown by the following equation.

$$VFBc_{L} = Vc_{L} \times \frac{(R_{1}//R_{2}) \times S \times C_{C}}{(R_{1}//R_{2}) \times S \times C_{C} + 1}$$

Figure 19 shows the equivalent circuit for calculating the magnitude of the ripple contribution due to the output voltage ripple.

Figure 19 — FB Voltage by Output Voltage

The magnitude of the FB ripple contribution due to output voltage ripple is shown by the following equation.

$$VFB\Delta V_{OUT} = \Delta V_{OUT} \times \frac{R_2}{R_1 /\!/ \frac{1}{S \times C_C} + R_2}$$