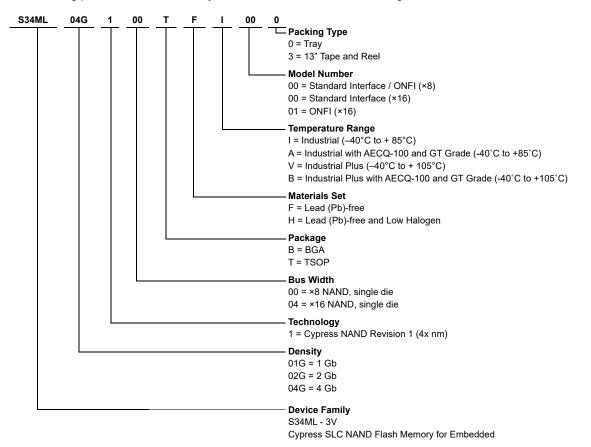

# 1 Gb/2 Gb/4 Gb, 3 V, SLC NAND Flash for Embedded

## **Distinctive Characteristics**

- Density

- □ 1 Gb/ 2 Gb / 4 Gb

- Architecture

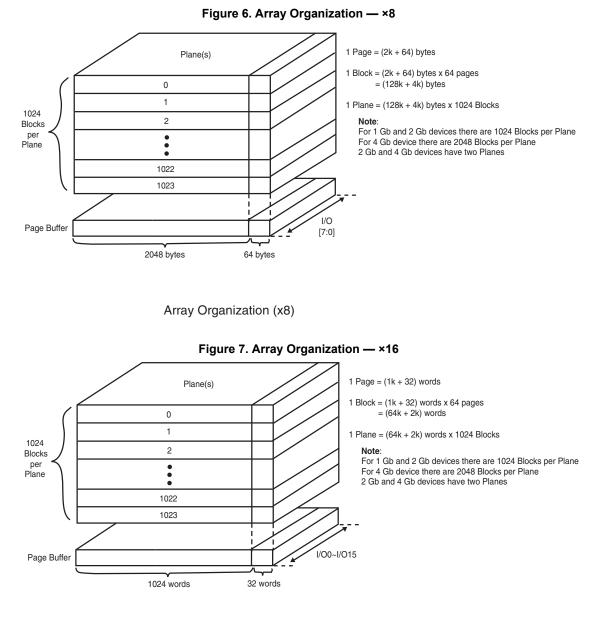

- Input / Output Bus Width: 8-bits / 16-bits

- Page size:

- x8 = 2112 (2048 + 64) bytes; 64 bytes is spare area

- x16 = 1056 (1024 + 32) words; 32 words is spare area

- Block size: 64 Pages

- x8 = 128 KB + 4 KB

- x16 = 64k + 2k words

- Plane size:

- 1 Gb / 2 Gb: 1024 Blocks per Plane x8 = 128 MB + 4 MB

- x16 = 64M + 2M words

- 4 Gb: 2048 Blocks per Plane x8 = 256 MB+ 8 MB x16 = 128M + 4M words

- X 10 = 128101 + 4101

- Device size:

1 Gb: 1 Plane per Device or 128 MB

- 2 Gb: 2 Planes per Device or 256 MB

- 4 Gb: 2 Planes per Device or 512 MB

## Performance

- Page Read / Program

- □ Random access: 25 µs (Max)

- Sequential access: 25 ns (Min)

- □ Program time / Multiplane Program time: 200 µs (Typ)

- Block Erase (S34ML01G1)

Block Erase time: 2.0 ms (Typ)

- Block Erase / Multiplane Erase (S34ML02G1, S34ML04G1)

Block Erase time: 3.5 ms (Typ)

- Reliability

- □ 100,000 Program / Erase cycles (Typ)

- (with 1 bit ECC per 528 bytes (x8) or 264 words (x16))

- 10 Year Data retention (Typ)

- NAND flash interface

Open NAND Flash Interface (ONFI) 1.0 compliant

Address, Data and Commands multiplexed

- Supply voltage

3.3-V device: Vcc = 2.7 V ~ 3.6 V

- Security

One Time Programmable (OTP) area

- □ Hardware program/erase disabled during power transition

S34ML04G1

- Additional features

- 2 Gb and 4 Gb parts support Multiplane Program and Erase commands

- Supports Copy Back Program

- □ 2 Gb and 4 Gb parts support Multiplane Copy Back Program □ Supports Read Cache

- Electronic signature

Manufacturer ID: 01h

- Operating temperature

- □ Industrial: -40 °C to 85 °C

- □ Automotive: -40 °C to 105 °C

- □ For one plane structure (1-Gb density)

- Block zero is valid and will be valid for at least 1,000 program-erase cycles with ECC

- □ For two plane structures (2-Gb and 4-Gb densities)

- Blocks zero and one are valid and will be valid for at least 1,000 program-erase cycles with ECC

- Package options

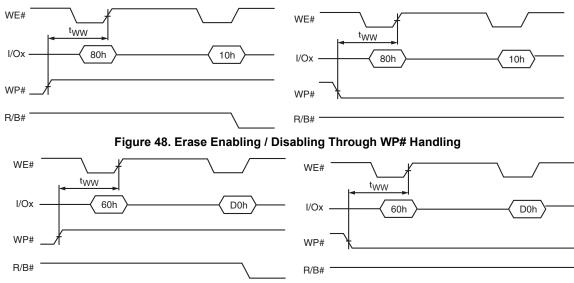

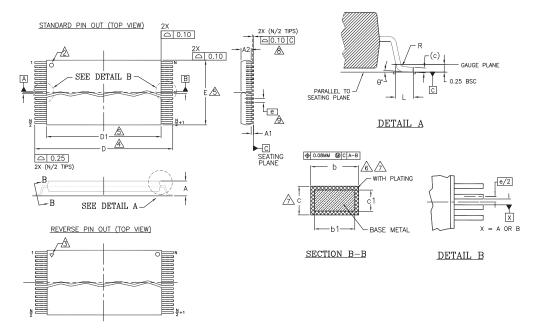

- □ Lead Free and Low Halogen □ 48-Pin TSOP  $12 \times 20 \times 1.2$  mm □ 63-Ball BGA  $9 \times 11 \times 1$  mm

## Contents

| <b>1.</b><br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7  | General Description<br>Logic Diagram<br>Connection Diagram<br>Pin Description<br>Block Diagram<br>Array Organization<br>Addressing<br>Mode Selection                                            | . 5<br>. 6<br>. 7<br>. 8<br>. 9<br>10 |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| <b>2.</b><br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6         | Bus Operation<br>Command Input<br>Address Input<br>Data Input<br>Data Output<br>Write Protect<br>Standby                                                                                        | 13<br>13<br>13<br>13<br>13<br>13      |

| <b>3.</b><br>3.1<br>3.2<br>3.3                              | Command Set<br>Page Read<br>Page Program<br>Multiplane Program<br>— S34ML02G1 and S34ML04G1                                                                                                     | 15<br>15                              |

| 3.4                                                         | Page Reprogram<br>— S34ML02G1 and S34ML04G1                                                                                                                                                     | 16                                    |

| 3.5<br>3.6                                                  | Block Erase<br>Multiplane Block Erase<br>— S34ML02G1 and S34ML04G1                                                                                                                              |                                       |

| 3.7<br>3.8<br>3.9<br>3.10                                   | Copy Back Program<br>EDC Operation — S34ML02G1 and S34ML04G1<br>Read Status Register<br>Read Status Enhanced                                                                                    | 18<br>19                              |

| 3.12<br>3.13                                                | - S34ML02G1 and S34ML04G1<br>Read Status Register Field Definition<br>Reset<br>Read Cache                                                                                                       | 22<br>22<br>23                        |

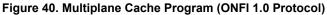

| 3.15                                                        | Cache Program<br>Multiplane Cache Program<br>— S34ML02G1 and S34ML04G1                                                                                                                          | 25                                    |

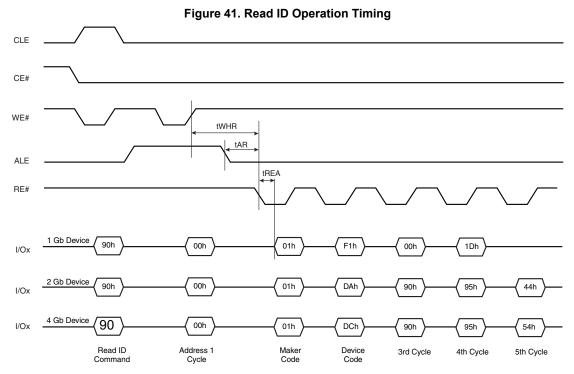

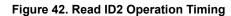

| 3.17<br>3.18<br>3.19                                        | Read ID<br>Read ID2<br>Read ONFI Signature<br>Read Parameter Page<br>One-Time Programmable (OTP) Entry                                                                                          | 29<br>29<br>29                        |

| <b>4.</b><br>4.1<br>4.2<br>4.3                              | Signal Descriptions<br>Data Protection and Power On / Off Sequence<br>Ready/Busy<br>Write Protect Operation                                                                                     | 32<br>32                              |

| <b>5</b> .<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7 | Electrical Characteristics<br>Valid Blocks<br>Absolute Maximum Ratings<br>Recommended Operating Conditions<br>AC Test Conditions<br>AC Characteristics<br>DC Characteristics<br>Pin Capacitance | 34<br>34<br>34<br>35<br>36            |

| 5.8<br>5.9  | Thermal Resistance<br>Program / Erase Characteristics                  |    |

|-------------|------------------------------------------------------------------------|----|

| 6.          | Timing Diagrams                                                        |    |

| <b>6</b> .1 | Command Latch Cycle                                                    |    |

| 6.2         | Address Latch Cycle                                                    |    |

| 6.3         | Data Input Cycle Timing                                                |    |

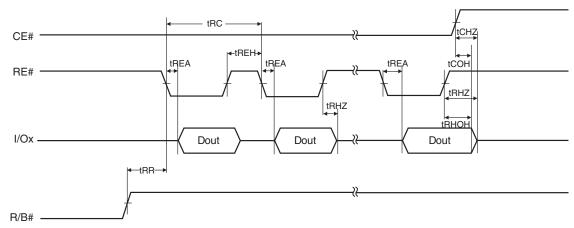

| 6.4         | Data Output Cycle Timing                                               | 59 |

| 0.1         | (CLE=L, WE#=H, ALE=L, WP#=H)                                           | 39 |

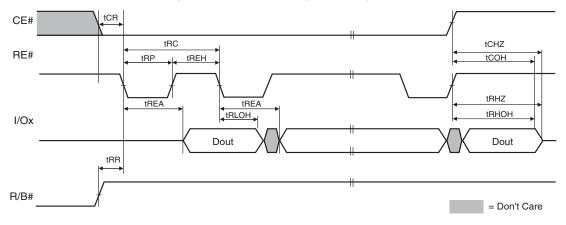

| 6.5         | Data Output Cycle Timing                                               | 00 |

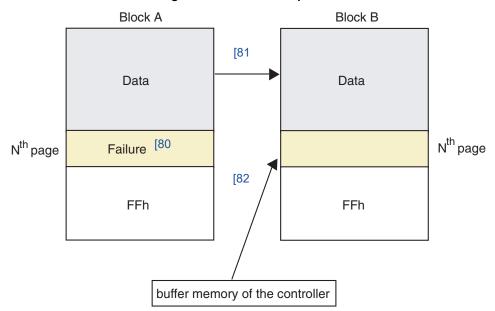

|             | (EDO Type, CLE=L, WE#=H, ALE=L)                                        | 40 |

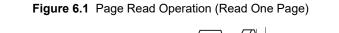

| 6.6         | Page Read Operation                                                    | 40 |

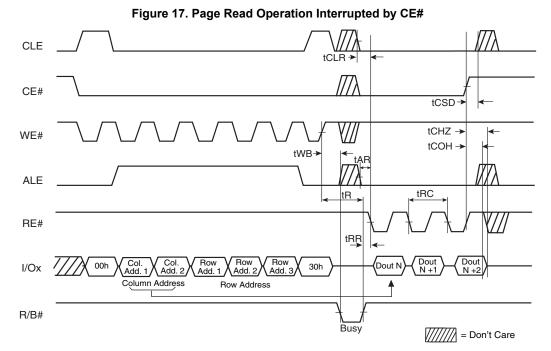

| 6.7         | Page Read Operation (Interrupted by CE#)                               | 41 |

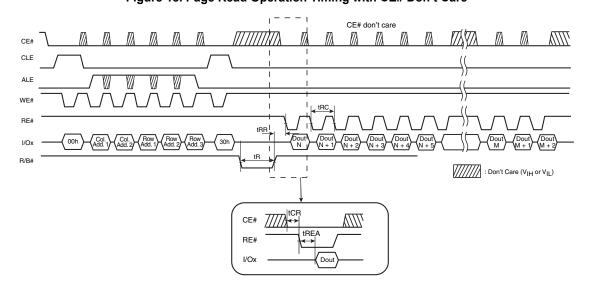

| 6.8         | Page Read Operation Timing with CE# Don't Care                         | 41 |

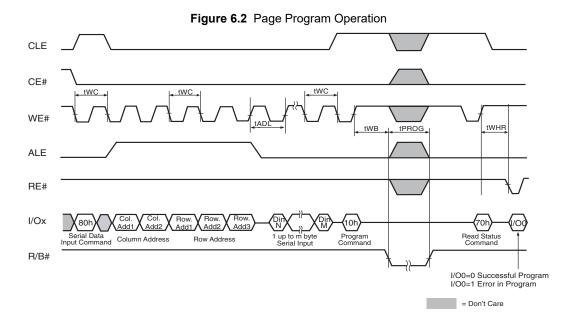

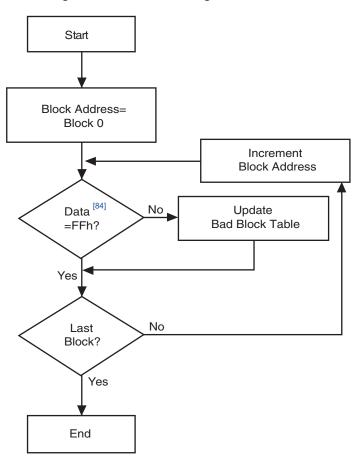

| 6.9         | Page Program Operation                                                 | 42 |

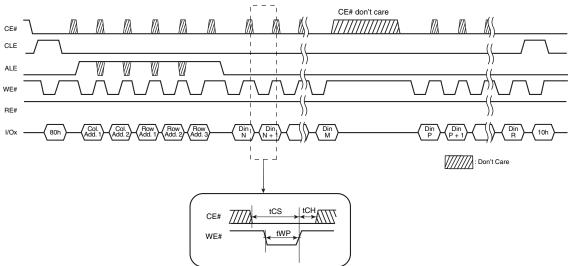

| 6.10        | Page Program Operation Timing                                          |    |

|             | with CE# Don't Care                                                    |    |

|             | Page Program Operation with Random Data Input                          |    |

|             | Random Data Output In a Page                                           | 43 |

| 6.13        | Multiplane Page Program Operation                                      |    |

|             | — S34ML02G1 and S34ML04G1                                              |    |

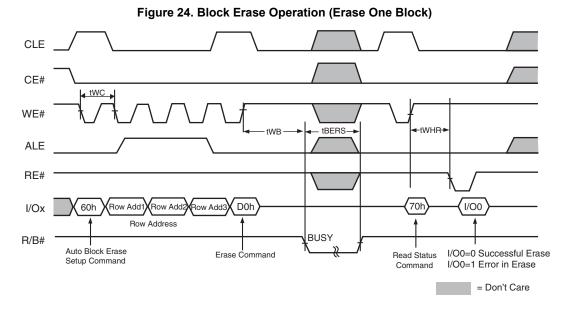

|             | Block Erase Operation                                                  | 45 |

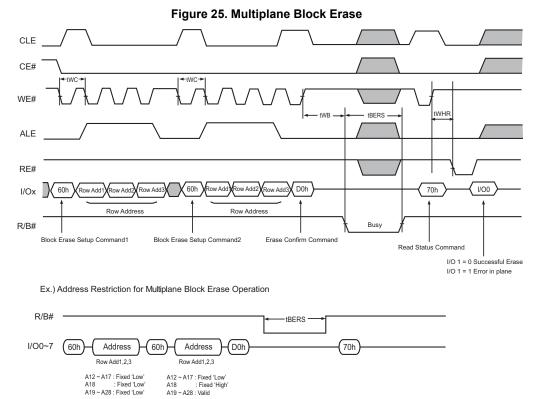

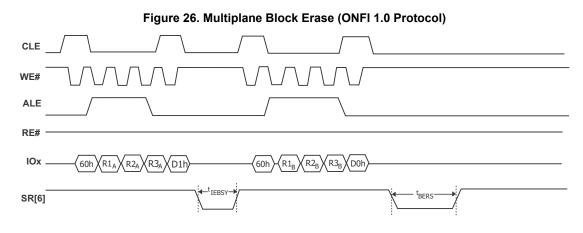

| 6.15        | Multiplane Block Erase                                                 | 45 |

| 6 16        | — S34ML02G1 and S34ML04G1<br>Copy Back Read with Optional Data Readout |    |

|             | Copy Back Program Operation                                            | 40 |

| 0.17        | With Random Data Input                                                 | 46 |

| 6 18        | Multiplane Copy Back Program                                           | 40 |

| 0.10        | - S34ML02G1 and S34ML04G1                                              | 47 |

| 6 19        | Read Status Register Timing                                            |    |

|             | Read Status Enhanced Timing                                            |    |

|             | Reset Operation Timing                                                 |    |

|             | Read Cache                                                             |    |

|             | Cache Program                                                          |    |

|             | Multiplane Cache Program                                               |    |

|             | — S34ML02G1 and S34ML04G1                                              |    |

|             | Read ID Operation Timing                                               |    |

|             | Read ID2 Operation Timing                                              |    |

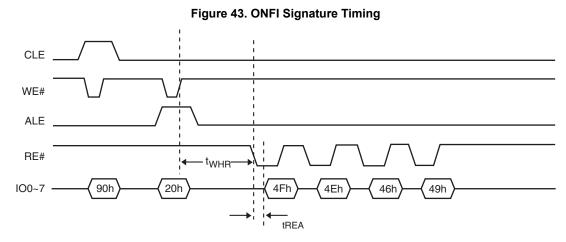

|             | Read ONFI Signature Timing                                             |    |

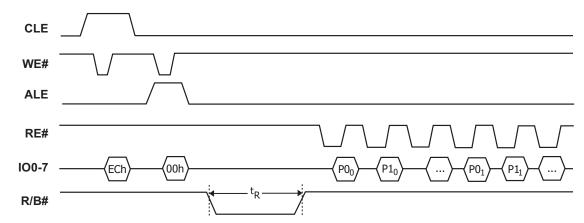

|             | Read Parameter Page Timing                                             |    |

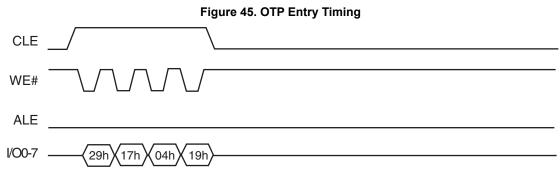

|             | OTP Entry Timing                                                       |    |

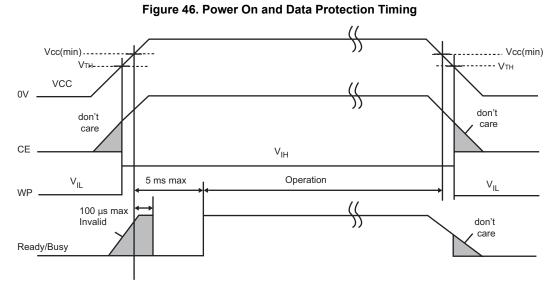

|             | Power On and Data Protection Timing                                    |    |

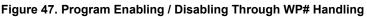

| 6.31        | WP# Handling                                                           | 55 |

| 7.          | Physical Interface                                                     | 56 |

| 7.1         | Physical Diagram                                                       | 56 |

| 8.          | System Interface                                                       | 58 |

| 9.          | Error Management                                                       | 59 |

| 9.1         | System Bad Block Replacement                                           |    |

| 9.2         | Bad Block Management                                                   |    |

| 10.         | Ordering Information                                                   |    |

|             | -                                                                      |    |

| 11.         | Document History Page                                                  | 62 |

| Sales, Solutions, and Legal Information | 71 |

|-----------------------------------------|----|

| Worldwide Sales and Design Support      | 71 |

| Products                                | 71 |

| PSoC® Solutions                         | 71 |

| Cypress Developer Community             | 71 |

| Technical Support                       | 71 |

## 1. General Description

The Cypress S34ML01G1, S34ML02G1, and S34ML04G1 series is offered with a 3.3-V V<sub>CC</sub> power supply, and with ×8 or ×16 I/O interface. Its NAND cell provides the most cost-effective solution for the solid state mass storage market. The memory is divided into blocks that can be erased independently so it is possible to preserve valid data while old data is erased. The page size for ×8 is (2048 + 64 spare) bytes; for ×16 (1024 + 32) words.

Each block can be programmed and erased up to 100,000 cycles with ECC (error correction code) on. To extend the lifetime of NAND flash devices, the implementation of an ECC is mandatory.

The chip supports CE# don't care function. This function allows the direct download of the code from the NAND flash memory device by a microcontroller, since the CE# transitions do not stop the read operation.

The devices have a Read Cache feature that improves the read throughput for large files. During cache reading, the devices load the data in a cache register while the previous data is transferred to the I/O buffers to be read.

Like all other 2-kB page NAND flash devices, a program operation typically writes 2112 bytes (×8), or 1056 words (×16) in 200 µs and an erase operation can typically be performed in 2 ms (S34ML01G1) on a 128-kB block (×8) or 64-kword block (×16). In addition, thanks to multiplane architecture, it is possible to program two pages at a time (one per plane) or to erase two blocks at a time (again, one per plane). The multiplane architecture allows program time to be reduced by 40% and erase time to be reduced by 50%.

In multiplane operations, data in the page can be read out at 25 ns cycle time per byte. The I/O pins serve as the ports for command and address input as well as data input/output. This interface allows a reduced pin count and easy migration towards different densities, without any rearrangement of the footprint.

Commands, Data, and Addresses are asynchronously introduced using CE#, WE#, ALE, and CLE control pins.

The on-chip Program/Erase Controller automates all read, program, and erase functions including pulse repetition, where required, and internal verification and margining of data. A WP# pin is available to provide hardware protection against program and erase operations.

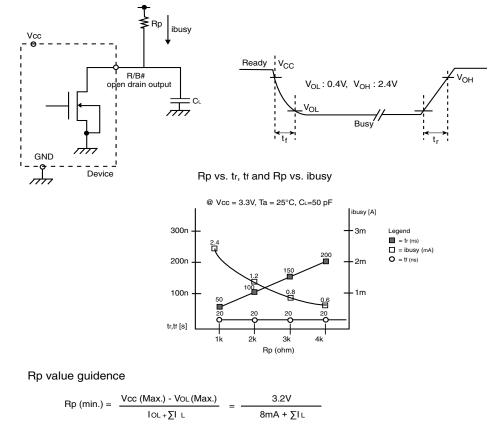

The output pin R/B# (open drain buffer) signals the status of the device during each operation. It identifies if the program/erase/read controller is currently active. The use of an open-drain output allows the Ready/Busy pins from several memories to connect to a single pull-up resistor. In a system with multiple memories the

R/B# pins can be connected all together to provide a global status signal.

The Reprogram function allows the optimization of defective block management — when a Page Program operation fails the data can be directly programmed in another page inside the same array section without the time consuming serial data insertion phase. The Copy Back operation automatically executes embedded error detection operation: 1-bit error out of every 528 bytes (×8) or 256 words (×16) can be detected. With this feature it is no longer necessary to use an external mechanism to detect Copy Back operation errors.

Multiplane Copy Back is also supported. Data read out after Copy Back Read (both for single and multiplane cases) is allowed.

In addition, Cache Program and Multiplane Cache Program operations improve the programing throughput by programing data using the cache register.

The devices provide two innovative features: Page Reprogram and Multiplane Page Reprogram. The Page Reprogram re-programs one page. Normally, this operation is performed after a failed Page Program operation. Similarly, the Multiplane Page Reprogram re-programs two pages in parallel, one per plane. The first page must be in the first plane while the second page must be in the second plane. The Multiplane Page Reprogram operation is performed after a failed Multiplane Page Program operation. The Page Reprogram operation. The Page Reprogram and Multiplane Page Reprogram guarantee improved performance, since data insertion can be omitted during re-program operations.

Note: The S34ML01G1 device does not support EDC.

The devices come with an OTP (one time programmable) area, which is a restricted access area where sensitive data/code can be stored permanently. This security feature is subject to an NDA (non-disclosure agreement) and is, therefore, not described in the data sheet. For more details, contact your nearest Cypress sales office.

#### Table 1. Product List

| Device      | Densit    | y (bits) | Number of Planes | Number of Blocks | EDC Support |

|-------------|-----------|----------|------------------|------------------|-------------|

| Device      | Main      | Spare    | Number of Fidnes | per Plane        |             |

| S34ML01G1   | 128M x 8  | 4M x 8   | 1                | 1024             | No          |

|             | 64M x 16  | 2M x 16  |                  | 1024             | INO         |

| S34ML02G1   | 256M x 8  | 8M x 8   | 2                | 1024             | Yes         |

| 334IVIL02G1 | 128M x 16 | 4M x 16  | 2                | 1024             | 165         |

| S34ML04G1   | 512M x 8  | 16M x 8  | 2                | 2048             | Yes         |

| 554IVIL04G1 | 256M x 16 | 8M x 16  | 2                | 2040             | Tes         |

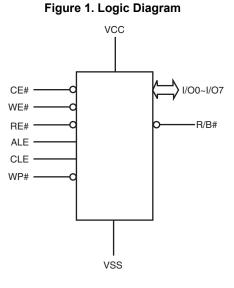

### 1.1 Logic Diagram

#### Table 2. Signal Names

| Signal                      | Description          |  |  |  |  |

|-----------------------------|----------------------|--|--|--|--|

| I/O7 - I/O0 <b>(×8)</b>     | Data Input / Outputs |  |  |  |  |

| I/O8 - I/O15 ( <b>×16</b> ) |                      |  |  |  |  |

| CLE                         | Command Latch Enable |  |  |  |  |

| ALE                         | Address Latch Enable |  |  |  |  |

| CE#                         | Chip Enable          |  |  |  |  |

| RE#                         | Read Enable          |  |  |  |  |

| WE#                         | Write Enable         |  |  |  |  |

| WP#                         | Write Protect        |  |  |  |  |

| R/B#                        | Read/Busy            |  |  |  |  |

| VCC                         | Power Supply         |  |  |  |  |

| VSS                         | Ground               |  |  |  |  |

| NC                          | Not Connected        |  |  |  |  |

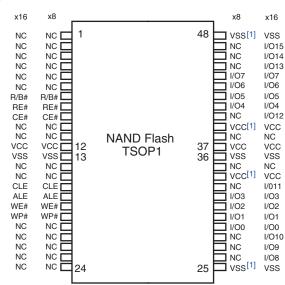

#### **Connection Diagram** 1.2

Figure 2. 48-Pin TSOP1 Contact ×8, ×16 Devices

Note

1. These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

Figure 3. 63-BGA Contact, ×8 Device (Balls Down, Top View)

(A2) NC (A9) NC (A1) NC A10 (B1) (B9) (B10) NC NC

(C3) (C4) (C5) (C6) (C7) (08) ALE WP# VSS CE# WE# RB# (D3) (04) (D5) (D6) (08) VCC (1) RE# CLE NC NC NC (E4) (E5) (E6) (E7) (E8) (E3) NC NC NC NC NC NC (F3) NC (F6) NC (F4) (F7) (F5) (F8) NC NC VSS (1) NC (G3) (G4) (G5) (G6) (G7) (G8) NC VCC (1) NC NC NC NC (H8) (H3) (H4) (H5) (H6) (H7) NC 1/00 NC NC NC V<sub>cc</sub> ( J5 ) NC (J6) (J8) 1/07 (J3) (J4) (J7) NC 1/01 1/05 V<sub>CC</sub> (K5) (K3) (K4) (K6) ( 17) (K8) 1/02 1/03 1/04 1/06 VSS VSS (L2) NC L9 NC (L10) NC (M2) (M9) (M10) NC NC NC

## Note:

1. These pins should be connected to power supply or ground (as designated) following the ONFI specification, however they might not be bonded internally.

| (A1)<br>NC | A2 )<br>NC |              |              |               |                         |              |                         | (A9)<br>NC | A1       |

|------------|------------|--------------|--------------|---------------|-------------------------|--------------|-------------------------|------------|----------|

| (B1)<br>NC |            |              |              |               |                         |              |                         | NC         | B1<br>NC |

|            |            | (C3)<br>WP#  | C4)<br>ALE   | (C5)<br>VSS   | (C6)<br>CE#             | (C7)<br>WE#  | (C8)<br>RB#             |            |          |

|            |            | (D3)<br>VCC  | (D4)<br>RE#  | (D5)<br>CLE   | (D6)<br>NC              | (D7)<br>NC   | (D8)                    |            |          |

|            |            | (E3)<br>NC   | (E4)         | (E5)<br>NC    | (E6)                    | (E7)         | (E8)<br>NC              |            |          |

|            |            | (F3)         | (F4)<br>NC   | (F5)          | (F6)<br>NC              | (F7)<br>VSS  | (F8)                    |            |          |

|            |            | (G3)<br>NC   | (G4)<br>VCC  | (G5)<br>NC    | (G6)                    | (G7)         | (G8)<br>NC              |            |          |

|            |            | (H3)         | (H4)         | (H5)          | (H6)                    | (H7)         | (H8)<br>V <sub>cc</sub> |            |          |

|            |            | (J3)<br>1/09 | (J4)<br>1/01 | (J5)<br>I/011 | (J6)<br>V <sub>CC</sub> | (J7)<br>I/O5 | (J8)<br>1/07            |            |          |

|            |            | (K3)<br>Vss  | (K4)         | (K5)          | (K6)                    | (K7)         | (K8)<br>Vss             |            |          |

| (L1)<br>NC | (L2)<br>NC | 35           |              |               |                         |              | 55                      | (L9)<br>NC | (L1      |

| (M1)<br>NC | (M2)<br>NC |              |              |               |                         |              |                         | (M9)<br>NC | M1       |

#### Figure 4. 63-BGA Contact, ×16 Device (Balls Down, Top View)

#### 1.3 **Pin Description**

#### Table 3. Pin Description

| Pin Name                    | Description                                                                                                                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O0 - I/O7 <b>(×8)</b>     | Inputs/Outputs. The I/O pins are used for command input, address input, data input, and data output. The I/O pins float                                                                                                                            |

| I/O8 - I/O15 ( <b>×16</b> ) | to High-Z when the device is deselected or the outputs are disabled.                                                                                                                                                                               |

| CLE                         | <b>Command Latch Enable.</b> This input activates the latching of the I/O inputs inside the Command Register on the rising edge of Write Enable (WE#).                                                                                             |

| ALE                         | Address Latch Enable. This input activates the latching of the I/O inputs inside the Address Register on the rising edge of Write Enable (WE#).                                                                                                    |

| CE#                         | Chip Enable. This input controls the selection of the device. When the device is not busy CE# low selects the memory.                                                                                                                              |

| WE#                         | Write Enable. This input latches Command, Address and Data. The I/O inputs are latched on the rising edge of WE#.                                                                                                                                  |

| RE#                         | <b>Read Enable.</b> The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid t <sub>REA</sub> after the falling edge of RE# which also increments the internal column address counter by one. |

| WP#                         | Write Protect. The WP# pin, when low, provides hardware protection against undesired data modification (program / erase).                                                                                                                          |

| R/B#                        | Ready Busy. The Ready/Busy output is an Open Drain pin that signals the state of the memory.                                                                                                                                                       |

| VCC                         | <b>Supply Voltage</b> . The V <sub>CC</sub> supplies the power for all the operations (Read, Program, Erase). An internal lock circuit prevents the insertion of Commands when $V_{CC}$ is less than $V_{LKO}$ .                                   |

| VSS                         | Ground.                                                                                                                                                                                                                                            |

| NC                          | Not Connected.                                                                                                                                                                                                                                     |

#### Notes

A 0.1 μF capacitor should be connected between the V<sub>CC</sub> Supply Voltage pin and the V<sub>SS</sub> Ground pin to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during program and erase operations.

An internal voltage detector disables all functions whenever V<sub>CC</sub> is below 1.8V to protect the device from any involuntary program/erase during power transitions.

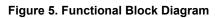

### 1.4 Block Diagram

## 1.5 Array Organization

Array Organization (x16)

#### Addressing 1.6

#### 1.6.1 S34ML01G1

#### Table 4. Address Cycle Map — 1 Gb Device

| Bus Cycle         | I/O [15:8] [8] | I/O0      | I/O1      | I/O2       | I/O3       | I/O4      | I/O5      | I/O6      | I/O7      |  |  |  |  |  |

|-------------------|----------------|-----------|-----------|------------|------------|-----------|-----------|-----------|-----------|--|--|--|--|--|

|                   | ×8             |           |           |            |            |           |           |           |           |  |  |  |  |  |

| 1st / Col. Add. 1 | —              | A0 (CA0)  | A1 (CA1)  | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)  | A7 (CA7)  |  |  |  |  |  |

| 2nd / Col. Add. 2 | —              | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | A11 (CA11) | Low       | Low       | Low       | Low       |  |  |  |  |  |

| 3rd / Row Add. 1  | —              | A12 (PA0) | A13 (PA1) | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (BA0) | A19 (BA1) |  |  |  |  |  |

| 4th / Row Add. 2  | —              | A20 (BA2) | A21 (BA3) | A22 (BA4)  | A23 (BA5)  | A24 (BA6) | A25 (BA7) | A26 (BA8) | A27 (BA9) |  |  |  |  |  |

|                   |                |           |           | ×16        |            |           |           |           |           |  |  |  |  |  |

| 1st / Col. Add. 1 | Low            | A0 (CA0)  | A1 (CA1)  | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)  | A7 (CA7)  |  |  |  |  |  |

| 2nd / Col. Add. 2 | Low            | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | Low        | Low       | Low       | Low       | Low       |  |  |  |  |  |

| 3rd / Row Add. 1  | Low            | A11 (PA0) | A12 (PA1) | A13 (PA2)  | A14 (PA3)  | A15 (PA4) | A16 (PA5) | A17 (BA0) | A18 (BA1) |  |  |  |  |  |

| 4th / Row Add. 2  | Low            | A19 (BA2) | A20 (BA3) | A21 (BA4)  | A22 (BA5)  | A23 (BA6) | A24 (BA7) | A25 (BA8) | A26 (BA9) |  |  |  |  |  |

#### Notes

CAx = Column Address bit.

PAx = Page Address bit.

6. BAx = Block Address bit.

7. Block address concatenated with page address = actual page address, also known as the row address.

8. I/O[15:8] are not used during the addressing sequence and should be driven Low.

For the ×8 address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18 A27: block address

For the ×16 address bits, the following rules apply:

- A0 A10: column address in the page

- A11 A16: page address in the block

- A17 A26: block address

#### 1.6.2 S34ML02G1

#### Table 5. Address Cycle Map — 2 Gb Device

| Bus Cycle         | I/O [15:8] [14] | I/O0      | I/O1      | I/O2       | I/O3       | I/O4      | I/O5      | I/O6       | I/07      |  |  |  |  |

|-------------------|-----------------|-----------|-----------|------------|------------|-----------|-----------|------------|-----------|--|--|--|--|

|                   | ×8              |           |           |            |            |           |           |            |           |  |  |  |  |

|                   |                 |           |           |            |            |           |           |            |           |  |  |  |  |

| 1st / Col. Add. 1 | —               | A0 (CA0)  | A1 (CA1)  | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |  |  |  |

| 2nd / Col. Add. 2 | —               | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | A11 (CA11) | Low       | Low       | Low        | Low       |  |  |  |  |

| 3rd / Row Add. 1  | —               | A12 (PA0) | A13 (PA1) | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (PLA0) | A19 (BA0) |  |  |  |  |

| 4th / Row Add. 2  | —               | A20 (BA1) | A21 (BA2) | A22 (BA3)  | A23 (BA4)  | A24 (BA5) | A25 (BA6) | A26 (BA7)  | A27 (BA8) |  |  |  |  |

| 5th / Row Add. 3  | —               | A28 (BA9) | Low       | Low        | Low        | Low       | Low       | Low        | Low       |  |  |  |  |

|                   | •               |           |           | ×16        |            |           |           |            |           |  |  |  |  |

| 1st / Col. Add. 1 | Low             | A0 (CA0)  | A1 (CA1)  | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |  |  |  |

| 2nd / Col. Add. 2 | Low             | A8 (CA8)  | A9 (CA9)  | A10 (CA10) | Low        | Low       | Low       | Low        | Low       |  |  |  |  |

| 3rd / Row Add. 1  | Low             | A11 (PA0) | A12 (PA1) | A13 (PA2)  | A14 (PA3)  | A15 (PA4) | A16 (PA5) | A17 (PLA0) | A18 (BA0) |  |  |  |  |

| 4th / Row Add. 2  | Low             | A19 (BA1) | A20 (BA2) | A21 (BA3)  | A22 (BA4)  | A23 (BA5) | A24 (BA6) | A25 (BA7)  | A26 (BA8) |  |  |  |  |

| 5th / Row Add. 3  | Low             | A27 (BA9) | Low       | Low        | Low        | Low       | Low       | Low        | Low       |  |  |  |  |

#### Notes

- 9. CAx = Column Address bit.

- 10. PAx = Page Address bit.

- 11. PLA0 = Plane Address bit zero. 12. BAx = Block Address bit.

- Block address concatenated with page address and plane address = actual page address, also known as the row address.

- 14. I/O[15:8] are not used during the addressing sequence and should be driven Low.

For the ×8 address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18: plane address (for multiplane operations) / block address (for normal operations)

- A19 A28: block address

For the ×16 address bits, the following rules apply:

- A0 A10: column address in the page

- A11 A16: page address in the block

- A17: plane address (for multiplane operations) / block address (for normal operations)

- A18 A27: block address

### 1.6.3 S34ML04G1

### Table 6. Address Cycle Map — 4 Gb Device

| Bus Cycle         | I/O [15:8] [20] | I/O0      | I/O1       | I/O2       | I/O3       | I/O4      | I/O5      | I/O6       | I/07      |  |  |  |  |

|-------------------|-----------------|-----------|------------|------------|------------|-----------|-----------|------------|-----------|--|--|--|--|

| ×8                |                 |           |            |            |            |           |           |            |           |  |  |  |  |

| 1st / Col. Add. 1 | —               | A0 (CA0)  | A1 (CA1)   | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |  |  |  |

| 2nd / Col. Add. 2 | —               | A8 (CA8)  | A9 (CA9)   | A10 (CA10) | A11 (CA11) | Low       | Low       | Low        | Low       |  |  |  |  |

| 3rd / Row Add. 1  | —               | A12 (PA0) | A13 (PA1)  | A14 (PA2)  | A15 (PA3)  | A16 (PA4) | A17 (PA5) | A18 (PLA0) | A19 (BA0) |  |  |  |  |

| 4th / Row Add. 2  | —               | A20 (BA1) | A21 (BA2)  | A22 (BA3)  | A23 (BA4)  | A24 (BA5) | A25 (BA6) | A26 (BA7)  | A27 (BA8) |  |  |  |  |

| 5th / Row Add. 3  | —               | A28 (BA9) | A29 (BA10) | Low        | Low        | Low       | Low       | Low        | Low       |  |  |  |  |

|                   |                 |           |            | ×16        |            |           |           |            |           |  |  |  |  |

| 1st / Col. Add. 1 | Low             | A0 (CA0)  | A1 (CA1)   | A2 (CA2)   | A3 (CA3)   | A4 (CA4)  | A5 (CA5)  | A6 (CA6)   | A7 (CA7)  |  |  |  |  |

| 2nd / Col. Add. 2 | Low             | A8 (CA8)  | A9 (CA9)   | A10 (CA10) | Low        | Low       | Low       | Low        | Low       |  |  |  |  |

| 3rd / Row Add. 1  | Low             | A11 (PA0) | A12 (PA1)  | A13 (PA2)  | A14 (PA3)  | A15 (PA4) | A16 (PA5) | A17 (PLA0) | A18 (BA0) |  |  |  |  |

| 4th / Row Add. 2  | Low             | A19 (BA1) | A20 (BA2)  | A21 (BA3)  | A22 (BA4)  | A23 (BA5) | A24 (BA6) | A25 (BA7)  | A26 (BA8) |  |  |  |  |

| 5th / Row Add. 3  | Low             | A27 (BA9) | A28 (BA10) | Low        | Low        | Low       | Low       | Low        | Low       |  |  |  |  |

#### Notes

15. CAx = Column Address bit.

16. PAx = Page Address bit.

17. PLA0 = Plane Address bit zero.

18. BAx = Block Address bit.

19. Block address concatenated with page address and plane address = actual page address, also known as the row address.

20. I/O[15:8] are not used during the addressing sequence and should be driven Low.

For the ×8 address bits, the following rules apply:

- A0 A11: column address in the page

- A12 A17: page address in the block

- A18: plane address (for multiplane operations) / block address (for normal operations)

- A19 A29: block address

For the ×16 address bits, the following rules apply:

- A0 A10: column address in the page

- A11 A16: page address in the block

- A17: plane address (for multiplane operations) / block address (for normal operations)

- A18 A28: block address

#### 1.7 **Mode Selection**

### Table 7. Mode Selection

| Mode                    |               | CLE  | ALE  | CE#  | WE#    | RE#       | WP#                       |

|-------------------------|---------------|------|------|------|--------|-----------|---------------------------|

| Read Mode               | Command Input | High | Low  | Low  | Rising | High      | Х                         |

| Read Mode               | Address Input | Low  | High | Low  | Rising | High      | Х                         |

| Program or Erase Mode   | Command Input | High | Low  | Low  | Rising | High      | High                      |

| Flogram of Erase Mode   | Address Input | Low  | High | Low  | Rising | High      | High                      |

| Data Input              |               | Low  | Low  | Low  | Rising | High      | High                      |

| Data Output (on going)  |               | Low  | Low  | Low  | High   | Falling   | Х                         |

| Data Output (suspended) |               | Х    | Х    | Х    | High   | High      | Х                         |

| Busy Time in Read       |               | х    | Х    | Х    | High   | High [23] | Х                         |

| Busy Time in Program    |               | Х    | Х    | Х    | Х      | Х         | High                      |

| Busy Time in Erase      |               | Х    | Х    | Х    | Х      | Х         | High                      |

| Write Protect           |               | х    | Х    | Х    | Х      | Х         | Low                       |

| Stand By                |               | х    | Х    | High | Х      | Х         | 0V / V <sub>CC</sub> [22] |

#### Notes

21. X can be  $V_{IL}$  or  $V_{IH}$ . High= Logic level high. Low = Logic level low. 22. WP# should be biased to CMOS high or CMOS low for stand-by mode.

23. During Busy Time in Read, RE# must be held high to prevent unintended data out.

## 2. Bus Operation

There are six standard bus operations that control the device: Command Input, Address Input, Data Input, Data Output, Write Protect, and Standby. (See Table 7.)

Typically glitches less than 5 ns on Chip Enable, Write Enable, and Read Enable are ignored by the memory and do not affect bus operations.

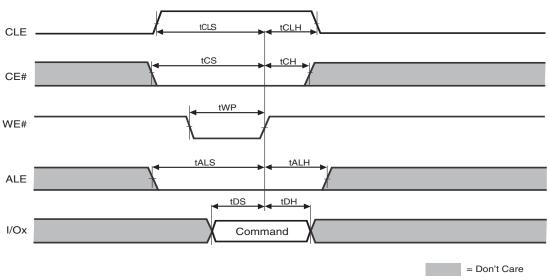

## 2.1 Command Input

The Command Input bus operation is used to give a command to the memory device. Commands are accepted with Chip Enable low, Command Latch Enable high, Address Latch Enable low, and Read Enable high and latched on the rising edge of Write Enable. Moreover, for commands that start a modify operation (program/erase) the Write Protect pin must be high. See Figure 12 on page 38 and Table 20 on page 35 for details of the timing requirements. Command codes are always applied on I/O7:0 regardless of the bus configuration (×8 or ×16).

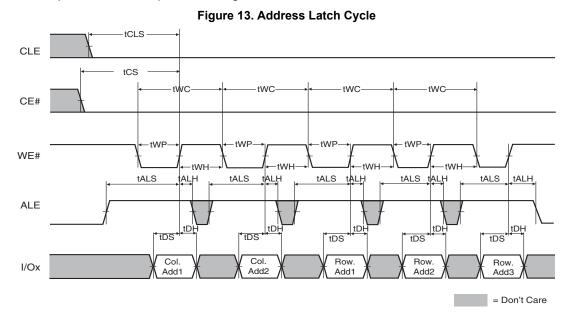

## 2.2 Address Input

The Address Input bus operation allows the insertion of the memory address. For the S34ML02G1 and S34ML04G1 devices, five write cycles are needed to input the addresses. For the S34ML01G1, four write cycles are needed to input the addresses. If necessary, a 5th dummy address cycle can be issued to S34ML01G1, which will be ignored by the NAND device without causing problems. Addresses are accepted with Chip Enable low, Address Latch Enable high, Command Latch Enable low, and Read Enable high and latched on the rising edge of Write Enable. Moreover, for commands that start a modify operation (program/erase) the Write Protect pin must be high. See Figure 13 on page 38 and Table 20 on page 35 for details of the timing requirements. Addresses are always applied on I/O7:0 regardless of the bus configuration (×8 or ×16). Refer to Table 4 through Table 6 on page 11 for more detailed information.

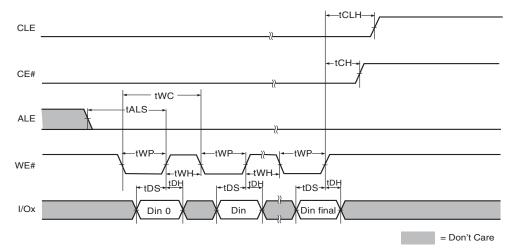

## 2.3 Data Input

The Data Input bus operation allows the data to be programmed to be sent to the device. The data insertion is serial and timed by the Write Enable cycles. Data is accepted only with Chip Enable low, Address Latch Enable low, Command Latch Enable low, Read Enable high, and Write Protect high and latched on the rising edge of Write Enable. See Figure 14 on page 39 and Table 20 on page 35 for details of the timing requirements.

## 2.4 Data Output

The Data Output bus operation allows data to be read from the memory array and to check the Status Register content, the EDC register content, and the ID data. Data can be serially shifted out by toggling the Read Enable pin with Chip Enable low, Write Enable high, Address Latch Enable low, and Command Latch Enable low. See Figure 15 on page 39 and Table 20 on page 35 for details of the timings requirements.

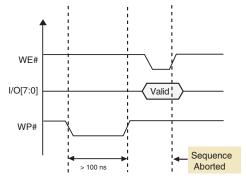

## 2.5 Write Protect

The Hardware Write Protection is activated when the Write Protect pin is low. In this condition, modify operations do not start and the content of the memory is not altered. The Write Protect pin is not latched by Write Enable to ensure the protection even during power up.

## 2.6 Standby

In Standby, the device is deselected, outputs are disabled, and power consumption is reduced.

## 3. Command Set

### Table 8. Command Set

| Command                                           | 1st Cycle       | 2nd Cycle | 3rd Cycle | 4th Cycle | Acceptable<br>Command<br>during Busy | Supported on<br>S34ML01G1 |

|---------------------------------------------------|-----------------|-----------|-----------|-----------|--------------------------------------|---------------------------|

| Page Read                                         | 00h             | 30h       |           |           | No                                   | Yes                       |

| Page Program                                      | 80h             | 10h       |           |           | No                                   | Yes                       |

| Random Data Input                                 | 85h             |           |           |           | No                                   | Yes                       |

| Random Data Output                                | 05h             | E0h       |           |           | No                                   | Yes                       |

| Multiplane Program                                | 80h             | 11h       | 81h       | 10h       | No                                   | No                        |

| ONFI Multiplane Program                           | 80h             | 11h       | 80h       | 10h       | No                                   | No                        |

| Page Reprogram                                    | 8Bh             | 10h       |           |           | No                                   | No                        |

| Multiplane Page Reprogram                         | 8Bh             | 11h       | 8Bh       | 10h       | No                                   | No                        |

| Block Erase                                       | 60h             | D0h       |           |           | No                                   | Yes                       |

| Multiplane Block Erase                            | 60h             | 60h       | D0h       |           | No                                   | No                        |

| ONFI Multiplane Block Erase                       | 60h             | D1h       | 60h       | D0h       | No                                   | No                        |

| Copy Back Read                                    | 00h             | 35h       |           |           | No                                   | Yes                       |

| Copy Back Program                                 | 85h             | 10h       |           |           | No                                   | Yes                       |

| Multiplane Copy Back Program                      | 85h             | 11h       | 81h       | 10h       | No                                   | No                        |

| ONFI Multiplane Copy Back Program                 | 85h             | 11h       | 85h       | 10h       | No                                   | No                        |

| Special Read For Copy Back                        | 00h             | 36h       |           |           | No                                   | No                        |

| Read EDC Status Register                          | 7Bh             |           |           |           | Yes                                  | No                        |

| Read Status Register                              | 70h             |           |           |           | Yes                                  | Yes                       |

| Read Status Enhanced                              | 78h             |           |           |           | Yes                                  | No                        |

| Reset                                             | FFh             |           |           |           | Yes                                  | Yes                       |

| Read Cache                                        | 31h             |           |           |           | No                                   | Yes                       |

| Read Cache Enhanced                               | 00h             | 31h       |           |           | No                                   | No                        |

| Read Cache End                                    | 3Fh             |           |           |           | No                                   | Yes                       |

| Cache Program (End)                               | 80h             | 10h       |           |           | No                                   | Yes                       |

| Cache Program (Start) / (Continue)                | 80h             | 15h       |           |           | No                                   | Yes                       |

| Multiplane Cache Program (Start/Continue)         | 80h             | 11h       | 81h       | 15h       | No                                   | No                        |

| ONFI Multiplane Cache Program<br>(Start/Continue) | 80h             | 11h       | 80h       | 15h       | No                                   | No                        |

| Multiplane Cache Program (End)                    | 80h             | 11h       | 81h       | 10h       | No                                   | No                        |

| ONFI Multiplane Cache Program (End)               | 80h             | 11h       | 80h       | 10h       | No                                   | No                        |

| Read ID                                           | 90h             |           |           |           | No                                   | Yes                       |

| Read ID2                                          | 30h-65h-00h     | 30h       |           |           | No                                   | Yes                       |

| Read ONFI Signature                               | 90h             |           |           |           | No                                   | Yes                       |

| Read Parameter Page                               | ECh             |           |           |           | No                                   | Yes                       |

| One-time Programmable (OTP) Area Entry            | 29h-17h-04h-19h |           |           |           | No                                   | Yes                       |

## 3.1 Page Read

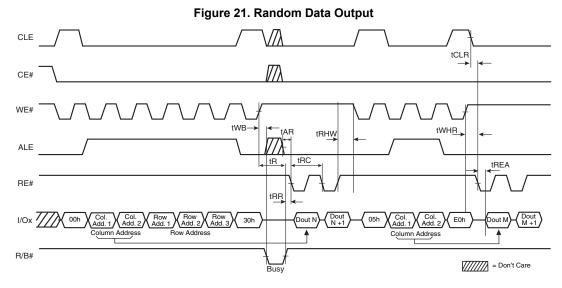

Page Read is initiated by writing 00h and 30h to the command register along with five address cycles (four or five cycles for S34ML01G1). Two types of operations are available: random read and serial page read. Random read mode is enabled when the page address is changed. All data within the selected page are transferred to the data registers. The system controller may detect the completion of this data transfer ( $t_R$ ) by analyzing the output of the R/B pin. Once the data in a page is loaded into the data registers, they may be read out in 25 ns cycle time by sequentially pulsing RE#. The repetitive high to low transitions of the RE# signal makes the device output the data, starting from the selected column address up to the last column address.

The device may output random data in a page instead of the sequential data by writing Random Data Output command. The column address of next data, which is going to be out, may be changed to the address that follows Random Data Output command. Random Data Output can be performed as many times as needed.

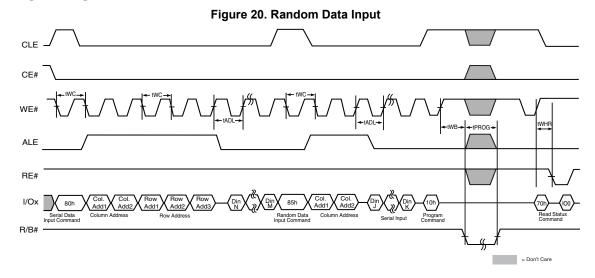

After power up, the device is in read mode, so 00h command cycle is not necessary to start a read operation. Any operation other than read or Random Data Output causes the device to exit read mode. See Figure 6.1 on page 40 and Figure 21 on page 43 as references.

## 3.2 Page Program

A page program cycle consists of a serial data loading period in which up to 2112 bytes (×8) or 1056 words (×16) of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell.

The serial data loading period begins by inputting the Serial Data Input command (80h), followed by the five cycle address inputs (four cycles for S34ML01G1) and then serial data. The words other than those to be programmed do not need to be loaded. The device supports Random Data Input within a page. The column address of next data, which will be entered, may be changed to the address that follows the Random Data Input command (85h). Random Data Input may be performed as many times as needed.

The Page Program confirm command (10h) initiates the programming process. The internal write state controller automatically executes the algorithms and controls timings necessary for program and verify, thereby freeing the system controller for other tasks.

Once the program process starts, the Read Status Register commands (70h or 78h) may be issued to read the Status Register. The system controller can detect the completion of a program cycle by monitoring the

R/B# output, or the Status bit (I/O6) of the Status Register. Only the Read Status commands (70h or 78h) or Reset command are valid while programming is in progress. When the Page Program is complete, the Write Status Bit (I/O0) may be checked. The internal write verify detects only errors for 1's that are not successfully programmed to 0's. The command register remains in Read Status command mode until another valid command is written to the command register. Figure 6.2 on page 42 and Figure 20 on page 43 detail the sequence.

The device is programmable by page, but it also allows multiple partial page programming of a word or consecutive bytes up to 2112 bytes (×8) or 1056 words (×16) in a single page program cycle.

The number of consecutive partial page programming operations (NOP) within the same page must not exceed the number indicated in Table 23 on page 37. Pages may be programmed in any order within a block.

Users who use "EDC check" (for S34ML02G1 and S34ML04G1 only) in copy back must comply with some limitations related to data handling during one page program sequence. Refer to Section 3.8 on page 19 for details.

If a Page Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted page is not used for further reading or programming operations until the next uninterrupted block erase is complete.

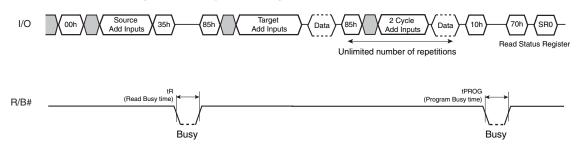

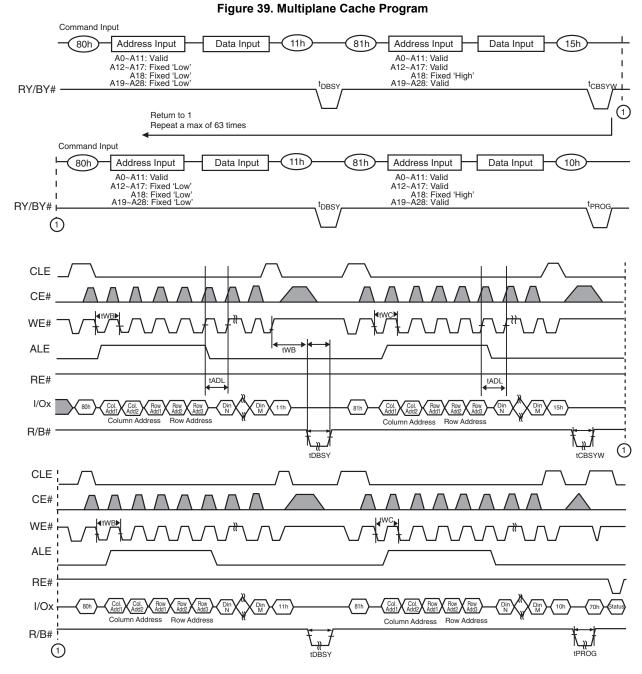

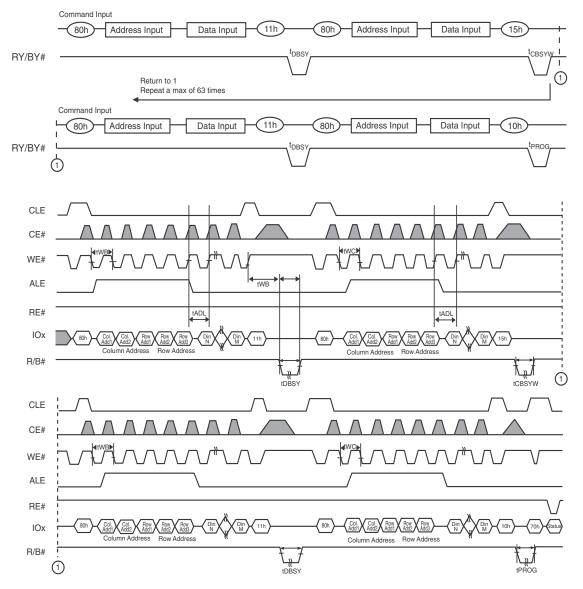

## 3.3 Multiplane Program — S34ML02G1 and S34ML04G1

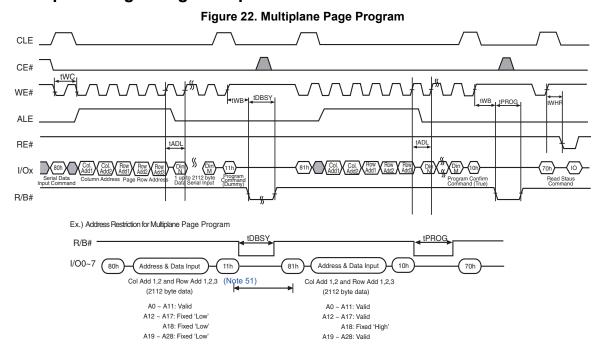

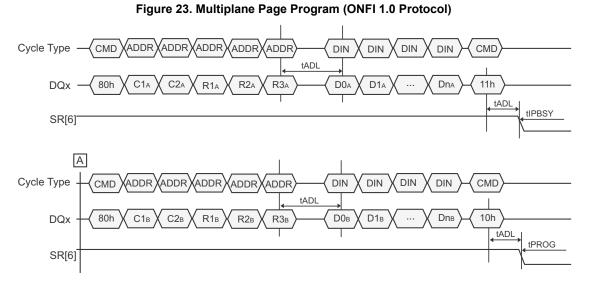

The S34ML02G1 and S34ML04G1 devices support Multiplane Program, making it possible to program two pages in parallel, one page per plane.

A Multiplane Program cycle consists of a double serial data loading period in which up to 4224 bytes (×8) or 2112 words (×16) of data may be loaded into the data register, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell. The serial data loading period begins with inputting the Serial Data Input command (80h), followed by the five cycle address inputs and serial data for the 1st page. The address for this page must be in the 1st plane (PLA0 = 0). The device supports Random Data Input exactly the same as in the case of page program operation. The Dummy Page Program Confirm command (11h) stops 1st page data input and the device becomes busy for a short time ( $t_{DBSY}$ ). Once it has become ready again, the '81h' command must be issued, followed by 2nd page address (5 cycles) and its serial data input. The address for this page must be in the 2nd plane (PLA0 = 1). The Program Confirm command (10h) starts parallel programming of both pages.

Figure 22 on page 44 describes the sequences using the legacy protocol. In this case, the block address bits for the first plane are all zero and the second address issued selects the block for both planes. Figure 23 on page 44 describes the sequences using the ONFI protocol. For both addresses issued in this protocol, the block address bits must be the same except for the bit(s) that select the plane.

The user can check operation status by monitoring R/B# pin or reading the Status Register (command 70h or 78h). The Read Status Register command is also available during Dummy Busy time (t<sub>DBSY</sub>). In case of failure in either page program, the fail bit of the Status Register will be set. Refer to Section 3.9 on page 21 for further info.

The number of consecutive partial page programming operations (NOP) within the same page must not exceed the number indicated in Table 23 on page 37. Pages may be programmed in any order within a block.

If a Multiplane Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted pages are not used for further reading or programming operations until the next uninterrupted block erases are complete for the applicable blocks.

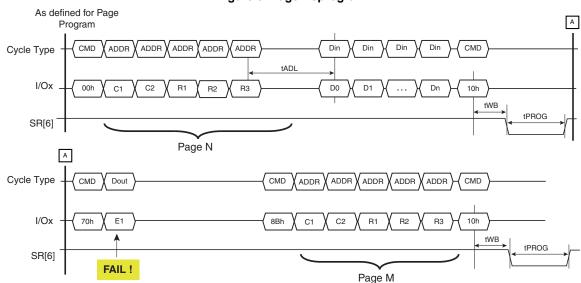

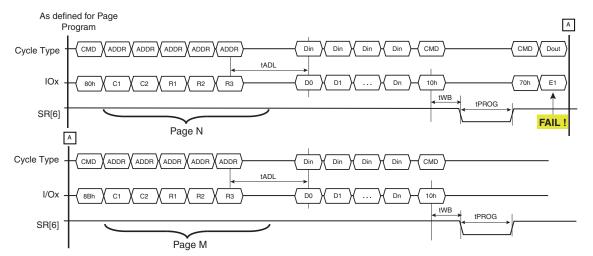

## 3.4 Page Reprogram — S34ML02G1 and S34ML04G1

Page Program may result in a fail, which can be detected by Read Status Register. In this event, the host may call Page Reprogram. This command allows the reprogramming of the same pattern of the last (failed) page into another memory location. The command sequence initiates with reprogram setup (8Bh), followed by the five cycle address inputs of the target page. If the target pattern for the destination page is not changed compared to the last page, the program confirm can be issued (10h) without any data input cycle, as described in Figure 8.

### Figure 8. Page Reprogram

On the other hand, if the pattern bound for the target page is different from that of the previous page, data in cycles can be issued before program confirm '10h', as described in Figure 9.

Figure 9. Page Reprogram with Data Manipulation

The device supports Random Data Input within a page. The column address of next data, which will be entered, may be changed to the address which follows the Random Data Input command (85h). Random Data Input may be operated multiple times regardless of how many times it is done in a page.

The Program Confirm command (10h) initiates the re-programming process. The internal write state controller automatically executes the algorithms and controls timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status Register command may be issued to read the Status Register. The system controller can detect the completion of a program cycle by monitoring the R/B# output, or the Status bit (I/O6) of the Status Register. Only the Read Status command and Reset command are valid when programming is in progress. When the Page Program is complete, the Write Status Bit (I/O0) may be checked. The internal write verify detects only errors for 1's that are not successfully programmed to 0's. The command register remains in Read Status command mode until another valid command is written to the command register.

The Page Reprogram must be issued in the same plane as the Page Program that failed. In order to program the data to a different plane, use the Page Program operation instead. The Multiplane Page Reprogram can re-program two pages in parallel, one per plane. The Multiplane Page Reprogram operation is performed after a failed Multiplane Page Program operation. The command sequence is very similar to Figure 22 on page 44, except that it requires the Page Reprogram Command (8Bh) instead of 80h and 81h.

If a Page Reprogram operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted page is not used for further reading or programming operations until the next uninterrupted block erase is complete.

## 3.5 Block Erase

The Block Erase operation is done on a block basis. Block address loading is accomplished in three cycles (two cycles for S34ML01G1) initiated by an Erase Setup command (60h). Only the block address bits are valid while the page address bits are ignored.

The Erase Confirm command (D0h) following the block address loading initiates the internal erasing process. This two-step sequence of setup followed by the execution command ensures that memory contents are not accidentally erased due to external noise conditions.

At the rising edge of WE# after the erase confirm command input, the internal write controller handles erase and erase verify. Once the erase process starts, the Read Status Register commands (70h or 78h) may be issued to read the Status Register.

The system controller can detect the completion of an erase by monitoring the R/B# output, or the Status bit (I/O6) of the Status Register. Only the Read Status commands (70h or 78h) and Reset command are valid while erasing is in progress. When the erase operation is completed, the Write Status Bit (I/O0) may be checked. Figure 24 on page 45 details the sequence.

If a Block Erase operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted block is erased under continuous power conditions before that block can be trusted for further programming and reading operations.

## 3.6 Multiplane Block Erase — S34ML02G1 and S34ML04G1

Multiplane Block Erase allows the erase of two blocks in parallel, one block per memory plane.

The Block erase setup command (60h) must be repeated two times, followed by 1st and 2nd block address respectively (3 cycles each). As for block erase, D0h command makes embedded operation start. In this case, multiplane erase does not need any Dummy Busy Time between 1st and 2nd block insertion. See Table 23 on page 37 for performance information.

For the Multiplane Block Erase operation, the address of the first block must be within the first plane (PLA0 = 0) and the address of the second block in the second plane (PLA0 = 1). See Figure 25 on page 45 for a description of the legacy protocol. In this case, the block address bits for the first plane are all zero and the second address issued selects the block for both planes. Figure 26 on page 46 describes the sequences using the ONFI protocol. For both addresses issued in this protocol, the block address bits must be the same except for the bit(s) that select the plane.

The user can check operation status by monitoring R/B# pin or reading the Status Register (command 70h or 78h). The Read Status Register command is also available during Dummy Busy time (t<sub>DBSY</sub>). In case of failure in either erase, the fail bit of the Status Register will be set. Refer to Section 3.9 on page 21 for further information.

If a Multiplane Block Erase operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted blocks are erased under continuous power conditions before those blocks can be trusted for further programming and reading operations.

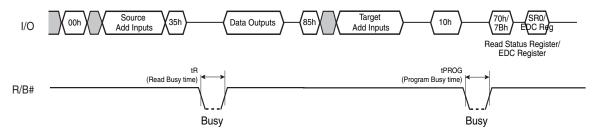

### 3.7 Copy Back Program

The copy back feature is intended to quickly and efficiently rewrite data stored in one page without utilizing an external memory. Since the time-consuming cycles of serial access and re-loading cycles are removed, the system performance is greatly improved. The benefit is especially obvious when a portion of a block needs to be updated and the rest of the block also needs to be copied to the newly assigned free block. The operation for performing a copy back is a sequential execution of page-read (without mandatory serial access) and Copy Back Program with the address of destination page. A read operation with the '35h' command and the address of the source page moves the whole page of data into the internal data register. As soon as the device returns to the Ready state, optional data read-out is allowed by toggling RE# (see Figure 27 on page 46), or the Copy Back Program command (85h) with the address cycles of the destination page may be written. The Program Confirm command (10h) is required to actually begin programming.

The source and the destination pages in the Copy Back Program sequence must belong to the same device plane (same PLA0 for S34ML02G1 and S34ML04G1). Copy Back Read and Copy Back Program for a given plane must be between odd address pages or between even address pages for the device to meet the program time (t<sub>PROG</sub>) specification. Copy Back Program may not meet this specification when copying from an odd address page (source page) to an even address page (target page) or from an even address page (source page) to an odd address page (target page).

The data input cycle for modifying a portion or multiple distinct portions of the source page is allowed as shown in Figure 28 on page 46. As noted in Section 1. on page 4 the device may include an automatic EDC (for S34ML02G1 and S34ML04G1) check during the copy back operation, to detect single bit errors in EDC units contained within the source page. More details on EDC operation and limitations related to data input handling during one Copy Back Program sequence are available in Section 3.8 on page 19.

If a Copy Back Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted page is not used for further reading or programming operations until the next uninterrupted block erase is complete.

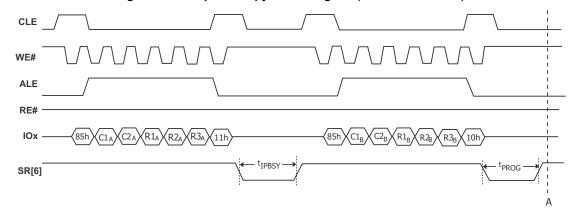

### 3.7.1 Multiplane Copy Back Program — S34ML02G1 and S34ML04G1

The device supports Multiplane Copy Back Program with exactly the same sequence and limitations as the Page Program. Multiplane Copy Back Program must be preceded by two single page Copy Back Read command sequences (1st page must be read from the 1st plane and 2nd page from the 2nd plane).

Multiplane Copy Back cannot cross plane boundaries — the contents of the source page of one device plane can be copied only to a destination page of the same plane. EDC check is available also for Multiplane Copy Back Program only for S34ML02G1 and S34ML04G1.

When "EDC check" is used in copy back, it must comply with some limitations related to data handling during one Multiplane Copy Back Program sequence. Please refer to Section 3.8 on page 19 for details on EDC operation. The Multiplane Copy Back Program sequence represented in Figure 29 on page 47 shows the legacy protocol. In this case, the block address bits for the first plane are all zero and the second address issued selects the block for both planes. Figure 30 on page 47 describes the sequence using the ONFI protocol. For both addresses issued in this protocol, the block address bits must be the same except for the bit(s) that select the plane.

If a Multiplane Copy Back Program operation is interrupted by hardware reset, power failure or other means, the host must ensure that the interrupted pages are not used for further reading or programming operations until the next uninterrupted block erases are complete for the applicable blocks.

### 3.7.2 Special Read for Copy Back — S34ML02G1 and S34ML04G1

The S34ML02G1 and S34ML04G1 devices support Special Read for Copy Back. If Copy Back Read (described in Section 3.7 and Section 3.7.1 on page 19) is triggered with confirm command '36h' instead '35h', Copy Back Read from target page(s) will be executed with an increased internal (V<sub>PASS</sub>) voltage.

This special feature is used in order to minimize the number of read errors due to over-program or read disturb — it shall be used only if ECC read errors have occurred in the source page using Page Read or Copy Back Read sequences.

Excluding the Copy Back Read confirm command, all other features described in Section 3.7 and Section 3.7.1 for standard copy back remain valid (including the figures referred to in those sections).

## 3.8 EDC Operation — S34ML02G1 and S34ML04G1

Error Detection Code check is a feature that can be used during the copy back operation (both single and multiplane) to detect single bit errors occurring in the source page(s).

Note: The S34ML01G1 device does not support EDC.

- EDC check allows detection of up to 1 single bit error every 528 bytes, where each 528 byte group is composed of 512 bytes of main array and 16 bytes of spare area (see Table 10 and Table 11 on page 21). The described 528-byte area is called an "EDC unit."

- In the ×16 device, EDC allows detection of up to 1 single bit error every 264 words, where each 264 word group is composed by 256 words of main array and 8 words of spare area see Table 10 and Table 11 on page 21). The described 264-word area is called "EDC unit."

EDC results can be checked through a specific Read EDC register command, available only after issuing a Copy Back Program or a Multiplane Copy Back Program. The EDC register can be queried during the copy back program busy time (t<sub>PROG</sub>).

For the "EDC check" feature to operate correctly, specific conditions on data input handling apply for program operations.

For the case of Page Program, Multiplane Page Program, Page Reprogram, Multiplane Page Reprogram, Cache Program, and Multiplane Cache Program operations:

- In Section 3.2 on page 15 it was explained that a number of consecutive partial program operations (NOP) is allowed within the same page. In case this feature is used, the number of partial program operations occurring in the same EDC unit must not exceed 1. In other words, page program operations must be performed on the whole page, or on whole EDC unit at a time.

- "Random Data Input" in a given EDC unit can be executed several times during one page program sequence, but data cannot be written to any column address more than once before the program is initiated.

For the case of Copy Back Program or Multiplane Copy Back Program operations:

- If Random Data Input is applied in a given EDC unit, the entire EDC unit must be written to the page buffer. In other words, the EDC check is possible only if the whole EDC unit is modified during one Copy Back Program sequence.

- "Random Data Input" in a given EDC unit can be executed several times during one Copy Back Program sequence, but data insertion in each column address of the EDC unit must not exceed 1.

If you use copy back without EDC check, none of the limitations described above apply.

After a Copy Back Program operation, the host can use Read EDC Status Register to check the status of both the program operation and the Copy Back Read. If the EDC was valid and an error was reported in the EDC (see Table 9 on page 20), the host may perform Special Read For Copy Back on the source page and attempt the Copy Back Program again. If this also fails, the host can execute a Page Read operation in order to correct a single bit error with external ECC software or hardware.

### 3.8.1 Read EDC Status Register — S34ML02G1 and S34ML04G1

This operation is available only after issuing a Copy Back Program and it allows the detection of errors during Copy Back Read. In the case of multiplane copy back, it is not possible to know which of the two read operations caused the error.

After writing the Read EDC Status Register command (7Bh) to the command register, a read cycle outputs the content of the EDC Register to the I/O pins on the falling edge of CE# or RE#, whichever occurs last.

The operation is the same as the Read Status Register command. Refer to Table 9 for specific EDC Register definitions:

| ID | Copy Back Program | Coding                         |

|----|-------------------|--------------------------------|

| 0  | Pass / Fail       | Pass: 0; Fail: 1               |

| 1  | EDC status        | No error: 0; Error: 1          |

| 2  | EDC validity      | Invalid: 0; Valid: 1           |

| 3  | NA                | —                              |

| 4  | NA                | —                              |

| 5  | Ready / Busy      | Busy: 0; Ready: 1              |

| 6  | Ready / Busy      | Busy: 0; Ready: 1              |

| 7  | Write Protect     | Protected: 0; Not Protected: 1 |

#### Table 9. EDC Register Coding

### Table 10. Page Organization in EDC Units

|              | Main Field (2048 Byte) |              |              |              | Spare Field (64 Byte) |              |              |  |

|--------------|------------------------|--------------|--------------|--------------|-----------------------|--------------|--------------|--|

| "A" area     | "B" area               | "C" area     | "D" area     | "E" area     | "F" area              | "G" area     | "H" area     |  |

| (1st sector) | (2nd sector)           | (3rd sector) | (4th sector) | (1st sector) | (2nd sector)          | (3rd sector) | (4th sector) |  |

|              | ·                      |              | ×8           |              |                       |              |              |  |

| 512 byte     | 512 byte               | 512 byte     | 512 byte     | 16 byte      | 16 byte               | 16 byte      | 16 byte      |  |

|              | ×16                    |              |              |              |                       |              |              |  |

| 256 words    | 256 words              | 256 words    | 256 words    | 8 words      | 8 words               | 8 words      | 8 words      |  |

#### Table 11. Page Organization in EDC Units by Address

| Sector              | Main Field (0 | Column 0-2047)           | Spare Field (Column 2048-2111) |                |  |

|---------------------|---------------|--------------------------|--------------------------------|----------------|--|

| Sector              | Area Name     | Area Name Column Address |                                | Column Address |  |

|                     |               | ×8                       |                                |                |  |

| 1st 528-byte Sector | А             | 0-511                    | E                              | 2048-2063      |  |

| 2nd 528-byte Sector | В             | 512-1023                 | F                              | 2064-2079      |  |

| 3rd 528-byte Sector | С             | 1024-1535                | G                              | 2080-2095      |  |

| 4th 528-byte Sector | D             | 1536-2047                | Н                              | 2096-2111      |  |

|                     |               | ×16                      |                                |                |  |

| 1st 256-word Sector | A             | 0-255                    | E                              | 1024-1031      |  |

| 2nd 256-word Sector | В             | 256-511                  | F                              | 1032-1039      |  |

| 3rd 256-word Sector | С             | 512-767                  | G                              | 1040-1047      |  |

| 4th 256-word Sector | D             | 768-1023                 | Н                              | 1048-1055      |  |

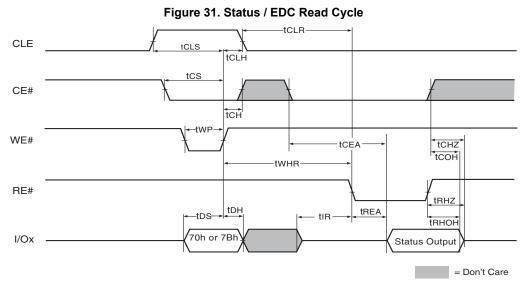

### 3.9 Read Status Register

The Status Register is used to retrieve the status value for the last operation issued. After writing 70h command to the command register, a read cycle outputs the content of the Status Register to the I/O pins on the falling edge of CE# or RE#, whichever occurs last. This two-line control allows the system to poll the progress of each device in multiple memory connections even when R/B# pins are common-wired. Refer to Section 13 on page 22 for specific Status Register definition, and to Figure 31 on page 48 for timings.

If the Read Status Register command is issued during multiplane operations then Status Register polling will return the combined status value related to the outcome of the operation in the two planes according to the following table.

#### Table 12. Read Status Definition

| Status Register Bit    | Composite Status Value |

|------------------------|------------------------|

| Bit 0, Pass/Fail       | OR                     |

| Bit 1, Cache Pass/Fail | OR                     |

In other words, the Status Register is dynamic; the user is not required to toggle RE# / CE# to update it.

The command register remains in Status Read mode until further commands are issued. Therefore, if the Status Register is read during a random read cycle, the read command (00h) must be issued before starting read cycles.

Note: The Read Status Register command shall not be used for concurrent operations in multi-die stack configurations (single CE#). "Read Status Enhanced" shall be used instead.

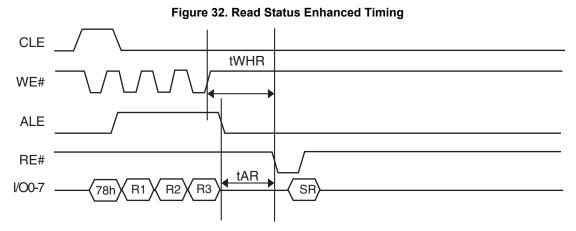

## 3.10 Read Status Enhanced — S34ML02G1 and S34ML04G1

Read Status Enhanced is used to retrieve the status value for a previous operation in the specified plane.

Figure 32 on page 48 defines the Read Status Enhanced behavior and timings. The plane and die address must be specified in the command sequence in order to retrieve the status of the die and the plane of interest.

Refer to Table 13 for specific Status Register definitions. The command register remains in Status Read mode until further commands are issued.

The Status Register is dynamic; the user is not required to toggle RE# / CE# to update it.

## 3.11 Read Status Register Field Definition

Table 13 below lists the meaning of each bit of the Read Status Register and Read Status Enhanced (S34ML02G1 and S34ML04G1).

| ID | Page Program /<br>Page Reprogram | Block Erase   | Read         | Read Cache   | Cache Program /<br>Cache Reprogram | Coding                                       |

|----|----------------------------------|---------------|--------------|--------------|------------------------------------|----------------------------------------------|

| 0  | Pass / Fail                      | Pass / Fail   | NA           | NA           | Pass / Fail                        | N Page<br>Pass: 0<br>Fail: 1                 |

| 1  | NA                               | NA            | NA           | NA           | Pass / Fail                        | N - 1 Page<br>Pass: 0<br>Fail: 1             |

| 2  | NA                               | NA            | NA           | NA           | NA                                 | _                                            |

| 3  | NA                               | NA            | NA           | NA           | NA                                 |                                              |

| 4  | NA                               | NA            | NA           | NA           | NA                                 |                                              |

| 5  | Ready / Busy                     | Ready / Busy  | Ready / Busy | Ready / Busy | Ready / Busy                       | Internal Data Operation Active: 0<br>Idle: 1 |

| 6  | Ready / Busy                     | Ready / Busy  | Ready / Busy | Ready / Busy | Ready / Busy                       | Ready / Busy<br>Busy: 0<br>Ready: 1          |

| 7  | Write Protect                    | Write Protect | NA           | NA           | Write Protect                      | Protected: 0<br>Not Protected: 1             |

Table 13. Status Register Coding

### 3.12 Reset

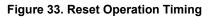

The Reset feature is executed by writing FFh to the command register. If the device is in the Busy state during random read, program, or erase mode, the Reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data may be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value E0h when WP# is high or value 60h when WP# is low. If the device is already in reset state a new Reset command will not be accepted by the command register. The R/B# pin transitions to low for t<sub>RST</sub> after the Reset command is written. Refer to Figure 33 on page 48 for further details. The Status Register can also be read to determine the status of a Reset operation.

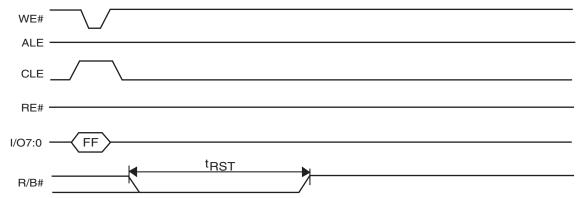

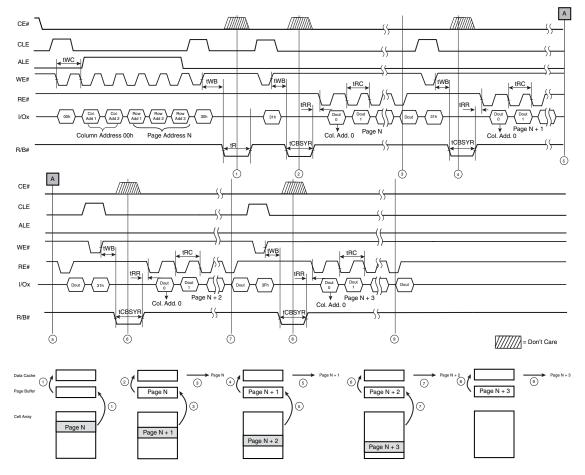

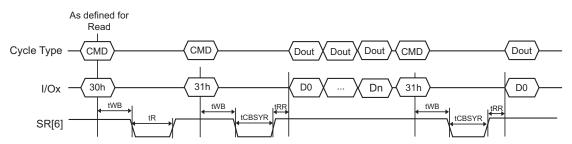

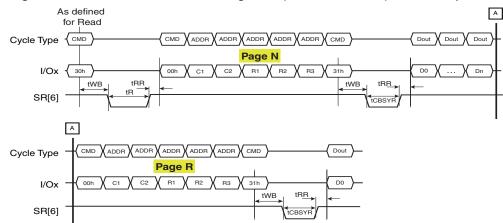

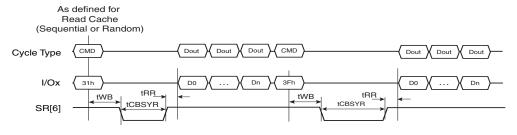

## 3.13 Read Cache

Read Cache can be used to increase the read operation speed, as defined in Section 3.1 on page 15, and it cannot cross a block boundary. As soon as the user starts to read one page, the device automatically loads the next page into the cache register. Serial data output may be executed while data in the memory is read into the cache register. Read Cache is initiated by the Page Read sequence (00-30h) on a page M.

After random access to the first page is complete (R/B# returned to high, or Read Status Register I/O6 switches to high), two command sequences can be used to continue read cache:

- Read Cache (command '31h' only): once the command is latched into the command register (see Figure 35 on page 49), device goes busy for a short time (t<sub>CBSYR</sub>), during which data of the first page is transferred from the data register to the cache register. At the end of this phase, the cache register data can be output by toggling RE# while the next page (page address M+1) is read from the memory array into the data register.

- Read Cache Enhanced (sequence '00h' <page N address> '31'): once the command is latched into the command register (see Figure 36 on page 50), device goes busy for a short time (t<sub>CBSYR</sub>), during which data of the first page is transferred from the data register to the cache register. At the end of this phase, cache register data can be output by toggling RE# while page N is read from the memory array into the data register.

Note: The S34ML01G1 device does not support Read Cache Enhanced.

Subsequent pages are read by issuing additional Read Cache or Read Cache Enhanced command sequences. If serial data output time of one page exceeds random access time (t<sub>R</sub>), the random access time of the next page is hidden by data downloading of the previous page.

On the other hand, if 31h is issued prior to completing the random access to the next page, the device will stay busy as long as needed to complete random access to this page, transfer its contents into the cache register, and trigger the random access to the following page.

To terminate the Read Cache operation, 3Fh command should be issued (see Figure 37 on page 50). This command transfers data from the data register to the cache register without issuing next page read.

During the Read Cache operation, the device doesn't allow any other command except for 00h, 31h, 3Fh, Read SR, or Reset (FFh). To carry out other operations, Read Cache must be terminated by the Read Cache End command (3Fh) or the device must be reset by issuing FFh.

Read Status command (70h) may be issued to check the status of the different registers and the busy/ready status of the cached read operations.

- The Cache-Busy status bit I/O6 indicates when the cache register is ready to output new data.

- The status bit I/O5 can be used to determine when the cell reading of the current data register contents is complete.