# Easy to Use, Low Power, Sub GHz, ISM/SRD, FSK/GFSK, Transceiver IC

**ADF7024 Data Sheet**

#### **FEATURES**

Radio frequency (RF) bands: 431 MHz to 435 MHz and 862 MHz to 928 MHz

Data rates supported: 9.6 kbps, 38.4 kbps, 50 kbps, 100 kbps, 200 kbps, and 300 kbps

Modulation: two-level frequency (FSK) and Gaussian frequency (GFSK) shift keving

2.2 V to 3.6 V power supply

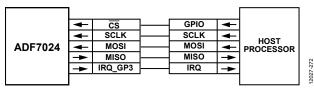

Ultralow power sleep modes for long battery life Simple serial port interface (SPI) control interface

Fast radio state transitions

Automatic frequency control (AFC) and automatic gain control (AGC)

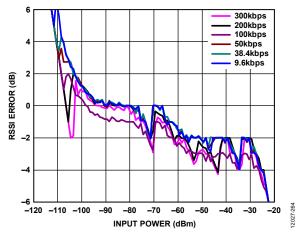

Digital received signal strength indication (RSSI)

Fully integrated low noise RF synthesizer and transmit (Tx)/receive (Rx) switch

Image rejection calibration (U.S. Patent 8,238,865 and U.S. Patent 8,358,993)

Integrated packet management support

Insertion/detection of preamble/sync word/cyclic redundancy check (CRC)

Manchester and 8-bit/10-bit data encoding and decoding Data whitening

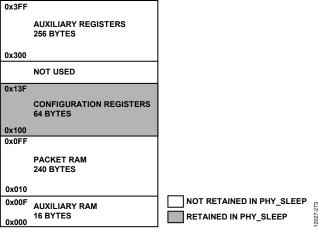

240-byte packet buffer for Tx/Rx data

Smart wake mode (SWM)

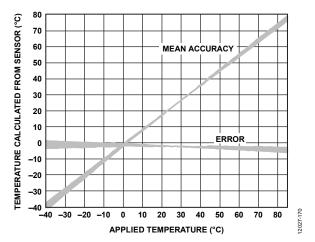

Autonomous carrier sense, packet sniffing, and reception Integrated battery alarm and temperature sensor **Integrated RC oscillator** On-chip, 8-bit analog-to-digital converter (ADC)

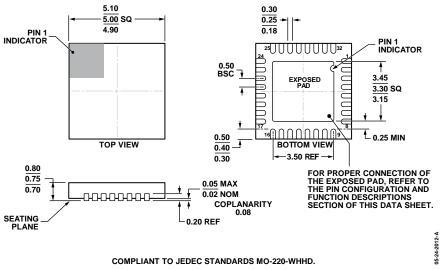

5 mm × 5 mm, 32-lead LFCSP

#### **Receiver performance**

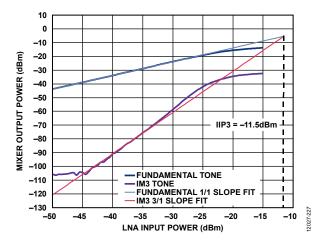

Highly linear: -11.5 dBm input IP3 Blocking: 76 dB at 10 MHz offset Receiver sensitivity, bit error rate (BER)

-111 dBm at 9.6 kbps

-105 dBm at 100 kbps Low power: 12.8 mA in Rx

**Transmitter performance**

High efficiency power amplifier (PA): 23.3 mA in Tx at 10 dBm

Output power range: -20 dBm to +13.5 dBm

Output power resolution: 0.5 dB

Low power mode performance

0.33 µA in PHY\_SLEEP mode (Deep Sleep Mode 1)

0.75 µA in PHY\_SLEEP mode (32 kHz RC oscillator active)

11.75 µA autonomous Rx sniff using SWM, 300 kbps

**Supported regulations**

**ETSI EN 300 220**

FCC Part 15.231, Part 15.247, Part 15.249

#### **APPLICATIONS**

Wireless sensor networks (WSNs) Home and building automation sset tracking Process and building control Industrial control Internet of Things (IoT)

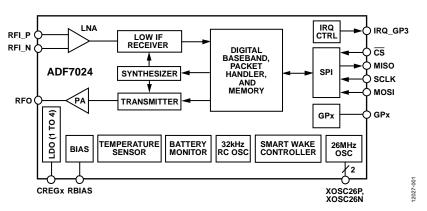

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

# **TABLE OF CONTENTS**

6/14—Revision 0: Initial Version

| reatures                                          |

|---------------------------------------------------|

| Applications1                                     |

| Functional Block Diagram                          |

| Revision History                                  |

| General Description                               |

| Specifications4                                   |

| RF and Synthesizer Specifications4                |

| Transmitter Specifications                        |

| Receiver Specifications6                          |

| Timing and Digital Specifications8                |

| Auxilary Block Specifications9                    |

| General Specifications                            |

| Timing Specifications                             |

| Absolute Maximum Ratings                          |

| ESD Caution                                       |

| DEVICION LUCTORY                                  |

| REVISION HISTORY                                  |

| 7/15—Rev. A to Rev. B                             |

| Changes to Features Section                       |

| Changes to General Description Section            |

| Changes to Theory of Operation Section            |

| Changes to Radio Profiles Section                 |

| Changes to Typical Application Circuit Section    |

| 7/14—Rev. 0 to Rev. A                             |

| Changes to Adjacent Channel Rejection Parameter 6 |

| Changes to Table 1121                             |

| Updated Outline Dimensions                        |

| Pin Configuration and Function Descriptions | 13 |

|---------------------------------------------|----|

| Typical Performance Characteristics         | 15 |

| Theory of Operation                         | 21 |

| SPI Interface                               | 21 |

| Radio Control                               | 21 |

| Memory Map                                  | 21 |

| Radio Blocks                                | 21 |

| Radio Profiles                              | 22 |

| Packet Management                           | 22 |

| Smart Wake Modes                            | 22 |

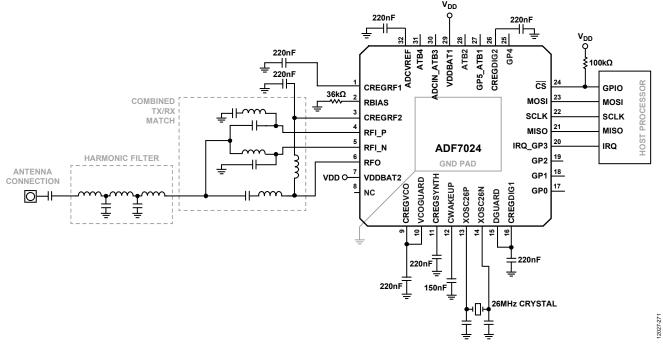

| Typical Application Circuit                 | 23 |

| Outline Dimensions                          | 24 |

| Ordering Guide                              | 24 |

## **GENERAL DESCRIPTION**

The ADF7024 is an ultralow power, integrated transceiver for use in the license-free ISM bands at 433 MHz, 868 MHz, and 915 MHz. Its ease of use and high performance make it suitable for a wide variety of wireless applications. The ADF7024 is suitable for operation under the European ETSI EN 300-220 regulation, the North American FCC Part 15 regulation, and other similar regulatory standards.

The ADF7024 can operate under a number of predefined radio profiles. For each radio profile, optimized register settings are provided for the ADF7024 radio. This ensures that the RF communication layer works seamlessly, allowing the user to concentrate on the protocol and system level design and prototyping. The radio profiles cover common data rate and modulation options. There are six radio profiles in total, as shown in Table 1.

The ADF7024 operates with a power supply range of 2.2 V to 3.6 V and has very low power consumption in both Tx and Rx modes, enabling long lifetimes in battery-operated systems while maintaining excellent RF performance.

The low IF receiver minimizes power consumption and provides excellent sensitivity. The receiver is exceptionally linear and, therefore, is very resilient to the presence of interferers in spectrally noisy environments. The highly efficient transmitter has programmable output power up to 13.5 dBm and automatic power amplifier (PA) ramping to meet transient spurious

specifications. The RF synthesizer comprises a voltage controlled oscillator (VCO), a low noise fractional-N phase-locked loop (PLL) and a loop filter, all of which are fully integrated and automatically calibrated. This agile frequency synthesizer facilitates the implementation of frequency-hopping spread spectrum (FHSS) systems.

The smart wake mode (SWM) allows the ADF7024 to wake up autonomously from sleep using the internal wake-up timer without intervention from the host processor. This functionality allows carrier sense, packet sniffing, and packet reception while the host processor is in sleep, thereby reducing overall system current consumption.

The ADF7024 eases the processing burden of the host processor by integrating the lower layers of a typical communication protocol stack. The host processor can configure the ADF7024 using a simple command-based protocol over a standard 4-wire SPI interface. A single-byte command transitions the radio between states or performs a radio function.

A complete wireless solution can be built using a small number of external discrete components and a host processor (typically a microcontroller).

For more information, see the ADF7024 Hardware Reference Manual, UG-698, which is only available as part of the ADF7024 design resource package.

**Table 1. Radio Profiles**

| Radio<br>Profile | Data Rate<br>(kbps) | Modulation | Frequency Deviation (kHz) | IF Bandwidth<br>(kHz) | Typical Channel<br>Spacing (kHz) | RF Range (MHz)         |

|------------------|---------------------|------------|---------------------------|-----------------------|----------------------------------|------------------------|

| Α                | 9.6                 | FSK/GFSK   | 9.6                       | 100                   | 200                              | 862 to 928             |

| В                | 38.4                | FSK/GFSK   | 20                        | 100                   | 200                              | 431 to 435, 862 to 928 |

| C                | 50                  | FSK/GFSK   | 25                        | 100                   | 200                              | 862 to 928             |

| D                | 100                 | FSK/GFSK   | 25                        | 100                   | 200                              | 862 to 928             |

| E                | 200                 | FSK/GFSK   | 50                        | 200                   | 400                              | 862 to 928             |

| F                | 300                 | FSK/GFSK   | 75                        | 300                   | 600                              | 862 to 928             |

# **SPECIFICATIONS**

$V_{DD} = VDDBAT1 = VDDBAT2 = 2.2\ V\ to\ 3.6\ V, GND = 0\ V, T_A = T_{MIN}\ to\ T_{MAX}, unless\ otherwise\ noted.$  Typical specifications are at  $V_{DD} = 3\ V, T_A = 25^{\circ}C.$

### RF AND SYNTHESIZER SPECIFICATIONS

Table 2.

| Parameter                    | Min | Тур   | Max | Unit   | Test Conditions/Comments                                                                                                                      |

|------------------------------|-----|-------|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| RF CHARACTERISTICS           |     |       |     |        |                                                                                                                                               |

| Frequency Ranges             | 862 |       | 928 | MHz    | All radio profiles                                                                                                                            |

|                              | 431 |       | 435 | MHz    | Radio Profile B only                                                                                                                          |

| PHASE-LOCKED LOOP (PLL)      |     |       |     |        |                                                                                                                                               |

| Channel Frequency Resolution |     | 396.7 |     | Hz     |                                                                                                                                               |

| Phase Noise (In-Band)        |     | -88   |     | dBc/Hz | 10 kHz offset, PA output power = 10 dBm, RF = 868 MHz                                                                                         |

| Phase Noise at Offset        |     |       |     |        |                                                                                                                                               |

| 1 MHz                        |     | -126  |     | dBc/Hz | PA output power = 10 dBm, RF = 868 MHz                                                                                                        |

| 2 MHz                        |     | -131  |     | dBc/Hz | PA output power = 10 dBm, RF = 868 MHz                                                                                                        |

| 10 MHz                       |     | -142  |     | dBc/Hz | PA output power = 10 dBm, RF = 868 MHz                                                                                                        |

| VCO Calibration Time         |     | 142   |     | μs     |                                                                                                                                               |

| Synthesizer Settling Time    |     | 56    |     | μs     | Frequency synthesizer settles to within ±5 ppm of the target frequency within this time following the VCO calibration in transmit and receive |

| CRYSTAL OSCILLATOR           |     |       |     |        |                                                                                                                                               |

| Crystal Frequency            |     | 26    |     | MHz    | Parallel load resonant crystal                                                                                                                |

| Recommended Load Capacitance | 7   |       | 18  | pF     |                                                                                                                                               |

| Maximum Crystal ESR          |     | 1800  |     | Ω      | 26 MHz crystal with 18 pF load capacitance                                                                                                    |

| Pin Capacitance              |     | 2.1   |     | pF     | Capacitance for XOSC26P and XOSC26N                                                                                                           |

| Start-Up Time                |     | 310   |     | μs     | 26 MHz crystal with 7 pF load capacitance                                                                                                     |

|                              |     | 388   |     | μs     | 26 MHz crystal with 18 pF load capacitance                                                                                                    |

| SPURIOUS EMISSIONS           |     |       |     |        |                                                                                                                                               |

| Integer Boundary Spurious    |     |       |     |        |                                                                                                                                               |

| 910.1 MHz                    |     | -39   |     | dBc    | Radio Profile A, integer boundary spur at 910 MHz (26 MHz × 35), inside synthesizer loop bandwidth                                            |

| 911.0 MHz                    |     | -79   |     | dBc    | Radio Profile A, integer boundary spur at 910 MHz (26 MHz × 35), outside synthesizer loop bandwidth                                           |

| Reference Spurious           |     |       |     |        |                                                                                                                                               |

| 868 MHz/915 MHz              |     | -80   |     | dBc    | Radio Profile A                                                                                                                               |

| Clock Related Spur Level     |     | -60   |     | dBc    | Measured in a span of $\pm 350$ MHz, RF = 868.95 MHz, PA output power = 10 dBm, $V_{DD}$ = 3.6 V                                              |

### TRANSMITTER SPECIFICATIONS

Table 3.

| Parameter                          | Min | Тур          | Max | Unit | Test Conditions/Comments                                 |

|------------------------------------|-----|--------------|-----|------|----------------------------------------------------------|

| DATA RATE                          |     |              |     |      |                                                          |

| Radio Profile A                    |     | 9.6          |     | kbps |                                                          |

| Radio Profile B                    |     | 38.4         |     | kbps |                                                          |

| Radio Profile C                    |     | 50           |     | kbps |                                                          |

| Radio Profile D                    |     | 100          |     | kbps |                                                          |

| Radio Profile E                    |     | 200          |     | kbps |                                                          |

| Radio Profile F                    |     | 300          |     | kbps |                                                          |

| FSK/GFSK FREQUENCY DEVIATION       |     |              |     |      |                                                          |

| Radio Profile A                    |     | 9.6          |     | kHz  |                                                          |

| Radio Profile B                    |     | 20           |     | kHz  |                                                          |

| Radio Profile C                    |     | 25           |     | kHz  |                                                          |

| Radio Profile D                    | 1   | 25           |     | kHz  |                                                          |

| Radio Profile E                    |     | 50           |     | kHz  |                                                          |

| Radio Profile F                    |     | 75           |     | kHz  |                                                          |

| GAUSSIAN FILTER BANDWITH TIME (BT) |     | 0.5          |     |      | Not programmable                                         |

| POWER AMPLIFIER                    |     |              |     |      |                                                          |

| Maximum Power <sup>1</sup>         |     | 13.5         |     | dBm  | Programmable, separate PA and LNA match <sup>2</sup>     |

| Minimum Power                      |     | -20          |     | dBm  |                                                          |

| Transmit Power                     |     |              |     |      |                                                          |

| Variation vs. Temperature          |     | ±0.5         |     | dB   | -40°C to +85°C, RF = 868 MHz                             |

| Variation vs. V <sub>DD</sub>      |     | ±1           |     | dB   | 2.2 V to 3.6 V, RF = 868 MHz                             |

| Flatness                           |     | ±1           |     | dB   | 902 MHz to 928 MHz and 863 MHz to 870 MHz                |

| Programmable Step Size             |     | 0.5          |     | dB   | -20 dBm to +13.5 dBm, programmable in 60 steps           |

| HARMONICS                          |     |              |     |      | 868 MHz, unfiltered conductive, PA output power = 10 dBm |

| Second Harmonic                    |     | -15.1        |     | dBc  |                                                          |

| Third Harmonic                     |     | -29.3        |     | dBc  |                                                          |

| All Other Harmonics                |     | -47.6        |     | dBc  |                                                          |

| OPTIMUM PA LOAD IMPEDANCE          |     |              |     |      |                                                          |

| PA Output in Transmit Mode         |     |              |     |      |                                                          |

| $f_{RF} = 915 \text{ MHz}$         |     | 50.8 + j10.2 | 2   | Ω    |                                                          |

| $f_{RF} = 868 \text{ MHz}$         |     | 45.5 + j12.1 |     | Ω    |                                                          |

| $f_{RF} = 433 \text{ MHz}$         | 1   | 46.8 + j19.9 | )   | Ω    |                                                          |

| PA Output in Receive Mode          | 1   |              |     |      |                                                          |

| $f_{RF} = 915 \text{ MHz}$         |     | 9.4 – j124   |     | Ω    |                                                          |

| $f_{RF} = 868 \text{ MHz}$         | 1   | 9.5 – j130.6 | 5   | Ω    |                                                          |

| $f_{RF} = 433 \text{ MHz}$         |     | 11.9 –       |     | Ω    |                                                          |

|                                    |     | j260.1       |     |      |                                                          |

<sup>&</sup>lt;sup>1</sup> Measured as the maximum unmodulated power. <sup>2</sup> A combined single-ended PA and LNA match can reduce the maximum achievable output power by as much as 1 dB.

### **RECEIVER SPECIFICATIONS**

Table 4.

| Parameter                                               | Min Typ | Max | Unit | Test Conditions/Comments                                                                                                                                                                                               |

|---------------------------------------------------------|---------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INPUT SENSITIVITY, BIT ERROR RATE (BER) <sup>1</sup>    |         |     |      | BER = $10^{-3}$ , LNA and PA matched separately <sup>2</sup>                                                                                                                                                           |

| Radio Profile A                                         | -111    |     | dBm  | 9.6 kbps                                                                                                                                                                                                               |

| Radio Profile B                                         | -107.5  |     | dBm  | 38.4 kbps                                                                                                                                                                                                              |

| Radio Profile C                                         | -107.4  |     | dBm  | 50 kbps                                                                                                                                                                                                                |

| Radio Profile D                                         | -105    |     | dBm  | 100 kbps                                                                                                                                                                                                               |

| Radio Profile E                                         | -103    |     | dBm  | 200 kbps                                                                                                                                                                                                               |

| Radio Profile F                                         | -100.5  |     | dBm  | 300 kbps                                                                                                                                                                                                               |

| INPUT SENSITIVITY, PACKET ERROR RATE (PER) <sup>3</sup> |         |     |      | At PER = 1%, LNA and PA matched separately, <sup>2</sup> packet length = 128 bits                                                                                                                                      |

| Radio Profile A                                         | -110.6  |     | dBm  | 9.6 kbps                                                                                                                                                                                                               |

| Radio Profile B                                         | -106    |     | dBm  | 38.4 kbps                                                                                                                                                                                                              |

| Radio Profile C                                         | -104.1  |     | dBm  | 50 kbps                                                                                                                                                                                                                |

| Radio Profile D                                         | -102.6  |     | dBm  | 100 kbps                                                                                                                                                                                                               |

| Radio Profile E                                         | -99.1   |     | dBm  | 200 kbps                                                                                                                                                                                                               |

| Radio Profile F                                         | -97.9   |     | dBm  | 300 kbps                                                                                                                                                                                                               |

| LNA AND MIXER, INPUT IP3                                |         |     |      | Receiver local oscillator (LO) frequency (f <sub>LO</sub> ) = 914.8 MHz,                                                                                                                                               |

|                                                         |         |     |      | $f_{\text{SOURCE}1} = f_{\text{LO}} + 0.4 \text{ MHz}, f_{\text{SOURCE}2} = f_{\text{LO}} + 0.7 \text{ MHz}$                                                                                                           |

| LNA Gain                                                |         |     |      |                                                                                                                                                                                                                        |

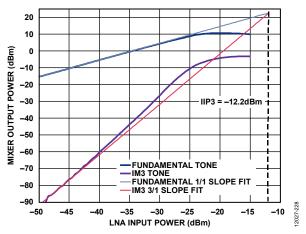

| Minimum                                                 | -11.5   |     | dBm  |                                                                                                                                                                                                                        |

| Maximum                                                 | -12.2   |     | dBm  |                                                                                                                                                                                                                        |

| LNA AND MIXER, INPUT IP2                                |         |     |      | f <sub>LO</sub> = 920.8 MHz, f <sub>SOURCE1</sub> = f <sub>LO</sub> + 1.1 MHz, f <sub>SOURCE2</sub> =                                                                                                                  |

|                                                         |         |     |      | f <sub>LO</sub> + 1.3 MHz                                                                                                                                                                                              |

| Gain                                                    |         |     |      |                                                                                                                                                                                                                        |

| Maximum LNA, Maximum Mixer                              | 18.5    |     | dBm  |                                                                                                                                                                                                                        |

| Minimum LNA, Minimum Mixer                              | 27      |     | dBm  |                                                                                                                                                                                                                        |

| LNA AND MIXER, 1 dB COMPRESSION<br>POINT                |         |     |      | RF = 915 MHz                                                                                                                                                                                                           |

| Gain                                                    |         |     |      |                                                                                                                                                                                                                        |

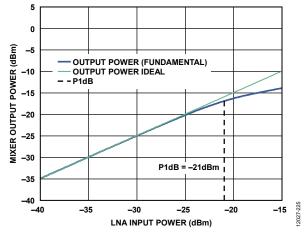

| Maximum LNA, Maximum Mixer                              | -21.9   |     | dBm  |                                                                                                                                                                                                                        |

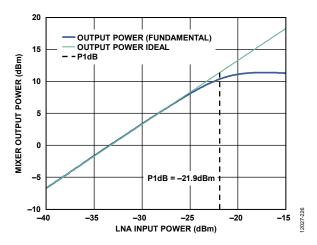

| Minimum LNA, Minimum Mixer                              | -21     |     | dBm  |                                                                                                                                                                                                                        |

| ADJACENT CHANNEL REJECTION                              |         |     |      |                                                                                                                                                                                                                        |

| CW Interferer                                           |         |     |      | Wanted signal 3 dB above the input sensitivity level (BER = $10^{-3}$ ), CW interferer power level increased until BER = $10^{-3}$ , image calibrated                                                                  |

| 200 kHz Channel Spacing                                 | 41      |     | dB   | Radio Profile B, RF = 433 MHz                                                                                                                                                                                          |

| 400 kHz Channel Spacing                                 | 40      |     | dB   | Radio Profile E                                                                                                                                                                                                        |

| 600 kHz Channel Spacing                                 | 41      |     | dB   | Radio Profile F                                                                                                                                                                                                        |

| Modulated Interferer                                    |         |     |      | Wanted signal 3 dB above the input sensitivity level (BER = $10^{-3}$ ), modulated interferer with the same modulation as the wanted signal; interferer power level increased until BER = $10^{-3}$ , image calibrated |

| 200 kHz Channel Spacing                                 | 37      |     | dB   | Radio Profile B, RF = 433 MHz                                                                                                                                                                                          |

| 400 kHz Channel Spacing                                 | 34      |     | dB   | Radio Profile E                                                                                                                                                                                                        |

| 600 kHz Channel Spacing                                 | 35      |     | dB   | Radio Profile F                                                                                                                                                                                                        |

| CO-CHANNEL REJECTION                                    | -4      |     | dB   | Desired signal 10 dB above the input sensitivity level (BER = $10^{-3}$ ), Radio Profile B, RF = 868 MHz                                                                                                               |

| Parameter                          | Min | Тур Мах      | Unit | Test Conditions/Comments                                                                                                                                                             |

|------------------------------------|-----|--------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

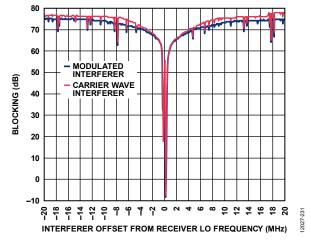

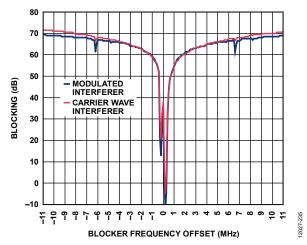

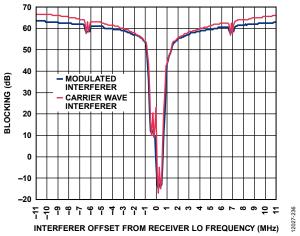

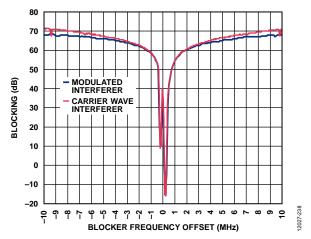

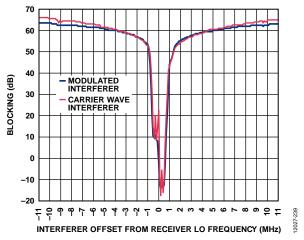

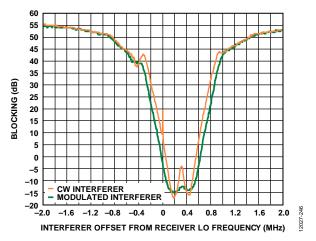

| BLOCKING                           |     |              |      | Desired signal 3 dB above the input sensitivity level (BER = $10^{-3}$ ), carrier wave interferer, power level increased until BER = $10^{-3}$ , Radio Profile B                     |

| RF = 433 MHz                       |     |              |      |                                                                                                                                                                                      |

| ±2 MHz                             |     | 68           | dB   |                                                                                                                                                                                      |

| ±10 MHz                            |     | 76           | dB   |                                                                                                                                                                                      |

| RF = 868 MHz                       |     |              |      |                                                                                                                                                                                      |

| ±2 MHz                             |     | 66           | dB   |                                                                                                                                                                                      |

| ±10 MHz                            |     | 74           | dB   |                                                                                                                                                                                      |

| RF = 915 MHz                       |     |              |      |                                                                                                                                                                                      |

| ±2 MHz                             |     | 66           | dB   |                                                                                                                                                                                      |

| ±10 MHz                            |     | 74           | dB   |                                                                                                                                                                                      |

| BLOCKING, ETSI EN 300 220          |     |              |      | Measurement procedure as per ETSI EN 300-220-1 V2.3.1; desired signal 3 dB above the ETSI EN 300-220 reference sensitivity level of –99 dBm, Radio Profile B, unmodulated interferer |

| ±2 MHz                             |     | -28          | dBm  |                                                                                                                                                                                      |

| ±10 MHz                            |     | -20.5        | dBm  |                                                                                                                                                                                      |

| WIDEBAND INTERFERENCE REJECTION    |     | 75           | dB   | RF = 868 MHz, swept from 10 MHz to 100 MHz either side of the RF                                                                                                                     |

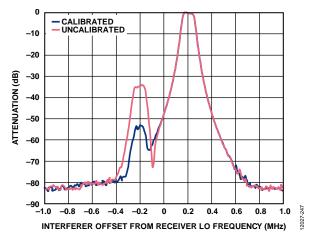

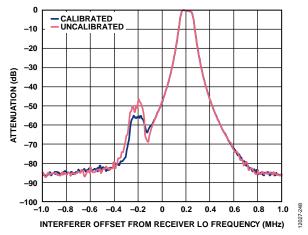

| IMAGE CHANNEL ATTENUATION          |     |              |      | Measured as image attenuation at the IF filter output, carrier wave interferer at 400 kHz below the channel frequency, 100 kHz IF filter bandwidth                                   |

| 868 MHz, 915 MHz                   |     | 36/45        | dB   | Uncalibrated/calibrated                                                                                                                                                              |

| 433 MHz                            |     | 40/54        | dB   | Uncalibrated/calibrated                                                                                                                                                              |

| AFC                                |     |              |      |                                                                                                                                                                                      |

| Accuracy                           |     | 1            | kHz  |                                                                                                                                                                                      |

| RSSI                               |     |              |      |                                                                                                                                                                                      |

| Range at Input                     |     | −97 to −26   | dBm  |                                                                                                                                                                                      |

| Linearity                          |     | ±2           | dB   |                                                                                                                                                                                      |

| Absolute Accuracy                  |     | ±3           | dB   |                                                                                                                                                                                      |

| MAXIMUM RF INPUT LEVEL             |     | 12           | dBm  |                                                                                                                                                                                      |

| LNA INPUT IMPEDANCE, DIFFERENTIAL  |     |              |      |                                                                                                                                                                                      |

| Receive Mode                       |     |              |      |                                                                                                                                                                                      |

| $f_{RF} = 915 \text{ MHz}$         |     | 75.9 – j32.3 | Ω    |                                                                                                                                                                                      |

| $f_{RF} = 868 \text{ MHz}$         |     | 78.0 – j32.4 | Ω    |                                                                                                                                                                                      |

| $f_{RF} = 433 \text{ MHz}$         | 1   | 95.5 – j23.9 | Ω    |                                                                                                                                                                                      |

| Transmit Mode                      | 1   | •            |      |                                                                                                                                                                                      |

| $f_{RF} = 915 \text{ MHz}$         | 1   | 7.6 + j9.2   | Ω    |                                                                                                                                                                                      |

| $f_{RF} = 868 \text{ MHz}$         | 1   | 7.7 + j8.6   | Ω    |                                                                                                                                                                                      |

| $f_{RF} = 433 \text{ MHz}$         | 1   | 7.9 + j4.6   | Ω    |                                                                                                                                                                                      |

| RX SPURIOUS EMISSIONS <sup>4</sup> | 1   | <u>-</u>     |      |                                                                                                                                                                                      |

| Maximum < 1 GHz                    | 1   | -66          | dBm  | At antenna input, unfiltered conductive                                                                                                                                              |

| Maximum > 1 GHz                    | 1   | -62          | dBm  | At antenna input, unfiltered conductive                                                                                                                                              |

Sensitivity measured with FSK modulation.

Sensitivity for combined Tx/Rx matching network case is typically 1 dB less than separate Tx/Rx matching networks.

Sensitivity measured with FSK modulation and AFC disabled.

Follow the matching and layout guidelines to achieve the relevant FCC/ETSI specifications.

## **TIMING AND DIGITAL SPECIFICATIONS**

Table 5.

| Parameter                           | Symbol                             | Min                 | Тур             | Max                       | Unit | Test Conditions/Comments                                                       |

|-------------------------------------|------------------------------------|---------------------|-----------------|---------------------------|------|--------------------------------------------------------------------------------|

| Rx AND Tx TIMING PARAMETERS         |                                    |                     |                 |                           |      |                                                                                |

| PHY_ON to PHY_RX (on                |                                    |                     | 300             |                           | μs   | Includes VCO calibration and synthesizer settling                              |

| CMD_PHY_RX)                         |                                    |                     |                 |                           |      |                                                                                |

| PHY_ON to PHY_TX (on<br>CMD_PHY_TX) |                                    |                     | 296             |                           | μs   | Includes VCO calibration and synthesizer settling, does not include PA ramp-up |

| LOGIC INPUTS                        |                                    |                     |                 |                           |      |                                                                                |

| Input Voltage                       |                                    |                     |                 |                           |      |                                                                                |

| High                                | V <sub>INH</sub>                   | $0.7 \times V_{DD}$ |                 |                           | ٧    |                                                                                |

| Low                                 | V <sub>INL</sub>                   |                     |                 | $0.2\times V_{\text{DD}}$ | ٧    |                                                                                |

| Input Current                       | I <sub>INH</sub> /I <sub>INL</sub> |                     |                 | ±1                        | μΑ   |                                                                                |

| Input Capacitance                   | C <sub>IN</sub>                    |                     |                 | 10                        | рF   |                                                                                |

| LOGIC OUTPUTS                       |                                    |                     |                 |                           |      |                                                                                |

| Output Voltage                      |                                    |                     |                 |                           |      |                                                                                |

| High                                | V <sub>OH</sub>                    | $V_{DD} - 0.4$      |                 |                           | ٧    | I <sub>OH</sub> = 500 μA                                                       |

| Low                                 | Vol                                |                     |                 | 0.4                       | ٧    | $I_{OL} = 500  \mu A$                                                          |

| GPx Rise/Fall                       |                                    |                     |                 | 5                         | ns   |                                                                                |

| GPx Load                            |                                    |                     |                 | 10                        | рF   |                                                                                |

| Maximum Output Current              |                                    |                     | 5               |                           | mΑ   |                                                                                |

| ATB OUTPUTS                         |                                    |                     |                 |                           |      | Used for external PA and LNA control                                           |

| ADCIN_ATB3 and ATB4                 |                                    |                     |                 |                           |      |                                                                                |

| Output High Voltage, Vон            |                                    |                     | 1.8             |                           | ٧    |                                                                                |

| Output Low Voltage, Vol             |                                    |                     | 0.1             |                           | ٧    |                                                                                |

| Maximum Output Current              |                                    |                     | 0.5             |                           | mA   |                                                                                |

| GP5_ATB1 and ATB2                   |                                    |                     |                 |                           |      |                                                                                |

| Output High Voltage, Vон            |                                    |                     | $V_{\text{DD}}$ |                           | ٧    |                                                                                |

| Output Low Voltage, Vol             |                                    |                     | 0.1             |                           | ٧    |                                                                                |

| Maximum Output Current              |                                    |                     | 5               |                           | mA   |                                                                                |

## **AUXILARY BLOCK SPECIFICATIONS**

Table 6.

| Parameter                        | Min                 | Тур      | Max                  | Unit     | Test Conditions/Comments                                                    |

|----------------------------------|---------------------|----------|----------------------|----------|-----------------------------------------------------------------------------|

| 32 kHz RC OSCILLATOR             |                     |          |                      |          |                                                                             |

| Frequency                        |                     | 32.768   |                      | kHz      | After calibration                                                           |

| Frequency Accuracy               |                     | 1.5      |                      | %        | After calibration at 25°C                                                   |

| Frequency Drift                  |                     |          |                      |          |                                                                             |

| Temperature Coefficient          |                     | 0.14     |                      | %/°C     |                                                                             |

| Voltage Coefficient              |                     | 4        |                      | %/V      |                                                                             |

| Calibration Time                 |                     | 1.25     |                      | ms       |                                                                             |

| WAKE-UP CONTROLLER (WUC)         |                     |          |                      |          |                                                                             |

| Hardware Timer                   |                     |          |                      |          |                                                                             |

| Wake-Up Period                   | $61 \times 10^{-6}$ |          | $1.31 \times 10^{5}$ | sec      |                                                                             |

| Firmware Timer                   |                     |          |                      |          |                                                                             |

| Wake-Up Period                   | 1                   |          | 2 <sup>16</sup>      | Hardware | Firmware counter counts of the number of                                    |

|                                  |                     |          |                      | periods  | hardware wake-up cycles, resolution of 16 bits                              |

| ADC                              |                     |          |                      |          |                                                                             |

| Resolution                       |                     | 8        |                      | Bits     |                                                                             |

| DNL                              |                     | ±1       |                      | LSB      | $V_{DD}$ from 2.2 V to 3.6 V, $T_A = 25^{\circ}$ C                          |

| INL                              |                     | ±1       |                      | LSB      | $V_{DD}$ from 2.2 V to 3.6 V, $T_A = 25^{\circ}$ C                          |

| Conversion Time                  |                     | 1        |                      | μs       |                                                                             |

| Input Capacitance                |                     | 12.4     |                      | pF       |                                                                             |

| BATTERY MONITOR                  |                     |          |                      |          |                                                                             |

| Absolute Accuracy                |                     | ±45      |                      | mV       |                                                                             |

| Alarm Voltage Set Point          | 1.7                 |          | 2.7                  | V        |                                                                             |

| Alarm Voltage Step Size          |                     | 62       |                      | mV       | 5-bit resolution                                                            |

| Start-Up Time                    |                     |          | 100                  | μs       |                                                                             |

| Current Consumption              |                     | 30       |                      | μΑ       | When enabled                                                                |

| TEMPERATURE SENSOR               |                     |          |                      |          |                                                                             |

| Range                            | -40                 |          | +85                  | °C       |                                                                             |

| Resolution                       |                     | 0.3      |                      | °C       | With averaging                                                              |

| Accuracy of Temperature Readback |                     | -4 to +7 |                      | °C       | Temperature range = $-40^{\circ}$ C to $+85^{\circ}$ C (calibrated at 25°C) |

|                                  |                     | ±4       |                      | °C       | Temperature range = $-36^{\circ}$ C to $+84^{\circ}$ C (calibrated at 25°C) |

|                                  |                     | ±3       |                      | °C       | Temperature range = -12°C to +79°C (calibrated at 25°C)                     |

## **GENERAL SPECIFICATIONS**

Table 7.

| Parameter                        | Min | Тур   | Max | Unit | Test Conditions/Comments                                                                                                                                                    |

|----------------------------------|-----|-------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEMPERATURE RANGE, TA            | -40 |       | +85 | °C   |                                                                                                                                                                             |

| VOLTAGE SUPPLY                   |     |       |     |      |                                                                                                                                                                             |

| $V_{DD}$                         | 2.2 |       | 3.6 | V    | Applied to VDDBAT1 and VDDBAT2                                                                                                                                              |

| TRANSMIT CURRENT CONSUMPTION     |     |       |     |      | In the PHY_TX state, PA matched to 50 $\Omega$ , separate PA and LNA match                                                                                                  |

| 433 MHz                          |     |       |     |      |                                                                                                                                                                             |

| –10 dBm                          |     | 8.7   |     | mA   |                                                                                                                                                                             |

| 0 dBm                            |     | 12.2  |     | mA   |                                                                                                                                                                             |

| 10 dBm                           |     | 23.3  |     | mA   |                                                                                                                                                                             |

| 13.5 dBm                         |     | 32.1  |     | mA   |                                                                                                                                                                             |

| 868 MHz/915 MHz                  |     |       |     |      |                                                                                                                                                                             |

| –10 dBm                          |     | 10.3  |     | mA   |                                                                                                                                                                             |

| 0 dBm                            |     | 13.3  |     | mA   |                                                                                                                                                                             |

| 10 dBm                           |     | 24.1  |     | mA   |                                                                                                                                                                             |

| 13.5 dBm                         |     | 32.1  |     | mA   |                                                                                                                                                                             |

| POWER MODES                      |     |       |     |      |                                                                                                                                                                             |

| PHY_SLEEP (Deep Sleep Mode 2)    |     | 0.18  |     | μΑ   | Sleep mode, memory not retained                                                                                                                                             |

| PHY_SLEEP (Deep Sleep Mode 1)    |     | 0.33  |     | μΑ   | Sleep mode, memory retained                                                                                                                                                 |

| PHY_SLEEP (RC Oscillator Active) |     | 0.75  |     | μΑ   | WUC active, RC oscillator running, memory retained                                                                                                                          |

| PHY_OFF                          |     | 1     |     | mA   | Device in PHY_OFF state, 26 MHz oscillator running, digital and synthesizer regulators active, all register values retained                                                 |

| PHY_ON                           |     | 1     |     | mA   | Device in PHY_ON state, 26 MHz oscillator running, digital, synthesizer, VCO, and RF regulators active, baseband filter calibration performed, all register values retained |

| PHY_RX                           |     | 12.8  |     | mA   | Device in PHY_RX state                                                                                                                                                      |

| SMART WAKE MODE                  |     |       |     |      | Average current consumption                                                                                                                                                 |

|                                  |     | 21.78 |     | μΑ   | Autonomous reception every 1 sec, with receive dwell time of 1.25 ms, using RC oscillator, Radio Profile B                                                                  |

|                                  |     | 11.75 |     | μΑ   | Autonomous reception every 1 sec, with receive dwell time of 0.5 ms, using RC oscillator, Radio Profile F                                                                   |

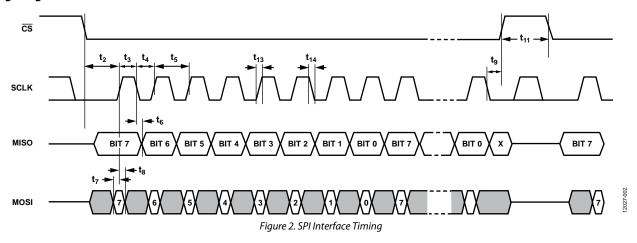

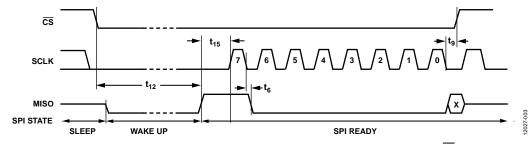

### **TIMING SPECIFICATIONS**

$V_{DD} = VDDBAT1 = VDDBAT2 = 2.2 \ V \ to \ 3.6 \ V, \\ V_{GND} = GND = 0 \ V, \\ T_A = T_{MIN} \ to \ T_{MAX}, \\ unless \ otherwise \ noted.$

**Table 8. SPI Interface Timing**

| Parameter             | Limit | Unit   | Test Conditions/Comments                                                                                                                    |

|-----------------------|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>2</sub>        | 85    | ns min | CS low to SCLK setup time                                                                                                                   |

| t <sub>3</sub>        | 85    | ns min | SCLK high time                                                                                                                              |

| t <sub>4</sub>        | 85    | ns min | SCLK low time                                                                                                                               |

| <b>t</b> <sub>5</sub> | 170   | ns min | SCLK period                                                                                                                                 |

| <b>t</b> <sub>6</sub> | 10    | ns max | SCLK falling edge to MISO delay                                                                                                             |

| <b>t</b> <sub>7</sub> | 5     | ns min | MOSI to SCLK rising edge setup time                                                                                                         |

| t <sub>8</sub>        | 5     | ns min | MOSI to SCLK rising edge hold time                                                                                                          |

| <b>t</b> 9            | 85    | ns min | SCLK falling edge to CS hold time                                                                                                           |

| t <sub>11</sub>       | 270   | ns min | CS high time                                                                                                                                |

| t <sub>12</sub>       | 310   | μs typ | $\overline{\text{CS}}$ low to MISO high wake-up time, 26 MHz crystal with 7 pF load capacitance, $T_A = 25^{\circ}\text{C}$                 |

| t <sub>13</sub>       | 20    | ns max | SCLK rise time                                                                                                                              |

| t <sub>14</sub>       | 20    | ns max | SCLK fall time                                                                                                                              |

| t <sub>15</sub>       | 25    | μs max | Initialization time; do not issue a command during this time; alternatively, poll the status word and wait for the CMD_READY bit to go high |

### **Timing Diagrams**

Figure 3. PHY\_SLEEP to SPI Ready State Timing (SPI Ready  $t_{12}$  After the Falling Edge of  $\overline{CS}$ )

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 9.

| Parameter                             | Rating            |

|---------------------------------------|-------------------|

| VDDBAT1, VDDBAT2 to GND               | −0.3 V to +3.96 V |

| Operating Temperature Range           |                   |

| Industrial                            | -40°C to +85°C    |

| Storage Temperature Range             | −65°C to +125°C   |

| Maximum Junction Temperature          | 150°C             |

| LFCSP $\theta_{JA}$ Thermal Impedance | 26°C/W            |

| Reflow Soldering                      |                   |

| Peak Temperature                      | 260°C             |

| Time at Peak Temperature              | 40 sec            |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Connect the exposed pad of the LFCSP to ground.

This device is a high performance, RF integrated circuit with an ESD rating of <2 kV; it is ESD sensitive. Take proper precautions for handling and assembly.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

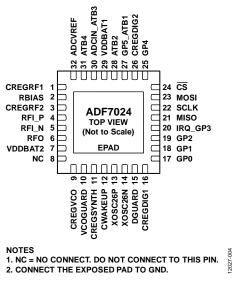

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 10. Pin Function Descriptions**

| Pin No. | Mnemonic  | Description                                                                                                                                                                        |  |  |  |

|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | CREGRF1   | Regulator Voltage for RF. For regulator stability and noise rejection, place a 220 nF capacitor between this pin and ground.                                                       |  |  |  |

| 2       | RBIAS     | External Bias Resistor. Place a 36 k $\Omega$ resistor with 2% tolerance between this pin and ground.                                                                              |  |  |  |

| 3       | CREGRF2   | Regulator Voltage for RF. For regulator stability and noise rejection, place a 220 nF capacitor between this pin and ground.                                                       |  |  |  |

| 4       | RFI_P     | LNA Positive Input in Receive Mode.                                                                                                                                                |  |  |  |

| 5       | RFI_N     | LNA Negative Input in Receive Mode.                                                                                                                                                |  |  |  |

| 6       | RFO       | PA Output.                                                                                                                                                                         |  |  |  |

| 7       | VDDBAT2   | Power Supply Pin 2. Place decoupling capacitors to the ground plane as close as possible to this pin.                                                                              |  |  |  |

| 8       | NC        | No Connect. Do not connect to this pin.                                                                                                                                            |  |  |  |

| 9       | CREGVCO   | Regulator Voltage for the VCO. For regulator stability and noise rejection, place a 220 nF capacitor between this pin and ground.                                                  |  |  |  |

| 10      | VCOGUARD  | Guard/Screen for VCO. Connect this pin to Pin 9.                                                                                                                                   |  |  |  |

| 11      | CREGSYNTH | Regulator Voltage for the Synthesizer. For regulator stability and noise rejection, place a 220 nF capacitor between this pin and ground.                                          |  |  |  |

| 12      | CWAKEUP   | External Capacitor for Wake-Up Control. Place a 150 nF capacitor between this pin and ground.                                                                                      |  |  |  |

| 13      | XOSC26P   | Crystal Oscillator, Positive. Connect the 26 MHz reference crystal between this pin and XOSC26N. If an external reference is connected to XOSC26N, leave this pin open circuited.  |  |  |  |

| 14      | XOSC26N   | Crystal Oscillator, Negative. Connect the 26 MHz reference crystal between this pin and XOSC26P. Alternatively, an external 26 MHz reference signal can be ac-coupled to this pin. |  |  |  |

| 15      | DGUARD    | Internal Guard/Screen for the Digital Circuitry. Connect this pin to Pin 16, CREGDIG1.                                                                                             |  |  |  |

| 16      | CREGDIG1  | Regulator Voltage for Digital Section of the Chip. For regulator stability and noise rejection, place a 220 nF capacitor between this pin and ground.                              |  |  |  |

| 17      | GP0       | Digital GPIO Pin 0.                                                                                                                                                                |  |  |  |

| 18      | GP1       | Digital GPIO Pin 1.                                                                                                                                                                |  |  |  |

| 19      | GP2       | Digital GPIO Pin 2.                                                                                                                                                                |  |  |  |

| 20      | IRQ_GP3   | Interrupt Request/Digital GPIO Test Pin 3.                                                                                                                                         |  |  |  |

| 21      | MISO      | Serial Port Master Input/Slave Output.                                                                                                                                             |  |  |  |

| 22      | SCLK      | Serial Port Clock.                                                                                                                                                                 |  |  |  |

| 23      | MOSI      | Serial Port Master Output/Slave Input.                                                                                                                                             |  |  |  |

| 24      | CS        | Chip Select (Active Low). A pull-up resistor of 100 k $\Omega$ to $V_{DD}$ is recommended to prevent the host processor from inadvertently waking the ADF7024 from sleep.          |  |  |  |

| 25      | GP4       | Digital GPIO Test Pin 4.                                                                                                                                                           |  |  |  |

| Pin No. | Mnemonic   | Description                                                                                                                                           |

|---------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26      | CREGDIG2   | Regulator Voltage for Digital Section of the Chip. For regulator stability and noise rejection, place a 220 nF capacitor between this pin and ground. |

| 27      | GP5_ATB1   | Digital GPIO Test Pin 5/Analog Test Pin 1.                                                                                                            |

| 28      | ATB2       | Analog Test Pin 2.                                                                                                                                    |

| 29      | VDDBAT1    | Digital Power Supply Pin One. Place decoupling capacitors to the ground plane as close as possible to this pin.                                       |

| 30      | ADCIN_ATB3 | Analog-to-Digital Converter Input/Analog Test Pin 3.                                                                                                  |

| 31      | ATB4       | Analog Test Pin 4.                                                                                                                                    |

| 32      | ADCVREF    | ADC Reference Output. Place a 220 nF capacitor between this pin and ground for adequate noise rejection.                                              |

|         | EPAD       | Exposed Package Pad. Connect the exposed pad to GND.                                                                                                  |

# TYPICAL PERFORMANCE CHARACTERISTICS

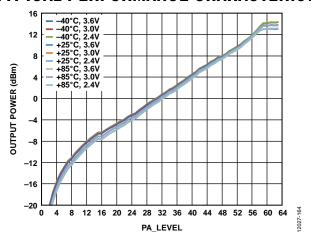

Figure 5. Output Power vs. PA\_LEVEL Setting, Temperature, and  $V_{DD}$  at 433 MHz

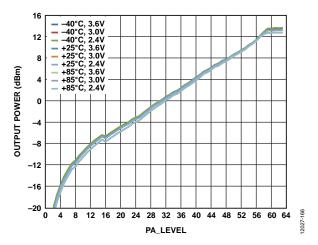

Figure 6. Output Power vs. PA\_LEVEL Setting, Temperature, and  $V_{DD}$  at 868 MHz

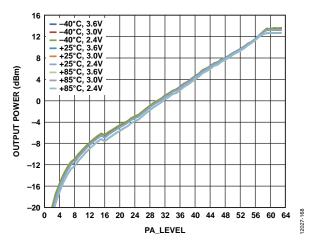

Figure 7. Output Power vs. PA\_LEVEL Setting, Temperature, and  $V_{DD}$  at 915 MHz

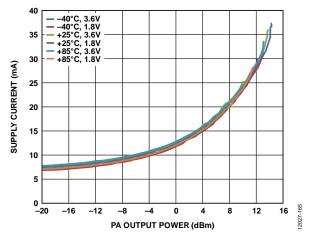

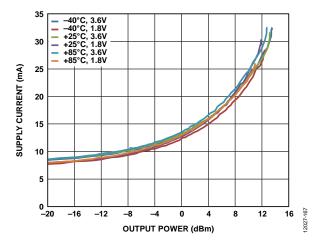

Figure 8. Supply Current vs. PA Output Power, Temperature, and  $V_{DD}$  at 433 MHz (Minimum Recommended  $V_{DD}$  = 2.2 V, 1.8 V Operation Shown for Robustness)

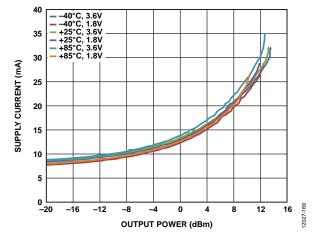

Figure 9. Supply Current vs. Output Power, Temperature, and  $V_{DD}$  at 868 MHz (Minimum Recommended  $V_{DD} = 2.2 V$ , 1.8 V Operation Shown for Robustness)

Figure 10. Supply Current vs. Output Power, Temperature, and  $V_{DD}$  at 915 MHz (Minimum Recommended  $V_{DD}$  = 2.2 V, 1.8 V Operation Shown for Robustness)

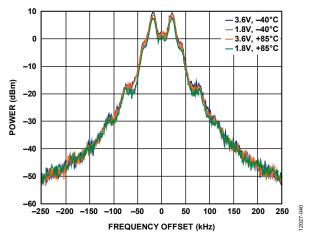

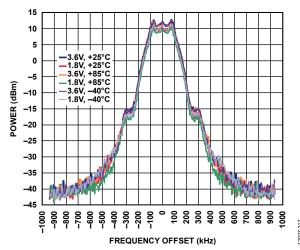

Figure 11. Transmit Spectrum at 868 MHz, FSK, Radio Profile B, (Minimum Recommended  $V_{DD}$  = 2.2 V, 1.8 V Operation Shown for Robustness)

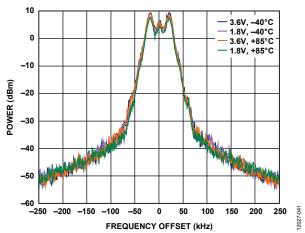

Figure 12. Transmit Spectrum at 868 MHz, GFSK, Radio Profile B, (Minimum Recommended  $V_{DD} = 2.2 V$ , 1.8 V Operation Shown for Robustness)

Figure 13. Transmit Spectrum at 928 MHz, GFSK, Radio Profile F, (Minimum Recommended  $V_{DD}$  = 2.2 V, 1.8 V Operation Shown for Robustness)

Figure 14. LNA/Mixer 1 dB Compression Point,  $V_{DD}$  = 3.0 V, Temperature = 25°C, RF = 915 MHz, LNA Gain = Low, Mixer Gain = Low

Figure 15. LNA/Mixer 1 dB Compression Point,  $V_{DD} = 3.0$  V, Temperature =  $25^{\circ}$ C, RF = 915 MHz, LNA Gain = High, Mixer Gain = High

Figure 16. LNA/Mixer IIP3, V<sub>DD</sub> = 3.0 V, Temperature = 25°C, RF = 915 MHz, LNA Gain = Low, Mixer Gain = Low, Source 1 Frequency = 915 MHz + 0.4 MHz, Source 2 Frequency = 915 MHz + 0.7 MHz

Figure 17. LNA/Mixer IIP3, V<sub>DD</sub> = 3.0 V, Temperature = 25°C, RF = 915 MHz, LNA Gain = High, Mixer Gain = High, Source 1 Frequency = 915 MHz + 0.4 MHz, Source 2 Frequency = 915 MHz + 0.7 MHz

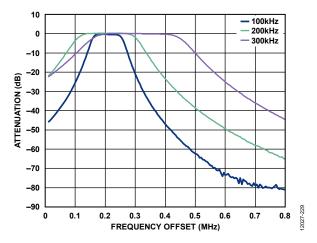

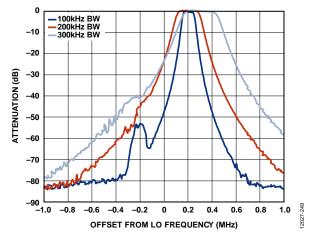

Figure 18. IF Filter Profile vs. IF Bandwidth,  $V_{DD} = 3.0 \text{ V}$ , Temperature = 25°C

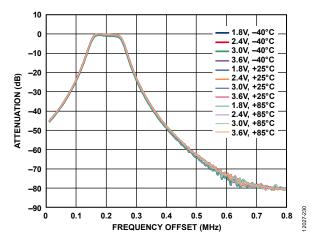

Figure 19. IF Filter Profile vs.  $V_{DD}$  and Temperature, 100 kHz IF Filter Bandwidth (Minimum Recommended  $V_{DD} = 2.2 V$ , 1.8 V Operation Shown for Robustness)

Figure 20. Receiver Wideband Blocking at 433 MHz, Radio Profile B

Figure 21. Receiver Wideband Blocking at 868 MHz, Radio Profile D

Figure 22. Receiver Wideband Blocking at 868 MHz, Radio Profile F

Figure 23. Receiver Wideband Blocking at 915 MHz, Radio Profile D

Figure 24. Receiver Wideband Blocking at 915 MHz, Radio Profile F

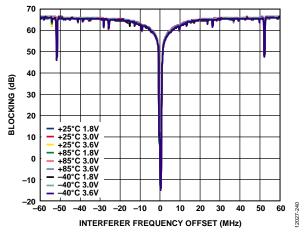

Figure 25. Receiver Wideband Blocking vs. V<sub>DD</sub> and Temperature, 915 MHz, Radio Profile F

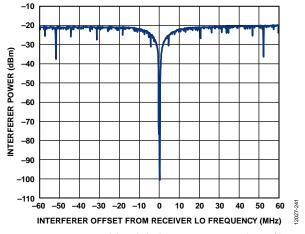

Figure 26. Receiver Wideband Blocking at 868 MHz, Radio Profile B, Measured as per ETSI EN 300 220

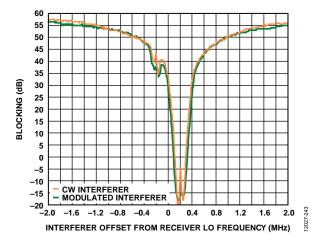

Figure 27. Receiver Close-In Blocking at 915 MHz, Radio Profile D, Image Calibrated

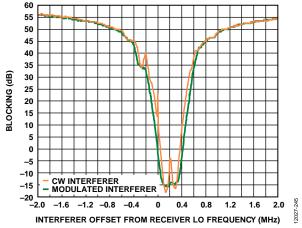

Figure 28. Receiver Close-In Blocking at 915 MHz, Radio Profile E, Image Calibrated

Figure 29. Receiver Close-In Blocking at 915 MHz, Radio Profile F, Image Calibrated

Figure 30. Image Attenuation with Calibrated and Uncalibrated Images, 915 MHz, IF Filter Bandwidth = 100 kHz,  $V_{DD}$  = 3.0 V, Temperature = 25°C

Figure 31. Image Attenuation with Calibrated and Uncalibrated Images, 433 MHz, IF Filter Bandwidth = 100 kHz,  $V_{DD}$  = 3.0 V, Temperature = 25°C

Figure 32. IF Filter Profile with Calibrated Image vs. IF Filter Bandwidth,  $921~\text{MHz}, V_{DD} = 3.0~\text{V}, \text{Temperature} = 25^{\circ}\text{C}$

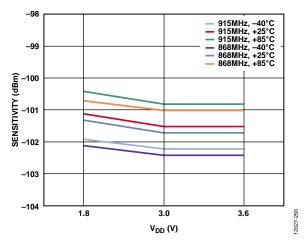

Figure 33. Receiver Sensitivity (Bit Error Rate at  $10^{-3}$ ) vs.  $V_{DD}$ , Temperature, and RF Frequency, Radio Profile F, FSK, (Minimum Recommended  $V_{DD}$  = 2.2 V, 1.8 V Operation Shown for Robustness)

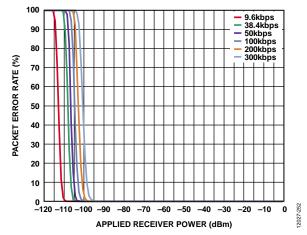

Figure 34. Packet Error Rate vs. RF Input Power and Radio Profile (Data Rate), FSK, 928 MHz, Preamble Length = 64 Bits,  $V_{DD}$  = 3.0 V, Temperature = 25°C

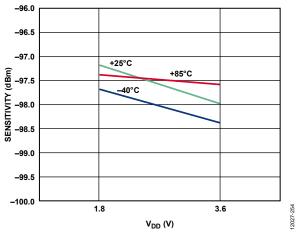

Figure 35. Receiver Sensitivity (Packet Error Rate at 1%) vs.  $V_{DD}$ , Temperature, and RF, Radio Profile F, FSK, (Minimum Recommended  $V_{DD} = 2.2 \text{ V}$ , 1.8 V Operation Shown for Robustness)

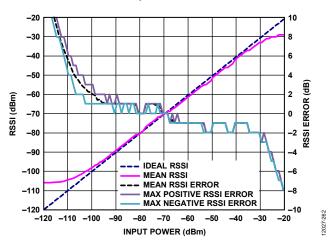

Figure 36. RSSI (via CMD\_GET\_RSSI) vs. RF Input Power, 868 MHz, GFSK, Radio Profile B, IF Bandwidth = 100 kHz, 100 RSSI Measurements at Each Power Level