# Desktop 3rd Generation Intel<sup>®</sup> Core<sup>™</sup> Processor Family, Desktop Intel<sup>®</sup> Pentium<sup>®</sup> Processor Family, and Desktop Intel<sup>®</sup> Celeron<sup>®</sup> Processor Family

Datasheet - Volume 1 of 2

November 2013

Document Number: 326764-008

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT. COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or go to: http://www.intel.com/design/literature.htm.

No computer system can provide absolute security under all conditions. Intel® Trusted Execution Technology (Intel® TXT) requires a computer system with Intel® Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). The MLE could consist of a virtual machine monitor, an OS or an application. In addition, Intel TXT requires the system to contain a TPM v1.2, as defined by the Trusted Computing Group and specific software for some uses. For more information, see http://www.intel.com/technology/security/

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, virtual machine monitor (VMM) and, for some uses, certain computer system software enabled for it. Functionality, performance or other benefits will vary depending on hardware and software configurations and may require a BIOS update. Software applications may not be compatible with all operating systems. Please check with your application vendor.

Intel® Active Management Technology requires the computer system to have an Intel(R) AMT-enabled chipset, network hardware and software, as well as connection with a power source and a corporate network connection. Setup requires configuration by the purchaser and may require scripting with the management console or further integration into existing security frameworks to enable certain functionality. It may also require modifications of implementation of new business processes. With regard to notebooks, Intel AMT may not be available or certain capabilities may be limited over a host OS-based VPN or when connecting wirelessly, on battery power, sleeping, hibernating or powered off. For more information, see <a href="http://www.intel.com/technology/platform-technology/intel-amt/">http://www.intel.com/technology/platform-technology/intel-amt/</a>

Hyper-Threading Technology requires a computer system with a processor supporting HT Technology and an HT Technology-enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. For more information including details on which processors support HT Technology, see <a href="http://www.intel.com/info/hyperthreading">http://www.intel.com/info/hyperthreading</a>.

"Intel® Turbo Boost Technology requires a PC with a processor with Intel Turbo Boost Technology capability. Intel Turbo Boost Technology performance varies depending on hardware, software and overall system configuration. Check with your PC manufacturer on whether your system delivers Intel Turbo Boost Technology.For more information, see <a href="http://www.intel.com/technology/turboboost">http://www.intel.com/technology/turboboost</a>."

Enhanced Intel SpeedStep® Technology See the <u>Processor Spec Finder</u> or contact your Intel representative for more information. Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="https://www.intel.com/products/processor\_number">www.intel.com/products/processor\_number</a> for details.

64-bit computing on Intel architecture requires a computer system with a processor, chipset, BIOS, operating system, device drivers and applications enabled for Intel® 64 architecture. Performance will vary depending on your hardware and software configurations. Consult with your system vendor for more information.

Intel, Pentium, Celeron, Intel Core, and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2013, Intel Corporation. All rights reserved.

# **Contents**

| 1 | Intro | duction  | 1                                                                                         | 9  |

|---|-------|----------|-------------------------------------------------------------------------------------------|----|

|   | 1.1   | Process  | sor Feature Details                                                                       | 11 |

|   |       | 1.1.1    | Supported Technologies                                                                    |    |

|   | 1.2   | Interfa  | ces                                                                                       |    |

|   |       | 1.2.1    | System Memory Support                                                                     | 11 |

|   |       | 1.2.2    | PCI Express*                                                                              | 12 |

|   |       | 1.2.3    | Direct Media Interface (DMI)                                                              | 14 |

|   |       | 1.2.4    | Platform Environment Control Interface (PECI)                                             | 14 |

|   |       | 1.2.5    | Processor Graphics                                                                        | 14 |

|   |       | 1.2.6    | Intel <sup>®</sup> Flexible Display Interface (Intel <sup>®</sup> FDI)                    | 15 |

|   | 1.3   | Power    | Management Support                                                                        |    |

|   |       | 1.3.1    | Processor Core                                                                            | 15 |

|   |       | 1.3.2    | System                                                                                    | 15 |

|   |       | 1.3.3    | Memory Controller                                                                         |    |

|   |       | 1.3.4    | PCI Express*                                                                              |    |

|   |       | 1.3.5    | Direct Media Interface (DMI)                                                              |    |

|   |       | 1.3.6    | Processor Graphics Controller (GT)                                                        |    |

|   |       | 1.3.7    | Thermal Management Support                                                                |    |

|   | 1.4   | Process  | sor SKU Definitions                                                                       |    |

|   | 1.5   |          | e                                                                                         |    |

|   | 1.6   |          | sor Compatibility                                                                         |    |

|   | 1.7   |          | ology                                                                                     |    |

|   | 1.8   |          | d Documents                                                                               |    |

| 2 | Intor | faces    |                                                                                           | 23 |

| _ | 2.1   |          | n Memory Interface                                                                        |    |

|   | ۷.۱   | 2.1.1    | System Memory Technology Supported                                                        |    |

|   |       | 2.1.1    | System Memory Timing Support                                                              |    |

|   |       | 2.1.2    | System Memory Organization Modes                                                          |    |

|   |       | 2.1.3    | 2.1.3.1 Single-Channel Mode                                                               |    |

|   |       |          | 2.1.3.2 Dual-Channel Mode – Intel <sup>®</sup> Flex Memory Technology Mode                | 25 |

|   |       | 2.1.4    | Rules for Populating Memory Slots                                                         |    |

|   |       | 2.1.5    | Technology Enhancements of Intel <sup>®</sup> Fast Memory Access (Intel <sup>®</sup> FMA) | 27 |

|   |       | 2.1.0    | 2.1.5.1 Just-in-Time Command Scheduling                                                   |    |

|   |       |          | 2.1.5.2 Command Overlap                                                                   |    |

|   |       |          | 2.1.5.3 Out-of-Order Scheduling                                                           |    |

|   |       | 2.1.6    | Data Scrambling                                                                           |    |

|   |       | 2.1.7    | DDR3 Reference Voltage Generation                                                         |    |

|   | 2.2   | PCI Ex   | oress* Interface                                                                          |    |

|   |       | 2.2.1    | PCI Express* Architecture                                                                 |    |

|   |       |          | 2.2.1.1 Transaction Layer                                                                 | 29 |

|   |       |          | 2.2.1.2 Data Link Layer                                                                   | 29 |

|   |       |          | 2.2.1.3 Physical Layer                                                                    |    |

|   |       | 2.2.2    | PCI Express* Configuration Mechanism                                                      | 30 |

|   |       | 2.2.3    | PCI Express* Port                                                                         |    |

|   |       |          | 2.2.3.1 PCI Express* Lanes Connection                                                     | 31 |

|   | 2.3   | Direct I | Media Interface (DMI)                                                                     | 32 |

|   |       | 2.3.1    | DMI Error Flow                                                                            |    |

|   |       | 2.3.2    | Processor / PCH Compatibility Assumptions                                                 |    |

|   |       | 2.3.3    | DMI Link Down                                                                             |    |

|   | 2.4   | Process  | sor Graphics Controller (GT)                                                              | 33 |

|   |      | 2.4.1              | 3D and Video Engines for Graphics Processing                                                                                             | 33  |

|---|------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   |      |                    | 2.4.1.1 3D Engine Execution Units                                                                                                        | 33  |

|   |      |                    | 2.4.1.2 3D Pipeline                                                                                                                      | 34  |

|   |      |                    | 2.4.1.3 Video Engine                                                                                                                     | 34  |

|   |      |                    | 2.4.1.4 2D Engine                                                                                                                        |     |

|   |      | 2.4.2              | Processor Graphics Display                                                                                                               |     |

|   |      |                    | 2.4.2.1 Display Planes                                                                                                                   | 36  |

|   |      |                    | 2.4.2.2 Display Pipes                                                                                                                    | 37  |

|   |      |                    | 2.4.2.3 Display Ports                                                                                                                    | 37  |

|   |      | 2.4.3              | Intel <sup>®</sup> Flexible Display Interface (Intel <sup>®</sup> FDI)                                                                   | 37  |

|   |      | 2.4.4              | Multi Graphics Controllers Multi-Monitor Support                                                                                         | 37  |

|   | 2.5  | Platfor            | rm Environment Control Interface (PECI)                                                                                                  | 38  |

|   | 2.6  |                    | ace Clocking                                                                                                                             | 38  |

|   |      | 2.6.1              | Internal Clocking Requirements                                                                                                           | 38  |

| 3 | Tech | nologie            | es                                                                                                                                       | 30  |

| 3 | 3.1  | Intal®             | Virtualization Technology (Intel <sup>®</sup> VT)                                                                                        | 20  |

|   | 3.1  | 3.1.1              | Intel® Virtualization Technology (Intel® VT)                                                                                             | 39  |

|   |      | 3.1.1              | Intel <sup>®</sup> Virtualization Technology (Intel <sup>®</sup> VT) for IA-32 Intel <sup>®</sup> 64 and Intel <sup>®</sup> Architecture |     |

|   |      |                    | IA-32, Intel® 64 and Intel® Architecture<br>(Intel® VT-x) Objectives                                                                     | 30  |

|   |      | 3.1.2              | Intel <sup>®</sup> Virtualization Technology (Intel <sup>®</sup> VT) for                                                                 |     |

|   |      | J. 1.Z             | $1\Delta_{-}32$ Intel <sup>®</sup> 64 and Intel <sup>®</sup> Architecture                                                                |     |

|   |      |                    | (Intel® VT-x) Features                                                                                                                   | 40  |

|   |      | 3.1.3              | (Intel® VT-x) Features                                                                                                                   |     |

|   |      | 00                 | I/O (Intel® VT-d) Objectives                                                                                                             | 40  |

|   |      | 3.1.4              | Intel® Virtualization Technology (Intel® VT) for Directed                                                                                |     |

|   |      |                    | I/O (Intel® VT-d) Features                                                                                                               | 41  |

|   |      | 3.1.5              | Intel® Virtualization Technology (Intel® VT) for Directed                                                                                |     |

|   |      |                    | I/O (Intel <sup>®</sup> VT-d) Features Not Supported                                                                                     | 41  |

|   | 3.2  | Intel®             | I/O (Intel® VT-d) Features Not Supported                                                                                                 | 42  |

|   | 3.3  | Intel <sup>®</sup> | Hyper-Threading Technology (Intel® HT Technology)                                                                                        | 42  |

|   | 3.4  | Intel <sup>®</sup> | Turbo Boost Technology                                                                                                                   | 43  |

|   |      | 3.4.1              | Intel® Turbo Boost Technology Frequency                                                                                                  | 43  |

|   |      | 3.4.2              | Intel® Turbo Boost Technology Graphics Frequency                                                                                         | 43  |

|   | 3.5  | Intel®             | Advanced Vector Extensions (Intel® AVX)                                                                                                  | 44  |

|   | 3.6  | Securi             | ty and Cryptography Technologies                                                                                                         | 44  |

|   |      | 3.6.1              | Intel® Advanced Encryption Standard New Instructions (Intel® AES-NI)                                                                     | 44  |

|   |      | 3.6.2              | PCLMULQDQ Instruction                                                                                                                    | 44  |

|   |      | 3.6.3              |                                                                                                                                          |     |

|   | 3.7  | Intel®             | 64 Architecture x2APIC                                                                                                                   |     |

|   | 3.8  | Superv             | visor Mode Execution Protection (SMEP)                                                                                                   | 46  |

|   | 3.9  | Power              | Aware Interrupt Routing (PAIR)                                                                                                           | 46  |

|   |      |                    |                                                                                                                                          |     |

| 4 |      |                    | agement                                                                                                                                  | 4 / |

|   | 4.1  | Advan              | ced Configuration and Power Interface                                                                                                    |     |

|   |      |                    | States Supported                                                                                                                         |     |

|   |      | 4.1.1              | System States                                                                                                                            |     |

|   |      | 4.1.2              | Processor Core / Package Idle States                                                                                                     |     |

|   |      | 4.1.3              | Integrated Memory Controller States                                                                                                      |     |

|   |      | 4.1.4              | PCI Express* Link States                                                                                                                 |     |

|   |      | 4.1.5              | Direct Media Interface (DMI) States                                                                                                      |     |

|   |      | 4.1.6              | Processor Graphics Controller States                                                                                                     |     |

|   |      | 4.1.7              | Interface State Combinations                                                                                                             |     |

|   | 4.2  |                    | ssor Core Power Management                                                                                                               |     |

|   |      | 4.2.1              | Enhanced Intel <sup>®</sup> SpeedStep <sup>®</sup> Technology                                                                            |     |

|   |      | 4.2.2              | Low-Power Idle States                                                                                                                    |     |

|   |      | 423                | Requesting Low-Power Idle States                                                                                                         | 52  |

|   |       | 4.2.4   | Core C-s             | itates                                                  |            |

|---|-------|---------|----------------------|---------------------------------------------------------|------------|

|   |       |         | 4.2.4.1              | Core C0 State                                           | 52         |

|   |       |         | 4.2.4.2              | Core C1 / C1E State                                     |            |

|   |       |         | 4.2.4.3              | Core C3 State                                           | 53         |

|   |       |         | 4.2.4.4              | Core C6 State                                           | 53         |

|   |       |         | 4.2.4.5              | C-State Auto-Demotion                                   |            |

|   |       | 4.2.5   |                      | C-States                                                |            |

|   |       |         | 4.2.5.1              | Package C0                                              | 55         |

|   |       |         | 4.2.5.2              | Package C1/C1E                                          |            |

|   |       |         | 4.2.5.3              | Package C3 State                                        | 56         |

|   |       |         | 4.2.5.4              | Package C6 State                                        |            |

|   | 4.3   | •       |                      | ory Controller (IMC) Power Management                   |            |

|   |       | 4.3.1   |                      | g Unused System Memory Outputs                          |            |

|   |       | 4.3.2   |                      | ower Management and Initialization                      |            |

|   |       |         |                      | Initialization Role of CKE                              |            |

|   |       |         |                      | Conditional Self-Refresh                                |            |

|   |       |         | 4.3.2.3              | Dynamic Power Down Operation                            | 59         |

|   |       |         | 4.3.2.4              | DRAM I/O Power Management                               | 59         |

|   |       | 4.3.3   |                      | ctrical Power Gating (EPG)                              |            |

|   | 4.4   |         |                      | wer Management                                          |            |

|   | 4.5   |         |                      | ngement                                                 |            |

|   | 4.6   | Graphi  |                      | Management                                              | 60         |

|   |       | 4.6.1   |                      | apid Memory Power Management (Intel <sup>®</sup> RMPM)  |            |

|   |       |         | (also_kno            | own as CxSR)                                            | 60         |

|   |       | 4.6.2   | Intel® G             | raphics Performance Modulation Technology (Intel® GPMT) | 60         |

|   |       | 4.6.3   | Graphics             | Render C-State                                          | 60         |

|   |       | 4.6.4   | Intel <sup>®</sup> S | mart 2D Display Technology (Intel <sup>®</sup> S2DDT)   | 61         |

|   |       | 4.6.5   |                      | raphics Dynamic Frequency                               |            |

|   | 4.7   | Graphi  |                      | al Power Management                                     |            |

| 5 | Thor  |         |                      | ıt                                                      |            |

|   |       |         | •                    |                                                         |            |

| 6 | Signa |         |                      |                                                         |            |

|   | 6.1   | Systen  | n Memory             | Interface Signals                                       | 66         |

|   | 6.2   | Memor   | y Referen            | ce and Compensation Signals                             | 67         |

|   | 6.3   | Reset a | and Misce            | llaneous Signals                                        | 68         |

|   | 6.4   | PCI Ex  | press*-ba            | sed Interface Signals                                   | 69         |

|   | 6.5   | Intel®  | Flexible D           | visplay (Intel <sup>®</sup> FDI) Interface Signals      | 69         |

|   | 6.6   |         |                      | erface (DMI) Signals                                    |            |

|   | 6.7   |         |                      | (PLL) Signals                                           |            |

|   | 6.8   |         |                      | ts (TAP) Signals                                        |            |

|   | 6.9   |         |                      | al Protection Signals                                   |            |

|   | 6.10  |         |                      | ng Signals                                              |            |

|   | 6.11  |         |                      | Signals                                                 |            |

|   | 6.12  |         |                      | Signals                                                 |            |

|   | 6.13  |         |                      | -Critical to Function (NCTF) Signals                    |            |

|   | 6.14  |         |                      | al Pull-Up / Pull-Down Resistors                        |            |

|   |       |         |                      | ·                                                       |            |

| 7 | Elect | •       |                      | ons                                                     |            |

|   | 7.1   |         |                      | nd Lands                                                |            |

|   | 7.2   | Decou   |                      | elines                                                  |            |

|   |       | 7.2.1   | Voltage              | Rail Decoupling                                         | 75         |

|   | 7.3   | Proces  | sor Clocki           | ng (BCLK[0], BCLK#[0])                                  | 7 <i>6</i> |

|   |       | 7.3.1   | Phase Lo             | ock Loop (PLL) Power Supply                             | 7 <i>6</i> |

|   | 7.4   | VCC V   |                      | ntification (VID)                                       |            |

|   | 7.5   |         |                      | SA) V <sub>CC</sub> VID                                 |            |

|   | 7.6   |         |                      | sed Signals                                             |            |

|   |       |         |                      |                                                         |            |

| 7.8 Test Access Port (TAP) Connection 7.9 Storage Conditions Specifications. 7.10 DC Specifications. 7.10 DC Specifications. 7.11 Platform Environmental Control Interface (PECI) DC Specifications. 7.11.1 PECI Bus Architecture. 7.11.2 DC Characteristics. 7.11.3 Input Device Hysteresis.  8 Processor Land and Signal Information. 8.1 Processor Land Assignments  9 DDR Data Swizzling.  Figures  1-1 Desktop Processor Platform. 1-2 Desktop Processor Compatibility Diagram 2-1 Intel® Flex Memory Technology Operation 2-2 PCI Express* Layering Diagram. 2-3 Packet Flow Through the Layers. 2-4 PCI Express* Related Register Structures in the Processor 2-5 PCI Express* Related Register Structures in the Processor Compatibility Diagram 2-7 Processor Graphics Controller Unit Block Diagram. 2-8 Processor Graphics Controller Unit Block Diagram. 2-9 Processor Graphics Controller Unit Block Diagram. 2-1 Processor Display Block Diagram. 2-1 Processor Power States. 3 Thread and Core C-State Entry and Exit. 3 Input Device Hysteresis. 3 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-1 Processor DIMM Support Summary by Product 2-2 Supported SO-DIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations. 3-4 Processor Core / Package State Support 4-5 Processor Core / Package State Support 4-6 Processor Core / Package State Support 4-7 Processor Core / Package State Support 4-8 Processor Core / Package State Support 4-9 Processor Core / Package State Support 4-1 System Memory Timing Support 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-4 PCI Express* Link States. 4-5 Processor Core / Package State Support 4-6 Processor Graphics Controller States.                                                  | 80    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 7.10 DC Specifications 7.10.1 Voltage and Current Specifications 7.10.1 Voltage and Current Specifications 7.11.1 PECI Bus Architecture 7.11.1 PECI Bus Architecture 7.11.2 DC Characteristics 7.11.3 Input Device Hysteresis 8  Processor Land and Signal Information 8.1 Processor Land Assignments 9  PDR Data Swizzling 9  Figures 1-1 Desktop Processor Platform 1-2 Desktop Processor Compatibility Diagram 1-2 PCI Express* Layering Diagram 1-2 PCI Express* Layering Diagram 1-2 PCI Express* Related Register Structures in the Processor 1-2 PCI Express* Related Register Structures in the Processor 1-2 PCI Express* Typical Operation 16 Lanes Mapping 1-2 Processor Graphics Controller Unit Block Diagram 1-2 Processor Display Block Diagram 1-2 Processor Display Block Diagram 1-2 Inprocessor Display Block Diagram 1-1 Processor Display Bl | 82    |

| 7.10.1 Voltage and Current Specifications. 7.11 Platform Environmental Control Interface (PECI) DC Specifications. 7.11.1 PECI Bus Architecture. 7.11.2 DC Characteristics. 7.11.3 Input Device Hysteresis.  8 Processor Land and Signal Information. 8.1 Processor Land Assignments.  9 DDR Data Swizzling.  Figures  1-1 Desktop Processor Platform. 1-2 Desktop Processor Compatibility Diagram. 2-1 Intel® Flex Memory Technology Operation. 2-2 PCI Express* Layering Diagram. 2-3 Packet Flow Through the Layers. 2-4 PCI Express* Related Register Structures in the Processor. 2-5 PCI Express* Typical Operation 16 Lanes Mapping. 2-6 Processor Graphics Controller Unit Block Diagram. 2-7 Processor Biplay Block Diagram. 4-1 Processor Power States. 4-2 Idle Power Management Breakdown of the Processor Cores. 4-3 Thread and Core C-State Entry and Exit. 4-4 Package C-State Entry and Exit. 4-4 Package C-State Entry and Exit. 4-7 Example for PECI Host-Clients Connection. 7-2 Input Device Hysteresis. 8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-4 Supported UDIMM Module Configurations. 2-3 Supported So-DiIMM Module Configurations (AIO Only). 2-4 System Memory Timing Support 2-5 Reference Clock. 4-1 System States. 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-5 Direct Media Interface (DMI) States.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83    |

| 7.11 Platform Environmental Control Interface (PECI) DC Specifications 7.11.1 PECI Bus Architecture. 7.11.2 DC Characteristics 7.11.3 Input Device Hysteresis.  8 Processor Land and Signal Information. 8.1 Processor Land Assignments  9 DDR Data Swizzling.  Figures  1-1 Desktop Processor Platform. 1-2 Desktop Processor Compatibility Diagram 1-2 Desktop Processor Compatibility Diagram 2-1 Intel® Flex Memory Technology Operation. 2-2 PCI Express* Layering Diagram. 2-3 Packet Flow Through the Layers 2-4 PCI Express* Typical Operation 16 Lanes Mapping. 2-5 PCI Express* Typical Operation 16 Lanes Mapping. 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram. 4-1 Processor Power States. 4-2 Idle Power Management Breakdown of the Processor Cores. 4-3 Thread and Core C-State Entry and Exit. 4-4 Package C-State Entry and Exit. 4-7 Example for PECI Host-Clients Connection. 7-2 Input Device Hysteresis. 8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations (AIO Only). 2-4 System Memory Timing Support 4-5 System Memory Timing Support 4-7 Integrated Memory Controller States. 4-8 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

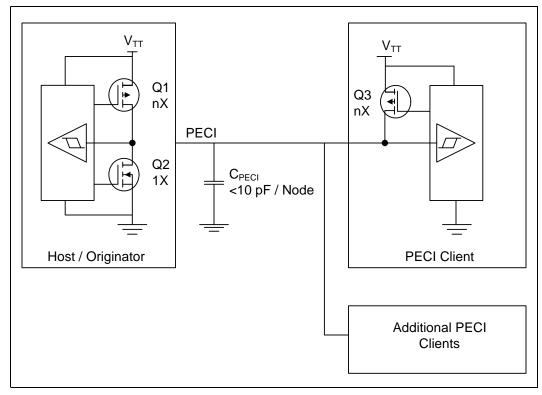

| 7.11.1 PECI Bus Architecture. 7.11.2 DC Characteristics. 7.11.3 Input Device Hysteresis.  8 Processor Land and Signal Information. 8.1 Processor Land Assignments.  9 DDR Data Swizzling.  Figures  1-1 Desktop Processor Platform. 1-2 Desktop Processor Compatibility Diagram. 2-1 Intel® Flex Memory Technology Operation. 2-2 PCI Express* Layering Diagram. 2-3 Packet Flow Through the Layers. 2-4 PCI Express* Related Register Structures in the Processor. 2-5 PCI Express* Typical Operation 16 Lanes Mapping. 2-6 Processor Graphics Controller Unit Block Diagram. 2-7 Processor Display Block Diagram. 4-1 Processor Plates. 4-2 Idle Power Management Breakdown of the Processor Cores. 4-3 Thread and Core C-State Entry and Exit. 4-4 Package C-State Entry and Exit. 4-4 Package C-State Entry and Exit. 4-5 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations. 2-4 System Memory Timing Support 4-5 Reference Clock. 4-1 System Memory Timing Support 4-3 Integrated Memory Controller States. 4-5 Direct Media Interface (DMI) States.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

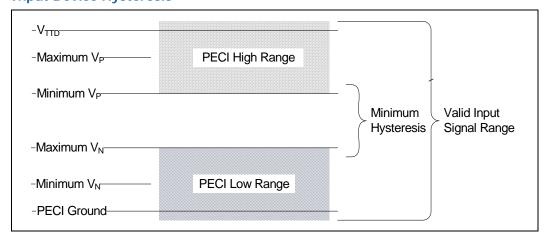

| 7.11.2 DC Characteristics 7.11.3 Input Device Hysteresis.  8 Processor Land and Signal Information 8.1 Processor Land Assignments  9 DDR Data Swizzling.  Figures  1-1 Desktop Processor Platform 1-2 Desktop Processor Compatibility Diagram 2-1 Intel® Flex Memory Technology Operation 2-2 PCI Express* Layering Diagram 2-3 Packet Flow Through the Layers 2-4 PCI Express* Related Register Structures in the Processor 2-5 PCI Express* Typical Operation 16 Lanes Mapping 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores. 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 4-7 Example for PECI Host-Clients Connection. 1-1 Example for PECI Host-Clients Connection. 1-2 Input Device Hysteresis 1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations (AIO Only). 2-4 System Memory Timing Support 2-5 Reference Clock 4-1 System States. 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 90    |

| 7.11.3 Input Device Hysteresis  8 Processor Land and Signal Information 8.1 Processor Land Assignments  9 DDR Data Swizzling  Figures  1-1 Desktop Processor Platform 1-2 Desktop Processor Compatibility Diagram 2-1 Intel® Flex Memory Technology Operation 2-2 PCI Express* Layering Diagram 2-3 Packet Flow Through the Layers 2-4 PCI Express* Related Register Structures in the Processor 2-5 PCI Express* Typical Operation 16 Lanes Mapping 2-7 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Dower States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 4-4 Package C-State Entry and Exit 4-5 Example for PECI Host-Clients Connection 7-1 Input Device Hysteresis 8-1 LGA Socket Land Map  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology 1-3 Related Documents 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations 2-3 Supported SO-DIMM Module Configurations 2-4 System Memory Timing Support 2-5 Reference Clock 4-1 System States 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States 4-4 PCI Express* Link States 4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

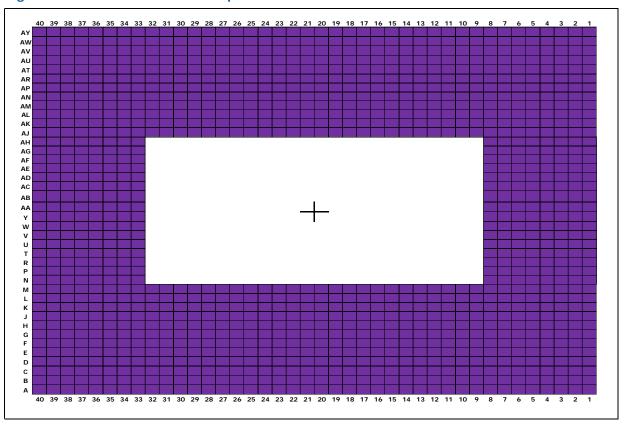

| 8 Processor Land and Signal Information. 8.1 Processor Land Assignments  9 DDR Data Swizzling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| Figures  1-1 Desktop Processor Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91    |

| Figures  1-1 Desktop Processor Platform.  1-2 Desktop Processor Compatibility Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93    |

| Figures  1-1 Desktop Processor Platform.  1-2 Desktop Processor Compatibility Diagram.  2-1 Intel® Flex Memory Technology Operation.  2-2 PCI Express* Layering Diagram.  2-3 Packet Flow Through the Layers.  2-4 PCI Express* Related Register Structures in the Processor.  2-5 PCI Express* Typical Operation 16 Lanes Mapping.  2-6 Processor Graphics Controller Unit Block Diagram.  2-7 Processor Display Block Diagram.  4-1 Processor Power States.  4-2 Idle Power Management Breakdown of the Processor Cores.  4-3 Thread and Core C-State Entry and Exit.  4-4 Package C-State Entry and Exit.  4-5 Package C-State Entry and Exit.  4-6 Package C-State Entry and Exit.  4-7 Example for PECI Host-Clients Connection.  4-8 Input Device Hysteresis.  4-9 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk  1-2 Terminology.  1-3 Related Documents.  2-1 Processor DIMM Support Summary by Product.  2-2 Supported UDIMM Module Configurations.  2-3 Supported SO-DIMM Module Configurations.  2-4 System Memory Timing Support.  2-5 Reference Clock.  4-1 System States.  4-2 Processor Core / Package State Support.  4-3 Integrated Memory Controller States.  4-5 Direct Media Interface (DMI) States.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 93    |

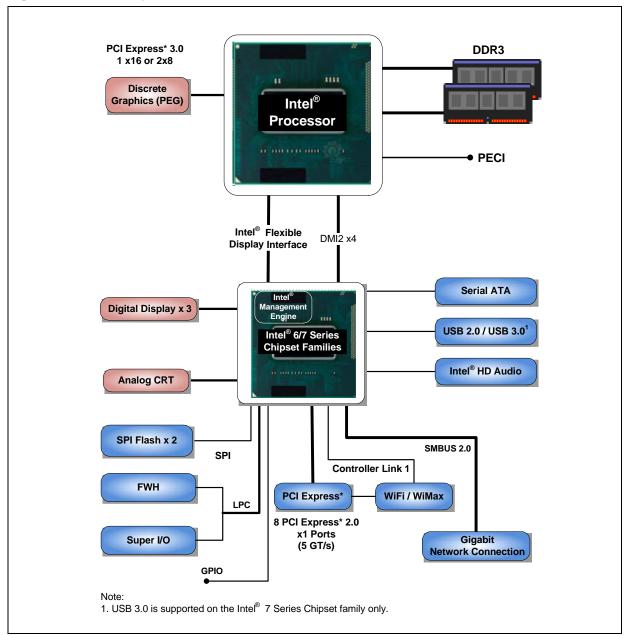

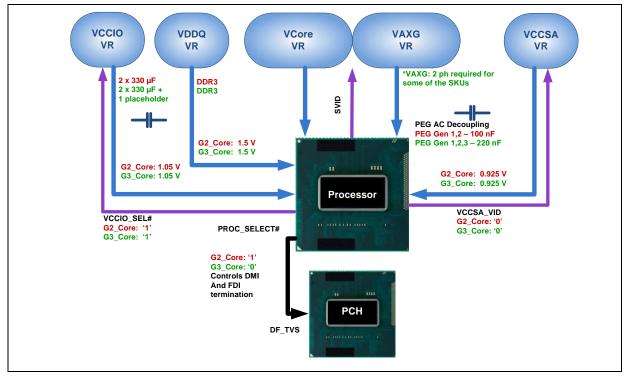

| 1-1 Desktop Processor Platform. 1-2 Desktop Processor Compatibility Diagram 2-1 Intel® Flex Memory Technology Operation. 2-2 PCI Express* Layering Diagram. 2-3 Packet Flow Through the Layers 2-4 PCI Express* Related Register Structures in the Processor. 2-5 PCI Express* Typical Operation 16 Lanes Mapping. 2-6 Processor Graphics Controller Unit Block Diagram. 2-7 Processor Display Block Diagram. 2-7 Processor Display Block Diagram. 4-1 Processor Power States. 4-2 Idle Power Management Breakdown of the Processor Cores. 4-3 Thread and Core C-State Entry and Exit. 4-4 Package C-State Entry and Exit. 4-5 Package C-State Entry and Exit. 4-7 Example for PECI Host-Clients Connection. 4-8 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations (AIO Only). 2-4 System Memory Timing Support. 2-5 Reference Clock. 4-1 System States. 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-5 Direct Media Interface (DMI) States.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 109   |

| 1-1 Desktop Processor Platform. 1-2 Desktop Processor Compatibility Diagram 2-1 Intel® Flex Memory Technology Operation. 2-2 PCI Express* Layering Diagram. 2-3 Packet Flow Through the Layers 2-4 PCI Express* Related Register Structures in the Processor. 2-5 PCI Express* Typical Operation 16 Lanes Mapping. 2-6 Processor Graphics Controller Unit Block Diagram. 2-7 Processor Display Block Diagram. 2-7 Processor Display Block Diagram. 4-1 Processor Power States. 4-2 Idle Power Management Breakdown of the Processor Cores. 4-3 Thread and Core C-State Entry and Exit. 4-4 Package C-State Entry and Exit. 4-5 Package C-State Entry and Exit. 4-7 Example for PECI Host-Clients Connection. 4-8 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations (AIO Only). 2-4 System Memory Timing Support. 2-5 Reference Clock. 4-1 System States. 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-5 Direct Media Interface (DMI) States.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| 1-2 Desktop Processor Compatibility Diagram 2-1 Intel® Flex Memory Technology Operation 2-2 PCI Express* Layering Diagram 2-3 Packet Flow Through the Layers 2-4 PCI Express* Related Register Structures in the Processor 2-5 PCI Express* Typical Operation 16 Lanes Mapping 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 4-7-1 Example for PECI Host-Clients Connection. 7-2 Input Device Hysteresis. 8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents. 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations (AIO Only). 2-4 System Memory Timing Support 2-5 Reference Clock. 4-1 System States. 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4.0   |

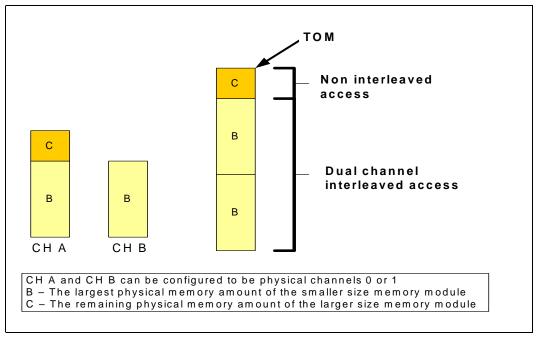

| 2-1 Intel® Flex Memory Technology Operation 2-2 PCI Express* Layering Diagram 2-3 Packet Flow Through the Layers 2-4 PCI Express* Related Register Structures in the Processor 2-5 PCI Express* Related Register Structures in the Processor 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 4-7 Example for PECI Host-Clients Connection 4-8 Input Device Hysteresis 4-9 LGA Socket Land Map  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology 1-3 Related Documents 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations 2-3 Supported SO-DIMM Module Configurations 2-4 System Memory Timing Support 2-5 Reference Clock 4-1 System States 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States 4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

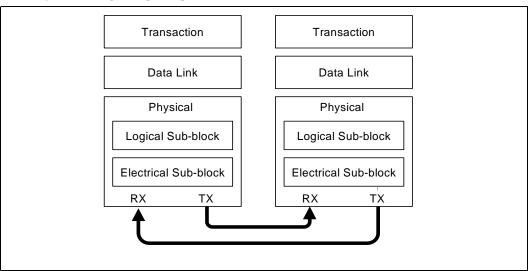

| 2-2 PCI Express* Layering Diagram  2-3 Packet Flow Through the Layers  2-4 PCI Express* Related Register Structures in the Processor  2-5 PCI Express* Typical Operation 16 Lanes Mapping  2-6 Processor Graphics Controller Unit Block Diagram  2-7 Processor Display Block Diagram  4-1 Processor Power States  4-2 Idle Power Management Breakdown of the Processor Cores  4-3 Thread and Core C-State Entry and Exit  4-4 Package C-State Entry and Exit  7-1 Example for PECI Host-Clients Connection  7-2 Input Device Hysteresis  8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk  1-2 Terminology.  1-3 Related Documents  2-1 Processor DIMM Support Summary by Product  2-2 Supported UDIMM Module Configurations.  2-3 Supported SO-DIMM Module Configurations (AIO Only).  2-4 System Memory Timing Support  2-5 Reference Clock  4-1 System States  4-2 Processor Core / Package State Support  4-3 Integrated Memory Controller States.  4-4 PCI Express* Link States  4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

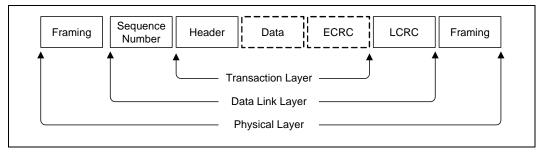

| 2-3 Packet Flow Through the Layers 2-4 PCI Express* Related Register Structures in the Processor 2-5 PCI Express* Typical Operation 16 Lanes Mapping 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 7-1 Example for PECI Host-Clients Connection 7-2 Input Device Hysteresis 8-1 LGA Socket Land Map.  Tables 1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations 2-3 Supported SO-DIMM Module Configurations (AIO Only). 2-4 System Memory Timing Support 2-5 Reference Clock 4-1 System States 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-4 PCI Express* Link States 4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

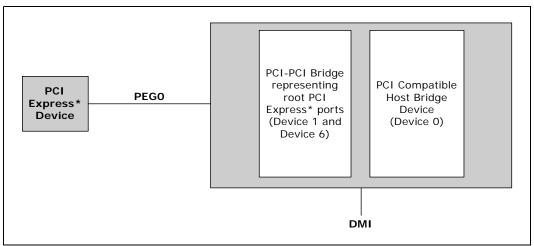

| 2-4 PCI Express* Related Register Structures in the Processor 2-5 PCI Express* Typical Operation 16 Lanes Mapping 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 7-1 Example for PECI Host-Clients Connection 7-2 Input Device Hysteresis 8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations. 2-3 Supported SO-DIMM Module Configurations (AIO Only) 2-4 System Memory Timing Support 2-5 Reference Clock. 4-1 System States. 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States. 4-4 PCI Express* Link States 4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

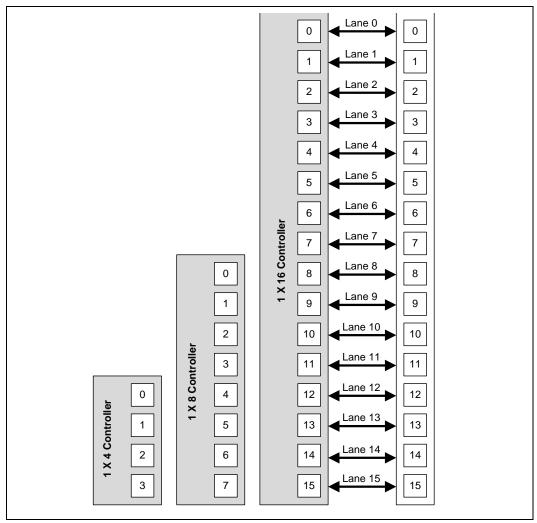

| 2-5 PCI Express* Typical Operation 16 Lanes Mapping 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 7-1 Example for PECI Host-Clients Connection. 7-2 Input Device Hysteresis 8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

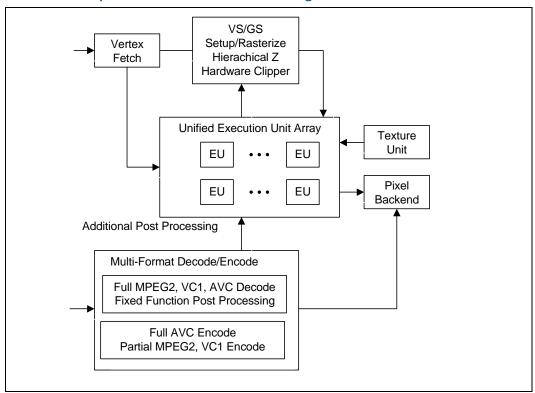

| 2-6 Processor Graphics Controller Unit Block Diagram 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 7-1 Example for PECI Host-Clients Connection. 7-2 Input Device Hysteresis 8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |

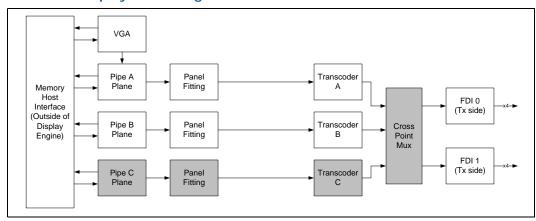

| 2-7 Processor Display Block Diagram 4-1 Processor Power States 4-2 Idle Power Management Breakdown of the Processor Cores 4-3 Thread and Core C-State Entry and Exit 4-4 Package C-State Entry and Exit 7-1 Example for PECI Host-Clients Connection. 7-2 Input Device Hysteresis 8-1 LGA Socket Land Map.  Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk 1-2 Terminology. 1-3 Related Documents 2-1 Processor DIMM Support Summary by Product 2-2 Supported UDIMM Module Configurations 2-3 Supported SO-DIMM Module Configurations (AIO Only) 2-4 System Memory Timing Support 2-5 Reference Clock. 4-1 System States. 4-2 Processor Core / Package State Support 4-3 Integrated Memory Controller States 4-4 PCI Express* Link States 4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

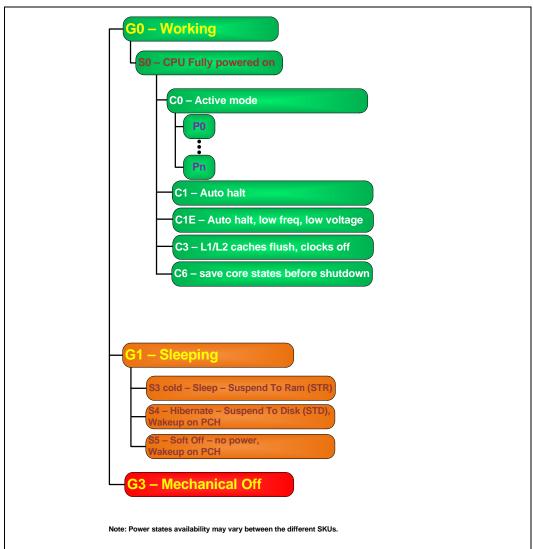

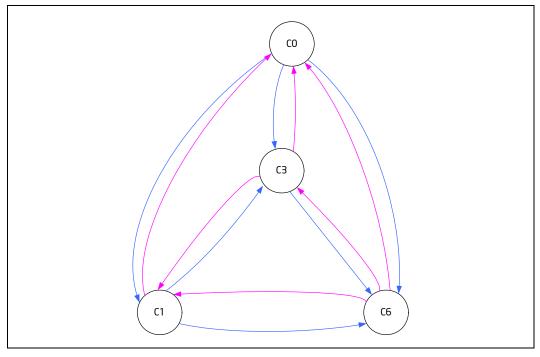

| 4-1 Processor Power States  4-2 Idle Power Management Breakdown of the Processor Cores  4-3 Thread and Core C-State Entry and Exit  4-4 Package C-State Entry and Exit  7-1 Example for PECI Host-Clients Connection.  7-2 Input Device Hysteresis  8-1 LGA Socket Land Map.   Tables  1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk  1-2 Terminology.  1-3 Related Documents  2-1 Processor DIMM Support Summary by Product  2-2 Supported UDIMM Module Configurations  2-3 Supported SO-DIMM Module Configurations (AIO Only).  2-4 System Memory Timing Support  2-5 Reference Clock.  4-1 System States.  4-2 Processor Core / Package State Support  4-3 Integrated Memory Controller States  4-4 PCI Express* Link States  4-5 Direct Media Interface (DMI) States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

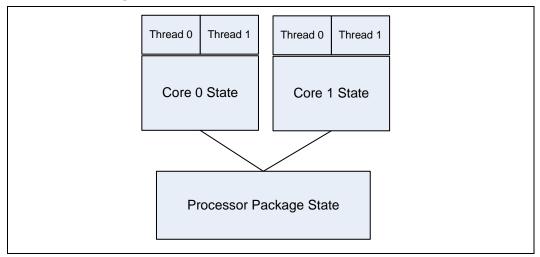

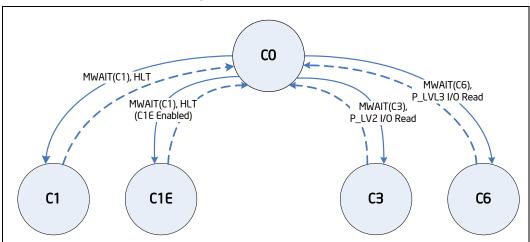

| <ul> <li>4-2 Idle Power Management Breakdown of the Processor Cores</li> <li>4-3 Thread and Core C-State Entry and Exit</li> <li>4-4 Package C-State Entry and Exit</li> <li>7-1 Example for PECI Host-Clients Connection</li> <li>7-2 Input Device Hysteresis</li> <li>8-1 LGA Socket Land Map</li> </ul> Tables <ul> <li>1-1 Desktop 3rd Generation Intel® Core™ Processor Family, Desktop Intel® Pentium® Processor Family, and Desktop Intel® Celeron® Processor Family Sk</li> <li>1-2 Terminology</li> <li>1-3 Related Documents</li> <li>2-1 Processor DIMM Support Summary by Product</li> <li>2-2 Supported UDIMM Module Configurations</li> <li>2-3 Supported SO-DIMM Module Configurations (AIO Only)</li> <li>2-4 System Memory Timing Support</li> <li>2-5 Reference Clock</li> <li>4-1 System States</li> <li>4-2 Processor Core / Package State Support</li> <li>4-3 Integrated Memory Controller States</li> <li>4-4 PCI Express* Link States</li> <li>4-5 Direct Media Interface (DMI) States</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |