#### **General Description**

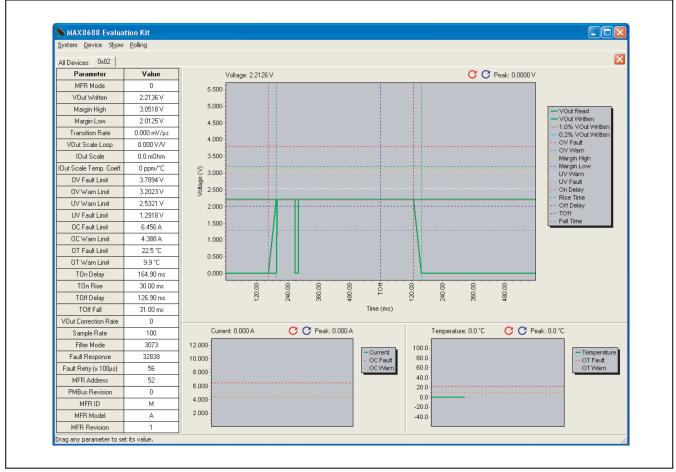

The MAX8688 fully integrated digital power-supply controller and monitor IC works with any existing POL (point-of-load) power supply to provide complete digital programmability. By interfacing to the reference input, feedback node, and output enable, the MAX8688 takes control of the POL to provide functions such as perfect tracking, sequencing, margining, and dynamic adjustment of the output voltage.

The MAX8688 offers an accurate 12-bit analog-to-digital converter (ADC) accompanied with two differential amplifiers for accurately monitoring both voltage and current. An integrated 12-bit digital-to-analog converter (DAC) is also available to margin power supplies as well as dynamically adjust the output voltage with 0.2% accuracy over temperature using this closed-loop system. An internal temperature sensor provides an additional level of system monitoring.

The user-programmable registers provide flexible and accurate control of time events such as a delay time and transition period, monitoring for overvoltage and undervoltage, overcurrent, reverse-current, overtemperature fault and warning handling. The closed-loop operation is also programmable to make sure the MAX8688 works with any existing POL to provide superior regulation accuracy and accurate margining.

The MAX8688 operates using a PMBus™-compliant communication protocol. The device is programmed using this protocol or simply with the use of a free graphic-user interface (GUI) available from the Maxim website that significantly reduces development time. Once the configuration is complete, the results can be saved into an EEPROM or loaded onto the part through the PMBus at power-up. This allows remote configuration of any POL using the MAX8688, replacing expensive recalls or field service. Module current sharing is also supported, since accurate current measurement and fine resolution voltage control are available. The MAX8688 can be programmed with up to 127 distinct addresses to support large systems. The MAX8688 is offered in a space-saving, 24-pin, lead-free 4mm x 4mm TQFN package.

### **Applications**

Telecom Networking DC-DC Modules and POLs

Servers

High-Reliability Infrastructure Equipment

PMBus is a trademark of SMIF, Inc.

### Features

- ◆ PMBus Interface for Programming, Monitoring, Sequencing Up and Down, and Accurate Output-Voltage Control

- ♦ Controls Output Voltage with 0.2% Accuracy for Line, Load, and Temperature Variations

- ♦ Output Voltage, Output Current, and Temperature Monitoring with Adjustable Monitor Rate

- ♦ Current Measurement with 2.6% Accuracy

- Programmable Soft-Start and Soft-Stop Ramp Rates

- ◆ Controls Up to 26 Power Supplies with Hardwired Address Pins and Up to 127 POLs with Software Addressing

- Compatible with REFIN and FB Terminals of POL Power Supplies

- ♦ Protection for POL Against Overvoltage, Undervoltage, Overcurrent, Negative Current and Overtemperature Faults with No Action, Latch and Retry (Hiccup) Options

- ♦ Open-Drain FLT Signal for Fault Detection

- ♦ Master-Slave Clocking Option Eliminates External Clock Requirement and Provides Accurate Timing Reference

- ◆ External EEPROM Interface for Auto-Programming on Power-Up

#### **Ordering Information**

| PART          | TEMP RANGE     | PIN-PACKAGE |

|---------------|----------------|-------------|

| MAX8688ALETG+ | -40°C to +85°C | 24 TQFN-EP* |

| MAX8688AHETG+ | -40°C to +85°C | 24 TQFN-EP* |

| MAX8688BLETG+ | -40°C to +85°C | 24 TQFN-EP* |

| MAX8688BHETG+ | -40°C to +85°C | 24 TQFN-EP* |

$<sup>+</sup> Denotes\ a\ lead (Pb) \hbox{-} free/RoHS \hbox{-} compliant\ package.$

#### **Selector Guide**

| PART          | ACCURACY<br>(%) | ENOUT POWER-UP<br>DEFAULT STATE |

|---------------|-----------------|---------------------------------|

| MAX8688ALETG+ | 0.2             | Low                             |

| MAX8688AHETG+ | 0.2             | High                            |

| MAX8688BLETG+ | 0.4             | Low                             |

| MAX8688BHETG+ | 0.4             | High                            |

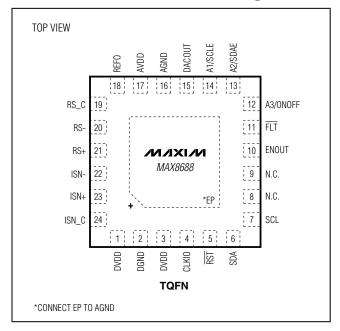

Pin Configuration appears at end of data sheet.

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed pad.

#### ABSOLUTE MAXIMUM RATINGS

| AVDD, DVDD to AGND                                                              |                               |

|---------------------------------------------------------------------------------|-------------------------------|

| DGND to AGND                                                                    | ±0.3V                         |

| RS+, RS-, ISN+, ISN- to AGND                                                    | 0.3V to +6V                   |

| RS_C, ISN_C, A1/SCLE, A2/SDAE,                                                  |                               |

| A3/ONOFF to AGND                                                                | 0.3V to $(V_{AVDD} + 0.3V)$   |

| DACOUT to AGND                                                                  | $0.3V$ to $(V_{AVDD} + 0.3V)$ |

| REFO to AGND                                                                    | 0.3V to +4.5V                 |

| Continuous Power Dissipation (T <sub>A</sub> = 24-Pin TQFN (derate 27.8mW/°C at |                               |

| SCL, SDA, CLKIO, RST to DGND               | 0.3V to +4.5V |

|--------------------------------------------|---------------|

| ENOUT, FLT to DGND                         | 0.3V to +6V   |

| Thermal Resistance from Junction to Expose | d Pad2.7°C/W  |

| Operating Temperature                      |               |

| Junction Temperature                       | +150°C        |

| Storage Temperature                        |               |

| Lead Temperature (soldering, 10s)          | +300°C        |

| Soldering Temperature (reflow) (Note 1)    | +260°C        |

Note 1: Hand soldering not recommended.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 2)

24 TOFN-FF

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>) .......36°C/W Junction-to-Case Thermal Resistance (θ<sub>JC</sub>) .......2.7°C/W

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maxim-ic.com/thermal-tutorial**.

#### **ELECTRICAL CHARACTERISTICS**

(VAVDD = VDVDD = 3.3V, TA = TJ = -40°C to +85°C, VRS+ - VRS- = 2V, VRS- = VAGND, unless otherwise stated.) (Note 3)

| PARAMETER                                                  | SYMBOL | CONDITIONS                                                                                      | MIN  | TYP | MAX  | UNITS |

|------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------|------|-----|------|-------|

| GENERAL                                                    |        |                                                                                                 |      |     |      |       |

| AVDD/DVDD Operating Range                                  |        |                                                                                                 | 3.0  |     | 3.6  | V     |

| AVDD and DVDD Operating Supply Current                     |        | V <sub>RS+</sub> = V <sub>RS-</sub> = V <sub>ISN+</sub> = V <sub>ISN-</sub> = V <sub>AGND</sub> |      | 6.7 | 8.5  | mA    |

| AVDD UVLO                                                  |        | Rising                                                                                          | 2.70 | 2.8 | 2.95 | V     |

| AVDD GVEG                                                  |        | Hysteresis                                                                                      |      | 100 |      | mV    |

| OUTPUT-VOLTAGE SENSING                                     |        |                                                                                                 |      |     |      |       |

|                                                            |        | MAX8688A, T <sub>A</sub> = 0°C to +85°C,<br>V <sub>RS+</sub> = 1V, V <sub>RS-</sub> = 0V        | -0.2 |     | +0.2 |       |

| Voltage Regulation Accuracy (2V                            |        | MAX8688A, $T_A = -40^{\circ}C$ to +85°C, $V_{RS+} = 1V$ , $V_{RS-} = 0V$                        | -0.3 |     | +0.3 | %     |

| Range, Table 8) (Note 4)                                   |        | MAX8688B, $T_A = 0^{\circ}C$ to +85°C, $V_{RS+} = 1V$ , $V_{RS-} = 0V$                          | -0.4 |     | +0.4 |       |

|                                                            |        | MAX8688B, $T_A = -40^{\circ}C$ to +85°C, $V_{RS+} = 1V$ , $V_{RS-} = 0V$                        | -0.5 |     | +0.5 |       |

|                                                            |        | MAX8688A, T <sub>A</sub> = 0°C to +85°C,<br>V <sub>RS+</sub> = 2.5V, V <sub>RS-</sub> = 0V      | -0.3 |     | +0.3 |       |

| Voltage Regulation Accuracy (5.5V range, Table 8) (Note 4) |        | MAX8688A, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , $V_{RS+} = 2.5V$ , $V_{RS-} = 0V$            | -0.4 |     | +0.4 | 0/    |

|                                                            |        | MAX8688B, T <sub>A</sub> = 0°C to +85°C,<br>V <sub>RS+</sub> = 2.5V, V <sub>RS-</sub> = 0V      | -0.4 |     | +0.4 | %     |

|                                                            |        | MAX8688B, T <sub>A</sub> = -40°C to +85°C,<br>V <sub>RS+</sub> = 2.5V, V <sub>RS-</sub> = 0V    | -0.5 |     | +0.5 |       |

| RS+, RS- Differential Mode Range                           |        |                                                                                                 | 0    |     | 5.5  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 3.3V, T_A = T_J = -40^{\circ}C \text{ to } +85^{\circ}C, V_{RS+} - V_{RS-} = 2V, V_{RS-} = V_{AGND}, unless otherwise stated.)$  (Note 3)

| PARAMETER                                     | SYMBOL   | CONDITIONS                                                                              | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------|----------|-----------------------------------------------------------------------------------------|------|------|------|-------|

| RS- to AGND Differential Voltage              |          |                                                                                         | -250 |      | +250 | mV    |

| DC . Innuit Diag Current                      |          | $2V \text{ range, } V_{RS+} = -0.25V \text{ to } +2V$                                   | -10  |      | +15  |       |

| RS+ Input Bias Current                        |          | 5.5V range, V <sub>RS+</sub> = -0.25V to +5.5V                                          | -10  |      | +60  | μΑ    |

| RS- Input Bias Current                        |          | 2V or 5.5V range, V <sub>RS</sub> - = -0.25V to +0.25V                                  | -10  |      | 0    | μΑ    |

| OUTPUT CURRENT SENSE                          |          |                                                                                         |      |      |      |       |

| Current-Sense Accuracy (Note 4)               |          | $V_{ISN+} = 1V$ , $V_{ISN+} - V_{ISN-} = 20mV$ , $T_A = +25^{\circ}C$ to $+85^{\circ}C$ | -2.6 |      | +2.6 | %     |

| Current-Sense Accuracy (Note 4)               |          | $V_{ISN+} = 1V$ , $V_{ISN+} - V_{ISN-} = 20mV$ , $T_A = -40^{\circ}C$ to $+85^{\circ}C$ | -7   |      | +7   | /0    |

| ISN+, ISN- Common-Mode Range                  |          |                                                                                         | 0    |      | 5.5  | V     |

| ISN+, ISN- Common-Mode<br>Current-Sense Error |          | V <sub>CM</sub> = 0 to 5.5V, V <sub>DM</sub> = 20mV                                     |      | 0.9  |      | %     |

| ISN+, ISN- Differential Mode<br>Range         |          |                                                                                         | -10  |      | +40  | mV    |

| ISN+, ISN- Input Bias Current                 |          | V <sub>ISN+</sub> , V <sub>ISN-</sub> to V <sub>AGND</sub> = 0V or 5.5V                 | -20  |      | +40  | μΑ    |

| RS_C, ISN_C                                   |          |                                                                                         |      |      |      | •     |

| RS_C, ISN_C Output Impedance                  |          |                                                                                         |      | 0.2  |      | kΩ    |

| TEMPERATURE SENSING                           |          |                                                                                         |      |      |      |       |

| Temperature Sensing Accuracy                  |          | Exposed pad = -40°C to +100°C                                                           |      | ±3   |      | °C    |

| CLKIO                                         |          |                                                                                         |      |      |      |       |

| CLKIO Input-Logic Low Voltage                 |          |                                                                                         |      |      | 0.8  | V     |

| CLKIO Input-Logic High Voltage                |          |                                                                                         | 2.1  |      |      | V     |

| CLKIO Input Bias Current                      |          | V <sub>CLKIO</sub> = 0V or 3.6V                                                         | -1   |      | +1   | μΑ    |

| CLKIO Input Clock Duty Cycle                  |          | f <sub>CLKIO</sub> = 100kHz to 2500kHz                                                  | 20   |      | 80   | %     |

| CLKIO Output Low Voltage                      |          | CLKIO in output mode, ISINK = 4mA                                                       |      |      | 0.4  | V     |

| CLKIO Output High Leakage                     |          | V <sub>CLKIO</sub> = V <sub>DVDD</sub> = V <sub>AVDD</sub> = 3.6V                       | -1   |      | +1   | μΑ    |

| CLKIO Input/Output Clock Rise<br>Time         |          | R <sub>PULLUP</sub> = $560\Omega$ , C <sub>LOAD</sub> = $20$ pF                         |      | 20   |      | ns    |

| CLKIO Input/Output Clock Fall Time            |          | R <sub>PULLUP</sub> = $560\Omega$ , C <sub>LOAD</sub> = $20$ pF                         |      | 2    |      | ns    |

| CLKIO Pullup Voltage                          |          |                                                                                         |      |      | DVDD | V     |

| CLKIO Input Frequency                         | fEXT_CLK |                                                                                         | 100  |      | 2500 | kHz   |

| CLKIO Output Frequency<br>Accuracy            | _        |                                                                                         | 0.95 | 1.00 | 1.05 | MHz   |

| ENOUT, FLT OPEN-DRAIN LOGIC                   | OUTPUTS  |                                                                                         |      |      |      |       |

| ENOUT, FLT Output Low Voltage                 |          | I <sub>SINK</sub> = 4mA                                                                 |      |      | 0.4  | V     |

| ENOUT, FLT Output High Leakage                |          | VENOUT = VFLT = 5.5V,<br>VDVDD = VAVDD = 3.6V                                           | -1   |      | +1   | μΑ    |

| ENOUT, FLT Pullup Voltage                     |          |                                                                                         |      |      | 5.5  | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = V_{DVDD} = 3.3V, T_A = T_J = -40^{\circ}C \text{ to } +85^{\circ}C, V_{RS+} - V_{RS-} = 2V, V_{RS-} = V_{AGND}, \text{ unless otherwise stated.})$  (Note 3)

| PARAMETER                                                   | SYMBOL              | CONDITIONS                                                                | MIN           | TYP             | MAX           | UNITS |

|-------------------------------------------------------------|---------------------|---------------------------------------------------------------------------|---------------|-----------------|---------------|-------|

| DAC                                                         |                     | ,                                                                         |               |                 |               | 1     |

| DAC Resolution                                              |                     |                                                                           |               | 12              |               | bits  |

| DAC Output-Voltage Range                                    |                     | No load                                                                   |               | REFO -<br>1 LSB |               | V     |

| DAC Output-Voltage Slew Rate                                |                     |                                                                           |               | 0.6             |               | V/µs  |

| DAC Output Resistance                                       |                     |                                                                           |               | 5               |               | Ω     |

| DAC Driving Capability                                      |                     |                                                                           |               | 2               |               | mA    |

| ADC                                                         |                     |                                                                           |               |                 |               |       |

| ADC Resolution                                              |                     | MAX8688A<br>MAX8688B                                                      |               | 12<br>11        |               | Bits  |

| THREE-STATE ADDRESS PINS (A                                 | 3/ONOFF, A2         | /SDAE, A1/SCLE)                                                           | 1             |                 |               |       |

| Three-State Address Pins Input<br>Low Voltage               |                     |                                                                           |               |                 | 0.3           | V     |

| Three-State Address Pins Input<br>Low Threshold Hysteresis  |                     |                                                                           |               | 50              |               | mV    |

| Three-State Address Pins Input<br>High Voltage              |                     |                                                                           | AVDD -<br>0.4 |                 |               | V     |

| Three-State Address Pins Input<br>High Threshold Hysteresis |                     |                                                                           |               | 50              |               | mV    |

| Three-State Address Pins Input<br>Bias Current              |                     | V <sub>AVDD</sub> = 3.6V, A3/ONOFF = A2/SDAE = A1/SCLE = AVDD or AGND     | -12           |                 | +12           | μΑ    |

| THREE-STATE ADDRESS PINS (A                                 | 2/SDAE (DAT         | A) AND A1/SCLE (CLOCK) WITH EEPROM                                        | /I) (Note 5)  |                 |               | •     |

| A2/SDAE, A1/SCLE Output Low<br>Voltage                      |                     | Output sink current = 100μA (Note 6)                                      |               |                 | 0.3 x<br>AVDD | V     |

| A2/SDAE, A1/SCLE Output High<br>Voltage                     |                     | Output source current = 100µA (Note 7)                                    | 0.7 x<br>AVDD |                 |               | V     |

| THREE-STATE ADDRESS PIN (A3)                                | ONOFF AS P          | OL ON/OFF CONTROL)                                                        | 1             |                 |               |       |

| Minimum A3/ONOFF Control Pulse<br>Low Time                  | ta3_low             |                                                                           |               | 250             |               | μs    |

| Minimum A3/ONOFF Control Pulse<br>High Time                 | ta3_High            |                                                                           |               | 750             |               | μs    |

| SCL, SDA SMBus™ SIGNALS                                     | •                   |                                                                           | 1             |                 |               |       |

| Maximum SMBus Speed                                         |                     |                                                                           |               | 100             |               | kHz   |

| SCL, SDA Input Low Voltage                                  | V <sub>SMB_IL</sub> | $V_{DVDD} = 3.0V \text{ to } 3.6V$                                        |               |                 | 0.8           | V     |

| SCL, SDA Input High Voltage                                 | V <sub>SMB_IH</sub> | V <sub>DVDD</sub> = 3.0V to 3.6V                                          | 2.1           |                 | DVDD          | V     |

| SCL, SDA Output Low Voltage                                 | V <sub>SMB_OL</sub> | V <sub>DVDD</sub> = 3.0V to 3.6V at I <sub>SINK</sub> = 4mA               |               |                 | 0.4           | V     |

| SCL, SDA Input Leakage Per<br>Device Pin                    | ISMB_ILEAK          | V <sub>DVDD</sub> = 3.6V, V <sub>SCL</sub> = V <sub>SDA</sub> = 0 or 3.6V | -1            |                 | +1            | μΑ    |

SMBus is a trademark of Intel Corp.

#### **ELECTRICAL CHARACTERISTICS (continued)**

(VAVDD = VDVDD = 3.3V, TA = TJ = -40°C to +85°C, VRS+ - VRS- = 2V, VRS- = VAGND, unless otherwise stated.) (Note 3)

| PARAMETER                                              | SYMBOL              | CONDITIONS                         | MIN | TYP | MAX | UNITS |  |  |

|--------------------------------------------------------|---------------------|------------------------------------|-----|-----|-----|-------|--|--|

| RST INPUT                                              | RST INPUT           |                                    |     |     |     |       |  |  |

| RST Input Low Voltage                                  | V <sub>RST_IL</sub> | V <sub>DVDD</sub> = 3.0V to 3.6V   |     |     | 0.8 | V     |  |  |

| RST Input High Voltage                                 | V <sub>RST_IH</sub> | $V_{DVDD} = 3.0V \text{ to } 3.6V$ | 2.1 |     |     | V     |  |  |

| RST Input Bias Current                                 |                     | RST = DVDD or DGND                 |     |     | 10  | μΑ    |  |  |

| Minimum SMBus Interface Reset Pulse Width              | tsmb_rst            |                                    | 1   |     | 455 | μs    |  |  |

| SMBus Interface Recovery Time<br>After Interface Reset | tsmb_wait           |                                    |     | 15  |     | μs    |  |  |

| Minimum Reset Pulse Width                              | trst                |                                    | 565 |     |     | μs    |  |  |

| Recovery Time After Device Reset                       | trst_wait           |                                    |     | 15  |     | μs    |  |  |

| OTHER TIMING PARAMETERS                                |                     |                                    |     |     |     |       |  |  |

| PMBus Command Response Time                            | tpmb_rsp            |                                    |     | 300 |     | μs    |  |  |

| Fault Response Time                                    | t=41.11. = DOD      | Overvoltage fault                  | 5   |     |     |       |  |  |

|                                                        | tFAULT_RSP          | Overcurrent fault                  |     | 5   | •   | ms    |  |  |

- Note 3: Production tested at T<sub>A</sub> = +25°C and T<sub>A</sub> = +85°C. Specifications from T<sub>A</sub> = -40°C to +25°C are guaranteed by design, unless otherwise noted.

- **Note 4:** Production tested at  $T_A = +85^{\circ}C$  only. All other temperatures are guaranteed by design.

- **Note 5:** When an EEPROM is connected to A2/SDAE and A1/SCLE, these pins cannot be hardwired to ground or supply. They must be connected through  $33k\Omega$   $\pm5\%$  resistors.

- Note 6: Equivalent of having  $33k\Omega$  pulldown resistor to DGND.

- **Note 7:** Equivalent of having  $33k\Omega$  pullup resistor to DVDD.

### **Typical Operating Characteristics**

$(V_{AVDD} = V_{DVDD} = 3.3V, T_A = +25$ °C, unless otherwise noted.)

### Typical Operating Characteristics (continued)

(VAVDD = VDVDD = 3.3V, TA = +25°C, unless otherwise noted.)

6 \_\_\_\_\_\_\_/N/JXI/M

### Typical Operating Characteristics (continued)

$(V_{AVDD} = V_{DVDD} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN  | NAME                                                                                                                                                                                                                                                                                      | FUNCTION                                                                                                                                                                                                                                                 |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 3 | DVDD                                                                                                                                                                                                                                                                                      | Digital Power-Supply Input (3.3V, typ). Connect AVDD to DVDD externally. Connect a 0.1µF capacitor from DVDD to DGND.                                                                                                                                    |  |  |

| 2    | DGND                                                                                                                                                                                                                                                                                      | Digital Ground. Connect AGND to DGND externally close to the device.                                                                                                                                                                                     |  |  |

| 4    | Clock Input/Output. User-configurable clock input/output signal. The system controller can provide input to synchronize the time bases of multiple MAX8688 devices. Alternatively, a MAX8688 can 1MHz output clock to other MAX8688s for synchronization. See the MFR_MODE (D1h) section. |                                                                                                                                                                                                                                                          |  |  |

| 5    | RST                                                                                                                                                                                                                                                                                       | Active-Low SMBus Interface and Device Reset Line. Active-low logic input. See the RST Operation section.                                                                                                                                                 |  |  |

| 6    | SDA                                                                                                                                                                                                                                                                                       | SMBus Data Line                                                                                                                                                                                                                                          |  |  |

| 7    | SCL                                                                                                                                                                                                                                                                                       | SMBus Clock Line                                                                                                                                                                                                                                         |  |  |

| 8, 9 | N.C.                                                                                                                                                                                                                                                                                      | No Connection. Not internally connected.                                                                                                                                                                                                                 |  |  |

| 10   | ENOUT                                                                                                                                                                                                                                                                                     | On/Off Signal Open-Drain Output. Typically used to turn on/off a POL power supply under the PMBus command or A3/ONOFF control. See the <i>ENOUT Operation</i> and <i>MFR_MODE</i> ( <i>D1h</i> ) sections.                                               |  |  |

| 11   | FLT                                                                                                                                                                                                                                                                                       | Fault Output, Active-Low Open-Drain Output. Typically connected to system controller/master interrupt input.                                                                                                                                             |  |  |

| 12   | A3/ONOFF                                                                                                                                                                                                                                                                                  | Dual-Functioned Three-State MAX8688 Slave Address Identifier (MSB) and POL On/Off Control using the MFR_MODE Command. See the <i>MAX8688 Address Assignment</i> and <i>A3/ONOFF Operation</i> sections.                                                  |  |  |

| 13   | A2/SDAE                                                                                                                                                                                                                                                                                   | Dual-Functioned Three-State MAX8688 Slave Address Identifier and EEPROM I <sup>2</sup> C Data Line. See the MAX8688 Address Assignment and External EEPROM Interface sections.                                                                           |  |  |

| 14   | A1/SCLE                                                                                                                                                                                                                                                                                   | Dual-Functioned Three-State MAX8688 Slave Address Identifier (LSB) and EEPROM I <sup>2</sup> C Clock Line. See the MAX8688 Address Assignment and External EEPROM Interface sections.                                                                    |  |  |

| 15   | DACOUT                                                                                                                                                                                                                                                                                    | Analog Voltage Output of Internal 12-Bit DAC. Connect DACOUT to REFIN or FB of the DC-DC module with high impedance in shutdown.                                                                                                                         |  |  |

| 16   | AGND                                                                                                                                                                                                                                                                                      | Analog Ground. Connect AGND to DGND externally close to the device.                                                                                                                                                                                      |  |  |

| 17   | AVDD                                                                                                                                                                                                                                                                                      | Analog Power-Supply Input (3.3V, typ). Connect AVDD to DVDD externally. Connect 0.1µF capacitor from AVDD to AGND.                                                                                                                                       |  |  |

| 18   | REFO                                                                                                                                                                                                                                                                                      | Buffered Reference Output. Connect a 1µF capacitor from REFO to ground.                                                                                                                                                                                  |  |  |

| 19   | RS_C                                                                                                                                                                                                                                                                                      | Filter Capacitor Connection for V <sub>SENSE</sub> Amplifier                                                                                                                                                                                             |  |  |

| 20   | RS-                                                                                                                                                                                                                                                                                       | Differential Remote-Sense Input Return of the DC-DC Output Voltage. Connect RS- to the return terminal at the load.                                                                                                                                      |  |  |

| 21   | RS+                                                                                                                                                                                                                                                                                       | Differential Remote-Sense Input of DC-DC Output Voltage. Connect RS+ to the load terminal where the output must be regulated.                                                                                                                            |  |  |

| 22   | ISN-                                                                                                                                                                                                                                                                                      | Differential-Sense Input Return of DC-DC Output Current. Connect ISN- to the negative end of the current-sense resistor (Figure 3). In case of DCR sensing, connect ISN- to the return terminal of filter capacitor Cs (Figure 7).                       |  |  |

| 23   | ISN+                                                                                                                                                                                                                                                                                      | Differential-Sense Input of DC-DC Output Current. Connect ISN+ to the positive end of the current-sense resistor. In case of DCR sensing, connect ISN+ to the junction of filter resistor and capacitor (R <sub>S</sub> and C <sub>S</sub> ) (Figure 7). |  |  |

| 24   | ISN_C                                                                                                                                                                                                                                                                                     | Filter Capacitor Connection for ISENSE Amplifier                                                                                                                                                                                                         |  |  |

| _    | EP                                                                                                                                                                                                                                                                                        | Exposed Pad. Connect EP to the AGND plane for the POL for best temperature measurement performance. Do not use EP as the main ground connection.                                                                                                         |  |  |

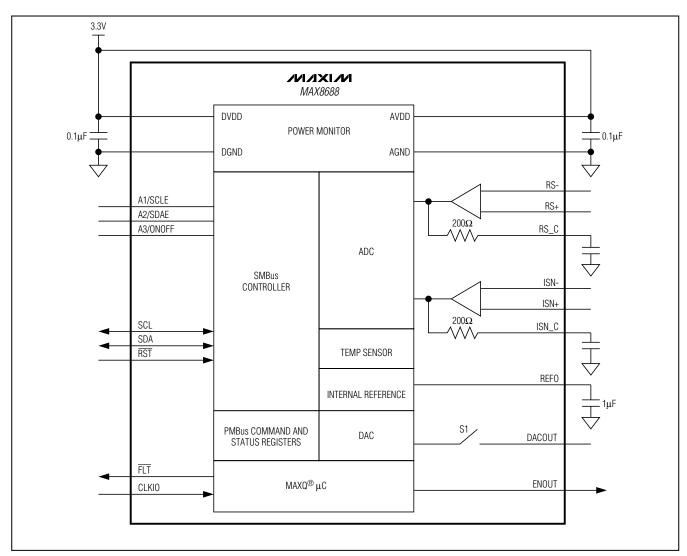

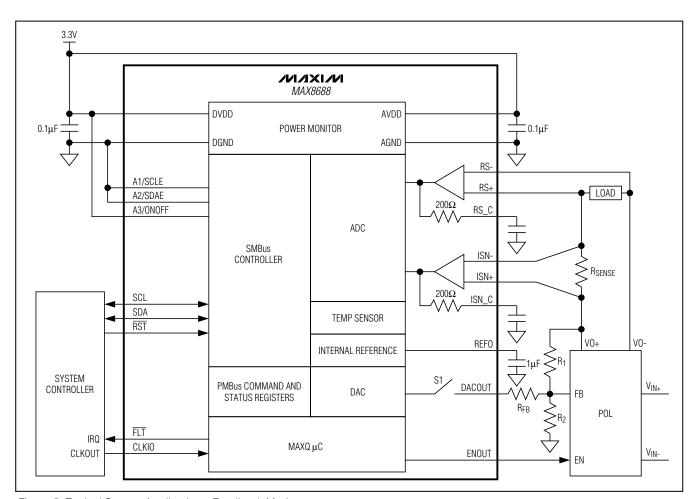

Figure 1. MAX8688 Functional Diagram

#### **Detailed Description**

For many applications, it is desirable to control the output voltage of a POL power supply to a much higher accuracy than the offered standard 1% overtemperature specification. Many designs are required to access information such as output voltage, output current, and temperature of individual power supplies in a board, for monitoring system health as well as logging fault information to help in failure analysis. Moreover, it is desirable to sequence startup and shutdown of multiple power supplies in an application with programmable start, stop delays, and soft-start ramp rates to avoid

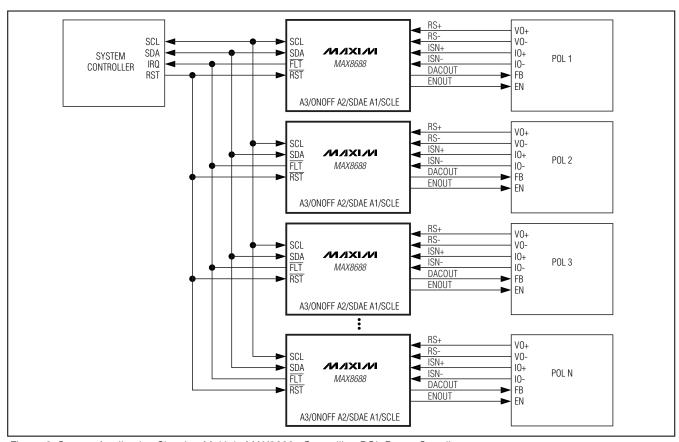

latchup and stressing of ESD structures. The MAX8688 solves these problems by providing the required functions in a small compact IC that is capable of interfacing with a master controller through an on-board PMBus interface. Up to 127 MAX8688s can reside on the same PMBus bus, each controlling its own POL, under command from the system controller, as shown in Figure 2. Long traces from POLs located at various system board locations for voltage sensing and current sensing are avoided resulting in a cleaner layout for the system designer. POLs can therefore be placed close to the load where they provide the best transient response with short power plane runs.

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

Figure 2. System Application Showing Multiple MAX8688s Controlling POL Power Supplies

### MAX8688 Operating Modes Reference Input (REFIN) Mode

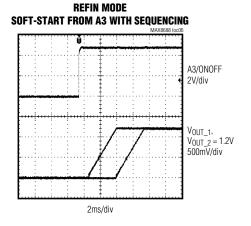

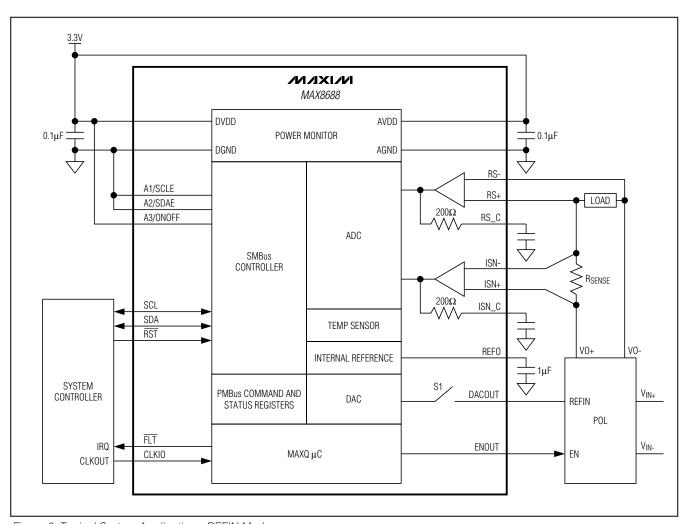

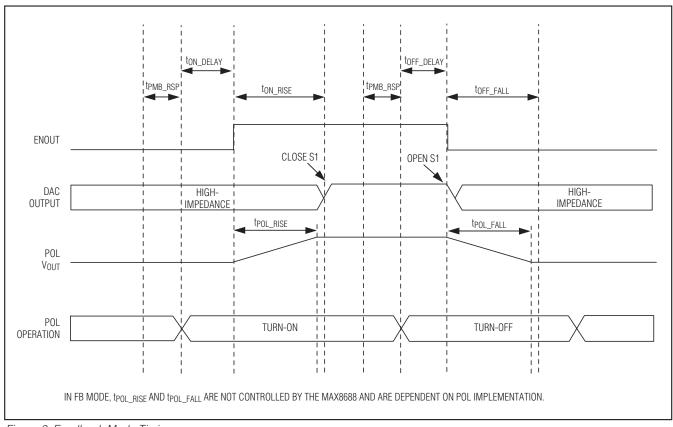

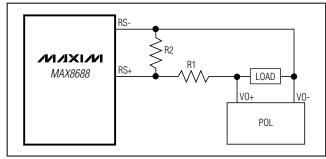

Figure 3 shows the typical manner in which the MAX8688 is used in an application where the POL has a reference input, REFIN, to which it regulates its output voltage between the VO+ and VO- terminals. In the REFIN application, the DACOUT of the MAX8688 is connected to the REFIN input of the POL. The output voltage of the POL is sensed using RS+ and RS-. The sensed voltage is suitably filtered by an internal  $200\Omega$  resistor and external capacitor connected to RS\_C and is multiplexed to a 12-bit ADC that uses an accurate internal reference voltage. On receipt of either an OPERATION ON command or a turn-on signal from A3/ONOFF, the MAX8688 commences the startup operation that has been programmed for the POL being controlled.

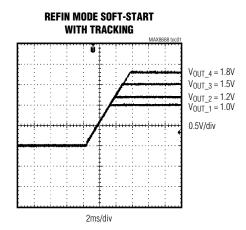

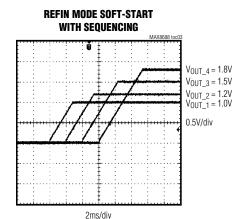

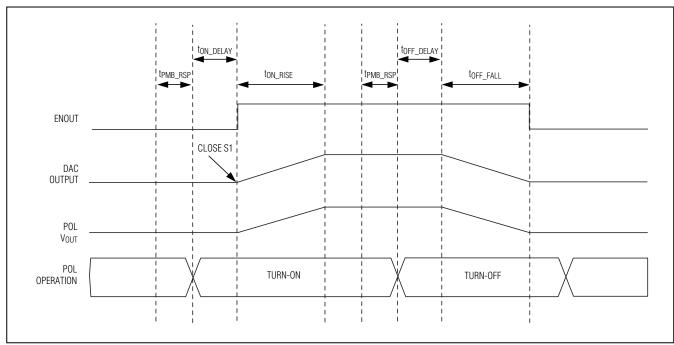

After the programmed ton\_DELAY time, the MAX8688 open-drain ENOUT output goes active and the POL output voltage is ramped up to its target VOUT\_COMMAND value precisely in the programmed ton\_RISE time. This facilitates easy implementation of tracking of multiple out-

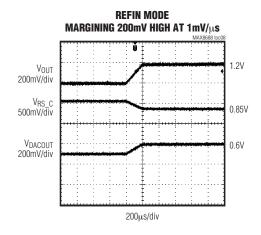

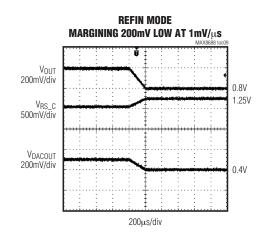

put rails. On reaching the target output voltage, the MAX8688 continuously monitors the POL output voltage obtained at the RS+ and RS- inputs, and regulates it to within ±0.2% for line, load, and temperature variations by incrementing or decrementing the DACOUT output 1 LSB (0.5mV) at a time. The MAX8688 output-voltage correction rate is programmable up to 10kHz by the MFR\_VOUT\_CORRECTION\_RATE parameter. Once the requested target POL voltage is reached, it is possible to easily margin up or down the POL voltage at a preprogrammed slew rate set by the parameter VOUT\_TRANSI-TION\_RATE. To achieve this, the MAX8688 increments or decrements the DACOUT output in a suitable number of steps that depend on the programmed transition rate. In addition, the user needs to program the VOUT\_SCALE\_LOOP parameter equal to any voltagedivider ratio implemented on the POL from its output voltage node to the inverting input of its error amplifier. This allows the MAX8688 to correctly calculate the number of DACOUT steps and voltage increments/decrements per step and thus achieves the programmed rise time and transition time.

10 \_\_\_\_\_\_\_ **/VIXI/M**

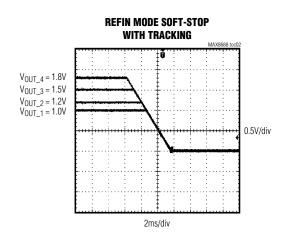

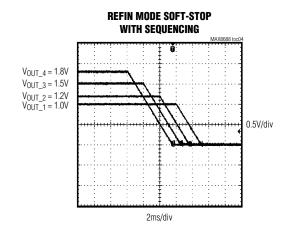

Since the reference voltage input is provided by the MAX8688, the REFIN mode provides complete control of the POL in terms of soft-start, soft-stop, and margining transitions. It may be noted that the slew rates during soft-start (ton\_RISE) and during margining (VOUT\_TRANSITION\_RATE) should be programmed with POL current-limit consideration. An excessively fast slew rate causes the POL to trip due to overcurrent. A general guideline for setting the output-voltage slew rate is as follows:

SLEW RATE

$$\leq \frac{(|L_{IMIT} - |L_{OAD})}{C_{OUT}}$$

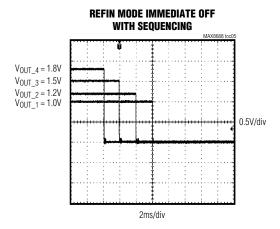

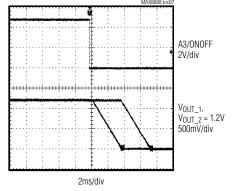

where C<sub>OUT</sub> is the output capacitance on the POL output, I<sub>LOAD</sub> is the load current being delivered by the POL, and I<sub>LIMIT</sub> is the current-limit setting of the POL. On receipt of either an OPERATION OFF command or a turn-off signal from A3/ONOFF, the MAX8688 commences the shutdown operation that has been programmed for the POL being controlled. After the programmed toff\_Delay time, the MAX8688 ramps down the output voltage to zero precisely in the programmed toff\_fall time, and deasserts its open-drain ENOUT output.

Figure 3. Typical System Application—REFIN Mode

Figure 4. REFIN Mode Timing

#### Feedback (FB) Mode

In applications where a REFIN input is not available, the MAX8688 interfaces to the inverting input of the POL error amplifier, the feedback node (FB), through a resistor RFB as shown in Figure 5. In steady-state operation, the MAX8688 controls the POL voltage as measured between RS+ and RS- to 0.2% accuracy over line, load, and temperature variations, by adjusting DACOUT 1 LSB (0.5mV) at a time, up and down as required. This mode of operation is termed FB mode. Since the MAX8688 does not have control over the POL error-amplifier reference voltage, this mode relies on the POL soft-start setting to implement the required soft-start time. On receipt of either an OPERATION ON command or a turn-on signal from A3/ONOFF, the MAX8688 commences startup operations that have been programmed for the POL being controlled. After the programmed ton DELAY time, the MAX8688 opendrain ENOUT output goes active, causing the POL to ramp up its output voltage to its target value. The softstart time taken by the POL to ramp from zero to its commanded output voltage should be entered into the MAX8688 with the ton RISE parameter.

During  $t_{ON\_RISE}$ , the MAX8688 maintains DACOUT in a high-impedance state by keeping the S1 switch open. This allows the voltage at DACOUT to equal that of the FB node of the POL. At the end of the  $t_{ON\_RISE}$  delay

time, the internal DAC output is initialized to the external voltage measured on DACOUT and switch S1 is closed. If the POL has completed its soft-start and settled down at its output voltage, the DAC output is initialized to the steady-state value of the POL FB voltage. Therefore, when switch S1 is closed, the voltages on either side of the resistor RFB are equal. Under these conditions, zero current flows into the FB node from DACOUT and no perturbations are introduced to the output voltage. From this point on, the MAX8688 adjusts the voltage at DACOUT to provide accurate output voltage control. In FB mode, the user is required to supply ton\_DELAY and ton\_RISE parameters. If those parameters are not set (the default values are zero), S1 closes prematurely and cause an initial error in the voltage monitor.

On receipt of either an OPERATION OFF command or a turn-off signal from A3/ONOFF, the MAX8688 commences the shutdown operation that has been programmed for the POL being controlled. After the programmed toff\_Delay time, the MAX8688 deasserts its open-drain ENOUT output, and turns off the POL.

For the FB mode, the value of RFB is selected based on following formula:

$$R_{FB} = R_1 \times \frac{\Delta V_{DAC}}{\Delta V_{O}}$$

12 \_\_\_\_\_\_ /I/XI/V

where R<sub>1</sub> is the upper feedback divider resistor,  $\Delta V_O$  is the required change in output voltage, and  $\Delta V_{DAC}$  is the DACOUT output voltage change that the user allows. The recommended operating range for the DACOUT voltage for POL output voltage adjustment is between 30mV and 2V. It should be noted that  $\Delta V_{DAC}$  is the difference between the steady-state POL FB node voltage, VFB, and the voltage limits on DACOUT. This is best illustrated with an example as follows:

Consider an application involving a POL with VFB = 0.6V. Let the desired margining be  $\pm 10\%$  for a POL output voltage of 1V. For a POL with an upper voltage-divider resistor R<sub>1</sub> =  $10k\Omega$ , RFB is calculated as follows:

$$R_{FB} = 10k\Omega \times \frac{(0.6V - 0.03V)}{0.1V} = 57k\Omega$$

This value of RFB allows the MAX8688 to margin the POL output voltage up by 10%. It is useful to check the margin low condition by using the formula:

$$\Delta V_O = R_1 \times \frac{\Delta V_{DAC}}{R_{FB}} = 10k\Omega \times \frac{(2.0V - 0.6V)}{57k\Omega} = 0.245V$$

The effective margining range for the  $57k\Omega$  resistor therefore turns out to be between +10% and -24.5%.

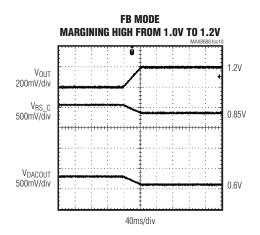

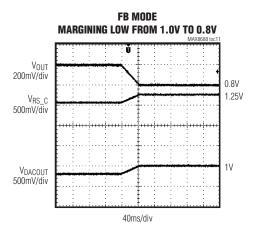

It should be noted that the VOUT\_TRANSITION\_RATE parameter has no effect on FB mode. The transition time for margining in the FB mode of operation is a function of the MFR\_VOUT\_CORRECTION\_RATE parameter, RFB and R<sub>1</sub>, and is given by the following formula:

$$t_{FB} = \frac{R_{FB}}{R_1} \times \frac{\Delta V_{OUT}}{MFR\_VOUT\_CORRECTION\_RATE}$$

Figure 5. Typical System Application—Feedback Mode

Figure 6. Feedback Mode Timing

#### **Current Sensing**

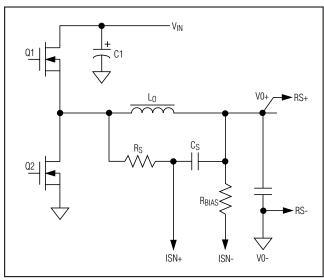

ISN+ and ISN- are the inputs of the MAX8688 currentsense amplifier. These pins may be connected to a current-sense element such as a current-sense resistor, as shown in Figures 3 and 5. The voltage proportional to the sensed current is suitably filtered by an internal  $200\Omega$  resistor and external capacitor connected to ISN\_C and is multiplexed to a 12-bit ADC that uses an accurate internal reference voltage. A scale factor can be programmed with an IOUT\_SCALE PMBus command to translate the sensed voltage information to the current. The MAX8688 accommodates a current-sense range of +40mV/-10mV across the ISN+ and ISNinputs. The common-mode voltage range for the current-sense signal can be between 0 and 5.5V. When a negative current is sensed by the MAX8688, FLT is asserted indicating a negative fault current flow into the POL output.

The DC resistance of the output inductor (DCR) in a switch-mode power supply can also function as a currentsense element, as shown in Figure 7. The RC filter formed by Rs and Cs is designed with a time constant of about 10 times larger than the Lo/DCR time constant. Under these conditions, the DC voltage across Cs is equal to the product of the average current flowing through the output inductor, essentially the output load current and the DCR. The resistor RBIAS equal to RS is placed in the currentsensing path as shown, to cancel the effect of the input bias current voltage drop across Rs.

MIXIM 14

Figure 7. DCR Sensing

#### **Temperature Sensing**

It is intended that the MAX8688 be placed in close proximity to the POL. An on-chip temperature sensor on the MAX8688 senses the temperature of the die, which is related to the exposed pad temperature of the MAX8688 by the junction-to-case thermal resistance. The exposed pad of the MAX8688 can be connected to the heat dissipating ground plane of the POL, and the POL board may be characterized to obtain the relationship between the POL temperature and temperature as measured by the MAX8688. This information may be used to set overtemperature fault settings in the MAX8688.

#### **External EEPROM Interface**

The MAX8688 is capable of communicating with an EEPROM attached to the A1/SCLE and A2/SDAE. The MAX8688 communicates to the EEPROM with an address byte of "1010 0000" for writing and "1010 0001" for reading. For the data values of 2 bytes, the most sig-

nificant byte is stored in the lower offset, whereas the least significant byte is stored in the higher offset.

Upon reset, the MAX8688 tests for the presence of a configuration EEPROM. It searches for the SIGNATURE bytes in the attached EEPROM. If the SIGNATURE bytes are present, it concludes that it has a valid configuration EEPROM and starts reading configuration information from the attached EEPROM. If slave address information is present, this overrides the slave address information previously set by the address A3:A1 pins.

Table 1 shows the contents and offsets of the configuration information expected by the MAX8688. This information is for reference only. It is recommended to use a properly configured, working MAX8688 and to save its state to the EEPROM and limit modifications to as few fields as possible (such as the slave address).

Some 'reserved' fields may contain data other than 0 when the state is saved to the EEPROM. These locations are ignored on restoration from the EEPROM or are frequently recomputed. Some reserved fields need to be set to greater than 0 to guarantee proper operation timing.

Temperature, voltage, and current values are stored in internal representation, which is not identical to the format used by the corresponding PMBus command(s). For details on EEPROM internal representation, see the notes following Table 1.

For example, to store to the EEPROM, VOUT\_COMMAND = 3.0V, m = 19995, b = 0, R = -1. First calculate the PMBus command value, which is 5998. If the voltage range is 2V, no conversion is required. Hence write 17h to offset 14 and 6Eh to offset 15. If the voltage range is 5.5V, the stored EEPROM value = 5998/2.75 = 2181. So at offset 14, write 08h and offset 15, write 85h.

Note that the conversion is automatically handled by the MAX8688 as it restores and stores configuration information into the EEPROM.

#### **Table 1. EEPROM Contents**

| OFFSET (BYTES) | VALUES (Note 8)                                            | PMBus COMMAND | NOTES   |

|----------------|------------------------------------------------------------|---------------|---------|

| 0              | MFR_TEMPERATURE_PEAK                                       | D6h           | Note 9  |

| 2              | MFR_VOUT_PEAK                                              | D4h           | Note 10 |

| 4              | MFR_IOUT_PEAK                                              | D5h           | Note 11 |

| 6              | MFR_STATUS_WORD (set to 0)                                 | D8h           | _       |

| 8–13           | Reserved (set to 0)                                        | _             | _       |

| 14             | VOUT_COMMAND                                               | 21h           | Note 10 |

| 16             | VOUT_SCALE_LOOP                                            | 29h           | _       |

| 18             | TON_RISE                                                   | 61h           | _       |

| 10             | TON_DELAY                                                  | 60h           | _       |

| <del>`</del>   | MFR_TICK_RELOAD                                            |               |         |

| 22             | This value equals to 0FE84h when using the internal clock. | D1h           | _       |

|                | else computed as 65535 - MFR_MODE[15:8]                    |               |         |

| 24             | VOUT_MARGIN_HIGH                                           | 25h           | Note 10 |

| 26             | VOUT_MARGIN_LOW                                            | 26h           | Note 10 |

| 28             | MFR_VOUT_CORRECTION_RATE                                   | D2h           | _       |

| 30             | MFR SAMPLE RATE                                            | D3h           | _       |

| 32             | VOUT_OV_FAULT_LIMIT                                        | 40h           | Note 10 |

| 34             | VOUT_OV_WARN_LIMIT                                         | 42h           | Note 10 |

| 36             | VOUT_UV_FAULT_LIMIT                                        | 44h           | Note 10 |

| 38             | VOUT_UV_WARN_LIMIT                                         | 43h           | Note 10 |

| 40             | IOUT_OC_FAULT_LIMIT                                        | 46h           | Note 11 |

| 42             | IOUT_OC_WARN_LIMIT                                         | 4Ah           | Note 11 |

| 44             | OT_FAULT_LIMIT                                             | 4Fh           | Note 9  |

| 46–53          | Reserved (set to 0)                                        |               |         |

|                | MFR MODE                                                   |               |         |

| 54             | Must match MFR_TICK_RELOAD setting                         | D1h           | _       |

| 56             | MFR_FAULT_RETRY                                            | DAh           | _       |

| 58             | MFR_FAULT_RESPONSE                                         | D9h           | _       |

| 60–63          | Reserved (set to 1)                                        |               | _       |

| 64–71          | Reserved (set to 0)                                        | _             | _       |

| 72             | OT_WARN_LIMIT                                              | 51h           | Note 9  |

| 74             | IOUT SCALE                                                 | 38h           |         |

| 76             | TOFF_DELAY                                                 | 64h           | _       |

| 78             | VOUT_TRANSITION_RATE                                       | 27h           | _       |

| 80             | Reserved (set to 0)                                        |               | _       |

| 82             | MFR_FILTER_MODE                                            | D7h           | _       |

|                | MFR SET ADDRESS                                            |               |         |

| 84             | Low byte: SMBus slave address, high byte: reserved         | DBh           | _       |

| 86             | TOFF FALL                                                  | 65h           | _       |

| 88             | MFR_IOUT_TEMP_COEFF                                        | DCh           | _       |

| 90             | Reserved (set to 0)                                        | _             | _       |

| 92–125         | Reserved (set to 0)                                        | _             | _       |

| 126            | SIGNATURE (set to 4453h)                                   | N/A           | _       |

**Note 8:** For a 2-byte value, the most significant byte is written first (lower offset) and then the least significant byte is written last (higher offset).

Note 9: To store temperature values to the EEPROM, add 3010 (decimal) to the PMBus value.

Note 10: To store voltage values to the EEPROM, no conversion is needed in 2V mode. For 5.5V mode value, divide the PMBus value by 2.75.

Note 11: To store current values to the EEPROM, multiply the PMBus value by IOUT\_SCALE and divide by 37.24.

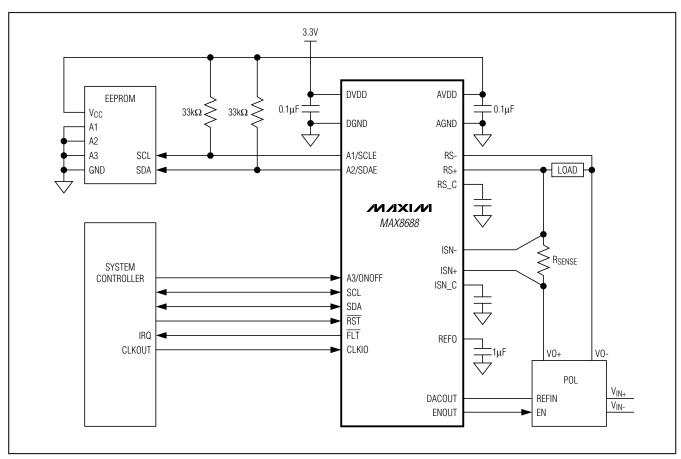

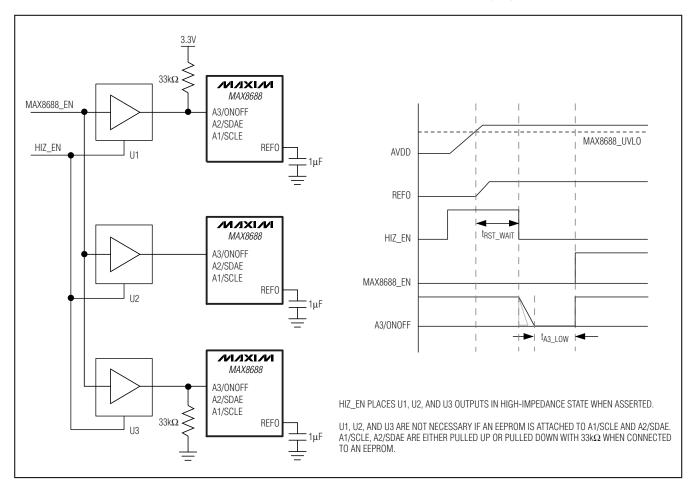

Figure 8 shows how the MAX8688 interfaces to an external serial SOT23 EEPROM (such as Atmel AT24C01A) using the A1/SCLE and A2/SDAE in applications where a master controller does not exist or is not required. Using the GUI, the user can select each MAX8688 device and configure all the required output-voltage settings and sequencing/tracking information. Once the configuration is complete, the results can be saved to the external EEPROM by using the STORE\_DEFAULT\_ALL command and configuration restored on the MAX8688 power-on reset. The EEPROM can also be preprogrammed prior to board assembly in the manufacturing environment. A3/ONOFF can be used as a control signal to turn on/off the POL in a similar fashion as the OPERATION command.

#### **MAX8688 Operation**

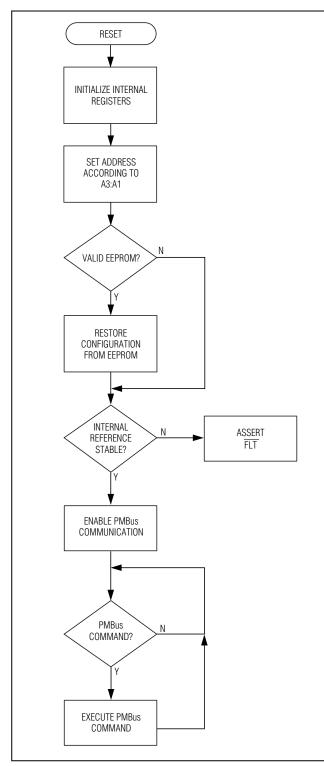

Upon reset (power-on reset or applying the device reset pulse to RST), the MAX8688 goes through an initialization process as shown in Figure 9.

After initialization, the MAX8688 constantly monitors the PMBus and executes the PMBus command accordingly. In addition, if the POL has been commanded to turn on, the MAX8688 also monitors the POL output voltage, current, and temperature at the MFR\_SAMPLE\_RATE. The system controller monitors the POL health by issuing various inquiries and status commands.

Figure 8. Typical System Application with External EEPROM

Figure 9. MAX8688 Initialization

#### **RST** Operation

The RST signal can be used to reset either the SMBus interface or the MAX8688 depending on the RST pulse width. To reset the SMBus interface, the RST signal is held low for tsmb\_Rst. This resets the SMBus interface, thus flushing any pending PMBus commands or portion of commands received thus far. None of the other MAX8688 internal registers are affected by an SMBus reset. If the host controller applies an active-low pulse to RST for treat, the MAX8688 undergoes a device reset and repeats the initialization process.

#### **ENOUT Operation**

To ensure a known and controlled POL power-up state, the MAX8688 is factory-programmed to a specific ENOUT initial power-up state. There are two types of POLs—active-high enable or active-low enable. By default, the MAX8688 assumes that the initial power-up state is the off-state. To operate properly, the POL onstate has to be configured. To configure the ENOUT active state, use the MFR\_MODE command ENOUT Polarity Select.

**Table 2. ENOUT Active State**

| ENOUT DEFAULT<br>STARTUP STATE | ENOUT POLARITY<br>SELECT | ENOUT ACTIVE<br>STATE |

|--------------------------------|--------------------------|-----------------------|

| 0 (Low)                        | 0                        | Active High           |

| 0 (Low)                        | 1                        | Active Low            |

| 1 (High)                       | 0                        | Active Low            |

| 1 (High)                       | 1                        | Active High           |

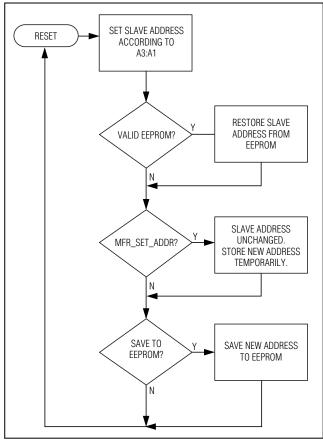

#### **MAX8688 Address Assignment**

The MAX8688 address can be assigned in one of the three ways described below:

- 1) Hardwire by A3:A2:A1.

- 2) Restore from EEPROM.

- By system controller using the MFR\_SET\_ADDRESS command.

Address assignment order is shown in Figure 10.

Figure 10. MAX8688 Address Assignment

The MAX8688 reads A3:A2:A1 address pins upon device reset and determines its address according to Table 3.

For example, to configure the MAX8688 to have a slave address of 010 0101 (25h), set A3:A2:A1 = H:L:Z. The MAX8688 also responds to the broadcast address (00h). While it is possible to configure the address pins such that the resulting address is 00h, the MAX8688 with such address is then only responsive to the broadcast address. This may cause undesired results if other PMBus devices are also present on the same bus. Therefore, the hardwire address pins option give 3<sup>3</sup> - 1 = 26 address options.

If an EEPROM with valid SIGNATURE bytes is attached to the MAX8688, the MAX8688 also tries to restore its slave address from the EEPROM. This overrides the address set by the address pins. This gives a total of 127 useful slave addresses (address 00h is normally for broadcast address). If the address bit 7 from the EEPROM is set to 1, this is an invalid address and the

Table 3. MAX8688 A3:A1 Address Assignment

| A3/ONOFF | A2/SDAE | A1/SCLE | ADDRESS |

|----------|---------|---------|---------|

| L        | L       | L       | 00h*    |

| L        |         | Z       | 01h**   |

| L        | Z       | L       | 02h     |

| L        | Z       | Z       | 03h     |

| Z        | L       | L       | 04h     |

| Z        | L       | Z       | 05h     |

| Z        | Z       | L       | 06h     |

| Z        | Z       | Z       | 07h     |

| L        | L       | Н       | 09h     |

| L        | Z       | Н       | 0Bh     |

| Z        | L       | Н       | 0Dh     |

| Z        | Z       | Н       | 0Fh     |

| L        | Н       | L       | 12h     |

| L        | Н       | Z       | 13h     |

| Z        | Н       | L       | 16h     |

| Z        | Н       | Z       | 17h     |

| L        | Н       | Н       | 1Bh     |

| Z        | Н       | Н       | 1Fh     |

| Н        | L       | L       | 24h     |

| Н        | L       | Z       | 25h     |

| Н        | Z       | L       | 26h     |

| Н        | Z       | Z       | 27h     |

| Н        | L       | Н       | 2Dh     |

| Н        | Z       | Н       | 2Fh     |

| Н        | Н       | L       | 36h     |

| Н        | Н       | Z       | 37h     |

| Н        | Н       | Н       | 3Fh     |

<sup>\*</sup>The address 00h is reserved for broadcast.

MAX8688 continues using the address set by the address pins. When an EEPROM is attached to A2/SDAE and A1/SCLE, these pins assume either a logic-high or logic-low level, therefore, the resulting number of possible addresses set by the A3:A2:A1 pins in this scenario is  $2^3$  - 1 = 7.

In addition, for the MAX8688 with an EEPROM attached, the system controller can change the MAX8688 slave address by sending the new address with the MFR\_SET\_ADDRESS command. However, the new address is not immediately effective. The new address must be stored to the EEPROM first. Then, a device reset has to be applied to the MAX8688 which undergoes the address assignment procedure and recalls the new address from the EEPROM.

<sup>\*\*</sup>The shaded addresses are not available if an external EEPROM is attached.

#### A3/ONOFF Operation

In addition to providing address information to the MAX8688, A3/ONOFF can also be used as a control signal for turning the POL on or off, similar to the OPERATION command. To use A3/ONOFF to control the POL, configure the A3 Control Enable bit in MFR\_MODE command.

When A3 control is enabled, a transition of A3/ONOFF from low to high turns the POL on, as if the MAX8688 has received an OPERATION ON command. A transition of A3/ONOFF from high to low initiates a soft-off to the POL—as if the MAX8688 has received an OPERATION OFF command (soft-off, with sequencing). The MAX8688 still responds to the PMBus OPERATION command while A3 control is enabled. To detect the A3/ONOFF input, the A3/ONOFF signal pulse width has to satisfy the tA3\_LOW and tA3\_HIGH requirement to be detected. If disabled (cleared to 0), the MAX8688 ignores the

A3/ONOFF state and function as directed by the OPER-ATION command only.

The dual functionality of A3/ONOFF of the MAX8688 requires the system enable signal to be isolated from A3/ONOFF until the address setting has been read and latched by the MAX8688. Figure 11 shows one implementation for the three possible states of the A3/ONOFF setting. In each case, the system enable signal (MAX8688\_EN) is applied to the input of a threestate buffer whose output is kept in the high-impedance state by a control input signal (HIZ EN) for a time period during which the MAX8688 reads and latches the A3/ONOFF address setting. After this period, the control signal HIZ EN goes low and allows the system enable signal to be applied to the MAX8688 A3/ONOFF pin. After a tag Low, the MAX8688\_EN signal transitions from low to high and causes the MAX8688s to commence POL startup operations.

Figure 11. Application Diagram with A3/ONOFF as Both Address and On/Off Control Signal

20 /V/X//V

#### **PMBus Digital Interface**

From a software perspective, the MAX8688 appears as a PMBus device capable of executing a subset of PMBus commands. A PMBus 1.0-compliant device uses the SMBus version 1.1 for transport protocol and responds to the SMBus slave address. In this data sheet, the term SMBus is used to refer to the electrical characteristics of the PMBus communication using the SMBus physical layer. The term PMBus is used to refer to the PMBus command protocol.

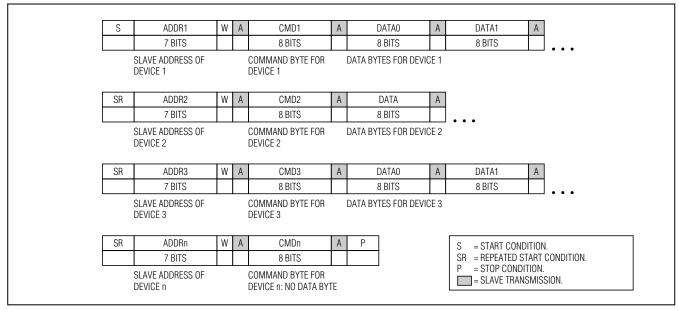

The MAX8688 employs five standard SMBus protocols (Write Word, Read Word, Write Byte, Read Byte and Send Byte (see Figures 12–15)) to program output voltage and warning/faults thresholds, read monitored data, and provide access to all manufacturer-specific commands.

The MAX8688 also supports the group command. The group command is used to send commands to more than one PMBus device. It is not required that all the devices receive the same command. However, no more than one command can be sent to any one device in one group command packet. The group command must not be used with commands that require receiving devices to respond with data, such as the STATUS\_BYTE command. When the MAX8688 receives a command through this protocol, it immediately begins execution of the received command after detecting the STOP condition.

When the data word is transmitted, the lower order byte is sent first and the higher order byte is sent last. Within any byte, the most significant bit (MSB) is sent first and the least significant bit (LSB) is sent last.

|                | ADDR                            | W    | Α        | COMMAND                                                                     | Α |    | DATA A                                                                  | Р    |          |                                      |              |     |        |        |     |   |

|----------------|---------------------------------|------|----------|-----------------------------------------------------------------------------|---|----|-------------------------------------------------------------------------|------|----------|--------------------------------------|--------------|-----|--------|--------|-----|---|

|                | 7 BITS                          |      |          | 8 BITS                                                                      | П |    | 8 BITS                                                                  |      | 1        |                                      |              |     |        |        |     |   |

|                | SLAVE ADDRESS                   |      |          | COMMAND BYTE:<br>SELECTS WHICH<br>COMMAND PARAMETE<br>TO WRITE TO           |   |    | TE: DATA FOR THE CO                                                     | AMMC | ND       | )                                    |              |     |        |        |     |   |

|                | YTE FORMAT                      |      | _        |                                                                             | _ |    |                                                                         |      | _        |                                      |              | _   |        | 1      |     |   |

| S              | ADDR                            | W    | Α        | COMMAND                                                                     | Α | SR | ADDR                                                                    | R    |          | A DATA                               |              | NA  | Р      |        |     |   |

|                | 7 BITS                          |      | <u> </u> | 8 BITS                                                                      |   |    | 7 BITS                                                                  |      |          | 8 BIT                                | 3            |     |        |        |     |   |

| VDITE:         | SLAVE ADDRESS                   |      |          | COMMAND BYTE:<br>SELECTS WHICH<br>COMMAND PARAMETEI<br>TO READ FROM         | R |    | SLAVE ADDRESS:<br>REPEATED DUE TO<br>CHANGE IN DATA-FLI<br>DIRECTION    | OW   |          | DATA BYTE: D<br>SET BY THE C         |              |     |        | ND     |     |   |

|                | WORD FORMAT                     | Lvar |          | 001414110                                                                   |   |    | DATAS A                                                                 |      | <u> </u> | ATA4 A                               | Р            | 1   |        |        |     |   |

| S              | ADDR<br>7 BITS                  | W    | А        | COMMAND<br>8 BITS                                                           | Α |    | DATAO A 8 BITS                                                          |      |          | ATA1 A                               | P            | -   |        |        |     |   |

|                | SLAVE ADDRESS                   |      |          | COMMAND BYTE:<br>SELECTS WHICH<br>COMMAND PARAMETE<br>TO WRITE TO           |   |    | TE: DATA FOR THE CO<br>ND BYTE                                          | AMM  | ND       | ) SET BY THE                         |              |     |        |        |     |   |

|                | ACCE FORMAT                     |      |          |                                                                             |   |    |                                                                         |      |          | A DATA                               | 0            | Α   |        | DATA1  |     |   |

|                | VORD FORMAT                     | 14/  | _        | COMMAND                                                                     | ٨ | CD | ADDD                                                                    | D    |          | A DATA                               |              |     |        |        | NIA | D |

| R <b>ead V</b> | ADDR                            | W    | Α        | COMMAND<br>8 RITS                                                           | А | SR | ADDR<br>7 RITS                                                          | R    | ľ        | _                                    | -            | А   |        |        | NA  | Р |

|                |                                 | W    |          | COMMAND  8 BITS  COMMAND BYTE: SELECTS WHICH COMMAND PARAMETE! TO READ FROM |   | -  | ADDR 7 BITS SLAVE ADDRESS: REPEATED DUE TO CHANGE IN DATA-FLI DIRECTION |      |          | 8 BITS<br>DATA BYTE: D<br>COMMAND BY | S<br>ATA FOR |     |        | 8 BITS |     | P |

| S              | ADDR<br>7 BITS                  | W    |          | 8 BITS COMMAND BYTE: SELECTS WHICH COMMAND PARAMETE                         |   | -  | 7 BITS SLAVE ADDRESS: REPEATED DUE TO CHANGE IN DATA-FLI                |      |          | 8 BIT:<br>DATA BYTE: D               | S<br>ATA FOR |     |        | 8 BITS |     | P |

| S              | ADDR<br>7 BITS<br>SLAVE ADDRESS | W    |          | 8 BITS COMMAND BYTE: SELECTS WHICH COMMAND PARAMETE                         |   | -  | 7 BITS SLAVE ADDRESS: REPEATED DUE TO CHANGE IN DATA-FLI                |      |          | 8 BIT:<br>DATA BYTE: D<br>COMMAND BY | S<br>ATA FOR | THE | COMMAN | 8 BITS |     | P |

Figure 12. SMBus Protocols

Figure 13. SMBus Group Command Protocol

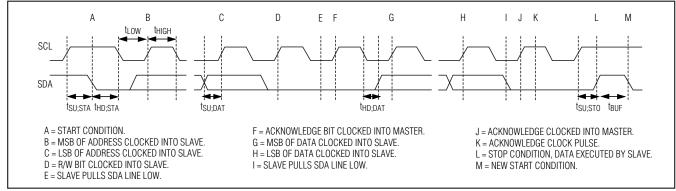

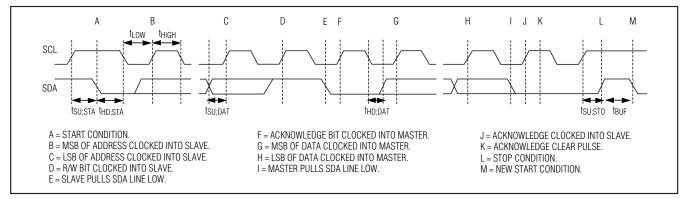

Figure 14. SMBus Write Timing Diagram

Figure 15. SMBus Read Timing Diagram

The MAX8688 SMBus interface does not support packet error checking (PEC). It does not support the 35ms timeout either. Therefore, to reset the MAX8688 SMBus interface, the host controller has to hold  $\overline{RST}$  low for tSMB\_RST. This resets the SMBus interface. See the  $\overline{RST}$  Operation section.

#### **PMBus Protocol Support**

The MAX8688 supports a subset of the commands defined in the Power System Management Protocol Specification Part II - Command Language Revision 1.0. For detailed specifications and the complete list of PMBus commands, refer to Part II of the PMBus specification available at <a href="https://www.PMBus.org">www.PMBus.org</a>. The supported PMBus commands and the corresponding MAX8688 behavior are described in this document.

All data values are represented in DIRECT format, unless otherwise stated. Whenever the resolution of the data is less than the number of bits required, data are right justified (only the lower bits are significant) and the higher order bits are zero-padded, unless otherwise

stated. For example, for a 2-byte value where the MAX8688 only has 12-bit data to return, the MAX8688 returns data in the lower 12 bits and zero-padded the upper 4 bits. Whenever the PMBus specification refers to the "PMBus device," it is referring to MAX8688 operating in conjuction with a POL device. While the command may call for turning on or off the PMBus device, the MAX8688 always remains on to continue communicating with the PMBus master and the MAX8688 transfers the command to the POL device accordingly.

#### **Data Format**

Voltage data for commanding or reading the output voltage or related parameters (such as the overvoltage threshold) are presented in DIRECT format. DIRECT format data is a 2-byte, two's complement binary value. DIRECT format data may be used with any command that sends or reads a parametric value. The DIRECT format uses an equation and defined coefficients to calculate the desired values. The coefficients used by the MAX8688 can be found in Table 4.

Table 4. MAX8688 PMBus Command Summary

|    | COMMAND<br>CODE | COMMAND NAME         | TRANSACTION<br>TYPE | NO. OF<br>BYTES | m     | b   | R  |

|----|-----------------|----------------------|---------------------|-----------------|-------|-----|----|

| 1  | 01h             | OPERATION            | R/W Byte            | 1               | _     | _   | _  |

| 2  | 03h             | CLEAR_FAULTS         | Send Byte           | 0               |       | _   | _  |

| 3  | 11h             | STORE_DEFAULT_ALL    | Send Byte           | 0               | _     | _   | _  |

| 4  | 12h             | RESTORE_DEFAULT_ALL  | Send Byte           | 0               | _     | _   | _  |

| 5  | 21h             | VOUT_COMMAND         | R/W Word            | 2               | 19995 | 0   | -1 |

| 6  | 25h             | VOUT_MARGIN_HIGH     | R/W Word            | 2               | 19995 | 0   | -1 |

| 7  | 26h             | VOUT_MARGIN_LOW      | R/W Word            | 2               | 19995 | 0   | -1 |

| 8  | 27h             | VOUT_TRANSITION_RATE | R/W Word            | 2               | 256   | 0   | 0  |

| 9  | 29h             | VOUT_SCALE_LOOP      | R/W Word            | 2               | 128   | 0   | 0  |

| 10 | 38h             | IOUT_SCALE           | R/W Word            | 2               | 1     | 0   | 1  |