# DS2432 1Kb Protected 1-Wire EEPROM with SHA-1 Engine

#### **FEATURES**

- 1128 Bits of 5V EEPROM Memory Partitioned Into Four Pages of 256 Bits, a 64-Bit Write-Only Secret, and Up to Five General-Purpose Read/Write Registers

- On-Chip 512-Bit ISO/IEC 10118-3 SHA-1 Engine to Compute 160-Bit Message Authentication Codes (MACs) and to Generate Secrets

- Write Access Requires Knowledge of the Secret and the Capability of Computing and Transmitting a 160-Bit MAC as Authorization

- Secret and Data Memory Can Be Write Protected (All or Page 0 Only) or Put in EPROM-Emulation Mode ("Write to 0", Page 1)

- Unique, Factory-Lasered and Tested 64-Bit Registration Number Assures Absolute Traceability Because No Two Parts Are Alike

- Built-In Multidrop Controller Ensures Compatibility with Other 1-Wire<sup>®</sup> Net Products

- Reduces Control, Address, Data, and Power to a Single Data Pin

- Directly Connects to a Single Port Pin of a Microprocessor and Communicates at Up to 15.3kbps

- Overdrive Mode Boosts Communication Speed to 90.9kbps

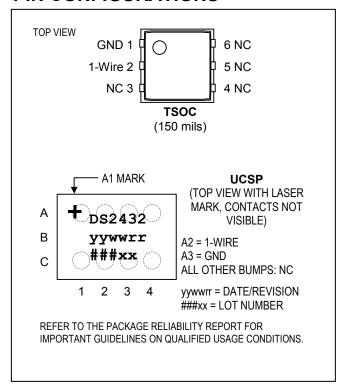

- Low-Cost 6-Lead TSOC Surface-Mount Package or Solder-Bumped UCSP<sup>TM</sup> Package

- Reads and Writes Over a Wide Voltage Range of 2.8V to 5.25V from -40°C to +85°C

#### PIN CONFIGURATIONS

#### ORDERING INFORMATION

| PART        | TEMP           | PIN-         |

|-------------|----------------|--------------|

| TAKI        | RANGE          | PACKAGE      |

| DS2432P+    | -40°C to +85°C | 6 TSOC       |

| DS2432P+T&R | -40°C to +85°C | 6 TSOC       |

| DS2432X-S+  | -40°C to +85°C | 8 UCSP (2.5k |

| DS2432A-ST  | -40 C W 783 C  | pcs, T&R)    |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. T&R = Tape and reel.

#### **Request Full Data Sheet at:**

www.maximintegrated.com/DS2432

1-Wire is a registered trademark and UCSP is a trademark of Maxim Integrated Products, Inc.

#### DESCRIPTION

The DS2432 combines 1024 bits of EEPROM, a 64-bit secret, an 8-byte register/control page with up to five user read/write bytes, a 512-bit SHA-1 engine, and a fully-featured 1-Wire interface in a single chip. Each DS2432 has its own 64-bit ROM registration number that is factory lasered into the chip to provide a guaranteed unique identity for absolute traceability. Data is transferred serially via the 1-Wire protocol, which requires only a single data lead and a ground return. The DS2432 has an additional memory area called the scratchpad that acts as a buffer when writing to the main memory, the register page or when installing a new secret. Data is first written to the scratchpad from where it can be read back. After the data has been verified, a copy scratchpad command will transfer the data to its final memory location, provided that the DS2432 receives a matching 160-Bit MAC. The computation of the MAC involves the secret and additional data stored in the DS2432 including the device's registration number. Only a new secret can be loaded without providing a MAC. The SHA-1 engine can also be activated to compute 160-bit message authentication codes (MAC) when reading a memory page or to compute a new secret, instead of loading it. Applications of the DS2432 include intellectual property security, after-market management of consumables, and tamper-proof data carriers.

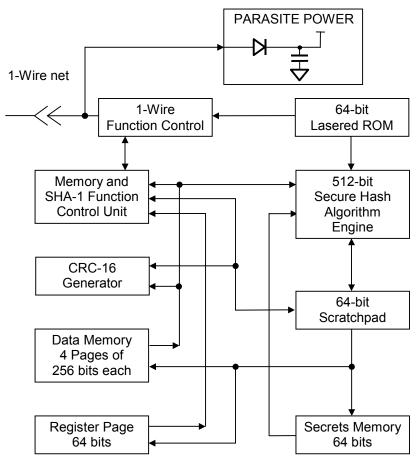

#### **OVERVIEW**

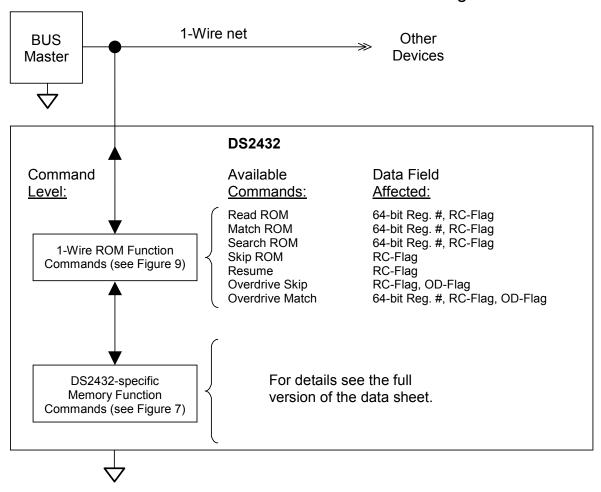

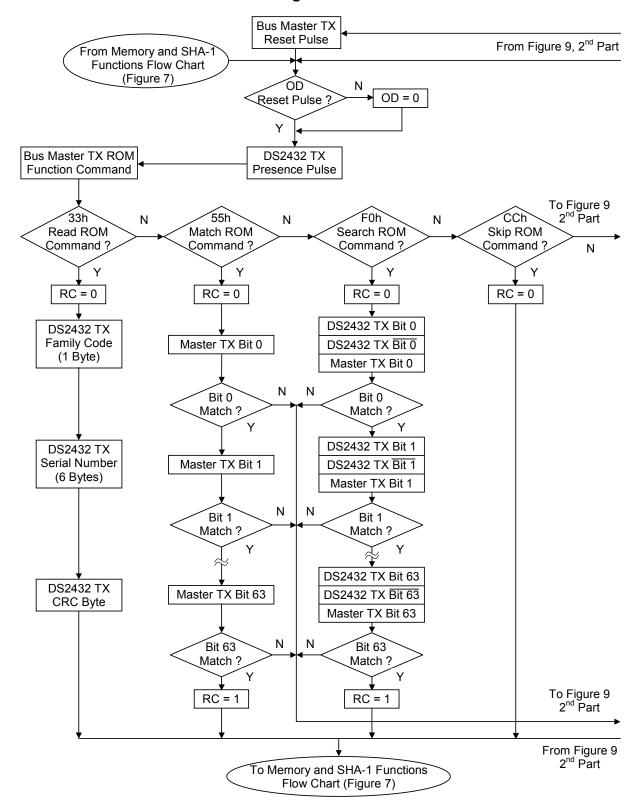

The block diagram in Figure 1 shows the relationships between the major control and memory sections of the DS2432. The DS2432 has five main data components: 1) 64-bit lasered ROM, 2) 64-bit scratchpad, 3) four 32-byte pages of EEPROM, 4) 64-bit register page, 5) 64-bit Secrets Memory, and 6) a 512-bit SHA-1 Engine (SHA = Secure Hash Algorithm). The hierarchical structure of the 1-Wire protocol is shown in Figure 2. The bus master must first provide one of the seven ROM Function Commands, 1) Read ROM, 2) Match ROM, 3) Search ROM, 4) Skip ROM, 5) Resume Communication, 6) Overdrive-Skip ROM or 7) Overdrive-Match ROM. Upon completion of an Overdrive ROM command byte executed at regular speed, the device will enter Overdrive mode where all subsequent communication occurs at a higher speed. The protocol required for these ROM function commands is described in Figure 9. After a ROM function command is successfully executed, the memory and SHA-1 functions become accessible and the master may provide any one of the seven memory function commands. The protocol for these memory function commands is described in Figure 7\*. All data is read and written least significant bit first.

\_

<sup>\*</sup> For Figure 7, refer to the full version of the data sheet.

# **DS2432 BLOCK DIAGRAM** Figure 1

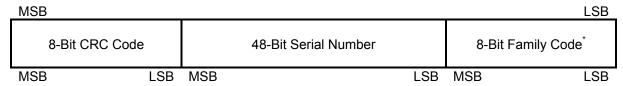

#### 64-BIT LASERED ROM

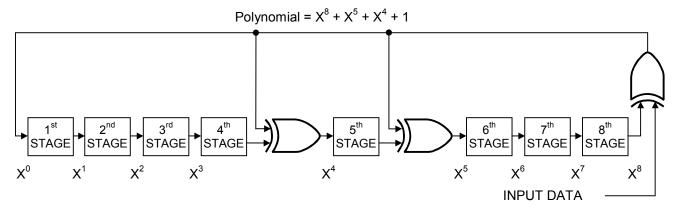

Each DS2432 contains a unique ROM code that is 64 bits long. The first eight bits are a 1-Wire family code. The next 48 bits are a unique serial number. The last eight bits are a CRC of the first 56 bits. (See Figure 3.) The 1-Wire CRC is generated using a polynomial generator consisting of a shift register and XOR gates as shown in Figure 4. The polynomial is  $X^8 + X^5 + X^4 + 1$ . Additional information about the 1-Wire Cyclic Redundancy Check is available in Application Note 27. The shift register bits are initialized to zero. Then starting with the least significant bit of the family code, one bit at a time is shifted in. After the 8<sup>th</sup> bit of the family code has been entered, then the serial number is entered. After the 48<sup>th</sup> bit of the serial number has been entered, the shift register contains the CRC value. Shifting in the eight bits of CRC should return the shift register to all zeros.

### **HIERARCHCAL STRUCTURE FOR 1-Wire PROTOCOL** Figure 2

## **64-BIT LASERED ROM** Figure 3

<sup>\*</sup>For the actual Family Code value, refer to the full version of the data sheet.

### **1-Wire CRC GENERATOR** Figure 4

#### **MEMORY MAP**

The DS2432 has four memory areas: data memory, secrets memory, register page with special function registers and user-bytes, and a scratchpad. The data memory is organized in pages of 32 bytes. Secret, register page and scratchpad are 8 bytes each. The scratchpad acts as a buffer when writing to the data memory, loading the initial secret or when writing to the register page. For further details (including Figure 5) refer to the full version of the data sheet.

#### ADDRESS REGISTERS AND TRANSFER STATUS

The DS2432 employs three address registers: TA1, TA2 and E/S (Figure 6). These registers are common to many other 1-Wire devices but operate slightly differently with the DS2432. Registers TA1 and TA2 must be loaded with the target address to which the data will be written or from which data will be read. Register E/S is a read-only transfer-status register, used to verify data integrity with write commands. Since the scratchpad of the DS2432 is designed to accept data in blocks of eight bytes only, the lower three bits of TA1 will be forced to 0 and the lower three bits of the E/S register (Ending Offset) will always read 1. This indicates that all the data in the scratchpad will be used for a subsequent copying into main memory or secret. Bit 5 of the E/S register, called PF or "partial byte flag", is a logic-1 if the number of data bits sent by the master is not an integer multiple of 8 or if the data in the scratchpad is not valid due to a loss of power. A valid write to the scratchpad will clear the PF bit. Bits 3, 4 and 6 have no function; they always read 1. The Partial Flag supports the master checking the data integrity after a Write command. The highest valued bit of the E/S register, called AA or Authorization Accepted, acts as a flag to indicate that the data stored in the scratchpad has already been copied to the target memory address. Writing data to the scratchpad clears this flag.

# **ADDRESS REGISTERS** Figure 6

| Bit #                                                   | 7   | 6   | 5   | 4   | 3   | 2         | 1         | 0         |

|---------------------------------------------------------|-----|-----|-----|-----|-----|-----------|-----------|-----------|

| Target Address (TA1)                                    | Т7  | Т6  | T5  | T4  | Т3  | T2<br>(0) | T1<br>(0) | T0<br>(0) |

| Target Address (TA2)                                    | T15 | T14 | T13 | T12 | T11 | T10       | Т9        | Т8        |

| Ending Address with<br>Data Status (E/S)<br>(Read Only) | AA  | 1   | PF  | 1   | 1   | E2<br>(1) | E1<br>(1) | E0<br>(1) |

#### WRITING WITH VERIFICATION

To write data to the DS2432, the scratchpad has to be used as intermediate storage. First the master issues the Write Scratchpad command to specify the desired target address, followed by the data to be written to the scratchpad. Note that writes to data memory must be performed on 8-byte boundaries with the 3 LSBs of the target address (T2..T0) equal to 000b. If T2..T0 are sent with non-zero values, the device will set these bits to zero and will write to the modified address upon completion of the command sequence. In addition, the entire 8-byte scratchpad will be copied to memory when commanded, therefore eight bytes of data should be written into the scratchpad to ensure that the data to be copied is known. Under certain conditions (see the Write Scratchpad command) the master will receive an inverted CRC-16 of the command, address (actual address sent) and data at the end of the write scratchpad command sequence. Note that the CRC is calculated based on the actual target address sent and not the modified address in the case of a non-zero T2..T0. Knowing this CRC value, the master can compare it to the value it has calculated itself to decide if the communication was successful and proceed to the Copy Scratchpad command. If the master could not receive the CRC-16, it should send the Read Scratchpad command to verify data integrity. As preamble to the scratchpad data, the DS2432 repeats the target address TA1 and TA2 and sends the contents of the E/S register. If the PF flag is set, data did not arrive correctly in the scratchpad or there was a loss of power since data was last written to the scratchpad. The master does not need to continue reading; it can start a new trial to write data to the scratchpad. Similarly, a set AA flag together with a cleared PF flag indicates that the device did not recognize the Write command. If everything went correctly, both flags are cleared. Now the master can continue reading and verifying every data byte. After the master has verified the data, it can send the Copy Scratchpad command, for example. This command must be followed exactly by the data of the three address registers TA1, TA2 and E/S. The master should obtain the contents of these registers by reading the scratchpad.

#### **MEMORY AND SHA-1 FUNCTION COMMANDS**

This section describes the commands and flow charts to use the memory and SHA-1 engine of the device. It includes Tables 1 to 4 and Figure 7. Please refer to the full version of the data sheet.

#### SHA-1 COMPUTATION ALGORITHM

The SHA-1 computation is adapted from the Secure Hash Standard SHA-1 document as it can be downloaded from the NIST website (http://www.itl.nist.gov/fipspubs/fip180-1.htm). Further details are found in the full version of the data sheet.

#### 1-Wire BUS SYSTEM

The 1-Wire bus is a system, which has a single bus master and one or more slaves. In all instances the DS2432 is a slave device. The bus master is typically a microcontroller. The discussion of this bus system is broken down into three topics: hardware configuration, transaction sequence, and 1-Wire signaling (signal types and timing). A 1-Wire protocol defines bus transactions in terms of the bus state during specific time slots that are initiated on the falling edge of sync pulses from the bus master.

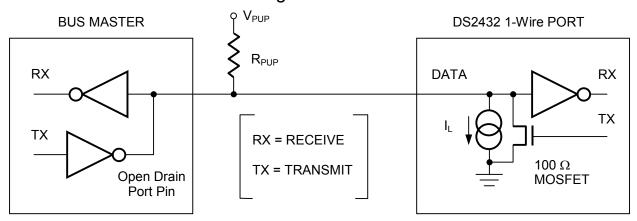

#### HARDWARE CONFIGURATION

The 1-Wire bus has only a single line by definition; it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must have open drain or 3-state outputs. The 1-Wire port of the DS2432 is open drain with an internal circuit equivalent to that shown in Figure 8. A multidrop bus consists of a 1-Wire bus with multiple slaves attached. At regular speed the 1-Wire bus has a maximum data rate of 15.3kbps. The speed can be boosted to 90.9kbps by activating the Overdrive Mode. The DS2432 requires a 1-Wire pullup resistor of maximum 2.2 k $\Omega$  for executing any of its memory and SHA-1 function commands at any speed. When communicating with several DS2432 simultaneously, e.g., to install the same secret in several devices, the resistor should be bypassed by a low-impedance pullup to  $V_{PUP}$  while the device transfers data from the scratchpad to the EEPROM.

The idle state for the 1-Wire bus is high. If for any reason a transaction needs to be suspended, the bus MUST be left in the idle state if the transaction is to resume. If this does not occur and the bus is left low for more than 16  $\mu$ s (Overdrive Speed) or more than 120  $\mu$ s (regular speed), one or more devices on the bus may be reset.

## **HARDWARE CONFIGURATION** Figure 8

#### TRANSACTION SEQUENCE

The protocol for accessing the DS2432 via the 1-Wire port is as follows:

- Initialization

- ROM Function Command

- Memory or SHA-1 Function Command

- Transaction/Data

#### INITIALIZATION

All transactions on the 1-Wire bus begin with an initialization sequence. The initialization sequence consists of a reset pulse transmitted by the bus master followed by presence pulse(s) transmitted by the slave(s). The presence pulse lets the bus master know that the DS2432 is on the bus and is ready to operate. For more details, see the *1-Wire Signaling* section.

#### **ROM FUNCTION COMMANDS**

Once the bus master has detected a presence, it can issue one of the seven ROM function commands that the DS2432 supports. All ROM function commands are eight bits long. A list of these commands follows (refer to flowchart in Figure 9):

#### Read ROM [33h]

This command allows the bus master to read the DS2432's 8-bit family code, unique 48-bit serial number, and 8-bit CRC. This command should only be used if there is a single slave on the bus. If more than one slave is present on the bus, a data collision will occur when all slaves try to transmit at the same time (open drain will produce a wired-AND result). The resultant family code and 48-bit serial number read by the master will be invalid.

#### Match ROM [55h]

The match ROM command, followed by a 64-bit registration number, allows the bus master to address a specific DS2432 on a multidrop bus. Only the DS2432 that exactly matches the 64-bit registration number will respond to the following memory function command. All other slaves will wait for a reset pulse. This command can be used with a single or multiple devices on the bus.

#### Search ROM [F0h]

When a system is initially brought up, the bus master might not know the number of devices on the 1-Wire bus or their 64-bit registration numbers. The search ROM command allows the bus master to use a process of elimination to identify the 64-bit numbers of all slave devices on the bus. The search ROM process is the repetition of a simple 3-step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this 3-step routine on each bit of the registration number. After one complete pass, the bus master knows the 64-bit number of one device. Additional passes will identify the registration numbers of the remaining devices. Refer to Application Note 187 for a detailed discussion of a search ROM, including an actual example.

### Skip ROM [CCh]

This command can save time in a single drop bus system by allowing the bus master to access the memory and SHA-1 functions without providing the 64-bit registration number. If more than one slave is present on the bus and, for example, a read command is issued following the Skip ROM command, data collision will occur on the bus as multiple slaves transmit simultaneously (open-drain pulldowns will produce a wired-AND result).

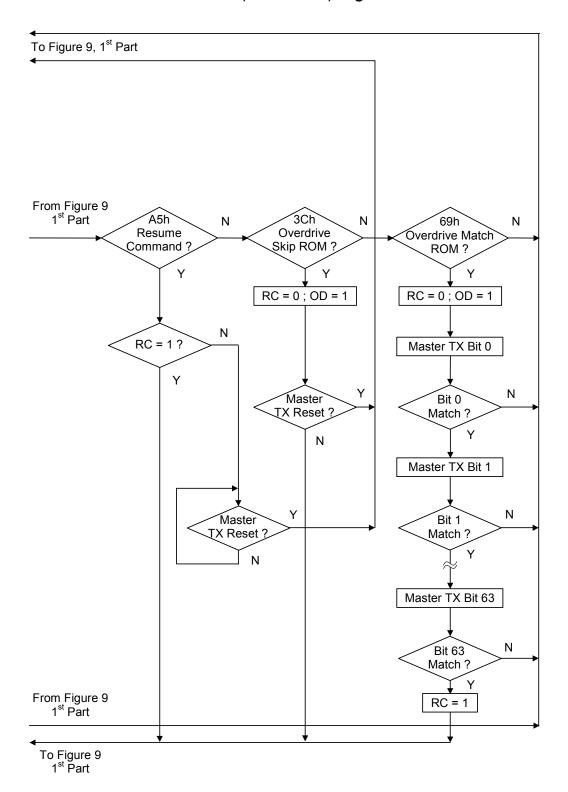

### Overdrive Skip ROM [3Ch]

On a single-drop bus this command can save time by allowing the bus master to access the memory and SHA-1 functions without providing the 64-bit registration number. Unlike the normal Skip ROM command the Overdrive Skip ROM sets the DS2432 in the Overdrive Mode (OD = 1). All communication following this command code has to occur at Overdrive Speed until a reset pulse of minimum 480  $\mu$ s duration resets all devices on the bus to regular speed (OD = 0).

When issued on a multidrop bus this command will set all Overdrive-supporting devices into Overdrive mode. To subsequently address a specific Overdrive-supporting device, a reset pulse at Overdrive speed has to be issued followed by a Match ROM or Search ROM command sequence. This will speed up the search process. If more than one Overdrive-supporting slave is present on the bus and the Overdrive Skip ROM command is followed by a read command, data collision will occur on the bus as multiple slaves transmit simultaneously (open drain pulldowns will produce a wired-AND result).

## **ROM FUNCTIONS FLOW CHART Figure 9**

# ROM FUNCTIONS FLOW CHART (continued) Figure 9

#### Overdrive Match ROM [69h]

The Overdrive Match ROM command, followed by a 64-bit registration number transmitted at Overdrive Speed, allows the bus master to address a specific DS2432 on a multidrop bus and to simultaneously set it in Overdrive Mode. Only the DS2432 that exactly matches the 64-bit number will respond to the subsequent memory or SHA-1 function command. Slaves already in Overdrive mode from a previous Overdrive Skip or a successful Overdrive Match command will remain in Overdrive mode. All Overdrive-capable slaves will return to regular speed at the next Reset Pulse of minimum 480 µs duration. The Overdrive Match ROM command can be used with a single or multiple devices on the bus.

### **Resume Command [A5h]**

In a typical application the DS2432 needs to be accessed several times to write a full 32-byte page. In a multidrop environment this means that the 64-bit registration number of a Match ROM command has to be repeated for every access. To maximize the data throughput in a multidrop environment the Resume Command function was implemented. This function checks the status of the RC bit and, if it is set, directly transfers control to the Memory and SHA-1 functions, similar to a Skip ROM command. The only way to set the RC bit is through successfully executing the Match ROM, Search ROM or Overdrive Match ROM command. Once the RC bit is set, the device can repeatedly be accessed through the Resume Command function. Accessing another device on the bus will clear the RC bit, preventing two or more devices from simultaneously responding to the Resume Command function.

#### 1-Wire SIGNALING

The DS2432 requires strict protocols to ensure data integrity. The protocol consists of four types of signaling on one line: Reset Sequence with Reset Pulse and Presence Pulse, Write 0, Write 1 and Read Data. Except for the presence pulse the bus master initiates all these signals. The DS2432 can communicate at two different speeds, regular speed and Overdrive Speed. If not explicitly set into the Overdrive mode, the DS2432 will communicate at regular speed. While in Overdrive Mode the fast timing applies to all waveforms.

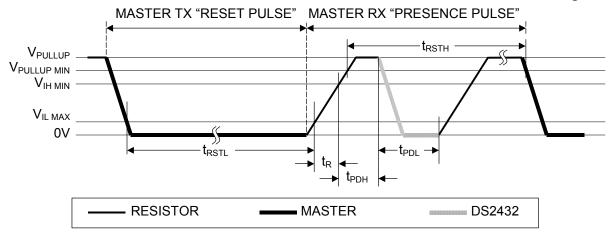

The initialization sequence required to begin any communication with the DS2432 is shown in Figure 10. A Reset Pulse followed by a Presence Pulse indicates the DS2432 is ready to send or receive data. The bus master transmits (TX) a reset pulse ( $t_{RSTL}$ , minimum 480  $\mu$ s at regular speed, 48  $\mu$ s at Overdrive Speed). The bus master then releases the line and goes into receive mode (RX). The 1-Wire bus is pulled to a high state via the pullup resistor. After detecting the rising edge on the data pin, the DS2432 waits ( $t_{PDH}$ , 15-60  $\mu$ s at regular speed, 2-6  $\mu$ s at Overdrive speed) and then transmits the Presence Pulse ( $t_{PDL}$ , 60-240  $\mu$ s at regular speed, 8-24  $\mu$ s at Overdrive Speed). A Reset Pulse of 480  $\mu$ s or longer will exit the Overdrive Mode returning the device to regular speed. If the DS2432 is in Overdrive Mode and the Reset Pulse is no longer than 80  $\mu$ s the device will remain in Overdrive Mode.

## INITIALIZATION PROCEDURE "RESET AND PRESENCE PULSES" Figure 10

#### **Read/Write Time Slots**

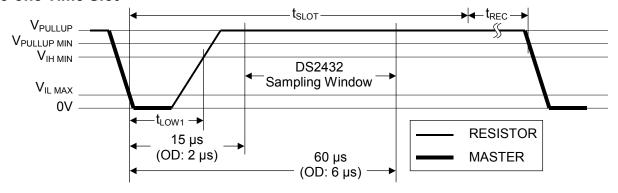

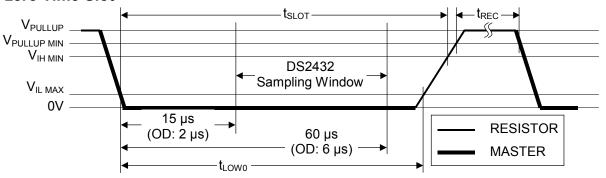

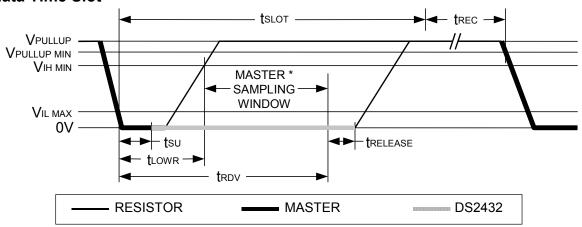

The definitions of write and read time slots are illustrated in Figure 11. The master initiates all time slots by driving the data line low. The falling edge of the data line synchronizes the DS2432 to the master by triggering an internal delay circuit. During write time slots, the delay circuit determines when the DS2432 will sample the data line. For a read data time slot, if a "0" is to be transmitted, the delay circuit determines how long the DS2432 will hold the data line low. If the data bit is a "1", the DS2432 will not hold the data line low at all.

## **READ/WRITE TIMING DIAGRAM** Figure 11

#### Write-one Time Slot

#### Write-zero Time Slot

### **READ/WRITE TIMING DIAGRAM** Figure 11 (continued)

#### **Read-data Time Slot**

<sup>\*</sup>The optimal sampling point for the master is as close as possible to the end time of the  $t_{RDV}$  period without exceeding  $t_{RDV}$ . For the case of a Read-one time slot, this maximizes the amount of time for the pullup resistor to recover the line to a high level. For a Read-zero time slot it ensures that a read will occur before the fastest 1-Wire device releases the line ( $t_{RELEASE} = 0$ ).

#### **CRC GENERATION**

With the DS2432 there are two different types of CRCs (Cyclic Redundancy Checks). One CRC is an 8-bit type. It is computed at the factory and lasered into the most significant byte of the 64-bit ROM. The equivalent polynomial function of this CRC is  $X^8 + X^5 + X^4 + 1$ . To determine whether the ROM data has been read without error the bus master can compute the CRC value from the first 56 bits of the 64-bit ROM and compare it to the value read from the DS2432. This 8-bit CRC is received in the true form (non-inverted) when reading the ROM.

The other CRC is a 16-bit type, which is used for error detection with Memory and SHA-1 function commands. For details (including Figure 12), refer to the full version of the data sheet.

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range on Any Pin Relative to Ground Operating Temperature Range Storage Temperature Range Lead Temperature (TSOC only; soldering, 10s) Soldering Temperature (reflow) -0.5V to +5.5V -40°C to +85°C -55°C to +125°C +300°C

+260°C

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER                 | SYMBOL            | MIN                                      | TYP | MAX  | UNITS | NOTES |

|---------------------------|-------------------|------------------------------------------|-----|------|-------|-------|

| 1-Wire Pullup Voltage     | $ m V_{PUP}$      | 2.8                                      |     | 5.25 | V     | 1, 2  |

| 1-Wire Input High         | $V_{\mathrm{IH}}$ | 2.2                                      |     |      | V     | 1, 3  |

| 1-Wire Input Low          | $V_{ m IL}$       | -0.3                                     |     | 0.3  | V     | 1     |

| 1-Wire Output Low at 4mA  | $ m V_{OL}$       |                                          |     | 0.4  | V     | 1     |

| Input Load Current        | $ m I_L$          |                                          | 5   |      | μA    | 4     |

| Programming Current       | $I_{LPROG}$       |                                          | 500 |      | μΑ    | 5, 6  |

| SHA-1 Computation Current | $I_{CSHA}$        | Refer to the full version of data sheet. |     |      |       |       |

**CAPACITANCE**

$(T_A = +25^{\circ}C.)$

| PARAMETER  | SYMBOL              | MIN | TYP | MAX | UNITS | NOTES |

|------------|---------------------|-----|-----|-----|-------|-------|

| 1-Wire I/O | C <sub>IN/OUT</sub> |     | 100 | 800 | pF    | 7     |

**EEPROM**

$(V_{PUP} = 5.0V, T_A = +25^{\circ}C.)$

| PARAMETER                | SYMBOL             | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|--------------------|-----|-----|-----|-------|-------|

| Write/Erase Cycles       | N <sub>CYCLE</sub> | 50k |     |     | _     |       |

| Data Retention (at 85°C) | $t_{ m DRET}$      | 10  |     |     | years |       |

### **AC ELECTRICAL CHARACTERISTICS: REGULAR SPEED**

$(V_{PUP} = 2.8V \text{ to } 5.25V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER              | SYMBOL               | MIN      | TYP | MAX | UNITS | NOTES |

|------------------------|----------------------|----------|-----|-----|-------|-------|

| Time Slot              | $t_{ m SLOT}$        | 60       |     | 120 | μs    |       |

| Write 1 Low Time       | $t_{ m LOW1}$        | 1        |     | 15  | μs    |       |

| Write 0 Low Time       | $t_{ m LOW0}$        | 60       |     | 120 | μs    |       |

| Read Low Time          | $t_{LOWR}$           | 1        |     | 15  | μs    |       |

| Read Data Valid        | $t_{ m RDV}$         |          | 15  |     | μs    | 8     |

| Release Time           | $t_{\text{RELEASE}}$ | 0        | 15  | 45  | μs    |       |

| Read Data Setup        | $t_{ m SU}$          |          |     | 1   | μs    | 9     |

| Recovery Time          | $t_{REC}$            | 5        |     |     | μs    | 10    |

| Reset High Time        | $t_{RSTH}$           | 480      |     |     | μs    |       |

| Reset Low Time         | $t_{RSTL}$           | 480      |     |     | μs    | 11    |

| Presence Detect High   | t <sub>PDHIGH</sub>  | 15       |     | 60  | μs    | 12    |

| Presence Detect Low    | $t_{ m PDLOW}$       | 60       |     | 240 | μs    | 12    |

| Programming Time       | $t_{PROG}$           |          |     | 10  | ms    |       |

| SHA-1 Computation Time | $t_{CSHA}$           | Refer to |     |     |       |       |

#### **AC ELECTRICAL CHARACTERISTICS: OVERDRIVE SPEED**

$(V_{PUP} = 2.8V \text{ to } 5.25V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.)$

| PARAMETER              | SYMBOL              | MIN      | TYP         | MAX           | UNITS  | NOTES |

|------------------------|---------------------|----------|-------------|---------------|--------|-------|

| Time Slot              | $t_{ m SLOT}$       | 6        |             | 16            | μs     |       |

| Write 1 Low Time       | $t_{LOW1}$          | 1        |             | 2             | μs     |       |

| Write 0 Low Time       | $t_{ m LOW0}$       | 6        |             | 16            | μs     |       |

| Read Low Time          | $t_{LOWR}$          | 1        |             | 2             | μs     |       |

| Read Data Valid        | $t_{ m RDV}$        |          | 2           |               | μs     | 8     |

| Release Time           | $t_{ m RELEASE}$    | 0        | 1.5         | 4             | μs     |       |

| Read Data Setup        | $t_{ m SU}$         |          |             | 1             | μs     | 9     |

| Recovery Time          | $t_{REC}$           | 5        |             |               | μs     | 10    |

| Reset High Time        | $t_{RSTH}$          | 48       |             |               | μs     |       |

| Reset Low Time         | $t_{RSTL}$          | 48       |             | 80            | μs     |       |

| Presence Detect High   | t <sub>PDHIGH</sub> | 2        |             | 6             | μs     |       |

| Presence Detect Low    | $t_{ m PDLOW}$      | 8        |             | 24            | μs     |       |

| Programming Time       | $t_{PROG}$          |          |             | 10            | ms     |       |

| SHA-1 Computation Time | $t_{CSHA}$          | Refer to | the full ve | rsion of data | sheet. |       |

#### NOTES:

- 1. All voltages are referenced to ground.

- 2.  $V_{PUP}$  = external pullup voltage, see Figure 8.

- 3.  $V_{IH}$  is a function of the external pullup resistor and  $V_{PUP}$ .

- 4. Input load is to ground.

- 5. During write operations to the EEPROM the voltage on the 1-Wire bus must not fall below 2.8V.

- 6. Guaranteed by design, not production tested.

- 7. Capacitance on the data pin could be 800 pF when power is first applied. Once the parasite capacitance is charged, it does not affect normal communication.

- 8. The optimal sampling point for the master is as close as possible to the end time of the  $t_{RDV}$  period without exceeding  $t_{RDV}$ . For the case of a Read-one time slot, this maximizes the amount of time for the pullup resistor to recover the line to a high level. For a Read-zero time slot it ensures that a read will occur before the fastest 1-Wire device releases the line ( $t_{RELEASE} = 0$ ).

- 9. Read data setup time refers to the time the host must pull the 1-Wire bus low to read a bit. Data is guaranteed to be valid within 1 µs of this falling edge.

- 10. Applies to a single device attached to a 1-Wire line and a pullup resistor of maximum  $2.2k\Omega$ .

- 11. The reset low time (t<sub>RSTL</sub>) should be restricted to a maximum of 960µs, to allow interrupt signaling, otherwise, it could mask or conceal interrupt pulses.

- 12. The first presence pulse after power-up could be outside the  $t_{PDHIGHmax}$  to  $(t_{PDHIGHmin} + t_{PDLOWmin})$  interval, but will be complete within 2ms after power-up.

## **PACKAGE INFORMATION**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO.               |

|--------------|--------------|----------------|--------------------------------|

| 6 TSOC       | D6+1         | <u>21-0382</u> | <u>90-0321</u>                 |

| 8 UCSP       | BR823+1      | <u>21-0373</u> | Refer to Application Note 1891 |

## **REVISION HISTORY**

| REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                                              | PAGES<br>CHANGED |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 040907           | Initial release.                                                                                                                                                                                                                                                                                         |                  |

|                  | Removed the leaded parts from the <i>Ordering Information</i> table and corrected package name from $\mu$ CSP to UCSPR.                                                                                                                                                                                  | 1                |

|                  | Removed 64-Bit Registration Number from Overdrive Skip ROM in Figure 2.                                                                                                                                                                                                                                  | 4                |

|                  | Removed reference to tamper detect register (does not exist).                                                                                                                                                                                                                                            | 7                |

| 060608           | In Figure 8, changed "5µA typ" to "I <sub>L</sub> ".                                                                                                                                                                                                                                                     | 7                |

| 000008           | In the <i>DC Electrical Characteristics</i> table, added the 1-Wire Pullup Voltage parameter (V <sub>PUP</sub> ) (moved from the headline into the table) and removed the 1-Wire Output High parameter (V <sub>OH</sub> ). In the <i>EEPROM</i> table, added (at +85°C) to the Data Retention parameter. | 14               |

|                  | Added Package Information section.                                                                                                                                                                                                                                                                       | 16               |

|                  | Minor nontechnical corrections to the text (various pages).                                                                                                                                                                                                                                              | 1, 2, 4, 8, 15   |

|                  | Electrical characteristics table: t <sub>RECMIN</sub> changed from 1μs to 5μs (regular speed) and 2μs (overdrive speed); V <sub>ILMAX</sub> changed from "TBD" to 0.3V; SHA-1 computation current added.                                                                                                 | 14, 15           |

| 2/10             | UCSP package outline deleted; see section Package Information to access the latest drawing.                                                                                                                                                                                                              | 16               |

|                  | Typo- and style corrections                                                                                                                                                                                                                                                                              | Various pages    |

|                  | Original Note 8 deleted from EC table notes and remaining notes renumbered to conform to Style Guide.                                                                                                                                                                                                    | 14, 15           |

|                  | Deleted DS2432X+ from the <i>Ordering Information</i> table.                                                                                                                                                                                                                                             | 1                |

|                  | Updated the soldering information and added the lead temperature to the <i>Absolute Maximum Ratings</i> .                                                                                                                                                                                                | 14               |

| 3/12             | Added Note 12 to AC Electrical Characteristics: Regular Speed table parameters tpDHIGH and tpDLOW.                                                                                                                                                                                                       | 14               |

|                  | Revised the electrical characteristics tables Note 7.                                                                                                                                                                                                                                                    | 15               |

|                  | Added the land pattern column to the Package Information table.                                                                                                                                                                                                                                          | 16               |

| 9/12             | Changed Overdrive communication speed from 125kbps to 90.9kbps; changed Overdrive t <sub>RECmin</sub> from 2µs to 5µs and updated the Overdrive speed accordingly; reworded Note 10.                                                                                                                     | 1, 7, 15         |

17 of 17

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for EEPROM category:

Click to view products by Maxim manufacturer:

Other Similar products are found below:

M29F040-70K6 718278CB 718620G AT28C256-15PU-ND 444358RB 444362FB BR93C46-WMN7TP 442652G 701986CB

TC58NVG0S3HBAI4 5962-8751413XA TC58BVG0S3HBAI4 TH58NYG3S0HBAI6 CAT25320YIGT-KK CAT25320DWF LE24C162-RE 5962-8751417YA 5962-8751409YA CAT25M01LI-G DS28E11P+ BR9016AF-WE2 LE2464DXATBG CAS93C66VP2I-GT3

DS28E25+T DS28EL15Q+T M95320-DFDW6TP DS28E05GB+T AT25320B-SSPDGV-T HE24C64WLCSPD BL24SA128B-CSRC

24FC16T-I/OT 24FC08T-I/OT M24128-BFMN6TP S-24CS04AFM-TFH-U M24C04-FMC5TG M24C16-DRMN3TPK M24C64-DFMN6TP

34AA02-EMS M95080-RMC6TG M95128-DFCS6TP/K M95128-DFDW6TP M95256-DFMN6TP M95320-RDW6TP M95640-RDW6TP

AT17LV010-10CU AT24C01C-SSHM-B AT24C01D-MAHM-T AT24C04D-MAHM-T AT24C04D-SSHM-T AT24C08C-SSHM-B