#### Important notice

Dear Customer,

On 7 February 2017 the former NXP Standard Product business became a new company with the tradename **Nexperia**. Nexperia is an industry leading supplier of Discrete, Logic and PowerMOS semiconductors with its focus on the automotive, industrial, computing, consumer and wearable application markets

In data sheets and application notes which still contain NXP or Philips Semiconductors references, use the references to Nexperia, as shown below.

Instead of <a href="http://www.nxp.com">http://www.nxp.com</a>, <a href="http://www.semiconductors.philips.com/">http://www.nxp.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>, <a href="http://www.nexperia.com">http://www.nexperia.com</a>)

Instead of sales.addresses@www.nxp.com or sales.addresses@www.semiconductors.philips.com, use salesaddresses@nexperia.com (email)

Replace the copyright notice at the bottom of each page or elsewhere in the document, depending on the version, as shown below:

- © NXP N.V. (year). All rights reserved or © Koninklijke Philips Electronics N.V. (year). All rights reserved

Should be replaced with:

- © Nexperia B.V. (year). All rights reserved.

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or telephone (details via **salesaddresses@nexperia.com**). Thank you for your cooperation and understanding,

Kind regards,

Team Nexperia

### **INTEGRATED CIRCUITS**

# DATA SHEET

## 74ALVCH16821

20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

Product specification

1998 May 29

IC24 Data Handbook

### 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

#### 74ALVCH16821

#### **FEATURES**

- Wide supply voltage range of 1.2V to 3.6V

- Complies with JEDEC standard no. 8-1A

- Current drive ± 24 mA at 3.0 V

- CMOS low power consumption

- Direct interface with TTL levels

- MULTIBYTE<sup>TM</sup> flow-through standard pin-out architecture

- Low inductance multiple V<sub>CC</sub> and ground pins for minimum noise and ground bounce

- All data inputs have bus hold

- Output drive capability 50Ω transmission lines @ 85°C

#### DESCRIPTION

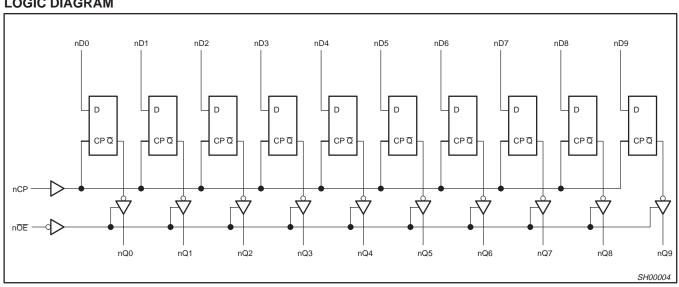

The 74ALVCH16821 has two 10-bit, edge triggered registers, with each register coupled to a 3-State output buffer. The two sections of each register are controlled independently by the clock (nCP) and Output Enable (nOE) control gates.

Each register is fully edge triggered. The state of each D input, one set-up time before the Low-to-High clock transition, is transferred to the corresponding flip-flop's Q output.

When nOE is LOW, the data in the register appears at the outputs. When nOE is HIGH, the outputs are in high impedance OFF state. Operation of the nOE input does not affect the state of the flip-flops.

The 74ALVCH16821 has active bus hold circuitry which is provided to hold unused or floating data inputs at a valid logic level. This feature eliminates the need for external pull-up or pull-down resistors.

#### **QUICK REFERENCE DATA**

GND = 0V;  $T_{amb} = 25^{\circ}C$ ;  $t_r = t_f \le 2.5$ ns

| SYMBOL                             | PARAMETER                                 | CONDIT                                                     | TONS             | TYPICAL    | UNIT |

|------------------------------------|-------------------------------------------|------------------------------------------------------------|------------------|------------|------|

| t <sub>PHL</sub> /t <sub>PLH</sub> | Propagation delay nCP to nQ <sub>n</sub>  | 2.6<br>2.5                                                 | ns               |            |      |

| C <sub>I</sub>                     | Input capacitance                         |                                                            | 5.0              | pF         |      |

|                                    | Davier discipation consistence neglection | V CND to V 1                                               | 33               |            |      |

| C <sub>PD</sub>                    | Power dissipation capacitance per buffer  | $V_I = GND \text{ to } V_{CC}^1$                           | Outputs disabled | 17         | pF   |

| F <sub>max</sub>                   | Maximum clock frequency                   | $V_{CC} = 2.5V, C_L = 30pF$<br>$V_{CC} = 3.3V, C_L = 50pF$ |                  | 250<br>350 | MHz  |

#### NOTE:

$P_D = C_{PD} \times V_{CC}^2 \times f_i + \Sigma (C_L \times V_{CC}^2 \times f_o)$  where:  $f_i = \text{input frequency in MHz}$ ;  $C_L = \text{output load capacitance in pF}$ ;  $f_0 = \text{output frequency in MHz}$ ;  $V_{CC} = \text{supply voltage in V}$ ;

$\Sigma (C_L \times V_{CC}^2 \times f_0) = \text{sum of outputs.}$

#### ORDERING INFORMATION

| PACKAGES                     | TEMPERATURE RANGE | OUTSIDE NORTH AMERICA | NORTH AMERICA | DWG NUMBER |

|------------------------------|-------------------|-----------------------|---------------|------------|

| 56-Pin Plastic SSOP Type III | –40°C to +85°C    | 74ALVCH16821 DL       | ACH16821 DL   | SOT371-1   |

| 56-Pin Plastic TSSOP Type II | -40°C to +85°C    | 74ALVCH16821 DGG      | ACH16821 DGG  | SOT364-1   |

$C_{PD}$  is used to determine the dynamic power dissipation ( $P_D$  in  $\mu W$ ):

# 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

## 74ALVCH16821

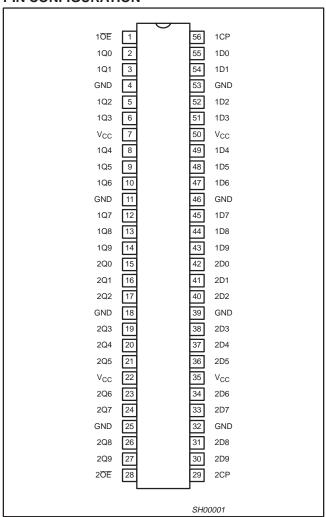

#### PIN DESCRIPTION

| PIN NUMBER                                | SYMBOL          | FUNCTION                                |

|-------------------------------------------|-----------------|-----------------------------------------|

| 55, 54, 52, 51, 49,<br>48, 47, 45, 44, 43 | 1D0 - 1D9       | Data inputs                             |

| 42, 41, 40, 38, 37,<br>36, 34, 33, 31, 30 | 2D0 - 2D9       | Data Inputs                             |

| 2, 3, 5, 6, 8,<br>9, 10, 12, 13, 14       | 1Q0 - 1Q9       | Data outputs                            |

| 15, 16, 17, 19, 20,<br>21, 23, 24, 26, 27 | 2Q0 - 2Q9       | Bata outputs                            |

| 1, 28                                     | 10E, 20E        | Output enable inputs (active-Low)       |

| 56, 29                                    | 1CP, 2CP        | Clock pulse inputs (active rising edge) |

| 4, 11, 18, 25,<br>32, 39, 46, 53          | GND             | Ground (0V)                             |

| 7, 22, 35, 50                             | V <sub>CC</sub> | Positive supply voltage                 |

#### **PIN CONFIGURATION**

#### **FUNCTION TABLE**

|     | INPUTS   | OUTPUT |    |

|-----|----------|--------|----|

| nOE | СР       | Dx     | Q  |

| L   | 1        | L      | L  |

| L   | <b>↑</b> | Н      | Н  |

| L   | ‡        | Х      | Q0 |

| Н   | X        | Х      | Z  |

H = HIGH voltage level

L = LOW voltage level

X = Don't care

Z = High impedance OFF state ↑ = LOW to HIGH clock transition

‡ = Not a LOW-to-HIGH clock transition

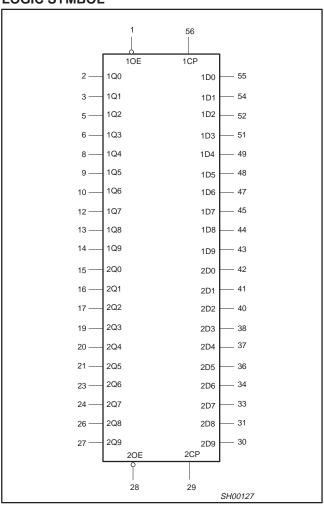

#### **LOGIC SYMBOL**

# 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

### 74ALVCH16821

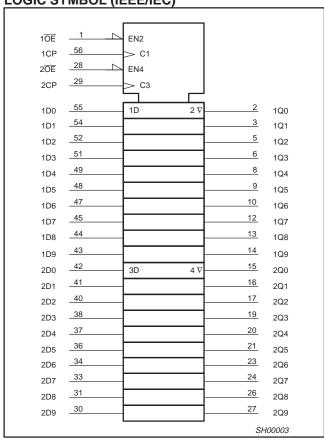

LOGIC SYMBOL (IEEE/IEC)

#### **LOGIC DIAGRAM**

# 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

### 74ALVCH16821

#### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL                          | PARAMETER                                                                     | CONDITIONS                                                                         | LIM     | UNIT            |      |

|---------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------|-----------------|------|

| STWIBUL                         | PARAMETER                                                                     | CONDITIONS                                                                         | MIN MAX |                 | UNIT |

| V                               | DC supply voltage 2.5V range (for max. speed performance @ 30 pF output load) |                                                                                    | 2.3     | 2.7             | V    |

| V <sub>CC</sub>                 | DC supply voltage 3.3V range (for max. speed performance @ 50 pF output load) |                                                                                    | 3.0     | 3.6             | V    |

| V <sub>I</sub>                  | DC Input voltage range                                                        |                                                                                    | 0       | V <sub>CC</sub> | V    |

| Vo                              | DC output voltage range                                                       |                                                                                    | 0       | V <sub>CC</sub> | V    |

| T <sub>amb</sub>                | Operating free-air temperature range                                          |                                                                                    | -40     | +85             | °C   |

| t <sub>r</sub> , t <sub>f</sub> | Input rise and fall times                                                     | $V_{CC} = 2.3 \text{ to } 3.0 \text{V}$<br>$V_{CC} = 3.0 \text{ to } 3.6 \text{V}$ | 0       | 20<br>10        | ns/V |

#### **ABSOLUTE MAXIMUM RATINGS**

In accordance with the Absolute Maximum Rating System (IEC 134) Voltages are referenced to GND (ground = 0V)

| SYMBOL                             | PARAMETER                                                                                       | CONDITIONS                                                                                                               | RATING                       | UNIT |  |

|------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------|------|--|

| V <sub>CC</sub>                    | DC supply voltage                                                                               |                                                                                                                          | -0.5 to +4.6                 | V    |  |

| I <sub>IK</sub>                    | DC input diode current                                                                          | V <sub>I</sub> < 0                                                                                                       | -50                          | mA   |  |

| \/                                 | DC input voltage                                                                                | For control pins <sup>1</sup>                                                                                            | -0.5 to +4.6                 | V    |  |

| VI                                 | DC input voltage                                                                                | For data inputs <sup>1</sup>                                                                                             | -0.5 to V <sub>CC</sub> +0.5 | 1    |  |

| I <sub>OK</sub>                    | DC output diode current                                                                         | $V_{O} > V_{CC}$ or $V_{O} < 0$                                                                                          | ±50                          | mA   |  |

| Vo                                 | DC output voltage                                                                               | Note 1                                                                                                                   | -0.5 to V <sub>CC</sub> +0.5 | V    |  |

| ΙO                                 | DC output source or sink current                                                                | $V_O = 0$ to $V_{CC}$                                                                                                    | ±50                          | mA   |  |

| I <sub>GND</sub> , I <sub>CC</sub> | DC V <sub>CC</sub> or GND current                                                               |                                                                                                                          | ±100                         | mA   |  |

| T <sub>stg</sub>                   | Storage temperature range                                                                       |                                                                                                                          | -65 to +150                  | °C   |  |

| P <sub>TOT</sub>                   | Power dissipation per package –plastic medium-shrink (SSOP) –plastic thin-medium-shrink (TSSOP) | For temperature range: -40 to +125 °C above +55°C derate linearly with 11.3 mW/K above +55°C derate linearly with 8 mW/K | 850<br>600                   | mW   |  |

#### NOTE:

<sup>1.</sup> The input and output voltage ratings may be exceeded if the input and output current ratings are observed.

# 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

74ALVCH16821

#### DC ELECTRICAL CHARACTERISTICS

Over recommended operating conditions. Voltage are referenced to GND (ground = 0 V).

|                   |                                         |                                                                                |                      | LIMITS                 |      |      |  |

|-------------------|-----------------------------------------|--------------------------------------------------------------------------------|----------------------|------------------------|------|------|--|

| SYMBOL            | PARAMETER                               | TEST CONDITIONS                                                                | Temp :               | = -40°C to +8          | 5°C  | UNIT |  |

|                   |                                         |                                                                                | MIN                  | TYP <sup>1</sup>       | MAX  |      |  |

| .,                |                                         | V <sub>CC</sub> = 2.3 to 2.7V                                                  | 1.7                  | 1.2                    |      | ,,   |  |

| $V_{IH}$          | HIGH level Input voltage                | V <sub>CC</sub> = 2.7 to 3.6V                                                  | 2.0                  | 1.5                    |      | \ \  |  |

| .,                | 1000                                    | V <sub>CC</sub> = 2.3 to 2.7V                                                  |                      | 1.2                    | 0.7  | ,,   |  |

| $V_{IL}$          | LOW level Input voltage                 | V <sub>CC</sub> = 2.7 to 3.6V                                                  |                      | 1.5                    | 0.8  | \ \  |  |

|                   |                                         | $V_{CC}$ = 2.3 to 3.6V; $V_I$ = $V_{IH}$ or $V_{IL}$ ; $I_O$ = $-100\mu A$     | V <sub>CC</sub> -0.2 | V <sub>CC</sub>        |      |      |  |

|                   |                                         | $V_{CC} = 2.3V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = -6mA$                    | V <sub>CC</sub> -0.3 | V <sub>CC</sub> -0.08  |      | 1    |  |

|                   | LHOLLI I I I I                          | $V_{CC} = 2.3V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = -12mA$                   | V <sub>CC</sub> _0.6 | V <sub>CC</sub> - 0.26 |      | 1 ,  |  |

| V <sub>OH</sub>   | HIGH level output voltage               | $V_{CC} = 2.7V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = -12mA$                   | V <sub>CC</sub> _0.5 | V <sub>CC</sub> _0.14  |      | \ \  |  |

|                   |                                         | $V_{CC} = 3.0V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = -12mA$                   | V <sub>CC</sub> _0.6 | V <sub>CC</sub> _0.09  |      | 1    |  |

|                   |                                         | $V_{CC} = 3.0V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = -24$ mA                  | V <sub>CC</sub> -1.0 | V <sub>CC</sub> _0.28  |      | 1    |  |

|                   |                                         | $V_{CC}$ = 2.3 to 3.6V; $V_I$ = $V_{IH}$ or $V_{IL}$ ; $I_O$ = 100 $\mu$ A     |                      | GND                    | 0.20 | ٧    |  |

|                   |                                         | $V_{CC} = 2.3V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = 6mA$                     |                      | 0.07                   | 0.40 | V    |  |

| $V_{OL}$          | LOW level output voltage                | $V_{CC} = 2.3V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = 12mA$                    |                      | 0.15                   | 0.70 |      |  |

|                   |                                         | $V_{CC} = 2.7V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = 12mA$                    |                      | 0.14                   | 0.40 | V    |  |

|                   |                                         | $V_{CC} = 3.0V$ ; $V_I = V_{IH}$ or $V_{IL}$ ; $I_O = 24$ mA                   |                      | 0.27                   | 0.55 | 1    |  |

| II                | Input leakage current                   | V <sub>CC</sub> = 2.3 to 3.6V;<br>V <sub>I</sub> = V <sub>CC</sub> or GND      |                      | 0.1                    | 5    | μА   |  |

| I <sub>OZ</sub>   | 3-State output OFF-state current        | $V_{CC}$ = 2.7 to 3.6V; $V_I$ = $V_{IH}$ or $V_{IL}$ ; $V_O$ = $V_{CC}$ or GND |                      | 0.1                    | 10   | μА   |  |

| I <sub>CC</sub>   | Quiescent supply current                | $V_{CC}$ = 2.3 to 3.6V; $V_I$ = $V_{CC}$ or GND; $I_O$ = 0                     |                      | 0.2                    | 40   | μΑ   |  |

| $\Delta I_{CC}$   | Additional quiescent supply current     | $V_{CC} = 2.3V$ to 3.6V; $V_I = V_{CC} - 0.6V$ ; $I_O = 0$                     |                      | 150                    | 750  | μА   |  |

|                   | Dura halili OW anatalala a anamat       | $V_{CC} = 2.3V; V_I = 0.7V^2$                                                  | 45                   | -                      |      |      |  |

| I <sub>BHL</sub>  | Bus hold LOW sustaining current         | $V_{CC} = 3.0V; V_I = 0.8V^2$                                                  | 75                   | 150                    |      | μΑ   |  |

|                   | Due held I II Ci I eveteining a surrent | $V_{CC} = 2.3V; V_I = 1.7V^2$                                                  | -45                  |                        |      |      |  |

| <sup>I</sup> внн  | Bus hold HIGH sustaining current        | $V_{CC} = 3.0V; V_1 = 2.0V^2$                                                  | -75                  | -175                   |      | μΑ   |  |

| I <sub>BHLO</sub> | Bus hold LOW overdrive current          | $V_{CC} = 3.6V^2$                                                              |                      |                        |      | μΑ   |  |

| I <sub>BHHO</sub> | Bus hold HIGH overdrive current         | $V_{CC} = 3.6V^2$                                                              | -500                 |                        |      | μΑ   |  |

#### NOTES:

All typical values are at T<sub>amb</sub> = 25°C.

Valid for data inputs of bus hold parts.

## 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

74ALVCH16821

# AC CHARACTERISTICS FOR $V_{CC}$ = 2.3V TO 2.7V RANGE GND = 0V; $t_{r}$ = $t_{f}$ $\leq$ 2.0ns; $C_{L}$ = 30pF

|                                    |                                                          |          |                | LIMITS           |     |     |

|------------------------------------|----------------------------------------------------------|----------|----------------|------------------|-----|-----|

| SYMBOL                             | PARAMETER                                                | WAVEFORM | V <sub>C</sub> | UNIT             |     |     |

|                                    |                                                          |          | MIN            | TYP <sup>1</sup> | MAX |     |

| t <sub>PLH</sub> /t <sub>PHL</sub> | Propagation delay<br>nCP to nQ <sub>n</sub>              | 1, 4     | 1.0            | 2.6              | 5.8 | ns  |

| t <sub>PZH</sub> /t <sub>PZL</sub> | 3-State output enable time $n\overline{OE}_n$ to $nQ_n$  | 2, 4     | 1.0            | 2.8              | 6.6 | ns  |

| t <sub>PHZ</sub> /t <sub>PLZ</sub> | 3-State output disable time $n\overline{OE}_n$ to $nQ_n$ | 2, 4     | 1.0            | 2.2              | 5.7 | ns  |

| t <sub>W</sub>                     | nCP pulse width HIGH or LOW                              | 3, 4     | 3.0            | 1.8              |     | ns  |

| t <sub>SU</sub>                    | Set up time nD <sub>n</sub> to nCP                       | 3, 4     | 1.4            | 0.3              |     | ns  |

| t <sub>h</sub>                     | Hold time nD <sub>n</sub> to nCP                         | 3, 4     | 0.4            | 0.0              |     | ns  |

| F <sub>max</sub>                   | Maximum clock pulse frequency                            | 1, 4     | 150            | 250              |     | MHz |

#### AC CHARACTERISTICS FOR $V_{CC}$ = 3.0V TO 3.6V RANGE AND $V_{CC}$ = 2.7V

$\text{GND} = \text{OV; } t_{\text{r}} = t_{\text{f}} \leq \text{2.5ns; } C_{\text{L}} = \text{50pF}$

|                                    |                                                                 |          | LIMITS |                             |     |     |                        |     |      |  |  |

|------------------------------------|-----------------------------------------------------------------|----------|--------|-----------------------------|-----|-----|------------------------|-----|------|--|--|

| SYMBOL                             | PARAMETER                                                       | WAVEFORM | Vc     | $_{\text{C}}$ = 3.3 $\pm$ 0 | .3V | ,   | V <sub>CC</sub> = 2.7V | 7   | UNIT |  |  |

|                                    |                                                                 |          | MIN    | TYP <sup>1</sup>            | MAX | MIN | TYP <sup>1</sup>       | MAX |      |  |  |

| t <sub>PHL</sub> /t <sub>PLH</sub> | Propagation delay nCP to nQ <sub>n</sub>                        | 1, 4     | 1.0    | 2.5                         | 4.5 | 1.0 | 2.8                    | 5.3 | ns   |  |  |

| t <sub>PZH</sub> /t <sub>PZL</sub> | 3-State output enable time nOE <sub>n</sub> to nQ <sub>n</sub>  | 2, 4     | 1.0    | 2.3                         | 5.1 | 1.0 | 3.2                    | 6.2 | ns   |  |  |

| t <sub>PHZ</sub> /t <sub>PLZ</sub> | 3-State output disable time nOE <sub>n</sub> to nQ <sub>n</sub> | 2, 4     | 1.0    | 2.8                         | 4.6 | 1.0 | 3.1                    | 5.0 | ns   |  |  |

| t <sub>W</sub>                     | nCP pulse width HIGH or<br>LOW                                  | 3, 4     | 3.3    | 0.2                         |     | 3.3 | 1.7                    |     | ns   |  |  |

| tsu                                | Set up time nD <sub>n</sub> to nCP                              | 3, 4     | 1.0    | 0.2                         |     | 1.2 | 0.3                    |     | ns   |  |  |

| t <sub>h</sub>                     | Hold time nD <sub>n</sub> to nCP                                | 3, 4     | 0.8    | 0.4                         |     | 0.6 | -0.3                   |     | ns   |  |  |

| F <sub>max</sub>                   | Maximum clock pulse frequency                                   | 1, 4     | 150    | 350                         |     | 150 | 300                    |     | MHz  |  |  |

<sup>1.</sup> All typical values are at  $V_{CC}$  = 2.5V and  $T_{amb}$  = 25°C.

<sup>1.</sup> All typical values are at  $T_{amb} = 25$ °C.

### 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

#### 74ALVCH16821

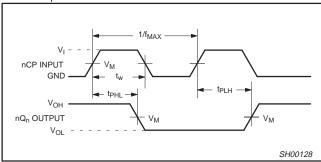

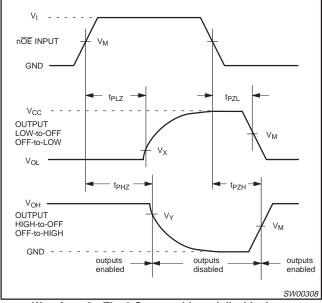

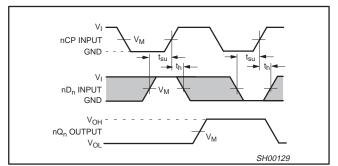

#### **AC WAVEFORMS**

# $V_{CC}$ = 2.3 TO 2.7 V RANGE 1. $V_{M}$ = 0.5 V

- $V_X = V_{OL} + 0.15V$

- 3.  $V_Y = V_{OH} 0.15V$

- 4. V<sub>I</sub> = V<sub>CC</sub>

5. V<sub>OL</sub> and V<sub>OH</sub> are the typical output voltage drop that occur with the output load.

# $V_{CC}$ = 3.0 TO 3.6 V RANGE AND $V_{CC}$ = 2.7 V 1. $V_{M}$ = 1.5 V

- 2.  $V_X^{"} = V_{OL} + 0.3V$

- 3.  $V_Y = V_{OH} 0.3V$ 4.  $V_I = 2.7 V$

- $\rm V_{OL}$  and  $\rm V_{OH}$  are the typical output voltage drop that occur with the output load.

Waveform 1. The input (nCP) to output propagation delays.

Waveform 2. The 3-State enable and disable times.

Waveform 3. Set up and hold times.

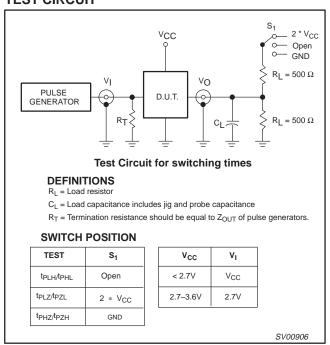

#### **TEST CIRCUIT**

Waveform 4. Load circuitry for switching times

# 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

### 74ALVCH16821

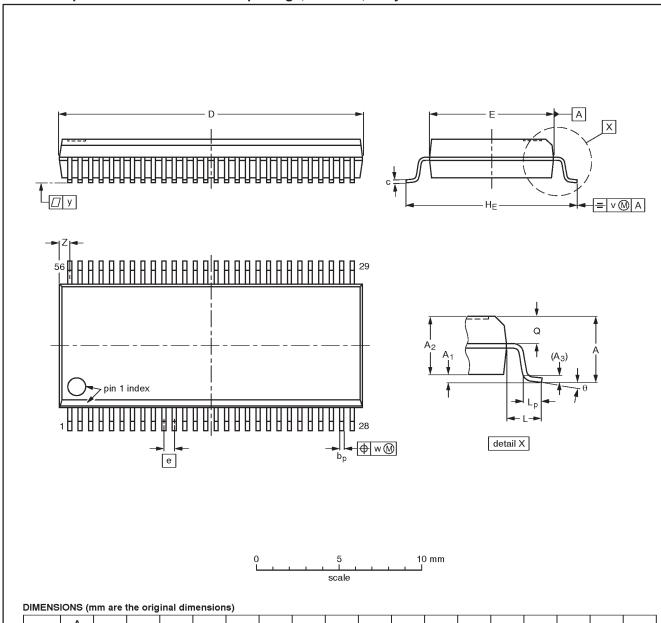

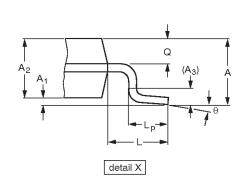

#### SSOP56: plastic shrink small outline package; 56 leads; body width 7.5 mm

SOT371-1

| UNIT | A<br>max. | Α <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | рb         | O            | D <sup>(1)</sup> | E <sup>(1)</sup> | е     | HE           | ٦   | Lp         | ø          | v    | w    | у   | Z <sup>(1)</sup> | θ        |

|------|-----------|----------------|----------------|-----------------------|------------|--------------|------------------|------------------|-------|--------------|-----|------------|------------|------|------|-----|------------------|----------|

| mm   | 2.8       | 0.4<br>0.2     | 2.35<br>2.20   | 0.25                  | 0.3<br>0.2 | 0.22<br>0.13 | 18.55<br>18.30   | 7.6<br>7.4       | 0.635 | 10.4<br>10.1 | 1.4 | 1.0<br>0.6 | 1.2<br>1.0 | 0.25 | 0.18 | 0.1 | 0.85<br>0.40     | 8°<br>0° |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  |     | REFER         | EUROPEAN | ISSUE DATE |            |                                 |  |  |

|----------|-----|---------------|----------|------------|------------|---------------------------------|--|--|

| VERSION  | IEC | IEC JEDEC EIA |          |            | PROJECTION | ISSUE DATE                      |  |  |

| SOT371-1 |     | MO-118AB      |          |            |            | <del>93-11-02</del><br>95-02-04 |  |  |

# 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

### 74ALVCH16821

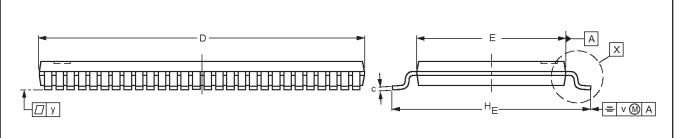

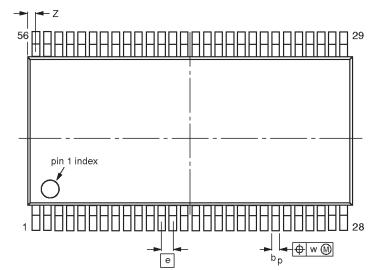

#### TSSOP56: plastic thin shrink small outline package; 56 leads; body width 6.1mm

SOT364-1

#### $\label{eq:def:DIMENSIONS} \textbf{DIMENSIONS (mm are the original dimensions)}.$

| UNIT | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | А3   | bp           | c          | D <sup>(1)</sup> | E <sup>(2)</sup> | e   | HE         | L   | Lp         | ø            | >    | V    | у   | Z          | θ        |

|------|-----------|----------------|----------------|------|--------------|------------|------------------|------------------|-----|------------|-----|------------|--------------|------|------|-----|------------|----------|

| mm   | 1.2       | 0.15<br>0.05   | 1.05<br>0.85   | 0.25 | 0.28<br>0.17 | 0.2<br>0.1 | 14.1<br>13.9     | 6.2<br>6.0       | 0.5 | 8.3<br>7.9 | 1.0 | 0.8<br>0.4 | 0.50<br>0.35 | 0.25 | 0.08 | 0.1 | 0.5<br>0.1 | 8°<br>0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic interlead protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  | REFERENCES |          |      |  |  | EUROPEAN   | ISSUE DATE                       |

|----------|------------|----------|------|--|--|------------|----------------------------------|

| VERSION  | IEC        | JEDEC    | EIAJ |  |  | PROJECTION | ISSUE DATE                       |

| SOT364-1 |            | MO-153EE |      |  |  |            | <del>-93-02-03</del><br>95-02-10 |

20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

74ALVCH16821

**NOTES**

# 20-bit bus-interface D-type flip-flop; positive-edge trigger (3-State)

74ALVCH16821

#### Data sheet status

| Data sheet status         | Product status | Definition [1]                                                                                                                                                                                                                                            |  |

|---------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Objective specification   | Development    | This data sheet contains the design target or goal specifications for product development. Specification may change in any manner without notice.                                                                                                         |  |

| Preliminary specification | Qualification  | This data sheet contains preliminary data, and supplementary data will be published at a later date. Philips Semiconductors reserves the right to make chages at any time without notice in order to improve design and supply the best possible product. |  |

| Product specification     | Production     | This data sheet contains final specifications. Philips Semiconductors reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.                                                      |  |

<sup>[1]</sup> Please consult the most recently issued datasheet before initiating or completing a design.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### **Disclaimers**

**Life support** — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 1998 All rights reserved. Printed in U.S.A.

print code Date of release: 05-96

Document order number: 9397-750-04553

Let's make things better.

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Flip Flops category:

Click to view products by NXP manufacturer:

Other Similar products are found below:

5962-8955201EA MC74HC11ADTG MC10EP29MNG MC74HC11ADTR2G NLV14013BDTR2G NLV14027BDG NLX1G74MUTCG

703557B 746431H 5962-90606022A 5962-9060602FA NLV14013BDR2G M38510/30104BDA M38510/07106BFA M38510/06102BFA

M38510/06101B2A NLV74HC74ADR2G TC4013BP(N,F) NLV14013BDG NLV74AC32DR2G NLV74AC74DR2G MC74HC73ADG

CY74FCT16374CTPACT MC74HC11ADR2G 74LVT74D,118 74VHCT9273FT(BJ) MM74HC374WM 74ALVCH162374PAG

TC7WZ74FK,LJ(CT CD54HCT273F HMC853LC3TR HMC723LC3CTR MM74HCT574MTCX MM74HCT273WM SN74LVC74APW

SN74LVC74AD MC74HC73ADTR2G MC74HC11ADG SN74ALVTH16374GR M74HCT273B1R M74HC377RM13TR

M74HC374RM13TR M74HC175B1R M74HC174RM13TR 74ALVTH16374ZQLR 74ALVTH32374ZKER 74AUP1G74DC,125

74VHC374FT(BJ) 74VHC9273FT(BJ) NLV14013BCPG