# 3-Axis Digital Compass IC HMC5983

Advanced Information

The Honeywell HMC5983 is a temperature compensated three-axis integrated circuit e-compass. This surface-mount, multi-chip module is designed for low-field magnetic sensing for applications such as mobile phones, tablets, netbooks, consumer electronics, automotive navigation systems, and personal navigation devices.

The HMC5983 includes our state-of-the-art, high-resolution HMC118X series magnetoresistive sensors plus an ASIC containing amplification, automatic degaussing strap drivers, offset cancellation, and a 12-bit ADC that enables 1° to 2° compass heading accuracy. The I<sup>2</sup>C or SPI serial bus allows for easy interface. The HMC5983 is a 3.0x3.0x0.9mm surface mount 16-pin leadless chip carrier (LCC).

The HMC5983 utilizes Honeywell's Anisotropic Magnetoresistive (AMR) technology that provides advantages over other magnetic sensor technologies. Honeywell's anisotropic, directional sensors excel in linearity, low hysteresis, null output and scale factor stability over temperature, and with very low cross-axis sensitivity. These sensors' solid-state construction is designed to measure both the direction and the magnitude of magnetic fields, from milli-gauss to 8 gauss. Honeywell's Magnetic Sensors are among the most sensitive and reliable low-field sensors in the industry.

#### **FEATURES**

- 3-Axis Magnetoresistive Sensors and ASIC in a 3.0x3.0x0.9mm LCC Surface Mount Package

- Temperature Compensated Data Output and Temperature Output

- Automatic Offset Compensation

- ▶ 12-Bit ADC Coupled with Low Noise AMR Sensors Achieves 2 milli-gauss Field Resolution

- ▶ I<sup>2</sup>C (Standard, Fast, High-Speed modes) or SPI Digital Interface

- ▶ Fast 220 Hz Maximum Output Rate

- Built-in Self Test

- Low Voltage Operations (2.16 to 3.6V) and Low Power Consumption (100 μA)

- Built-In Strap Drive Circuits

- Lead Free Package Construction

- Wide Magnetic Field Range (+/-8 Oe)

- Software and Algorithm Support Available

#### **BENEFIT**

- Small size for Highly Integrated Products. Just add a microcontroller interface, plus two external SMT Capacitors designed for high volume, cost sensitive OEM Designs. Easy to assemble & compatible with High Speed SMT Assembly.

- Automatically maintains sensor's sensitivity under wide operating temperature range

- Maximizes sensor's full dynamic range and resolution

- ▶ Enables 1° to 2° degree compass heading accuracy

- ▶ High-speed interfaces for fast data communications. I<sup>2</sup>C up to 3.4 mHz and SPI up to 8.0 mHz

- ▶ Enables Pedestrian Navigation and LBS Applications

- ▶ Enables low-cost functionality test after assembly in production

- ▶ Compatible for battery powered applications

- ▶ Set/reset and offset strap drivers for degaussing, self test, and offset compensation. Eliminates sensor calibration necessary for other magnetic sensor technologies.

- RoHS Compliance

- Sensors can be used in strong magnetic field environments with a 1° to 2° degree compass heading accuracy

- Compassing Heading, Hard Iron, Soft Iron, and Auto Calibration libraries available

# **SPECIFICATIONS** (\* Tested at 25°C except stated otherwise.)

| Characteristics                   | Conditions*                                                                                                                                   | Min          | Тур                    | Max            | Units          |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------|----------------|----------------|

| Power Supply                      |                                                                                                                                               |              |                        |                |                |

| Supply Voltage                    | VDD Referenced to AGND VDDIO Referenced to DGND                                                                                               | 2.16<br>1.71 | 2.5<br>1.8             | 3.6<br>VDD+0.1 | Volts<br>Volts |

| Average Current Draw              | Idle Mode                                                                                                                                     | 1.7 1        | 2                      | VDD+0.1        |                |

| Average Current Draw              | Measurement Mode (7.5 Hz ODR; No measurement average, MA1:MA0 = 00) VDD = 2.5V, VDDIO = 1.8V (Dual Supply) VDD = VDDIO = 2.5V (Single Supply) |              | 100                    | -              | μA<br>μA       |

| Performance                       |                                                                                                                                               |              |                        |                |                |

| Field Range                       | Full scale (FS)                                                                                                                               | -8           |                        | +8             | gauss          |

| Mag Dynamic Range                 | 3-bit gain control                                                                                                                            | ±1           |                        | ±8             | gauss          |

| Sensitivity (Gain)                | VDD=3.0V, GN=0 to 7, 12-bit ADC                                                                                                               | 230          |                        | 1370           | LSb/gauss      |

| Digital Resolution                | VDD=3.0V, GN=0 to 7, 1-LSb, 12-bit ADC                                                                                                        | 0.73         |                        | 4.35           | milli-gauss    |

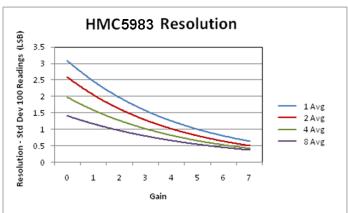

| Noise Floor<br>(Field Resolution) | VDD=3.0V, GN=0, No measurement average, Standard Deviation 100 samples (See typical performance graphs below)                                 |              | 2                      |                | milli-gauss    |

| Linearity                         | ±2.0 gauss input range                                                                                                                        |              |                        | 0.1            | ±% FS          |

| Hysteresis                        | ±2.0 gauss input range                                                                                                                        |              | ±25                    |                | ppm            |

| Cross-Axis Sensitivity            | Test Conditions: Cross field = 0.5 gauss,<br>Happlied = ±3 gauss                                                                              |              | ±0.2%                  |                | %FS/gauss      |

| Output Rate (ODR)                 | Continuous Measurment Mode Single Measurement Mode                                                                                            | 0.75         |                        | 220<br>160     | Hz             |

| Measurement Period                | From receiving command to data ready                                                                                                          |              | 6                      |                | ms             |

| Turn-on Time                      | Ready for I <sup>2</sup> C commands<br>Analog Circuit Ready for Measurements                                                                  |              | 200<br>50              |                | μs<br>ms       |

| Gain Tolerance                    | All gain/dynamic range settings                                                                                                               |              | ±5                     |                | %              |

| I <sup>2</sup> C Address          | 8-bit read address<br>8-bit write address                                                                                                     |              | 0x3D<br>0x3C           |                | hex            |

| Clock Rate                        | Controlled by I <sup>2</sup> C /SPI Master I <sup>2</sup> C SPI                                                                               |              |                        | 3400<br>8000   | kHz            |

| I <sup>2</sup> C Hysteresis       | Hysteresis of Schmitt trigger inputs on SCL and SDA - Fall (VDDIO=1.8V) Rise (VDDIO=1.8V)                                                     |              | 0.2*VDDIO<br>0.8*VDDIO |                | Volts          |

| Self Test                         | X & Y Axes<br>Z Axis                                                                                                                          |              | ±1.16<br>±1.08         |                | gauss          |

|                                   | X & Y & Z Axes (GN=5) Positive Bias<br>X & Y & Z Axes (GN=5) Negative Bias                                                                    | 243<br>-575  |                        | 575<br>-243    | LSb            |

| Sensitivity Tempco                | T <sub>A</sub> = -40 to 125°C, Compensated Output<br>Temperature Sensor On                                                                    |              | -0.03<br>(1σ =0.04)    |                | %/°C           |

| Characteristics       | Conditions*                     | Min  | Min Typ N |      | Units |

|-----------------------|---------------------------------|------|-----------|------|-------|

| General               |                                 |      |           |      |       |

| ESD Voltage           | Human Body Model (all pins)     |      |           | 2000 | Volts |

|                       | Charged Device Model (all pins) |      |           | 750  |       |

| Operating Temperature | Ambient                         | -30  |           | 85   | °C    |

| Storage Temperature   | Ambient, unbiased               | -40  |           | 125  | °C    |

| Reflow Classification | MSL 3, 260 °C Peak Temperature  |      |           |      |       |

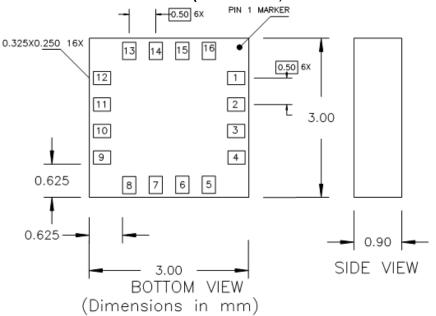

| Package Size          | Length and Width                | 2.85 | 3.00      | 3.15 | mm    |

| Package Height        |                                 | 0.8  | 0.9       | 1.0  | mm    |

| Package Weight        |                                 |      | 18        |      | mg    |

# Absolute Maximum Ratings (\* Tested at 25°C except stated otherwise.)

| Characteristics      | Min  | Max | Units |

|----------------------|------|-----|-------|

| Supply Voltage VDD   | -0.3 | 4.8 | Volts |

| Supply Voltage VDDIO | -0.3 | 4.8 | Volts |

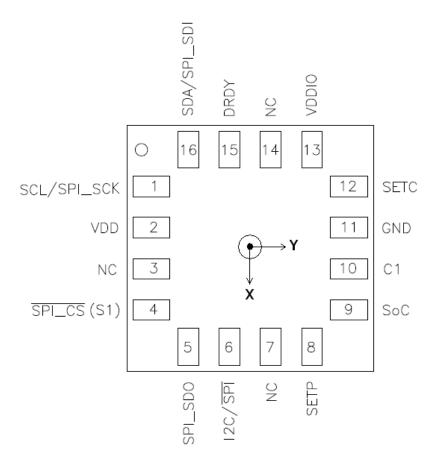

# **PIN CONFIGURATIONS**

Table 1: Pin Configurations

| Pin | Name        | Description                                                                                                                                  |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SCL/SPI_SCK | Serial Clock – I <sup>2</sup> C Master/Slave Clock or SPI Serial Clock                                                                       |

| 2   | VDD         | Power Supply (2.16V to 3.6V)                                                                                                                 |

| 3   | NC          | Not to be Connected                                                                                                                          |

| 4   | SPI_CS      | Chip Select line for SPI (active low). Tie to VDDIO for I <sup>2</sup> C Interface                                                           |

| 5   | SPI_SDO     | SPI Serial Data Out                                                                                                                          |

| 6   | I²C /~SPI   | I <sup>2</sup> C / SPI selection pin. Connect to VDD for I <sup>2</sup> C (Also connect SPI_CS to VDDIO). Connect to GND for SPI.            |

| 7   | NC          | Not to be Connected                                                                                                                          |

| 8   | SETP        | Set/Reset Strap Positive – S/R Capacitor (C2) Connection                                                                                     |

| 9   | SoC         | Start of Conversion (leading edge active) Connect to Ground when this function/pad is not used in application.                               |

| 10  | C1          | Reservoir Capacitor (C1) Connection                                                                                                          |

| 11  | GND         | Supply Ground                                                                                                                                |

| 12  | SETC        | S/R Capacitor (C2) Connection – Driver Side                                                                                                  |

| 13  | VDDIO       | IO Power Supply (1.71V to VDD)                                                                                                               |

| 14  | NC          | Not to be Connected. No internal connection.                                                                                                 |

| 15  | DRDY        | Data Ready, Interrupt Pin. Internally pulled high. Optional connection. Low for >200 µsec when data are placed in the data output registers. |

| 16  | SDA/SPI_SDI | Serial Data – I <sup>2</sup> C Master/Slave Data or SPI Serial Data In or SPI Serial Data I/O (SDI/O) for 3-wire interface                   |

TOP VIEW (Looking Through)

Arrow indicates direction of magnetic field that generates a positive output reading in Normal Measurement configuration.

#### **PACKAGE OUTLINES**

## PACKAGE DRAWING HMC5983 (16-PIN LPCC, dimensions in millimeters)

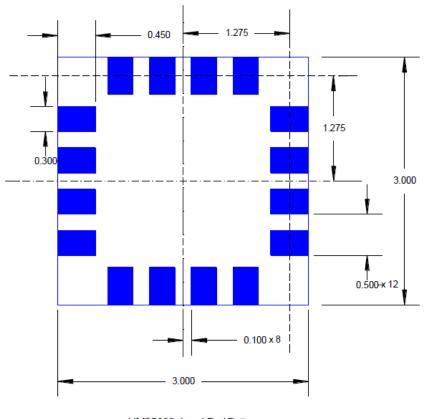

#### **MOUNTING CONSIDERATIONS**

The following is the recommend printed circuit board (PCB) footprint for the HMC5983.

HMC5983 Land Pad Pattern (All dimensions are in mm)

#### LAYOUT CONSIDERATIONS

Besides keeping all components that may contain ferrous materials (nickel, etc.) away from the sensor on both sides of the PCB, it is also recommended that there is no conducting copper under/near the sensor in any of the PCB layers. See recommended layout below.

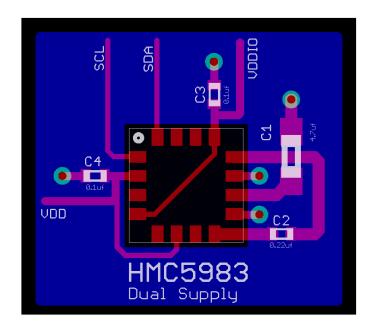

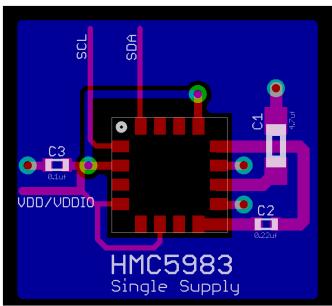

I<sup>2</sup>C Layout Examples: Notice that the one trace under the sensor in the dual supply mode is not expected to carry active current since it is for pin 4 pull-up to VDDIO. Power and ground planes are removed under the sensor to minimize possible source of magnetic noise. For best results, use non-ferrous materials for all exposed copper coding.

\*Layout examples are for [20] (dual supply and single supply) modes only.

#### **PCB Pad Definition and Traces**

The HMC5983 is a fine pitch LCC package. Refer to previous figure for recommended PCB footprint for proper package centering. Size the traces between the HMC5983 and the external capacitors (C1 and C2) to handle the 1 ampere peak current pulses with low voltage drop on the traces.

#### Stencil Design and Solder Paste

A 4 mil stencil and 100% paste coverage is recommended for the electrical contact pads.

#### **Reflow Assembly**

This device is classified as MSL 3 with 260°C peak reflow temperature. A baking process (125°C, 24 hrs) is required if device is not kept continuously in a dry (< 10% RH) environment before assembly. No special reflow profile is required for HMC5983, which is compatible with lead eutectic and lead-free solder paste reflow profiles. Honeywell recommends adherence to solder paste manufacturer's guidelines. Hand soldering is not recommended. Built-in self test can be used to verify device functionalities after assembly.

#### **External Capacitors**

The two external capacitors should be ceramic type construction with low ESR characteristics. The exact ESR values are not critical but values less than 200 milli-ohms are recommended. Reservoir capacitor C1 is nominally 4.7  $\mu$ F in capacitance, with the set/reset capacitor C2 nominally 0.22  $\mu$ F in capacitance. Low ESR characteristics may not be in many small SMT ceramic capacitors (0402), so be prepared to up-size the capacitors to gain Low ESR characteristics.

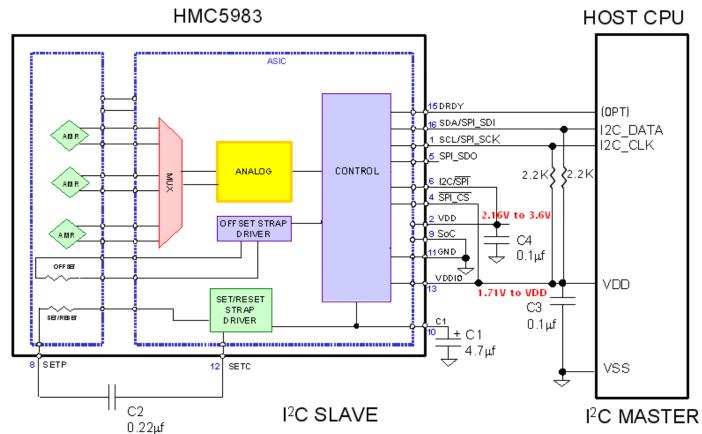

# INTERNAL SCHEMATIC DIAGRAM HMC5983

\*External connections are shown as an example for I2C with dual supplies

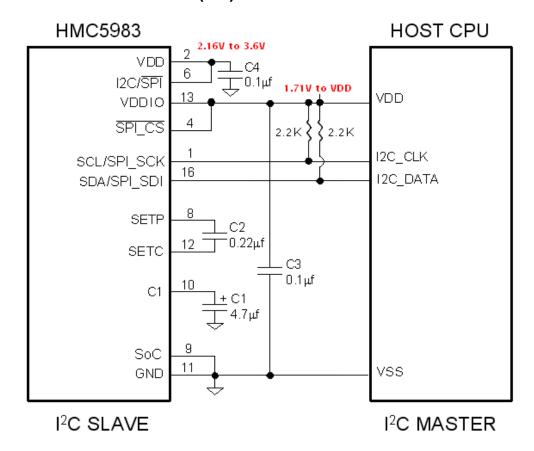

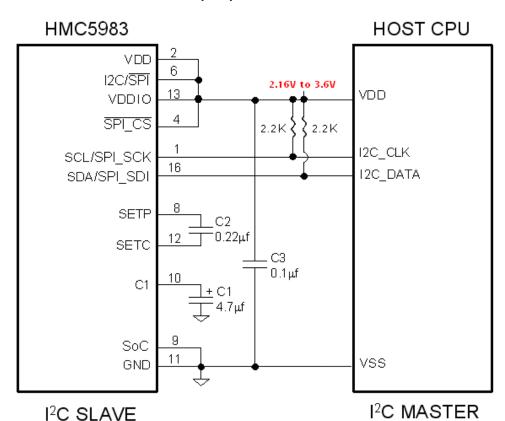

# **DUAL SUPPLY REFERENCE DESIGN (I2C)**

# SINGLE SUPPLY REFERENCE DESIGN (I2C)

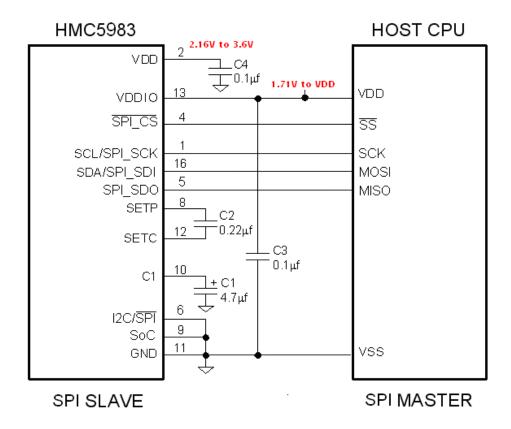

# **DUAL SUPPLY REFERENCE DESIGN (SPI)**

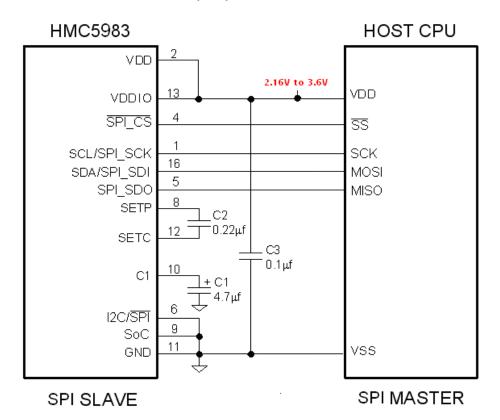

# SINGLE SUPPLY REFERENCE DESIGN (SPI)

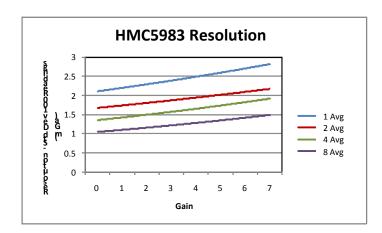

#### **PERFORMANCE**

The following graph(s) highlight HMC5983's performance.

#### **Typical Noise Floor (Field Resolution)**

#### **BASIC DEVICE OPERATION**

#### **Anisotropic Magneto-Resistive Sensors**

The Honeywell HMC5983 magnetoresistive sensor circuit is a trio of sensors and application specific support circuits to measure magnetic fields. With power supply applied, the sensor converts any incident magnetic field in the sensitive axis directions to a differential voltage output. The magnetoresistive sensors are made of a nickel-iron (Permalloy) thin-film and patterned as a resistive strip element. In the presence of a magnetic field, a change in the bridge resistive elements causes a corresponding change in voltage across the bridge outputs.

These resistive elements are aligned together to have a common sensitive axis (indicated by arrows in the pinout diagram) that will provide positive voltage change with magnetic fields increasing in the sensitive direction. Because the output is only proportional to the magnetic field component along its axis, additional sensor bridges are placed at orthogonal directions to permit accurate measurement of magnetic field in any orientation.

#### **Self Test**

To check the HMC5983 for proper operation, a self test feature is incorporated in which the sensor is internally excited with a nominal magnetic field (in either positive or negative bias configuration). This field is then measured and reported. This function is enabled and the polarity is set by bits MS[n] in the configuration register A. An internal current source generates a DC current (about 10 mA) from the VDD supply. This DC current is applied to the offset straps of the magneto-resistive sensor, which creates an artificial magnetic field on the sensor. The difference of this measurement and the measurement of the ambient field will be put in the data output register for each of the three axes. By using this built-in function, the manufacturer can quickly verify the sensor's full functionality after the assembly without additional test setup. The self test results can also be used to estimate/compensate the sensor's sensitivity drift due to temperature.

For each "self test measurement", the ASIC:

- 1. Sends a "Set" pulse

- 2. Takes one measurement (M1)

- 3. Sends the (~10 mA) offset current to generate the (~1.1 Gauss) offset field and takes another measurement (M2)

- 4. Puts the difference of the two measurements in sensor's data output register:

Output = [M2 - M1] (i.e. output = offset field only)

See SELF TEST OPERATION section later in this datasheet for additional details.

#### **Power Management**

This device has two different domains of power supply. The first one is VDD that is the power supply for internal operations and the second one is VDDIO that is dedicated to IO interface. It is possible to work with VDDIO equal to VDD; Single Supply mode, or with VDDIO lower than VDD allowing HMC5983 to be compatible with other devices on board.

#### Communication Bus Interface

This device will be connected to a serial interface bus as a slave device under the control of a master device, such as the processor. Control of this device is carried out via I<sup>2</sup>C or SPI interfaces. Use pin 6 (I<sup>2</sup>C /~SPI) to select between I<sup>2</sup>C and SPI interface modes.

#### I<sup>2</sup>C Interface

This device is compliant with *I*<sup>2</sup>*C* -*Bus Specification*, document number: 9398 393 40011. As an I<sup>2</sup>C compatible device, this device has a 7-bit serial address and supports I<sup>2</sup>C protocols. This device supports standard, fast, and high speed modes, 100kHz, 400kHz, and 3400kHz, respectively. External pull-up resistors are required to support all these modes.

Activities required by the master (register read and write) have priority over internal activities, such as the measurement. The purpose of this priority is to not keep the master waiting and the I<sup>2</sup>C bus engaged for longer than necessary.

#### **SPI Interface**

This device is compliant with both 4-wire and 3-wire SPI interface standards. Selection 3-wire mode is by setting SIM (SPI serial interface mode selection) bit (MR2) in mode register to 1. See SPI Communication Protocol section later in this datasheet for additional details.

#### Internal Clock

The device has an internal clock for internal digital logic functions and timing management. This clock is not available to external usage.

#### H-Bridge for Set/Reset Strap Drive

The ASIC contains large switching FETs capable of delivering a large but brief pulse to the Set/Reset strap of the sensor. This strap is largely a resistive load. There is no need for an external Set/Reset circuit. The controlling of the Set/Reset function is done automatically by the ASIC for each measurement. One half of the difference from the measurements taken after a set pulse and after a reset pulse will be put in the data output register for each of the three axes. By doing so, the sensor's internal offset and its temperature dependence is removed/cancelled for all measurements. The set/reset pulses also effectively remove the past magnetic history (magnetism) in the sensor, if any.

For each "measurement", the ASIC:

- 1. Sends a "Set" pulse

- Takes one measurement (Mset)

- 3. Sends a "Reset" pulse

- 4. Takes another measurement (Mreset)

- 5. Puts the following result in sensor's data output register:

#### Output = [Mset - Mreset] / 2

#### **Charge Current Limit**

The current that reservoir capacitor (C1) can draw when charging is limited for both single supply and dual supply configurations. This prevents drawing down the supply voltage (VDD).

#### **Temperature Compensation**

Temperature compensation of the measured magnetic data is enabled by default at the factory. Temperature measured by the built-in temperature sensor will be used to compensate the sensor's sensitivity change due to temperature based on the sensor's typical sensitivity temperature coefficient. The compensated data will be placed in the Data Output Registers automatically. Temperature sensor must be enabled (set CRA7 =1) for compensation to work.

#### **Temperature Output**

HMC5983 has a built-in temperature sensor that its output can be enabled by setting bit 7 of Configuration Register A (CRA7). This bit is disabled at power-on by default. When this feature is enabled, a temperature measurement will be taken at each magnetic measurement and the output is placed in Temperature Output Registers (0x31 and 0x32).

#### **Automatic Offset Compensation**

HMC5983 automatically adjusts the sensor's internal (bridge) offset to zero before each measurement is taken. This feature allows the full dynamic range of the sensor to be available for measuring the external magnetic field. This feature is particularly important when the gain setting is high (lower GN#) because the dynamic range is smaller at higher gain. As long as the sensor does not saturate within the full range of the external field to be measured, higher gain usually means better resolution and better accuracy.

#### MODES OF OPERATION

This device has several operating modes whose primary purpose is power management and is controlled by the Mode Register. This section describes these modes.

#### **Continuous-Measurement Mode**

During continuous-measurement mode, the device continuously makes measurements, at user selectable rate, and places measured data in data output registers. Data can be re-read from the data output registers if necessary; however, if the master does not ensure that the data register is accessed before the completion of the next measurement, the data output registers are updated with the new measurement. To conserve current between measurements, the device is placed in a state similar to idle mode, but the Mode Register is not changed to Idle Mode. That is, MD[n] bits are unchanged. Settings in the Configuration Register A affect the data output rate (bits DO[n]), the measurement configuration (bits MS[n]), when in continuous-measurement mode. All registers maintain values while in continuous-measurement mode. The I<sup>2</sup>C bus is enabled for use by other devices on the network in while continuous-measurement mode.

#### Single-Measurement Mode

This is the default power-up mode. During single-measurement mode, the device makes a single measurement and places the measured data in data output registers. After the measurement is complete and output data registers are updated, the device is placed in idle mode, and the Mode Register *is* changed to idle mode by setting MD[n] bits. Settings in the configuration register affect the measurement configuration (bits MS[n]) when in single-measurement mode. All registers maintain values while in single-measurement mode. The I<sup>2</sup>C bus is enabled for use by other devices on the network while in single-measurement mode.

#### Idle Mode

During this mode the device is accessible through the I<sup>2</sup>C bus, but major sources of power consumption are disabled, such as, but not limited to, the ADC, the amplifier, and the sensor bias current. All registers maintain values while in idle mode. The I<sup>2</sup>C bus is enabled for use by other devices on the network while in idle mode.

#### **REGISTERS**

This device is controlled and configured via a number of on-chip registers, which are described in this section. In the following descriptions, set implies a logic 1, and *reset* or *clear* implies a logic 0, unless stated otherwise.

#### **Register List**

The table below lists the registers and their access. All address locations are 8 bits.

Table2: Register List

| Address | Location | Name                            | Access     |

|---------|----------|---------------------------------|------------|

| 00      | 0x00     | Configuration Register A        | Read/Write |

| 01      | 0x01     | Configuration Register B        | Read/Write |

| 02      | 0x02     | Mode Register                   | Read/Write |

| 03      | 0x03     | Data Output X MSB Register      | Read       |

| 04      | 0x04     | Data Output X LSB Register      | Read       |

| 05      | 0x05     | Data Output Z MSB Register      | Read       |

| 06      | 0x06     | Data Output Z LSB Register      | Read       |

| 07      | 0x07     | Data Output Y MSB Register      | Read       |

| 08      | 0x08     | Data Output Y LSB Register      | Read       |

| 09      | 0x09     | Status Register                 | Read       |

| 10      | 0x0A     | Identification Register A       | Read       |

| 11      | 0x0B     | Identification Register B       | Read       |

| 12      | 0x0C     | Identification Register C       | Read       |

| 49      | 0x31     | Temperature Output MSB Register | Read       |

| 50      | 0x32     | Temperature Output LSB Register | Read       |

#### **Register Access**

This section describes the process of reading from and writing to this device. The devices uses an address pointer to indicate which register location is to be read from or written to. These pointer locations are sent from the master to this slave device and succeed the 7-bit address (0x1E) plus 1 bit read/write identifier, i.e. 0x3D for read and 0x3C for write.

To minimize the communication between the master and this device, the address pointer updated automatically without master intervention. The register pointer will be incremented by 1 automatically after the current register has been read successfully.

The address pointer value itself cannot be read via the I2C bus.

Any attempt to read an invalid address location returns 0's, and any write to an invalid address location or an undefined bit within a valid address location is ignored by this device.

To move the address pointer to a random register location, first issue a "write" to that register location with no data byte following the commend. For example, to move the address pointer to register 10, send 0x3C 0x0A.

#### **Configuration Register A**

The configuration register is used to configure the device for setting the data output rate and measurement configuration. CRA0 through CRA7 indicate bit locations, with *CRA* denoting the bits that are in the configuration register. CRA7 denotes the first bit of the data stream. The number in parenthesis indicates the default value of that bit.CRA default is 0x10.

Table 3: Configuration Register A

| CRA7 | CRA6   | CRA5   | CRA4    | CRA3    | CRA2    | CRA1    | CRA0    |

|------|--------|--------|---------|---------|---------|---------|---------|

| (0)  | MA1(0) | MA0(0) | DO2 (1) | DO1 (0) | DO0 (0) | MS1 (0) | MS0 (0) |

Table 4: Configuration Register A Bit Designations

| Location     | Name       | Description                                                                                                                                                                                        |

|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CRA7         | TS         | Set this bit to enable temperature sensor. Temperature sensor will be measured at each magnetic measurement. Enable Temperature sensor for automatic compensation of Sensitivity over temperature. |

| CRA6 to CRA5 | MA1 to MA0 | Select number of samples averaged (1 to 8) per measurement output.  00 = 1(Default); 01 = 2; 10 = 4; 11 = 8                                                                                        |

| CRA4 to CRA2 | DO2 to DO0 | Data Output Rate Bits. These bits set the rate at which data is written to all three data output registers.                                                                                        |

| CRA1 to CRA0 | MS1 to MS0 | Measurement Configuration Bits. These bits define the measurement flow of the device, specifically whether or not to incorporate an applied bias into the measurement.                             |

The Table below shows all selectable output rates in continuous measurement mode. All three channels shall be measured within a given output rate. Other output rates with maximum rate of 160 Hz can be achieved by monitoring DRDY interrupt pin in single measurement mode.

Table 5: Data Output Rates

| DO2 | DO1 | DO0 | Typical Data Output Rate (Hz) |

|-----|-----|-----|-------------------------------|

| 0   | 0   | 0   | 0.75                          |

| 0   | 0   | 1   | 1.5                           |

| 0   | 1   | 0   | 3                             |

| 0   | 1   | 1   | 7.5                           |

| 1   | 0   | 0   | 15 (Default)                  |

| 1   | 0   | 1   | 30                            |

| 1   | 1   | 0   | 75                            |

| 1   | 1   | 1   | 220                           |

Table 6: Measurement Modes

| MS1 | MS0 | Measurement Mode                                                                                                                                                                                                       |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Normal measurement configuration (Default). In normal measurement configuration the device follows normal measurement flow. The positive and negative pins of the resistive load are left floating and high impedance. |

| 0   | 1   | Positive bias configuration for X, Y, and Z axes. In this configuration, a positive current is forced across the resistive load for all three axes.                                                                    |

| 1   | 0   | Negative bias configuration for X, Y and Z axes. In this configuration, a negative current is forced across the resistive load for all three axes.                                                                     |

| 1   | 1   | Temperature sensor only. Magnetic sensor will not be enabled during measurement.                                                                                                                                       |

#### **Configuration Register B**

The configuration register B for setting the device gain. CRB0 through CRB7 indicate bit locations, with *CRB* denoting the bits that are in the configuration register. CRB7 denotes the first bit of the data stream. The number in parenthesis indicates the default value of that bit. CRB default is 0x20.

Table 7: Configuration B Register

| CRB7    | CRB6    | CRB5    | CRB4 | CRB3 | CRB2 | CRB1 | CRB0 |

|---------|---------|---------|------|------|------|------|------|

| GN2 (0) | GN1 (0) | GN0 (1) | (0)  | (0)  | (0)  | (0)  | (0)  |

Table 8: Configuration Register B Bit

| Designations<br>Location | Name       | Description                                                                                                               |

|--------------------------|------------|---------------------------------------------------------------------------------------------------------------------------|

| CRB7 to CRB5             | GN2 to GN0 | Gain Configuration Bits. These bits configure the gain for the device. The gain configuration is common for all channels. |

| CRB4 to CRB0             | N/A        | These bits must be cleared for correct operation.                                                                         |

The table below shows nominal gain settings. Use the "Gain" column to convert counts to Gauss. The "Digital Resolution" column is the theoretical value in term of milli-Gauss per count (LSb) which is the inverse of the values in the "Gain" column. The effective resolution of the usable signal also depends on the noise floor of the system, i.e.

Effective Resolution = Max (Digital Resolution, Noise Floor)

Choose a lower gain value (higher GN#) when total field strength causes overflow in one of the data output registers (saturation). Note that the very first measurement after a gain change maintains the same gain as the previous setting. The new gain setting is effective from the second measurement and on.

Table 9: Gain Settings

| GN2 | GN1 | GN0 | Recommended<br>Sensor Field<br>Range | Gain<br>(LSb/<br>Gauss) | Digital<br>Resolution<br>(mG/LSb) | Output Range                  |

|-----|-----|-----|--------------------------------------|-------------------------|-----------------------------------|-------------------------------|

| 0   | 0   | 0   | ± 0.88 Ga                            | 1370                    | 0.73                              | 0xF800-0x07FF<br>(-2048-2047) |

| 0   | 0   | 1   | ± 1.3 Ga                             | 1090 (default)          | 0.92                              | 0xF800-0x07FF<br>(-2048-2047) |

| 0   | 1   | 0   | ± 1.9 Ga                             | 820                     | 1.22                              | 0xF800-0x07FF<br>(-2048-2047) |

| 0   | 1   | 1   | ± 2.5 Ga                             | 660                     | 1.52                              | 0xF800-0x07FF<br>(-2048-2047) |

| 1   | 0   | 0   | ± 4.0 Ga                             | 440                     | 2.27                              | 0xF800-0x07FF<br>(-2048-2047) |

| 1   | 0   | 1   | ± 4.7 Ga                             | 390                     | 2.56                              | 0xF800-0x07FF<br>(-2048-2047) |

| 1   | 1   | 0   | ± 5.6 Ga                             | 330                     | 3.03                              | 0xF800-0x07FF<br>(-2048-2047) |

| 1   | 1   | 1   | ± 8.1 Ga                             | 230                     | 4.35                              | 0xF800-0x07FF<br>(-2048-2047) |

#### **Mode Register**

The mode register is an 8-bit register from which data can be read or to which data can be written. This register is used to select the operating mode of the device. MR0 through MR7 indicate bit locations, with *MR* denoting the bits that are in the mode register. MR7 denotes the first bit of the data stream. The number in parenthesis indicates the default value of that bit. Mode register default is 0x01.

Table 10: Mode Register

| MR7 | MR6 | MR5 | MR4 | MR3 | MR2 | MR1     | MR0     |

|-----|-----|-----|-----|-----|-----|---------|---------|

| (0) | (0) | (0) | (0) | (0) | (0) | MD1 (0) | MD0 (1) |

Table 11: Mode Register Bit Designations

| Location      | Name          | Description                                                                          |  |  |  |  |

|---------------|---------------|--------------------------------------------------------------------------------------|--|--|--|--|

| MR7           | HS            | Set this pin to enable I <sup>2</sup> C High Speed mode, 3400 kHz.                   |  |  |  |  |

| MR6           | N/A           | Clear this bit for correct operation.                                                |  |  |  |  |

| MR5           | LP            | Lowest power mode. When set, ODR=0.75 Hz, and Averaging = 1.                         |  |  |  |  |

| MR4           | N/A           | This bit has no functionality.                                                       |  |  |  |  |

| MR3           | N/A           | Clear this bit for correct operation.                                                |  |  |  |  |

| MR2           | SIM           | SPI serial interface mode selection: 0: 4-wire SPI interface 1: 3-wire SPI interface |  |  |  |  |

| MR1 to<br>MR0 | MD1 to<br>MD0 | Mode Select Bits. These bits select the operation mode of this device.               |  |  |  |  |

Table 12: Operating Modes

| MD1 | MD0 | Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | Continuous-Measurement Mode. In continuous-measurement mode, the device continuously performs measurements and places the result in the data register. RDY goes high when new data is placed in all three registers. After a power-on or a write to the mode or configuration register, the first measurement set is available from all three data output registers after a period of $2/f_{DO}$ and subsequent measurements are available at a frequency of $f_{DO}$ , where $f_{DO}$ is the frequency of data output. |

| 0   | 1   | Single-Measurement Mode (Default). When single-measurement mode is selected, device performs a single measurement, sets RDY high and returned to idle mode. Mode register returns to idle mode bit values. The measurement remains in the data output register and RDY remains high until the data output register is read or another measurement is performed.                                                                                                                                                         |

| 1   | 0   | Idle Mode. Device is placed in idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1   | 1   | Idle Mode. Device is placed in idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Data Output X Registers A and B

The data output X registers are two 8-bit registers, data output register A and data output register B. These registers store the measurement result from channel X. Data output X register A contains the MSB from the measurement result, and data output X register B contains the LSB from the measurement result. The value stored in these two registers is a 16-bit value in 2's complement form, whose range is 0xF800 to 0x07FF. DXRA0 through DXRA7 and DXRB0 through DXRB7 indicate bit locations, with DXRA and DXRB denoting the bits that are in the data output X registers. DXRA7 and DXRB7 denote the first bit of the data stream. The number in parenthesis indicates the default value of that bit.

In the event the ADC reading overflows or underflows for the given channel, or if there is a math overflow during the bias measurement, this data register will contain the value -4096. This register value will clear when after the next valid measurement is made.

| DXRA7 | DXRA6 | DXRA5 | DXRA4 | DXRA3 | DXRA2 | DXRA1 | DXRA0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

| DXRB7 | DXRB6 | DXRB5 | DXRB4 | DXRB3 | DXRB2 | DXRB1 | DXRB0 |

| (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

Table 13: Data Output X Registers A and B

#### Data Output Y Registers A and B

The data output Y registers are two 8-bit registers, data output register A and data output register B. These registers store the measurement result from channel Y. Data output Y register A contains the MSB from the measurement result, and data output Y register B contains the LSB from the measurement result. The value stored in these two registers is a 16-bit value in 2's complement form, whose range is 0xF800 to 0x07FF. DYRA0 through DYRA7 and DYRB0 through DYRB7 indicate bit locations, with *DYRA* and *DYRB* denoting the bits that are in the data output Y registers. DYRA7 and DYRB7 denote the first bit of the data stream. The number in parenthesis indicates the default value of that bit.

In the event the ADC reading overflows or underflows for the given channel, or if there is a math overflow during the bias measurement, this data register will contain the value -4096. This register value will clear when after the next valid measurement is made.

| DYRA7 | DYRA6 | DYRA5 | DYRA4 | DYRA3 | DYRA2 | DYRA1 | DYRA0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

| DYRB7 | DYRB6 | DYRB5 | DYRB4 | DYRB3 | DYRB2 | DYRB1 | DYRB0 |

| (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

Table 14: Data Output Y Registers A and B

#### Data Output Z Registers A and B

The data output Z registers are two 8-bit registers, data output register A and data output register B. These registers store the measurement result from channel Z. Data output Z register A contains the MSB from the measurement result, and data output Z register B contains the LSB from the measurement result. The value stored in these two registers is a 16-bit value in 2's complement form, whose range is 0xF800 to 0x07FF. DZRA0 through DZRA7 and DZRB0 through DZRB7 indicate bit locations, with DZRA and DZRB denoting the bits that are in the data output Z registers. DZRA7 and DZRB7 denote the first bit of the data stream. The number in parenthesis indicates the default value of that bit.

In the event the ADC reading overflows or underflows for the given channel, or if there is a math overflow during the bias measurement, this data register will contain the value -4096. This register value will clear when after the next valid measurement is made.

Table 15: Data Output Z Registers A and B

| DZRA7 | DZRA6 | DZRA5 | DZRA4 | DZRA3 | DZRA2 | DZRA1 | DZRA0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

| DZRB7 | DZRB6 | DZRB5 | DZRB4 | DZRB3 | DZRB2 | DZRB1 | DZRB0 |

| (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   | (0)   |

#### **Data Output Register Operation**

When one or more of the output registers are read, new data cannot be placed in any of the output data registers until all six data output registers are read. This requirement also impacts DRDY and RDY, which cannot be cleared until new data is placed in all the output registers.

#### **Status Register**

The status register is an 8-bit read-only register. This register is used to indicate device status. SR0 through SR7 indicate bit locations, with *SR* denoting the bits that are in the status register. SR7 denotes the first bit of the data stream.

Table 16: Status Register

| SR7 | SR6 | SR5 | SR4 | SR3 | SR2 | SR1      | SR0    |

|-----|-----|-----|-----|-----|-----|----------|--------|

| (0) | (0) | (0) | (0) | (0) | (0) | LOCK (0) | RDY(0) |

Table 17: Status Register Bit Designations

| Location      | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR7 to<br>SR5 | 0    | These bits are reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SR4           | DOW  | Data Over Written. Set when the measurement data are not read before the subsequent data measurements are posted to the output registers. This happens when master device skips reading one or more data samples. Bit is cleared at the beginning of a data read.                                                                                                                                                                                                                                 |

| DR3 to<br>DR2 | N/A  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SR1           | LOCK | Data output register lock. This bit is set when:  1.some but not all of of the six data output registers have been read,  2. Mode register has been read.  When this bit is set, the six data output registers are locked and any new data will not be placed in these register until one of these conditions are met:  1.all six bytes have been read and the next measurement starts,  2. The mode register is written,  3. The measurement configuration (CRA) is written,  4. Power is reset. |

| SR0           | RDY  | Ready Bit. Set when data is written to all six data registers. Cleared when device initiates a write to the data output registers and after one or more of the data output registers are written to. When RDY bit is clear it shall remain cleared for >200 µs. DRDY pin can be used as an alternative to the status register for monitoring the device for measurement data.                                                                                                                     |

### **Identification Register A**

The identification register A is used to identify the device. IRA0 through IRA7 indicate bit locations, with *IRA* denoting the bits that are in the identification register A. IRA7 denotes the first bit of the data stream. The number in parenthesis indicates the default value of that bit.

The identification value for this device is stored in this register. This is a read-only register. Register values. ASCII value  ${\cal H}$

Table 18: Identification Register A Default Values

| IRA7 | IRA6 | IRA5 | IRA4 | IRA3 | IRA2 | IRA1 | IRA0 |

|------|------|------|------|------|------|------|------|

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    |

#### **Identification Register B**

The identification register B is used to identify the device. IRB0 through IRB7 indicate bit locations, with *IRB* denoting the bits that are in the identification register A. IRB7 denotes the first bit of the data stream.

Register values. ASCII value 4

Table 19: Identification Register B Default Values

| IRB7 | IRB6 | IRB5 | IRB4 | IRB3 | IRB2 | IRB1 | IRB0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    |

#### Identification Register C

The identification register C is used to identify the device. IRC0 through IRC7 indicate bit locations, with *IRC* denoting the bits that are in the identification register A. IRC7 denotes the first bit of the data stream.

Register values. ASCII value 3

Table 20: Identification Register C Default Values

| IRC7 | IRC6 | IRC5 | IRC4 | IRC3 | IRC2 | IRC1 | IRC0 |

|------|------|------|------|------|------|------|------|

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    |

#### Temperature Output Registers H and L

The temperature output registers are two 8-bit registers, temperature output register H and temperature output register L. These registers store the measurement result from the internal temperature sensor. Temperature output register H contains the MSB from the measurement result, and temperature output register L contains the LSB from the measurement result. The value stored in these two registers is a 16-bit value in 2's complement form, whose range is 0xF800 to 0x07FF. TEMPH0 through TEMPH7 and TEMPL0 through TEMPL7 indicate bit locations, with *TEMPH* and *TEMPL* denoting the bits that are in the temperature output registers. TEMPH7 and TEMPL7 denote the first bit of the data stream. The number in parenthesis indicates the default value of that bit.

Table 21: Temperature Output Registers H and L

| ТЕМРН7  | ТЕМРН 6 | ТЕМРН 5 | TEMPH 4 | ТЕМРН 3 | TEMPH 2 | TEMPH 1 | TEMPH 0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| (0)     | (0)     | (0)     | (0)     | (0)     | (0)     | (0)     | (0)     |

| TEMPL 7 | TEMPL 6 | TEMPL 5 | TEMPL 4 | TEMPL 3 | TEMPL 2 | TEMPL 1 | TEMPL 0 |

| (0)     | (0)     | (0)     | (0)     | (0)     | (0)     | (0)     | (0)     |

Temperature output in °C is related to the temperature output register values as follows.

Temperature = (MSB \* 2^8 + LSB) / (2^4 \* 8) + 25 in °C

#### I<sup>2</sup>C COMMUNICATION PROTOCOL

If selected, the HMC5983 communicates via a two-wire I²C bus system as a slave device. The HMC5983 uses a simple protocol with the interface protocol defined by the I²C bus specification, and by this document. The data rate is at the standard-mode 100kbps, 400kbps, or 3400kbps rates as defined in the I²C Bus Specifications. The bus bit format is an 8-bit Data/Address send and a 1-bit acknowledge bit. The format of the data bytes (payload) shall be case sensitive ASCII characters or binary data to the HMC5983 slave, and binary data returned. Negative binary values will be in two's complement form. The default (factory) HMC5983 8-bit slave address is 0x3C for write operations, or 0x3D for read operations.

The HMC5983 Serial Clock (SCL) and Serial Data (SDA) lines require resistive pull-ups (Rp) between the master device (usually a host microprocessor) and the HMC5983. Pull-up resistance values of about 2.2K to 10K ohms are recommended with a nominal VDDIO voltage. Other resistor values may be used as defined in the I<sup>2</sup>C Bus Specifications that can be tied to VDDIO.

The SCL and SDA lines in this bus specification may be connected to multiple devices. The bus can be a single master to multiple slaves, or it can be a multiple master configuration. All data transfers are initiated by the master device, which is responsible for generating the clock signal, and the data transfers are 8 bit long. All devices are addressed by I<sup>2</sup>C 's unique 7-bit address. After each 8-bit transfer, the master device generates a 9<sup>th</sup> clock pulse, and releases the SDA line. The receiving device (addressed slave) will pull the SDA line low to acknowledge (ACK) the successful transfer or leave the SDA high to negative acknowledge (NACK).

Per the I<sup>2</sup>C spec, all transitions in the SDA line must occur when SCL is low. This requirement leads to two unique conditions on the bus associated with the SDA transitions when SCL is high. Master device pulling the SDA line low while the SCL line is high indicates the Start (S) condition, and the Stop (P) condition is when the SDA line is pulled high while the SCL line is high. The I<sup>2</sup>C protocol also allows for the Restart condition in which the master device issues a second start condition without issuing a stop.

All bus transactions begin with the master device issuing the start sequence followed by the slave address byte. The address byte contains the slave address; the upper 7 bits (bits7-1), and the Least Significant bit (LSb). The LSb of the address byte designates if the operation is a read (LSb=1) or a write (LSb=0). At the 9<sup>th</sup> clock pulse, the receiving slave device will issue the ACK (or NACK). Following these bus events, the master will send data bytes for a write operation, or the slave will clock out data with a read operation. All bus transactions are terminated with the master issuing a stop sequence.

I<sup>2</sup>C bus control can be implemented with either hardware logic or in software. Typical hardware designs will release the SDA and SCL lines as appropriate to allow the slave device to manipulate these lines. In a software implementation, care must be taken to perform these tasks in code.

#### SPI COMMUNICATION PROTOCOL

If selected, the HMC5983 communicates via a 3-wire or 4-wire SPI bus as a slave device. The SPI allows writing and reading the registers of the device.

The standard Serial Interface interacts with the outside world with 4 wires: **CS**, **SCK**, **SDI** and **SDO** that correspond to commonly used notations **SS**, **SCK**, **MOSI** and **MISO**, respectively.

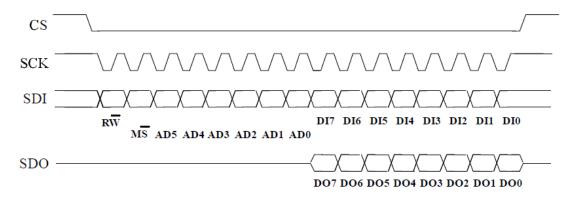

#### Read and Write protocol

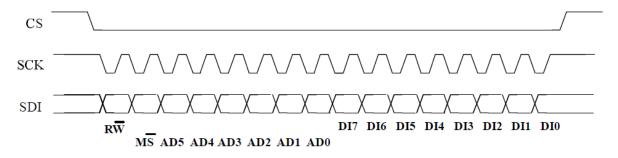

Figure 1: Read & Write Protocol

CS (SPI\_CS) is the Serial Port Enable and it is controlled by the SPI master. It goes low at the start of the transmission and goes back high at the end. SCK (SPI\_SCK) is the Serial Port Clock and it is controlled by the SPI master. It is stopped high when CS is high (no transmission). SDI (SPI\_SDI) and SDO (SPI\_SDO) are respectively the Serial Port Data Input and Output. Those lines are driven at the falling edge of SCK and should be captured at the rising edge of SCK.

Both the Read Register and Write Register commands are completed in 16 clocks pulses or in multiple of 8 in case of multiple byte read/write. Bit duration is the time between two falling edges of **SCK**. The first bit (bit 0) starts at the first falling edge of **SCK** after the falling edge of **SCK** while the last bit (bit 15, bit 23, ...) starts at the last falling edge of **SCK** (SPI\_CS) just before the rising edge of **CS**.

bit 0: RW bit. When 0, the data DI(7:0) is written into the device. When 1, the data DO(7:0) from the device is read. In latter case, the chip will drive **SDO** at the start of bit 8.

bit 1: MS bit. When 0, the address will remain unchanged in multiple read/write commands. When 1, the address will be auto incremented in multiple read/write commands.

bit 2-7: address AD(5:0). This is the address field of the indexed register.

bit 8-15: data DI(7:0) (write mode). This is the data that will be written into the device (MSb first).

bit 8-15: data DO(7:0) (read mode). This is the data that will be read from the device (MSb first).

In multiple read/write commands further blocks of 8 clock periods will be added. When MS bit is 0 the address used to read/write data remains the same for every block. When MS bit is 1 the address used to read/write data is incremented at every block.

The function and the behavior of **SDI** and **SDO** remain unchanged.

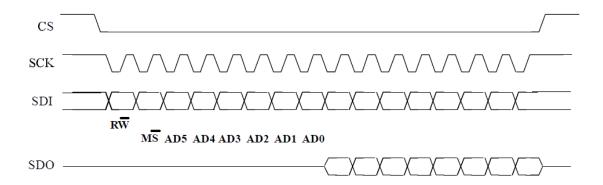

#### SPI Read

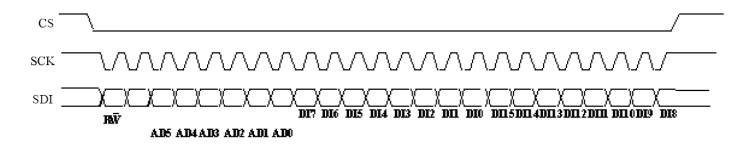

Figure 2: SPI Read Protocol

The SPI Read command is performed with 16 clocks pulses. Multiple byte read command is performed adding blocks of 8 clocks pulses at the previous one.

bit 0: READ bit. The value is 1.

bit 1: MS bit. When 0 do not increment address, when 1 increment address in multiple reading.

bit 2-7: address AD(5:0). This is the address field of the indexed register.

bit 8-15: data DO(7:0) (read mode). This is the data that will be read from the device (MSb first).

bit 16-...: data DO(...-8). Further data in multiple byte reading.

Figure 3: Multiple Bytes SPI Read Protocol (2 bytes example)

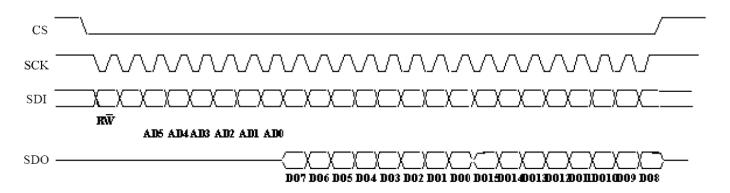

#### SPI Write

Figure 4: SPI Write Protocol

The SPI Write command is performed with 16 clocks pulses. Multiple byte write command is performed adding blocks of 8 clocks pulses at the previous one.

bit 0: WRITE bit. The value is 0.

bit 1: MS bit. When 0 do not increment address, when 1 increment address in multiple writing.

bit 2 -7: address AD(5:0). This is the address field of the indexed register.

bit 8-15: data DI(7:0) (write mode). This is the data that will be written inside the device (MSb first).

bit 16-...: data DI(...-8). Further data in multiple byte writing.

Figure 5: Multiple bytes SPI Write Protocol (2 bytes example)

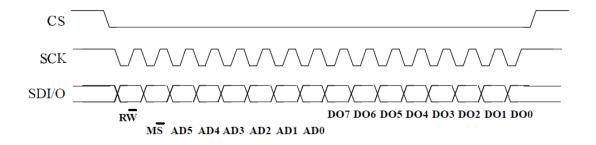

#### SPI Read in 3-wires mode

3-wires mode is entered by setting to 1 bit SIM (SPI Serial Interface Mode selection) in MODE\_REG(2).

Figure 6: SPI Read Protocol in 3-wires Mode

The SPI Read command is performed with 16 clocks pulses:

bit 0: READ bit. The value is 1.

bit 1: MS bit. When 0 do not increment address, when 1 increment address in multiple reading.

bit 2-7: address AD(5:0). This is the address field of the indexed register.

bit 8-15: data DO(7:0) (read mode). This is the data that will be read from the device (MSb first).

Multiple write command is also available in 3-wires mode.

#### I<sup>2</sup>C OPERATIONAL EXAMPLES

The HMC5983 has a fairly quick stabilization time from no voltage to stable and ready for data retrieval. The nominal 56 milli-seconds with the factory default single measurement mode means that the six bytes of magnetic data registers (DXRA, DXRB, DZRA, DZRB, DYRA, and DYRB) are filled with a valid first measurement.

To change the measurement mode to continuous measurement mode, after the power-up time send the three bytes:

0x3C 0x02 0x00

This writes the 00 into the second register or mode register to switch from single to continuous measurement mode setting. With the data rate at the factory default of 15Hz updates, a 67 milli-second typical delay should be allowed by the I<sup>2</sup>C master before querying the HMC5983 data registers for new measurements. To clock out the new data, send:

0x3D, and clock out DXRA, DXRB, DZRA, DZRB, DYRA, and DYRB located in registers 3 through 8. The HMC5983 will automatically re-point back to register 3 for the next 0x3D query. All six data registers must be read properly before new data can be placed in any of these data registers.

Below is an example of a (power-on) initialization process for "continuous-measurement mode" via I<sup>2</sup>C interface:

- 1. Write CRA (00) send **0x3C 0x00 0x70** (8-average, 15 Hz default, normal measurement)

- 2. Write CRB (01) send **0x3C 0x01 0xA0** (Gain=5, or any other desired gain)

- 3. Write Mode (02) send **0x3C 0x02 0x00** (Continuous-measurement mode)

- 4. Wait 6 ms or monitor status register or DRDY hardware interrupt pin

- 5. Loop

Send **0x3D 0x06** (Read all 6 bytes. If gain is changed then this data set is using previous gain) Convert three 16-bit 2's compliment hex values to decimal values and assign to X, Z, Y, respectively. Send **0x3C 0x03** (point to first data register 03)

Wait about 67 ms (if 15 Hz rate) or monitor status register or DRDY hardware interrupt pin

End\_loop

Below is an example of a (power-on) initialization process for "single-measurement mode" via I<sup>2</sup>C interface:

- 1. Write CRA (00) send **0x3C 0x00 0x70** (8-average, 15 Hz default or any other rate, normal measurement)

- 2. Write CRB (01) send **0x3C 0x01 0xA0** (Gain=5, or any other desired gain)

- 3. For each measurement query:

Write Mode (02) – send **0x3C 0x02 0x01** (Single-measurement mode)

Wait 6 ms or monitor status register or DRDY hardware interrupt pin

Send **0x3D 0x06** (Read all 6 bytes. If gain is changed then this data set is using previous gain)

Convert three 16-bit 2's compliment hex values to decimal values and assign to X, Z, Y, respectively.

#### SPI OPERATIONAL EXAMPLES

| To read Configuration B register Lower CS line Write 0x81 to the SPI bus Read 1 byte from SPI bus Raise CS line                                                 | To read Status Lower CS line Write 0x89 to the SPI bus Read 1 byte from SPI bus Raise CS line |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| To write Configuration B register Lower CS line Write 0x01 to the SPI bus Write 0xVV to the SPI bus (VV is the value to be written to register B) Raise CS line | To read output Lower CS line Write 0xC3 to the SPI bus Read 6 byte from SPI bus Raise CS line |

#### **SELF TEST OPERATION**

To check the HMC5983 for proper operation, a self test feature is incorporated in which the sensor offset straps are excited to create a nominal field strength (bias field) to be measured. To implement self test, the least significant bits (MS1 and MS0) of configuration register A are changed from 00 to 01 (positive bias) or 10 (negative bias).

Then, by placing the mode register into single or continuous-measurement mode, two data acquisition cycles will be made on each magnetic vector. The first acquisition will be a set pulse followed shortly by measurement data of the external field. The second acquisition will have the offset strap excited (about 10 mA) in the positive bias mode for X, Y, and Z axes to create about a 1.1 gauss self test field plus the external field. The first acquisition values will be subtracted from the second acquisition, and the net measurement will be placed into the data output registers.

Since self test adds ~1.1 Gauss additional field to the existing field strength, using a reduced gain setting prevents the sensor from being saturated and the data registers from overflowing. For example, if the configuration register B is set to 0xA0 (Gain=5), values around +452 LSb (1.16 Ga \* 390 LSb/Ga) will be placed in the X and Y data output registers and around +421 (1.08 Ga \* 390 LSb/Ga) will be placed in Z data output register. To leave the self test mode, change MS1 and MS0 bit of the configuration register A back to 00 (Normal Measurement Mode). Acceptable limits of the self test values depend on the gain setting. Limits for Gain=5 are provided in the specification table.

Below is an example of a "positive self test" process using continuous-measurement mode via I<sup>2</sup>C interface:

- 1. Write CRA (00) send **0x3C 0x00 0x71** (8-average, 15 Hz default, positive self test measurement)

- 2. Write CRB (01) send **0x3C 0x01 0xA0** (Gain=5)

- 3. Write Mode (02) send **0x3C 0x02 0x00** (Continuous-measurement mode)

- 4. Wait 6 ms or monitor status register or DRDY hardware interrupt pin

- 5. Loop

Send **0x3D 0x06** (Read all 6 bytes. If gain is changed then this data set is using previous gain) Convert three 16-bit 2's compliment hex values to decimal values and assign to X, Z, Y, respectively. Send **0x3C 0x03** (point to first data register 03)

Wait about 67 ms (if 15 Hz rate) or monitor status register or DRDY hardware interrupt pin

End loop

6. Check limits -

If all 3 axes (X, Y, and Z) are within reasonable limits (243 to 575 for Gain=5, adjust these limits based on the gain setting used. See an example below.) Then

All 3 axes pass positive self test

Write CRA (00) – send **0x3C 0x00 0x70** (Exit self test mode and this procedure)

Else

If Gain<7

Write CRB (01) – send **0x3C 0x01 0xn0** (Increase gain setting to next value; *n*, and retry. Skip the next data set)

Else

At least one axis did not pass positive self test

Write CRA (00) – send **0x3C 0x00 0x70** (Exit self test mode and this procedure)

End If

Below is an example of how to adjust the "positive self test" limits based on the gain setting:

1. If Gain = 6, self test limits are: Low Limit = 243 \* 330/390 = 206 High Limit = 575 \* 330/390 = 487

2. If Gain = 7, self test limits are: Low Limit = 243 \* 230/390 = 143 High Limit = 575 \* 230/390 = 339

#### ORDERING INFORMATION

| Ordering Number | Product                      |

|-----------------|------------------------------|

| HMC5983-TR      | Tape and Reel 4k pieces/reel |

#### Caution

This part is sensitive to damage by electrostatic discharge. Use ESD precautionary procedures when touching, removing or inserting.

**CAUTION: ESDS CAT. 1B**

#### FIND OUT MORE

For more information on Honeywell's Magnetic Sensors visit us online at www.magneticsensors.com or contact us at 800-323-8295 (763-954-2474 internationally).

The application circuits herein constitute typical usage and interface of Honeywell product. Honeywell does not warranty or assume liability of customer-designed circuits derived from this description or depiction.

Honeywell reserves the right to make changes to improve reliability, function or design. Honeywell does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

U.S. Patents 4,441,072, 4,533,872, 4,569,742, 4,681,812, 4,847,584 and 6,529,114 apply to the technology described

Honeywell

Honeywell 12001 Highway 55 Plymouth, MN 55441 Tel: 800-323-8295 www.magneticsensors.com

Form # 900425 September 2011 ©2011 Honeywell International Inc.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for honeywell manufacturer:

Other Similar products are found below:

MML93J 3010A 5VP1 5VP2 LZJ3-7M V7-2B27E9 LTPCTAA50UEBITX01 MPRLS0001PG0000SAB LZZ7J3-7M 76072-00000150-15

NSCDRRN030PDUNV 5SM3-TN196 NSCDRRN001PGUNV 14CE2-2 91MCE2-S5 SE3450-013 GLLA06A1B 3600080010001 23944-01

53C110K 58C1-25 58C1-3K 591SXP56S252SC 5ML1-E1 5SE1-12 602HE1-6 604HE223-6B 61CX11-D01 624HE17-RB M3050A13

64AT22-3D 66AT23-7 6AT3-T 6HM7-6 MA215HT-96 6PA104 6PA148-E6 701PB580 70B1N056S202W 727033 EXD-AR20

MD3211Q16 76054-00000700-01 76061-00000015-15 76061-B00000020-01 76078-00000350-01 76078-B00000400-01 76580-00000130-01

76584-M00000100-24 F78EA502