### PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### **General Description**

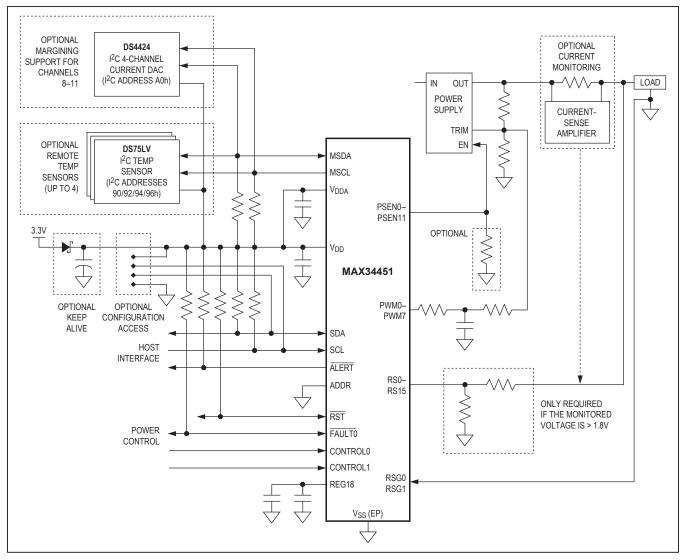

The MAX34451 is a power-supply system manager that is capable of monitoring up to 16 different voltage rails or currents and is also capable of sequencing and margining up to 12 power supplies. The system manager monitors the power-supply output voltages and currents and constantly checks them for user programmable over and under threshold limits. If a fault is detected, the device automatically shuts down the system in an orderly fashion. The device can sequence the supplies in any order at both power-up and power-down. The device has the ability to close-loop margin the power-supply output voltages up or down to a user-programmable level. The device contains an internal temperature sensor and can support up to four external remote temperature sensors. Once configured, the device can operate autonomously without any host intervention.

#### **Applications**

- Network Switches/Routers

- Base Stations

- Servers

- Smart Grid Network Systems

PMBus is a trademark of SMIF, Inc.

<u>Ordering Information and Typical Operating Circuit</u> appear at end of data sheet.

#### **Benefits and Features**

- Integration Enables Management of Multiple Power Supplies to Maximize System Performance

- 16 Channels of Voltage or Current Monitoring

- 12 Channels of Sequencing and Margining (8 PWM, 4 External Current DACs (1 x DS4424), and Sequencing

- Expandable Channel Operation with Parallel Devices

- Remote Ground Sensing Improves Measurement Accuracy

- Programmable Up and Down Time-Based or Event-Based Sequencing

- Dual Sequencing Loops

- Configurable Combinatorial Logic Supporting Up to 16 GPIs and 20 GPOs

- Automatic Closed-Loop Margining

- No External Clocking Required

- PMBus™-Compliant Command Interface

- Fast, Reliable Control and Fault Detection Improves System Reliability

- Fast Minimum/Maximum Threshold Excursion

Detection

- Supports Up to 5 Temperature Sensors (1 Internal and 4 Remote)

- Fault Detection on All Temperature Sensors

- Reports Peak, Minimum, and Average Levels for a Number of Parameters

- Programmable Alarm Outputs

- On-Board Nonvolatile Black Box Fault Logging and Default Configuration Setting

- I<sup>2</sup>C-/SMBus-Compatible Serial Bus with Bus Time-Out Function Simplifies Additional Temperature Sensors and DACs to the MAX34451

- +3.0V to +3.6V Supply Voltage

### PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### **Benefits and Features** Absolute Maximum Ratings ..... Pin Description..... 14

#### TABLE OF CONTENTS

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

|    | Interpreting Received DIRECT Format Values | .27 |

|----|--------------------------------------------|-----|

|    | Sending a DIRECT Format Value              | 28  |

|    | Fault Management and Reporting             | 29  |

|    | Password Protection                        | 31  |

|    | Power-Supply Sequencing                    | 31  |

|    | Dual-Loop Sequencing                       | 31  |

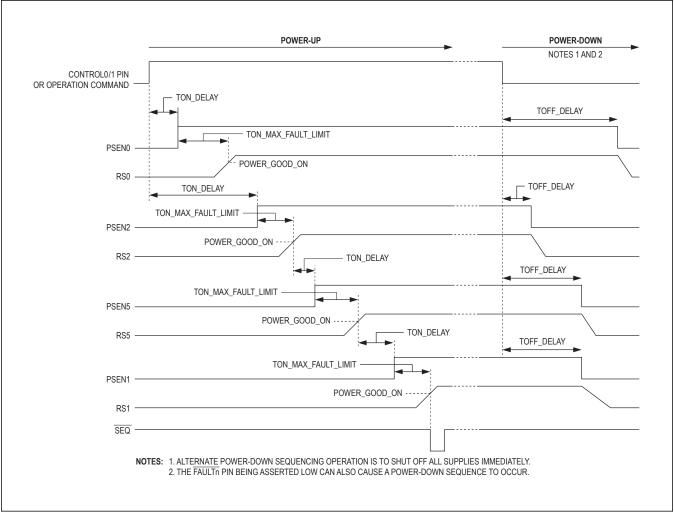

|    | Power-On Sequencing                        | 32  |

|    | Power-Off Sequencing                       | 32  |

|    | Sequencing Example                         | 32  |

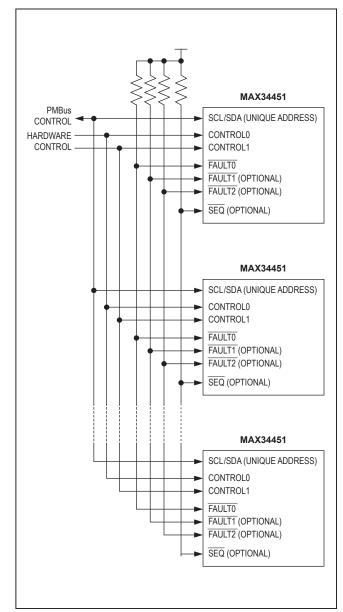

|    | Multiple Device Connections                | 33  |

|    | SEQ Pin Operation                          | 34  |

|    | System Watchdog Timer                      | 34  |

|    | CRC Memory Check                           | 34  |

| Pľ | MBus Commands                              | 35  |

|    | PAGE (00h)                                 | 35  |

|    | OPERATION (01h)                            | 36  |

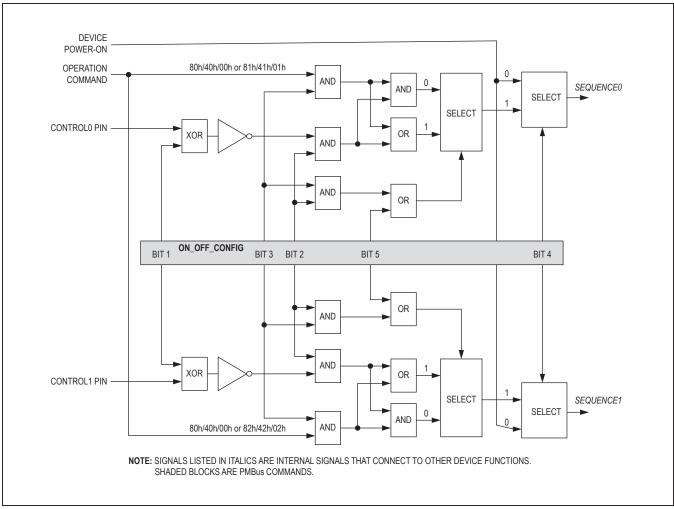

|    | ON_OFF_CONFIG (02h)                        | 38  |

|    | CLEAR_FAULTS (03h)                         | 40  |

|    | WRITE_PROTECT (10h)                        | 40  |

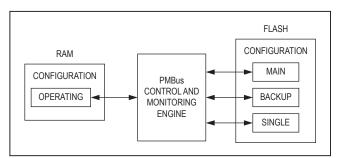

|    | Device Configuration Data Management       | 40  |

|    | STORE_DEFAULT_ALL (11h).                   | 41  |

|    | RESTORE_DEFAULT_ALL (12h)                  | 41  |

|    | MFR_STORE_ALL (EEh)                        | 41  |

|    | MFR_RESTORE_ALL (EFh)                      | 41  |

|    | MFR_STORE_SINGLE (FCh)                     | 42  |

|    | MFR_CRC (FEh)                              | 42  |

|    | CAPABILITY (19h)                           | 42  |

|    | VOUT_MODE (20h)                            | 43  |

|    | VOUT_MARGIN_HIGH (25h)                     | 43  |

|    | VOUT_MARGIN_LOW (26h)                      | 43  |

|    | VOUT_SCALE_MONITOR (2Ah)                   | 43  |

|    | IOUT_CAL_GAIN (38h).                       | 44  |

|    | VOUT_OV_FAULT_LIMIT (40h)                  |     |

|    | VOUT_OV_WARN_LIMIT (42h)                   | 44  |

|    | VOUT_UV_WARN_LIMIT (43h)                   | 44  |

|    | VOUT_UV_FAULT_LIMIT (44h)                  | 44  |

#### **TABLE OF CONTENTS (continued)**

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

| TABLE OF CONTENTS (continued) |

|-------------------------------|

| IOUT_OC_WARN_LIMIT (46h)      |

| IOUT_OC_FAULT_LIMIT (4Ah)     |

| OT_FAULT_LIMIT (4Fh)          |

| OT_WARN_LIMIT (51h)           |

| POWER_GOOD_ON (5Eh)           |

| POWER_GOOD_OFF (5Fh)          |

| TON_DELAY (60h)               |

| TOFF_DELAY (64h)              |

| TON_MAX_FAULT_LIMIT (62h)     |

| STATUS_WORD (79h)             |

| STATUS_VOUT (7Ah)             |

| STATUS_IOUT (7Bh)             |

| STATUS_TEMPERATURE (7Dh)      |

| STATUS_CML (7Eh)              |

| STATUS_MFR_SPECIFIC (80h)     |

| READ_VOUT (8Bh)               |

| READ_IOUT (8Ch)               |

| READ_TEMPERATURE_1 (8Dh)      |

| PMBUS_REVISION (98h)          |

| MFR_ID (99h)                  |

| MFR_MODEL (9Ah)               |

| MFR_REVISION (9Bh)            |

| MFR_LOCATION (9Ch)            |

| MFR_DATE (9Dh)                |

| MFR_SERIAL (9Eh)              |

| MFR_MODE (D1h)                |

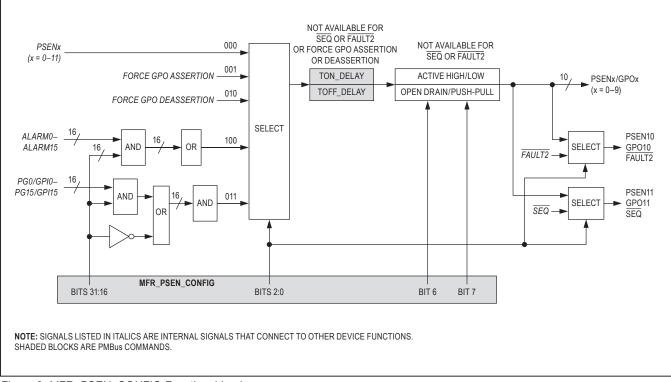

| MFR_PSEN_CONFIG (D2h)         |

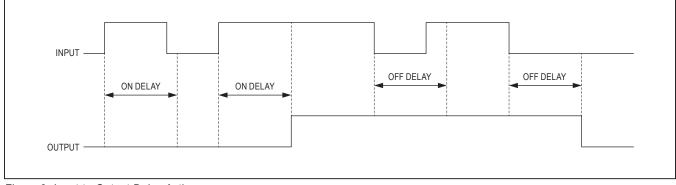

| Delay Function                |

| MFR_VOUT_PEAK (D4h)           |

| MFR_IOUT_PEAK (D5h)           |

| MFR_TEMPERATURE_PEAK (D6h)    |

| MFR_VOUT_MIN (D7h)            |

| MFR_FW_SERIAL (E0h)           |

| MFR_IOUT_AVG (E2h)            |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

### **TABLE OF CONTENTS (continued)**

| MFR_NV_LOG_CONFIG (D8h)                                   | 54 |

|-----------------------------------------------------------|----|

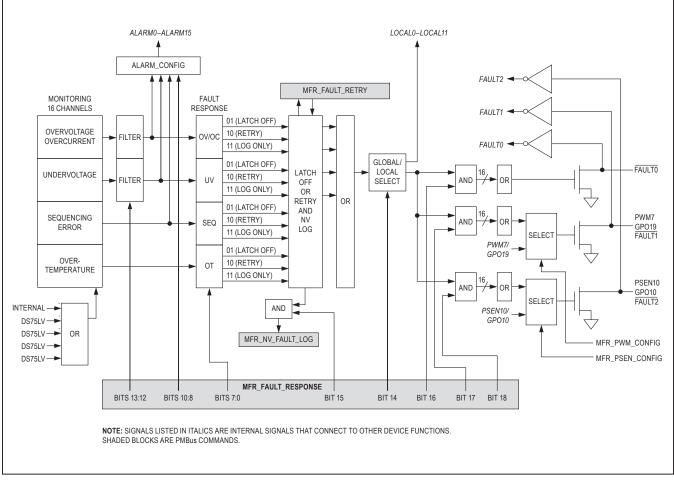

| MFR_FAULT_RESPONSE (D9h)                                  | 56 |

| LOCAL vs. GLOBAL Channels                                 | 56 |

| GLOBAL Channels Respond to FAULTn Assertion               | 56 |

| Temperature Fault Response                                | 56 |

| Fault Detection Before Power-On Sequencing                | 57 |

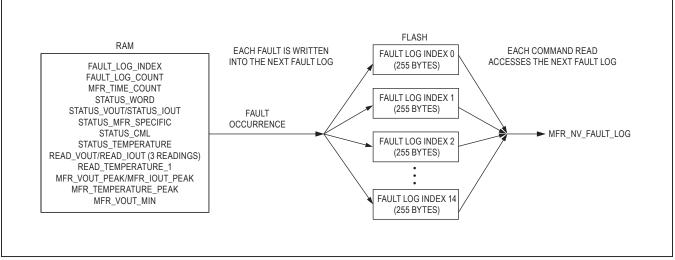

| Logging Faults into MFR_NV_FAULT_LOG                      | 57 |

| Alarm Output Functionality                                | 61 |

| MFR_FAULT_RETRY (DAh)                                     | 61 |

| MFR_NV_FAULT_LOG (DCh)                                    | 61 |

| MFR_TIME_COUNT (DDh)                                      | 64 |

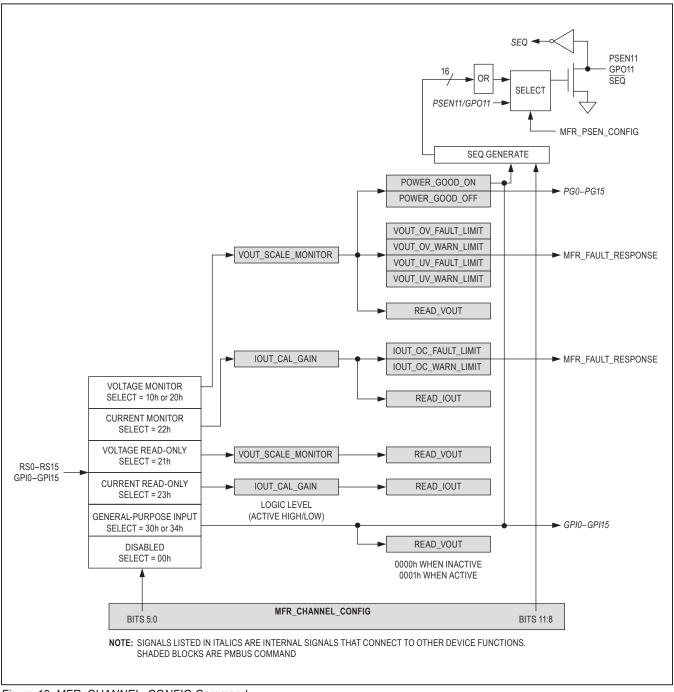

| MFR_CHANNEL_CONFIG (E4h)                                  | 64 |

| MFR_TON_SEQ_MAX (E6h)                                     | 68 |

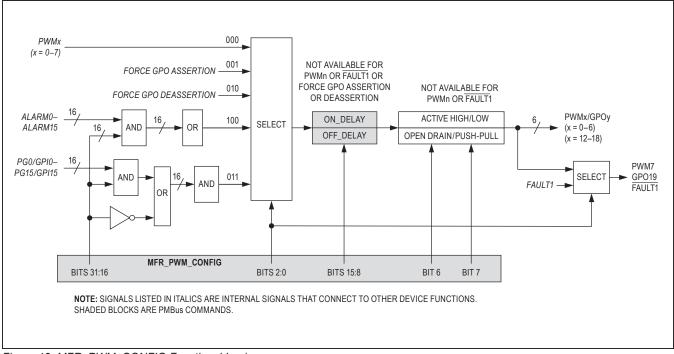

| MFR_PWM_CONFIG (E7h)                                      | 68 |

| Delay Function                                            | 70 |

| MFR_SEQ_CONFIG (E8h).                                     | 70 |

| MFR_MARGIN_CONFIG (DFh)                                   | 71 |

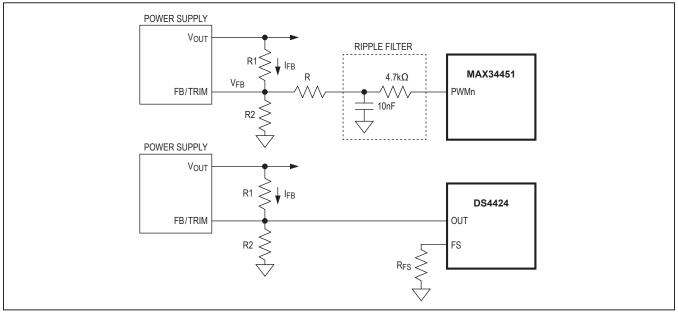

| Power-Supply Margining Operation                          | 71 |

| Margining Faults                                          | 72 |

| DC_DAC Value                                              | 72 |

| PWM/DAC Margining Component Selection                     | 72 |

| Temperature Sensor Operation                              |    |

| Applications Information.                                 |    |

| V <sub>DD</sub> , V <sub>DDA</sub> , and REG18 Decoupling | 74 |

| Open-Drain Pins                                           |    |

| Keep-Alive Circuit                                        | 74 |

| Configuration Port                                        |    |

| Resistor-Dividers and Source Impedance for RSn Inputs     |    |

| Protecting Input Pins                                     |    |

| Exposed Pad Grounding                                     |    |

| Typical Operating Circuit                                 |    |

| Ordering Information                                      |    |

| Revision History                                          |    |

PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### **LIST OF FIGURES**

| Figure 1. PMBus/SMBus Address Select             | 23 |

|--------------------------------------------------|----|

| Figure 2. Sequence Control Logic                 | 31 |

| Figure 3. Sequencing Example                     | 33 |

| Figure 4. Multiple MAX34451 Hardware Connections | 34 |

| Figure 5. ON_OFF_CONFIG Logical Control          | 39 |

| Figure 6. Device Configuration Data Management   | 40 |

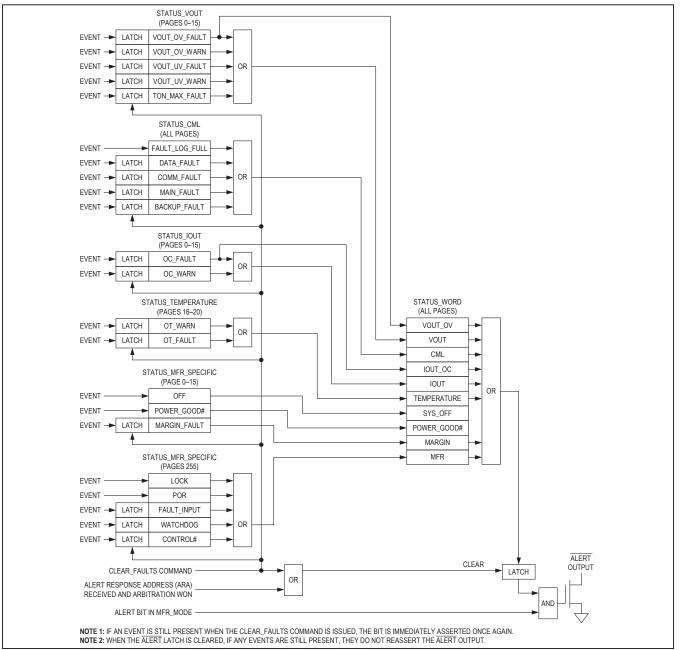

| Figure 7. Status Register Organization           | 46 |

| Figure 8. MFR_PSEN_CONFIG Functional Logic       | 53 |

| Figure 9. Input-to-Output Delay Action           | 54 |

| Figure 10. MFR_FAULT_RESPONSE Operation          | 59 |

| Figure 11. MFR_NV_FAULT_LOG                      | 61 |

| Figure 12. MFR_CHANNEL_CONFIG Command            | 66 |

| Figure 13. MFR_PWM_CONFIG Functional Logic       | 70 |

| Figure 14. Margining Hardware Configurations     | 73 |

#### LIST OF TABLES

| 19 |

|----|

| 20 |

| 21 |

| 22 |

| 23 |

| 24 |

| 28 |

| 28 |

| 30 |

| 32 |

| 35 |

| 36 |

| 37 |

| 37 |

| 38 |

| 40 |

|    |

PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

### LIST OF TABLES (continued)

| Table 15. Memory Transfer PMBus Commands               | . 40 |

|--------------------------------------------------------|------|

| Table 16. MFR_CRC (FEh) Command Byte                   | . 42 |

| Table 17. CAPABILITY (19h) Command Byte                | . 42 |

| Table 18. VOUT_SCALE_MONITOR (2Ah) Examples            | . 43 |

| Table 19. STATUS_WORD (79h)                            | . 47 |

| Table 20. STATUS_VOUT (7Ah)                            | . 47 |

| Table 21. STATUS_IOUT (7Bh)                            | . 48 |

| Table 22. STATUS_TEMPERATURE (7Dh)                     | . 48 |

| Table 23. STATUS_CML (7Eh)                             | . 48 |

| Table 24. STATUS_MFR_SPECIFIC (80h) (for PAGES 0–11)   | . 49 |

| Table 25. STATUS_MFR_SPECIFIC (for PAGE 255)           | . 49 |

| Table 26. MFR_MODE (D1h)                               | . 51 |

| Table 27. MFR_PSEN_CONFIG (D2h)                        | . 52 |

| Table 28. MFR_NV_LOG_CONFIG (D8h)                      | . 55 |

| Table 29. Fault Monitoring States                      | . 57 |

| Table 30. MFR_FAULT_RESPONSE (D9h)                     | . 58 |

| Table 31. ALARM_CONFIG Codes                           | . 59 |

| Table 32. MFR_FAULT_RESPONSE Codes for GLOBAL Channels | . 60 |

| Table 33. MFR_FAULT_RESPONSE Codes for LOCAL Channels  | . 60 |

| Table 34. MFR_NV_FAULT_LOG (DCh)                       | . 62 |

| Table 35. MFR_CHANNEL_CONFIG (E4h)                     | . 65 |

| Table 36. Fault-Monitoring States                      | . 67 |

| Table 37. MFR_PWM_CONFIG (E7h)                         | . 69 |

| Table 38. MFR_SEQ_CONFIG (E8h)                         | . 71 |

| Table 39. MFR_MARGIN_CONFIG (DFh)                      | . 72 |

| Table 40. Power-Supply DAC Outputs.                    | . 72 |

| Table 41. DS75LV Address Pin Configuration             | 74   |

| Table 42. MFR_TEMP_SENSOR_CONFIG (F0h)                 | 74   |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### **Absolute Maximum Ratings**

| V <sub>DD</sub> and V <sub>DDA</sub> to V <sub>SS</sub> | 0.3V to +4.0V                      |

|---------------------------------------------------------|------------------------------------|

| RSG0 and RSG1 to V <sub>SS</sub>                        | -0.3V to +0.3V                     |

| All Other Pins Except REG18                             |                                    |

| Relative to V <sub>SS</sub>                             | -0.3V to (V <sub>DD</sub> + 0.3V)* |

| REG18 to V <sub>SS</sub>                                | -0.3V to +2.0V                     |

| 00                                                      |                                    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

|-------------------------------------------------------|-----------------|

| TQFN (derate 27.8mW/°C above +70°C)                   | 2222.2mW        |

| Operating Temperature Range                           | 40°C to +85°C   |

| Storage Temperature Range                             | -55°C to +125°C |

| Lead Temperature (soldering, 10s)                     | +260°C          |

| Soldering Temperature (reflow)                        | +260°C          |

\*Subject to not exceeding +4.0V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

(T<sub>A</sub> = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                                                | SYMBOL           | CONDITIONS              | MIN                      | TYP MAX                  | UNITS |

|----------------------------------------------------------|------------------|-------------------------|--------------------------|--------------------------|-------|

| V <sub>DD</sub> Operating Voltage Range                  | V <sub>DD</sub>  | (Note 1)                | 3.0                      | 3.6                      | V     |

| Input Logic 1<br>(Except I <sup>2</sup> C and GPIn Pins) | V <sub>IH1</sub> |                         | 0.7 x<br>V <sub>DD</sub> | V <sub>DD</sub> +<br>0.3 | V     |

| Input Logic 0<br>(Except I <sup>2</sup> C and GPIn Pins) | V <sub>IL1</sub> |                         | -0.3                     | +0.3 x V <sub>DD</sub>   | V     |

| Input Logic 1: SCL, SDA,<br>MSCL, MSDA                   | V <sub>IH2</sub> |                         | 2.1                      | V <sub>DD</sub> + 0.3    | V     |

| Input Logic 0: SCL, SDA,<br>MSCL, MSDA                   | V <sub>IL2</sub> |                         | -0.3                     | +0.8                     | V     |

| Input Logic 1 (GPIn Pins)                                | V <sub>IH3</sub> | Minimum pulse width 5ms | 1.5                      | V <sub>DD</sub> + 0.3    | V     |

| Input Logic 0 (GPIn Pins)                                | V <sub>IL3</sub> | Minimum pulse width 5ms | -0.3                     | +1.0                     | V     |

|                                                          |                  | ADC_TIME[1:0] = 00      |                          | 1                        |       |

| Course lange demos to DOs                                |                  | ADC_TIME[1:0] = 01      |                          | 5                        | 1.0   |

| Source Impedance to RSn                                  |                  | ADC_TIME[1:0] = 10      |                          | 10                       | kΩ    |

|                                                          |                  | ADC_TIME[1:0] = 11      |                          | 20                       |       |

| V <sub>DD</sub> Rise Time                                |                  | From 0V to 3.0V         |                          | 4                        | ms    |

| V <sub>DD</sub> Source Impedance                         |                  |                         |                          | 10                       | Ω     |

### **Package Information**

| PACKAGE TYPE: 56 TQFN |                |  |  |  |

|-----------------------|----------------|--|--|--|

| Package Code          | T5677+2        |  |  |  |

| Outline Number        | <u>21-0144</u> |  |  |  |

| Land Pattern Number   | 90-0043        |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### **Electrical Characteristics**

$(V_{DD} \text{ and } V_{DDA} = 3.0V \text{ to } 3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{DD}/V_{DDA} = 3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 2)

| PARAMETER                                           | SYMBOL            | CONDITIONS                                    | MIN                   | TYP   | MAX   | UNITS |

|-----------------------------------------------------|-------------------|-----------------------------------------------|-----------------------|-------|-------|-------|

| GENERAL                                             |                   |                                               |                       |       |       |       |

| 0 1 0 1                                             | I <sub>CPU</sub>  | (Note 3)                                      |                       | 12    |       | - mA  |

| Supply Current                                      | IPROGRAM          |                                               |                       | 18    |       |       |

| Svetere Cleak Error                                 | £                 | +25°C < T <sub>A</sub> < +85°C                | -3                    |       | +3    | %     |

| System Clock Error                                  | ferr:mosc         | -40°C < T <sub>A</sub> < +25°C                | -4                    |       | +4    |       |

| Output Logic-Low<br>(Except I <sup>2</sup> C Pins)  | V <sub>OL1</sub>  | I <sub>OL</sub> = 4mA (Note 1)                |                       |       | 0.4   | V     |

| Output Logic-High<br>(Except I <sup>2</sup> C Pins) | V <sub>OH1</sub>  | I <sub>OH</sub> = -2mA (Note 1)               | V <sub>DD</sub> - 0.5 |       |       | V     |

| Output Logic-Low: SCL, SDA,<br>MSCL, MSDA           | V <sub>OL2</sub>  | I <sub>OL</sub> = 4mA (Note 1)                |                       |       | 0.4   | V     |

| SCL, SDA, MSCL, MSDA<br>Leakage                     | IL <sub>I2C</sub> | V <sub>DD</sub> = 0V or unconnected           |                       |       | ±5    | μA    |

| CONTROL0 Threshold                                  |                   |                                               |                       | 2.048 |       | V     |

| CONTROL0 Hysteresis                                 |                   |                                               |                       | 50    |       | mV    |

| ADC                                                 |                   |                                               |                       |       |       |       |

| ADC Bit Resolution                                  |                   |                                               |                       | 12    |       | Bits  |

| ADC Conversion Time                                 |                   | ADC_TIME[1:0] = 00                            |                       | 1000  |       | ns    |

| ADC Full Scale                                      | V <sub>FS</sub>   | $T_A = 0^{\circ}C$ to +85°C                   | 2.032                 | 2.048 | 2.064 | V     |

| ADC Measurement Resolution                          | V <sub>LSB</sub>  |                                               |                       | 500   |       | μV    |

| RSn Input Capacitance                               | C <sub>RS</sub>   |                                               |                       | 15    |       | pF    |

| RSn Input Leakage                                   | IL <sub>RS</sub>  | 0V < V <sub>RSn</sub> < 2.1V                  |                       | ±0.25 |       | μA    |

| ADC Integral Nonlinearity                           | INL               |                                               |                       | ±1    |       | LSB   |

| ADC Differential Nonlinearity                       | DNL               |                                               |                       | ±1    |       | LSB   |

| TEMPERATURE SENSOR                                  |                   | ·                                             |                       |       |       |       |

| Internal Temperature-<br>Measurement Error          |                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                       | ±2    |       | °C    |

### PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### **Electrical Characteristics (continued)**

(V<sub>DD</sub> and V<sub>DDA</sub> = 3.0V to 3.6V,  $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted. Typical values are at V<sub>DD</sub>/V<sub>DDA</sub> = 3.3V,  $T_A = +25^{\circ}$ C.) (Note 2)

| PARAMETER                                      | SYMBOL             | CONDITIONS                      | MIN    | TYP   | MAX | UNITS           |

|------------------------------------------------|--------------------|---------------------------------|--------|-------|-----|-----------------|

| FLASH                                          |                    |                                 |        |       |     | •               |

| Flash Endurance                                | N <sub>FLASH</sub> | Note 3                          | 20,000 |       |     | Write<br>Cycles |

| Data Retention                                 |                    | T <sub>A</sub> = +50°C (Note 4) | 100    |       |     | Years           |

| STORE_DEFAULT_ALL,<br>MFR_STORE_ALL Write Time |                    |                                 |        | 80    |     | ms              |

| RESTORE_DEFAULT_ALL                            |                    | With MFR_STORE_SINGLE data      |        | 105   |     | ms              |

| RESTORE_DEFAULT_ALL or<br>MFR_RESTORE_ALL      |                    | Without MFR_STORE_SINGLE data   |        | 500   |     | μs              |

| MFR_STORE_SINGLE<br>Write Time                 |                    |                                 |        | 310   |     | μs              |

| MFR_NV_FAULT_LOG<br>Write Time                 |                    | Writing 1 fault log             |        | 11    |     | ms              |

| MFR_NV_FAULT_LOG<br>Delete Time                |                    | Deleting all fault logs         |        | 200   |     | ms              |

| MFR_NV_FAULT_LOG<br>Overwrite Time             |                    |                                 |        | 40    |     | ms              |

| TIMING OPERATING CHARACT                       | ERISTICS           |                                 |        |       |     |                 |

| Round-Robin Voltage and                        |                    | Threshold excursion (Note 5)    |        | 64    |     | μs              |

| Current Sample Rate                            |                    | Data collection                 |        | 5     |     | ms              |

| Temperature Sample Rate                        |                    |                                 |        | 1000  |     | ms              |

| Device Startur Time                            |                    | With MFR_STORE_SINGLE data      |        | 170   |     | - ms            |

| Device Startup Time                            |                    | Without MFR_STORE_SINGLE data   |        | 90    |     |                 |

| PWM Frequency                                  |                    | PWM power-supply margining      |        | 312.5 | -   | kHz             |

| PWM Resolution                                 |                    | PWM power-supply margining      |        | 8     |     | Bits            |

Note 1: All voltages are referenced to ground. Current entering the device are specified as positive and currents exiting the device are negative.

**Note 2:** Limits are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and chacterization.

**Note 3:** This does not include pin input/output currents.

Note 4: Guaranteed by design.

**Note 5:** The round-robin threshold excursion rate can be changed with the ADC\_AVERAGE and ADC\_TIME bits in MFR\_MODE from 16µs (no averaging and 1µs conversion) to 1024µs (8x averaging and 8µs conversion).

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

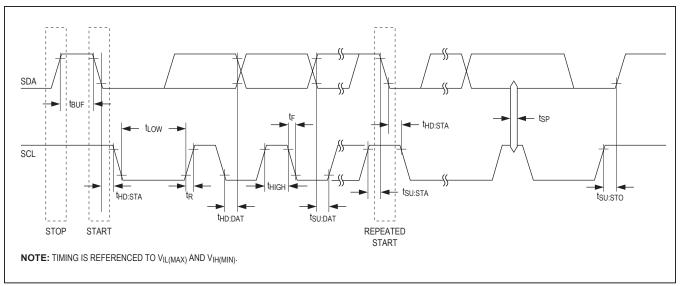

#### I<sup>2</sup>C/SMBus Interface Electrical Specifications

(V<sub>DD</sub> and V<sub>DDA</sub> = 3.0V to 3.6V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>DD</sub>/V<sub>DDA</sub> = 3.3V,  $T_A$  = +25°C.)

| PARAMETER                                       | SYMBOL              | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|---------------------|------------|-----|-----|-----|-------|

| SCL Clock Frequency                             | f <sub>SCL</sub>    |            | 10  |     | 400 | kHz   |

| MSCL Clock Frequency                            | f <sub>MSCL</sub>   |            |     | 100 |     | kHz   |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |            | 1.3 |     |     | μs    |

| Hold Time (Repeated)<br>START Condition         | t <sub>HD:STA</sub> |            | 0.6 |     |     | μs    |

| Low Period of SCL                               | t <sub>LOW</sub>    |            | 1.3 |     |     | μs    |

| High Period of SCL                              | thigh               |            | 0.6 |     |     | μs    |

| Data Hald Time                                  |                     | Receive    | 0   |     |     |       |

| Data Hold Time                                  | thd:dat             | Transmit   | 300 |     |     | ns    |

| Data Setup Time                                 | <sup>t</sup> SU:DAT |            | 100 |     |     | ns    |

| Start Setup Time                                | t <sub>SU:STA</sub> |            | 0.6 |     |     | μs    |

| SDA and SCL Rise Time                           | t <sub>R</sub>      |            |     |     | 300 | ns    |

| SDA and SCL Fall Time                           | t <sub>F</sub>      |            |     |     | 300 | ns    |

| Stop Setup Time                                 | t <sub>SU:STO</sub> |            | 0.6 |     |     | μs    |

| Clock Low Timeout                               | t <sub>TO</sub>     |            | 25  | 27  | 35  | ms    |

#### **I<sup>2</sup>C/SMBus Timing**

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

20ms/div

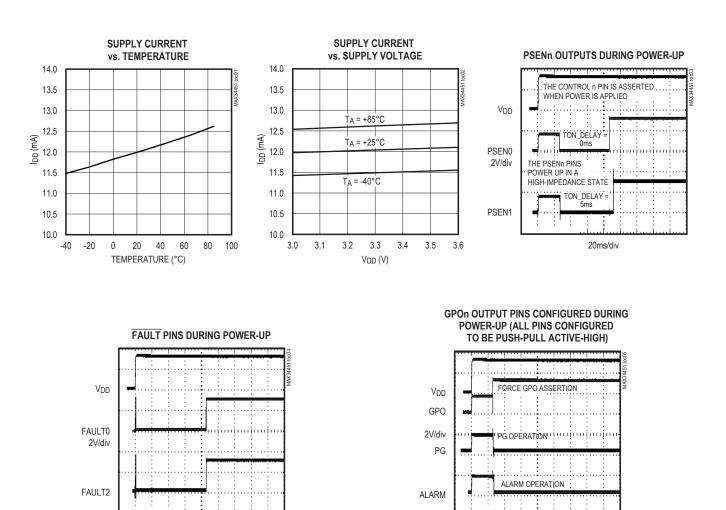

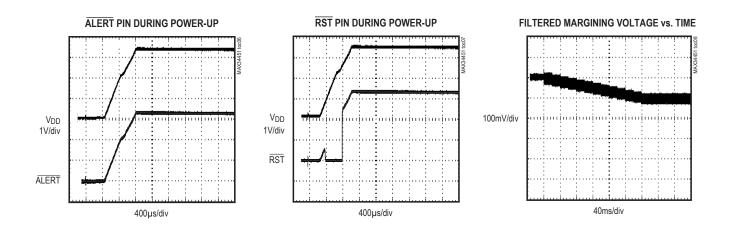

#### **Typical Operating Characteristics**

20ms/div

(V<sub>DD</sub> = 3.3V and T<sub>A</sub> = +25°C, without MFR\_STORE\_SINGLE data, unless otherwise noted.)

www.maximintegrated.com

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

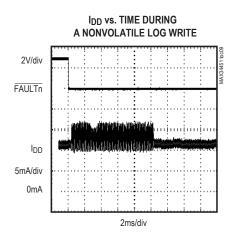

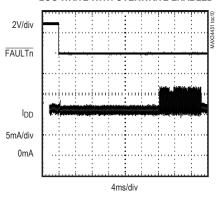

#### **Typical Operating Characteristics (continued)**

( $V_{DD}$  = 3.3V and  $T_A$  = +25°C, without MFR\_STORE\_SINGLE data, unless otherwise noted.)

IDD vs. TIME DURING A NONVOLATILE LOG WRITE WITH OVERWRITE ENABLED

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

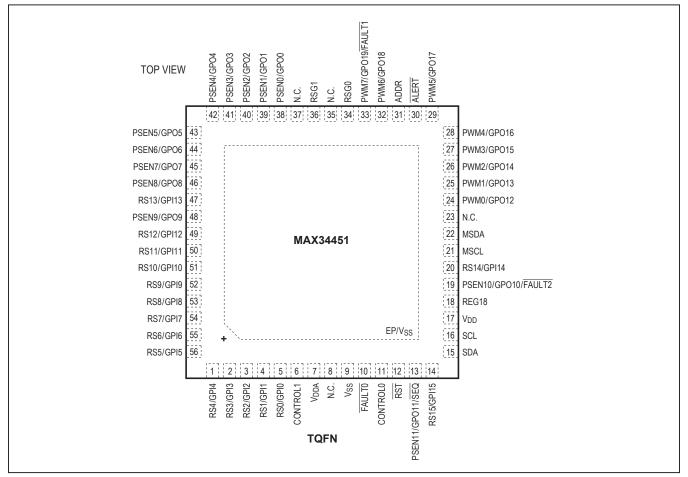

### **Pin Configuration**

#### **Pin Description**

| PIN* | NAME          | TYPE** | FUNCTION                                                                                                                                    |  |  |  |

|------|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 4    | RS4           | AI     | ADC Voltage-Sense Input 4. Connect to V <sub>SS</sub> if unused.                                                                            |  |  |  |

| I    | GPI4          | AI     | General-Purpose Input 4. Connect to V <sub>SS</sub> if unused.                                                                              |  |  |  |

| 2    | RS3           | AI     | ADC Voltage-Sense Input 3. Connect to V <sub>SS</sub> if unused.                                                                            |  |  |  |

| Z    | GPI3          | AI     | General-Purpose Input 3. Connect to V <sub>SS</sub> if unused.                                                                              |  |  |  |

| 3    | RS2           | AI     | ADC Voltage-Sense Input 2. Connect to V <sub>SS</sub> if unused.                                                                            |  |  |  |

| 3    | GPI2          | AI     | General-Purpose Input 2. Connect to V <sub>SS</sub> if unused.                                                                              |  |  |  |

| 4    | RS1           | AI     | ADC Voltage-Sense Input 1. Connect to V <sub>SS</sub> if unused.                                                                            |  |  |  |

| 4    | GPI1          | AI     | General-Purpose Input 1. Connect to V <sub>SS</sub> if unused.                                                                              |  |  |  |

| F    | RS0           | AI     | ADC Voltage-Sense Input 0. Connect to V <sub>SS</sub> if unused.                                                                            |  |  |  |

| Э    | 5 GPI0 AI     |        | General-Purpose Input 0. Connect to V <sub>SS</sub> if unused.                                                                              |  |  |  |

| 6    | 6 CONTROL1 DI |        | Power-Supply Master On/Off Control Input 1. Active low or active high based on ON_OFF_CONFIG command. Connect to V <sub>SS</sub> if unused. |  |  |  |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

### **Pin Description (continued)**

| PIN* | NAME             | TYPE** | FUNCTION                                                                                                                                                |

|------|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | V <sub>DDA</sub> | Power  | Analog Supply Voltage. Bypass $V_{DDA}$ to $V_{SS}$ with 0.1µF. Connect to $V_{DD}$ .                                                                   |

| 8    | N.C.             | _      | No Connection. Do not connect any signal to this pin.                                                                                                   |

| 9    | V <sub>SS</sub>  | Power  | Ground Reference. Must be connected to EP (exposed pad).                                                                                                |

| 10   | FAULT0           | DIO    | Fault Input/Output 0. Open-drain, active-low I/O. See the <i>Expanded Pin Description</i> section for more details.                                     |

| 11   | CONTROL0         | AI     | Power-Supply Master On/Off Control Input 0. Active low or active high based on ON_OFF_CONFIG command. Connect to $V_{SS}$ if unused.                    |

| 12   | RST              | DIO    | Active-Low Reset Input/Output. Contains an internal pullup.                                                                                             |

|      | PSEN11           | DO     | Power-Supply Enable 11. See the <i>Expanded Pin Description</i> section for more details.                                                               |

| 13   | GPO11            | DO     | General-Purpose Output 11                                                                                                                               |

| 10   | SEQ              | DIO    | Sequencing Input/Output. Open-drain, active-low I/O. This pin is used as a handshake signal to coordinate sequencing in systems using multiple devices. |

| 14   | RS15             | AI     | ADC Voltage-Sense Input 15. Connect to V <sub>SS</sub> if unused.                                                                                       |

| 14   | GPI15            | AI     | General-Purpose Input 15. Connect to V <sub>SS</sub> if unused.                                                                                         |

| 15   | SDA              | DIO    | I <sup>2</sup> C/SMBus-Compatible Input/Output. Open-drain output.                                                                                      |

| 16   | SCL              | DIO    | I <sup>2</sup> C/SMBus-Compatible Clock Input/Output. Open-drain output.                                                                                |

| 17   | V <sub>DD</sub>  | Power  | Digital Supply Voltage. Bypass $V_{DD}$ to $V_{SS}$ with 0.1µF. Connect to $V_{DDA}$ .                                                                  |

| 18   | REG18            | Power  | Regulator for Digital Circuitry. Bypass to $V_{SS}$ with 1µF and 10nF (500m $\Omega$ maximum ESR). Do not connect other circuitry to this pin.          |

|      | PSEN10           | DO     | Power-Supply Enable 10. See the <i>Expanded Pin Description</i> section for more details.                                                               |

| 19   | GPO10            | DO     | General-Purpose Output 10                                                                                                                               |

| 10   | FAULT2           | DIO    | Fault Input/Output 2. Open-drain, active-low I/O. See the <i>Expanded Pin Description</i> section for more details.                                     |

| 00   | RS14             | AI     | ADC Voltage-Sense Input 14. Connect to V <sub>SS</sub> if unused.                                                                                       |

| 20   | GPI14            | AI     | General-Purpose Input 14. Connect to V <sub>SS</sub> if unused.                                                                                         |

| 21   | MSCL             | DIO    | Master I <sup>2</sup> C Clock Input/Output. Open-drain output.                                                                                          |

| 22   | MSDA             | DIO    | Master I <sup>2</sup> C Data Input/Output. Open-drain output.                                                                                           |

| 23   | N.C.             | —      | No Internal Connection                                                                                                                                  |

| 24   | PWM0             | DO     | PWM Margin Output 0. See the <i>Expanded Pin Description</i> section for more details.                                                                  |

| 24   | GPO12            | DO     | General-Purpose Output 12                                                                                                                               |

| 05   | PWM1             | DO     | PWM Margin Output 1. See the <i>Expanded Pin Description</i> section for more details.                                                                  |

| 25   | GPO13            | DO     | General-Purpose Output 13                                                                                                                               |

| 26   | PWM2             | DO     | PWM Margin Output 2. See the <i>Expanded Pin Description</i> section for more details.                                                                  |

| 26   | GPO14            | DO     | General-Purpose Output 14                                                                                                                               |

| 27   | PWM3             | DO     | PWM Margin Output 3. See the <i>Expanded Pin Description</i> section for more details.                                                                  |

| 27   | GPO15            | DO     | General-Purpose Output 15                                                                                                                               |

| 28   | PWM4             | DO     | PWM Margin Output 4. See the <i>Expanded Pin Description</i> section for more details.                                                                  |

| 20   | GPO16            | DO     | General-Purpose Output 16                                                                                                                               |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

### **Pin Description (continued)**

| PIN* | NAME   | TYPE** | FUNCTION                                                                                                                                                                                                                      |

|------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20   | PWM5   | DO     | PWM Margin Output 5. See the Expanded Pin Description section for more details.                                                                                                                                               |

| 29   | GPO17  | DO     | General-Purpose Output 17                                                                                                                                                                                                     |

| 30   | ALERT  | DO     | Alert Output. Open-drain, active-low output.                                                                                                                                                                                  |

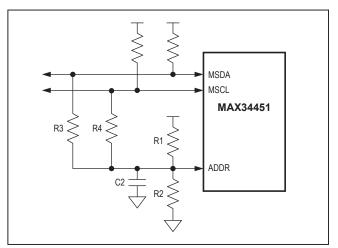

| 31   | ADDR   | DI     | SMBus Slave Address Select. This pin is sampled on device power-up to determine the SMBus address. See the <i>PMBus/SMBus Address Select</i> section for details on how to strap this pin to select the proper slave address. |

| 32   | PWM6   | DO     | PWM Margin Output 6. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                        |

| 52   | GPO18  | DO     | General-Purpose Output 18                                                                                                                                                                                                     |

|      | PWM7   | DO     | PWM Margin Output 7. See the Expanded Pin Description section for more details.                                                                                                                                               |

| 33   | GPO19  | DO     | General-Purpose Output 19                                                                                                                                                                                                     |

| 55   | FAULT1 | DIO    | Fault Input/Output 1. Open-drain, active-low I/O. See the <i>Expanded Pin Description</i> section for more details.                                                                                                           |

| 34   | RSG0   | Al     | Remote-Sense Ground for RS0/GPI0 to RS3/GPI3 and RS12/GPI12 to RS15/GPI15.                                                                                                                                                    |

| 35   | N.C.   | —      | No Internal Connection                                                                                                                                                                                                        |

| 36   | RSG1   | Al     | Remote-Sense Ground for RS4/GPI4 to RS11/GPI11.                                                                                                                                                                               |

| 37   | N.C.   | —      | No Internal Connection                                                                                                                                                                                                        |

| 20   | PSEN0  | DO     | Power-Supply Enable 0. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 38   | GPO0   | DO     | General-Purpose Output 0                                                                                                                                                                                                      |

| 20   | PSEN1  | DO     | Power-Supply Enable 1. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 39   | GPO1   | DO     | General-Purpose Output 1                                                                                                                                                                                                      |

| 40   | PSEN2  | DO     | Power-Supply Enable 2. See the Expanded Pin Description section for more details.                                                                                                                                             |

| 40   | GPO2   | DO     | General-Purpose Output 2                                                                                                                                                                                                      |

| 44   | PSEN3  | DO     | Power-Supply Enable 3. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 41   | GPO3   | DO     | General-Purpose Output 3                                                                                                                                                                                                      |

| 40   | PSEN4  | DO     | Power-Supply Enable 4. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 42   | GPO4   | DO     | General-Purpose Output 4                                                                                                                                                                                                      |

| 40   | PSEN5  | DO     | Power-Supply Enable 5. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 43   | GPO5   | DO     | General-Purpose Output 5                                                                                                                                                                                                      |

| 4.4  | PSEN6  | DO     | Power-Supply Enable 6. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 44   | GPO6   | DO     | General-Purpose Output 6                                                                                                                                                                                                      |

| 45   | PSEN7  | DO     | Power-Supply Enable 7. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 45   | GPO7   | DO     | General-Purpose Output 7                                                                                                                                                                                                      |

| 40   | PSEN8  | DO     | Power-Supply Enable 8. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 46   | GPO8   | DO     | General-Purpose Output 8                                                                                                                                                                                                      |

| 47   | RS13   | AI     | ADC Voltage-Sense Input 13. Connect to V <sub>SS</sub> if unused.                                                                                                                                                             |

| 47   | GPI13  | Al     | General-Purpose Input 13. Connect to V <sub>SS</sub> if unused.                                                                                                                                                               |

| 40   | PSEN9  | DO     | Power-Supply Enable 9. See the <i>Expanded Pin Description</i> section for more details.                                                                                                                                      |

| 48   | GPO9   | DO     | General-Purpose Output 9                                                                                                                                                                                                      |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

| PIN* | NAME               | TYPE** | FUNCTION                                                                                                                                               |

|------|--------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 49   | RS12               | AI     | ADC Voltage-Sense Input 12. Connect to V <sub>SS</sub> if unused.                                                                                      |

| 49   | GPI12              | AI     | General-Purpose Input 12. Connect to V <sub>SS</sub> if unused.                                                                                        |

| 50   | RS11               | AI     | ADC Voltage-Sense Input 11. Connect to V <sub>SS</sub> if unused.                                                                                      |

| 50   | GPI11              | AI     | General-Purpose Input 11. Connect to V <sub>SS</sub> if unused.                                                                                        |

| E 4  | RS10               | AI     | ADC Voltage-Sense Input 10. Connect to V <sub>SS</sub> if unused.                                                                                      |

| 51   | GPI10              | AI     | General-Purpose Input 10. Connect to V <sub>SS</sub> if unused.                                                                                        |

| 50   | RS9                | AI     | ADC Voltage-Sense Input 9. Connect to V <sub>SS</sub> if unused.                                                                                       |

| 52   | GPI9               | AI     | General-Purpose Input 9. Connect to V <sub>SS</sub> if unused.                                                                                         |

| 50   | RS8                | AI     | ADC Voltage-Sense Input 8. Connect to V <sub>SS</sub> if unused.                                                                                       |

| 53   | GPI8               | AI     | General-Purpose Input 8. Connect to V <sub>SS</sub> if unused.                                                                                         |

| 54   | RS7                | AI     | ADC Voltage-Sense Input 7. Connect to V <sub>SS</sub> if unused.                                                                                       |

| 54   | GPI7               | AI     | General-Purpose Input 7. Connect to V <sub>SS</sub> if unused.                                                                                         |

| EE   | RS6                | AI     | ADC Voltage-Sense Input 6. Connect to V <sub>SS</sub> if unused.                                                                                       |

| 55   | GPI6               | AI     | General-Purpose Input 6. Connect to V <sub>SS</sub> if unused.                                                                                         |

| FC   | RS5                | AI     | ADC Voltage-Sense Input 5. Connect to V <sub>SS</sub> if unused.                                                                                       |

| 56   | GPI5               | AI     | General-Purpose Input 5. Connect to V <sub>SS</sub> if unused.                                                                                         |

| _    | EP/V <sub>SS</sub> | Power  | Exposed Pad (Bottom Side of Package). Must be connected to local ground.<br>The exposed pad is the ground reference (V <sub>SS</sub> ) for the device. |

#### **Pin Description (continued)**

\*All pins except the power pins, ALERT, and ADDR are high impedance during device power-up and reset.

\*\*AI = Analog input, AO = Analog output, DI = Digital input, DIO = Digital input/output, and DO = Digital output.

#### **Expanded Pin Description**

| PIN           | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PSEN0-PSEN11  | The PSEN0–PSEN11 outputs are programmable with the MFR_PSEN_CONFIG command for either active-<br>high or active-low operation and can be either open drain or push-pull. If not used for power-supply enables,<br>these outputs can be repurposed as general-purpose outputs using the MFR_PSEN_CONFIG command. If<br>these pins are used to enable power supplies, it is <b>highly recommended</b> that they have external pullups or<br>pulldowns to force the supplies into an off state when the device is not active.                                                                                                                                                                                      |

| PWM0-PWM7     | The PWM0–PWM7 outputs are high impedance when the margining is disabled. A 100% duty cycle implies the pins are continuously high. If not used for margining, these pins can be repurposed as general-purpose outputs with the MFR_PWM_CONFIG command.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| FAULT0-FAULT2 | The FAULT0–FAULT2 pins operate independently. Any global channel can be enabled with the MFR_FAULT_RESPONSE command to assert one or more of the FAULTn signals. Also, each global channel can be enabled to shut down when one or more of the FAULTn signals asserts. These pins are used to provide hardware control for power supplies across multiple devices. These outputs are unconditionally deasserted while RST is asserted or the device is power cycled. After device reset and upon device power-up, these outputs are pulled low immediately after program recall and held low until monitoring starts. Once monitoring starts, the FAULTn signals are released if no enabled faults are present. |

## PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

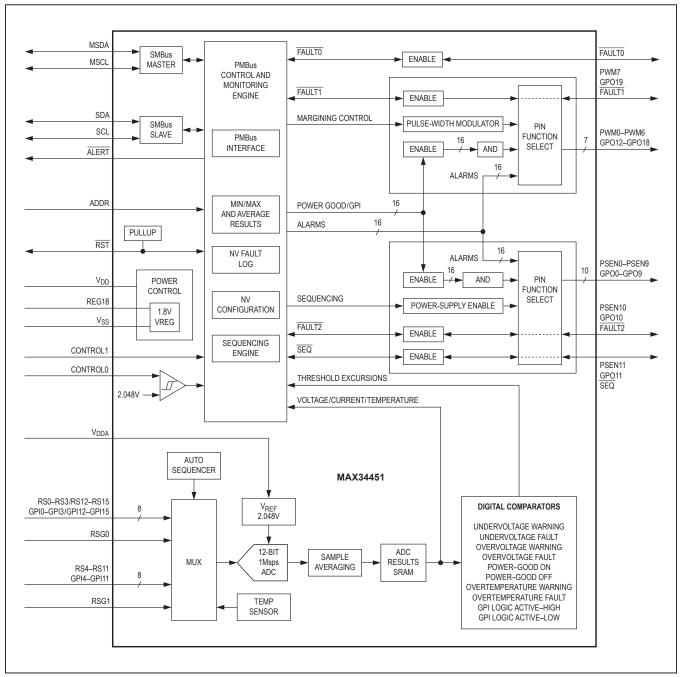

### Block Diagram

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### **Detailed Description**

The MAX34451 is a highly integrated system monitor with functionality to monitor up to 16 different voltages or currents and to sequence and close-loop margin up to 12 power supplies. It also supports local and remote thermal sensing.

The power-supply manager monitors the powersupply output voltage and current and constantly checks for user-programmable overvoltage, undervoltage, and overcurrent thresholds. It also has the ability to margin the power-supply output voltage up or down by a userprogrammable level. The margining is performed in a closed-loop arrangement, whereby the device automatically adjusts a PWM signal or an external current DAC output and then measures the resultant output voltage. The power-supply manager can also sequence the supplies in any order at both power-up and power-down.

Thermal monitoring can be accomplished using up to five temperature sensors including an on-chip temperature sensor and up to four external remote DS75LV digital temperature sensors. Communications with the DS75LV temperature sensors is conducted through a dedicated I<sup>2</sup>C/SMBus interface.

The device provides ALERT and FAULTn output signals. Host communications are conducted through a PMBuscompatible communications port.

See <u>Table 1</u> and <u>Table 2</u> for more details on specific device operation.

#### Table 1. PMBus PAGE to Pin/Resource Mapping

|               |                                     |                                       |     |                                                                        | PIN NAME                               |     |                                  |                                        |           |  |

|---------------|-------------------------------------|---------------------------------------|-----|------------------------------------------------------------------------|----------------------------------------|-----|----------------------------------|----------------------------------------|-----------|--|

| PMBus         | (1                                  | RSn/GPIn<br>6 AVAILABLE)              |     |                                                                        | PSENn/GPOn<br>12 AVAILABLE             | )   |                                  | PWMn/GPOn<br>(8 AVAILABLE)             |           |  |

| PMBus<br>PAGE | VOLTAGE<br>OR<br>CURRENT<br>MONITOR | GENERAL-<br>PURPOSE<br>INPUT<br>(GPI) | PIN | POWER-<br>SUPPLY<br>ENABLE<br>(PSEN)                                   | GENERAL-<br>PURPOSE<br>OUTPUT<br>(GPO) | PIN | PWM<br>MARGIN<br>OUTPUT<br>(PWM) | GENERAL-<br>PURPOSE<br>OUTPUT<br>(GPO) | PIN       |  |

| 0             | RS0                                 | GPI0                                  | 5   | PSEN0                                                                  | GPO0                                   | 38  | PWM0                             | GPO12                                  | 24        |  |

| 1             | RS1                                 | GPI1                                  | 4   | PSEN1                                                                  | GPO1                                   | 39  | PWM1                             | GPO13                                  | 25        |  |

| 2             | RS2                                 | GPI2                                  | 3   | PSEN2                                                                  | GPO2                                   | 40  | PWM2                             | GPO14                                  | 26        |  |

| 3             | RS3                                 | GPI3                                  | 2   | PSEN3                                                                  | GPO3                                   | 41  | PWM3                             | GPO15                                  | 27        |  |

| 4             | RS4                                 | GPI4                                  | 1   | PSEN4                                                                  | GPO4                                   | 42  | PWM4                             | GPO16                                  | 28        |  |

| 5             | RS5                                 | GPI5                                  | 56  | PSEN5                                                                  | GPO5                                   | 43  | PWM5                             | GPO17                                  | 29        |  |

| 6             | RS6                                 | GPI6                                  | 55  | PSEN6                                                                  | GPO6                                   | 44  | PWM6                             | GPO18                                  | 32        |  |

| 7             | RS7                                 | GPI7                                  | 54  | PSEN7                                                                  | GPO7                                   | 45  | PWM7                             | GPO19                                  | 33        |  |

| 8             | RS8                                 | GPI8                                  | 53  | PSEN8                                                                  | GPO8                                   | 46  |                                  |                                        |           |  |

| 9             | RS9                                 | GPI9                                  | 52  | PSEN9                                                                  | GPO9                                   | 48  | Margin ca                        | pability provided                      | d through |  |

| 10            | RS10                                | GPI10                                 | 51  | PSEN10                                                                 | GPO10                                  | 19  | the                              | external DS442                         | 24        |  |

| 11            | RS11                                | GPI11                                 | 50  | PSEN11                                                                 | GPO11                                  | 13  | ]                                |                                        |           |  |

| 12            | RS12                                | GPI12                                 | 49  |                                                                        |                                        |     |                                  |                                        |           |  |

| 13            | RS13                                | GPI13                                 | 47  | 47<br>20<br>14<br>Can monitor voltage or current or be assigned as GPI |                                        |     |                                  |                                        |           |  |

| 14            | RS14                                | GPI14                                 | 20  |                                                                        |                                        |     |                                  |                                        |           |  |

| 15            | RS15                                | GPI15                                 | 14  |                                                                        |                                        |     |                                  |                                        |           |  |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

### Table 2. Device Channel Capabilities and Options

| MAX34451<br>CHANNEL | PMBus<br>COMMAND<br>PAGE | CHANNEL CAPABILITIES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     |                          | <b>Voltage Monitor/Sequence/Margin/GPO Option:</b><br>Pins RSn/GPIn, PSENn, and PWMn (where n = 0–7) have a one-to-one association for each channel that monitors for voltage (RSn) and can be used to sequence (PSENn) and margin (PWMn) the power supply. The voltage monitored on this channel can also be configured to determine a power-good state. If not required for either sequencing or margining, the associated PSENn and PWMn outputs can be repurposed as GPOn outputs that can either indicate a logic combination of power-good (PG) and GPI states or report alarms. |

| 0–7                 | 0–7                      | <b>Current Monitor/GPO Option:</b><br>If the RSn/GPIn input is used to monitor current, then the channel is not used to sequence or margin. The associated PSENn and PWMn outputs can be repurposed as GPOn outputs that can either indicate a logic combination of power-good (PG) and GPI states or report alarms.                                                                                                                                                                                                                                                                   |

|                     |                          | <b>GPI/GPO Option:</b><br>If the RSn/GPIn input is configured as a general-purpose input (GPI), it can be used as a term in a logic combination to determine a power-good (PG) state and assert a GPOn output or act as a condition to allow a power supply to be enabled. The associated PSENn and PWMn outputs can be repurposed as GPOn outputs that can indicate power-good (PG) states or report alarms.                                                                                                                                                                          |

| 8–11                | 8–11                     | <b>Same as Channels 0–7 Except No PWM Outputs:</b><br>Pins RSn/GPIn, and PSENn (where n = 8–11) are the same as channels 0–7, except the PWMn outputs for these channels do not exist and instead the device uses an external DS4424 current DAC (connected to the master I <sup>2</sup> C local bus) to margin the power supplies. These channels can also be used to monitor current or be used as GPIn inputs just like channels 0–7.                                                                                                                                               |

| 12–15               | 12–15                    | Pins RSn/GPIn (where n = 12–15) cannot be used to control sequencing or for margining.<br><b>Voltage Monitor Option:</b><br>Monitor voltage including channel power-good (PG) and can also be configured to shut down one<br>or more power supplies if a fault occurs.<br><b>Current Monitor Option:</b><br>Monitor current and can be configured to shut down one or more power supplies if a fault occurs.<br><b>GPI Option:</b><br>As a general purpose input (CDI), can be used as a term in a logic combination to determine a                                                    |

|                     |                          | As a general-purpose input (GPI), can be used as a term in a logic combination to determine a power-good (PG) state and assert a GPOn output or act as a condition to allow a power supply to be enabled.                                                                                                                                                                                                                                                                                                                                                                              |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### Table 3. PMBus Command Codes

|      |                     |           |      | PA    | GE    |     |        | FLASH             | DEFAULT  |

|------|---------------------|-----------|------|-------|-------|-----|--------|-------------------|----------|

| CODE | COMMAND NAME        | TYPE      | 0–11 | 12–15 | 16–20 | 255 | NO. OF | STORED/<br>LOCKED | VALUE    |

|      |                     |           |      | (NO   | ГЕ 1) |     |        | (NOTE 2)          | (NOTE 2) |

| 00h  | PAGE                | R/W byte  | R/W  | R/W   | R/W   | R/W | 1      | N/N               | 00h      |

| 01h  | OPERATION           | R/W byte  | R/W  |       |       | W   | 1      | N/N               | 00h      |

| 02h  | ON_OFF_CONFIG       | R/W byte  | R/W  | R/W   | R/W   | R/W | 1      | Y/Y               | 1Ah      |

| 03h  | CLEAR_FAULTS        | Send byte | W    | W     | W     | W   | 0      | N/N               | _        |

| 10h  | WRITE_PROTECT       | R/W byte  | R/W  | R/W   | R/W   | R/W | 1      | N/Y               | 00h      |

| 11h  | STORE_DEFAULT_ALL   | Send byte | W    | W     | W     | W   | 0      | N/Y               | _        |

| 12h  | RESTORE_DEFAULT_ALL | Send byte | W    | W     | W     | W   | 0      | N/Y               | _        |

| 19h  | CAPABILITY          | Read byte | R    | R     | R     | R   | 1      | N/N               | 20h/30h  |

| 20h  | VOUT_MODE           | Read byte | R    | R     | R     | R   | 1      | FIXED/N           | 40h      |

| 25h  | VOUT_MARGIN_HIGH    | R/W word  | R/W  | _     | —     | _   | 2      | Y/Y               | 0000h    |

| 26h  | VOUT_MARGIN_LOW     | R/W word  | R/W  |       | _     | _   | 2      | Y/Y               | 0000h    |

| 2Ah  | VOUT_SCALE_MONITOR  | R/W word  | R/W  | R/W   |       | _   | 2      | Y/Y               | 7FFFh    |

| 38h  | IOUT_CAL_GAIN       | R/W word  | R/W  | R/W   | _     | _   | 2      | Y/Y               | 0000h    |

| 40h  | VOUT_OV_FAULT_LIMIT | R/W word  | R/W  | R/W   |       |     | 2      | Y/Y               | 7FFFh    |

| 42h  | VOUT_OV_WARN_LIMIT  | R/W word  | R/W  | R/W   | _     | _   | 2      | Y/Y               | 7FFFh    |

| 43h  | VOUT_UV_WARN_LIMIT  | R/W word  | R/W  | R/W   | —     | _   | 2      | Y/Y               | 0000h    |

| 44h  | VOUT_UV_FAULT_LIMIT | R/W word  | R/W  | R/W   | —     | _   | 2      | Y/Y               | 0000h    |

| 46h  | IOUT_OC_WARN_LIMIT  | R/W word  | R/W  | R/W   | —     | _   | 2      | Y/Y               | 7FFFh    |

| 4Ah  | IOUT_OC_FAULT_LIMIT | R/W word  | R/W  | R/W   | —     | _   | 2      | Y/Y               | 7FFFh    |

| 4Fh  | OT_FAULT_LIMIT      | R/W word  | —    | _     | R/W   | _   | 2      | Y/Y               | 7FFFh    |

| 51h  | OT_WARN_LIMIT       | R/W word  |      | _     | R/W   | _   | 2      | Y/Y               | 7FFFh    |

| 5Eh  | POWER_GOOD_ON       | R/W word  | R/W  | R/W   | _     | _   | 2      | Y/Y               | 0000h    |

| 5Fh  | POWER_GOOD_OFF      | R/W word  | R/W  | R/W   | —     | _   | 2      | Y/Y               | 0000h    |

| 60h  | TON_DELAY           | R/W word  | R/W  | _     | _     | _   | 2      | Y/Y               | 0000h    |

| 62h  | TON_MAX_FAULT_LIMIT | R/W word  | R/W  | _     | _     | _   | 2      | Y/Y               | FFFFh    |

| 64h  | TOFF_DELAY          | R/W word  | R/W  |       | _     | _   | 2      | Y/Y               | 0000h    |

| 79h  | STATUS_WORD         | Read word | R    | R     | R     | R   | 2      | N/N               | 0000h    |

| 7Ah  | STATUS_VOUT         | Read byte | R    | R     | _     | _   | 1      | N/N               | 00h      |

| 7Bh  | STATUS_IOUT         | Read byte | R    | R     | _     | _   | 1      | N/N               | 00h      |

| 7Dh  | STATUS_TEMPERATURE  | Read byte | _    | _     | R     | _   | 1      | N/N               | 00h      |

| 7Eh  | STATUS_CML          | Read byte | R    | R     | R     | R   | 1      | N/N               | 00h      |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### Table 3. PMBus Command Codes (continued)

|      |                         |           |      | PA    | GE    |     |                 | FLASH             | DEFAULT<br>VALUE<br>(NOTE 2)            |

|------|-------------------------|-----------|------|-------|-------|-----|-----------------|-------------------|-----------------------------------------|

| CODE | COMMAND NAME            | TYPE      | 0–11 | 12–15 | 16–20 | 255 | NO. OF<br>BYTES | STORED/<br>LOCKED |                                         |

|      |                         |           |      | (NO   | ГЕ 1) | 1   | DITES           | (NOTE 2)          |                                         |

| 80h  | STATUS_MFR_SPECIFIC     | Read byte | R    | R     | _     | R   | 1               | N/N               | 00h                                     |

| 8Bh  | READ_VOUT               | Read word | R    | R     | —     | —   | 2               | N/N               | 0000h                                   |

| 8Ch  | READ_IOUT               | Read word | R    | R     | —     | —   | 2               | N/N               | 0000h                                   |

| 8Dh  | READ_TEMPERATURE_1      | Read word | —    | _     | R     | —   | 2               | N/N               | 0000h                                   |

| 98h  | PMBUS_REVISION          | Read byte | R    | R     | R     | R   | 1               | FIXED/N           | 11h                                     |

| 99h  | MFR_ID                  | Read byte | R    | R     | R     | R   | 1               | FIXED/N           | 4Dh                                     |

| 9Ah  | MFR_MODEL               | Read byte | R    | R     | R     | R   | 1               | FIXED/N           | 59h                                     |

| 9Bh  | MFR_REVISION            | Read word | R    | R     | R     | R   | 2               | FIXED/N           | (Note 3)                                |

| 9Ch  | MFR_LOCATION            | R/W 64    | R/W  | R/W   | R/W   | R/W | 8               | Y/Y               | (Note 4)                                |

| 9Dh  | MFR_DATE                | R/W 64    | R/W  | R/W   | R/W   | R/W | 8               | Y/Y               | (Note 4)                                |

| 9Eh  | MFR_SERIAL              | R/W 64    | R/W  | R/W   | R/W   | R/W | 8               | Y/Y               | (Note 4)                                |

| D1h  | MFR_MODE                | R/W word  | R/W  | R/W   | R/W   | R/W | 2               | Y/Y               | 0020h                                   |

| D2h  | MFR_PSEN_CONFIG         | R/W 32    | R/W  |       | _     |     | 4               | Y/Y               | (Note 5)                                |

| D4h  | MFR_VOUT_PEAK           | R/W word  | R/W  | R/W   | _     | _   | 2               | N/Y               | 0000h                                   |

| D5h  | MFR_IOUT_PEAK           | R/W word  | R/W  | R/W   | _     |     | 2               | N/Y               | 0000h                                   |

| D6h  | MFR_TEMPERATURE_PEAK    | R/W word  | —    | —     | R/W   | —   | 2               | N/Y               | 8000h                                   |

| D7h  | MFR_VOUT_MIN            | R/W word  | R/W  | R/W   | —     | _   | 2               | N/Y               | 7FFFh                                   |

| D8h  | MFR_NV_LOG_CONFIG       | R/W word  | R/W  | R/W   | R/W   | R/W | 2               | Y/Y               | 0000h                                   |

| D9h  | MFR_FAULT_RESPONSE      | R/W 32    | R/W  | R/W   |       |     | 4               | Y/Y               | (Note 5)                                |

| DAh  | MFR_FAULT_RETRY         | R/W word  | R/W  | R/W   | R/W   | R/W | 2               | Y/Y               | 0000h                                   |

| DCh  | MFR_NV_FAULT_LOG        | Read 32   | R    | R     | R     | R   | 255             | Y/Y               | (Note 6)                                |

| DDh  | MFR_TIME_COUNT          | R/W 32    | R/W  | R/W   | R/W   | R/W | 4               | N/Y               | (Note 5)                                |

| DFh  | MFR_MARGIN_CONFIG       | R/W word  | R/W  |       | _     |     | 2               | Y/Y               | 0000h                                   |

| E0h  | MFR_FW_SERIAL           | R word    | _    | _     | _     | R   | 2               | N/N               | <firmware<br>revision&gt;</firmware<br> |

| E2h  | MFR_IOUT_AVG            | R/W word  | R    | R     | _     | _   | 2               | N/Y               | 0000h                                   |

| E4h  | MFR_CHANNEL_CONFIG      | R/W word  | R/W  | R/W   | _     |     | 2               | Y/Y               | 0000h                                   |

| E6h  | MFR_TON_SEQ_MAX         | R/W word  | R/W  |       | _     |     | 2               | Y/Y               | 0000h                                   |

| E7h  | MFR_PWM_CONFIG (Note 7) | R/W 32    | R/W  | _     | _     | _   | 4               | Y/Y               | (Note 5)                                |

| E8h  | MFR_SEQ_CONFIG          | R/W 32    | R/W  | _     | —     | —   | 4               | Y/Y               | (Note 5)                                |

# PMBus 16-Channel V/I Monitor and 12-Channel Sequencer/Marginer

#### Table 3. PMBus Command Codes (continued)

|      | CODE COMMAND NAME      |            | PAGE     |       |       |     |          | FLASH             | DEFAULT |  |

|------|------------------------|------------|----------|-------|-------|-----|----------|-------------------|---------|--|

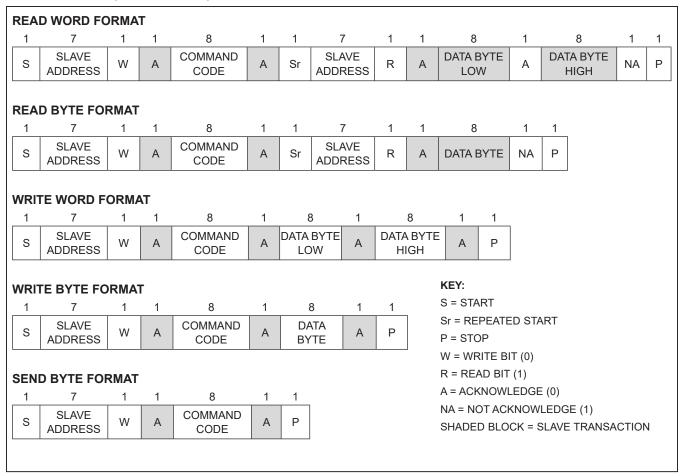

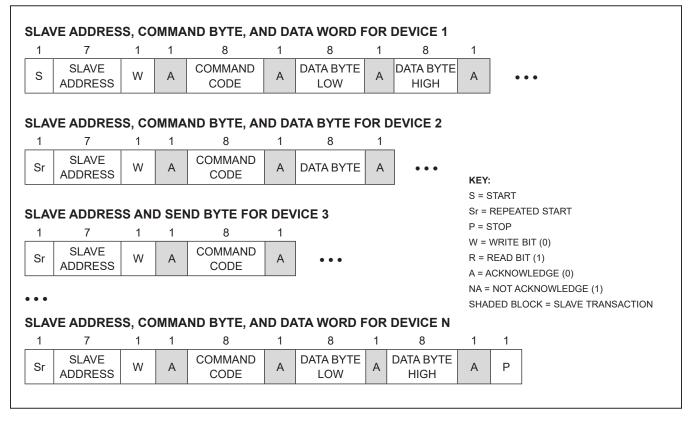

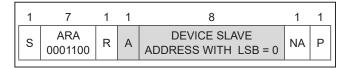

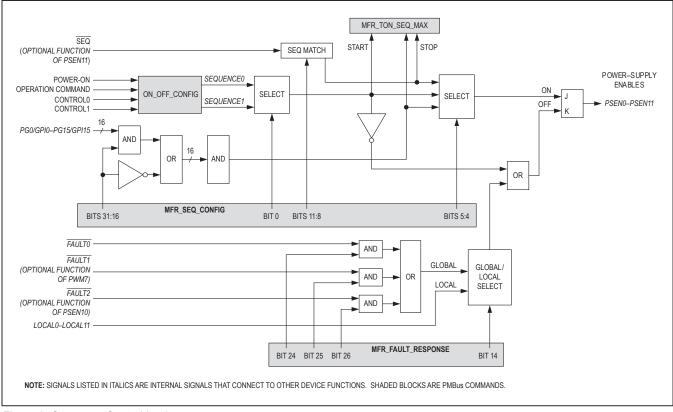

| CODE |                        |            | 0–11     | 12–15 | 16–20 | 255 | NO. OF   | STORED/<br>LOCKED | VALUE   |  |