LTC2846

# 3.3V Software-Selectable Multiprotocol Transceiver with Termination

The LTC<sup>®</sup>2846 is a 3-driver/3-receiver multiprotocol trans-

ceiver with on-chip cable termination. When combined with

the LTC2844 or LTC2845, this chip set forms a complete

software-selectable DTE or DCE interface port that supports

the RS232, RS449, EIA530, EIA530-A, V.35, V.36 and X.21

protocols. All necessary cable termination is provided inside

the LTC2846. The LTC2846 has a boost regulator that takes in a 3.3V input and switches at 1.2MHz, allowing the use of

tiny, low cost capacitors and inductors 2mm or less in height.

The 5V output drives an internal charge pump that requires

only five space-saving surface mounted capacitors. The

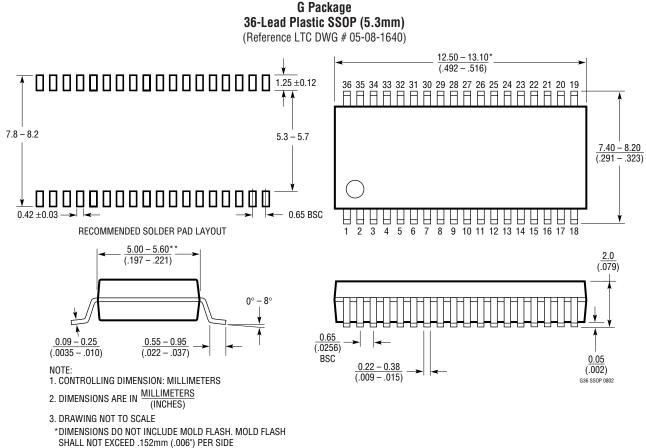

LTC2846 is available in a 36-lead SSOP surface mount

T, LTC and LT are registered trademarks of Linear Technology Corporation.

DESCRIPTION

# FEATURES

- Software-Selectable Transceiver Supports: RS232, RS449, EIA530, EIA530-A, V.35, V.36, X.21

- Operates from Single 3.3V Supply

- TUV Rheinland of North America Inc. Certified NET1, NET2 and TBR2 Compliant, Report No.: TBR2/050101/02, TBR2/051501/02

- 1.2MHz Boost Switching Regulator for 3.3V to 5V Conversion

- On-Chip Cable Termination

- Complete DTE or DCE Port with LTC2844 or LTC2845

- Small Footprint

- Available in 36-Lead SSOP (0.209 Wide) Package

# **APPLICATIONS**

- Data Networking

- CSU and DSU

- Data Routers

# TYPICAL APPLICATION

#### Ш CTS DSR DCD DTR RTS RXD RXC тхс SCTE TXD LTC2844 LTC2846 D2 D1 D4 T T Т Т Т Ŧ ۲ CTS A (106) CTS B DTR B RTS B DSR B DCD B SG (102) RXD B SCTE B TXD B DCD A (109) DTR A (108 RXC B TXC B DSR A (107 RTS A (105) SHIELD (101 RXD A (104 RXC A (115) TXC A (114) SCTE A (113) LL A (141) TXD A (103) **DB-25 CONNECTOR** 2846 TA01

Complete DTE or DCE Multiprotocol Serial Interface with DB-25 Connector

package.

# **ABSOLUTE MAXIMUM RATINGS**

| (Note 1)                                            |

|-----------------------------------------------------|

| $V_{CC}$ Voltage0.3V to 6.5V                        |

| V <sub>IN</sub> Voltage0.3V to 6.5V                 |

| Input Voltage                                       |

| Transmitters $-0.3V$ to (V <sub>CC</sub> + 0.3V)    |

| Receivers18V to 18V                                 |

| Logic Pins $-0.3V$ to (V <sub>CC</sub> + 0.3V)      |

| Output Voltage                                      |

| Transmitters $(V_{EE} - 0.3V)$ to $(V_{DD} + 0.3V)$ |

| Receivers $-0.3V$ to $(V_{IN} + 0.3V)$              |

| V <sub>EE</sub> – 10V to 0.3V                       |

| V <sub>DD</sub> 0.3V to 10V                         |

| Short-Circuit Duration                              |

| Transmitter Output Indefinite                       |

| Receiver Output Indefinite                          |

| V <sub>EE</sub>                                     |

| SW Voltage0.4V to 36V                               |

| FB Voltage0.3V to 2.5V                              |

| Current into FB Pin ±1mA                            |

| SHDN Voltage0.3V to 10V                             |

| Operating Temperature Range                         |

| LTC2846C                                            |

| LTC2846I40°C to 85°C                                |

| Storage Temperature Range –65°C to 150°C            |

| Lead Temperature (Soldering, 10 sec) 300°C          |

|                                                     |

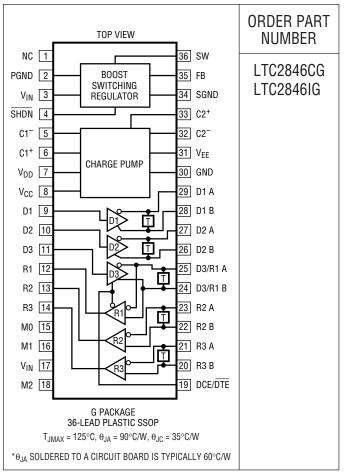

# PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

# **ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. $V_{CC} = 5V$ , $V_{IN} = 3.3V$ , $V_{\overline{SHDN}} = V_{IN}$ , unless otherwise noted. (Notes 2, 3)

| SYMBOL          | PARAMETER                                                                                | CONDITIONS                                                                                                                                               |   | MIN         | ТҮР                                 | MAX                     | UNITS                      |

|-----------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------|-------------------------------------|-------------------------|----------------------------|

| Supplies        |                                                                                          |                                                                                                                                                          |   |             |                                     |                         |                            |

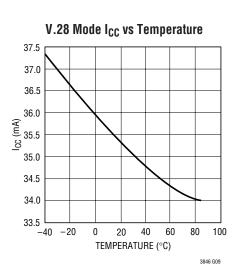

| I <sub>CC</sub> | V <sub>CC</sub> Supply Current (DCE Mode,<br>All Digital Pins = GND or V <sub>IN</sub> ) | RS530, RS530-A, X.21 Modes, No Load<br>RS530, RS530-A, X.21 Modes, Full Load<br>V.35 Mode<br>V.28 Mode, No Load<br>V.28 Mode, Full Load<br>No-Cable Mode | • |             | 14<br>100<br>126<br>20<br>35<br>300 | 130<br>170<br>75<br>900 | mA<br>mA<br>mA<br>mA<br>μA |

| P <sub>D</sub>  | Internal Power Dissipation (DCE Mode)                                                    | RS530, RS530-A, X.21 Modes, Full Load<br>V.35 Mode, Full Load<br>V.28 Mode, Full Load                                                                    |   |             | 550<br>775<br>200                   |                         | mW<br>mW<br>mW             |

| V+              | Positive Charge Pump Output Voltage                                                      | V.11 or V.28 Mode, No Load<br>V.35 Mode<br>V.28 Mode, with Load<br>V.28 Mode, with Load, I <sub>DD</sub> = 10mA                                          | • | 8<br>7<br>8 | 9.3<br>8.0<br>8.7<br>6.5            |                         | V<br>V<br>V<br>V           |

**ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$ ,  $V_{IN} = 3.3V$ ,  $V_{\overline{SHDN}} = V_{IN}$ , unless otherwise noted. (Notes 2, 3)

| SYMBOL                          | PARAMETER                                                        | CONDITIONS                                                                                                                                                                                    |   | MIN                       | ТҮР                          | MAX                              | UNITS                |

|---------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------|------------------------------|----------------------------------|----------------------|

| V-                              | Negative Charge Pump Output Voltage                              | V.28 Mode, No Load<br>V.28 Mode, Full Load<br>V.35 Mode<br>RS530, RS530-A, X.21 Modes, Full Load                                                                                              | • | -7.5<br>-5.5<br>-4.5      | -9.6<br>-8.5<br>-6.5<br>-6.0 |                                  | V<br>V<br>V<br>V     |

| f <sub>OSC</sub>                | Charge Pump Oscillator Frequency                                 |                                                                                                                                                                                               |   |                           | 500                          |                                  | kHz                  |

| t <sub>r</sub>                  | Charge Pump Rise Time                                            | No-Cable Mode/Power-Off to Normal Operation                                                                                                                                                   |   |                           | 2                            |                                  | ms                   |

| Logic Input                     | ts and Outputs                                                   |                                                                                                                                                                                               |   |                           |                              |                                  |                      |

| V <sub>IH</sub>                 | Logic Input High Voltage                                         | D1, D2, D3, M0, M1, M2, DCE/DTE<br>SHDN                                                                                                                                                       | • | 2.0<br>2.4                |                              |                                  | V<br>V               |

| V <sub>IL</sub>                 | Logic Input Low Voltage                                          | D1, D2, D3, M0, M1, M2, DCE/DTE<br>SHDN                                                                                                                                                       | • |                           |                              | 0.8<br>0.5                       | V<br>V               |

| I <sub>IN</sub>                 | Logic Input Current                                              | D1, D2, D3<br>M0, M1, M2, DCE/ $\overline{\text{DTE}}$ = GND<br>M0, M1, M2, DCE/ $\overline{\text{DTE}}$ = V <sub>IN</sub><br>$\overline{\text{SHDN}}$ = GND<br>$\overline{\text{SHDN}}$ = 3V | • | -30                       | -75<br>16                    | ±10<br>-120<br>±10<br>±0.1<br>32 | μΑ<br>μΑ<br>μΑ<br>μΑ |

| V <sub>OH</sub>                 | Output High Voltage                                              | $I_0 = -3mA$                                                                                                                                                                                  | • | 2.7                       | 3                            |                                  |                      |

| V <sub>OL</sub>                 | Output Low Voltage                                               | I <sub>0</sub> = 1.6mA                                                                                                                                                                        | • |                           | 0.2                          | 0.4                              | V                    |

| I <sub>OSR</sub>                | Output Short-Circuit Current                                     | $0V \le V_0 \le V_{IN}$                                                                                                                                                                       | • |                           |                              | ±50                              | mA                   |

| I <sub>OZR</sub>                | Three-State Output Current                                       | $MO = M1 = M2 = V_{IN}, V_O = GND$<br>$MO = M1 = M2 = V_{IN}, V_O = V_{IN}$                                                                                                                   | • | -30                       | -85                          | -160<br>±10                      | μΑ<br>μΑ             |

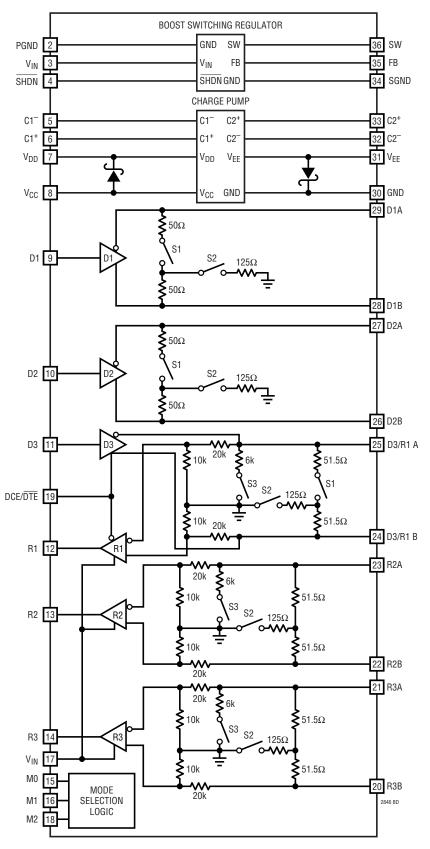

| V.11 Drive                      | r                                                                | -                                                                                                                                                                                             |   |                           |                              |                                  |                      |

| V <sub>ODO</sub>                | Open Circuit Differential Output Voltage                         | R <sub>L</sub> = 1.95k (Figure 1)                                                                                                                                                             |   |                           |                              | ±5                               | V                    |

| V <sub>ODL</sub>                | Loaded Differential Output Voltage                               | $ \begin{array}{l} R_{L} = 50\Omega \; (\text{Figure 1}) \\ R_{L} = 50\Omega \; (\text{Figure 1}) \end{array} $                                                                               | • | 0.5V <sub>0D0</sub><br>±2 |                              | 0.67V <sub>0D0</sub>             | V<br>V               |

| $\Delta V_{0D}$                 | Change in Magnitude of Differential<br>Output Voltage            | $R_L = 50\Omega$ (Figure 1)                                                                                                                                                                   | • |                           |                              | 0.2                              | V                    |

| V <sub>OC</sub>                 | Common Mode Output Voltage                                       | $R_L = 50\Omega$ (Figure 1)                                                                                                                                                                   |   |                           |                              | 3                                | V                    |

| $\Delta V_{0C}$                 | Change in Magnitude of Common Mode<br>Output Voltage             | $R_L = 50\Omega$ (Figure 1)                                                                                                                                                                   | • |                           |                              | 0.2                              | V                    |

| I <sub>SS</sub>                 | Short-Circuit Current                                            | V <sub>OUT</sub> = GND                                                                                                                                                                        |   |                           |                              | ±150                             | mA                   |

| I <sub>OZ</sub>                 | Output Leakage Current                                           | $ V_A $ and $ V_B  \le 0.25V,$ Power Off or No-Cable Mode or Driver Disabled                                                                                                                  | • |                           | ±1                           | ±100                             | μA                   |

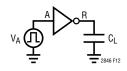

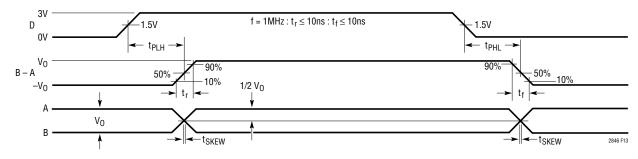

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                                                | (Figures 2, 13)                                                                                                                                                                               | • | 2                         | 15                           | 25                               | ns                   |

| t <sub>PLH</sub>                | Input to Output Rising                                           | (Figures 2, 13)                                                                                                                                                                               | • | 15                        | 40                           | 65                               | ns                   |

| t <sub>PHL</sub>                | Input to Output Falling                                          | (Figures 2, 13)                                                                                                                                                                               | • | 15                        | 40                           | 65                               | ns                   |

| Δt                              | Input to Output Difference,  t <sub>PLH</sub> - t <sub>PHL</sub> | (Figures 2, 13)                                                                                                                                                                               | • | 0                         | 3                            | 12                               | ns                   |

| t <sub>SKEW</sub>               | Output to Output Skew                                            | (Figures 2, 13)                                                                                                                                                                               |   |                           | 3                            |                                  | ns                   |

**ELECTRICAL CHARACTERISTICS** The • denotes specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V_{CC} = 5V$ ,  $V_{IN} = 3.3V$ ,  $V_{SHDN} = V_{IN}$ , unless otherwise noted. (Notes 2, 3)

| SYMBOL                            | PARAMETER                                                        |                                                                                         | MIN | ТҮР   | MAX   | UNITS         |        |

|-----------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-------|-------|---------------|--------|

| V.11 Receiv                       | ver                                                              |                                                                                         |     |       |       | I             |        |

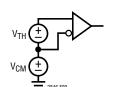

| V <sub>TH</sub>                   | Input Threshold Voltage                                          | $-7V \le V_{CM} \le 7V$                                                                 |     | -0.2  |       | 0.2           | V      |

| $\Delta V_{TH}$                   | Input Hysteresis                                                 | $-7V \le V_{CM} \le 7V$                                                                 |     |       | 15    | 40            | mV     |

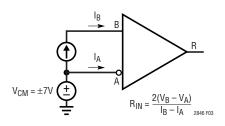

| R <sub>IN</sub>                   | Input Impedance                                                  | $-7V \le V_{CM} \le 7V$ (Figure 3)                                                      |     | 100   | 103   |               | Ω      |

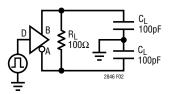

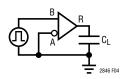

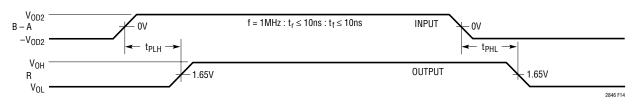

| t <sub>r</sub> , t <sub>f</sub>   | Rise or Fall Time                                                | C <sub>L</sub> = 50pF (Figures 4, 14)                                                   |     |       | 15    |               | ns     |

| t <sub>PLH</sub>                  | Input to Output Rising                                           | C <sub>L</sub> = 50pF (Figures 4, 14)                                                   | •   |       | 50    | 90            | ns     |

| t <sub>PHL</sub>                  | Input to Output Falling                                          | C <sub>L</sub> = 50pF (Figures 4, 14)                                                   |     |       | 50    | 90            | ns     |

| Δt                                | Input to Output Difference,  t <sub>PLH</sub> - t <sub>PHL</sub> | C <sub>L</sub> = 50pF (Figures 4, 14)                                                   | •   | 0     | 4     | 25            | ns     |

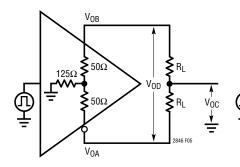

| V.35 Driver                       |                                                                  |                                                                                         |     |       |       | <b>I</b>      |        |

| V <sub>OD</sub>                   | Differential Output Voltage                                      | Open Circuit, $R_L = 1.95k$ (Figure 5)<br>With Load, $-4V \le V_{CM} \le 4V$ (Figure 6) | •   | ±0.44 | ±0.55 | ±1.2<br>±0.66 | V<br>V |

| V <sub>OA</sub> , V <sub>OB</sub> | Single-Ended Output Voltage                                      | Open Circuit, R <sub>L</sub> = 1.95k (Figure 5)                                         | •   |       |       | ±1.2          | V      |

| V <sub>OC</sub>                   | Transmitter Output Offset                                        | $R_L = 50\Omega$ (Figure 5)                                                             | •   |       |       | ±0.6          | V      |

| I <sub>OH</sub>                   | Transmitter Output High Current                                  | $V_A, V_B = 0V$                                                                         | •   | -9    | -11   | -13           | mA     |

| I <sub>OL</sub>                   | Transmitter Output Low Current                                   | $V_A, V_B = 0V$                                                                         | •   | 9     | 11    | 13            | mA     |

| I <sub>OZ</sub>                   | Transmitter Output Leakage Current                               | $ V_A $ and $ V_B  \le 0.25V$                                                           | •   |       | ±1    | ±100          | μA     |

| R <sub>0D</sub>                   | Transmitter Differential Mode Impedance                          |                                                                                         | •   | 50    | 100   | 150           | Ω      |

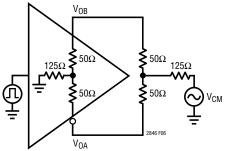

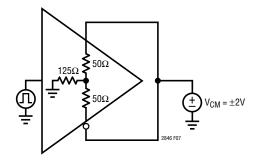

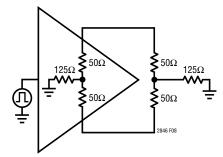

| R <sub>0C</sub>                   | Transmitter Common Mode Impedance                                | $-2V \le V_{CM} \le 2V$ (Figure 7)                                                      |     | 135   | 150   | 165           | Ω      |

| t <sub>r</sub> , t <sub>f</sub>   | Rise or Fall Time                                                | (Figures 8, 13)                                                                         |     |       | 5     |               | ns     |

| t <sub>PLH</sub>                  | Input to Output                                                  | (Figures 8, 13)                                                                         | •   | 15    | 35    | 65            | ns     |

| t <sub>PHL</sub>                  | Input to Output                                                  | (Figures 8, 13)                                                                         | •   | 15    | 35    | 65            | ns     |

| Δt                                | Input to Output Difference,  t <sub>PLH</sub> - t <sub>PHL</sub> | (Figures 8, 13)                                                                         | •   |       | 0     | 16            | ns     |

| t <sub>SKEW</sub>                 | Output to Output Skew                                            | (Figures 8, 13)                                                                         |     |       | 4     |               | ns     |

| V.35 Receiv                       | ver                                                              | ·                                                                                       |     |       |       |               |        |

| V <sub>TH</sub>                   | Differential Receiver Input Threshold Voltage                    | $-2V \le V_{CM} \le 2V$ (Figure 9)                                                      |     | -0.2  |       | 0.2           | V      |

| $\Delta V_{TH}$                   | Receiver Input Hysteresis                                        | $-2V \le V_{CM} \le 2V$ (Figure 9)                                                      |     |       | 15    | 40            | mV     |

| R <sub>ID</sub>                   | Receiver Differential Mode Impedance                             | $-2V \le V_{CM} \le 2V$                                                                 | •   | 90    | 103   | 110           | Ω      |

| R <sub>IC</sub>                   | Receiver Common Mode Impedance                                   | $-2V \le V_{CM} \le 2V$ (Figure 10)                                                     |     | 135   | 150   | 165           | Ω      |

| t <sub>r</sub> , t <sub>f</sub>   | Rise or Fall Time                                                | C <sub>L</sub> = 50pF (Figures 4, 14)                                                   |     |       | 15    |               | ns     |

| t <sub>PLH</sub>                  | Input to Output                                                  | $C_L = 50 pF$ (Figures 4, 14)                                                           |     |       | 50    | 90            | ns     |

| t <sub>PHL</sub>                  | Input to Output                                                  | C <sub>L</sub> = 50pF (Figures 4, 14)                                                   | •   |       | 50    | 90            | ns     |

| Δt                                | Input to Output Difference, $ t_{PLH} - t_{PHL} $                | C <sub>L</sub> = 50pF (Figures 4, 14)                                                   | •   | 0     | 4     | 25            | ns     |

| V.28 Driver                       |                                                                  |                                                                                         | •   |       |       |               |        |

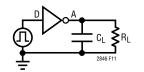

| V <sub>0</sub>                    | Output Voltage                                                   | Open Circuit<br>R <sub>L</sub> = 3k (Figure 11)                                         | •   | ±5    | ±8.5  | ±10           | V<br>V |

| I <sub>SS</sub>                   | Short-Circuit Current                                            | V <sub>OUT</sub> = GND                                                                  | •   |       |       | ±150          | mA     |

| R <sub>0Z</sub>                   | Power-Off Resistance                                             | $-2V < V_0 < 2V$ , Power Off<br>or No-Cable Mode                                        | •   | 300   |       |               | Ω      |

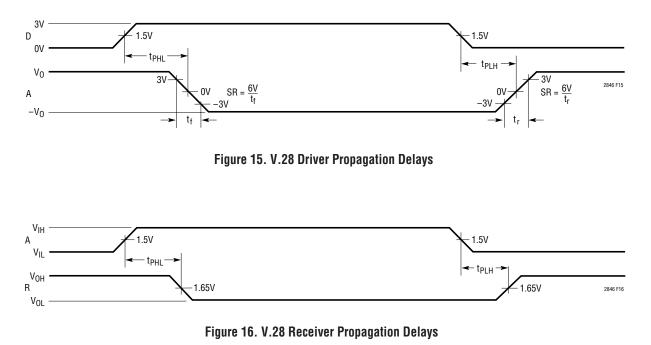

| SR                                | Slew Rate                                                        | $R_L = 7k, C_L = 0$ (Figures 11, 15)                                                    | •   | 4     |       | 30            | V/µs   |

| t <sub>PLH</sub>                  | Input to Output                                                  | R <sub>L</sub> = 3k, C <sub>L</sub> = 2500pF (Figures 11, 15)                           | •   |       | 1.5   | 2.5           | μs     |

| t <sub>PHL</sub>                  | Input to Output                                                  | R <sub>L</sub> = 3k, C <sub>L</sub> = 2500pF (Figures 11, 15)                           |     |       | 1.5   | 2.5           | μs     |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>CC</sub> = 5V, V<sub>IN</sub> = 3.3V, V<sub>SHDN</sub> = V<sub>IN</sub>, unless otherwise noted. (Notes 2, 3)

| SYMBOL                          | PARAMETER                                          | CONDITIONS                                                                                 |   | MIN   | ТҮР         | MAX    | UNITS    |

|---------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------|---|-------|-------------|--------|----------|

| V.28 Recei                      | ver                                                | <u>.</u>                                                                                   |   |       |             |        |          |

| V <sub>THL</sub>                | Input Low Threshold Voltage                        | (Figure 12)                                                                                | • |       |             | 0.8    | V        |

| V <sub>TLH</sub>                | Input High Threshold Voltage                       | (Figure 12)                                                                                | • | 2     |             |        | V        |

| $\Delta V_{TH}$                 | Receiver Input Hysteresis                          | (Figure 12)                                                                                | • | 0     | 0.05        | 0.3    | V        |

| R <sub>IN</sub>                 | Receiver Input Impedance                           | $-15V \le V_A \le 15V$                                                                     | • | 3     | 5           | 7      | kΩ       |

| t <sub>r</sub> , t <sub>f</sub> | Rise or Fall Time                                  | C <sub>L</sub> = 50pF (Figures 12, 16)                                                     |   |       | 15          |        | ns       |

| t <sub>PLH</sub>                | Input to Output                                    | C <sub>L</sub> = 50pF (Figures 12, 16)                                                     | • |       | 60          | 300    | ns       |

| t <sub>PHL</sub>                | Input to Output                                    | C <sub>L</sub> = 50pF (Figures 12, 16)                                                     | • |       | 160         | 300    | ns       |

| Boost Swit                      | ching Regulator (Note 4)                           |                                                                                            |   |       |             |        |          |

| V <sub>IN</sub>                 | Operating Voltage                                  |                                                                                            |   | 3     | 3.3         | 3.6    | V        |

| V <sub>FB</sub>                 | Feedback Voltage                                   |                                                                                            | • | 1.230 | 1.255       | 1.280  | V        |

| I <sub>FB</sub>                 | FB Pin Bias Current                                | V <sub>FB</sub> = 1.255V                                                                   | • |       | 120         | 360    | nA       |

| IQ                              | Quiescent Current<br>Quiescent Current in Shutdown | $V_{\overline{SHDN}} = 2.4V$ , Not Switching<br>$V_{\overline{SHDN}} = 0V$ , $V_{IN} = 3V$ |   |       | 4.2<br>0.01 | 6<br>1 | mA<br>μA |

| $\Delta V_{FB(LR)}$             | Reference Line Regulation                          | $3V \le V_{IN} \le 3.6V$                                                                   |   |       | 0.01        | 0.05   | %/V      |

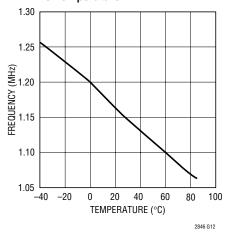

| f                               | Switching Frequency                                |                                                                                            | • | 0.85  | 1.2         | 1.6    | MHz      |

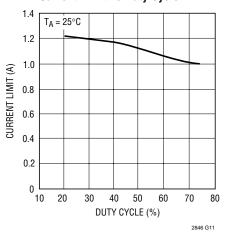

| DC <sub>MAX</sub>               | Maximum Duty Cycle                                 |                                                                                            | • | 82    | 90          |        | %        |

| I <sub>LIM</sub>                | Switch Current Limit                               | (Note 5)                                                                                   |   | 1     | 1.2         | 2      | A        |

| V <sub>SAT</sub>                | Switch V <sub>CESAT</sub>                          | I <sub>SW</sub> = 900mA                                                                    |   |       | 350         |        | mV       |

| I <sub>LEAK</sub>               | Switch Leakage Current                             | V <sub>SW</sub> = 5V                                                                       |   |       | 0.01        | 1      | μA       |

Note 1: Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

Note 3: All typicals are given for  $V_{CC} = 5V$ ,  $V_{IN} = 3.3V$ ,  $C_{VCC} = C_{VIN} = 10 \mu F$ ,  $C_{VDD}$  = 1µF,  $C_{VEE}$  = 3.3µF and  $T_A$  = 25°C.

Note 2: All currents into device pins are positive; all currents out of device are negative. All voltages are referenced to device ground unless otherwise specified.

Note 4: The Boost Regulator is specified for  $V_{IN}$  = 3V unless otherwise noted.

Note 5: Current limit guaranteed by design and/or correlation to static test.

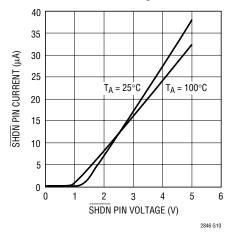

# TYPICAL PERFORMANCE CHARACTERISTICS

# **TYPICAL PERFORMANCE CHARACTERISTICS**

Boost Switching Regulator Oscillator Frequency vs Temperature

Boost Switching Regulator SHDN Pin Current vs Voltage

Boost Switching Regulator Current Limit vs Duty Cycle

sn2846 2846fs

# PIN FUNCTIONS

NC (Pin 1): No Connect.

**PGND (Pin 2):** Boost Switching Regulator Power Ground. Tie PGND to SGND.

$V_{IN}$  (Pin 3): Input Supply Pin. Input supply to boost switching regulator.  $3V \leq V_{IN} \leq 3.6V$ . Bypass with a  $10 \mu F$  capacitor to ground.

**SHDN** (Pin 4): Boost Switching Regulator Shutdown Pin. Tie to 2.4V or more to enable regulator. Ground to shut down.

**C1<sup>-</sup> (Pin 5):** Capacitor C1 Negative Terminal. Connect a  $1\mu$ F capacitor between C1<sup>+</sup> and C1<sup>-</sup>.

**C1<sup>+</sup>** (**Pin 6**): Capacitor C1 Positive Terminal. Connect a  $1\mu$ F capacitor between C1<sup>+</sup> and C1<sup>-</sup>.

$V_{DD}$  (Pin 7): Generated Positive Supply Voltage for V.28. Connect a 1µF capacitor to ground.

$V_{CC}$  (Pin 8): Input Supply Pin. Input supply to transceiver. 4.75V  $\leq$   $V_{CC}$   $\leq$  5.25V. Connect to output of switching regulator.

D1 (Pin 9): TTL Level Driver 1 Input.

D2 (Pin 10): TTL Level Driver 2 Input.

D3 (Pin 11): TTL Level Driver 3 Input.

**R1 (Pin 12):** CMOS Level Receiver 1 Output with Pull-Up to  $V_{IN}$  when Three-Stated.

**R2 (Pin 13):** CMOS Level Receiver 2 Output with Pull-Up to  $V_{IN}$  when Three-Stated.

**R3 (Pin 14):** CMOS Level Receiver 3 Output with Pull-Up to V<sub>IN</sub> when Three-Stated.

**MO (Pin 15):** TTL Level Mode Select Input 0 with Pull-Up to  $V_{IN}$ . See Table 1.

**M1 (Pin 16):** TTL Level Mode Select Input 1 with Pull-Up to  $V_{IN}$ . See Table 1.

$V_{IN}$  (Pin 17): Input Supply Pin. Input supply to transceiver.  $3V \le V_{IN} \le 3.6V$ . Connect to Pin 3. **M2 (Pin 18):** TTL Level Mode Select Input 2 with Pull-Up to  $V_{IN}$ . See Table 1.

$\text{DCE}/\overline{\text{DTE}}$  (Pin 19): TTL Level Mode Select Input with Pull-Up to V\_{IN}. See Table 1.

R3 B (Pin 20): Receiver 3 Noninverting Input.

R3 A (Pin 21): Receiver 3 Inverting Input.

R2 B (Pin 22): Receiver 2 Noninverting Input.

R2 A (Pin 23): Receiver 2 Inverting Input.

**D3/R1 B (Pin 24):** Receiver 1 Noninverting Input and Driver 3 Noninverting Output.

**D3/R1 A (Pin 25):** Receiver 1 Inverting Input and Driver 3 Inverting Output.

D2 B (Pin 26): Driver 2 Noninverting Output.

D2 A (Pin 27): Driver 2 Inverting Output.

D1 B (Pin 28): Driver 1 Noninverting Output.

D1 A (Pin 29): Driver 1 Inverting Output.

GND (Pin 30): Transceiver Ground.

$V_{EE}$  (Pin 31): Generated Negative Supply Voltage. Connect a 3.3 $\mu$ F capacitor to GND.

C2<sup>-</sup> (Pin 32): Capacitor C2 Negative Terminal. Connect a  $1\mu$ F capacitor between C2<sup>+</sup> and C2<sup>-</sup>.

**C2<sup>+</sup>** (**Pin 33**): Capacitor C2 Positive Terminal. Connect a  $1\mu$ F capacitor between C2<sup>+</sup> and C2<sup>-</sup>.

**SGND (Pin 34):** Boost Switching Regulator Signal Ground. Tie PGND to SGND.

**FB (Pin 35):** Boost Switching Regulator Feedback Pin. Reference voltage is 1.255V. Connect resistive divider tap here. Minimize trace area at FB.

**SW (Pin 36):** Boost Switching Regulator Switch Pin. Connect inductor/diode here. Minimize trace area at this pin to reduce EMI.

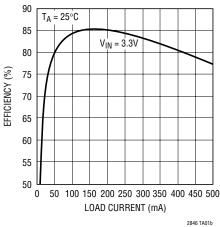

# **BLOCK DIAGRAM**

# **TEST CIRCUITS**

Figure 1. V.11 Driver DC Test Circuit

Figure 3. Input Impedance Test Circuit

Figure 5. V.35 Driver Open-Circuit Test

Figure 6. V.35 Driver Test Circuit

Figure 2. V.11 Driver AC Test Circuit

Figure 4. V.11, V.35 Receiver AC Test Circuit

Figure 7. V.35 Driver Common Mode Impedance Test Circuit

\$51.5Ω

125Ω

51.5Ω

. 2846 F10

Figure 10. Receiver Common Mode

Impedance Test Circuit

Figure 8. V.35 Driver AC Test Circuit

Figure 11. V.28 Driver Test Circuit

Figure 9. V.35 Receiver DC Test Circuit

Vcм

Figure 12. V.28 Receiver Test Circuit

# **MODE SELECTION**

Table 1

| Mode Name                  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |   | 3 | R1 R2<br>(Note 2) (Note 2) |         |         |      | R3<br>(Note 2) |      | R1<br>(Note 3) | R2,R3<br>(Note 3) | V <sub>DD</sub><br>(Note 4) | V <sub>EE</sub><br>(Note 5) |      |      |      |      |      |          |          |          |          |

|----------------------------|--------------------------------------------------------|---|---|----------------------------|---------|---------|------|----------------|------|----------------|-------------------|-----------------------------|-----------------------------|------|------|------|------|------|----------|----------|----------|----------|

|                            |                                                        |   |   |                            | (Note . | (Note . | Α    | В              | Α    | B              | A                 | В                           | A                           | B    | A    | B    | A    | B    | (NULE 3) | (NULE 3) | (NULE 4) | (NUCE D) |

| Not Used                   | 0                                                      | 0 | 0 | 0                          | TTL     | X       | V.11 | V.11           | V.11 | V.11           | z                 | z                           | V.11                        | V.11 | V.11 |      | V.11 | 1/11 | CMOS     | CMOS     | 9.3V     | GV       |

| (Default V.11)             | L.                                                     | 0 | 0 |                            |         |         |      |                |      |                |                   |                             |                             |      |      | V.11 |      | V.11 |          |          |          | -6V      |

| RS530A                     | 0                                                      | 0 | 1 | 0                          | TTL     | Х       | V.11 | V.11           | V.11 | V.11           | Z                 | Z                           | V.11                        | V.11 | V.11 | V.11 | V.11 | V.11 | CMOS     | CMOS     | 9.3V     | -6V      |

| RS530                      | 0                                                      | 1 | 0 | 0                          | TTL     | Х       | V.11 | V.11           | V.11 | V.11           | Z                 | Z                           | V.11                        | V.11 | V.11 | V.11 | V.11 | V.11 | CMOS     | CMOS     | 9.3V     | -6V      |

| X.21                       | 0                                                      | 1 | 1 | 0                          | TTL     | Х       | V.11 | V.11           | V.11 | V.11           | Z                 | Z                           | V.11                        | V.11 | V.11 | V.11 | V.11 | V.11 | CMOS     | CMOS     | 9.3V     | -6V      |

| V.35                       | 1                                                      | 0 | 0 | 0                          | TTL     | Х       | V.35 | V.35           | V.35 | V.35           | Z                 | Ζ                           | V.35                        | V.35 | V.35 | V.35 | V.35 | V.35 | CMOS     | CMOS     | 8V       | -6.5V    |

| RS449/V.36                 | 1                                                      | 0 | 1 | 0                          | TTL     | Х       | V.11 | V.11           | V.11 | V.11           | Ζ                 | Z                           | V.11                        | V.11 | V.11 | V.11 | V.11 | V.11 | CMOS     | CMOS     | 9.3V     | -6V      |

| V.28/RS232                 | 1                                                      | 1 | 0 | 0                          | TTL     | Х       | V.28 | Ζ              | V.28 | Z              | Ζ                 | Ζ                           | V.28                        | 30k  | V.28 | 30k  | V.28 | 30k  | CMOS     | CMOS     | 8.7V     | -8.5V    |

| No Cable                   | 1                                                      | 1 | 1 | 0                          | Х       | Х       | Z    | Ζ              | Z    | Z              | Ζ                 | Ζ                           | 30k                         | 30k  | 30k  | 30k  | 30k  | 30k  | Ζ        | Z        | 4.7V     | 0.3V     |

| Not Used<br>(Default V.11) | 0                                                      | 0 | 0 | 1                          | TTL     | TTL     | V.11 | V.11           | V.11 | V.11           | V.11              | V.11                        | 30k                         | 30k  | V.11 | V.11 | V.11 | V.11 | Z        | CMOS     | 9.3V     | -6V      |

| RS530A                     | 0                                                      | 0 | 1 | 1                          | TTL     | TTL     | V.11 | V.11           | V.11 | V.11           | V.11              | V.11                        | 30k                         | 30k  | V.11 | V.11 | V.11 | V.11 | Ζ        | CMOS     | 9.3V     | -6V      |

| RS530                      | 0                                                      | 1 | 0 | 1                          | TTL     | TTL     | V.11 | V.11           | V.11 | V.11           | V.11              | V.11                        | 30k                         | 30k  | V.11 | V.11 | V.11 | V.11 | Ζ        | CMOS     | 9.3V     | -6V      |

| X.21                       | 0                                                      | 1 | 1 | 1                          | TTL     | TTL     | V.11 | V.11           | V.11 | V.11           | V.11              | V.11                        | 30k                         | 30k  | V.11 | V.11 | V.11 | V.11 | Ζ        | CMOS     | 9.3V     | -6V      |

| V.35                       | 1                                                      | 0 | 0 | 1                          | TTL     | TTL     | V.35 | V.35           | V.35 | V.35           | V.35              | V.35                        | 30k                         | 30k  | V.35 | V.35 | V.35 | V.35 | Ζ        | CMOS     | 8V       | -6.5V    |

| RS449/V.36                 | 1                                                      | 0 | 1 | 1                          | TTL     | TTL     | V.11 | V.11           | V.11 | V.11           | V.11              | V.11                        | 30k                         | 30k  | V.11 | V.11 | V.11 | V.11 | Z        | CMOS     | 9.3V     | -6V      |

| V.28/RS232                 | 1                                                      | 1 | 0 | 1                          | TTL     | TTL     | V.28 | Ζ              | V.28 | Z              | V.28              | Z                           | 30k                         | 30k  | V.28 | 30k  | V.28 | 30k  | Z        | CMOS     | 8.7V     | -8.5V    |

| No Cable                   | 1                                                      | 1 | 1 | 1                          | Х       | Х       | Ζ    | Ζ              | Z    | Z              | Z                 | Ζ                           | 30k                         | 30k  | 30k  | 30k  | 30k  | 30k  | Ζ        | Z        | 4.7V     | 0.3V     |

Note 1: Driver inputs are TTL level compatible.

Note 2: Unused receiver inputs are terminated with 30k to ground. In addition, R2 and R3 are always terminated by a  $103\Omega$  differential impedence (see Block Diagram on page 8).

Note 3: Receiver Outputs are CMOS level compatible and have a weak pull up to  $V_{\text{IN}}$  when Z.

Note 4: V\_{DD} values shown are typical values for V\_{CC} = 5V, V\_{IN} = 3.3V and T\_A = 25°C with LTC2846 under full load for each mode.

Note 5:  $V_{EE}$  values shown are typical values for  $V_{CC}$  = 5V,  $V_{IN}$  = 3.3V and  $T_A$  = 25°C with LTC2846 under full load for each mode.

# SWITCHING TIME WAVEFORMS

Figure 13. V.11, V.35 Driver Propagation Delays

#### Figure 14. V.11, V.35 Receiver Propagation Delays

# SWITCHING TIME WAVEFORMS

# **APPLICATIONS INFORMATION**

#### Overview

The LTC2846 consists of a boost switching regulator, a charge pump and a 3-driver/3-receiver transceiver. The boost switching regulator generates a 5V V<sub>CC</sub> from the 3.3V input at V<sub>IN</sub> to power the charge pump and transceiver. The charge pump generates the V<sub>DD</sub> and V<sub>EE</sub> supplies. The LTC2846's V<sub>CC</sub>, V<sub>DD</sub> and V<sub>EE</sub> supplies can be used to power a companion chip like the LTC2844 or LTC2845. The receiver outputs are driven between 0V and V<sub>IN</sub> to interface with 3.3V logic.

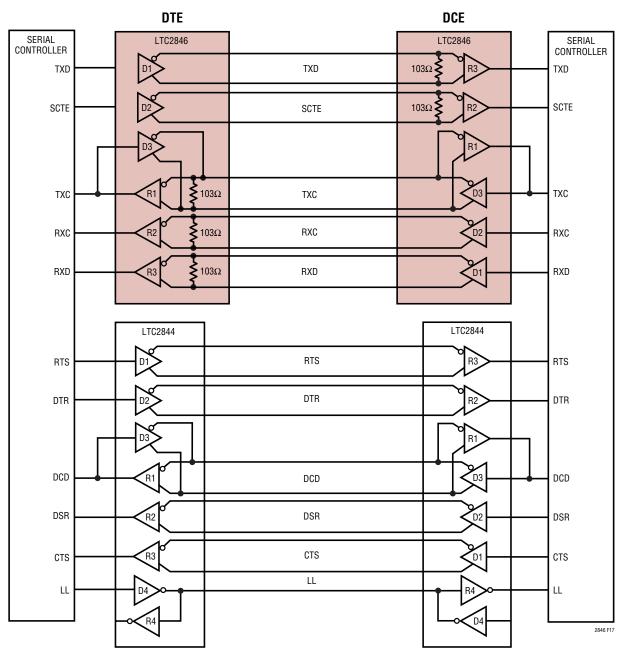

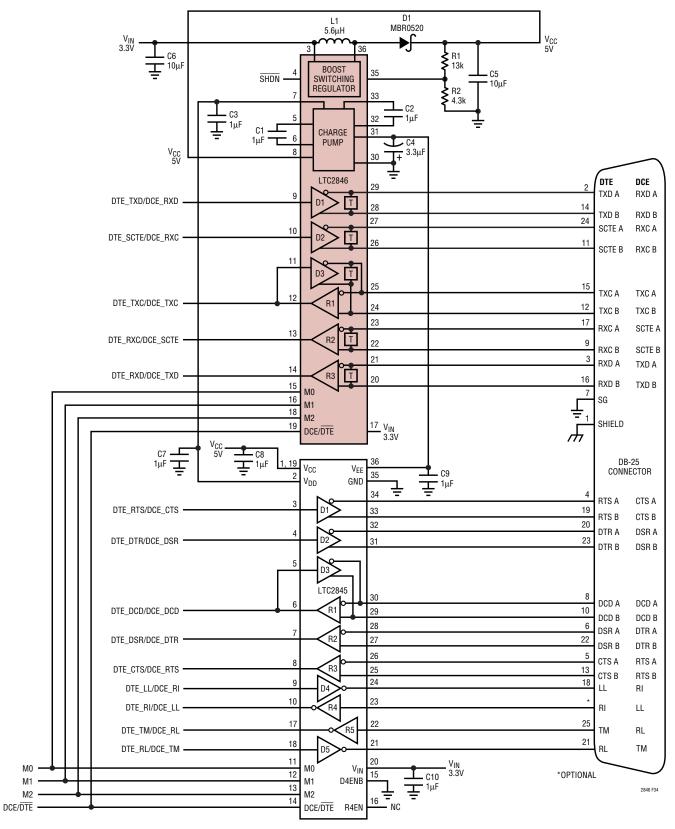

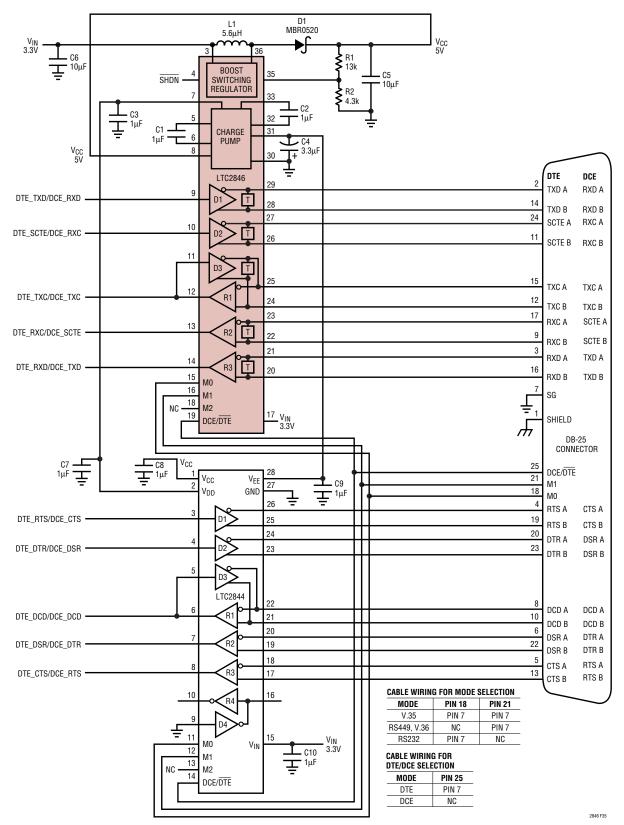

The LTC2846 and LTC2844 form a complete softwareselectable DTE or DCE interface port that supports the RS232, RS449, EIA530, EIA530-A, V.35, V.36 and X.21 protocols. Cable termination is provided on-chip, eliminating the need for discrete termination designs.

A complete DCE-to-DTE interface operating in EIA530 mode is shown in Figure 17. The LTC2846 half of each port is used to generate and appropriately terminate the clock and data signals. The LTC2844 is used to generate the control signals along with LL (Local Loopback).

#### **Mode Selection**

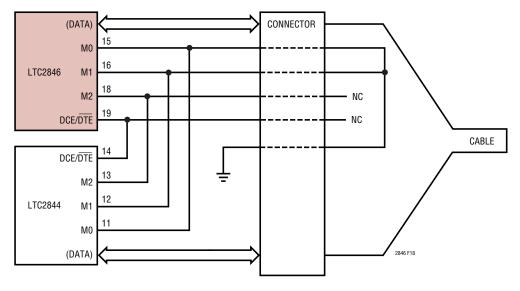

The interface protocol is selected using the mode select pins M0, M1 and M2 (see Table 1).

For example, if the port is configured as a V.35 interface, the mode selection pins should be M2 = 1, M1 = 0, M0 = 0. For the control signals, the drivers and receivers will operate in V.28 (RS232) electrical mode. For the clock and data signals, the drivers and receivers will operate in V.35 electrical mode. The DCE/DTE pin will configure the port for DCE mode when high, and DTE when low.

The interface protocol may be selected simply by plugging the appropriate interface cable into the connector. The mode pins are routed to the connector and are left unconnected (1) or wired to ground (0) in the cable as shown in Figure 18. The internal pull-up current sources will ensure a binary 1 when a pin is left unconnected.

The mode selection may also be accomplished by using jumpers to connect the mode pins to ground or  $V_{\mbox{IN}}$

When the cable is removed, leaving all mode pins unconnected, the LTC2846/LTC2844 will enter no-cable mode. In this mode the LTC2846/LTC2844 supply current drops to less than 900 $\mu$ A and the LTC2846/LTC2844 driver outputs are forced into a high impedance state. At the same time, the R2 and R3 receivers of the LTC2846 are differentially terminated with 103 $\Omega$  and the other receivers on

the LTC2846 and LTC2844 are terminated with 30k  $\!\Omega$  to ground.

#### **Cable Termination**

Traditional implementations used expensive relays to switch resistors or required the user to change termination modules every time a new interface standard was

Figure 18. Single Port DCE V.35 Mode Selection in the Cable

selected. Switching the terminations with FETs is difficult because the FETs must remain off when the signal voltage is beyond the supply voltage. Alternatively, custom cables may contain termination in the cable head or route signals to various terminations on the board.

The LTC2846/LTC2844 chip set solves the cable termination switching problem by automatically providing the appropriate termination and switching on-chip for the V.10 (RS423), V.11 (RS422), V.28 (RS232) and V.35 electrical protocols.

### V.10 (RS423) Interface

All V.10 drivers and receivers necessary for the RS449, EIA530, EIA530-A, V.36 and X.21 protocols are implemented on the LTC2844 or LTC2845.

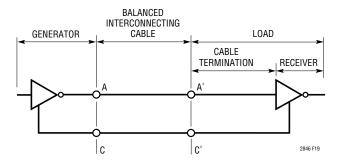

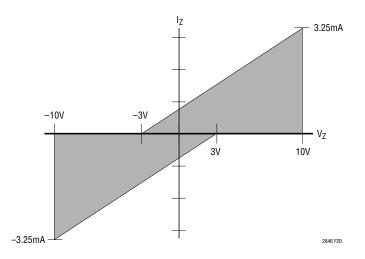

A typical V.10 unbalanced interface is shown in Figure 19. A V.10 single-ended generator with output A and ground C is connected to a differential receiver with input A' connected to A, and ground C' connected via the signal return to ground C. Usually, no cable termination is required for V.10 interfaces, but the receiver inputs must be compliant with the impedance curve shown in Figure 20.

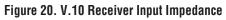

The V.10 receiver configuration in the LTC2844 and LTC2845 is shown in Figure 21. In V.10 mode, switch S3 inside the LTC2844 and LTC2845 is turned off. The noninverting input is disconnected inside the LTC2844

Figure 19. Typical V.10 Interface

Figure 21. V.10 Receiver Configuration

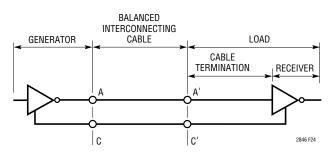

Figure 22. Typical V.11 Interface

and LTC2845 receivers and connected to ground. The cable termination is then the 30k input impedance to ground of the LTC2844 and LTC2845 V.10 receiver.

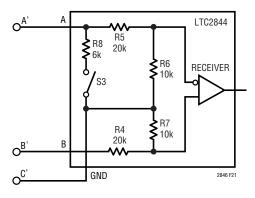

### V.11 (RS422) Interface

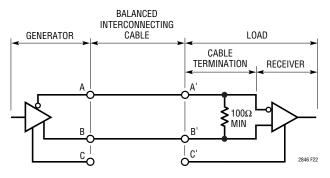

A typical V.11 balanced interface is shown in Figure 22. A V.11 differential generator with outputs A and B and ground C is connected to a differential receiver with input A' connected to A, input B' connected to B, and ground C' connected via the signal return to ground C. The V.11 interface has a differential termination at the receiver end that has a minimum value of  $100\Omega$ . The termination resistor is optional in the V.11 specification, but for the high speed clock and data lines, the termination is essential to prevent reflections from corrupting the data. The receiver inputs must also be compliant with the impedance curve shown in Figure 20.

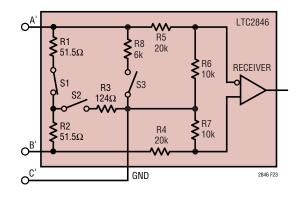

In V.11 mode, all switches are off except S1 of the LTC2846's receivers which connects a  $103\Omega$  differential

<sup>1</sup>Actually, there is no switch S1 in receivers R2 and R3. However, for simplicity, all termination networks on the LTC2846 can be treated identically if it is assumed that an S1 switch exists and is always closed on the R2 and R3 receivers.

Figure 23. V.11 Receiver Configuration

termination impedance to the cable as shown in Figure 23<sup>1</sup>. The LTC2844 and LTC2845 only handle control signals, so no termination other than their V.11 receivers' 30k input impedance is necessary.

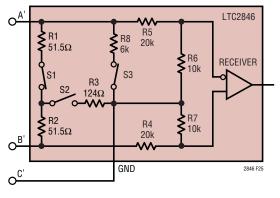

### V.28 (RS232) Interface

A typical V.28 unbalanced interface is shown in Figure 24. A V.28 single-ended generator with output A and ground C is connected to a single-ended receiver with input A' connected to A and ground C' connected via the signal return to ground C.

Figure 24. Typical V.28 Interface

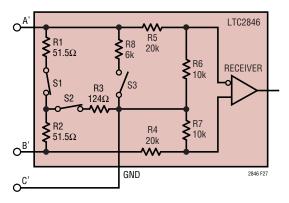

In V.28 mode, S3 is closed inside the LTC2846/LTC2844 which connects a 6k (R8) impedance to ground in parallel with 20k (R5) plus 10k (R6) for a combined impedance of 5k as shown in Figure 25. Proper termination is only provided when the B input of the receivers is floating, since S1 of the LTC2846's R2 and R3 receivers remains on in V.28 mode<sup>1</sup>. The noninverting input is disconnected inside the LTC2846/LTC2844 receiver and connected to a TTL level reference voltage to give a 1.4V receiver trip point.

#### V.35 Interface

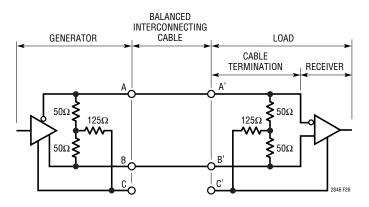

A typical V.35 balanced interface is shown in Figure 26. A V.35 differential generator with outputs A and B and ground C is connected to a differential receiver with input A' connected to A, input B' connected to B, and ground C' connected via the signal return to ground C. The V.35 interface requires a T or delta network termination at the receiver end and the generator end. The receiver differential impedance measured at the connector must be

Figure 26. Typical V.35 Interface

Figure 27. V.35 Receiver Configuration

$100\Omega \pm 10\Omega,$  and the impedance between shorted terminals (A' and B') and ground (C') must be  $150\Omega \pm 15\Omega.$

In V.35 mode, both switches S1 and S2 inside the LTC2846 are on, connecting a T network impedance as shown in Figure 27. The 30k input impedance of the receiver is placed in parallel with the T network termination, but does not affect the overall input impedance significantly.

The generator differential impedance must be  $50\Omega$  to  $150\Omega$  and the impedance between shorted terminals (A and B) and ground (C) must be  $150\Omega \pm 15\Omega$ .

#### **No-Cable Mode**

The no-cable mode (M0 = M1 = M2 = 1) is intended for the case when the cable is disconnected from the connector. The charge pump, bias circuitry, drivers and receivers are turned off, the driver outputs are forced into a high impedance state, and the V<sub>CC</sub> supply current to the transceiver drops to less than 300µA while its V<sub>IN</sub> supply current drops to less than 10µA. Note that the LTC2846's R2 and R3 receivers continue to be terminated by a 103 $\Omega$  differential impedance.

#### **Charge Pump**

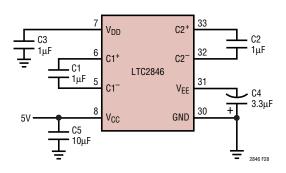

The LTC2846 uses an internal capacitive charge pump to generate  $V_{DD}$  and  $V_{EE}$  as shown in Figure 28. A voltage doubler generates about 8V on  $V_{DD}$  and a voltage inverter generates about -7.5V on  $V_{EE}$ . Three 1µF surface mounted tantalum or ceramic capacitors are required for C1, C2 and C3. The  $V_{EE}$  capacitor C4 should be a minimum of  $3.3\mu$ F. All capacitors are 16V and should be placed as close as possible to the LTC2846 to reduce EMI.

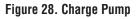

#### Switching Regulator

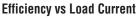

The circuit as shown in Figure 29 can provide up to 480mA at 5V to drive the LTC2846's transceiver as well as its companion chip in the DTE-DCE interface. In its shut down mode with the SHDN pin at 0V, the boost switching regulator draws less than  $10\mu$ A.

Ferrite core inductors should be used to obtain the best efficiency, as core losses at 1.2MHz are much lower for ferrite cores than for cheaper powdered-iron types. Choose an inductor that can handle at least 1A without saturating, and ensure that the inductor has a low DCR (copper wire resistance) to minimize  $I^2R$  power losses.

Use low ESR capacitors for the output to minimize output ripple voltage. Multilayer ceramic capacitors are an excellent choice, as they have extremely low ESR and are available in very small packages. Ceramic capacitors also make a good choice for the input decoupling capacitor, and should be placed as close as possible to the switching regulator. Solid tantalum or OS-CON capacitors can be used but they will occupy more board area than a ceramic and will have a higher ESR.

A Schottky diode is recommended for use with the switching regulator. The ON Semiconductor MBR0520 is a very good choice.

To set the output voltage, select the values of R1 and R2 according to the following equation.

R1 = R2[(5V/1.255V) - 1]

A good value for R2 is 4.3k which sets the current in the resistor divider chain to  $1.255V/4.3k = 292\mu A$ .

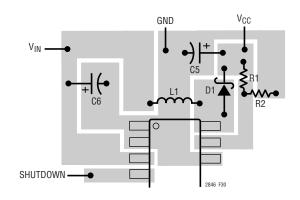

Figure 29. Boost Switching Regulator

The switching regulator has a switch current limit of 1A. This current limit protects the switch as well as the external components connected to the switching regulator.

The high speed operation of the boost switching regulator demands careful attention to board layout. Figure 30 shows the recommended component placement.

#### **Receiver Fail-Safe**

All LTC2846/LTC2844 receivers feature fail-safe operation in all modes. If the receiver inputs are left floating or are shorted together by a termination resistor, the receiver output will always be forced to a logic high.

#### **DTE vs DCE Operation**

The DCE/DTE pin acts as an enable for Driver 3/Receiver 1 in the LTC2846, and Driver 3/Receiver 1 and Receiver 4/ Driver 4 in the LTC2844.

The LTC2846/LTC2844 can be configured for either DTE or DCE operation in one of two ways: a dedicated DTE or DCE port with a connector of appropriate gender or a port with one connector that can be configured for DTE or DCE operation by rerouting the signals to the LTC2846/LTC2844 using a dedicated DTE cable or dedicated DCE cable.

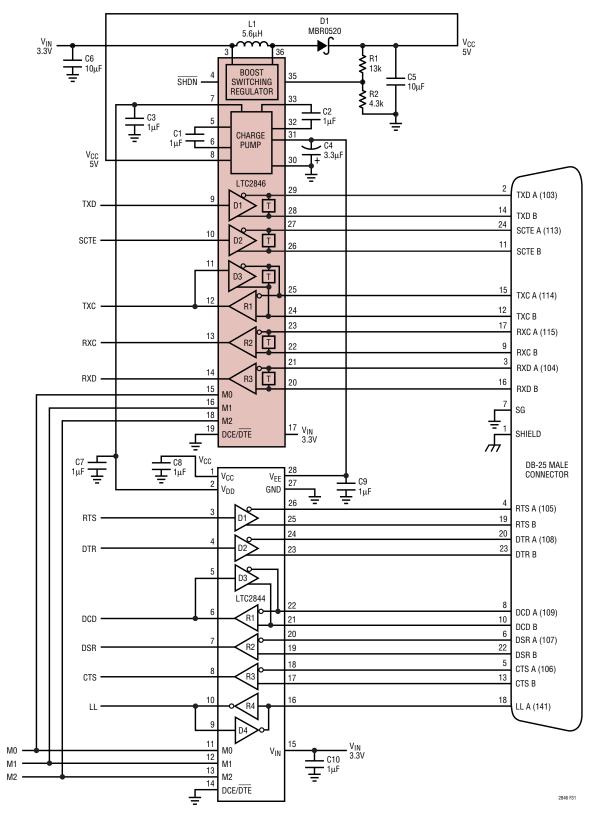

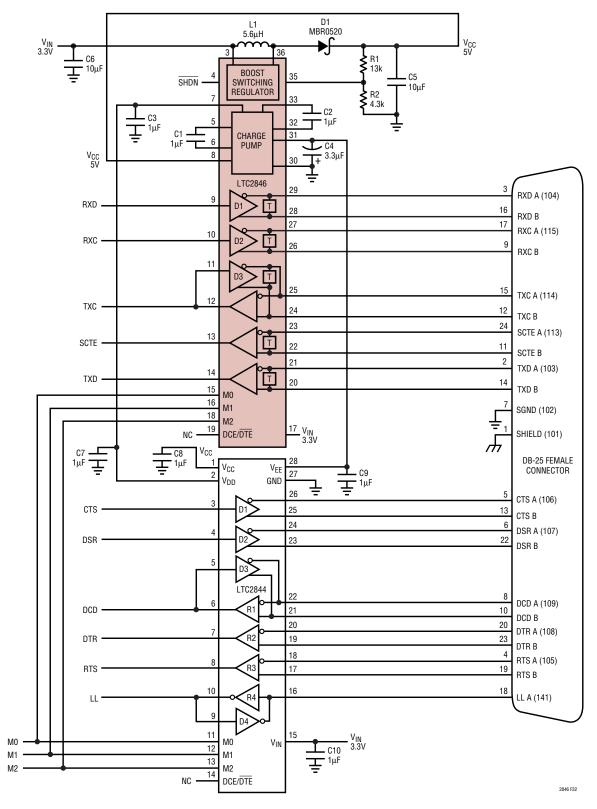

A dedicated DTE port using a DB-25 male connector is shown in Figure 31. The interface mode is selected by logic outputs from the controller or from jumpers to either  $V_{IN}$  or GND on the mode select pins. A dedicated DCE port using a DB-25 female connector is shown in Figure 32.

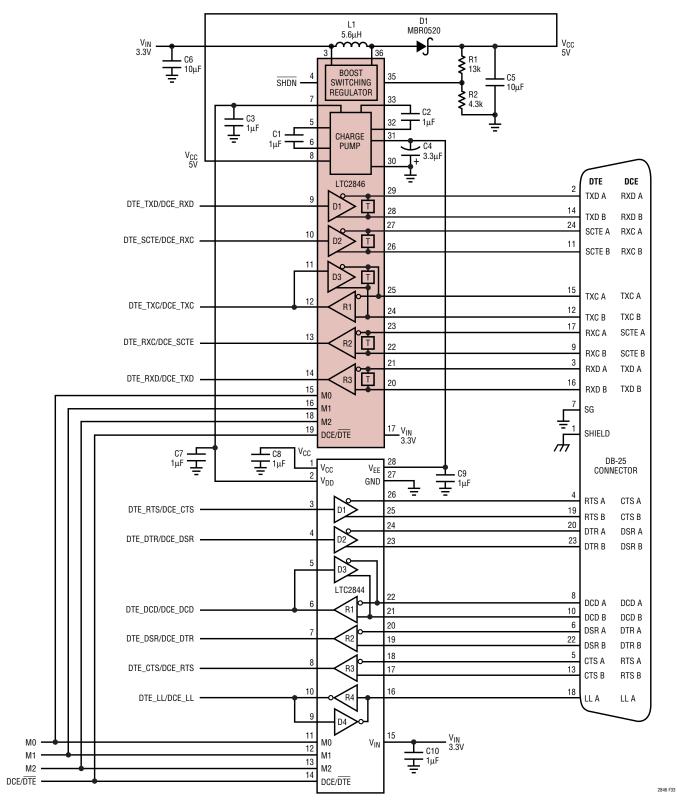

Figure 30. Suggested Layout

A port with one DB-25 connector, that can be configured for either DTE or DCE operation is shown in Figure 33. The configuration requires separate cables for proper signal routing in DTE or DCE operation. For example, in DTE mode, the TXD signal is routed to Pins 2 and 14 via the LTC2846's Driver 1. In DCE mode, Driver 1 now routes the RXD signal to Pins 2 and 14.

#### Multiprotocol Interface with RL, LL, TM and a DB-25 Connector

If the RL, LL and TM signals are implemented, there are not enough drivers and receivers available in the LTC2846/ LTC2844. In Figure 34, the required control signals are handled by the LTC2845. The LTC2845 has an additional single-ended driver/receiver pair that can handle two more optional control signals such as TM and RL.

#### Cable-Selectable Multiprotocol Interface

A cable-selectable multiprotocol DTE/DCE interface is shown in Figure 35. The select lines M0, M1 and DCE/DTE are brought out to the connector. The mode is selected by the cable by wiring M0 (connector Pin 18) and M1 (connector Pin 21) and DCE/DTE (connector Pin 25) to ground (connector Pin 7) or letting them float. If M0, M1 or DCE/DTE is floating, internal pull-up current sources will pull the signals to  $V_{IN}$ . The select bit M2 is floating, and therefore, internally pulled high. When the cable is pulled out, the interface will go into the no-cable mode.

### Power Dissipation Calculations

The LTC2846 takes in a 3.3V supply and produces a 5V  $V_{CC}$ with an internal switcher at approximately 80% efficiency.  $V_{DD}$  and  $V_{FF}$  are in turn produced from  $V_{CC}$  with an internal charge pump at approximately 80% and 70% efficiency respectively. Current drawn internally from  $V_{DD}$  or  $V_{EE}$ translates directly into a higher I<sub>CC</sub>. The LTC2846 dissipates power according to the equation:

$$P_{\text{DISS}(2846)} = 125\% \bullet (V_{\text{CC}} \bullet I_{\text{CC}}) - N_{\text{D}} \bullet P_{\text{RT}} + N_{\text{R}} \bullet P_{\text{RT}}$$

(1)

P<sub>BT</sub> refers to the power dissipated by each driver in a receiver termination on the far end of the cable while  $N_D$  is the number of drivers. Conversely, current from the far end drivers dissipate power N<sub>B</sub> • P<sub>BT</sub> in the internal receiver termination where N<sub>B</sub> is the number of receivers.

### LTC2846 Power Dissipation

Consider an LTC2846 in X.21, DCE mode (three V.11 drivers and two V.11 receivers). From the Electrical Characteristics Table,  $I_{CC}$  at no load = 14mA,  $I_{CC}$  at full load = 100mA. Each receiver termination is  $100\Omega$  (R<sub>BT</sub>) and current going into each receiver termination = (100mA - $14mA)/3 = 28.7mA (I_{BT}).$

$$P_{\rm RT} = (I_{\rm RT})^2 \bullet R_{\rm RT} \tag{2}$$

From Equation (2),  $P_{RT} = 82.4$  mW and from Equation (1), DC power dissipation P<sub>DISS(2846)</sub> = 125% • (5V • 100mA)  $-3 \cdot 82.4$ mW  $+ 2 \cdot 82.4$ mW = 543mW.

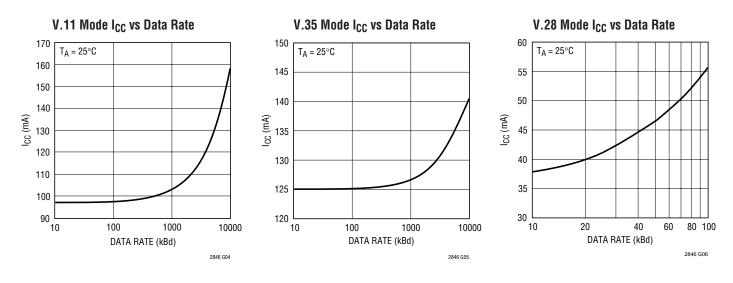

Consider the above example running at a baud rate of 10MBd. From the Typical Characteristic for "V.11 Mode Icc vs Data Rate," the Icc at 10MBd is 160mA. Icc increases with baud rate due to driver transient dissipation. From Equation (1), AC power dissipation P<sub>DISS(2846)</sub> = 125% • (5V • 160mA) -3 • 82.4mW + 2 • 82.4mW = 918mW.

### LTC2845 Power Dissipation

If a LTC2845 is used to form a complete DCE port with the LTC2846, it will be running in the X.21 mode (three V.11 drivers and two V.10 drivers, two V.11 receivers and two V.10 receivers, all with internal 30k termination). In addition to  $V_{CC}$ , it uses the  $V_{DD}$  and  $V_{EE}$  outputs from the LTC2846. Negligible power is dissipated in the large internal receiver termination of the LTC2845 so the N<sub>B</sub> •  $P_{BT}$  term of Equation (1) can be omitted. Thus Equation (1) is modified as follows:

$P_{DISS(2845)} = (V_{CC} \bullet I_{CC}) + (V_{DD} \bullet I_{DD})$

+

$$(V_{EE} \bullet I_{EE}) - N_D \bullet P_{RT}$$

(3)

Since power is drawn from the supplies of the LTC2846 (V<sub>CC</sub>, V<sub>DD</sub> and V<sub>EE</sub>) at less than 100% efficiency, the LTC2846 dissipates extra power to source  $P_{DISS(2845)}$  and  $P_{RT}$ :

$$\begin{split} \mathsf{P}_{\mathsf{DISS1}(2846)} &= 125\% \bullet (\mathsf{V}_{\mathsf{CC}} \bullet \mathsf{I}_{\mathsf{CC}}) + 125\% \bullet 125\% \\ &\bullet (\mathsf{V}_{\mathsf{DD}} \bullet \mathsf{I}_{\mathsf{DD}}) + 125\% \bullet 143\% \bullet (\mathsf{V}_{\mathsf{EE}} \bullet \mathsf{I}_{\mathsf{EE}}) \\ &- \mathsf{P}_{\mathsf{DISS}(2845)} - \mathsf{N}_{\mathsf{D}} \bullet \mathsf{P}_{\mathsf{RT}} \\ &= 25\% \bullet (\mathsf{V}_{\mathsf{CC}} \bullet \mathsf{I}_{\mathsf{CC}}) + 56\% \bullet (\mathsf{V}_{\mathsf{DD}} \bullet \mathsf{I}_{\mathsf{DD}}) \\ &+ 79\% \bullet (\mathsf{V}_{\mathsf{EE}} \bullet \mathsf{I}_{\mathsf{EE}}) \end{split}$$

From the LTC2845 Electrical Characteristics Table, for  $V_{CC} = 5V$ ,  $V_{DD} = 8V$  and  $V_{EE} = -5.5V$ :

| I <sub>CC</sub> at no load                              | 2.7mA |

|---------------------------------------------------------|-------|

| $I_{CC}$ at full load with all drivers high             | 110mA |

| I <sub>EE</sub> at no load                              | 2mA   |

| I <sub>EE</sub> at full load with both V.10 drivers low | 23mA  |

| I <sub>DD</sub> at no load                              | 0.3mA |

| I <sub>DD</sub> at full load                            | 0.3mA |

The V.11 drivers are driven between V<sub>CC</sub> and GND while the V.10 drivers are driven between V<sub>CC</sub> and V<sub>EE</sub>. Assume that the V.11 driver outputs are high and V.10 driver outputs low. Current going into each  $100\Omega$  V.11 receiver termination = (110mA - 2.7mA) - 23mA/3 = 28.1mA. Current going into each  $450\Omega$  V.10 receiver termination = 23mA - 2mA/2 = 10.5mA. From Equation (2), V.11 P<sub>RT</sub> = 79mW and V.10  $P_{RT}$  = 49.6mW.

From Equation (3),  $P_{DISS(2845)} = 5V \cdot (110mA - 23mA) + (8V \cdot 0.3mA) + 5.5V \cdot 23mA - 3 \cdot 79mW - 2 \cdot 49.6mW = 228mW$ . Since the LTC2845 runs slow control signals, the AC power dissipation can be assumed to be equal to the DC power dissipation.

The extra power dissipated in the LTC2846 due to LTC2845 is given by Equation(4),  $P_{DISS1(2846)} = 25\% \cdot (5V \cdot 87mA) + 56\% \cdot (8V \cdot 0.3mA) + 79\% \cdot (5.5V \cdot 23mA) = 210mW$ . So for an X.21 DCE port running at 10MBd, the LTC2846 dissipates approximately 918mW + 210mW = 1128mW while the LTC2845 dissipates 228mW.

#### **Compliance Testing**

The LTC2846/LTC2844 and LTC2846/LTC2845 chipsets have been tested by TUV Rheinland of North America Inc. and passed the NET1, NET2 and TBR2 requirements. Copies of the test reports are available from LTC or TUV Rheinland of North America Inc.

The title of the reports are Test Report No.: TBR2/051501/02 and TBR2/050101/02

The address of TUV Rheinland of North America Inc. is:

TUV Rheinland of North America Inc. 1775, Old Highway 8 NW, Suite 107 St. Paul, MN 55112 Tel. (651) 639-0775 Fax (651) 639-0873

Figure 31. Controller-Selectable Multiprotocol DTE Port with DB-25 Connector

19

Figure 32. Controller-Selectable DCE Port with DB-25 Connector

Figure 33. Controller-Selectable Multiprotocol DTE/DCE Port with DB-25 Connector

Figure 34. Controller-Selectable Multiprotocol DTE/DCE Port with RL, LL, TM and DB-25 Connector

Figure 35. Cable-Selectable Multiprotocol DTE/DCE Port with DB-25 Connector

Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

# PACKAGE DESCRIPTION

\*\*DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED .254mm (.010") PER SIDE

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                        | COMMENTS                                                                                                 |

|-------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| LTC1321     | Dual RS232/RS485 Transceiver                       | Two RS232 Driver/Receiver Pairs or Two RS485 Driver/Receiver Pairs                                       |

| LTC1334     | Single 5V RS232/RS485 Multiprotocol Transceiver    | Two RS232 Driver/Receiver or Four RS232 Driver/Receiver Pairs                                            |

| LTC1343     | Software-Selectable Multiprotocol Transceiver      | 4-Driver/4-Receiver for Data and Clock Signals                                                           |

| LTC1344A    | Software-Selectable Cable Terminator               | Perfect for Terminating the LTC1543 (Not Needed with LTC1546)                                            |

| LTC1345     | Single Supply V.35 Transceiver                     | 3-Driver/3-Receiver for Data and Clock Signals                                                           |

| LTC1346A    | Dual Supply V.35 Transceiver                       | 3-Driver/3-Receiver for Data and Clock Signals                                                           |

| LTC1543     | Software-Selectable Multiprotocol Transceiver      | Terminated with LTC1344A for Data and Clock Signals, Companion to LTC1544 or LTC1545 for Control Signals |

| LTC1544     | Software-Selectable Multiprotocol Transceiver      | Companion to LTC1546 or LTC1543 for Control Signals Including LL                                         |

| LTC1545     | Software-Selectable Multiprotocol Transceiver      | 5-Driver/5-Receiver Companion to LTC1546 or LTC1543<br>for Control Signals Including LL, TM and RL       |

| LTC1546     | Software-Selectable Multiprotocol Transceiver      | 3-Driver/3-Receiver with Termination for Data and Clock Signals                                          |

| LTC2844     | 3.3V Software-Selectable Multiprotocol Transceiver | Companion to LTC2846 for Control Signals Including LL                                                    |

| LTC2845     | 3.3V Software-Selectable Multiprotocol Transceiver | 5-Driver/5-Receiver Companion to LTC2846 for Control Signals<br>Including LL, TM and RL                  |

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for RS-232 Interface IC category:

Click to view products by Analog Devices manufacturer:

Other Similar products are found below :

062191EB 713266CB MAX3250EAIT MAX13223EEUP+T SP508EEF-L MAX3218EAP+T MAX561CAI+T MAX3218CAP+T MAX218EAP+T MAX3232ECUP+G071 MAX3228AEEWV+T LT1180AISW#TRPBF MAX3386ECPWR TRSF3223ECPWR ADM202EARWZ-REEL ICL3232IVZ-T7A ICL3232IBZ-T ICL3222EIBZ-T 5962-7802004MEA 5962-89877012C AZ75232GTR-G1 AZ75232GSTR-G1 TRS222IDWR TRS3223ECDWR MAX563CPN+ MAX491EESD+ MAX489ESD+ MAX489CPD+ MAX491ECSD+ MAX487EESA+ MAX3389ECUG MAX3318EEAP MAX3244EEUI+ MAX3232ECUE+ MAX3225EETP+ MAX3223EAPT MAX3222ECUP+T MAX3221EUE+T MAX3221EUE+ MAX3190EEUTT MAX251CSD+T MAX248CQH+D MAX3245CWI+ MAX3241CUI+T MAX221EEUE+ MAX3232EEWET MAX3232EEUET MAX3232ECPE+ MAX3232CPW MAX3225EAAP+