# **Dual SPDT CMOS Analog Switch**

### HI-5051/883

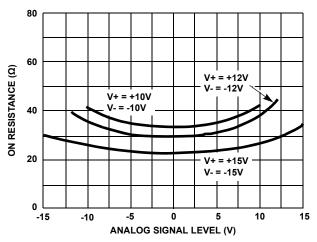

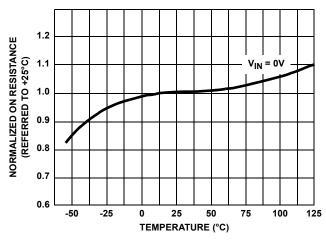

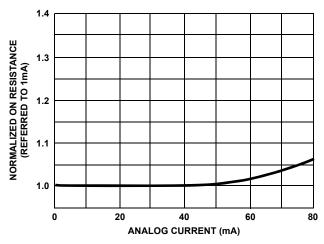

This CMOS analog switch offers low resistance switching performance for analog voltages up to the supply rails and for signal currents up to 70mA. "ON" resistance is low and stays reasonably constant over the full range of operating signal voltage and current.  $R_{ON}$  remains exceptionally constant for input voltages between +5V and -5V and currents up to 50mA. Switch impedance also changes very little over temperature, particularly between 0 °C and +75 °C.  $R_{ON}$  is nominally  $25\Omega_{\odot}$

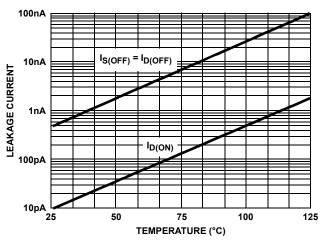

The HI-5051/883 provides break-before-make switching and is TTL and CMOS compatible for maximum application versatility. Performance is further enhanced by Dielectric Isolation processing which insures latch-free operation with very low input and output leakage currents (0.8nA at  $\pm 25\,^{\circ}$ C). The HI-5051/883 switch also features very low power operation (1.5mW at  $\pm 25\,^{\circ}$ C). The HI-5051/883 is available in a 20 Ld CLCC package and operates over the  $\pm 55\,^{\circ}$ C to  $\pm 125\,^{\circ}$ C temperature range.

### **Features**

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- High Current Capability . . . . . . . . . . . . . 70mA (Max)

- · Break-Before-Make Switching

- No Latch-Up

- Input MOS Gates are Protected from Electrostatic Discharge

- DTL, TTL, CMOS, PMOS Compatible

## **Applications**

- · High Frequency Switching

- · Sample and Hold

- · Digital Filters

- · Operational Amplifier Gain Switching

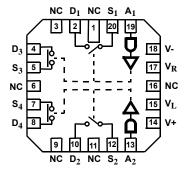

# **Pin Configuration**

HI-5051/883 20 LD CLCC TOP VIEW LOGIC "0" INPUT

NOTE: Unused pins may be internally connected. Ground all unused pins.

# **Ordering Information**

| PART<br>NUMBER | PART<br>MARKING | TEMP. RANGE<br>(°C) | PACKAGE    | PKG.<br>DWG.<br># |   |

|----------------|-----------------|---------------------|------------|-------------------|---|

| HI4-5051/883   | HI4-5051 883    | -55 to +125         | 20 Ld CLCC | J20.A             | Ì |

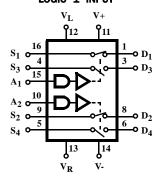

# **Functional Diagram**

LOGIC "1" INPUT

NOTE: Source and Drain are arbitrarily depicted as Analog Input and Output, respectively. They may be interchanged without affecting performance.

### **Absolute Maximum Ratings**

| Voltage Between V+ and V- Terminals                                                                          |

|--------------------------------------------------------------------------------------------------------------|

| $\pm V_{SUPPLY}$ to Ground (V+, V-) $\pm 18V$                                                                |

| V <sub>R</sub> to GroundV <sub>SUPPLY</sub>                                                                  |

| V <sub>L</sub> to Ground +V <sub>SUPPLY</sub>                                                                |

| Digital and Analog Input Voltage (V <sub>A</sub> , V <sub>S</sub> , V <sub>D</sub> )+V <sub>SUPPLY</sub> +4V |

| -V <sub>SUPPLY</sub> -4V                                                                                     |

| Peak Current (Source to Drain)                                                                               |

| (Pulse at 1ms, 10% Duty Cycle Max)                                                                           |

| Continuous Current (Any Pin)                                                                                 |

| ESD Rating<2000V                                                                                             |

### **Thermal Information**

| Thermal Resistance                          | $\theta_{JA}$ (°C/W) | $\theta_{JC}(^{\circ}C/W)$ |

|---------------------------------------------|----------------------|----------------------------|

| CLCC Package                                | 80                   | 20                         |

| Package Power Dissipation at +75°C          |                      |                            |

| CLCC Package                                |                      | 1.0W                       |

| Package Power Dissipation Derating Factor a | above +75°C          |                            |

| CLCC Package                                |                      | 12.5mW/°C                  |

| Junction Temperature                        |                      | +175°C                     |

| Storage Temperature Range                   | 6                    | 5°C to +150°C              |

| Lead Temperature (Soldering 10s)            |                      | +300°C                     |

### **Recommended Operating Conditions**

| Operating Temperature Range               | 55°C to +125°C       |

|-------------------------------------------|----------------------|

| Operating Supply Voltage                  | ±15V                 |

| Logic Supply Voltage (V <sub>L</sub> )    | +5.0V                |

| Logic Reference Voltage (V <sub>R</sub> ) |                      |

| Analog Input Voltage (V <sub>S</sub> )    | ±V <sub>SUPPLY</sub> |

| Address Low Level (V <sub>AL</sub> )      | 0V to 0.8V           |

| Address High Level (V <sub>AH</sub> )     | 2.4V to +5.0V        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

### TABLE 1. D.C. ELECTRICAL PERFORMANCE SPECIFICATIONS

Device Tested at: Supply Voltage =  $\pm$ 15V, V<sub>L</sub> = +5.0V, V<sub>R</sub> = 0.0V, V<sub>AH</sub> = 2.4V, V<sub>AL</sub> = +0.8V, unused pins are grounded, unless otherwise specified.

| D.C. PARAMETERS            | SYMBOL              | CONDITIONS                                                                                 | GROUP A<br>SUBGROUPS | TEMPERATURE (°C) | MIN  | MAX | UNITS |

|----------------------------|---------------------|--------------------------------------------------------------------------------------------|----------------------|------------------|------|-----|-------|

| Switch "ON" Resistance     | R <sub>DS2</sub>    | $V_D = -10V$ , $I_S = 10$ mA<br>S1/S2/S3/S4<br>$V_D = 10V$ , $I_S = -10$ mA<br>S1/S2/S3/S4 | 1                    | +25              | -    | 45  | Ω     |

|                            |                     |                                                                                            | 2, 3                 | -55 to +125      | -    | 50  | Ω     |

|                            |                     |                                                                                            | 1                    | +25              | -    | 45  | Ω     |

|                            |                     |                                                                                            | 2, 3                 | -55 to +125      | -    | 50  | Ω     |

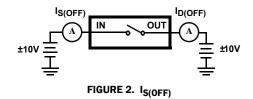

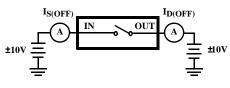

| Source "OFF"               | I <sub>S(OFF)</sub> | $V_S = -10V, V_D = 10V$                                                                    | 1                    | +25              | -1   | 1   | nA    |

| Leakage Current            |                     | S1/S2/S3/S4                                                                                | 2, 3                 | -55 to +125      | -100 | 100 | nA    |

|                            |                     | V <sub>S</sub> = 10V, V <sub>D</sub> = -10V<br>S1/S2/S3/S4                                 | 1                    | +25              | -1   | 1   | nA    |

|                            |                     |                                                                                            | 2, 3                 | -55 to +125      | -100 | 100 | nA    |

| Drain "OFF"                | I <sub>D(OFF)</sub> | V <sub>D</sub> = -10V, V <sub>S</sub> = 10V<br>S1/S2/S3/S4                                 | 1                    | +25              | -1   | 1   | nA    |

| Leakage Current            |                     |                                                                                            | 2, 3                 | -55 to +125      | -100 | 100 | nA    |

|                            |                     | V <sub>D</sub> = 10V, V <sub>S</sub> = -10V<br>S1/S2/S3/S4                                 | 1                    | +25              | -1   | 1   | nA    |

|                            |                     |                                                                                            | 2, 3                 | -55 to +125      | -100 | 100 | nA    |

| Channel "ON"               | I <sub>D(ON)</sub>  | $V_D = V_S = 10V$<br>S1/S2/S3/S4<br>$V_D = V_S = -10V$<br>S1/S2/S3/S4                      | 1                    | +25              | -2   | 2   | nA    |

| Leakage Current            |                     |                                                                                            | 2, 3                 | -55 to +125      | -200 | 200 | nA    |

|                            |                     |                                                                                            | 1                    | +25              | -2   | 2   | nA    |

|                            |                     |                                                                                            | 2, 3                 | -55 to +125      | -200 | 200 | nA    |

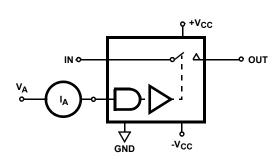

| Low Level Address Current  | I <sub>AL</sub>     | V <sub>A</sub> = 0V<br>A <sub>1</sub> , A <sub>2</sub>                                     | 1                    | +25              | -1   | 1   | μA    |

|                            |                     |                                                                                            | 2, 3                 | -55 to +125      | -10  | 1   | μΑ    |

| High Level Address Current | I <sub>AH</sub>     | V <sub>A</sub> = 2.4V, 5V                                                                  | 1                    | +25              | -1   | 1   | μΑ    |

|                            |                     | A <sub>1</sub> , A <sub>2</sub>                                                            | 2, 3                 | -55 to +125      | -1   | 10  | μΑ    |

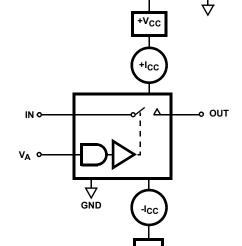

| Positive Supply Current    | +I <sub>CC</sub>    | V <sub>A</sub> = 0V, 5V                                                                    | 1                    | +25              | -    | 200 | μA    |

|                            |                     | A <sub>1</sub> , A <sub>2</sub>                                                            | 2, 3                 | -55 to +125      | -    | 300 | μΑ    |

| Negative Supply Current    | -lcc                | V <sub>A</sub> = 0V, 5V                                                                    | 1                    | +25              | -200 | -   | μA    |

|                            |                     | A <sub>1</sub> , A <sub>2</sub>                                                            | 2, 3                 | -55 to +125      | -300 | -   | μA    |

## HI-5051/883

#### TABLE 1. D.C. ELECTRICAL PERFORMANCE SPECIFICATIONS (Continued)

Device Tested at: Supply Voltage =  $\pm$ 15V, V<sub>L</sub> = +5.0V, V<sub>R</sub> = 0.0V, V<sub>AH</sub> = 2.4V, V<sub>AL</sub> = +0.8V, unused pins are grounded, unless otherwise specified.

| D.C. PARAMETERS          | SYMBOL          | CONDITIONS              | GROUP A<br>SUBGROUPS | TEMPERATURE<br>(°C) | MIN  | MAX | UNITS |

|--------------------------|-----------------|-------------------------|----------------------|---------------------|------|-----|-------|

| Logic Supply Current     | +IL             | V <sub>A</sub> = 0V, 5V | 1                    | +25                 | -    | 200 | μΑ    |

|                          |                 |                         | 2, 3                 | -55 to +125         | -    | 300 | μΑ    |

| Reference Supply Current | +I <sub>R</sub> | V <sub>A</sub> = 0V, 5V | 1                    | +25                 | -200 | -   | μΑ    |

|                          |                 |                         | 2, 3                 | -55 to +125         | -300 | -   | μΑ    |

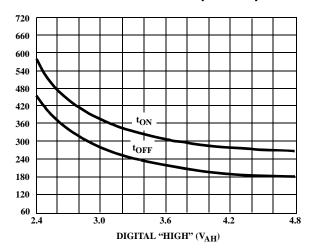

#### **TABLE 2. A.C. ELECTRICAL PERFORMANCE SPECIFICATIONS**

Device Tested at: Supply Voltage =  $\pm$ 15V,  $V_L = +5.0V$ ,  $V_R = 0.0V$ ,  $V_{AH} = +5.0V$ ,  $V_{AL} = +0.0V$ , unused pins are grounded, unless otherwise specified.

| PARAMETERS      | SYMBOL                      | CONDITIONS                                             | GROUP A<br>SUBGROUPS | TEMPERATURE<br>(°C) | MIN | MAX | UNITS |

|-----------------|-----------------------------|--------------------------------------------------------|----------------------|---------------------|-----|-----|-------|

| Turn "ON" Time  | n "ON" Time t <sub>ON</sub> | $V_S = 10V$ , -10V<br>$C_L = 10pF$<br>$R_L = 1k\Omega$ | 11                   | -55                 | -   | 450 | ns    |

|                 |                             |                                                        | 9                    | +25                 | -   | 500 | ns    |

|                 |                             |                                                        | 10                   | +125                | -   | 800 | ns    |

| Turn "OFF" Time | t <sub>OFF</sub>            | V <sub>S</sub> = 10V, -10V                             | 11                   | -55                 | -   | 350 | ns    |

|                 |                             | $C_L = 10pF$<br>$R_L = 1k\Omega$                       | 9                    | +25                 | -   | 450 | ns    |

|                 | ""                          | 112                                                    | 10                   | +125                | -   | 600 | ns    |

#### **TABLE 3. ELECTRICAL PERFORMANCE SPECIFICATIONS (NOTE 1)**

Device Characterized at: Supply Voltage =  $\pm 15$ V,  $V_L = +5.0$ V,  $V_R = 0.0$ V,  $V_{AH} = 4.0$ V,  $V_{AL} = 0.8$ V, unused pins are grounded, unless otherwise specified.

| PARAMETERS                                    | SYMBOL                 | CONDITIONS                                                                              | NOTE | TEMPERATURE (°C) | MIN | MAX | UNITS |

|-----------------------------------------------|------------------------|-----------------------------------------------------------------------------------------|------|------------------|-----|-----|-------|

| "ON" Resistance Match<br>(Channel to Channel) | R <sub>ON2</sub> Match | V <sub>D</sub> = ±10V<br>I <sub>D</sub> = 10mA                                          | 1    | +25              | -   | 10  | Ω     |

| Address Capacitance                           | C <sub>A</sub>         | V <sub>A</sub> = 0V, 5V                                                                 | 1    | +25              | -   | 45  | pF    |

| Switch Input Capacitance                      | C <sub>S(OFF)</sub>    | Switch Off: V <sub>A</sub> = 0V                                                         | 1    | +25              | -   | 60  | pF    |

| Switch Output Capacitance                     | C <sub>D(OFF)</sub>    | Switch Off: V <sub>A</sub> = 0V                                                         | 1    | +25              | -   | 60  | pF    |

|                                               | C <sub>D(ON)</sub>     | Switch On: V <sub>A</sub> = 5V                                                          | 1    | +25              | -   | 60  | pF    |

| Drain to Source Capacitance                   | C <sub>DS(OFF)</sub>   | Switch Off: V <sub>A</sub> = 0V                                                         | 1    | +25              | -   | 10  | pF    |

| Off Isolation                                 | V <sub>ISO</sub>       | $V_S = 2V_{P-P} @ f = 100kHz,$<br>$R_L = 100\Omega$                                     | 1    | +25              | -   | 60  | dB    |

| Crosstalk                                     | V <sub>CT</sub>        | $V_S = 2V_{P-P} @ f = 100kHz,$<br>$R_L = 100\Omega$                                     | 1    | +25              | -   | 60  | dB    |

| Charge Transfer Error                         | V <sub>CTE</sub>       | V <sub>S</sub> = GND, C <sub>L</sub> = 0.01μF<br>V <sub>A</sub> = 0V to 4V @ f = 200kHz | 1    | +25              | -   | 30  | mV    |

#### NOTE:

1. Parameters listed in Table 3 are controlled via design or process parameters and are not directly tested at final production. These parameters are lab characterized upon initial design release, or upon design changes. These parameters are guaranteed by characterization based upon data from multiple production runs which reflect lot to lot and within lot variation.

### **TABLE 4. ELECTRICAL TEST REQUIREMENTS**

| MIL-STD-883 TEST REQUIREMENTS               | SUBGROUPS (See Tables 1 and 2) |

|---------------------------------------------|--------------------------------|

| Interim Electrical Parameters (Pre Burn-in) | 1                              |

| Final Electrical Test Parameters            | 1 (Note 2), 2, 3, 9, 10, 11    |

| Group A Test Requirements                   | 1, 2, 3, 9, 10, 11             |

| Groups C & D Endpoints                      | 1                              |

#### NOTE:

2. PDA applies to Subgroup 1 only.

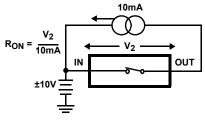

# **Test Circuits**

FIGURE 1.  $R_{DS}$

$I_{D(ON)} \\$ ±10V

FIGURE 3. I<sub>D(OFF)</sub>

FIGURE 4. I<sub>D(ON)</sub>

FIGURE 6. SUPPLY CURRENTS

FIGURE 5. ADDRESS CURRENT

## Test Circuits (Continued)

NOTE: Applies only to dual or double throw switches.

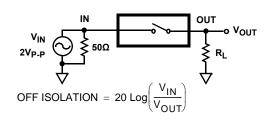

FIGURE 7. OFF ISOLATION

FIGURE 8. CROSSTALK

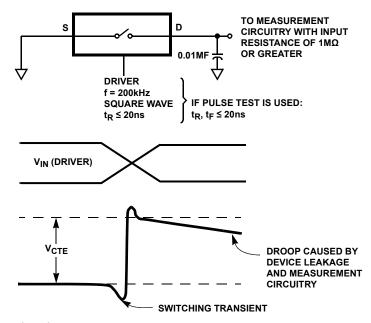

NOTE:  $V_{\mbox{CTE}}$  may be a positive or negative value.

FIGURE 9. CHARGE TRANSFER

# **Test Characteristics**

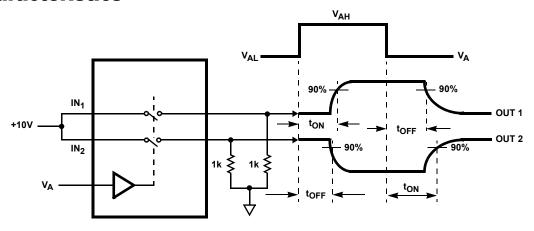

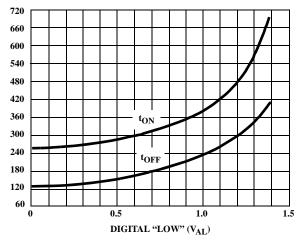

FIGURE 10. ON/OFF SWITCH TIME  $(t_{\mbox{ON}},t_{\mbox{OFF}})$

# Test Characteristics (Continued)

FIGURE 11. SWITCHING TIMES FOR DIGITAL TRANSITION

FIGURE 12. SWITCHING TIMES FOR NEGATIVE DIGITAL TRANSITION

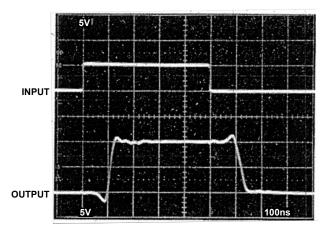

### **Test Waveforms**

Vertical Scale: Input = 5V/Div, (TTL;  $V_{AH} = 5V$ ,  $V_{AL} = 0V$ ) Output = 5V/Div

Horizontal Scale: 100ns/Div

FIGURE 13.

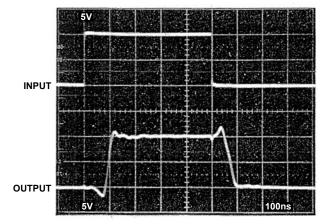

Vertical Scale: Input = 5V/Div, (CMOS;  $V_{AH} = 10V$ ,  $V_{AL} = 0V$ )

Output = 5V/Div Horizontal Scale: 100ns/Div

FIGURE 14.

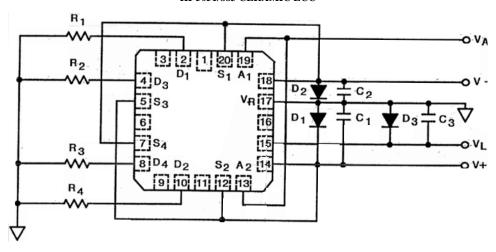

# **Burn-In Circuit**

### HI-5051/883 CERAMIC LCC

#### NOTES:

$\begin{array}{l} R_1 \; \text{thru} \; R_4 = 10 \text{k}\Omega, \; \pm 5\%, \; 1/4 \text{W (Min)} \\ C_1, \; C_2, \; C_3 = 0.01 \mu \text{F/Socket (Min) or } 0.1 \mu \text{F/Row, (Min)} \\ D_1, \; D_2, \; D_3 = 1 \text{N4}002 \; \text{or Equivalent/Board} \\ V_L = 5.5 \text{V} \; \pm 0.5 \text{V} \\ A_2 = A_2 = 5.5 \text{V} \; \pm 0.5 \text{V} \\ | \; (\text{V+}) \; - \; (\text{V-}) \; | \; = 30 \text{V} \end{array}$

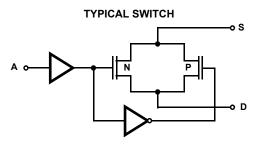

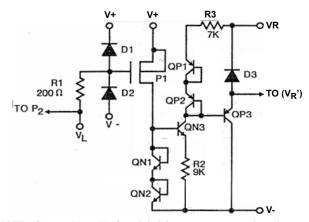

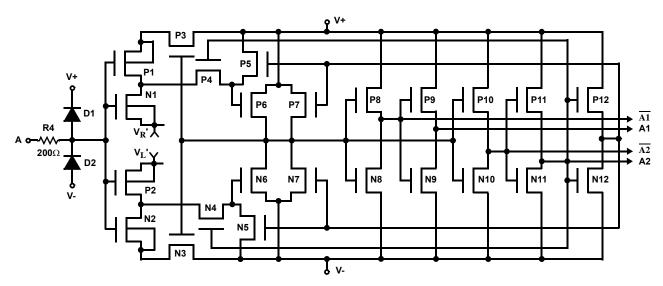

# **Schematic Diagrams**

NOTE: Connect V+ to  ${\rm V}_{\rm L}$  for minimizing power consumption when driving from CMOS circuits.

FIGURE 15. TTL/CMOS REFERENCE CIRCUIT

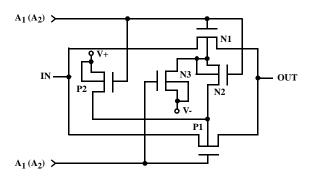

FIGURE 16. SWITCH CELL

NOTE: All N-Channel bodies to V-, all P-Channel bodies to V+ except as shown.

DIGITAL INPUT BUFFER AND LEVEL SHIFTER

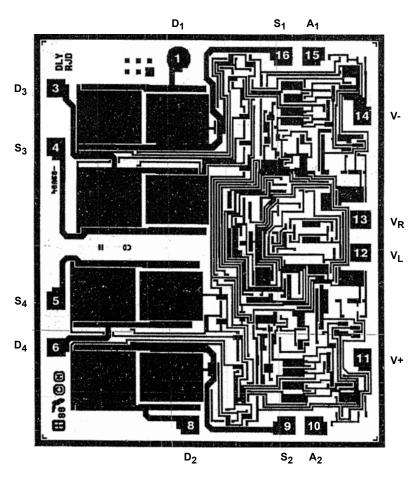

### **Die Characteristics**

### **DIE DIMENSIONS:**

96mils x 81mils x 20mils (2430µm x 2050µm x 508µm)

#### **METALLIZATION:**

Type: Aluminum Thickness: 16kÅ ±2kÅ

### **GLASSIVATION:**

Type: Nitride over Silox Silox Thickness: 12kÅ ±2kÅ Nitride Thickness: 3.5kÅ ±1kÅ

SUBSTRATE POTENTIAL (Powered-up): V-

**DEVICE COUNT: 82**

### **WORST CASE CURRENT DENSITY:**

$1.0 \times 10^5 \text{A/cm}^2$  at 20 mA

# **Metallization Mask Layout**

HI-5051/883

**Design Information** The information contained in this section has been developed through characterization and is for use as application and design information only. No guarantee is implied.

### **Typical Performance Curves** $T_A = +25$ °C, $V_{SUPPLY} = \pm 15V$

FIGURE 17. ON RESISTANCE vs ANALOG SIGNAL LEVEL AND POWER SUPPLY VOLTAGE

FIGURE 18. NORMALIZED ON RESISTANCE vs TEMPERATURE

FIGURE 19. NORMALIZED ON RESISTANCE vs ANALOG CURRENT

FIGURE 20. ON/OFF LEAKAGE CURRENTS vs TEMPERATURE

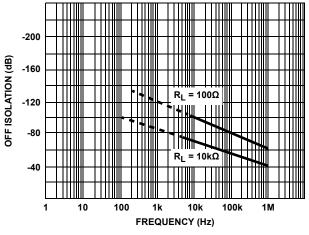

FIGURE 21. OFF ISOLATION vs FREQUENCY

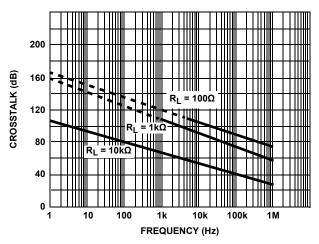

FIGURE 22. CROSSTALK vs FREQUENCY

**Design Information** The information contained in this section has been developed through characterization and is for use as application and design information only. No guarantee is implied.

### Typical Performance Curves $T_A = +25 \,^{\circ}\text{C}, V_{SUPPLY} = \pm 15 \text{V}$ (Continued)

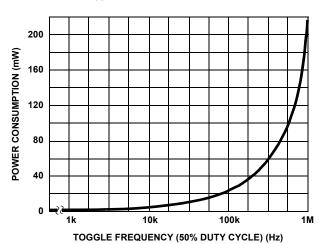

FIGURE 23. POWER CONSUMPTION vs FREQUENCY

For additional products, see <a href="www.intersil.com/product-tree">www.intersil.com/product-tree</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

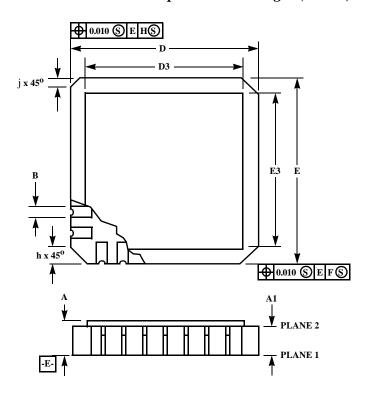

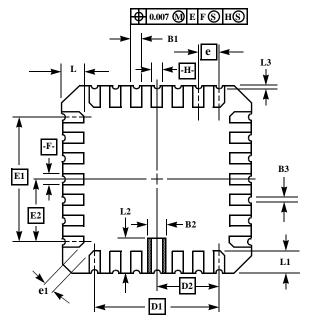

### Ceramic Leadless Chip Carrier Packages (CLCC)

12

J20.A MIL-STD-1835 CQCC1-N20 (C-2) 20 PAD CERAMIC LEADLESS CHIP CARRIER PACKAGE

|        | INC   | HES MILLIMETERS |          |      |       |  |

|--------|-------|-----------------|----------|------|-------|--|

| SYMBOL | MIN   | MAX             | MIN      | MAX  | NOTES |  |

| A      | 0.060 | 0.100           | 1.52     | 2.54 | 6, 7  |  |

| A1     | 0.050 | 0.088           | 1.27     | 2.23 | -     |  |

| В      | -     | -               | -        | -    | -     |  |

| B1     | 0.022 | 0.028           | 0.56     | 0.71 | 2,4   |  |

| B2     | 0.072 | REF             | 1.83     | REF  | -     |  |

| В3     | 0.006 | 0.022           | 0.15     | 0.56 | -     |  |

| D      | 0.342 | 0.358           | 8.69     | 9.09 | -     |  |

| D1     | 0.200 | BSC             | 5.08     | BSC  | -     |  |

| D2     | 0.100 | BSC             | 2.54     | BSC  | -     |  |

| D3     | -     | 0.358           | -        | 9.09 | 2     |  |

| Е      | 0.342 | 0.358           | 8.69     | 9.09 | -     |  |

| E1     | 0.200 | BSC             | 5.08 BSC |      | -     |  |

| E2     |       | BSC             | 2.54     | BSC  | -     |  |

| E3     | -     | 0.358           | -        | 9.09 | 2     |  |

| e      | 0.050 | 0.050 BSC       |          | BSC  | -     |  |

| e1     | 0.015 | -               | 0.38     | -    | 2     |  |

| h      | 0.040 | 0.040 REF       |          | REF  | 5     |  |

| j      | 0.020 | REF             | 0.51     | REF  | 5     |  |

| L      | 0.045 | 0.055           | 1.14     | 1.40 | -     |  |

| L1     | 0.045 | 0.055           | 1.14     | 1.40 | -     |  |

| L2     | 0.075 | 0.095           | 1.91     | 2.41 | -     |  |

| L3     | 0.003 | 0.015           | 0.08     | 0.38 | -     |  |

| ND     | 4     | 5               | 5        |      | 3     |  |

| NE     | 4     | 5               |          | 5    | 3     |  |

| N      | 2     | 20              |          | 20   |       |  |

Rev. 0 5/18/94

#### NOTES:

- 1. Metallized castellations shall be connected to plane 1 terminals and extend toward plane 2 across at least two layers of ceramic or completely across all of the ceramic layers to make electrical connection with the optional plane 2 terminals.

- Unless otherwise specified, a minimum clearance of 0.015 inch (0.38mm) shall be maintained between all metallized features (e.g., lid, castellations, terminals, thermal pads, etc.)

- 3. Symbol "N" is the maximum number of terminals. Symbols "ND" and "NE" are the number of terminals along the sides of length "D" and "E", respectively.

- 4. The required plane 1 terminals and optional plane 2 terminals (if used) shall be electrically connected.

- 5. The corner shape (square, notch, radius, etc.) may vary at the manufacturer's option, from that shown on the drawing.

- 6. Chip carriers shall be constructed of a minimum of two ceramic layers.

- 7. Dimension "A" controls the overall package thickness. The maximum "A" dimension is package height before being solder dipped.

- 8. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- 9. Controlling dimension: INCH.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Analog Switch ICs category:

Click to view products by Renesas manufacturer:

Other Similar products are found below:

DG9233EDY-GE3 NLAS4684FCTCG NLAS5223BLMNR2G NLV74HC4066ADR2G MC74HC4067ADTG NCN2612BMTTWG

NLX2G66DMUTCG NS5A4684SMNTAG 732480R 733995E 425541DB 425528R 099044FB FSA221UMX MAX4888ETI+T

MAX4968CEXB+ MAX4760EWX+T NLAS3799BMNR2G NLAS5123MNR2G NLAS5213AMUTAG NLAS7222AMTR2G

NLAS5213AUSG MAX14807ECB+ MAX4968ECM+ NLV14066BDG LC78615E-01US-H PI5A4599BCEX PI5A3157BZUEX

NLAS4717EPFCT1G PI5A3167CCEX MAX4744ELB+T MAX4802ACXZ+ SLAS3158MNR2G PI5A3157BC6EX PI5A392AQE

MAX4744HELB+T PI5A4157ZUEX MC74HC4067ADTR2G PI5A4158ZAEX PI5A3166TAEX MAX4901EBL+T MAX14510EEVB+T

PI3A3899ZTEX MAX4996ETG+T MAX4889AETO+T MAX14508EEVB+T MAX4701ETE+T MAX4996LETG+T NLX2G66FCTAG

TMUX136RSER