# PI6LC48P0101

## HiFlex 10GbE Clock Generator

#### Features

- ➔ One Differential LVPECL output

- → Crystal oscillator interface, 18pF parallel resonant crystal (23.2MHz - 30MHz)

- → Output frequency range: 290MHz 750MHz

- → RMS phase jitter @ 312.5MHz, using a 25MHz crystal (12kHz - 20MHz): 0.3ps (typical), 0.5ps (max)

- → 3.3V or 2.5V operating supply

- → -40°C to 85°C operating temperature

- ➔ Available in 8pin TSSOP

#### **Description**

The PI6LC48P0101 is a 10Gb Ethernet Clock Generator. The PI6LC48P0101 uses an 18pF parallel resonant crystal over the range of 23.2MHz - 30MHz. For Ethernet applications, a 25MHz crystal is used. The PI6LC48P0101 can achieve <0.5ps RMS phase jitter performance over the 12kHz - 20MHz integration range. The PI6LC48P0101 is packaged in a small 8-pin TSSOP, making it ideal for use in systems with limited board space.

| 5                          | In       | puts |   |                             |                           |

|----------------------------|----------|------|---|-----------------------------|---------------------------|

| Crystal Frequency<br>(MHz) | FREQ_SEL | М    | N | Multiplication Value<br>M/N | Output Frequency<br>(MHz) |

| 25                         | 1        | 25   | 1 | 25                          | 625                       |

| 25                         | 0        | 25   | 2 | 12.5                        | 312.5                     |

## **Common Configuration Table**

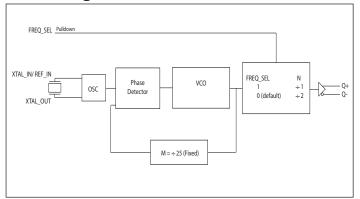

## **Block Diagram**

## **Pin Configuration**

|                        | 8 🛛 Vdd    |

|------------------------|------------|

| VEE 🛛 2                | 7 🛛 Q+     |

| XTAL_OUT 🛛 3           | 6 🛛 Q-     |

| XTAL_IN/ 🛛 4<br>REF_IN | 5 FREQ_SEL |

|                        |            |

09/01/15

PI6LC48P0101 Rev A

## **Pin Description**

| Pin # | Pin Name           | Ту     | pe       | Description                                                   |

|-------|--------------------|--------|----------|---------------------------------------------------------------|

| 1     | V <sub>DDA</sub>   | Power  |          | Analog supply pin.                                            |

| 2     | V <sub>EE</sub>    | Power  |          | Negative supply pin.                                          |

| 3     | XTAL_OUT           | Output |          | XTAL_OUT is the output.                                       |

| 4     | XTAL_IN/<br>REF_IN | Input  |          | XTAL_IN, can also be driven by a single ended reference clock |

| 5     | FREQ_SEL           | Input  | Pulldown | Frequency select pin. LVCMOS/LVTTL interface levels.          |

| 6,7   | Q-, Q+             | Output |          | Differential clock outputs. LVPECL interface levels.          |

| 8     | V <sub>DD</sub>    | Power  |          | Core supply pin.                                              |

NOTE: Pulldown refers to internal input resistors. See Pin Characteristics for typical values.

## **Pin Characteristics**

| Symbol                | Parameter               | Test Condition | Minimum | Typical | Maximum | Units |

|-----------------------|-------------------------|----------------|---------|---------|---------|-------|

| C <sub>IN</sub>       | Input Capacitance       |                |         | 4       |         | pF    |

| R <sub>PULLDOWN</sub> | Input Pulldown Resistor |                |         | 51      |         | kΩ    |

## **Maximum Ratings**

#### Note:

NOTE: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the DC Characteristics or AC Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

## **DC Electrical Characteristics**

Power Supply DC Characteristics ( $V_{DD} = 3.3V \pm 5\%$ ,  $V_{EE} = 0V$ ,  $T_A = -40$  °C to 85 °C)

| Symbol           | Parameter             | Test Condition | Min.                   | Тур. | Max.            | Units |

|------------------|-----------------------|----------------|------------------------|------|-----------------|-------|

| V <sub>DD</sub>  | Core Supply Voltage   |                | 3.135                  | 3.3  | 3.465           | V     |

| V <sub>DDA</sub> | Analog Supply Voltage |                | V <sub>DD</sub> - 0.25 | 3.3  | V <sub>DD</sub> | V     |

| I <sub>EE</sub>  | Power Supply Current  |                |                        |      | 83              | mA    |

| I <sub>DDA</sub> | Analog Supply Current |                |                        |      | 28              | mA    |

#### Power Supply DC Characteristics ( $V_{DD} = 2.5V \pm 5\%$ , $V_{EE} = 0V$ , $T_A = -40$ °C to 85 °C)

| Symbol           | Parameter             | Test Condition | Min.                   | Тур. | Max.            | Units |

|------------------|-----------------------|----------------|------------------------|------|-----------------|-------|

| V <sub>DD</sub>  | Core Supply Voltage   |                | 2.375                  | 2.5  | 2.625           | V     |

| VDDA             | Analog Supply Voltage |                | V <sub>DD</sub> - 0.25 | 2.5  | V <sub>DD</sub> | V     |

| I <sub>EE</sub>  | Power Supply Current  |                |                        |      | 78              | mA    |

| I <sub>DDA</sub> | Analog Supply Current |                |                        |      | 28              | mA    |

**LVCMOS/LVTTL DC Characteristics** ( $V_{DD}$  = 3.3V±5% or 2.5V±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to 85°C)

| Symbol          | Parameter          | Test Condition                                       | Min. | Тур. | Max.                  | Units |

|-----------------|--------------------|------------------------------------------------------|------|------|-----------------------|-------|

| V               | Innut High Voltage | $V_{DD} = 3.3 V$                                     | 2    |      | V <sub>DD</sub> + 0.3 | V     |

| V <sub>IH</sub> | Input High Voltage | $V_{DD} = 2.5 V$                                     | 1.7  |      | $V_{DD} + 0.3$        | V     |

| V               |                    | $V_{DD} = 3.3 V$                                     | -0.3 |      | 0.8                   | V     |

| V <sub>IL</sub> | Input Low Voltage  | $V_{DD} = 2.5 V$                                     | -0.3 |      | 0.7                   | V     |

| I <sub>IH</sub> | Input High Current | $V_{DD} = V_{IN} = 2.625 V \text{ or } 3.465 V$      |      |      | 150                   | μA    |

| I <sub>IL</sub> | Input Low Current  | $V_{DD} = 2.625 V \text{ or } 3.465 V, V_{IN} = 0 V$ | -5   |      |                       | μA    |

#### **LVPECL DC Characteristics (** $V_{DD}$ = 3.3V±5%, $V_{EE}$ = 0V, $T_A$ = -40°C to 85°C)

| Symbol             | Parameter                         | Test Condition   | Min. | Тур. | Max. | Units |

|--------------------|-----------------------------------|------------------|------|------|------|-------|

| N7                 | Output High Valta gat             | $V_{DD} = 3.3V$  | 1.9  |      | 2.4  | V     |

| V <sub>OH</sub>    | Output High Voltage*              | $V_{DD} = 2.5 V$ | 1.1  |      | 1.6  | v     |

| 17                 | Orthout I and Walts and           | $V_{DD} = 3.3V$  | 1.2  |      | 1.6  | 17    |

| V <sub>OL</sub>    | Output Low Voltage*               | $V_{DD} = 2.5 V$ | 0.4  |      | 0.8  |       |

| V <sub>SWING</sub> | Peak-to-Peak Output Voltage Swing |                  | 0.6  |      | 1.0  | V     |

Note: LVPECL Termination: Source 1500hm to GND and 1000hm across CLK+ and CLK-

#### **Crystal Characteristics**

| Parameter                          | Test Condition | Min. | Тур.        | Max. | Units |

|------------------------------------|----------------|------|-------------|------|-------|

| Mode of Oscillation                |                | I    | Fundamental | l    |       |

| Frequency                          |                | 23.2 |             | 30   | MHz   |

| Equivalent Series Resistance (ESR) |                |      |             | 40   | Ω     |

| Shunt Capacitance                  |                |      |             | 7    | pF    |

4

NOTE: It is not recommended to overdrive the crystal input with an external clock.

## **AC Electrical Characteristics**

$(V_{DD} = 3.3V \pm 5\%, V_{EE} = 0V, T_A = -40^{\circ}C \text{ to } 85^{\circ}C)$

| Symbol                          | Parameter                  | Test Conditions                                   | Min. | Тур.  | Max. | Units |  |

|---------------------------------|----------------------------|---------------------------------------------------|------|-------|------|-------|--|

| C                               | Output Englisher av        | $FREQ\_SEL = 0$                                   |      | 312.5 |      | MHz   |  |

| fout                            | Output Frequency           | $FREQ\_SEL = 1$                                   |      | 625   |      | MHz   |  |

|                                 |                            | 312.5MHz @ Integration Range:<br>12kHz - 20MHz    |      | 0.3   | 0.5  |       |  |

| tjit                            | RMS Phase Jitter (Random)* | 312.5MHz @ Integration Range:<br>1.875MHz - 20MHz |      | 0.1   |      | ps    |  |

|                                 |                            | 625MHz @ Integration Range:<br>12kHz - 20MHz      |      | 0.3   | 0.5  |       |  |

|                                 |                            | 625MHz @ Integration Range:<br>1.875MHz - 20MHz   |      | 0.07  |      | ps    |  |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time      | 20% to 80%                                        | 100  |       | 400  | ps    |  |

| odc                             | Output Duty Cycle          |                                                   | 47   |       | 53   | %     |  |

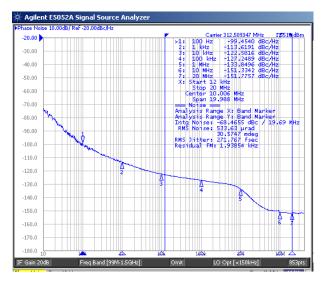

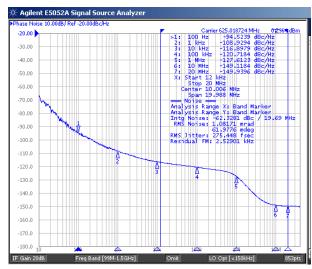

NOTE: Refer to the Phase Noise Plots following this section.

| AC Electrical Characteristics ( $V_{DD} = 2.5V \pm 5\%$ , $V_{EE} = 0V$ , | $I_{\rm A} = -40^{\circ}{\rm C}$ to 85°C) |

|---------------------------------------------------------------------------|-------------------------------------------|

|---------------------------------------------------------------------------|-------------------------------------------|

| Symbol                          | Parameter                  | Test Conditions               | Min. | Тур.  | Max. | Units |

|---------------------------------|----------------------------|-------------------------------|------|-------|------|-------|

| f <sub>OUT</sub>                | Output Frequency           | $FREQ\_SEL = 0$               |      | 312.5 |      | MHz   |

|                                 |                            | $FREQ\_SEL = 1$               |      | 625   |      | MHz   |

| tjit                            | RMS Phase Jitter (Random)* | 312.5MHz @ Integration Range: |      | 0.2   | 0.5  | - ps  |

|                                 |                            | 12kHz - 20MHz                 |      | 0.3   | 0.5  |       |

|                                 |                            | 312.5MHz @ Integration Range: |      | 0.1   |      |       |

|                                 |                            | 1.875MHz - 20MHz              |      | 0.1   |      |       |

|                                 |                            | 625MHz @ Integration Range:   |      | 0.3   | 0.5  |       |

|                                 |                            | 12kHz - 20MHz                 |      | 0.5   |      |       |

|                                 |                            | 625MHz @ Integration Range:   |      | 0.07  |      | ps    |

|                                 |                            | 1.875MHz - 20MHz              |      | 0.07  |      |       |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time      | 20% to 80%                    | 100  |       | 400  | ps    |

| odc                             | Output Duty Cycle          |                               | 47   |       | 53   | %     |

5

NOTE: Refer to the Phase Noise Plots following this section.

#### **Phase Noise Plots**

312.5MHz

#### 625MHz

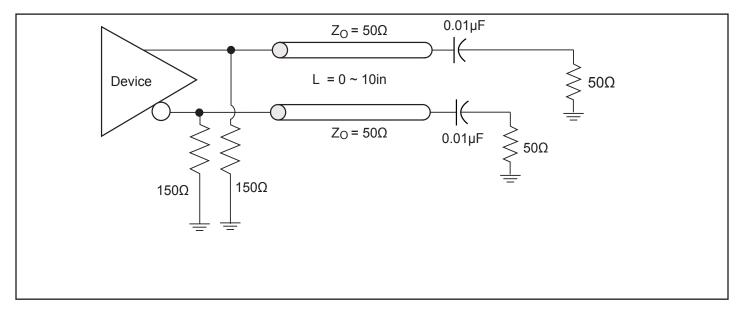

## **LVPECL** Test Circuit

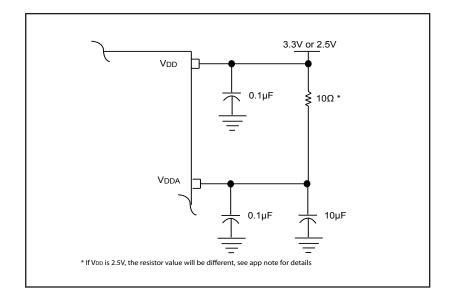

## **Power Supply Filtering Techniques**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. The PI6LC48P0101 provides separate power supplies to isolate any high switching noise from the outputs to the internal PLL.  $V_{DD}$  and  $V_{DDA}$  should be individually connected to the power supply plane through vias, and 0.1µF bypass capacitors should be used for each pin. Figure below illustrates this for a generic  $V_{DD}$  pin and also shows that  $V_{DDA}$ requires that an additional 10 $\Omega$  resistor along with a 10µF bypass capacitor be connected to the  $V_{DDA}$  pin.

PERICOM<sup>®</sup>

## **Crystal Input Interface**

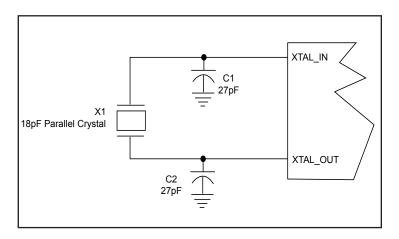

The clock generator has been characterized with 18pF parallel resonant crystals. The capacitor values shown in the figure below were determined using a 25MHz, 18pF parallel resonant crystal and were chosen to minimize the ppm error.

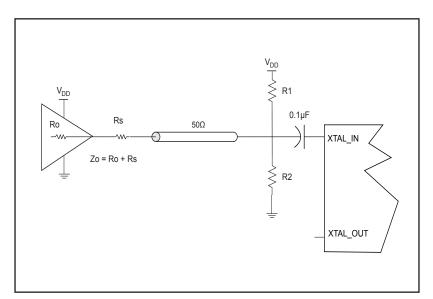

## **LVCMOS to XTAL Interface**

The XTAL\_IN input can accept a single-ended LVCMOS signal through an AC coupling capacitor. A general interface diagram is shown in the figure below. The XTAL\_OUT pin can be left floating. The input edge rate can be as slow as 10ns. For LVCMOS signals, it is recommended that the amplitude be reduced from full swing to half swing in order to prevent signal interference with the power rail and to reduce noise. This configuration requires that the output impedance of the driver (Ro) plus the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the crystal input will attenuate the signal in half. This can be done in one of the two ways. First, R1 and R2 in parallel should equal the transmission line empedance. For most  $50\Omega$  applications, R1 and R2 can be  $100\Omega$ . This can also be accomplished by removing R1 and making R2  $50\Omega$ . By overdriving the crystal oscillator, the device will be functional, but note, the device performance is quaranteed by using a quartz crystal.

## **Thermal Information**

| Symbol               | Description                            |          |

|----------------------|----------------------------------------|----------|

| $\Theta_{_{JA}}$     | Junction-to-ambient thermal resistance | 124 °C/W |

| $\Theta_{_{\rm JC}}$ | Junction-to-case thermal resistance    | 37°C/W   |

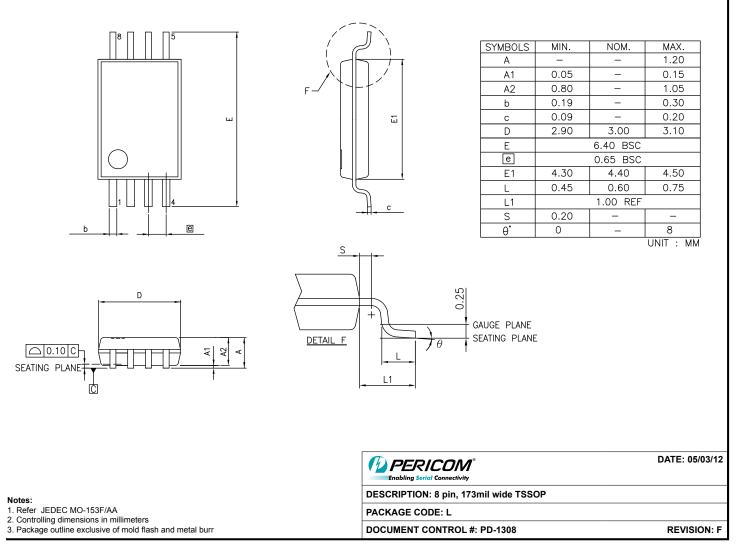

## **Packaging Mechanical:**

# Ordering Information

| Ordering Code    | Package Code | Package Type                              |

|------------------|--------------|-------------------------------------------|

| PI6LC48P0101LIE  | L            | Pb-free & Green, 8-pin TSSOP              |

| PI6LC48P0101LIEX | L            | Pb-free & Green, 8-pin TSSOP, Tape & Reel |

9

#### Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

2. "E" denotes Pb-free and Green

3. Adding an "X" at the end of the ordering code denotes tape and Reel packaging

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Clock Generators & Support Products category:

Click to view products by Diodes Incorporated manufacturer:

Other Similar products are found below :

5P49V5901A748NLGI 5P49V5901B680NLGI 5P49V5901B744NLGI 5P49V5929B502NLGI 5P49V5935B520LTGI 5V49EE903-116NLGI CV183-2TPAG 82P33814ANLG/W 8T49N004A-002NLGI 8T49N004A-039NLGI 9FGV0631CKLF 9FGV0641AKLFT 9LRS3197AKLF 9UMS9633BFILF 9VRS4450AKLF NB3N51132DTR2G 8N3Q001EG-0035CDI 932SQ426AKLF 950810CGLF 9DBV0531AKILF 9DBV0741AKILF 9FGV0641AKLF 9UMS9633BKLF 9VRS4420DKILF 9VRS4420DKLF 9VRS4420DKLFT CY25404ZXI226 CY25422SXI-004 5P49V5901B712NLGI NB3H5150-01MNTXG 6INT61041NDG PL602-20-K52TC PL613-51QC 8N3Q001FG-1114CDI 9FGV0641AKILF ZL30314GKG2 ZL30253LDG1 ZL30251LDG1 ZL30250LDG1 ZL30169LDG1 ZL30142GGG2 9UMS9633BKILFT 9FGV0631CKLFT 9FGV0631CKILF 5P49V5935B536LTGI PI6LC48P0101LIE DS1099U-ST+ MAX24305EXG+ PI6LC48H02-01LIE 82P33814ANLG