# Lattice **CORE**

PCI Express 1.1 Root Complex Lite x1, x4 IP Core User's Guide

# **Table of Contents**

| Chapter 1. Introduction                                   | 4  |

|-----------------------------------------------------------|----|

| Quick Facts                                               |    |

| Features                                                  |    |

| PHY Layer                                                 | 5  |

| Data Link Layer                                           |    |

| Transaction Layer                                         |    |

| Top Level IP Support                                      |    |

| Chapter 2. Functional Description                         |    |

| Overview                                                  |    |

| Interface Description                                     |    |

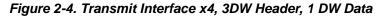

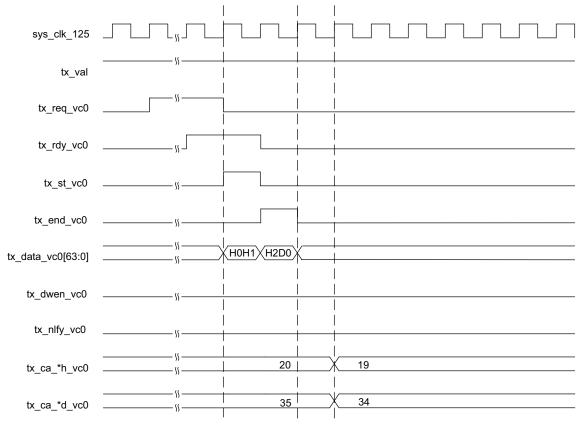

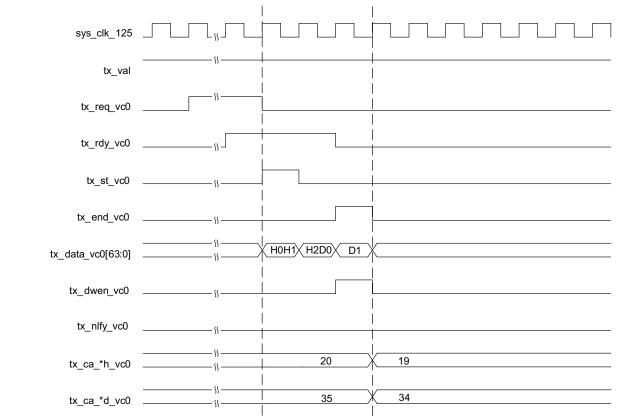

| Transmit TLP Interface                                    |    |

| Transmit TLP Interface Waveforms for x1                   |    |

| Receive TLP Interface                                     |    |

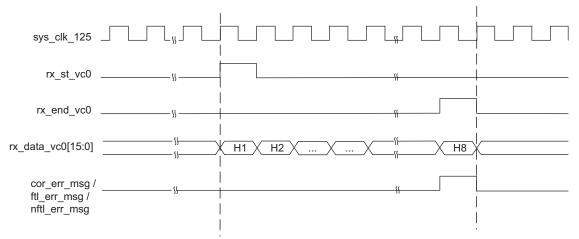

| Message Decode Interface                                  |    |

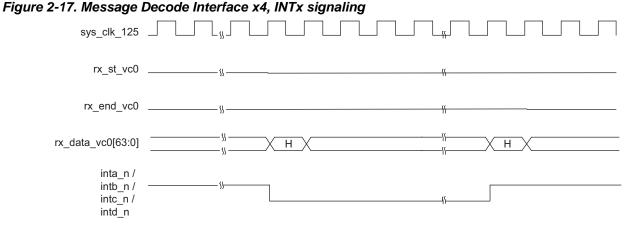

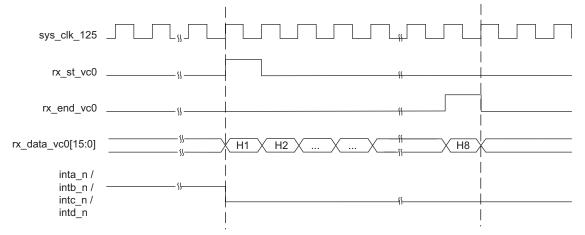

| Interrupt Signaling Messages                              |    |

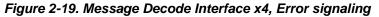

| Error Signaling Messages                                  |    |

| Using the Transmit and Receive Interfaces                 |    |

| As a Receiver                                             |    |

| As a Transmitter                                          |    |

| Chapter 3. Parameter Settings                             |    |

| General Tab                                               |    |

| PCI Express Link Configuration                            |    |

| Include Master Loopback Data Path                         |    |

| Maximum Payload Size                                      |    |

| Include ECRC Support                                      |    |

| Flow Control Tab                                          |    |

| Initial Receive Credits                                   |    |

| Infinite PH Credits                                       |    |

| Initial PH Credits Available                              |    |

| Infinite PD Credits                                       |    |

| Initial PD Credits Available                              |    |

| Infinite NPH Credits                                      |    |

| Initial NPH Credits Available                             |    |

| Infinite NPD Credits                                      |    |

| Initial NPD Credits Available                             |    |

| Infinite CPLH Credits                                     |    |

| Initial CPLH Credits Available                            |    |

| Infinite CPLD Credits                                     |    |

| Initial CPLD Credits Available                            |    |

| Update Flow Control Generation Control                    |    |

| Number of P TLPs Between UpdateFC                         |    |

| Number of PD TLPs Between UpdateFC                        |    |

| Number of NP TLPs Between UpdateFC                        |    |

| Number of NPD TLPs Between UpdateFC                       |    |

| Number of CPL TLPs Between UpdateFC                       |    |

| Number of CPLD TLPs Between UpdateFC                      |    |

| Worst Case Number of 125MHz Clock Cycles Between UpdateFC |    |

| Chapter 4. IP Core Generation and Evaluation              |    |

| Licensing the IP Core                                     |    |

|                                                           | 35 |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Licensing Requirements for LatticeECP2M/LatticeECP3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Getting Started                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                              |

| IPexpress-Created Files and Top Level Directory Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                              |

| Running Functional Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                              |

| Synthesizing and Implementing the Core in a Top-Level Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

| Hardware Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                              |

| Enabling Hardware Evaluation in Diamond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                              |

| Enabling Hardware Evaluation in ispLEVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 41                                                                                                                                                                           |

| Updating/Regenerating the IP Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                              |

| Regenerating an IP Core in Diamond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                                                           |

| Regenerating an IP Core in ispLEVER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42                                                                                                                                                                           |

| Chapter 5. Using the IP Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 43                                                                                                                                                                           |

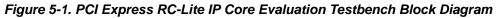

| Simulation and Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                                                                                                                                           |

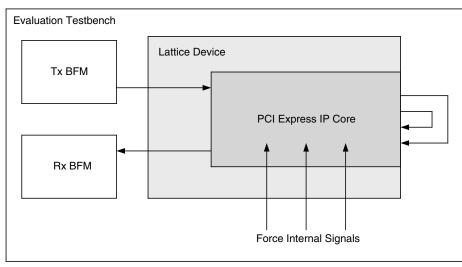

| Simulation Strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43                                                                                                                                                                           |

| Third Party Verification IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44                                                                                                                                                                           |

| FPGA Design Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                              |

| Setting Up the Core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                              |

| Setting Up for x4 (No Flip)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |

| Setting Up for x4 (Flipped)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                              |

| Setting Design Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                              |

| Errors and Warnings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                              |

| Clocking Scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                              |

| Locating the IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                              |

| Board-Level Implementation Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                              |

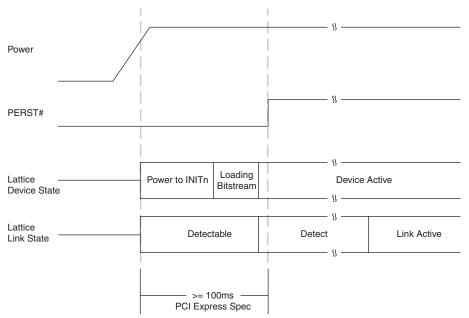

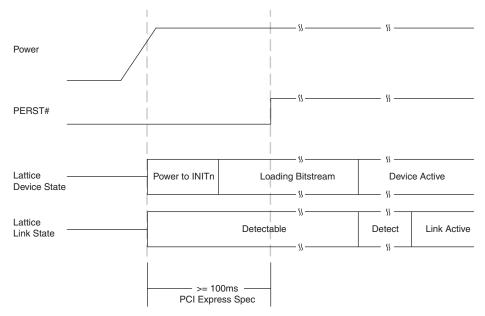

| PCI Express Power-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                              |

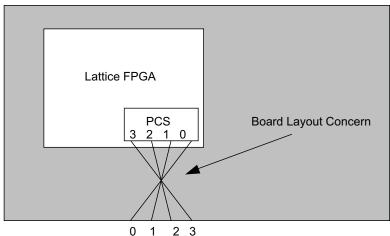

| Board Layout Concerns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                              |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                              |

| I rouplesnooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                              |

| Troubleshooting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                              |

| Chapter 6. Core Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                              |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 56<br>57                                                                                                                                                                     |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>56</b><br><b>57</b><br>57                                                                                                                                                 |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>56</b><br><b>57</b><br>57<br>57<br>57                                                                                                                                     |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline                                                                                                                                                                                                                                                                                                                                                                                                           | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57                                                                                                                               |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support                                                                                                                                                                                                                                                                                                                                                                                         | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57                                                                                                                         |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support                                                                                                                                                                                                                                                                                                                                                                        | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                                                             |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet                                                                                                                                                                                                                                                                                                                                                            | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                                                       |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site                                                                                                                                                                                                                                                                                                                                 | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                                                 |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support.<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website                                                                                                                                                                                                                                                                                                             | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                                     |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References                                                                                                                                                                                                                                                                                                | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                               |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3                                                                                                                                                                                                                                                                                 | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                         |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M                                                                                                                                                                                                                                                                 | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                         |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums.<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet.<br>PCIe Solutions Web Site<br>PCI-SIG Website.<br>References.<br>LatticeECP3<br>LatticeECP2M<br>Revision History                                                                                                                                                                                                                                         | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58                                                 |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>Revision History<br>Appendix A. Resource Utilization                                                                                                                                                                                                         | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58                               |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP3<br>LatticeECP3<br>Revision History<br>Appendix A. Resource Utilization<br>Configuration                                                                                                                                                                          | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58                   |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP3<br>Revision History<br>Appendix A. Resource Utilization<br>Configuration                                                                                                                                                                                         | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58       |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP2M<br>Revision History<br>Appendix A. Resource Utilization<br>Configuration<br>LatticeECP2M Utilization (x4 RC-Lite)<br>Ordering Part Number                                                                                                                       | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                         |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support.<br>Online Forums.<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet.<br>PCIe Solutions Web Site<br>PCI-SIG Website.<br>References.<br>LatticeECP3<br>LatticeECP3<br>LatticeECP2M<br>Revision History.<br>Appendix A. Resource Utilization<br>Configuration<br>LatticeECP2M Utilization (x4 RC-Lite)<br>Ordering Part Number.<br>LatticeECP3 Utilization (x4 RC-Lite)                                                         | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                         |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support.<br>Online Forums.<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet.<br>PCIe Solutions Web Site.<br>PCI-SIG Website.<br>References<br>LatticeECP3<br>LatticeECP3<br>LatticeECP2M<br>Revision History.<br>Appendix A. Resource Utilization<br>Configuration<br>LatticeECP2M Utilization (x4 RC-Lite)<br>Ordering Part Number                                                                                                  | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58 |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP3<br>LatticeECP4<br>Revision History<br>Appendix A. Resource Utilization<br>Configuration<br>LatticeECP2 Utilization (x4 RC-Lite)<br>Ordering Part Number<br>LatticeECP3 Utilization (x1 RC-Lite)<br>Ordering Part Number<br>LatticeECP2M Utilization (x1 RC-Lite) | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58       |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57                                                                         |

| Chapter 6. Core Verification<br>Chapter 7. Support Resources<br>Lattice Technical Support<br>Online Forums<br>Telephone Support Hotline<br>E-mail Support<br>Local Support<br>Internet<br>PCIe Solutions Web Site<br>PCI-SIG Website<br>References<br>LatticeECP3<br>LatticeECP3<br>LatticeECP4<br>Revision History<br>Appendix A. Resource Utilization<br>Configuration<br>LatticeECP2 Utilization (x4 RC-Lite)<br>Ordering Part Number<br>LatticeECP3 Utilization (x1 RC-Lite)<br>Ordering Part Number<br>LatticeECP2M Utilization (x1 RC-Lite) | <b>56</b><br><b>57</b><br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>57<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58<br>58       |

PCI Express is a high performance, fully scalable, well defined standard for a wide variety of computing and communications platforms. It has been defined to provide software compatibility with existing PCI drivers and operating systems. Being a packet based serial technology, PCI Express greatly reduces the number of required pins and simplifies board routing and manufacturing. PCI Express is a point-to-point technology, as opposed to the multidrop bus in PCI. Each PCI Express device has the advantage of full duplex communication with its neighbor to greatly increase overall system bandwidth. The basic data rate for a single lane is double that of the 32 bit/33 MHz PCI bus. A four lane link has eight times the data rate in each direction of a conventional bus.

Lattice's PCI Express Root Complex (RC) Lite core provides an x1 or x4 root complex solution from the electrical SERDES interface, physical layer, data link layer and a minimum transaction layer in PCI express protocol stack. This IP is a lighter version of the root complex intended to be used in simple local bus bridging applications. This solution supports the LatticeECP3<sup>™</sup> and LatticeECP2M<sup>™</sup> FPGA device families and is an extremely economical, high value FPGA platform.

This user's guide covers two versions of the Lattice PCI Express RC-Lite core:

- The PCI Express x4 RC-Lite Core targets the LatticeECP3 and LatticeECP2M families of devices.

- The PCI Express x1 RC-Lite Core targets the LatticeECP3 and LatticeECP2M families. This is a reduced LUT count x1 core with a 16-bit datapath.

Refer to Lattice's PCIe Solutions web site at:

http://www.latticesemi.com/solutions/technologysolutions/pciexpresssolutions.cfm?source=topnav

# **Quick Facts**

Table 1-1 gives quick facts about the PCI Express RC-Lite IP core.

Table 1-1. PCI Express RC-Lite IP Core Quick Facts

|              |                                    | PCI Express RC-Lite IP Configuration                                                                                                                                         |                  |                  |                  |  |  |

|--------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|--|--|

|              |                                    | x4                                                                                                                                                                           | RC               | Native x1 RC     |                  |  |  |

| Core         | FPGA Families Supported            | LatticeECP3 and LatticeECP2M                                                                                                                                                 |                  |                  |                  |  |  |

| Requirements | Minimal Device Needed <sup>1</sup> | LFE3-17E-7FN484C                                                                                                                                                             | LFE2M-20E-6F484C | LFE3-17E-7FN484C | LFE2M-20E-6F484C |  |  |

|              | Targeted Device                    | LFE3-70E-7FN672C                                                                                                                                                             | LFE2M-50E-6F672C | LFE3-70E-7FN672C | LFE2M-50E-6F672C |  |  |

| Typical      | Data Path Width                    | 64                                                                                                                                                                           | 64               | 16               | 16               |  |  |

| Resource     | LUTs                               | 10650                                                                                                                                                                        | 10900            | 4700             | 4800             |  |  |

| Utilization  | sysMEM EBRs                        | 9                                                                                                                                                                            | 9                | 5                | 5                |  |  |

|              | Registers                          | 8500                                                                                                                                                                         | 8500             | 3100             | 3150             |  |  |

|              | Lattice Implementation             | Diamond <sup>®</sup> 1.1 or ispLEVER <sup>®</sup> 8.1                                                                                                                        |                  |                  |                  |  |  |

|              | Suptagia                           | Synopsys <sup>®</sup> Synplify <sup>®</sup> Pro for Lattice D-2009.12L-1                                                                                                     |                  |                  |                  |  |  |

| Design Tool  | Synthesis                          | Mentor Graphics <sup>®</sup> Precision® RTL                                                                                                                                  |                  |                  |                  |  |  |

| Support      |                                    | Aldec Active-HDL® 8.2 (Windows only, Verilog and VHDL)           lation         Mentor Graphics ModelSim® SE 6.5F (Verilog Only)           Cadence® NC-Verilog® (Linux only) |                  |                  |                  |  |  |

|              | Simulation                         |                                                                                                                                                                              |                  |                  |                  |  |  |

|              |                                    |                                                                                                                                                                              |                  |                  |                  |  |  |

1. The packages specified in the Minimal Device Needed row relate to the many user interface signals implemented as I/Os in the evaluation design. Depending on the application, it might be possible to implement a design in a package with fewer I/O pins since the majority of the user interface signals are terminated inside the FPGA.

# **Features**

The Lattice PCI Express RC-Lite IP core supports the following features.

## **PHY Layer**

- 2.5 Gbps CML electrical interface

- PCI Express 1.1 electrical compliance

- Many options for signal integrity including differential output voltage, transmit pre-emphasis and receiver equalization

- · Serialization and de-serialization

- 8b10b symbol encoding/decoding

- · Link state machine for symbol alignment

- Clock tolerance compensation supports +/- 300 ppm

- · Framing and application of symbols to lanes

- Data scrambling and de-scrambling

- Lane-to-lane de-skew

- Link Training and Status State Machine (LTSSM)

- Electrical idle generation

- Receiver detection

- TS1/TS2 generation/detection

- Lane polarity inversion

- Link width negotiation

- Higher layer control to jump to defined states

## **Data Link Layer**

- Data link control and management state machine

- · Flow control initialization

- Ack/Nak DLLP generation/termination

- LCRC generation/checking

- Sequence number appending/checking/removing

- Retry buffer and management

- Receiver buffer

## **Transaction Layer**

- Transmit and Receive Flow control

- Malformed and poisoned TLP detection

- Optional ECRC generation/checking

- INTx message TLP decoding and interrupt signaling to user

- Error message TLP decoding and signaling to user.

- 128, 256, 512, 1k, 2k or 4k bytes maximum payload size

## **Top Level IP Support**

- 125 MHz user interface

- x4 supports a 64-bit data path

- x1 supports a 16-bit data path

- In transmit, user creates TLPs without ECRC, LCRC, or sequence number

- In receive, user receives valid TLPs without ECRC, LCRC, or sequence number

- Credit interface for transmit and receive for PH, PD, NPH, NPD, CPLH, CPLD credit types

- Higher layer control of LTSSM via ports

This chapter provides a functional description of the Lattice PCI Express RC-Lite IP core.

# Overview

The PCI Express RC-Lite IP core is implemented in several different FPGA technologies. These technologies include soft FPGA fabric elements such as LUTs, registers, embedded block RAMs (EBRs) and embedded hard elements with the PCS/SERDES.

The IPexpress<sup>™</sup> tool is used to customize and create a complete IP module for the user to instantiate in a design. Inside the module created by the IPexpress tool are several blocks implemented in heterogeneous technologies. All of the connectivity is provided, allowing the user to interact at the top level of the IP core.

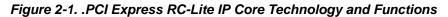

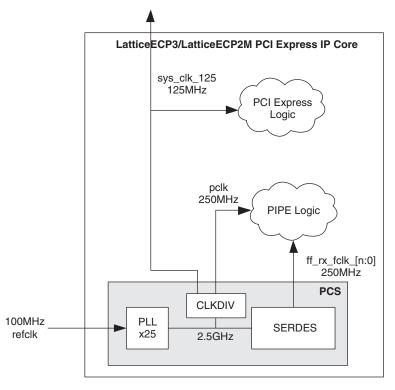

Figure 2-1 provides a high-level block diagram to illustrate the main functional blocks and the technology used to implement PCI Express RC-Lite IP core functions.

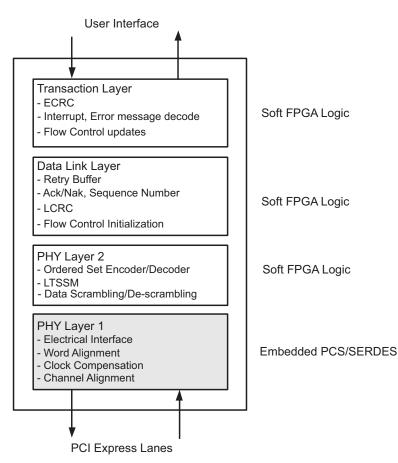

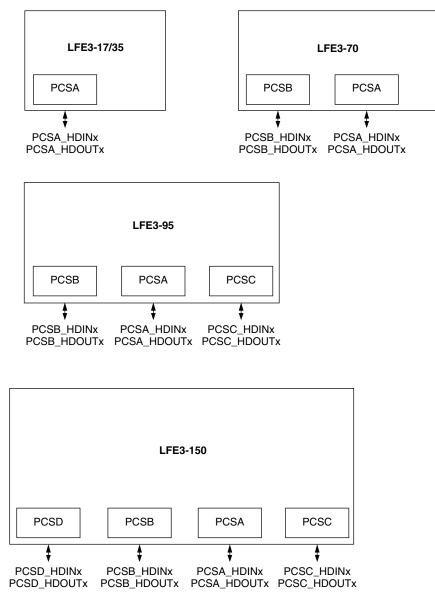

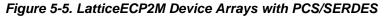

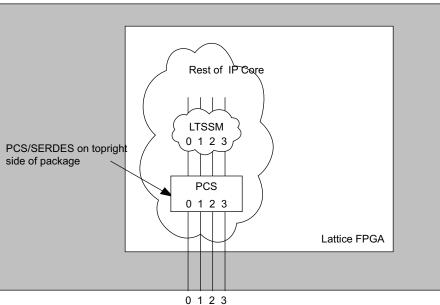

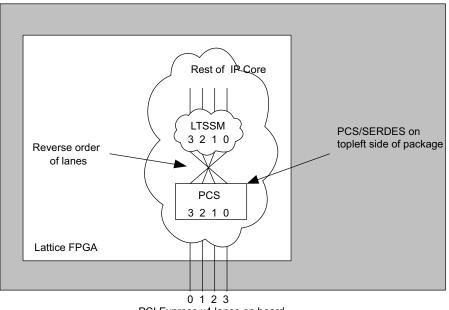

As the PCI Express RC-Lite IP core proceeds through the Diamond or ispLEVER software design flow specific technologies are targeted to their specific locations on the device. Figure 2-2 provides implementation representations of the LFE3/LFE2M devices with a PCI Express RC-Lite IP core.

Figure 2-2. PCI Express RC-Lite IP Core Implementation in LatticeECP3 and LatticeECP2M Devices

As shown, the data flow moves in and out of the heterogeneous FPGA technology. The user is responsible for selecting the location of the hard SERDES/PCS blocks as described in "Overview" on page 7. The FPGA logic placement and routing is the job of the Diamond or ispLEVER design tools to select regions nearby the hard SERDES/PCS blocks to achieve the timing goals.

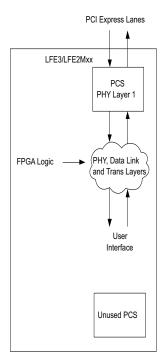

Figure 2-3 provides a high-level interface representation.

#### Figure 2-3. PCI Express RC-Lite IP Core Interfaces

Table 2-1 provides the list of ports and descriptions for the PCI Express RC-Lite IP core.

#### Table 2-1. PCI Express RC-Lite IP Core Port List

| Port Name                 | Direction | Clock | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock and Reset Interface |           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| refclk[p,n]               | Input     |       | 100 MHz PCI Express differential reference clock used to generate the 2.5 Gbps data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| sys_clk_125               | Output    |       | 125 MHz clock derived from refclk to be used in the user application.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| rst_n                     | Input     |       | Active-low asynchronous data path and state machine<br>reset. This port will be connected to the GSR for the entire<br>device. This reset is pulsed after bit stream download and<br>will not need to be asserted by the user.                                                                                                                                                                                                                                                                                                                                          |

| hdin[p,n]_[0,1,2,3]       | Input     |       | PCI Express 2.5 Gbps CML inputs for lanes 0,1,2, and 3.<br>The port "flip_lanes" is used to define the connection of<br>PCS/SERDES channel to PCI Express lane.<br>flip_lanes=0<br>hdin[p,n]_0 - PCI Express Lane 0<br>hdin[p,n]_1 - PCI Express Lane 1<br>hdin[p,n]_2 - PCI Express Lane 2<br>hdin[p,n]_3 - PCI Express Lane 3<br>flip_lanes=1<br>hdin[p,n]_0 - PCI Express Lane 3<br>hdin[p,n]_1 - PCI Express Lane 2<br>hdin[p,n]_2 - PCI Express Lane 3<br>hdin[p,n]_2 - PCI Express Lane 1<br>hdin[p,n]_2 - PCI Express Lane 1<br>hdin[p,n]_3 - PCI Express Lane 1 |

| Port Name              | Direction | Clock       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hdout[p,n]_[0,1,2,3]   | Output    |             | PCI Express 2.5 Gbps CML outputs for lanes 0,1,2, and 3.<br>The port "flip_lanes" is used to define the connection of<br>PCS/SERDES channel to PCI Express lane.<br>flip_lanes=0<br>hdout[p,n]_0 - PCI Express Lane 0<br>hdout[p,n]_1 - PCI Express Lane 1<br>hdout[p,n]_2 - PCI Express Lane 2<br>hdout[p,n]_3 - PCI Express Lane 3<br>flip_lanes=1<br>hdout[p,n]_0 - PCI Express Lane 3<br>hdout[p,n]_1 - PCI Express Lane 2<br>hdout[p,n]_1 - PCI Express Lane 3<br>hdout[p,n]_2 - PCI Express Lane 1<br>hdout[p,n]_2 - PCI Express Lane 1<br>hdout[p,n]_3 - PCI Express Lane 0 |

| Transmit TLP Interface |           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| tx_data_vc0[n:0]       | Input     | sys_clk_125 | x4 Transmit data bus<br>[63:56] Byte N<br>[55:48] Byte N+1<br>[47:40] Byte N+2<br>[39:32] Byte N+3<br>[31:24] Byte N+4<br>[23:16] Byte N+5<br>[15: 8] Byte N+6<br>[7: 0] Byte N+7                                                                                                                                                                                                                                                                                                                                                                                                  |

|                        |           |             | x1 Transmit data bus<br>[15:8] Byte N<br>[7:0] Byte N+1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

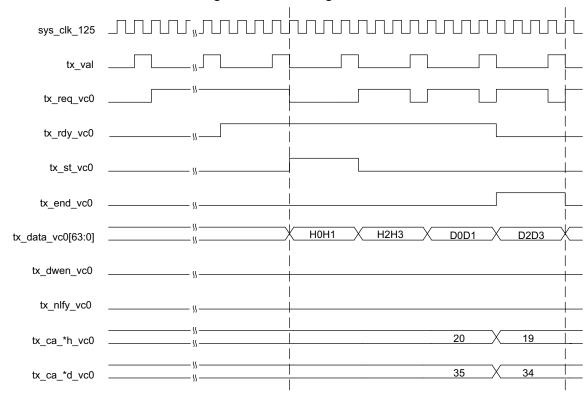

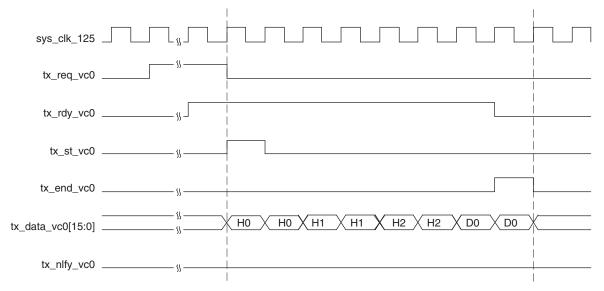

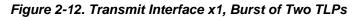

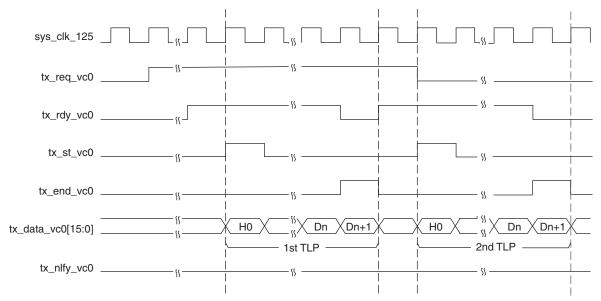

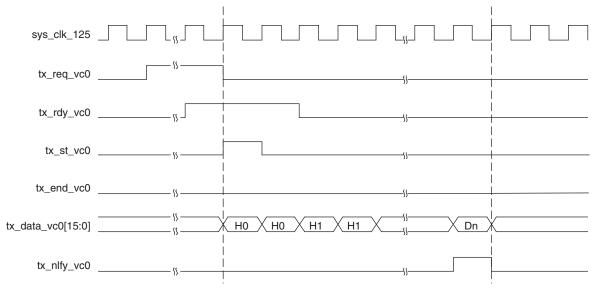

| tx_req_vc0             | Input     | sys_clk_125 | Active High transmit request. This port is asserted when<br>the user wants to send a TLP. If several TLPs will be pro-<br>vided in a burst, this port can remain High until all TLPs<br>have been sent.                                                                                                                                                                                                                                                                                                                                                                            |

| tx_rdy_vc0             | Output    | sys_clk_125 | Active High transmit ready indicator. Tx_st should be pro-<br>vided next clock cycle after tx_rdy is High.This port will go<br>Low between TLPs.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| tx_st_vc0              | Input     | sys_clk_125 | Active High transmit start of TLP indicator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| tx_end_vc0             | Input     | sys_clk_125 | Active High transmit end of TLP indicator. This signal must go Low at the end of the TLP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| tx_nlfy_vc0            | Input     | sys_clk_125 | Active High transmit nullify TLP. Can occur anywhere dur-<br>ing the TLP. If tx_nlfy_vc0 is asserted to nullify a TLP the<br>tx_end_vc0 port should not be asserted. The tx_nlfy_vc0<br>terminates the TLP.                                                                                                                                                                                                                                                                                                                                                                        |

| tx_dwen_vc0            | Input     | sys_clk_125 | Active High transmit 32-bit word indicator. Used if only bits [63:32] provide valid data. This port is available only on the x4 core.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| tx_val                 | Output    | sys_clk_125 | Active High transmit clock enable. When a x4 is down-<br>graded to a x1, this signal is used as the clock enable to<br>downshift the transmit bandwidth. This port is available only<br>on the x4 core.                                                                                                                                                                                                                                                                                                                                                                            |

| Port Name                     | Direction | Clock       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tx_ca_[ph,nph,cplh]_vc0[8:0]  | Output    | sys_clk_125 | Transmit Interface credit available bus. This port will decre-<br>ment as TLPs are sent and increment as UpdateFCs are<br>received.<br>Ph - Posted header<br>Nph - Non-posted header<br>Cplh - Completion header<br>This credit interface is only updated when an UpdateFC<br>DLLP is received from the PCI Express line.<br>[8] - This bit indicates the receiver has infinite credits. If this<br>bit is High then bits. [7:0] should be ignored. [7:0] - The<br>amount of credits available at the receiver. |

| tx_ca_[pd,npd,cpld]_vc0[12:0] | Output    | sys_clk_125 | Transmit Interface credit available bus.<br>This port will decrement as TLPs are sent and increment as<br>UpdateFCs are received.<br>pd - posted data<br>npd - non-posted data<br>cpld - completion data<br>[12] - This bit indicates the receiver has infinite credits. If<br>this bit is High, then bits [11:0] should be ignored.<br>[11:0] - The amount of credits available at the receiver.                                                                                                               |

| Port Name                                     | Direction | Clock       | Description                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------|-----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receive TLP Interface                         |           |             |                                                                                                                                                                                                                                                                                                                                                |

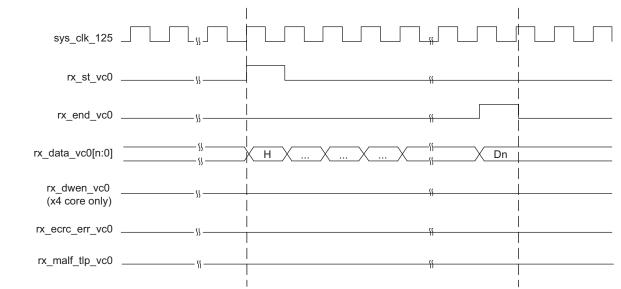

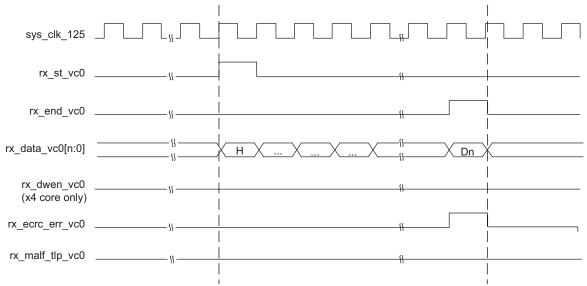

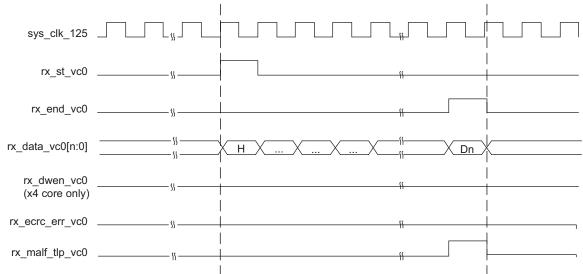

| rx_data_vc0[n:0]                              | Output    | sys_clk_125 | x4 Receive data bus<br>[63:56] Byte N<br>[55:48] Byte N+1<br>[47:40] Byte N+2<br>[39:32] Byte N+3<br>[31:24] Byte N+4<br>[23:16] Byte N+5<br>[15: 8] Byte N+6<br>[7: 0] Byte N+7<br>x1 Receive data bus<br>[15:8] Byte N<br>[7:0] Byte N+1                                                                                                     |

| rx_st_vc0                                     | Output    | sys_clk_125 | Active High receive start of TLP indicator.                                                                                                                                                                                                                                                                                                    |

| rx_end_vc0                                    | Output    | sys_clk_125 |                                                                                                                                                                                                                                                                                                                                                |

| rx_dwen_vc0                                   | Output    | sys_clk_125 | Active High 32-bit word indicator. Used if only bits [63:32] contain valid data. This port is available only on the x4 core.                                                                                                                                                                                                                   |

| rx_ecrc_err_vc0                               | Output    | sys_clk_125 | Active High ECRC error indicator. Indicates a ECRC error<br>in the current TLP.<br>This port is available only if ECRC feature is selected while<br>generating the IP core.                                                                                                                                                                    |

| rx_pois_tlp_vc0                               | Output    | sys_clk_125 | Active High poisoned TLP indicator. Asserted if<br>"poisoned (EP) " bits is set in any TLP with data.                                                                                                                                                                                                                                          |

| rx_malf_tlp_vc0                               | Output    | sys_clk_125 | Active High malformed TLP indicator. Indicates a problem with the current TLPs length or format.                                                                                                                                                                                                                                               |

| [ph,pd, nph,npd,cplh,cpld]<br>_buf_status_vc0 | Input     | sys_clk_125 | Active High user buffer full status indicator. When asserted,<br>an UpdateFC will be sent for the type specified as soon as<br>possible without waiting for the UpdateFC timer to expire.                                                                                                                                                      |

| [ph,nph,cplh]_processed_vc0                   | Input     | sys_clk_125 | Active High indicator to inform the IP core of how many<br>credits have been processed. Each clock cycle High counts<br>as one credit processed. The core will generate the<br>required UpdateFC DLLP when either the UpdateFC timer<br>expires or enough credits have been processed.                                                         |

| [pd,npd,cpld]_processed_vc0                   | Input     | sys_clk_125 | Active High enable for [pd, npd,cpld]_num_vc0 port. The user should place the number of data credits processed on the [pd, npd,cpld]_num_vc0 port and then assert [pd, npd]_processed_vc0 for one clock cycle. The core will generate the required UpdateFC DLLP when either the UpdateFC timer expires or enough credits have been processed. |

| [pd,npd]_num_vc0[7:0]                         | Input     | sys_clk_125 | This port provides the number of PD or NPD or CPLD cred-<br>its processed. It is enabled by the [pd,<br>npd,cpld]_processed_vc0 port.                                                                                                                                                                                                          |

| Control and Status                            | ı         | •           | ·                                                                                                                                                                                                                                                                                                                                              |

|                                               |           | PHYSICAL    | LAYER                                                                                                                                                                                                                                                                                                                                          |

| flip_lanes                                    | Input     | Async       | Reverses the lane connections to the SERDES. This func-<br>tion is used to provide flexibility for the PCB layout. The<br>"Locating" section later in this document describes how this<br>function can be used.<br>0-Lane 0 connects to SERDES Channel 0, etc.<br>1-Lane 0 connects to SERDES Channel 3, etc.                                  |

| Port Name            | Direction | Clock | Description                                                                                                                                                                                                         |  |

|----------------------|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| phy_ltssm_state[3:0] | Output    |       | PHY Layer LTSSM current state<br>0000 - Detect<br>0001 - Polling<br>0010 - Config<br>0011 - L0<br>0100 - L0s<br>0101 - L1<br>0110 - L2<br>0111 - Recovery<br>1000 - Loopback<br>1001 - Hot Reset<br>1010 - Disabled |  |

| Port Name               | Direction | Clock       | Description                                                                                                                                                                                                         |

|-------------------------|-----------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| phy_ltssm_substate[2:0] | Output    | sys_clk_125 | PHY Layer LTSSM current sub state. Each major LTSSM state has a series of sub states.                                                                                                                               |

|                         |           |             | When phy_ltssm_state=DETECT<br>000 - DET_WAIT<br>001 - DET_QUIET<br>010 - DET_GODET1<br>011 - DET_ACTIVE1<br>100 - DET_WAIT12MS<br>101 - DET_GODET2<br>110 - DET_ACTIVE2<br>111 - DET_EXIT                          |

|                         |           |             | When phy_Itssm_state=POLLING<br>000 - POL_WAIT<br>001 - POL_ACTIVE<br>010 - POL_COMPLIANCE<br>011 - POL_CONFIG<br>100 - POL_EXIT                                                                                    |

|                         |           |             | When phy_ltssm_state=CONFIG<br>000 - CFG_WAIT<br>001 - CFG_LINK_WIDTH_ST<br>010 - CFG_LINK_WIDTH_ACC<br>011 - CFG_LANE_NUM_WAIT<br>100 - CFG_LANE_NUM_ACC<br>101 - CFG_COMPLETE<br>110 - CFG_IDLE<br>111 - CFG_EXIT |

|                         |           |             | When phy_ltssm_state=L0<br>000 - L0_WAIT<br>001 - L0_L0<br>010 - L0_L0RX<br>011 - L0_L0TX<br>100 - L0_EIDLE_0<br>101 - L0_EIDLE_1<br>110 - L0_EXIT                                                                  |

|                         |           |             | When phy_ltssm_state=L0s<br>000 - L0s_RX_WAIT<br>001 - L0s_RX_ENTRY<br>010 - L0s_RX_IDLE<br>011 - L0s_RX_FTS<br>100 - L0s_RX_EXIT                                                                                   |

|                         |           |             | When phy_ltssm_state=L1<br>000 - L1_WAIT<br>001 - L1_ENTRY<br>010 - L1_IDLE<br>011 - L1_EXIT                                                                                                                        |

|                         |           |             | When phy_ltssm_state=L2<br>000 - L2_WAIT<br>001 - L2_IDLE                                                                                                                                                           |

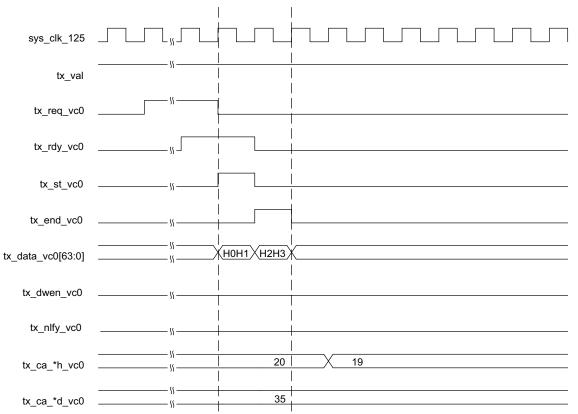

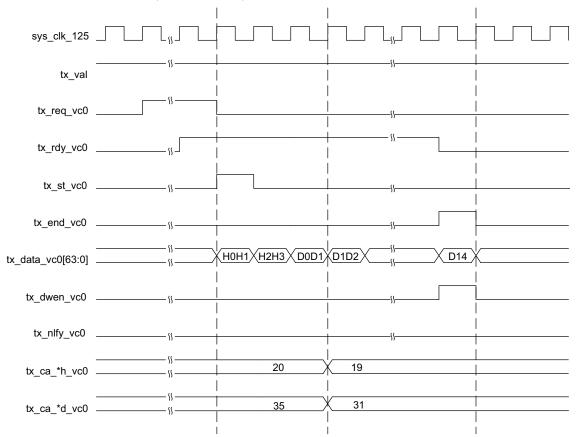

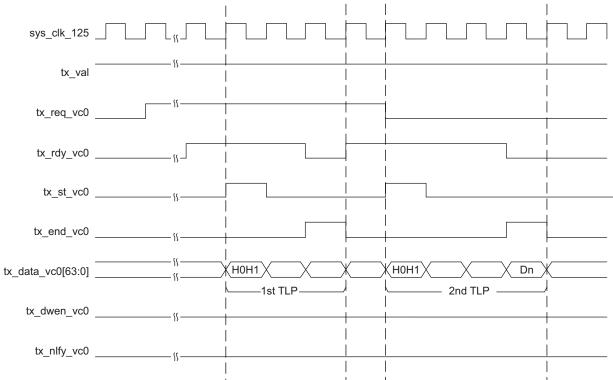

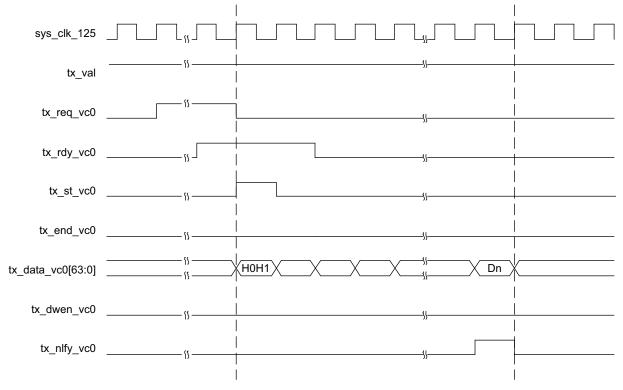

| phy_cfgln_sum[2:0]      | Output    | sys_clk_125 | Link Width<br>000 - No link defined<br>001 - Link width = 1<br>100 - Link width = 4                                                                                                                                 |