XAUI IP Core User's Guide

# **Table of Contents**

| Chapter 1. Introduction                                      | 4    |

|--------------------------------------------------------------|------|

| Quick Facts                                                  | 4    |

| Features                                                     | 4    |

| Chapter 2. Functional Description                            | 6    |

| XAUI IP Core I/O                                             | 9    |

| Functional Description                                       | . 10 |

| XGMII and Slip Buffers                                       | . 14 |

| XAUI-to-XGMII Translation (Receive Interface)                | . 15 |

| XGMII-to-XAUI Translation (Transmit Interface)               | . 16 |

| Management Data Input/Output (MDIO) Interface (Optional)     |      |

| Management Frame Structure                                   |      |

| Register Descriptions                                        |      |

| Input/Output Timing                                          |      |

| XGMII Specifications                                         |      |

| XAUI Specifications                                          |      |

| MDIO Specifications                                          |      |

| Chapter 3. Parameter Settings                                |      |

| XAUI IP Configuration Dialog Box                             |      |

| Parameter Descriptions                                       |      |

| Tx Slip Buffer                                               |      |

| Rx Slip Buffer                                               |      |

| MDIO                                                         |      |

| Behavioral Model                                             |      |

| Netlist [.ngo]                                               |      |

| Evaluation Directory                                         |      |

| Tools Support                                                |      |

| Chapter 4. IP Core Generation                                |      |

| Licensing the IP Core                                        |      |

| Getting Started                                              |      |

| IPexpress-Created Files and Top Level Directory Structure    |      |

| Instantiating the Core                                       |      |

| Running Functional Simulation                                |      |

| Synthesizing and Implementing the Core in a Top-Level Design |      |

| Hardware Evaluation                                          |      |

| Enabling Hardware Evaluation in Diamond                      |      |

| Enabling Hardware Evaluation in ispLEVER                     |      |

| Updating/Regenerating the IP Core                            |      |

| Regenerating an IP Core in Diamond                           |      |

| Regenerating an IP Core in ispLEVER                          |      |

| Chapter 5. Support Resources                                 |      |

| Lattice Technical Support                                    |      |

| Online Forums                                                |      |

| Telephone Support Hotline                                    |      |

| E-mail Support                                               |      |

| Local Support                                                |      |

| Internet                                                     |      |

| References                                                   |      |

| LatticeECP3                                                  |      |

| LatticeECP2M                                                 |      |

|                                                              | -    |

© 2012 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## Lattice Semiconductor

## **Table of Contents**

| Revision History                 |  |

|----------------------------------|--|

|                                  |  |

| Appendix A. Resource Utilization |  |

| LatticeECP2M FPGAs               |  |

| Ordering Part Number             |  |

| Jitter and XAUI Compliance       |  |

| LatticeECP3 FPGAs                |  |

| Ordering Part Number             |  |

| Jitter and XAUI Compliance       |  |

# Chapter 1: Introduction

The 10Gb Ethernet Attachment Unit Interface (XAUI) IP Core User's Guide for the LatticeECP2M<sup>™</sup> and LatticeECP3<sup>™</sup> FPGAs provides a solution for bridging between XAUI and 10-Gigabit Media Independent Interface (XGMII) devices. This IP core implements 10Gb Ethernet Extended Sublayer (XGXS) capabilities in soft logic that together with PCS and SERDES functions implemented in the FGPA provides a complete XAUI-to-XGMII solution.

The XAUI IP core package comes with the following documentation and files:

- Protected netlist/database

- Behavioral RTL simulation model

- · Source files for instantiating and evaluating the core

The XAUI IP core supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited period of time (approximately four hours) without requiring the purchase on an IP license. It may also be used to evaluate the core in hardware in user-defined designs. Details for using the hardware evaluation capability are described in the Hardware Evaluation section of this document.

## **Quick Facts**

Table 1-1 gives quick facts about the XAUI IP core.

| Table         | 1-1. | XAUI    | IP | Core | Quick | Facts  |

|---------------|------|---------|----|------|-------|--------|

| <i>i</i> anic |      | /// /// |    | 00.0 | quion | , aoto |

| Γ                    |                          | XAUI IP Con                                                  | figuration               |  |

|----------------------|--------------------------|--------------------------------------------------------------|--------------------------|--|

|                      |                          | Across All IP co                                             | onfigurations            |  |

| Core Requirements    | FPGA Families Supported  | Lattice ECP3, Lattice ECP2M                                  |                          |  |

| Core Requirements    | Minimal Device Supported | LFE3-17E-7FN256C                                             | LFE2M20E-6F256C          |  |

|                      | Data Path Width          | 72 bits                                                      | 72 bits                  |  |

| Resource Utilization | LUTs                     | 1700-2700                                                    | 1800-2800                |  |

|                      | sysMEM EBRs              | 0-4                                                          | 0-4                      |  |

|                      | Registers                | 1500-2700                                                    | 1500-2700                |  |

|                      | Lattice Implementation   | Diamond <sup>®</sup> 1.0 or i                                | spLEVER <sup>®</sup> 8.1 |  |

| Design Tool Support  | Synthesis                | Synopsys <sup>®</sup> Synplify™ Pro f                        | or Lattice D-2009.12L-1  |  |

|                      | Synthesis                | Mentor Graphics <sup>®</sup> Precision™ RTL                  |                          |  |

|                      | Simulation               | Aldec <sup>®</sup> Active-HDL™ 8.2 Lattice Edition           |                          |  |

|                      | Sinuation                | Mentor Graphics ModelSim <sup>™</sup> SE 6.3F (Verilog only) |                          |  |

## **Features**

- XAUI compliant functionality supported by embedded SERDES PCS functionality implemented in the LatticeECP2M and LatticeECP3, including four channels of 3.125 Gbps serializer/deserializer with 8b10b encoding/decoding.

- Complete 10Gb Ethernet Extended Sublayer (XGXS) solution based on LatticeECP2M and LatticeECP3 FPGA.

- Soft IP targeted to the FPGA implements XGXS functionality conforming to IEEE 802.3-2005, including:

- 10 GbE Media Independent Interface (XGMII).

- Optional slip buffers for clock domain transfer to/from the XGMII interface.

## Lattice Semiconductor

- Complete translation between XGMII and XAUI PCS layers, including 8b10b encoding and decoding of Idle, Start, Terminate, Error and Sequence code groups and sequences, and randomized Idle generation in the XAUI transmit direction.

- XAUI compliant lane-by-lane synchronization.

- Lane deskew functionality.

- Interface with the high-speed SERDES block embedded in the LatticeECP2M and LatticeECP3 that implements a standard XAUI.

- Optional standard compliant MDIO/MDC interface.

- Aldec and ModelSim simulation models and test benches provided for free evaluation.

Chapter 2:

XAUI is a high-speed interconnect that offers reduced pin count and has the ability to drive up to 20 inches of PCB trace on standard FR-4 material. Each XAUI comprises four self-timed 8b10b encoded serial lanes each operating at 3.125 Gbps and thus is capable of transferring data at an aggregate rate of 10 Gbps.

XGMII is a 156 MHz Double Data Rate (DDR), parallel, short-reach interconnect interface (typically less than 2 inches). It supports interfacing to 10 Gbps Ethernet Media Access Control (MAC) and PHY devices.

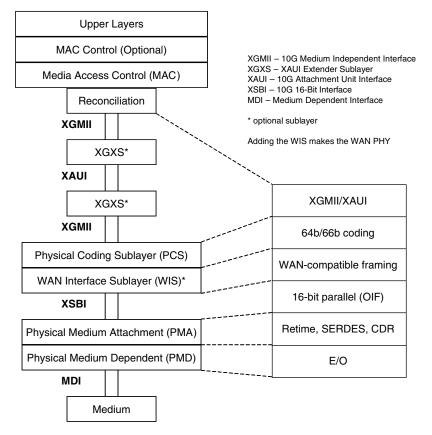

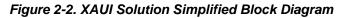

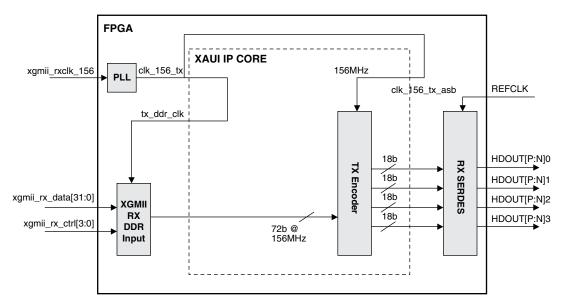

The locations of XAUI and XGXS in the 10GbE protocol stack are shown in Figure 2-1. A simplified block diagram of the XAUI solution is shown in Figure 2-2. The XGMII interface, XGXS coding and state machines and XAUI multichannel alignment capabilities are implemented in the FPGA array. The XAUI 8b10b coding and SERDES functionality are supported by the embedded SERDES\_PCS block. An optional MDIO interface module is also implemented in the FPGA array.

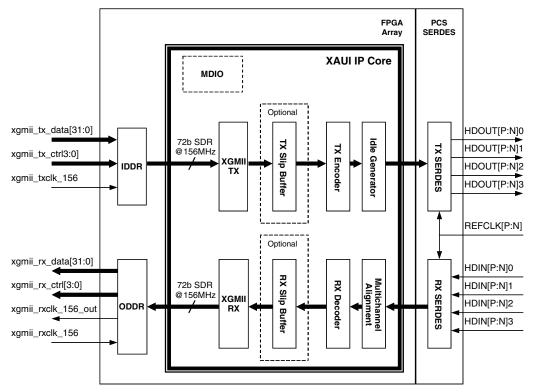

Figure 2-3 shows the I/O interface view of the XAUI IP core.

Figure 2-1. XAUI and XGXS Locations in 10 GbE Protocol Stack

### Figure 2-3. XAUI IP Core I/O

# XAUI IP Core I/O

Table 2-1 defines all I/O interface ports available in this core.

## Table 2-1. IP Core I/O and Signal Definitions

| Name               | Width (Bits) | Direction | Description                                                                                                 |  |

|--------------------|--------------|-----------|-------------------------------------------------------------------------------------------------------------|--|

| All Configurations | 5            |           |                                                                                                             |  |

| reset_n            | 1            | I         | Active-low asynchronous reset                                                                               |  |

| clk_156_asb_tx     | 1            | I         | 156MHz XAUI transmit clock (from PCS)                                                                       |  |

| clk_156_asb_rx     | 1            | I         | 156MHz XAUI receive clock (from PCS)                                                                        |  |

| rwdata_lane0       | 16           | I         | XAUI receive data channel 0 (from PCS)                                                                      |  |

| rwdata_lane1       | 16           | Ι         | XAUI receive data channel 1 (from PCS)                                                                      |  |

| rwdata_lane2       | 16           | Ι         | XAUI receive data channel 2 (from PCS)                                                                      |  |

| rwdata_lane3       | 16           | Ι         | XAUI receive data channel 3 (from PCS)                                                                      |  |

| rcomma_lane0       | 2            | Ι         | XAUI receive control channel 0 (from PCS)                                                                   |  |

| rcomma_lane1       | 2            | Ι         | XAUI receive control channel 1 (from PCS)                                                                   |  |

| rcomma_lane2       | 2            | I         | XAUI receive control channel 2 (from PCS)                                                                   |  |

| rcomma_lane3       | 2            | I         | XAUI receive control channel 3 (from PCS)                                                                   |  |

| twdata_lane0       | 16           | 0         | XAUI transmit data channel 0 (to PCS)                                                                       |  |

| twdata_lane1       | 16           | 0         | XAUI transmit data channel 1 (to PCS)                                                                       |  |

| twdata_lane2       | 16           | 0         | XAUI transmit data channel 2 (to PCS)                                                                       |  |

| twdata_lane3       | 16           | 0         | XAUI transmit data channel 3 (to PCS)                                                                       |  |

| tcomma_lane0       | 2            | 0         | XAUI transmit control channel 0 (to PCS)                                                                    |  |

| tcomma_lane1       | 2            | 0         | XAUI transmit control channel 1 (to PCS)                                                                    |  |

| tcomma_lane2       | 2            | 0         | XAUI transmit control channel 2 (to PCS)                                                                    |  |

| tcomma_lane3       | 2            | 0         | XAUI transmit control channel 3 (to PCS)                                                                    |  |

| rx_ddr_clk         | 1            | 0         | DDR clock from IP Core to the XGMII TX direction                                                            |  |

| tx_ddr_clk         | 1            | 0         | DDR clock from IP Core to the XGMII receive direction                                                       |  |

| tx_data            | 64           | I         | IP Core transmit data from XGMII RX                                                                         |  |

| tx_ctrl            | 8            | I         | IP Core transmit control from XGMII RX                                                                      |  |

| rx_data            | 64           | 0         | Receive data from core and sent to XGMII TX                                                                 |  |

| rx_ctrl            | 8            | 0         | Receive control from core and sent to XGMII TX                                                              |  |

| With Optional Rx   | Slip Buffer  |           |                                                                                                             |  |

| clk_156_rx         | 1            | Ι         | 156MHz XGMII TX clock                                                                                       |  |

| rx_fifo_empty      | 1            | 0         | Rx slip buffer FIFO empty flag                                                                              |  |

| rx_fifo_full       | 1            | 0         | Rx slip buffer FIFO full flag                                                                               |  |

| With Optional Tx   | Slip Buffer  |           |                                                                                                             |  |

| clk_156_tx         | 1            | Ι         | 156MHz XGMII RX clock                                                                                       |  |

| tx_fifo_empty      | 1            | 0         | Tx slip buffer FIFO empty flag                                                                              |  |

| tx_fifo_full       | 1            | 0         | Tx slip buffer FIFO full flag                                                                               |  |

| No MDIO Option     |              |           |                                                                                                             |  |

| mca_resync         | 1            | I         | XAUI multi-channel alignment resynchronization request                                                      |  |

| mca_sync_status    | 1            | 0         | XAUI multi-channel alignment status.<br>1 = All XAUI channels are aligned 0 = XAUI channels are not aligned |  |

| MDIO Option        | 1            |           |                                                                                                             |  |

| mdin               | 1            | I         | MDIO serial input data                                                                                      |  |

| mdc                | 1            | I         | MDIO input clock                                                                                            |  |

| Name         | Width (Bits) | Direction | Description                    |

|--------------|--------------|-----------|--------------------------------|

| mdout        | 1            | 0         | MDIO serial output data        |

| mdtri        | 1            | 0         | Tristate control for MDIO port |

| scireaddata  | 8            | Ι         | SCI read data (from PCS)       |

| sciwritedata | 8            | 0         | SCI write data (to PCS)        |

| sciwstn      | 1            | 0         | SCI write strobe               |

| scird        | 1            | 0         | SCI read probe                 |

| sciaddr      | 6            | 0         | SCI address bus                |

| scisel       | 4            | 0         | SCI quad select                |

| scien        | 4            | 0         | SCI quad enable                |

| sciselaux    | 1            | 0         | SCI auxiliary select           |

| scienaux     | 1            | 0         | SCI auxiliary enable           |

| gpi          | 4            | I         | General purpose input          |

| gpo          | 4            | 0         | General purpose output         |

Table 2-1. IP Core I/O and Signal Definitions (Continued)

## **Functional Description**

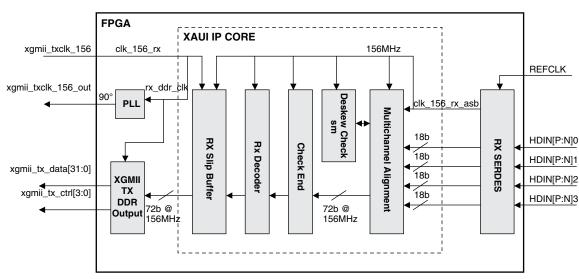

The XAUI receive path, shown in Figure 2-4, is the data path from the XAUI to the XGMII interface. In the receive direction, 8b10b encoded data received at the XAUI SERDES interface is demultiplexed and passed to the multichannel alignment block, that compensates for lane-to-lane skew between the four SERDES channels as specified in 802.3-2005. The aligned data streams are passed to decoder logic, where it is translated and mapped to the XGMII data format. The output of the encoder is then passed through an optional slip buffer that compensates for XAUI and XGMII timing differences and then to the XGMII 36-bit (32-bit data and four control bits) 156 MHz DDR external interface.

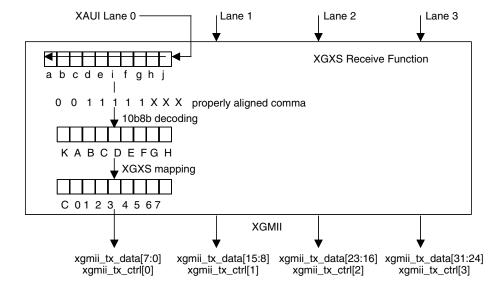

The receive direction data translations are shown in Figure 2-5. The 8b10b symbols on each XAUI lane are converted to XGMII format and passed to the corresponding XGMII lane. The XGMII comprises four lanes, labeled [0:3], and one clock in both transmit and receive directions. Each lane includes eight data signals and one control signal. Double Data Rate (DDR) transmission is utilized, with the data and control signals sampled on both the rising and falling edges of a 156.25 MHz (nom) clock for an effective data transfer rate of 2.5Gbps.

### Figure 2-4. XAUI IP Core Receive Path

With Optional Receive Direction Slip Buffer

Without Optional Receive Direction Slip Buffer

#### Figure 2-5. XAUI IP Core Receive Direction Data Translations

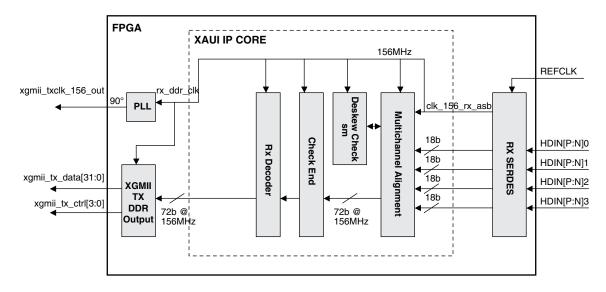

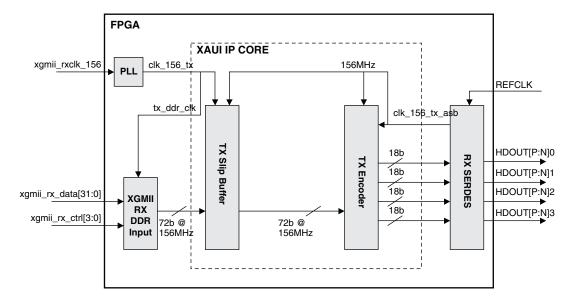

The transmit path, shown in Figure 2-6, is the data path from XGMII to XAUI. In the transmit direction, the 36-bit DDR data and control received at the XGMII are converted to single-edge timing and passed through an optional slip buffer that compensates for XAUI and XGMII timing differences. The XGMII data and control are then passed to the TX encoder, where they are translated and mapped to the 8b10b XAUI transmission code and then passed to the SERDES interface.

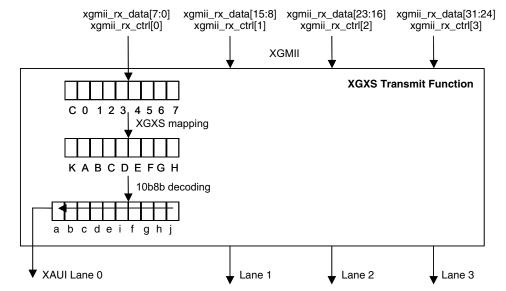

The transmit direction data translations are shown in Figure 2-7. Data and control from each of the four XGMII lanes are translated and mapped to the corresponding XAUI lanes. The transmit encoder includes the transmit idle generation state machine that generates a random sequence of /A/, /K/ and /R/ code groups as specified in IEEE 802.3-2005.

### Figure 2-6. XAUI IP Core Transmit Path

With Optional Transmit Direction Slip Buffer

Without Optional Transmit Direction Slip Buffer

#### Figure 2-7. XAUI IP Core Transmit Direction Data Translations

### **XGMII and Slip Buffers**

The 10Gigabit Media Independent Interface (XGMII) supported by the XAUI IP core solution conforms to Clause 46 of IEEE 802.3-2005. The XGMII is composed of independent transmit and receive paths. Each direction uses 32 data signals, four control signals and a clock. The 32 data signals in each direction are organized into four lanes of eight signals each. Each lane is associated with a control signal as shown in Table 2-2.

| Tx control (xgmii_rx_ctrl)<br>Rx control (xgmii_tx_ctrl) | XAUI Lane                                       |

|----------------------------------------------------------|-------------------------------------------------|

| [0]                                                      | 0                                               |

| [1]                                                      | 1                                               |

| [2]                                                      | 2                                               |

| [3]                                                      | 3                                               |

|                                                          | Rx control (xgmii_tx_ctrl)<br>[0]<br>[1]<br>[2] |

Table 2-2. XGMII Transmit and Receive Lane Associations<sup>1</sup>

1. The XGMII TX signals are XGXS inputs to the transmit path (XGMII to XAUI). The XGMII RX signals are XGXS outputs of the receive path (XAUI to XGMII).

The XGMII supports Double Data Rate (DDR) transmission (i.e., the data and control input signals are sampled on both the rising and falling edges of the corresponding clock). The XGXS XGMII input (RX) data is sampled based on an input clock typically sourced from the XGMII device running at 156.25 MHz, 1/64th of the 10Gb data rate and is transmitted by the IP transmit part. The XGXS XGMII output (TX) data is referenced to a forwarded clock that is phase locked to a 156.25 MHz (typical) input reference, and the data is received from the IP receiver part.

The control signal for each lane is de-asserted when a data octet is being sent on the corresponding lane and asserted when a control character is being sent. Supported control octet encodings are shown in Table 2-3. All data and control signals are passed directly to/from the 8b10b encoding/decoding blocks with no further processing by the XGMII block. Note that the packet Start control word is only valid on lane 0.

| Control | Data        | Description                     |

|---------|-------------|---------------------------------|

| 0       | 0x00 - 0xFF | Normal data transmission        |

| 1       | 0x00 - 0x06 | Reserved                        |

| 1       | 0x07        | Idle                            |

| 1       | 0x08 - 0x9B | Reserved                        |

| 1       | 0x9C        | Sequence (only valid on lane 0) |

| 1       | 0x9D - 0xFA | Reserved                        |

| 1       | 0xFB        | Start (only valid on lane 0)    |

| 1       | 0xFC        | Reserved                        |

| 1       | 0xFD        | Terminate                       |

| 1       | 0xFE        | Error                           |

| 1       | 0xFF        | Reserved                        |

### Table 2-3. XGMII Control Encoding

The XGMII blocks incorporate optional slip buffers that accommodate small differences between XGMII and XAUI timing by inserting or deleting idle characters. The slip buffer is implemented as a 256 x 72 FIFO. There are four flags out of the FIFO: full, empty, partially full, and partially empty. The partially empty flag is used as the watermark to start reading from the FIFO. If the difference between write and read pointers falls below the partially empty watermark and the entire packet has been transmitted, idle characters are inserted until the partially full watermark is reached. No idle is inserted during data transmission.

## XAUI-to-XGMII Translation (Receive Interface)

A block diagram of the XAUI IP core receive data path was shown previously in Figure 2-4. The IP receive interface converts the incoming XAUI stream into XGMII-compatible signals. At the embedded core interface, the IP core receive block receives 72 bits of data at 156 MHz (64 bits of data, 8 bits of control) from four XAUI lanes. Data from the embedded core are first passed to the RX multi-channel aligner block to de-skew the four XAUI lanes.

The multi-channel alignment block consists of four 16-byte deep FIFOs to individually buffer each XAUI lane. The multi-channel alignment block searches for the presence of the alignment character /A/ in each XAUI lane, and begins storing the data in the FIFO when the /A/ character is detected in a lane. When the alignment character has been detected in all four XAUI lanes, the data is retrieved from each FIFO so that all of the alignment characters /A/ are aligned across all four XAUI lanes. Once synchronization is achieved, the block does not resynchronize until a resynchronization request is issued.

The data from the RX multi-channel alignment is passed to the RX decoder. The RX decoder block converts the XAUI code to the corresponding XGMII code. Table 2-4 shows the 8b10b code points. Table 2-5 shows the code mapping between the two domains in the receive direction. XAUI /A/, /R/, /K/ characters are translated into XGMII Idle (/I/) characters.

Data from the RX decoder block is written to the RX slip buffer. As mentioned previously, the slip buffers are required to compensate for differences in the write and read clocks derived from the XAUI and XGMII reference clocks, respectively. Clock compensation is achieved by deleting (not writing) idle cells into the buffer when the "almost full" threshold is reached and by inserting (writing) additional idle cells into the buffer when the "almost empty" threshold is reached. All idle insertion/deletion occurs during the Inter-Packet Gap (IPG) between data frames.

| Symbol | Name      | Function                                   | Code Group |

|--------|-----------|--------------------------------------------|------------|

| /A/    | Align     | Lane Alignment (XGMII Idle)                | K28.3      |

| /K/    | Sync      | Code-Group Alignment (XGMII Idle)          | K28.5      |

| /R/    | Skip      | Clock Tolerance Compensation (XGMII Idle)  | K28.0      |

| /S/    | Start     | Start of Packet Delimiter (in Lane 0 only) | K27.7      |

| /T/    | Terminate | End of Packet Delimiter                    | K29.7      |

| /E/    | Error     | Error Propagation                          | K30.7      |

| /Q/    | Sequence  | Link Status Message Indicator              | K28.4      |

| /d/    | Data      | Information Bytes                          | Dxx.x      |

### Table 2-4. XAUI 8b10b Code Points

### Table 2-5. XAUI 8b10b to XGMII Code Mapping

| 8b10b Data from<br>Embedded Core [7:0] | XGMII Data [7:0]   | XGMII Control [3:0] |

|----------------------------------------|--------------------|---------------------|

| Dxx.x                                  | 0x00-0xFF (Data)   | 0                   |

| K28.5 (0xBC)                           | 0x07 (Idle)        | 1                   |

| K28.3 (0x7C)                           | 0x07 (Idle)        | 1                   |

| K28.0 (0x1C)                           | 0x07 (Idle)        | 1                   |

| K27.7 (0xFB)                           | 0xFB (Start)       | 1                   |

| K29.7 (0xFD)                           | 0xFD (Terminate)   | 1                   |

| K30.7 (0xFE)                           | 0xFE (Error)       | 1                   |

| K28.4 (0x9C)                           | 0x9C (Ordered Set) | 1                   |

### XGMII-to-XAUI Translation (Transmit Interface)

A block diagram of the XAUI IP core transmit data path was shown previously in Figure 2-6. The TX interface converts the incoming XGMII data into XAUI-compatible characters. 36-bit XGMII DDR input data and control signals are initially converted to a 72-bit bus based on a single edge 156MHz clock. The data and control read are then passed into an optional TX slip buffer identical to the one used for the RX interface.

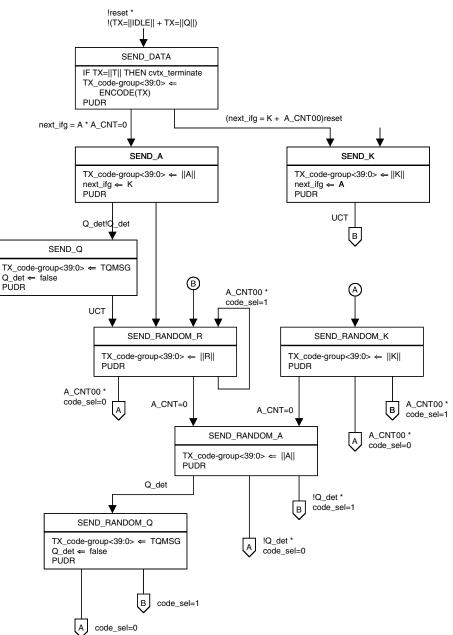

After the slip buffer, the XGMII formatted transmit data and control are input to the TX encoder that converts the XGMII characters into 8b10b format as shown in Table 7. The idle generation state machine in the TX encoder converts XGMII /l/ characters to a random sequence of XAUI /A/, /K/ and /R/ characters as specified in IEEE 802.3-2005. XGMII idles are mapped to a random sequence of code groups to reduce radiated emissions. The /A/ code groups support XAUI lane alignment and have a guaranteed minimum spacing of 16 code-groups. The /R/ code groups are used for clock compensation. The /K/ code groups contain the 8b10b comma sequence.

|             | XGMII       | XAUI                                                                                                        |

|-------------|-------------|-------------------------------------------------------------------------------------------------------------|

| Idle        | /l/ = 0x07  | Randomized /A/, /R/, /K/ Sequence<br>/A/ = K28.3 = 0x7C<br>/R/ = K28.0 = 0x1C<br>/K/ = K28.5 = 0xBC (Comma) |

| Start       | /S/ = 0xFB  | /S/ = 0xFB                                                                                                  |

| Error       | /E/ = 0xFE  | /E/ = 0xFE                                                                                                  |

| Terminate   | /T/ = 0xFD  | /T/ = 0xFD                                                                                                  |

| Ordered Set | /Q/ = 0x9C  | /Q/ = 0x9C                                                                                                  |

| Data        | Control = 0 | Control = 0                                                                                                 |

## Lattice Semiconductor

The random /A/, /R/, /K/ sequence is generated as specified in section 48.2.5.2.1 of IEEE 802.3-2005 and shown in the state machine diagram given in Figure 2-8. In addition to idle generation, the state machine also forwards sequences of ||Q|| ordered sets used for link status reporting. These sets have the XGMII sequence control character on lane 0 followed by three data characters in XGMII lanes 1 through 3. Sequence ordered-sets are only sent following an ||A|| ordered set.

The random selection of /A/, /K/, and /R/ characters is based on the generation of uniformly distributed random integers derived from a PRBS. Minimum ||A|| code group spacing is determined by the integer value generated by the PRBS (A\_cnt in Figure 2-8). ||K|| and ||R|| selection is driven by the value of the least significant bit of the generated integer value (code\_sel in Figure 2-8). The idle generation state machine specified in IEEE 802.3-2005 and shown in Figure 2-7 transitions between states based on a 312 MHz system clock. The TX encoder implemented in the XAUI IP runs at a system clock rate of 156 MHz. Thus the XGXS state machine implementation performs the equivalent of two state transitions each clock cycle.

## Management Data Input/Output (MDIO) Interface (Optional)

The MDIO interface provides access to the internal XAUI core registers. The register access mechanism corresponds to Clause 45 of IEEE 802.3-2005. The XAUI core provides access to XGXS registers 0x0000-0x0024 as specified in IEEE 802.3-2005. Additional registers in the vendor-specific address space have been allocated for implementation-specific control/status functions.

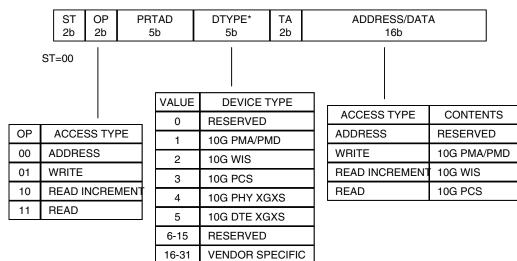

The physical interface consists of two signals: MDIO to transfer data/address/control to and from the device, and MDC, a clock up to 2.5 MHz sourced externally to provide the synchronization for MDIO. The fields of the MDIO transfer are shown in Figure 2-9.

### Figure 2-9. Fields of MDIO Protocol

\* If ST=01, this field is REGAD (register address).

### Management Frame Structure

Each management data frame consists of 64 bits. The first 32 bits are preamble consisting of 32 contiguous 1s on the MDIO. Following the preamble is the start-of-frame field (ST) which is a 00 pattern. The next field is the operation code (OP) that is shown in Figure 2-9.

The next two fields are the port address (PRTAD) and device type (DTYPE). Since the physical layer function in 10 GbE is partitioned into various logical (and possibly separate physical) blocks, two fields are used to access these blocks. The PRTAD provides the overall address to the PHY function. The first port address bit transmitted and received is the MSB of the address. The DTYPE field addresses the specific block within the physical layer function.

Device address zero is reserved to ensure that there is not a long sequence of zeros. If the ST field is 01 then the DTYPE field is replaced with REGAD (register address field of the original clause 22 specification). The XAUI core does not respond to any accesses with ST = 01.

The TA field (Turn Around) is a 2-bit turnaround time spacing between the device address field and the data field to avoid contention during a read transaction. The TA bits are treated as don't cares by the XAUI core.

During a write or address operation, the address/data field transports 16 bits of write data or register address depending on the access type. The register is automatically incremented after a read increment. The address/data field is 16 bits.

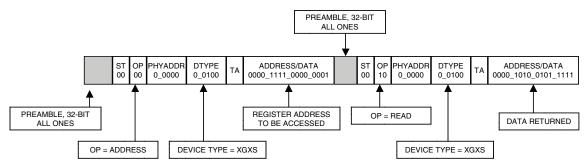

For an address cycle, this field contains the address of the register to be accessed on the next cycle. For read/write/increment cycles, the field contains the data for the register. The first bit of data transmitted and received in the address/data field is the MSB (bit 15). An example access is shown in Figure 2-10.

### Figure 2-10. Indirect Address Example

Table 2-7 shows PHY XGXS registers as described in IEEE 802.3-2005. The shaded areas are used to indicate register addresses that are specified in the draft but are not used in this implementation.

There are two vendor supported register ranges. The 4.8000h register range is used for accessing and programming the XGXS registers implemented in the programmable array. All corresponding registers are listed in Table 2-8. All PCS embedded core registers can be accessed thru the 4.9xxxh registers shown in Table 2-9, where the address is directly mapped to the PCS embedded registers.

## **Register Descriptions**

Table 2-7. Register Map for XAUI IP Core (Device Address = 4)

| Register Address | Register Name            |  |  |

|------------------|--------------------------|--|--|

| 0                | PHY XGXS Control 1       |  |  |

| 1                | PHY XGXS Status 1        |  |  |

| 2, 3             | PHY XGXS Identifier      |  |  |

| 4                | Reserved                 |  |  |

| 5                | PHY XGXS Status 2        |  |  |

| 6 - 23           | Reserved                 |  |  |

| 24               | 10G PHY XGXS Lane status |  |  |

| 25 - 32767       | Reserved                 |  |  |

| 32768 - 65535    | Vendor specific          |  |  |

| Table 2-8 | . XAUI IP | Core | Registers |

|-----------|-----------|------|-----------|

|-----------|-----------|------|-----------|

| Bit(s)       | Name                        | Description                                                                                                  | R/W     | Reset Value |

|--------------|-----------------------------|--------------------------------------------------------------------------------------------------------------|---------|-------------|

| Control 1 Re | egister                     |                                                                                                              |         |             |

| 4.0.15       | Reset                       | 1 = PHY XA reset, 0 = Normal operation                                                                       | R/W S/C | 0           |

| 4.0.14       | Loopback<br>(not supported) | Loop back functionality is supported in the PCS core.<br>The XAUI core does not provide loopback capability. | R       | 0           |

| 4.0.13       | Speed Selection             | Value always 0                                                                                               | R       | 0           |

| 4.0.12       | Reserved                    | Value always 0                                                                                               | R       | 0           |

| 4.0.11       | Low Power                   | 0= Low Power Mode 1= Normal operation This bit controls the power_down signal of the XAUI core.              | R/W     | 1           |

| 4.0.[10:7]   | Reserved                    | Value always 0                                                                                               | R       | 0           |

| 4.0.6        | Speed Selection             | Value always 0                                                                                               | R       | 0           |

| 4.0.[5:2]    | Speed Selection             | Value always 0                                                                                               | R       | 0           |

| 4.0.[1:0]    | Reserved                    | Value always 0                                                                                               | R       | 0           |

| Status 1 Reg | gister                      |                                                                                                              | •       | -           |

| 4.1.[15:8]   | Reserved                    | Value always 0                                                                                               | R       | 0           |

| Bit(s)                | Name                                          | Description                                               | R/W | Reset Value |

|-----------------------|-----------------------------------------------|-----------------------------------------------------------|-----|-------------|

| <b>ыц(s)</b><br>4.1.7 |                                               | -                                                         |     |             |

|                       | Fault (not supported)                         | 0 = No Fault condition                                    | R   | 0           |

| 4.1.[6:3]             | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.1.2                 | PHY XS TX link sta-<br>tus (not supported)    | The Link status is available in the PCS core register.    | R   | 0           |

| 4.1.1                 | Low Power Ability                             | 1 = Low Power Mode support                                | R   | 1           |

| 4.1.0                 | Reserved                                      | Value always 0                                            | R   | 0           |

| XGXS Identifie        | er Registers                                  |                                                           |     |             |

| 4.2:[15:0]            | PHY XS Identifier                             | MSB = 0x0000                                              | R   | 0           |

| 4.3:[15:0]            | PHY XS Identifier                             | LSB = 0x0004                                              | R   | 0004        |

| XGXS Reserve          | ed Register                                   |                                                           |     |             |

| 4.4.[15:1]            | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.4.0                 | 10 G Capable                                  | Value always 1                                            | R   | 1           |

| Status 1 Regis        | ster                                          |                                                           |     | 1           |

| 4.5.[15:6]            | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.5.5                 | DTE XS Present                                | Value always 0                                            | R   | 0           |

| 4.5.4                 | PHY XS Present                                | Value always 1                                            | R   | 1           |

| 4.5.3                 | PCS Present                                   | Value always 0                                            | R   | 0           |

| 4.5.2                 | WIS Present                                   | Value always 0                                            | R   | 0           |

| 4.5.1                 | PMD/PMA Present                               | Value always 0                                            | R   | 0           |

| 4.5.0                 | Clause 22 regs pres-<br>ent                   | Value always 0                                            | R   | 0           |

| XGXS Reserve          | ed Register                                   |                                                           |     |             |

| 4.6.15                | Vendor specific device present                | Value always 0                                            | R   | 0           |

| 4.6.[14:0]            | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.8.[15:14]           | Device present                                | 10 = Device responding to this address                    | R   | 10          |

| 4.8.[13:12]           | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.8.11                | Transmit Fault<br>(not supported)             | 0 = No fault of tx path                                   | R   | 0           |

| 4.8.10                | Receive Fault<br>(not supported)              | 0 = No fault of tx path                                   | R   | 0           |

| 4.8.9:0               | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.15, 4.14            | Package Identifier                            | Value always 0                                            | R   | 0           |

| 4.24.[15:13]          | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.24.12               | PHY XGXS Lane<br>Alignment<br>(not supported) | TX alignment status is available in the PCS core register | R   | 0 0         |

| 4.24.11               | Pattern Testing ability                       | 0 = Not able to generate pattern.                         | R   | 0           |

| 4.24.10               | PHY XGXS has loop<br>back capability          | 1 = Has loop back capability                              | R   | 1           |

| 4.24.[9:4]            | Reserved                                      | Value always 0                                            | R   | 0           |

| 4.24.3                | Lane 3 Sync (not<br>supported)                | Status is available from the PCS core                     | R   | 0 0         |

| 4.24.2                | Lane 2 Sync (not supported)                   | Status is available from the PCS core                     | R   | 0 0         |

#### Table 2-8. XAUI IP Core Registers (Continued)

4.24.1

Lane 1 Sync (not supported)

00

R

Status is available from the PCS core

| Bit(s)        | Name                           | Description                                                                                                                                           | R/W | Reset Value |

|---------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

| 4.24.0        | Lane 0 Sync (not<br>supported) | Status is available from the PCS core                                                                                                                 | R   | 0 0         |

| 4.25.15:3     | Reserved                       | Value always 0                                                                                                                                        | R   | 0           |

| 4.25.2        | Receive test pattern enable    | 0 = Receive test pattern not enabled                                                                                                                  | R   | 0           |

| 4.25.1:0      | Test pattern select            | 00                                                                                                                                                    | R   | 00          |

| 4.8000.[15:0] | MCA Sync Request               | Writing any value to this register triggers the MCA sync request. This register always read as 0.                                                     | R/W | 0           |

| 4.8001.15     | MCA Sync Status                | This bit provides MCA synchronization status.                                                                                                         |     | 0           |

| 4.8002.[15:8] | Unused                         | Bit [15:8] are unused                                                                                                                                 | R/W | 0           |

| 4.8002.[7:0]  | GPO                            | This field controls the General Purpose Outputs (GPO) when the MDIO is enabled. It is intended to control optional ports of the PCS core.             | R/W | 0           |

| 4.8003.[15:8] | Unused                         | Bit [15:8] are unused                                                                                                                                 |     | 0           |

| 4.8003.[7:0]  | GPI                            | This field senses the state of the General Purpose Inputs (GPI) when the MDIO is enabled. It is intended to sense the status control of the PCS core. |     | 0           |

Table 2-8. XAUI IP Core Registers (Continued)

Table 2-9. XAUI Vendor Specific Registers 4.9xxxh

| Bit(s)         | Name                | Description                                                                                                                                                                                                                                                                                                                                           | R/W | Reset Value |

|----------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|

| 4.9xxxx.[15:8] | Unused              | Bit [15:8] are unused                                                                                                                                                                                                                                                                                                                                 | R/W | 0           |

| 4.9xxxx.[7:0]  | PCS register access | Bit [7:0] are directly mapped to sci_data port.<br>Address [5:0] are directly mapped to sci_address port [5:0].<br>Address bit [8:6] are used to decode which SCI quad is<br>being selected.<br>[8:6] = 0 SCI0 is selected<br>[8:6] = 1 SCI1 is selected<br>[8:6] = 2 SCI2 is selected<br>[8:6] = 3 SCI3 is selected<br>[8:6] = 4 SCI AUX is selected | R/W | 0           |

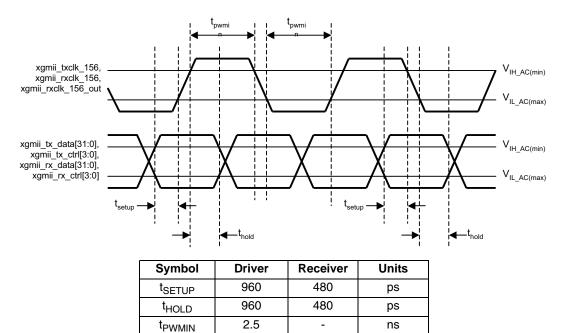

# Input/Output Timing

## **XGMII Specifications**

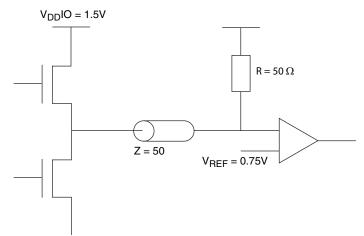

Clause 46 if IEEE 802.3-2005 specifies HSTL1 I/O with a 1.5V output buffer supply voltage for all XGMII signals. The HSTL1 specifications comply with EIA/JEDEC standard EIA/JESD8-6 using Class I output buffers with output impedance greater than 38<sup>3</sup>/<sub>4</sub> to ensure acceptable overshoot and undershoot performance in an unterminated interconnection. The parametric values for HSTL XGII signals are given in Table 2-10. The HSTL termination scheme is shown in Figure 2-11. Timing requirements for chip-to-chip XGMII signals are shown in Figure 2-12.

| Parameter | Condition  | Min.         | Тур. | Max.         | Units |

|-----------|------------|--------------|------|--------------|-------|

| VDDIO     | -          | 1.4          | 1.5  | 1.8          | V     |

| VREF      | -          | 0.68         | 0.75 | 0.9          | V     |

| VTT1      | -          | -            | 0.75 | -            | V     |

| VIH       | -          | VREF + 100mV | 0.85 | VDDIO + 0.3  | V     |

| VIL       | -          | -0.3         | 0.65 | VREF - 100mV | V     |

| VOH2      | IOH > 8mA  | 1            | 1.1  | -            | V     |

| VOL       | IOL > -8mA | -            | -    | 0.4          | V     |

Table 2-10. XGMII DC and AC Specifications

## Figure 2-11. HSTL1 Circuit Topology

Figure 2-12. XGMII Timing Parameters

## **XAUI Specifications**

Refer to the LatticeECP2M and LatticeECP3 PCS specifications for a complete XAUI timing requirements.

### **MDIO Specifications**

The electrical specifications of the MDIO signals conform to Clause 45.4 of IEEE 802.3-2005.

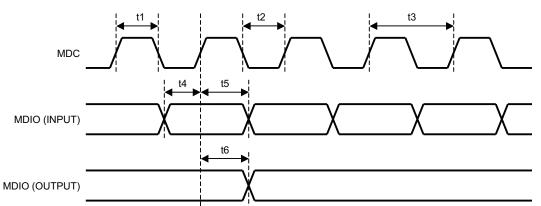

### Figure 2-13. MDIO Timing

| Symbol | Description                             | Min. | Max. | Units |

|--------|-----------------------------------------|------|------|-------|

| t1     | MDC high pulse width                    | 200  | _    | ns    |

| t2     | MDC low pulse width                     | 200  | _    | ns    |

| t3     | MDC period                              | 400  | _    | ns    |

| t4     | MDIO (I) setup to MDC rising edge       | 10   | _    | ns    |

| t5     | MDIO (O) hold time from MDC rising edge | 10   | _    | ns    |

| t6     | MDIO (O) valid from MDC rising edge     | 0    | 300  | ns    |

# **Parameter Settings**

The IPexpress<sup>™</sup> tool is used to create IP and architectural modules in the Diamond and ispLEVER software. Refer to "IP Core Generation" on page 27 for a description on how to generate the IP.

Table 3-1 provides the list of user configurable parameters for the XAUI IP core. The parameter settings are specified using the XAUI IP core Configuration GUI in IPexpress.

#### Table 3-1. XAUI IP Configuration Parameters

| Parameter                                                               | Range/Options                                            | Default                                                     |

|-------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|

| Configuration Options                                                   | Tx Slip Buffer/Rx Slip Buffer/MDIO                       | Tx Slip Buffer/<br>Rx Slip Buffer                           |

| Generation Options                                                      | Behavioral Model/Netlist [.ngo]/<br>Evaluation Directory | Behavioral<br>Model/Netlist [.ngo]/<br>Evaluation Directory |

| Support Synplify, Support Precision, Support ModelSim,<br>Support ALDEC | Enable, Disable                                          | Enable                                                      |

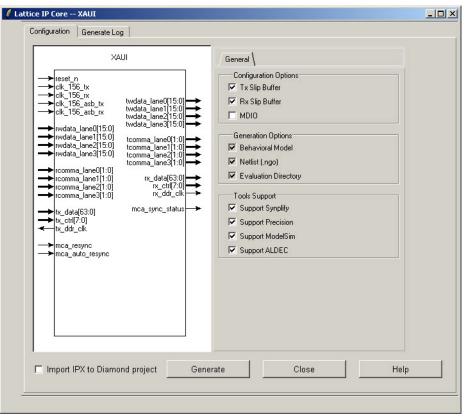

## **XAUI IP Configuration Dialog Box**

Figure 3-1 shows the XAUI IP core configuration dialog box.

### Figure 3-1. XAUI IP Configuration Dialog Box

| General \             |  |

|-----------------------|--|

| Configuration Options |  |

| 🔽 Tx Slip Buffer      |  |

| Rx Slip Buffer        |  |

| MDIO                  |  |

| Generation Options    |  |

| 🔽 Behavioral Model    |  |

| ☑ Netlist (.ngo)      |  |

| Evaluation Directory  |  |

| Tools Support         |  |

| Support Synplify      |  |

| Support Precision     |  |

| Support ModelSim      |  |

| Support ALDEC         |  |

## **Parameter Descriptions**

This section describes the available parameters for the XAUI IP core.

### **Tx Slip Buffer**

This option allows the user to include a slip buffer in the XAUI transmit direction for clock tolerance compensation (enabled by default).

## **Rx Slip Buffer**

This option allows the user to include a slip buffer in the XAUI receive direction for clock tolerance compensation (enabled by default).

## MDIO

This option allows the user to include an MDIO interface providing access to XAUI IP core internal registers (disabled by default).

### **Behavioral Model**

This option creates behavioral simulation model for IP core (always enabled).

## Netlist [.ngo]

This option creates a netlist (.ngo file) for IP core (always enabled).

### **Evaluation Directory**

This option creates an evaluation directory for IP core that includes simulation and implementation example projects (always enabled).

### **Tools Support**

The XAUI IP core evaluation capability supports multiple synthesis and simulation tool flows. These options allow the user to select desired tool support.

# **IP Core Generation**

This chapter provides information on licensing the XAUI IP core, generating the core using the Diamond or isp-LEVER software IPexpress tool, running functional simulation, and including the core in a top-level design. The Lattice XAUI IP core can be used in LatticeECP3 and LatticeECP2M device families.

## Licensing the IP Core

An IP license is required to enable full, unrestricted use of the XAUI IP core in a complete, top-level design. An IP license that specifies the IP core (XAUI) and device family (ECP3 or ECP2M) is required to enable full use of the XAUI IP core in LatticeECP2M or LatticeECP3. Instructions on how to obtain licenses for Lattice IP cores are given at:

### http://www.latticesemi.com/products/intellectualproperty/aboutip/isplevercoreonlinepurchas.cfm

Users may download and generate the XAUI IP core for Lattice ECP3 or LatticeECP2M and fully evaluate the core through functional simulation and implementation (synthesis, map, place and route) without an IP license. The XAUI IP core also supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited time (approximately four hours) without requiring an IP license (see "Hardware Evaluation" on page 32 for further details). However, a license is required to enable timing simulation, to open the design in the Diamond or ispLEVER EPIC tool, and to generate bitstreams that do not include the hardware evaluation timeout limitation.

## **Getting Started**

The XAUI IP core is available for download from the Lattice IP Server using the IPexpress tool in Diamond or isp-LEVER. The IP files are automatically installed using ispUPDATE technology in any customer-specified directory. After the IP core has been installed, it will be available in the IPexpress GUI dialog box shown in Figure 4-1.

The IPexpress tool GUI dialog box for the XAUI IP core is shown in Figure 4-1. To generate a specific IP core configuration the user specifies:

- **Project Path** Path to the directory where the generated IP files will be loaded.

- File Name "username" designation given to the generated IP core and corresponding folders and files.

- (Diamond) Module Output Verilog or VHDL.

- (ispLEVER) Design Entry Type Verilog HDL or VHDL

- **Device Family** Device family to which IP is to be targeted (e.g. LatticeECP2M, LatticeECP3, etc.). Only families that support the particular IP core are listed.

- Part Name Specific targeted part within the selected device family.

Figure 4-1. IPexpress Dialog Box (Diamond Version)

| # IPexpress                                                           |         |                                  |                                         |    |

|-----------------------------------------------------------------------|---------|----------------------------------|-----------------------------------------|----|

| File Design Help                                                      |         |                                  |                                         |    |

| 📗 🖉 🍠 🖏 🤣 🎥 🖬 🛙 All Device Family                                     | / 💌     |                                  |                                         |    |

| Name                                                                  | Version | XAUI 1.4                         | User Configurable IP Version: 1.4       |    |

| Arithmetic_Modules     DSP_Modules     DSP_Modules     Memory_Modules |         | IP Name:<br>Project Path:        | XAUI mond/1.0/examples/xaui_test Browse |    |

| Communications                                                        | 1.4     | File Name:                       | xaui_core0                              |    |

| 🕀 🧰 Connectivity<br>🕀 🧰 DSP                                           | 1.4     | Module Output:<br>Device Family: | Verilog                                 |    |

| ⊕ · 📋 Processors, Controllers and Peripherals                         |         | Part Name:                       | LFE3-150EA-6FN1156CES                   |    |

|                                                                       |         |                                  | Customize                               |    |

| <u> </u>                                                              |         | Configuration                    | About                                   |    |

| Ready                                                                 |         |                                  |                                         | 11 |

Note that if the IPexpress tool is called from within an existing project, Project Path, Module Output (Design Entry in ispLEVER), Device Family and Part Name default to the specified project parameters. Refer to the IPexpress tool online help for further information.

To create a custom configuration, the user clicks the **Customize** button in the IPexpress tool dialog box to display the XAUI SDRAM IP core Configuration GUI, as shown in Figure 4-2. From this dialog box, the user can select the IP parameter options specific to their application. Refer to "Parameter Settings" on page 25 for more information on the XAUI parameter settings.

Figure 4-2. Configuration GUI (Diamond Version)

## **IPexpress-Created Files and Top Level Directory Structure**

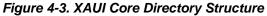

When the user clicks the **Generate** button in the IP Configuration dialog box, the IP core and supporting files are generated in the specified "Project Path" directory. The directory structure of the generated files is shown in Figure 4-3.

Table 4-1 provides a list of key files and directories created by the IPexpress tool and how they are used. The IPexpress tool creates several files that are used throughout the design cycle. The names of most of the created files are customized to the user's module name specified in the IPexpress tool.

### Table 4-1. File List

| File                              | Description                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <username>.lpc</username>         | This file contains the IPexpress tool options used to recreate or modify the core in the IPexpress tool.                                                                                                                                                                                                                                                                 |

| <username>.ipx</username>         | The IPX file holds references to all of the elements of an IP or Module after it is generated from the IPexpress tool (Diamond version only). The file is used to bring in the appropriate files during the design implementation and analysis. It is also used to re-load parameter settings into the IP/Module generation GUI when an IP/Module is being re-generated. |

| <username>.ngo</username>         | This file provides the synthesized IP core.                                                                                                                                                                                                                                                                                                                              |

| <username>_bb.v/.vhd</username>   | This file provides the synthesis black box for the user's synthesis.                                                                                                                                                                                                                                                                                                     |

| <username>_inst.v/.vhd</username> | This file provides an instance template for the PCI IP core.                                                                                                                                                                                                                                                                                                             |

| <username>_beh.v/.vhd</username>  | This file provides the front-end simulation library for the PCI IP core.                                                                                                                                                                                                                                                                                                 |

Table 4-2 provides a list of key additional files providing IP core generation status information and command line generation capability are generated in the user's project directory.

### Table 4-2. Additional Files

| File                               | Description                                                                                                 |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| <username>_generate.tcl</username> | This file is created when the GUI "Generate" button is pushed. This file may be run from com-<br>mand line. |  |  |  |  |  |

| <username>_generate.log</username> | This is the synthesis and map log file.                                                                     |  |  |  |  |  |

| <username>_gen.log</username>      | This is the IPexpress IP generation log file                                                                |  |  |  |  |  |

The *\xaui\_core\_eval* and subtending directories provide files supporting XAUI IP core evaluation. The *\models* directory shown in Figure 4-3 contains files/folders with content that is constant for all configurations of the XAUI IP core. The *\<username>* subfolder (*\XAUI\_core0* in this example) contains files/folders with content specific to the username configuration.

The \xaui\_core\_eval directory is created by IPexpress the first time the core is generated and updated each time the core is regenerated. A \<*username*> directory is created by IPexpress each time the core is generated and regenerated each time the core with the same file name is regenerated. A separate \<*username*> directory is generated for cores with different names, e.g. \xaui\_core0, \xaui\_core1, etc.

### Instantiating the Core

The generated XAUI IP core package includes black-box (*<username>\_bb.v*) and instance (*<username>\_inst.v*) templates that can be used to instantiate the core in a top-level design. Two example RTL top-level reference source files are provided in *\<project\_dir>\xaui\_core\_eval\<username>\src.*

The top-level file *<username>\_eval.v* is the same top-level file that is used in the simulation model described in the next section. Designers may use this top-level reference as a template for the top level of their design. Included in *<username>\_eval.v* sample packet generation and checking capabilities at the XGMII interface.

The top-level file *<username>\_*only\_top.v supports the ability to implement just the XAUI IP core itself. This design is intended only to provide an accurate indication of the device utilization associated with the XAUI IP core and should not be used as an actual implementation example.

To instantiate this IP core using the Linux platform, users must manually add one environment variable named "SYNPLIFY" to indicate the installation path of the OEM Synplify tool in the local environment file. For example, SYNPLIFY=/tools/local/isptools7\_2/isptools/synplify\_linux.

## Lattice Semiconductor

### **Running Functional Simulation**

The functional simulation includes a configuration-specific behavioral model of the XAUI IP core (*<username>\_beh.v*) that is instantiated in an FPGA top level along with user-side (XGMII) packet generation and checking capabilities. The top-level file supporting ModelSim simulation is provided in

<project\_dir>\xaui\_core\_eval\<username>\src. This FPGA top is instantiated in an evaluation testbench provided in <project\_dir>\xaui\_core\_eval\<username>\testbench.

Users may run the evaluation simulation by doing the following:

- 1. Open ModelSim.

- 2. Under the **File** tab, select **Change Directory** and choose folder <project dir>\xaui core eval\<username>\sim\modelsim.

- 3. Under the **Tools** tab, select **Execute Macro** and execute one of the ModelSim "do" scripts shown.

The simulation waveform results will be displayed in the ModelSim Wave window.

```

The top-level file supporting Aldec Active-HDL simulation is provided in \<project_dir>\xaui_core\<username>\sim\aldec. This is the same top-level that is used for ModelSim simulation.

```

Users may run the Aldec evaluation simulation by doing the following:

- 1. Open Active-HDL.

- 2. Under the console tab change the directory to \<project\_dir>\xaui\_core\_eval\<username>\sim\aldec

- 3. Execute the Active-HDL "do" scripts shown.

The simulation waveform results will be displayed in the Active-HDL Wave window.

### Synthesizing and Implementing the Core in a Top-Level Design

The XAUI IP core itself is synthesized and is provided in NGO format when the core is generated. Users may synthesize the core in their own top-level design by instantiating the core in their top level as described previously and then synthesizing the entire design with either Synplify or Precision RTL Synthesis (Synopsys Synplify is included with Diamond and ispLEVER. Precision RTL Synthesis is available separately from Mentor Graphics).

Two example RTL top-level configurations supporting the XAUI IP core top-level synthesis and implementation are provided with the XAUI IP core in \<project dir>\xaui core eval\<username>\impl.

The top-level file xaui\_core\_eval\_only\_top.v provided in

<project\_dir>\eval\<username>\src\rtl\top supports the ability to implement just the XAUI IP core. This design is intended only to provide an accurate indication of the device utilization associated with the core itself and should not be used as an actual implementation example.

The top-level file <username>\_eval.v provided in

\<project\_dir>\eval\<username>\src supports the ability to instantiate, simulate, map, place and route the XAUI IP core in an example design that include packet generation and checking modules at the XGMII interface. This is the same configuration that is used in the evaluation simulation capability described previously.

Push-button implementation of both top-level configurations is supported via the Diamond or ispLEVER project files, <username>\_core\_only\_eval.syn and <username>\_eval.syn. These files are located in

## Lattice Semiconductor

For the Linux platform, the top-level synthesis must be run separately with a synthesis tool such as Synplify Pro, since Diamond and ispLEVER for Linux only accept an EDIF entry. For the core-only project, the synthesis tcl file <*username*>\_core\_only.tcl is generated in

<project\_dir>\xaui\_core\_eval<<username>\impl\synplify. The user can run this tcl script to synthesize the core\_only top-level files in the above directory.

For the reference project, <username>\_eval.tcl will be generated in the

<project\_dir>\xaui\_core\_eval\<username>\impl\synplify directory. The user can run this tcl script to synthesize the reference top\_level files in the above directory.

To use this project file in Diamond:

- 1. Choose File > Open > Project.

- 2. Browse to

<project\_dir>\xaui\_core\_eval\<username>\impl\synplify (or precision) in the Open Project dialog box.

- 3. Select and open <username>.ldf. At this point, all of the files needed to support top-level synthesis and implementation will be imported to the project.

- 4. Select the Process tab in the left-hand GUI window.

- 5. Implement the complete design via the standard Diamond GUI flow.

To use this project file in ispLEVER:

- 1. Choose File > Open Project.

- 2. Browse to

\<project\_dir>\xaui\_core\_eval\<username>\impl\synplify (or precision) in the Open

Project dialog box.

- 3. Select and open <username>.syn. At this point, all of the files needed to support top-level synthesis and implementation will be imported to the project.

- 4. Select the device top-level entry in the left-hand GUI window.

- 5. Implement the complete design via the standard ispLEVER GUI flow.

## **Hardware Evaluation**

The XAUI IP core supports supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited period of time (approximately four hours) without requiring the purchase of an IP license. It may also be used to evaluate the core in hardware in user-defined designs.

### **Enabling Hardware Evaluation in Diamond**

Choose **Project > Active Strategy > Translate Design Settings**. The hardware evaluation capability may be enabled/disabled in the Strategy dialog box. It is enabled by default.

### **Enabling Hardware Evaluation in ispLEVER**

In the Processes for Current Source pane, right-click the **Build Database** process and choose **Properties** from the dropdown menu. The hardware evaluation capability may be enabled/disabled in the Properties dialog box. It is enabled by default.

## Updating/Regenerating the IP Core

By regenerating an IP core with the IPexpress tool, you can modify any of its settings including device type, design entry method, and any of the options specific to the IP core. Regenerating can be done to modify an existing IP core or to create a new but similar one.

### **Regenerating an IP Core in Diamond**

To regenerate an IP core in Diamond:

- 1. In IPexpress, click the Regenerate button.

- 2. In the Regenerate view of IPexpress, choose the IPX source file of the module or IP you wish to regenerate.

- 3. IPexpress shows the current settings for the module or IP in the Source box. Make your new settings in the Target box.

- 4. If you want to generate a new set of files in a new location, set the new location in the **IPX Target File** box. The base of the file name will be the base of all the new file names. The IPX Target File must end with an .ipx extension.

- 5. Click **Regenerate.** The module's dialog box opens showing the current option settings.

- 6. In the dialog box, choose the desired options. To get information about the options, click **Help**. Also, check the About tab in IPexpress for links to technical notes and user guides. IP may come with additional information. As the options change, the schematic diagram of the module changes to show the I/O and the device resources the module will need.

- 7. To import the module into your project, if it's not already there, select **Import IPX to Diamond Project** (not available in stand-alone mode).

- 8. Click Generate.

- 9. Check the Generate Log tab to check for warnings and error messages.

#### 10.Click Close.

The IPexpress package file (.ipx) supported by Diamond holds references to all of the elements of the generated IP core required to support simulation, synthesis and implementation. The IP core may be included in a user's design by importing the .ipx file to the associated Diamond project. To change the option settings of a module or IP that is already in a design project, double-click the module's .ipx file in the File List view. This opens IPexpress and the module's dialog box showing the current option settings. Then go to step 6 above.

### **Regenerating an IP Core in ispLEVER**

To regenerate an IP core in ispLEVER:

- 1. In the IPexpress tool, choose **Tools > Regenerate IP/Module**.

- 2. In the Select a Parameter File dialog box, choose the Lattice Parameter Configuration (.lpc) file of the IP core you wish to regenerate, and click **Open**.

- 3. The Select Target Core Version, Design Entry, and Device dialog box shows the current settings for the IP core in the Source Value box. Make your new settings in the Target Value box.

- 4. If you want to generate a new set of files in a new location, set the location in the LPC Target File box. The base of the .lpc file name will be the base of all the new file names. The LPC Target File must end with an .lpc extension.

- 5. Click **Next**. The IP core's dialog box opens showing the current option settings.

## Lattice Semiconductor

- 6. In the dialog box, choose desired options. To get information about the options, click **Help**. Also, check the About tab in the IPexpress tool for links to technical notes and user guides. The IP core might come with additional information. As the options change, the schematic diagram of the IP core changes to show the I/O and the device resources the IP core will need.

- 7. Click Generate.

- 8. Click the **Generate Log** tab to check for warnings and error messages.

# **Support Resources**

This chapter contains information about Lattice Technical Support, additional references, and document revision history.

## Lattice Technical Support

There are a number of ways to receive technical support.

### **Online Forums**

The first place to look is Lattice Forums (http://www.latticesemi.com/support/forums.cfm). Lattice Forums contain a wealth of knowledge and are actively monitored by Lattice Applications Engineers.

### **Telephone Support Hotline**

Receive direct technical support for all Lattice products by calling Lattice Applications from 5:30 a.m. to 6 p.m. Pacific Time.

- For USA & Canada: 1-800-LATTICE (528-8423)

- For other locations: +1 503 268 8001

In Asia, call Lattice Applications from 8:30 a.m. to 5:30 p.m. Beijing Time (CST), +0800 UTC. Chinese and English language only.

• For Asia: +86 21 52989090