Soft SPI4 IP Core User's Guide

# **Table of Contents**

| Quick Facts       4         Features       4         Chapter 2. Functional Description       6         Overview       6         Operational Description       6         SPI4 Transmitter - S4TX       7         SPI4 Transmit Parotocol - S4TXDP       7         SPI4 Transmit Status - S4TXIO       7         SPI4 Transmit Status - S4TXSP       11         SPI4 Receive Data Protocol - S4RXDP       15         SPI4 Receive Data Protocol - S4RXDP       15         SPI4 Receive Data Protocol - S4RXSP       18         SPI4 Receive Status Protocol - S4RXSP       18         SPI4 Receive Status Protocol -S4RXSP       18         Spratup Procedures       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Global Tab       33         Global Tab       36         User Data Interface       36         Global Tab       37         Transmit Tab                                                    | Chapter 1. Introduction                       | 4  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----|

| Chapter 2. Functional Description       6         Overview       6         Operational Description       6         SPI4 Transmit Data Protocol - S4TXDP       7         SPI4 Transmit Status - S4TXDP       7         SPI4 Transmit Status - S4TXDP       9         SPI4 Transmit Status - S4TXDP       11         SPI4 Receiver S4RX       14         SPI4 Receiver S4RX       14         SPI4 Receiver S4RX       14         SPI4 Receiver S4RX       14         SPI4 Receiver S4RXDP       15         SPI4 Receiver S4RXDP       15         SPI4 Receive Data Protocol - S4RXDP       18         SPI4 Receiver I/O - S4RXDO (RXGB)       21         Calendar and Status PAM Access       22         Start-Up Procedures       23         Dynamic Mode Start-Up and Recovery (SMSR) FSM       23         Static Mode Start-Up and Recovery (SMSR) FSM       23         Signal Descriptions       24         Signal Descriptions       24         Signal Descriptions       24         Signal Descriptions       36         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Une Si                                                                           |                                               |    |

| Overview       6         Operational Description       6         SPI4 Transmitter - S4TX       7         SPI4 Transmit Data Protocol - S4TXDP       7         SPI4 Transmit IO - S4TXIO (TXGB)       9         SFI4 Transmit Status - S4TXSP       11         SPI4 Receiver - S4RX       14         SPI4 Receiver - S4RX       14         SPI4 Receiver Data Protocol - S4RXDP       15         SPI4 Receiver Dotocol - S4RXSP       14         Receive Data Protocol - S4RXSP       18         SPI4 Receiver Overs       23         Receive Direction Start-Up       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Transmit Direction Start-Up       24         Signal Descriptions       24         Signal Descriptions       24         Signal Descriptions       33         Global Tab       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Date Path Options       37         Transmit Date Path Options       37         Transmit Use Side FIFO Thresholds       37                                                                               | Features                                      | 4  |

| Overview       6         Operational Description       6         SPI4 Transmitter - S4TX       7         SPI4 Transmit Data Protocol - S4TXDP       7         SPI4 Transmit IO - S4TXIO (TXGB)       9         SFI4 Transmit Status - S4TXSP       11         SPI4 Receiver - S4RX       14         SPI4 Receiver - S4RX       14         SPI4 Receiver Data Protocol - S4RXDP       15         SPI4 Receiver Dotocol - S4RXSP       14         Receive Data Protocol - S4RXSP       18         SPI4 Receiver Overs       23         Receive Direction Start-Up       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Transmit Direction Start-Up       24         Signal Descriptions       24         Signal Descriptions       24         Signal Descriptions       33         Global Tab       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Date Path Options       37         Transmit Date Path Options       37         Transmit Use Side FIFO Thresholds       37                                                                               | Chapter 2. Functional Description             | 6  |

| SPI4 Transmitter S4TX       7         SPI4 Transmit IData Protocol - S4TXID       7         SPI4 Transmit IDA - S4TXIO (TKGB)       9         SPI4 Transmit Status - S4TXSP       11         SPI4 Receiver S4RX       14         SPI4 Receiver S4RX       14         SPI4 Receiver Status Protocol - S4RXDP       15         SPI4 Receiver VOCOL - S4RXIC       16         SPI4 Receiver VOCOL - S4RXIC       17         Calendar and Status RAM Access       22         Statt-Up Procedures       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Signal Descriptions       24         Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Data Path Options       37         Transmit User Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Tab       38                     | •                                             |    |

| SPI4 Transmitter S4TX       7         SPI4 Transmit IData Protocol - S4TXID       7         SPI4 Transmit IDA - S4TXIO (TKGB)       9         SPI4 Transmit Status - S4TXSP       11         SPI4 Receiver S4RX       14         SPI4 Receiver S4RX       14         SPI4 Receiver Status Protocol - S4RXDP       15         SPI4 Receiver VOCOL - S4RXIC       16         SPI4 Receiver VOCOL - S4RXIC       17         Calendar and Status RAM Access       22         Statt-Up Procedures       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Signal Descriptions       24         Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Data Path Options       37         Transmit User Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Tab       38                     | Operational Description                       | 6  |

| SPI4 Transmit Data Protocol - S4TXDP       7         SPI4 Transmit VIO (TXGB)       9         SPI4 Transmit VIAUS (TXGB)       9         SPI4 Receive S4RX       11         SPI4 Receive Data Protocol - S4RXDP       15         SPI4 Receive Data Protocol - S4RXDP       16         SPI4 Receive Status Protocol - S4RXSP       18         SPI4 Receive Status Protocol - S4RXSP       18         SPI4 Receive Status Protocol - S4RXSP       22         Statr-Up Procedures       23         Receive Direction Start-Up.       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       24         Signal Descriptions       24         Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Data Path Options       38         Receive Data Path Options       39                             |                                               |    |

| SPI4 Transmit I/O - S4TXIO (TXGB)       9         SPI4 Transmit Status - S4TXSP       11         SPI4 Receive Data Protocol - S4RXDP       15         SPI4 Receive Status Protocol - S4RXSP       18         SPI4 Receive Status Protocol - S4RXSP       18         SPI4 Receive Status Protocol - S4RXSP       18         SPI4 Receive Status Protocol - S4RXSP       21         Calendar and Status RAM Access       22         Start-Up Procedures       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Gipal Descriptions       24         Signal Descriptions       24         Signal Descriptions       24         Signal Descriptions       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Line Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab - Lattice ECP       38         Receive Tab - Lattice ECP       38         Receive Tab - Lattice ECP       39 </td <td></td> <td></td> |                                               |    |

| SPI4 Transmit Status - SATXSP       11         SPI4 Receiver - S4RX.       14         SPI4 Receiver Data Protocol - S4RXDP       15         SPI4 Receive Status Protocol - S4RXSP       18         SPI4 Receiver I/O - S4RXIO (RXGB)       21         Calendar and Status RAM Access       22         Status Protocol - S4RXIO (RXGB)       23         Receive Direction Start-Up.       23         Dynamic Mode Start-up and Recovery (SMSR) FSM.       23         Static Mode Start-up and Recovery (SMSR) FSM.       23         Global Tab.       24         Signal Descriptions       24         Global Tab.       36         Global Tab.       36         Global Tab.       36         Generation Options       37         Transmit Tab.       37         Transmit User Side FIFO Thresholds       37                                      |                                               |    |

| SPI4 Receiver - S4RX       14         SPI4 Receive Data Protocol - S4RXDP       15         SPI4 Receive Stus Protocol - S4RXSP       18         SPI4 Receive Stus Protocol - S4RXSP       18         SPI4 Receives Stus Protocol - S4RXSP       22         Calendar and Status RAM Access       22         Start-Up Procedures       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Signal Descriptions       24         Chapter 3. Parameter Settings       24         Chapter 3. Parameter Settings       36         User Data Interface       36         Generation Options       37         Transmit Tab       37         Transmit Line Side FIFO Thresholds       37         Transmit Line Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       39         Status Tab       39         Status Tab       40         Status Tab       40         Status Channel Options       40         Receive Data Path Options <td></td> <td></td>                        |                                               |    |

| SPI4 Receive Data Protocol - S4RXDP       15         SPI4 Receiver I/O - S4RXD(RXGB)       11         Calendar and Status RAM Access       22         Stat-Up Procedures       23         Receive Direction Start-Up       23         Dynamic Mode Start-up and Recovery (SMSR) FSM.       23         Static Mode Start-up and Recovery (SMSR) FSM.       23         Transmit Direction Start-Up.       24         Signal Descriptions       24         Chapter 3. Parameter Settings       24         Global Tab.       36         User Data Interface       36         Generation Options       37         Transmit Tab.       36         Transmit User Side FIFO Thresholds       37         Transmit Use Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       38         Receive Tab - Lattice SC/SCM       38         Receive Data Path Options       39         Status Channel Options       40         Transmit Status Path Options       40         Transmit Status Path Options       40         Receive Status Path Options       40         Receive Data Path Options       40         Receive Data Path Options       40         Receive Statu                                        |                                               |    |

| SPI4 Receive Status Protocol - S4RXSP.       18         SPI4 Receiver I/O - S4RXIO (RXGB)       21         Calendar and Status RAM Access       22         Start-Up Procedures       23         Receive Direction Start-Up.       23         Dynamic Mode Start-up and Recovery (SMSR) FSM.       23         Static Mode Start-up and Recovery (SMSR) FSM.       23         Static Mode Start-up and Recovery (SMSR) FSM.       23         Signal Descriptions       24         Signal Descriptions       24         Chapter 3. Parameter Settings       23         Global Tab.       36         User Data Interface       36         Generation Options       37         Transmit Tab       37         Transmit User Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab - Lattice SC/SCM       39         Status Tab.       40         Transmit Status Path Options       40         Receive Status P                                        |                                               |    |

| SPI4 Receiver I/O - S4RXIO (RXGB)       21         Calendar and Status RAM Access       22         Start-Up Procedures       23         Receive Direction Start-Up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Transmit Direction Start-Up       24         Signal Descriptions       24         Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Tab       37         Transmit Data Path Options       37         Transmit Line Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Data Path Options       38         Receive Data Path Options       38         Receive Data Path Options       38         Receive Data Path Options       39         Receive Data Path Options       39         Receive Data Path Options       40         Status Channel Options       40         Status Channel Options       40         Status Channel Options       40         Calendars Tab       41 <td></td> <td></td>                                 |                                               |    |

| Calendar and Status RAM Access       22         Stat-Up Procedures       23         Receive Direction Start-Up       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Transmit Direction Start-Up       24         Signal Descriptions       24         Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       37         Transmit Tab       37         Transmit Tab       37         Transmit Line Side FIFO Thresholds       37         Transmit Line Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       39         Status Channel Options       39         Status Channel Options       40         Transmit Tab       40         Transmit Calendar Options       40         Receive Data Path Options       40         Receive Data Path Options       40         Receive Status Path Options       40         Receive Status Path Options       40         Rec                                                                           |                                               |    |

| Start-Up Procedures       23         Receive Direction Start-Up.       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Transmit Direction Start-Up.       24         Chapter 3. Parameter Settings       24         Chapter 3. Parameter Settings       33         Global Tab.       36         User Data Interface       36         Generation Options       37         Transmit Tab       37         Transmit Data Path Options       37         Transmit Data Path Options       37         Transmit User Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Data Path Options       38         Receive Data Path Options       39         Status Tab       40         Status Tab       40         Status Tab       40         Status Tab       40         Gleendars Tab       40         Chapter 4. IP Core Generation       40         Calendars Tab       41         Transmit Status Path Options                                                                                 |                                               |    |

| Receive Direction Start-Up       23         Dynamic Mode Start-up and Recovery (SMSR) FSM       23         Static Mode Start-up and Recovery (SMSR) FSM       23         Transmit Direction Start-Up       24         Signal Descriptions       24         Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       36         Transmit Tab       37         Transmit Data Path Options       37         Transmit Data Path Options       37         Transmit Data Path Options       37         Transmit Dacking Enable       38         Receive Tab – LatticeECP       38         Receive Tab – LatticeECP       38         Receive Data Path Options       39         Status Channel Options       39         Status Channel Options       40         Transmit Zalendar Options       40         Calendars Tab       41         Transmit Calendar Options       40         Receive Data Path Options       40         Status Channel Options       40         Calendars Tab       41         Transmit Calendar Options       40         Calendars Tab                                                                                    |                                               |    |

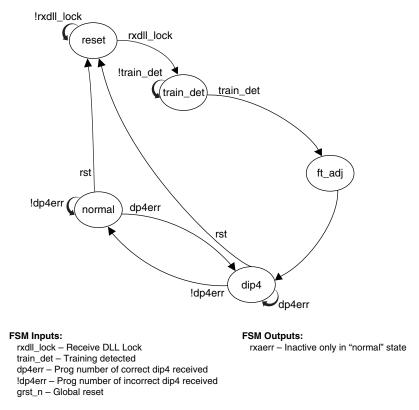

| Dynamic Mode Start-up and Recovery (SMSR) FSM.       23         Static Mode Start-up and Recovery (SMSR) FSM.       23         Transmit Direction Start-Up.       24         Signal Descriptions       24         Chapter 3. Parameter Settings       23         Global Tab.       36         User Data Interface       36         Generation Options       37         Transmit Tab.       37         Transmit Data Path Options       37         Transmit Data Path Options       37         Transmit User Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab – LatticeECP       38         Receive Tab – Lattice SC/SCM       39         Receive Data Path Options       39         Status Tab.       40         Status Channel Options       40         Transmit Status Path Options       40         Transmit Status Path Options       40         Receive Catel Apti Options       40         Receive Catel Apti Options       40         Receive Catel Options       40         Transmit Status Path Options       40         Transmit Tab.       41         Transmit Status Path Options       40                                                                            | Receive Direction Start-Up                    | 23 |

| Static Mode Start-up and Recovery (SMSR) FSM       23         Transmit Direction Start-Up       24         Signal Descriptions       24         Chapter 3. Parameter Settings       33         Global Tab.       36         User Data Interface       36         Generation Options       36         Transmit Tab       37         Transmit Data Path Options       37         Transmit Dire Side FIFO Thresholds       37         Transmit Vacking Enable       38         Receive Tab – LatticeECP       38         Receive Tab – LatticeECP       38         Receive Data Path Options       39         Status Tab       40         Status Channel Options       40         Transmit Status Path Options       40         Receive Data Path Options       40         Status Channel Options       40         Transmit Status Path Options       40         Receive Calendar Options       40         Receive Calendar Options       40         Receive Calendar Options       40         Receive Tab – Lattice ECP       41         Channel Options       40         Status Channel Options       40         Receive Data Path Options                                                                                   | Dynamic Mode Start-up and Recovery (SMSR) FSM | 23 |

| Transmit Direction Start-Up.       24         Signal Descriptions       24         Chapter 3. Parameter Settings       23         Global Tab.       36         User Data Interface       36         Generation Options       36         Transmit Tab.       37         Transmit Data Path Options       37         Transmit User Side FIFO Thresholds       37         Transmit Vacous Piero Patholds       37         Transmit Packing Enable       38         Receive Tab - Lattice ECP       38         Receive Data Path Options       39         Receive Tab - Lattice SC/SCM       39         Receive Data Path Options       39         Receive Data Path Options       40         Status Tab.       40         Status Channel Options       40         Receive Status Path Options       40         Receive Calendar Options       40         Receive Calendar Options       41         Transmit Calendar Options       41         Transmit Calendar Options       41         Transmit Calendar Options       41         Itensing the IP Core       42         Idexting the IP Core       42         Idexting the IP Core                                                                                           | Static Mode Start-up and Recovery (SMSR) FSM  | 23 |

| Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       36         Transmit Tab       37         Transmit Data Path Options       37         Transmit Line Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Vacking Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       39         Receive Data Path Options       39         Receive Data Path Options       39         Status Tab       40         Status Tab       40         Status Path Options       40         Transmit Status Path Options       40         Calendars Tab       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41                                                                                           |                                               |    |

| Chapter 3. Parameter Settings       33         Global Tab       36         User Data Interface       36         Generation Options       36         Transmit Tab       37         Transmit Data Path Options       37         Transmit Line Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Vacking Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       39         Receive Data Path Options       39         Receive Data Path Options       39         Status Tab       40         Status Tab       40         Status Path Options       40         Transmit Status Path Options       40         Calendars Tab       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41                                                                                           | Signal Descriptions                           | 24 |

| Global Tab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                               |    |

| User Data Interface36Generation Options36Transmit Tab37Transmit Data Path Options37Transmit Data Path Options37Transmit Data Path Options37Transmit User Side FIFO Thresholds37Transmit User Side FIFO Thresholds37Transmit Packing Enable38Receive Tab - Lattice ECP38Receive Tab - Lattice SC/SCM39Receive Data Path Options39Status Channel Options40Status Channel Options40Transmit Status Path Options40Calendars Tab41Transmit Calendar Options41Transmit Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                             |    |

| Generation Options       36         Transmit Tab       37         Transmit Data Path Options       37         Transmit Line Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Vacking Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       38         Receive Tab – Lattice SC/SCM       39         Receive Data Path Options       39         Status Tab       40         Status Channel Options       40         Transmit Calendar Options       40         Receive Status Path Options       40         Receive Calendar Options       41         Transmit Calendar Options       41         Receive Calendar Options       41         IPexpress-Created Files and Top Level Directory Structure       42         IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                 |                                               |    |

| Transmit Tab       37         Transmit Data Path Options       37         Transmit Line Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       39         Receive Data Path Options       39         Receive Data Path Options       39         Status Channel Options       39         Status Channel Options       40         Transmit Status Path Options       40         Calendars Tab       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Itensing the IP Core       42         Licensing the IP Core       42         IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                            |                                               |    |

| Transmit Data Path Options37Transmit Line Side FIFO Thresholds37Transmit User Side FIFO Thresholds37Transmit Packing Enable38Receive Tab – LatticeECP38Receive Data Path Options38Receive Data Path Options39Receive Data Path Options39Status Channel Options39Status Channel Options40Status Channel Options40Calendars Tab40Calendars Tab41Transmit Calendar Options41Receive Calendar Options41Receive Calendar Options41Receive Calendar Options41Receive Calendar Options41Instantiating the IP Core42Licensing the IP Core42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |    |

| Transmit Line Side FIFO Thresholds       37         Transmit User Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       38         Receive Tab – Lattice SC/SCM       39         Receive Data Path Options       39         Status Tab       40         Status Channel Options       40         Status Path Options       40         Receive Calendar Options       40         Receive Calendar Options       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       42         Licensing the IP Core       42         Getting Started       42         IPexpress-Created Files and Top Level Directory Structure       42         IPexpress-Created Files and Top Level Directory Structure       46         Running Functional Simulation       46         Synthesizin                                        |                                               |    |

| Transmit User Side FIFO Thresholds       37         Transmit Packing Enable       38         Receive Tab – LatticeECP       38         Receive Tab – Lattice SC/SCM       39         Receive Tab – Lattice SC/SCM       39         Receive Data Path Options       39         Status Tab       39         Status Tab       40         Status Channel Options       40         Transmit Status Path Options       40         Receive Status Path Options       40         Calendars Tab       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Instantiating the IP Core       42         Getting Started       42         IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                  |                                               |    |

| Transmit Packing Enable       38         Receive Tab – LatticeECP       38         Receive Data Path Options       38         Receive Tab – Lattice SC/SCM       39         Receive Data Path Options       39         Receive Data Path Options       39         Status Tab       40         Status Channel Options       40         Transmit Status Path Options       40         Receive Calendar Options       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Chapter 4. IP Core Generation       42         Licensing the IP Core       42         IPexpress-Created Files and Top Level Directory Structure       42         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                           |                                               |    |

| Receive Tab – LatticeECP       38         Receive Data Path Options       38         Receive Tab – Lattice SC/SCM       39         Receive Data Path Options       39         Receive Data Path Options       39         Status Tab.       40         Status Channel Options       40         Transmit Status Path Options       40         Receive Status Path Options       40         Calendars Tab.       41         Transmit Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Receive Calendar Options       41         Icensing the IP Core       42         Licensing the IP Core.       42         IPexpress-Created Files and Top Level Directory Structure       42         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                     |                                               |    |

| Receive Data Path Options.38Receive Tab – Lattice SC/SCM39Receive Data Path Options.39Status Tab.40Status Channel Options40Transmit Status Path Options40Receive Status Path Options40Calendars Tab.41Transmit Calendar Options41Receive Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core.42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                               |    |

| Receive Tab – Lattice SC/SCM       39         Receive Data Path Options       39         Status Tab       40         Status Channel Options       40         Transmit Status Path Options       40         Receive Status Path Options       40         Calendars Tab       40         Transmit Calendar Options       40         Calendars Tab       41         Transmit Calendar Options       41         Receive Calendar Options       41         Chapter 4. IP Core Generation       42         Licensing the IP Core       42         Getting Started       42         IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |    |

| Receive Data Path Options.39Status Tab.40Status Channel Options40Transmit Status Path Options40Receive Status Path Options40Calendars Tab.41Transmit Calendar Options41Receive Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core.42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |    |

| Status Tab40Status Channel Options40Transmit Status Path Options40Receive Status Path Options40Calendars Tab41Transmit Calendar Options41Receive Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Receive Data Path Options                     | 39 |

| Transmit Status Path Options40Receive Status Path Options40Calendars Tab.41Transmit Calendar Options41Receive Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core44Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                               |    |

| Transmit Status Path Options40Receive Status Path Options40Calendars Tab.41Transmit Calendar Options41Receive Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core44Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Status Channel Options                        | 40 |

| Calendars Tab.       41         Transmit Calendar Options       41         Receive Calendar Options       41 <b>Chapter 4. IP Core Generation</b> 42         Licensing the IP Core       42         Getting Started       42         IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |    |

| Transmit Calendar Options41Receive Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Receive Status Path Options                   | 40 |

| Receive Calendar Options41Chapter 4. IP Core Generation42Licensing the IP Core42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Calendars Tab                                 | 41 |

| Chapter 4. IP Core Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Transmit Calendar Options                     | 41 |

| Licensing the IP Core42Getting Started42IPexpress-Created Files and Top Level Directory Structure44Instantiating the Core46Running Functional Simulation46Synthesizing and Implementing the Core in a Top-Level Design47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ·                                             |    |

| Getting Started       42         IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |    |

| Getting Started       42         IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Licensing the IP Core                         | 42 |

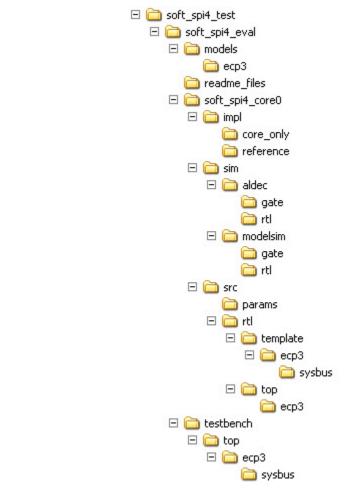

| IPexpress-Created Files and Top Level Directory Structure       44         Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                             |    |

| Instantiating the Core       46         Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |    |

| Running Functional Simulation       46         Synthesizing and Implementing the Core in a Top-Level Design       47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                               |    |

| Synthesizing and Implementing the Core in a Top-Level Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                               |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hardware Evaluation                           | 48 |

© 2010 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

| Enabling Hardware Evaluation in Diamond                        | 48 |

|----------------------------------------------------------------|----|

| Enabling Hardware Evaluation in ispLEVER                       | 48 |

| Updating/Regenerating the IP Core                              |    |

| Regenerating an IP Core in Diamond                             |    |

| Regenerating an IP Core in ispLEVER                            |    |

| Chapter 5. Application Support                                 |    |

| Hard-Core Physical Placement                                   | 51 |

| SPI4 Line-Side I/O                                             | 51 |

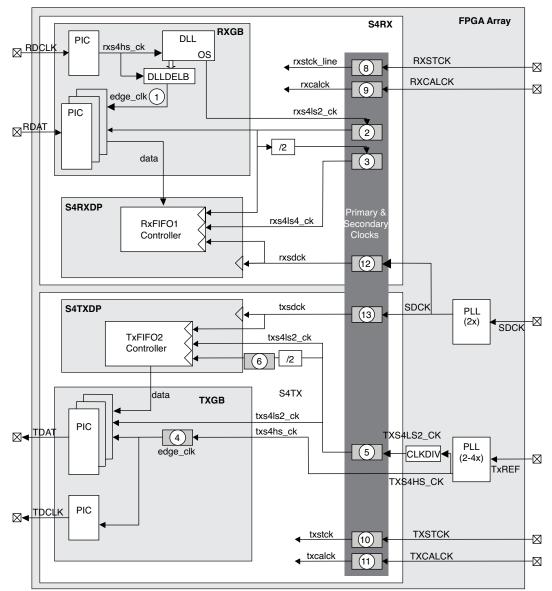

| Clocking and Synchronization                                   |    |

| Clock List                                                     |    |

| Clock Usage Diagram                                            |    |

| System-Level Synchronization                                   |    |

| Selecting a System Data Clock Frequency ('SDCK') - Receiver    |    |

| Selecting a System Data Clock Frequency ('SDCK') - Transmitter |    |

| Chapter 6. Core Verification                                   | 59 |

| Chapter 7. Support Resources                                   | 60 |

| Lattice Technical Support                                      | 60 |

| Online Forums                                                  | 60 |

| Telephone Support Hotline                                      | 60 |

| E-mail Support                                                 | 60 |

| Local Support                                                  |    |

| Internet                                                       | 60 |

| References                                                     | 60 |

| LatticeECP3                                                    |    |

| LatticeSCM                                                     |    |

| Revision History                                               |    |

| Appendix A. Resource Utilization                               |    |

| LatticeECP3 FPGAs                                              |    |

| Supplied Netlist Configurations                                |    |

| LatticeSC/M FPGAs                                              |    |

| Supplied Netlist Configurations                                | 62 |

|                                                                |    |

The Soft System Packet Interface 4 (SPI4) Intellectual Property (IP) core enables user instantiation of OIF-compliant System Packet Interface Level 4 Phase 2 Revision 1 (SPI4.2.1) cores in Lattice Field Programmable Gate Arrays (FPGAs).

The Soft SPI4 IP core supports up to 256 data channels with aggregate throughputs of between 3 and 12.8Gbps and can be used to connect network processors with OC192 framers, mappers, and fabrics, as well as Gigabit and 10-Gigabit Ethernet MACs. This user's guide explains the functionality of the SPI4 core and how it can be applied to interconnect physical and link layer devices in 10Gbps POS, Ethernet, and ATM applications.

### **Quick Facts**

Table 1-1 gives quick facts about the Soft SPI4 IP core.

Table 1-1. Soft SPI4 IP Core Quick Facts

|                              |                         | Se                                                             | oft SPI4 IP Core C      | Configuration         |                       |  |  |  |  |

|------------------------------|-------------------------|----------------------------------------------------------------|-------------------------|-----------------------|-----------------------|--|--|--|--|

|                              | FPGA Families Supported | LatticeE                                                       | CP3™                    | LatticeS              | C/SCM™                |  |  |  |  |

| Core Requirements            | Minimal Device Needed   | LFE3-35EA-<br>8FN484CES                                        | LFE3-35EA-<br>8FN484CES | LFSC3GA15<br>E-6F900C | LFSC3GA15<br>E-6F900C |  |  |  |  |

|                              | Target Device           | LFE3-17EA-<br>7FN484CES                                        | LFE3-17EA-<br>7FN484CES | LFSC3GA15<br>E-6F900C | LFSC3GA15<br>E-6F900C |  |  |  |  |

|                              | Status Mode             | Transparent                                                    | RAM                     | Transparent           | RAM                   |  |  |  |  |

| <b>Resources Utilization</b> | Data Path Width         | 100                                                            | 200                     | 100                   | 200                   |  |  |  |  |

|                              | LUTs                    | 2500                                                           | 4100                    | 3200                  | 5300                  |  |  |  |  |

|                              | sysMEM EBRs             | 12                                                             | 18                      | 12                    | 18                    |  |  |  |  |

|                              | Registers               | 3000                                                           | 4800                    | 3000                  | 4900                  |  |  |  |  |

|                              | Lattice Implementation  | C                                                              |                         |                       |                       |  |  |  |  |

| Design Tool Support          | Synthesis               | Synopsys <sup>®</sup> Synplify™ Pro for Lattice D-2009.12L-1   |                         |                       |                       |  |  |  |  |

| Design Tool Support          | Simulation              | Aldec <sup>®</sup> Active-HDL <sup>™</sup> 8.2 Lattice Edition |                         |                       |                       |  |  |  |  |

|                              | Simulation              | Mentor Graphics ModelSim™ SE 6.3F (                            |                         |                       |                       |  |  |  |  |

### Features

- The Soft SPI4 IP core is fully compliant with the OIF System Packet Interface Level 4 Phase 2 Revision 1 (SPI4.2.1) interface standard

- Supported through Diamond or ispLEVER IPexpress™ tool for easy user configuration and parameterization

- Supports up to 256 independent channels

- 400 to 500MHz DDR Dynamic mode operation in LatticeSC and LatticeSCM devices

- 156 to 350MHz DDR Static timing mode operations for LatticeECP3 devices. Supports non-standard "SPI4 Lite" line rates.

- Supports both 64b and 128b internal architectures for optimization of either speed or size

- Requires only ~2000 slices (64b mode) for a full 256-channel Static mode core

- Supports full bandwidth utilization of the SPI4 line in both directions requires no idle cycles in the receive direction or insertion of idles in the transmit direction between bursts (as long as there is data available)

- Parity error checking/generation on all receive and transmit control and data words (DIP4) and status (DIP2) interfaces

- Parity error force capabilities on data (independent controls: control word and data) and status interfaces

- Various run-time user controls

- Force idles (transmitter)

- Enable/disable packing (transmitter)

- Training pattern (CAL\_M, MAX\_T)

- Complete run-time programmability of all internal FIFO thresholds for efficient management of SPI4 line in terms of Lmax and packing

- Provides a direct interface to primary device I/O at the SPI4 interface and an internal FIFO interface to user logic

- Supports minimum transmit burst sizes in increments of 16 bytes from 16 bytes up to 1008 bytes for optimized network processor applications

- Support for packet sizes down to 4 bytes in length

- Fully configurable 512-location calendar RAM for Rx and Tx directions and associated 256-location status RAMs

- Two independently configurable methods of status reporting in the receive and transmit directions RAM addressable and Transparent

- Rising or falling edge selectable Status Channel I/O independently configurable in the receive and transmit directions

## Chapter 2: Functional Description

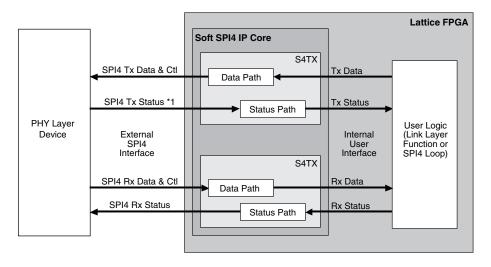

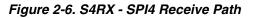

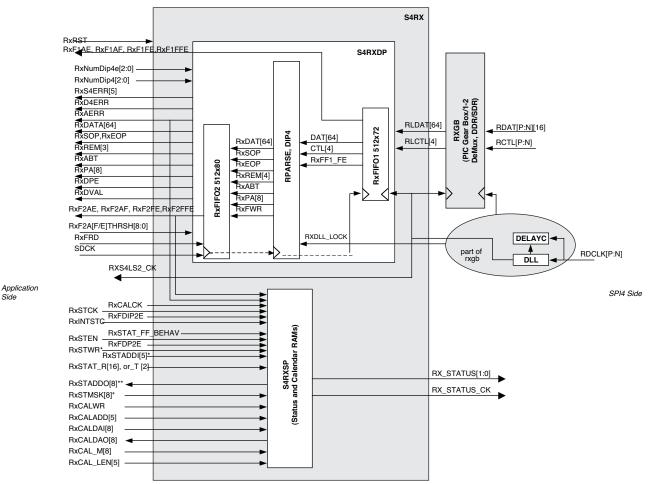

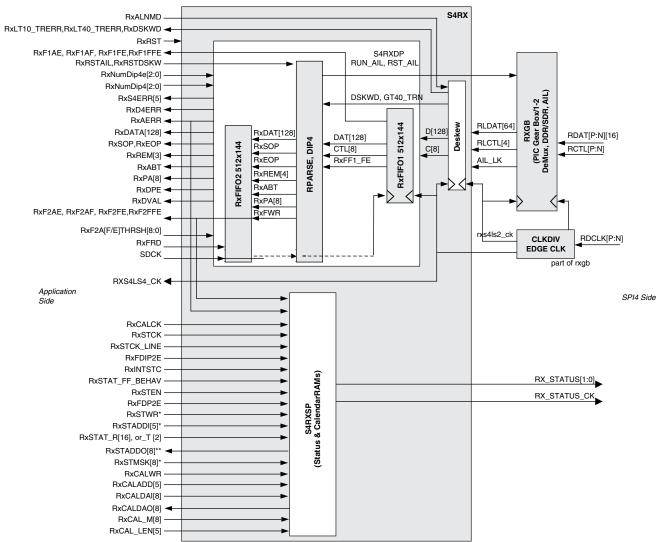

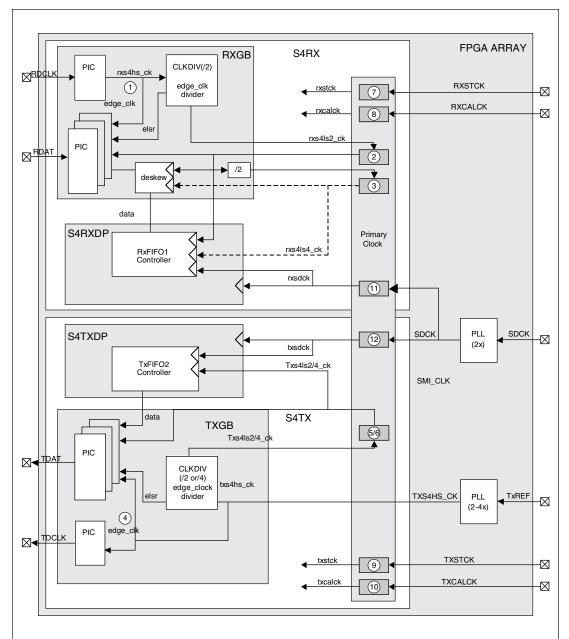

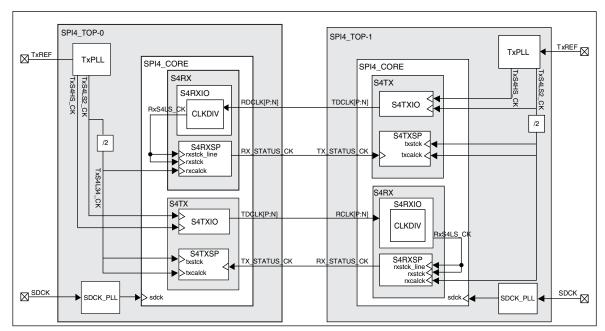

Figure 2-1 shows a system-level diagram of a typical Link layer application where the Soft SPI4 IP core is implemented in a Lattice FPGA. At the top level, the core is broken into two sub-blocks referred to as the SPI4 Transmitter (S4TX) and SPI4 Receiver (S4RX). The S4RX and S4TX blocks provide both status and data path functionality for the direction they serve. They provide a direct interface to the primary I/O of the device on one side (SPI4) and a device-internal FIFO interface to user logic on the other.

Also included is a user-side SPI4 "loop-around module" and a SPI4 test-bench for optional use. The loop-around module loops receive SPI4 data back to the SPI4 transmitter and transmit status back to the SPI4 receiver. An FPGA top-level RTL template design is provided that includes the IP core and loop-around module which can be used without modification for simulation verification and can also be synthesized, placed, and routed "as is" for initial debugging on physical hardware. With this capability, the user can connect their system to a Lattice FPGA via a SPI4 interconnect and easily verify the speed and functionality of the core.

#### Figure 2-1. Soft SPI4 IP Core, System-Level Context

## Overview

The Soft SPI4 IP core is used with additional user-side application logic that interfaces with the IP core via separate receive and transmit FIFO interfaces for SPI4 data information and separate receive and transmit interfaces for SPI4 flow control information. The data FIFOs (4KB 64b mode, 8KB 128b mode) are implemented using Embedded Block RAM (EBR) and provide shared channel buffering on a SPI4 line basis; there is no per-channel buffering within the core for the base design. User-side application logic is responsible for scheduling the maximum allowable SPI4 burst size and the overall amount of data (through credit accounting) that may be written into the S4TX FIFO and transmitted on a per-channel basis. The information needed by the user to manage the credit accounting procedure is received and transmitted on a per-channel basis via the status channel. Both the S4RX and S4TX modules support RAM mode and Transparent mode interfaces that are user selectable for transmitting and receiving status information as well as individual Calendar RAMs that contain configuration data defining the channel order and duration for which status information is transmitted and received for each channel.

## **Operational Description**

For the following descriptions, designations enclosed in single quotes (e.g. 'SDCK') refer to specific Soft SPI4 IP core I/O port names or synthesis parameters. Refer to "Signal Descriptions" on page 24 and "Parameter Settings" on page 33t for detailed descriptions of the functionality of these items.

With regard to timing diagram examples, there are a number of other simulation scenarios that are not captured here but are available for user simulation and viewing through evaluation simulation (see "Running Functional Simulation" on page 46 for a list of simulation scenarios available).

### **SPI4 Transmitter - S4TX**

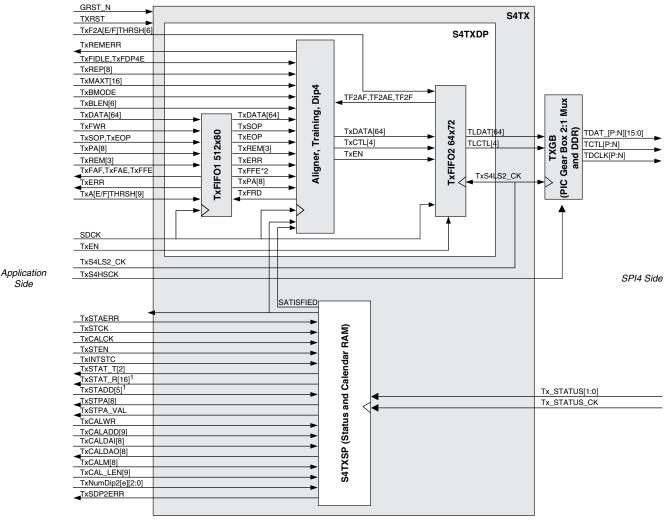

The transmit path, shown in Figure 2-2, is the path of data flow from the internal user application function towards the SPI4 line interface and the direction of status flow from the SPI4 line towards the application function. Figure 2-2 indicates through shading some of the hierarchical boundaries and identifies three distinct sub-sections of the S4TX block as described in the following sections.

Figure 2-2. S4TX - SPI4 Transmit Path (64b Mode)

1. In Transparent mode, TxSTADD[5] and TxSTAT\_R[16] do not exist and do not have an I/O appearance.

### SPI4 Transmit Data Protocol - S4TXDP

In this direction, the S4TXDP block automatically multiplexes data bursts received from the user-side transmit FIFO on a per-channel basis onto the SPI4 line using standard SPI4 port switching "control words". It uses the sop, eop, abt, and port ID fields received from the user to know when to start, stop, abort, or switch the channel on the SPI4 line. Both read and write sides of the user-side FIFO are operated at a frequency that is typically 10% greater than the equivalent line-side FIFO rate at 64 bits wide in order to carry out a "packing" operation (20% for 128b mode). Packing is required for all cases where the end-of-packet byte does not result in a fully valid 64-bit FIFO entry. In

this case, there is SPI4 line bandwidth available that can only be taken advantage of through over-speed at the user-side FIFO and in the aligner. The amount of instantaneous over-speed required is reduced by averaging the demand for over-speed over time through the smaller line-side FIFO.

User data is written into TxFIFO1 based on the availability of user data to transmit, availability of near-end FIFO space, and availability of FIFO space at the far end of the SPI4 link. The user-side transmit FIFO is either 4K or 8K bytes depending upon mode and is organized as 512 locations x 80 (64b) or 144 (128b) bits. User logic should monitor the Transmit FIFO Almost Full ('TxF1AF') signal as it writes data and control information into the FIFO. When 'TxF1AF' is asserted, writing should be suspended until the Transmit FIFO Almost Empty ('TxF1AE) signal is asserted. Thresholds associated with the almost empty and full flags are real-time controllable via top-level signal array connections to the core and can be set to optimize a minimum or maximum data transfer amount into the FIFO. These thresholds also allow the user to configure the rather large user-side FIFO for "shallow" mode operation that may be needed in some applications to ensure that there is not a large amount of data committed to the line when flow controlled.

The Aligner formats data read from the user-side FIFO into SPI4 control word encapsulated data segments and/or whole packets and writes the data into the line-side FIFO. The Aligner monitors the user-side Transmit FIFO Empty ('TxF1E') signal, reading data and control information when TxF1E is deactivated, and generates the appropriate SPI4 control word containing a DIP-4 parity calculation and control directives (sop, eop, cnt, abt, port ID, etc.) for each packet segment. Data is continually read and transmitted from the user-side FIFO until the 'TxF1E' asserts. If the FIFO empties in the middle of a packet, the segment is terminated with an Idle control word and the SPI4 line goes idle. Transmission resumes when the user-side FIFO is again loaded with data, which can be associated with the same or different channel. Once the user-side begins loading a segment of data into the FIFO, the Aligner block will not be able to over-run the segment as long as the user writes the segment into the FIFO on consecutive clock cycles. This FIFO is operated in a synchronous mode given user loading and Aligner functions both require the over-speed System Data Clock ('SDCK'). This synchronous operation minimizes the response time for flag generation through the FIFO. Before the Aligner block is allowed to transmit data toward the SPI4 line, the associated input direction status channel must be properly framed ('TxSTAERR' inactive). The Aligner will continually send training control and data sequences until this condition has been met.

The timing domains between the user-side System Data Clock ('SDCK') and the SPI4 line-side transmit clock ('TxS4LS\_CK') are crossed at the line-side FIFO - TxFIFO2. The line-side FIFO is 4352 or 8704 bytes organized as 64 locations x 68 or 136 bits. A detailed description of SPI4 core clocking and synchronization is given in a subsequent section of this document. The line-side FIFO can be optionally protected with four bits of parity generation and checking (see signal description for 'TxF2PERR' in "Signal Descriptions" on page 24) in order to ensure data integrity.

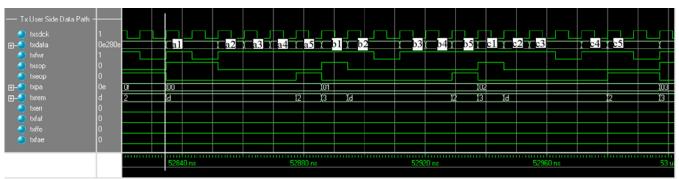

#### Transmit Data Timing Diagram Example

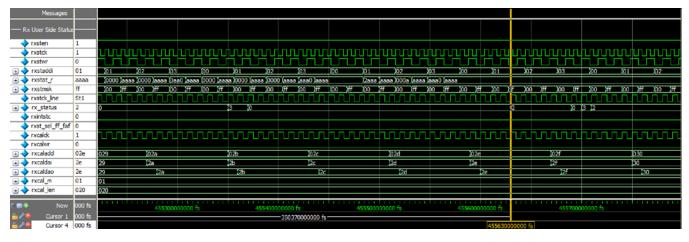

Figure 2-3 shows the transmission of three 67-byte full packets for channels 0, 1, and 2 over the S4TX transmit user FIFO interface for 128b mode. The interface operates in a synchronous fashion based on the user-supplied 'txsdck' clock input signal. This clock has over-speed relative to the equivalent SPI4 line-side as mentioned above, which is the case for this analysis. The first packet (channel 0) starts at time 52834ns in response to available data to send and an inactive Transmit FIFO Almost Full signal ('txfaf') from the IP core and is marked by the assertion of signals 'txfwr', 'txsop', 'txpa', and txdata[127:0]' from user. In the sixth clock cycle, 'txeop' and 'txrem' are asserted indicating the end of the packet and the amount of remaining bytes (0x2 = 3 bytes) in the last slice (128 bits) of data. It is in this clock cycle that signal 'txabt' (not shown) would be active if the user wants to abort the transfer. An active 'txabt' signal is acted upon by the core only when both 'dval' and 'txeop' signals are also active, otherwise it is ignored.

Although not reflected in this example, the effects of the over-speed will be noticed by the assertion of the 'txfaf' signal, mentioned above, at a regular interval assuming there is constant data to send. When asserted, the user-side must suspend writing to the user FIFO for some period of time. The simplest method is to fill the FIFO until 'txfaf' is asserted and then suspend until 'txfae' (almost empty) is asserted. This arrangement affords the smoothest and most efficient use of the SPI4 line in terms of its maximum bandwidth potential. Allowing the FIFO to run completely dry causes the pipelines, and partially the line-side FIFO, to fill with Idle control words increasing the latency of the next burst and decreasing the overall bandwidth utilization by reducing opportunities for packing the SPI4 line (no idle control word insertion - back-to-back, single control word separated packets and packet segments).

### SPI4 Transmit I/O - S4TXIO (TXGB)