# Lattice **CORE**

**CPRI IP Core User's Guide**

# **Table of Contents**

| Chapter 1. Introduction                                      | 4    |

|--------------------------------------------------------------|------|

| Quick Facts                                                  | 5    |

| Features                                                     | 5    |

| Chapter 2. Functional Description                            | 7    |

| Block Diagram                                                |      |

| General Description                                          |      |

| Signal Descriptions                                          | . 11 |

| Timing Specifications                                        |      |

| CPRI Overview                                                | . 13 |

| Functional Overview                                          | . 16 |

| User Plane IQ Data Interface                                 | . 16 |

| Ethernet Interface                                           |      |

| HDLC Interface                                               | . 21 |

| L1 Inband Protocol Interface                                 | . 22 |

| Vendor Specific Information                                  | . 22 |

| Start-up Sequence                                            | . 23 |

| Chapter 3. Parameter Settings                                | . 24 |

| CPRI Configuration Dialog Box                                |      |

| Generation Options                                           |      |

| Eval Configuration                                           |      |

| Programmable Parameters                                      |      |

| Chapter 4. IP Core Generation                                |      |

| Licensing the IP Core                                        |      |

| Getting Started                                              |      |

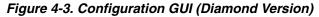

| IPexpress-Created Files and Top Level Directory Structure    |      |

| Instantiating the Core                                       |      |

| Running Functional Simulation                                |      |

| Using Aldec Active-HDL                                       |      |

| Using Mentor Graphics ModelSim                               |      |

| Synthesizing and Implementing the Core in a Top-Level Design |      |

| Hardware Evaluation                                          |      |

| Enabling Hardware Evaluation in Diamond                      |      |

| Updating/Regenerating the IP Core                            |      |

| Regenerating an IP Core in Diamond                           |      |

| Chapter 5. Application Support                               |      |

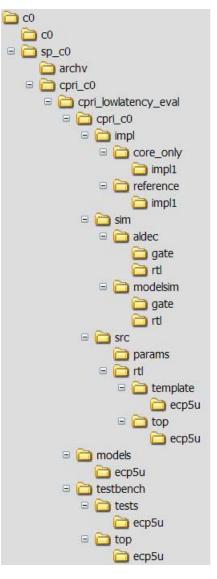

| CPRI IP Basic Configuration Top-Level Reference Design       |      |

| Test Bench                                                   |      |

| Register Descriptions                                        |      |

| Chapter 6. Support Resources                                 | . 45 |

| Lattice Technical Support                                    |      |

| E-mail Support                                               |      |

| Local Support                                                |      |

| Internet                                                     |      |

| IEEE                                                         | -    |

| References                                                   |      |

| LatticeECP3                                                  | -    |

| ECP5                                                         |      |

| Revision History                                             | -    |

| Appendix A. Resource Utilization                             |      |

| · · · · · · · · · · · · · · · · · · ·                        |      |

© 2014 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

### **Table of Contents**

| LatticeECP3 FPGAs4    | 47 |

|-----------------------|----|

| Ordering Part Number4 | 47 |

| ECP5 FPGAs            | 47 |

| Ordering Part Number4 | 47 |

This document provides technical information about the Lattice Common Public Radio Interface (CPRI) IP core. This IP core together with SERDES and Physical Coding Sublayer (PCS) functionality integrated in the LatticeECP3<sup>™</sup> and ECP5<sup>™</sup> FPGAs implements the physical layer of the CPRI specification and interleaves IQ data with synchronization, control and management information. It can be used to connect Radio Equipment Control (REC) and Radio Equipment (RE) modules.

Two CPRI core configurations are supported. The "basic" core configuration implements all of the capabilities required to support the physical layer of the CPRI specification, except specific requirements related to link delay accuracy. The "low latency" core configuration is equivalent to the basic configuration, but includes a modified SERDES/PCS interface that supports the ability to manage the variability in the absolute latency for data transmission through the core to meet the stringent CPRI link delay accuracy requirements.

The remainder of this document focuses on the detailed specifications associated with implementing and using the basic CPRI IP configuration. Areas of difference between the basic and low latency configurations are highlighted. Complete details on the implementation and use of the low latency configuration are included in IPUG74, CPRI IP Core Low Latency Variation Design Considerations User's Guide.

The CPRI soft-core comes with the following documentation and files:

- Data sheet

- Protected netlist/database

- · Behavioral RTL simulation model

- · Source files for instantiating and evaluating the core

The CPRI IP core supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited period of time (approximately four hours) without requiring the purchase of an IP license. It may also be used to evaluate the core in hardware in user-defined designs. Details for using the hardware evaluation capability are described in the Hardware Evaluation section of this document.

In the following text, transmit refers to data flow from the user application logic to the CPRI link. Receive refers to data flow from the CPRI link to the user application logic. Downlink refers to the direction of data flow from REC to RE, and uplink refers to the direction of data flow from RE to REC.

The Lattice CPRI core is compliant with the version 3.0 CPRI specification. Note however that the core does not directly support requirement R-31 (line-rate autonegotiation). Lattice supports dynamic switching between full and half rate line settings (i.e., 614M/1.2G or 1.2/2.4G) but switching dynamically between all line rates is not supported since some PCS/SERDES bit settings need to be re-programmed through the SCI to support reliable data transfer. It is anticipated that in most network applications, line rate negotiation will be established/managed at the system level and there is nothing in the IP core that precludes supporting such capability.

# **Quick Facts**

Table 1-1 gives quick facts about the CPRI IP core.

### Table 1-1. CPRI IP Core Quick Facts

|                      |                          | CPRI IP Core                                                            |                    |  |  |  |  |

|----------------------|--------------------------|-------------------------------------------------------------------------|--------------------|--|--|--|--|

|                      |                          | Across All IP Configurations                                            |                    |  |  |  |  |

| Core Requirements    | FPGA Families Supported  | d Lattice ECP3, ECP5                                                    |                    |  |  |  |  |

| Core nequirements    | Minimal Device Supported | LFE3-35E-6FTN256C                                                       | LFE5UM-85F-7MG381C |  |  |  |  |

|                      | Data Path Width          | 8-40                                                                    | bits               |  |  |  |  |

| Resource Utilization | LUTs                     | 1400-1600                                                               | 1600-2000          |  |  |  |  |

|                      | sysMEM EBRs              | 2-6                                                                     |                    |  |  |  |  |

|                      | Registers                | 1500-1700                                                               | 1500-1700          |  |  |  |  |

|                      | Lattice Implementation   | Lattice Diamond® 3.2                                                    |                    |  |  |  |  |

| Design Tool Support  | Synthesis                | Synopsys <sup>®</sup> Synplify Pro <sup>®</sup> for I-2013.09L-SP1 beta |                    |  |  |  |  |

| Design 1001 Support  | Simulation               | Aldec <sup>®</sup> Active HDL <sup>™</sup> 9.2 Lattice Edition          |                    |  |  |  |  |

|                      | Sinulation               | Mentor Graphics® ModelSim® 6.6E SE                                      |                    |  |  |  |  |

### Features

The following features apply to the basic CPRI core configuration:

- Supports the physical link layer (Layer 1) of the CPRI specification

- Supports four standard bit rates of the CPRI specification

- 614.4 Mbps

- 1228.8 Mbps

- 2457.6 Mbps

- 3072 Mbps

- Supports 8b/10b encoding/decoding performed in the PCS/SERDES

- Supports code-violation detection performed in the PCS/SERDES

- Performs CPRI Hyperframe Framing

- Performs interleaving of IQ data, sync, C&M data, and vendor specific information

- Provides an 8-, 16-, or 32-bit parallel interface for IQ data

- Performs subchannel mapping:

- Supports a slow C&M channel based on a serial HDLC interface at standard bit rates (240 Kbps, 480 Kbps, 960 Kbps, and 1920 Kbps). The HDLC framer, if needed, must be provided as a separate IP core.

- Supports a fast C&M channel based on a serial Ethernet interface (84.48 Mbps max.) to the user logic, a non-standard rate MII Ethernet interface to a MAC, or a 100 Mbps MII interface to a PHY device. Accepts a user-selected pointer to the CPRI subchannel where the Ethernet link starts. The Ethernet MAC function is provided as a separate IP core.

- Performs synchronization and timing as defined in section 4.2.8 of the CPRI Specification

- Supports the L1 Inband Protocol

- Provides a parallel interface for merging vendor specific data into the CPRI frame

- Provides a start-up sequence state machine in hardware for both REC and RE nodes which performs:

- Synchronization and Rate Negotiation

- C&M Plane setup

- Performs Link Maintenance as defined in section 4.2.10 of the CPRI Specification:

- LOS detection

- LOF detection

- RAI indication

- Optional top-level template that implements user registers for control and status management

- Optional 8-bit register interface through the JTAG port

The low latency CPRI core configuration supports all of the features specified for the basic core configuration with the following key exceptions/modifications:

- Supported for LatticeECP3 and ECP5 FPGA families only

- Supports 1228.8 Mbps, 2457.6 Mbps, and 3072 Mbps line bit rates only.

- FPGA bridge FIFOs in the SERDES/PCS (DCU in ECP5) block are bypassed in both the receive and transmit directions

- Logic blocks supporting receive direction 10b word alignment, 10b/8b decoding and core-violation detection in the SERDES/PCS (DCU in ECP5) block are bypassed and the corresponding functions are implemented in FPGA gates

Chapter 2:

This chapter provides a functional description of the CPRI IP core.

# **Block Diagram**

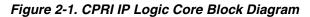

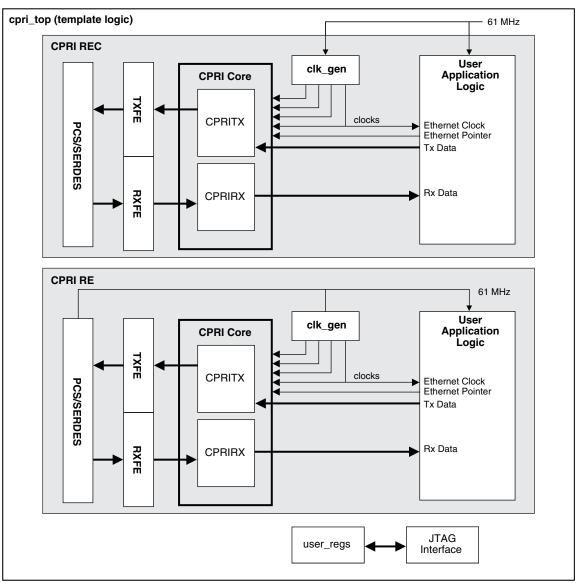

The complete CPRI IP core includes two key components, the CPRI IP logic core and separate logic blocks that support the interface between the logic core and the integrated PCS/SERDES block.

A block diagram of the CPRI IP logic core is shown in Figure 2-1. The CPRI IP logic core is identical for both the basic and low latency core configurations.

# **General Description**

The complete CPRI IP core includes two key components, the CPRI IP logic core and separate logic blocks that support the interface between the logic core and the SERDES and PCS (DCU for ECP5) functions integrated in the FPGA. Figure 2-1 shows a block diagram of the CPRI IP logic core. The CPRI IP logic core is identical for both the basic and low latency core configurations. Control and status parameters specifying core functionality are managed via bit-mapped I/O that may be hard-wired or interfaced to programmable registers, providing users with optimal flexibility in defining static and/or dynamic management of the various functional parameters needed for their particular applications.

The CPRI IP Core supports a parallel user IQ data interface, a serial HDLC interface, a serial Ethernet interface, a parallel interface for vendor specific information, and provides individual signals which allow the user to insert/receive L1 Inband Protocol information to/from the CPRI link. The interfaces to the user application are by design very simple to allow the CPRI IP Core to be as flexible as possible. All higher-level functions such as Ethernet MAC functions, HDLC framing, etc. are all intended to be done outside of the CPRI IP Core in user logic or in other Lattice IP Modules.

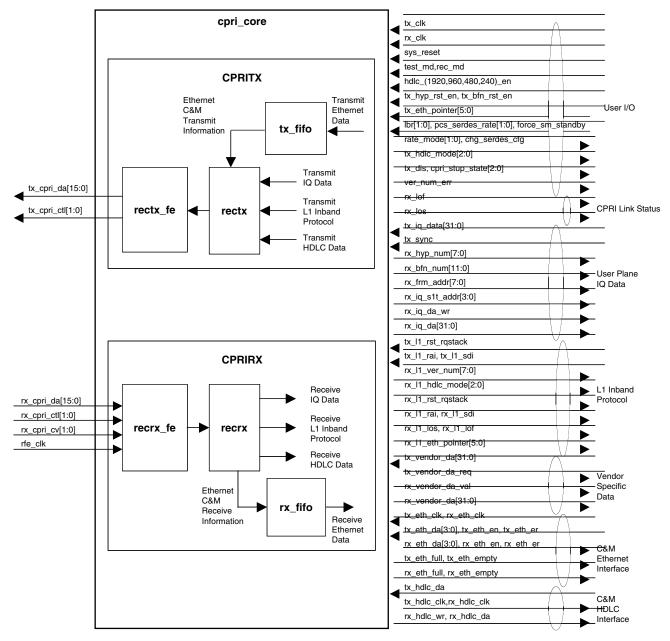

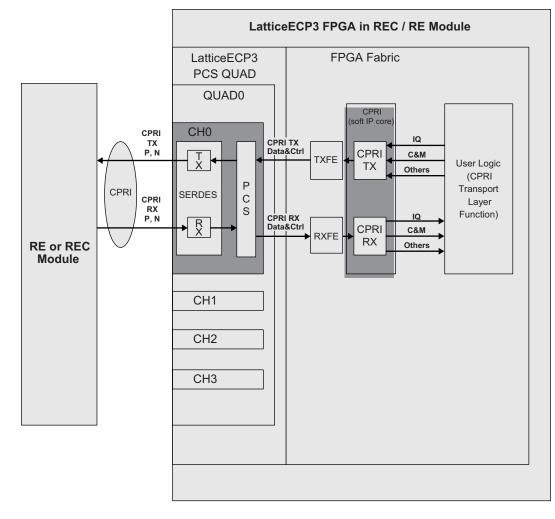

Figure 2-2 shows a system level block diagram of CPRI IP core instantiated in a ECP5 series FPGA. As indicated in Figure 2-2, additional IP cores may be instantiated to support multiple RP3 data links. Also shown in Figure 2-2 are RXFE and TXFE logic blocks that support the interface between IP logic core and the integrated SERDES/PCS (DCU for ECP5) block.

Figure 2-2. CPRI IP Core System Block Diagram in LatticeECP3

Figure 2-3. CPRI IP Core System Block Diagram in ECP5

Included in the CPRI IP core evaluation package is a reference module that provides an example of how the IP core is instantiated at the top level, as shown in Figure 2-4. This top-level template is provided in RTL format and provides a good starting point from which the user can begin to add custom logic to a design.

Figure 2-4. Top-Level Template Included with CPRI IP Core (Includes Example Connections for using IP Core in REC and RE Modes)

The CPRI IP logic core is provided in NGO format. For the basic CPRI IP core configuration, the rxfe and txfe logic blocks are provided in RTL format and may be used as-is or modified as necessary. For the low latency CPRI IP core configuration, the rxfe block also includes soft PCS logic in NGO format as described in detail in IPUG74, *CPRI IP Core Low Latency Variation Design Considerations User's Guide.*

Also included in the top-level netlist is a user side driver/monitor module and register implementation module for optional use. These included modules are used in the evaluation simulation capability. The driver/monitor module is used to provide data in the transmit direction and verify data in the receive direction. The register implementation module is used to control the IP core. The overall top-level design can be used without modification in the debugging phase on physical hardware needing only a CPRI source/sink capability to verify IP core operation.

# **Signal Descriptions**

### Table 2-1. CPRI I/O Signal Descriptions

| Signal Name      | Direction<br>Input/Output | Width<br>(Bits) | Description                                                                                                                                                                        |  |  |  |

|------------------|---------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| System Clock and | Reset                     |                 | ·                                                                                                                                                                                  |  |  |  |

| tx_clk           | I                         | 1               | 61 MHz system clock input                                                                                                                                                          |  |  |  |

| rx_clk           | I                         | 1               | 61 MHz receive side clock input                                                                                                                                                    |  |  |  |

| sys_reset        | I                         | 1               | Active low reset                                                                                                                                                                   |  |  |  |

| txrst            | I                         | 1               | Active high Ethernet FIFO reset (in TX CPRI)                                                                                                                                       |  |  |  |

| rxrst            | I                         | 1               | Active high Ethernet FIFO reset (in RX CPRI)                                                                                                                                       |  |  |  |

| User Interface   | 1                         |                 |                                                                                                                                                                                    |  |  |  |

| rec_md           | I                         | 1               | Select between REC or RE mode, REC = 1                                                                                                                                             |  |  |  |

| test_md          | I                         | 1               | test_mod = 1, speed up the timer for simulation                                                                                                                                    |  |  |  |

| hdlc_240_en      | I                         | 1               | 240 KHz HDLC frequency enable                                                                                                                                                      |  |  |  |

| hdlc_480_en      | I                         | 1               | 480 KHz HDLC frequency enable                                                                                                                                                      |  |  |  |

| hdlc_960_en      | I                         | 1               | 960 KHz HDLC frequency enable                                                                                                                                                      |  |  |  |

| hdlc_1920_en     | I                         | 1               | 1920 KHz HDLC frequency enable                                                                                                                                                     |  |  |  |

| hdlc_2400_en     | I                         | 1               | 2400 KHz HDLC frequency enable (only available in 3G)                                                                                                                              |  |  |  |

| auto_cnt         | I                         | 1               | For master CPRI TX only, update Z64, Z128, Z192 with hyp_cnt_init and bfn_cnt_init when low. When it is high, control words are updated by internal counter.                       |  |  |  |

| hyn_cnt_init     | I                         | 8               | For master CPRI TX only, used for two purposes:<br>Auto_cnt = 0: update Z64<br>Auto_cnt = 1: update internal hfn counter when tx_sync = 1 and<br>tx_hyp_rst_en = 1                 |  |  |  |

| bfn_cnt_init     | I                         | 12              | For master CPRI TX only, used for two purposes:<br>Auto_cnt = 0: update Z128, Z192<br>Auto_cnt = 1: update internal bfn counter when tx_sync = 1 and<br>tx_bfn_rst_en = 1          |  |  |  |

| tx_hyp_rst_en    | I                         | 1               | Transmit side hype frame counter reset enable during tx_sync active                                                                                                                |  |  |  |

| tx_bfn_rst_en    | I                         | 1               | Transmit side bfn counter reset enable during tx_sync active                                                                                                                       |  |  |  |

| tx_eth_pointer   | I                         | 6               | Transmit Ethernet pointer value                                                                                                                                                    |  |  |  |

| lbr_en           | I                         | 2               | [1:0] – Maximum CPRI Line bit rate enabled by user                                                                                                                                 |  |  |  |

| force_sm_standby | I                         | 1               | Force startup state machine to standby                                                                                                                                             |  |  |  |

| pcs_serdes_rate  | I                         | 2               | CPRI line rate supported by PCS/SERDES                                                                                                                                             |  |  |  |

| rate_mode        | 0                         | 2               | Final negotiated CPRI Line bit rate after start-up sequence completes                                                                                                              |  |  |  |

| chg_serdes_cfg   | 0                         | 1               | Indicator to program the SERDES for different rate                                                                                                                                 |  |  |  |

| tx_hdlc_mode     | 0                         | 3               | Transmit side HDLC negotiated bit rate                                                                                                                                             |  |  |  |

| tx_dis           | 0                         | 1               | For RE mode disable transmit side active high                                                                                                                                      |  |  |  |

| cpri_stup_stat   | 0                         | 3               | Start up sequence state<br>state 1 = synchronization<br>state 2 = protocol setup<br>state 3 = c/m plane setup<br>state 4 = interface and vendor negotiation<br>state 5 = operation |  |  |  |

| ver_num_err      | 0                         | 1               | Version number error                                                                                                                                                               |  |  |  |

| CPRI Link Status | J ]                       |                 | 1                                                                                                                                                                                  |  |  |  |

| rx_lof           | 0                         | 1               | Receive side Loss of Frame                                                                                                                                                         |  |  |  |

| rx_los           | 0                         | 1               | Receive side Loss of Signal                                                                                                                                                        |  |  |  |

### Table 2-1. CPRI I/O Signal Descriptions (Continued)

| Signal Name        | Direction<br>Input/Output | Width<br>(Bits)                                                                                                                          | Description                                  |  |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| User Plane IQ Data | Signals                   |                                                                                                                                          |                                              |  |

| tx_iq_da           | I                         | 32<br>(40 for 3G)                                                                                                                        | Transmit side IQ data                        |  |

| tx_sync            | I                         | 1                                                                                                                                        | Transmit side IQ data sync                   |  |

| rx_hyp_num         | 0                         | 8                                                                                                                                        | Receive side hyper frame number              |  |

| rx_bfn_num         | 0                         | 12                                                                                                                                       | Receive side basic frame number              |  |

| rx_frm_addr        | 0                         | 8                                                                                                                                        | Receive side frame address                   |  |

| rx_iq_slt_addr     | 0                         | 4                                                                                                                                        | Receive side IQ data slot address            |  |

| rx_iq_da_wr        | 0                         | 1                                                                                                                                        | Receive side IQ data write enable            |  |

| rx_iq_da           | 0                         | 32<br>(40 for 3G)                                                                                                                        | Receive side IQ data                         |  |

| L1 Inband Protoco  | l Signals                 | -                                                                                                                                        |                                              |  |

| tx_l1_rst_rqstack  | I                         | 1                                                                                                                                        | Transmit reset request or acknowledge        |  |

| tx_l1_rai          | I                         | 1                                                                                                                                        | Transmit Remote Alarm indication             |  |

| tx_l1_sdi          | I                         | 1                                                                                                                                        | Transmit SAP Defect Indication               |  |

| rx_l1_ver_num      | 0                         | 8                                                                                                                                        | Received version number                      |  |

| rx_l1_hdlc_mode    | 0                         | 3                                                                                                                                        | Receive side HDLC negotiated bit rate        |  |

| rx_l1_rst_rqstack  | 0                         | 1                                                                                                                                        | Receive reset request or acknowledge         |  |

| rx_l1_rai          | 0                         | 1                                                                                                                                        | Receive Remote Action Indication             |  |

| rx_l1_sdi          | 0                         | 1                                                                                                                                        | Receive SAP Defect Indication                |  |

| rx_l1_los          | 0                         | 1                                                                                                                                        | Receive Loss of Signal                       |  |

| rx_li_lof          | 0                         | 1                                                                                                                                        | Receive Loss of Frame                        |  |

| rx_l1_eth_pointer  | 0                         | 6                                                                                                                                        | Receive side Ethernet pointer value          |  |

| Vendor-Specific Da | ata Interface Sig         | gnals                                                                                                                                    |                                              |  |

| tx_vendor_da       | I                         | 32<br>(40 for 3G)                                                                                                                        | Vendor-specific transmit data                |  |

| tx_vendor_da_req   | 0                         | 1                                                                                                                                        | Vendor-specific transmit data request        |  |

| rx_vendor_da_val   | 0                         | 1                                                                                                                                        | Vendor-specific receive data valid           |  |

| rx_vendor_da       | 0                         | 32<br>(40 for 3G)                                                                                                                        | Vendor-specific receive data                 |  |

| CPRI to SERDES S   | ignals                    |                                                                                                                                          |                                              |  |

| tx_cpri_ctl        | 0                         | 2                                                                                                                                        | Transmit side CPRI control to SERDES         |  |

| tx_cpri_da         | 0                         | 16<br>(40 for 3G<br>applies to<br>tx-cpri_da &<br>rx_cpri_da)<br>(5 for 3G<br>applies to<br>tx_cpri_ctl,<br>rx_cpri_ctl &<br>rx_cpri_cv) | Transmit side CPRI data to SERDES            |  |

| rx_cpri_ctl        | I                         | 2                                                                                                                                        | Receive side CPRI control from SERDES        |  |

| rx_cpri_da         | I                         | 16                                                                                                                                       | Receive side CPRI data from SERDES           |  |

| rx_cpri_cv         | I                         | 2                                                                                                                                        | Receive side CPRI code violation from SERDES |  |

| slip_rxfe          | 0                         | 1                                                                                                                                        | Receive side slip to get "BC" in low byte    |  |

| Signal Name               | Direction<br>Input/Output | Width<br>(Bits) | Description                                                        |

|---------------------------|---------------------------|-----------------|--------------------------------------------------------------------|

| C&M Ethernet Inter        | face Signals              |                 |                                                                    |

| tx_eth_clk,<br>rx_eth_clk | I                         | 1               | Transmit Ethernet clock, Receive Ethernet clock                    |

| tx_eth_da                 | I                         | 4               | Transmit Ethernet data (1 bit wide in Serial mode)                 |

| tx_eth_en                 | I                         | 1               | Transmit Ethernet data enable (not equipped in Serial mode)        |

| tx_eth_er                 | I                         | 1               | Transmit Ethernet error (not equipped in Serial mode)              |

| rx_eth_da                 | 0                         | 4               | Receive Ethernet data (1 bit wide in Serial mode)                  |

| rx_eth_en                 | I                         | 1               | Receive Ethernet data enable (not equipped in Serial mode)         |

| rx_eth_er                 | I                         | 1               | Receive Ethernet error (not equipped in Serial mode)               |

| tx_eth_almost_full        | 0                         | 1               | Transmit Ethernet FIFO almost full. This is for user flow control. |

| tx_eth_empty              | 0                         | 1               | Transmit Ethernet FIFO empty                                       |

| rx_eth_full               | 0                         | 1               | Receive Ethernet FIFO full                                         |

| rx_eth_empty              | 0                         | 1               | Receive Ethernet FIFO empty                                        |

| rx_eth_fifo_err           | 0                         | 2               | Receive Ethernet FIFO error flag (only for Fixed mode)             |

| C&M HDLC Interfac         | ce Signals                |                 |                                                                    |

| tx_hdlc_da                | I                         | 1               | Transmit HDLC data                                                 |

| tx_hdlc_clk               | 0                         | 1               | Transmit HDLC clock                                                |

| rx_hdlc_clk               | 0                         | 1               | Receive HDLC clock                                                 |

| rx_hdlc_wr                | 0                         | 1               | Receive HDLC write                                                 |

| rx_hdlc_da                | 0                         | 1               | Receive HDLC data                                                  |

## **Timing Specifications**

Refer to DS1021, *LatticeECP3 Family Data Sheet* and DS1044, *ECP5 Family Data Sheet* for detailed SERDES and FPGA interface timing and electrical specifications.

## **CPRI** Overview

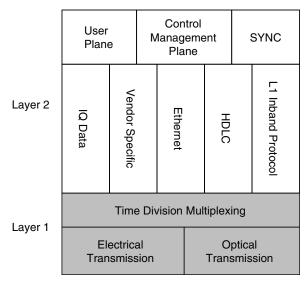

Figure 2-5 shows the CPRI layer 1 and layer 2 protocols. The CPRI IP core interleaves user IQ (in-phase and quadrature) data with control and management (C&M) data into the frame and hyperframe formats specified by the CPRI Specification and shown in Figure 2-6 and Figure 2-7, respectively.

Figure 2-5. CPRI Protocol Overview

#### Figure 2-7. CPRI Hyperframe Format

| Ns=0064Comma Byte, Synchronization and Tim1165Slow C&M Link2266pL1 Inband Protocol3367Reserved44Reserved58Reserved688Reserved8888988108810881088                                                                                  |      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 266pL1 Inband Protocol3367Reserved44Reserved5Reserved6Reserved78Reserved9Reserved                                                                                                                                                 | ning |

| 3       3       67       Reserved         4       4       Reserved       Reserved         5       8       Reserved       Reserved         8       8       Reserved       Reserved         9       8       Reserved       Reserved |      |

| 44AReserved5AAReserved6AAReserved7AAReserved8AAReserved9AAReserved                                                                                                                                                                |      |

| 5Reserved6Reserved7Reserved8Reserved9Reserved                                                                                                                                                                                     |      |

| 6   Reserved     7   Reserved     8   Reserved     9   Reserved                                                                                                                                                                   |      |

| 7   Reserved     8   Reserved     9   Reserved                                                                                                                                                                                    |      |

| 8   Reserved     9   Reserved                                                                                                                                                                                                     |      |

| 9 Reserved                                                                                                                                                                                                                        |      |

|                                                                                                                                                                                                                                   |      |

| 10 Bosonrod                                                                                                                                                                                                                       |      |

|                                                                                                                                                                                                                                   |      |

| 11 Reserved                                                                                                                                                                                                                       |      |

| 12 Reserved                                                                                                                                                                                                                       |      |

| 13 Reserved                                                                                                                                                                                                                       |      |

| 14 14 Reserved                                                                                                                                                                                                                    |      |

| 15 15 79 143 207 Reserved                                                                                                                                                                                                         |      |

| 16 16 80 144 208 Vendor-specific                                                                                                                                                                                                  |      |

| 17 17 Vendor-specific                                                                                                                                                                                                             |      |

| 18 Vendor-specific                                                                                                                                                                                                                |      |

| •                                                                                                                                                                                                                                 |      |

|                                                                                                                                                                                                                                   |      |

| Vendor-specific                                                                                                                                                                                                                   |      |

| Pointer p -> Fast C&M Link                                                                                                                                                                                                        |      |

| · · ·                                                                                                                                                                                                                             |      |

| :                                                                                                                                                                                                                                 |      |

| 61 61                                                                                                                                                                                                                             |      |

| 62 62 126 190 254                                                                                                                                                                                                                 |      |

| 63 63 127 191 255                                                                                                                                                                                                                 |      |

Four possible line rates for the CPRI frame are supported, as shown in Table 2-2. The maximum line bit rate that the core must support is selected by setting the lbr\_en[1:0] input signals. Once the maximum line bit rate has been selected, all lower line bit rates are automatically enabled. The bit rate between the REC and RE is then negotiated between the transmitting and receiving ends by the start-up sequence state machine within the CPRI IP core.

#### Table 2-2. CPRI Line Rates

| CPRI Line Bit Rate | Rate (Mbps) | lbr_en[1:0]                 |

|--------------------|-------------|-----------------------------|

| Option 1           | 614.4       | 00                          |

| Option 2           | 1228.8      | 01                          |

| Option 3           | 2457.6      | 1X or 10 (LatticeECP3 only) |

| Option 4           | 3072        | 11 (LatticeECP3 only)       |

## **Functional Overview**

A block diagram of a typical LatticeECP3 CPRI application is shown in Figure 2-2 and a block diagram of a typical ECP5 CPRI application is shown in Figure 2-3. These examples show four CPRI link transceivers implemented in a LatticeECP3 and an ECP5 device. The major functional blocks in the example are the CPRI Soft IP core, the PCS/SERDES block, and the user application logic. The CPRI IP Core (cpri\_core), shown in Figure 2-1, consists of two major functional blocks, the transmitter (CPRITX) and the receiver (CPRIRX). One side of each of these two blocks interfaces to the PCS/SERDES module, and the other side interfaces to the user logic that implements the data link and higher layers of the CPRI protocol.

The CPRI IP Core multiplexes user IQ data with synchronization and C&M data. The IP core is being designed with very simple and versatile interfaces for transferring data to the user application logic.

IQ data is transferred between the IP core and the user logic using a parallel data interface. In the transmit direction, the user application provides a sync pulse which determines the start of a CPRI BFN (every 150 hyperframes) frame. In the receive direction, the IP core transfers IQ data to the user application along with framing information recovered from the CPRI link.

In the transmit direction, the CPRI IP core accepts user C&M data at either the HDLC and/or the Ethernet interface and interleaves that data with the user IQ data into the CPRI frame. In the receive direction, C&M data received on the CPRI link is disinterleaved from the user IQ data, and the HDLC or Ethernet encapsulated data is presented to the user at either the HDLC or Ethernet interfaces of the CPRI IP core.

The C&M data can be encapsulated in either HDLC (slow channel) or Ethernet (fast channel) as desired by the user. For HDLC, the CPRI IP Core only performs the interleaving of the C&M data with user IQ data. It does not provide any of the HDLC Level 2 functions such as framing and serial to parallel conversion. These functions must be done in the user application logic or in another IP module. For Ethernet, three modes are provided. In mode 1, the core does not provide the serial to parallel and 4B/5B conversion. The interface is a serial bitstream that contains 5B encoded nibbles. In mode 2, the core provides a standard MII interface that can be connected to a standard Ethernet MAC. In mode 3, the core provides an MII like interface that has the clocks as inputs instead of outputs. This interface can be connected to a PHY that is operating at the 100 Mbps standard rate.

The following sections discuss the interfaces of the IQ data, HDLC, Ethernet, and vendor information interfaces of the CPRI IP core.

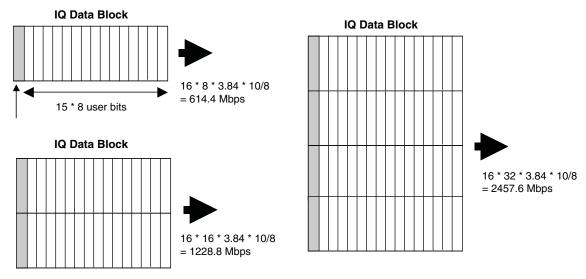

### User Plane IQ Data Interface

The user IQ data interface supports the four line rates shown in Table 2-2. Both the transmit and receive directions provide a 40-bit IQ data bus. However, the number of bits used depends on the line rate selected by the user. For the 614.4 Mbps line rate, 8 of the 32 bits on the IQ data interface are used (bits 7:0). For 1228.8 Mbps, bits 15:0 are used, and for a line rate of 2457.6 Mbps, 32 bits are used. For a line rate of 3072 Mbps, all 40 bits are used.

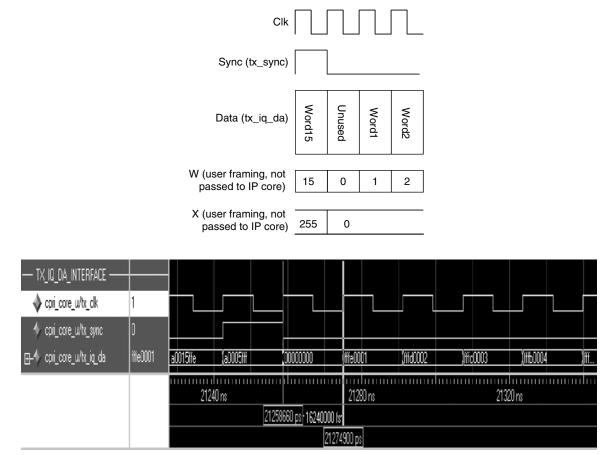

In the transmit direction, the user application must provide a sync pulse to the CPRI IP core to indicate the start of each CPRI BFN (every 150 hyperframes) frame. This sync pulse must be aligned with the IQ data, as shown in Figure 2-8.

Figure 2-8. Tx User IQ Interface Sync Pulse Alignment

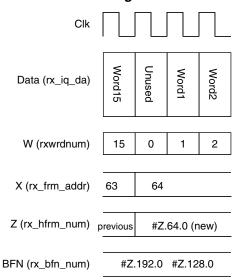

In the receive direction, the CPRI IP Core provides IQ data to the user interface along with a word number (W), frame number (X), hyperframe number (Z), and a BFN number, as shown in Figure 2-9.

Figure 2-9. Rx IQ Interface Data and Frame Number Alignment

| - RX_IQ_INTERFACE              |          |         |    |              |       |       |         |            |        |     |            |

|--------------------------------|----------|---------|----|--------------|-------|-------|---------|------------|--------|-----|------------|

| 🔷 cpri_core_u/rx_ck            | 1        |         |    |              |       |       |         |            |        |     |            |

| ♦ cpri_core_u/rx_iq_da_wr      | 0        |         |    |              |       |       |         |            |        |     |            |

| ⊕-∲ cpri_core_u/rx_iq_da       | ac0053ff | )ac0253 | íd | (ac0153fe    | jacil | 53ff  |         | jabfe5401  | )abid5 | 402 | jabfc5403  |

| ⊡-∲ cpri_core_u/rx_iq_slt_addr | 0        | c)d     |    | )e           | ji    |       | 0       | <u>)</u> 1 | 2      |     | <u>)</u> 3 |

| ⊡-∜ cpri_core_u/rx_frm_addr    | 40       | 31      |    |              |       |       | 40      |            |        |     |            |

| ⊡-∜ cpri_core_u/rx_hyp_num     | 05       | 04      |    |              |       |       | 05      |            |        |     |            |

| ⊡-∲ cpri_core_u/rx_bin_num     | 000      | 000     |    |              |       |       |         |            |        |     |            |

|                                |          |         |    | <u> </u><br> | 40 ns |       |         |            |        |     | 370720 ns  |

|                                |          |         |    | 0.00         |       | 37066 | 2260 ps | 01000010   |        |     | 01012010   |

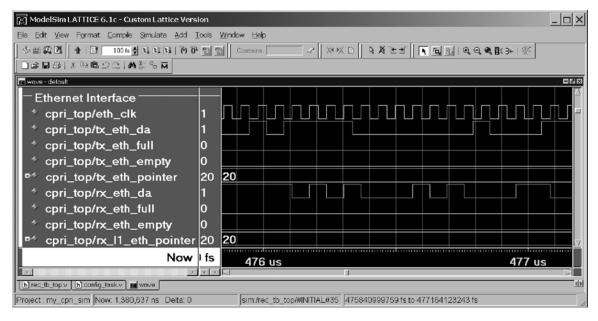

### **Ethernet Interface**

#### Mode 1 (Serial)

The CPRI IP Core Ethernet Interface transmits and receives Ethernet data to/from the user application logic using a simple serial data connection. The amount of bandwidth on the CPRI link which is allocated to Ethernet (fast C&M) data is determined by the pointer value (Z.194.0) which in turn determines which subchannel number the Ethernet data starts at within the CPRI hyperframe. The pointer value is set by the user using the tx\_eth\_pointer[7:0] inputs to the IP core. The transmitter and receiver of the REC and RE ends must be able to use the same pointer value.

Since a buffer is provided within the IP core for Ethernet data, the Ethernet interface clock between the IP core and the user application logic must be chosen such that the correct number of words are transferred between the IP core and the user's logic each frame or else the internal buffer may overrun or underrun. Due to the large number of possible pointer values available it is not practical for the IP core to generate the Ethernet interface clock. Instead, the IP core is designed such that the pointer value and the Ethernet interface clock are provided as inputs to the Core, giving the user the maximum flexibility. The template logic (cpri\_top) shown in Figure 2-10, which will be delivered with the IP core, will include an example of how to generate and connect an Ethernet interface clock frequency of 61.44 MHz. Additional clock frequencies and pointer values may be set by the user by modifying the template logic. The difficulty which will be encountered in generating various Ethernet clock frequencies and pointer values will be entirely dependent on the clock frequencies available in the user's system. This is why the

generation of the Ethernet clock frequency, and the assignment of the pointer value, must be done in the template logic and not within the IP core.

#### Figure 2-10. Ethernet C&M Interface

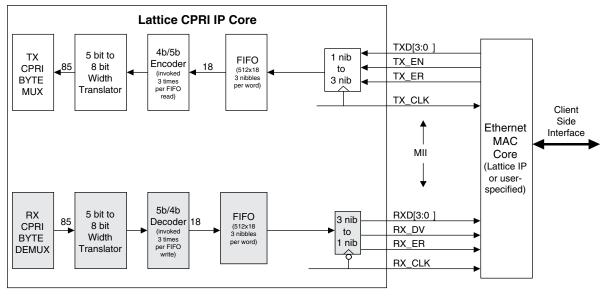

#### Mode 2 (Matched Rate MII)

The CPRI IP Core Ethernet Interface transmits and receives Ethernet data to/from the user application logic using a non-standard rate MII interface. The amount of bandwidth on the CPRI link which is allocated to Ethernet (fast C&M) data is determined by the pointer value (Z.194.0) which in turn determines which subchannel number the Ethernet data starts at within the CPRI hyperframe. The pointer value is set by the user using the tx\_eth\_pointer[7:0] inputs to the IP core.

Since a buffer is provided within the IP core for Ethernet data, the Ethernet interface clock between the IP core and the user application logic must be chosen such that the correct number of words are transferred between the IP core and the user's logic each frame or else the internal buffer may overrun or underrun. Due to the large number of possible pointer values available it is not practical for the IP Core to generate a periodic interface clock. Instead, the IP core is designed to produce a gapped clock. The Ethernet pointer and CPRI line rate are used to index a two parameter table that specifies the frequency and number of pulses contained in the gapped clock. The transmit Ethernet clock is based on the negotiated rate and transmit pointer. The receive Ethernet clock is based on the negotiated rate and the received L1 inband pointer in Z.194.0.

The core provides the 4B/5B code conversion required by the CPRI specification. The logic that interfaces the MII to CPRI byte mux/demux is shown in Figure 2-11.

Figure 2-11. Matched Rate MII CPRI Ethernet Interface

Note 1: TX\_CLK and RX\_CLK are gapped clocks with transition rates matching the effective data rate of the Fast C&M Channel specified by the pointer value in control byte #Z.194.0 and the CPRI line rate. Note 2: Both FIFOs are read and written as needed to source and sink data/control from/to the MII and CPRI mux/demux

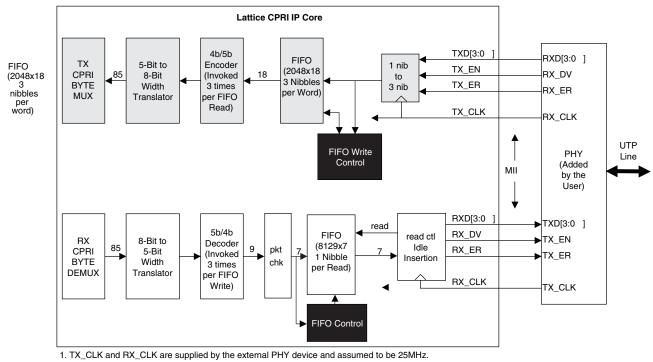

#### Mode 3 (100 Mb/s Fixed Rate MII)

The CPRI IP Core Ethernet Interface transmits and receives Ethernet data to/from the user application logic using a 100 Mbps rate MII interface. The amount of bandwidth on the CPRI link which is allocated to Ethernet (fast C&M) data is determined by the pointer value (Z.194.0) which in turn determines which subchannel number the Ethernet data starts at within the CPRI hyperframe. The pointer value is set by the user using the tx\_eth\_pointer[7:0] inputs to the IP core.

The logic needed to support mode 3 is similar to that required for mode 2 with the exception of handling the reading and writing of the FIFOs. On the transmit side, the FIFO is always written at a faster rate than it is read. This means that the reading of this FIFO is the same as mode 2. Interframe gap is only written into the FIFO if the almost empty threshold is not maintained. This prevents the FIFO from being filled with idle information. It is the responsibility of the driver of the 100 Mbps link to not over run the FIFO. There is no flow control provided to accommodate the rate mismatch between the 100Mbps link and the CPRI link. Packets must be spaced to allow enough time for the CPRI to transmit packets. On the receive side, the FIFO is always read at a faster rate than it is written. When the FIFO input data is not idle and passes basic SSD and ESD checks, it is written to the FIFO. When idle is detected on the FIFO input the FIFO is not written. When an end of packet is detected, a request is sent to the FIFO Read Control to send the packet on to the MII. A complete packet is received before it is read from the FIFO. FIFO reads begin when a request is received from the FIFO Write Control. FIFO reads continue until an end of packet is detected. When an end of packet is detected, FIFO reads stop and a minimum of 24 nibble IDLEs are supplied to the MII interface.

For 3.072 Gbps CPRI link, the MAC Ethernet MAX bandwidth is 3.84M/256\*(64-20)\*40, that is 26.4 Mbps (when Ethernet pointer p is set to 20), and MIN bandwidth is 0.6 Mbps (when Ethernet pointer p is set to 63). For example, if your real Ethernet bandwidth is 10 Mbps, please set Ethernet pointer p as 48~55, the corresponding bandwidth is 5.4~9.6 Mbps. If Ethernet pointer p is set too small, the TX FIFO for Ethernet may be empty, and the Ethernet package may be inserted by duplicated data of the partial package. If Ethernet pointer p is set too large, the TX FIFO for Ethernet may be full.

The core provides the 4B/5B code conversion required by the CPRI specification. The logic that interfaces the MII to CPRI byte mux/demux is shown in Figure 2-12.

Figure 2-12. 100 Mbps Fixed Rate MII CPRI Ethernet Interface

2. The transmit FIFO is read as needed to supply data/control to the CPRI mux.

The transmit FIFO is written as needed to sink packets from the MII and supply idle.

The receive FIFO is read and written as needed to source and sink packets from/to the MII and CPRI demux. Idle is supplied seperately.

### **HDLC Interface**

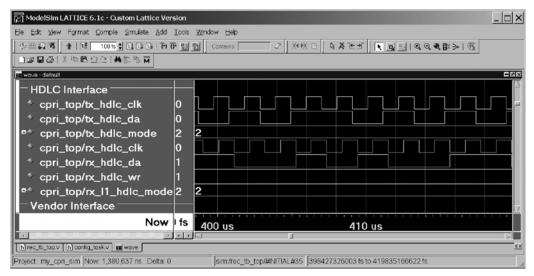

A timing diagram for the Ethernet C&M interface is given in Figure 2-13. The CPRI IP Core HDLC interface transmits and receives HDLC data to/from the user application logic using a serial data connection. The user selects the desired frequencies which the IP core will support by setting the hdlc\_(240,480,960,1920)\_en input signals. The HDLC data rates shown in Table 2-3 are supported.

The CPRI IP core HDLC Interface does not perform any HDLC framing or processing. This must be performed in the user application logic or in another IP module. The transmitter of the IP core will negotiate with the receiver of the end of the CPRI link to achieve the maximum HDLC rate possible.

#### Figure 2-13. HDLC C&M Interface

Table 2-3. HDLC Frequencies Supported

| HDLC Option | Input Signal     | HDLC Data<br>Rate (Kbps) |

|-------------|------------------|--------------------------|

| 0           | None selected    | HDLC disabled            |

| 1           | hdlc_240_en = 1  | 240                      |

| 2           | hdlc_480_en = 1  | 480                      |

| 3           | hdlc_960_en = 1  | 960                      |

| 4           | hdlc_1920_en = 1 | 1920                     |

| 5           | hdlc_2400_en = 1 | 2400                     |

#### L1 Inband Protocol Interface

The L1 Inband Protocol Interface provides signals that allow the user application logic to populate the control words listed in the CPRI specification, and to read the value of the L1 Inband Protocol control words that are received from the CPRI link.

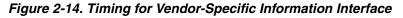

#### Vendor Specific Information

Figure 2-14 illustrates the timing of the vendor-specific information interface between the IP core and the user application logic. The IP core provides a simple parallel interface for merging vendor-specific information into the CPRI frame. The number of bytes available in the CPRI frame for vendor-specific information is dependent on the pointer value chosen. Any FIFOs required to support the bandwidth allocated to vendor-specific information must be implemented in the user logic.

The IP core provides a data request signal to the user application logic called tx\_vendor\_data\_req. When this signal goes high, the user logic must return the vendor-specific data to the IP core within six clock cycles. The user logic must continue to provide vendor-specific data until the tx\_vendor\_data\_req signal is once again asserted. If the user does not have any data to send in the vendor-specific bytes, then it must insert idle code.

In the receive direction, incoming vendor-specific information which is recovered from the CPRI link is presented to the user application logic along with a rx\_vendor\_da\_val signal. The vendor-specific information interface uses either 8, 16, or 32 (40 in 3G) of the available data bits, depending on which CPRI line bit rate has been selected. This is similar to the IQ data interface described previously.

### Start-up Sequence

The CPRI IP Core provides a start-up state machine which executes the startup state transitions as shown in Figure 30 in the CPRI Specification (Reference 2). This state machine will automatically perform the synchronization of Layer 1, and it will align the capabilities of the REC and the RE (line bit rate, protocol, C&M link speed, C&M protocol, and vendor specific signaling). The CPRI IP Core depends on software to program the correct data bus width into the LatticeECP3/ECP5 SERDES through the SCI Bus. For a 1228.8 or 2457.6 Mbps CPRI line bit rate, the SERDES must be provisioned for a 16-bit interface to the FPGA logic. For all CPRI line bit rate, the SERDES must be provisioned for an 8-bit interface to the FPGA logic to achieve low latency purpose. Since the provisioned mode of the SERDES may need to change while the start-up sequence is negotiating the CPRI line rate, a signal (chg\_serdes\_cfg) is provided to the user application logic indicating that the mode the SERDES should be programmed for needs to be changed. The user application must monitor this signal and program the SERDES to the correct mode while the REC and RE are attempting to match line bit rates. When the application has finished programming the PCS/SERDES it writes the rate that is being supported to lbr\_en[4:3].

Chapter 3:

# **Parameter Settings**

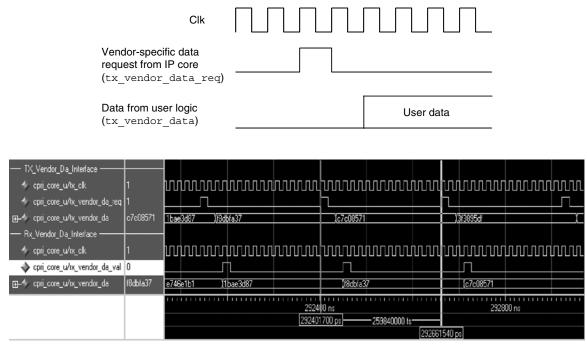

The IPexpress <sup>™</sup> and the Clarity Designer tools are used to create IP and architectural modules in the Diamond software. IPexpress is for LatticeECP3 CPRI IP Core and Clarity Designer is for ECP5 CPRI IP Core. Refer to "IP Core Generation" on page 27 for a description on how to generate the IP.

Table 3-1 provides the list of user configurable parameters for the CPRI IP core. The parameter settings are specified using the CPRI IP core Configuration GUI in IPexpress.

#### Table 3-1. IP Core Parameters

| Parameters         | Range/Options             | Default     |  |  |

|--------------------|---------------------------|-------------|--|--|

| General Options    |                           |             |  |  |

| Design Entry       | Low Latency               | Low Latency |  |  |

| Ethernet Mode      | 100 Mb/s, Matched, Serial | 100 Mb/s    |  |  |

| Eval Configuration | L                         |             |  |  |

| Synthesis Tool     | Synplify                  | Synplify    |  |  |

# **CPRI Configuration Dialog Box**

Figure 3-1 shows the CPRI Configuration dialog box.

#### Figure 3-1. CPRI Configuration Dialog Box

| Configuration \                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Generation Options<br>Design Entry:  C Low Latency C Basic<br>Ethernet Mode:                                                                                                      |

| Eval Configuration<br>Synthesis Tool: © Synplify © Precision                                                                                                                      |

| Note: Implementation of the "reference" evaluation<br>configuration is targeted to a specific device<br>and package type for each device family.<br>See user's guide for details. |

Figure 3-2 shows the CPRI PCS Configuration dialog box, it is for ECP5 CPRI IP Core only. The page 'PCS' is for ECP5UM PCS/SERDES settings. If the **PCS in debug mode** option is selected, the ECP5 DCU interface is displayed in <username>\_phy\_bb.v for debug. For further PCS configuration, click the **Advanced** button.

Figure 3-2. CPRI PCS Configuration Dialog Box

| Configuration PCS               |

|---------------------------------|

| PCS                             |

| FCS in debug mode               |

| PCS Instance Name cpri_c0_PCS   |

| PCS Instance Path //cpri_c0_pcs |

| PROTOCOL CPRI                   |

| MAX DATA RATE 3.072 Gbps        |

|                                 |

| Advanced                        |

|                                 |

Clicking the Advanced button opens the CPRI PCS Advanced Configuration Dialog Box shown in Figure 3-3.

If only one PCS is used in the project, select the Reset Sequence Select option in Control Setup tab.

If you want to revise the SERDES electric character, change the parameters on the SerDes Setup tab. Refer to TN1261, ECP5 SERDES/PCS Usage Guide.

Figure 3-3. CPRI PCS Advanced Configuration Dialog Box

| PCS                  | -             | Instance Setup \ SerDes Setup \                          | PCS Setup $\setminus$ Control Setup $\setminus$ Advanced Setup $\setminus$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------|---------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |               | Instance Protocol<br>Protocol                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      |               | Number of Channels<br>Mode                               | 1 V<br>Px and Tx V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                      | hdoutp 🔶      | TxPLL                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                      |               | Tx Max Data Rate PLL Multiplier                          | 3.072 (0.27 - 3.125) Gbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |