# NHD-2.7-12864WDW3

## **Graphic OLED Display Module**

NHD- Newhaven Display 2.7- 2.7" Diagonal Size

12864- 128 x 64 Pixel Resolution

WD- Model

W- Emitting Color: White 3- +3.3V Power Supply

## Newhaven Display International, Inc.

2661 Galvin Ct. Elgin IL, 60124

Ph: 847-844-8795 Fax: 847-844-8796

**Document Revision History**

| Revision | Date      | Description                      | Changed by |

|----------|-----------|----------------------------------|------------|

| -        | 6/9/2017  | Initial Release                  | ML         |

| 1        | 7/25/2017 | Update Storage Temperature range | ML         |

### **Functions and Features**

- 128 x 64 pixel resolution

- Built-in SSD1322 controller

- Parallel or Serial MPU interface

- Single, low voltage power supply

- Power options via on-board jumpers

- RoHS compliant

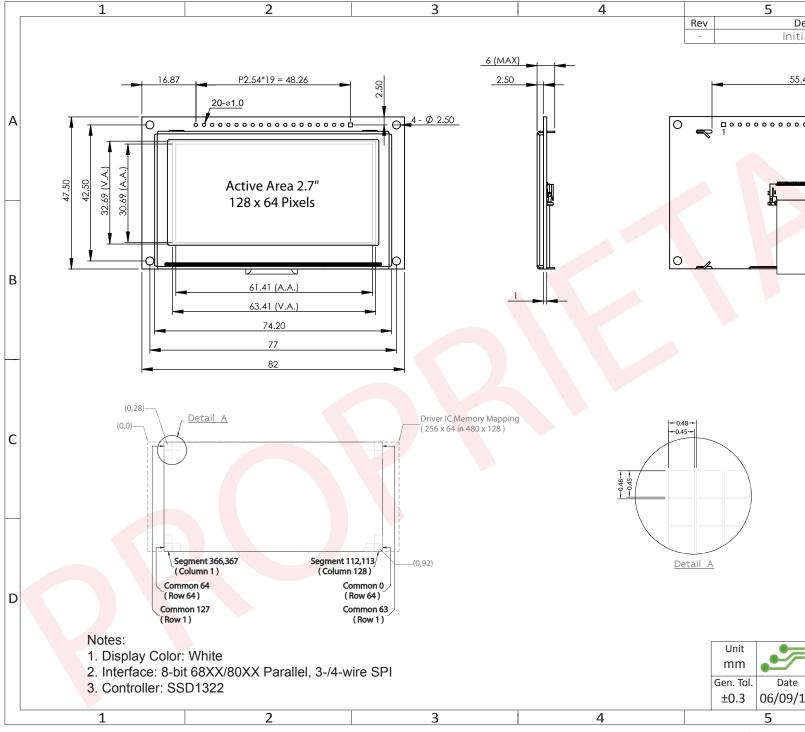

## **Mechanical Drawing**

## **Interface Description**

### Parallel Interface:

| Pin No. | Symbol        | External     | Function Description                                              |

|---------|---------------|--------------|-------------------------------------------------------------------|

|         |               | Connection   |                                                                   |

| 1       | VSS           | Power Supply | Ground                                                            |

| 2       | VDD           | Power Supply | Supply Voltage for OLED module                                    |

| 3       | N.C. (BC_VDD) | -            | No Connect by default. Can be configured to provide independent   |

|         |               |              | supply voltage (2.8V – 12V DC) for boost converter.               |

|         |               |              | (refer to On-Board Jumper Options section below)                  |

| 4       | D/C           | MPU          | Data/Command select signal, D/C=0: Command, D/C=1: Data           |

| 5       | R/W or /WR    | MPU          | 6800-interface:                                                   |

|         |               |              | Read/Write select signal, R/W=1: Read, R/W=0: Write               |

|         |               |              | 8080-interface:                                                   |

|         |               |              | Active LOW Write signal                                           |

| 6       | E or /RD      | MPU          | 6800-interface:                                                   |

|         |               |              | Operation Enable signal, falling edge triggered                   |

|         |               |              | 8080-interface:                                                   |

|         |               |              | Active LOW Read signal                                            |

| 7-14    | DB0 – DB7     | MPU          | 8-bit bi-directional Data Bus                                     |

| 15      | N.C. (VCC)    | -            | No Connect by default. Can be configured for external VCC (+15V). |

|         |               |              | (refer to On-Board Jumper Options table below)                    |

| 16      | /RES          | MPU          | Active LOW Reset signal                                           |

| 17      | /cs           | MPU          | Active LOW Chip Select signal                                     |

| 18      | /SHDN (N.C.)  | MPU          | Active LOW Shutdown control pin for boost converter               |

|         |               |              | (pulled HIGH via on-board 15kΩ resistor)                          |

|         |               |              | Can be made a No Connect by removing resistor R1.                 |

| 19      | BS1           | MPU          | MPU Interface select signal                                       |

| 20      | BS0           | MPU          | MPU Interface select signal                                       |

### Serial Interface:

| Pin No. | Symbol        | External     | Function Description                                              |

|---------|---------------|--------------|-------------------------------------------------------------------|

|         |               | Connection   |                                                                   |

| 1       | VSS           | Power Supply | Ground                                                            |

| 2       | VDD           | Power Supply | Supply Voltage for OLED module                                    |

| 3       | N.C. (BC_VDD) | -            | No Connect by default. Can be configured to provide independent   |

|         |               |              | supply voltage (2.8V – 12V DC) for boost converter.               |

|         |               |              | (refer to On-Board Jumper Options table below)                    |

| 4       | D/C           | MPU          | Data/Command select signal, D/C=0: Command, D/C=1: Data           |

|         |               |              | (tie LOW for 3-wire Serial Interface)                             |

| 5-6     | VSS           | Power Supply | Ground                                                            |

| 7       | SCLK          | MPU          | Serial Clock signal                                               |

| 8       | SDIN          | MPU          | Serial Data Input signal                                          |

| 9       | N.C.          | -            | No Connect                                                        |

| 10-14   | VSS           | Power Supply | Ground                                                            |

| 15      | N.C. (VCC)    | -            | No Connect by default. Can be configured for external VCC (+15V). |

|         |               |              | (refer to On-Board Jumper Options section below)                  |

| 16      | /RES          | MPU          | Active LOW Reset signal                                           |

| 17      | /CS           | MPU          | Active LOW Chip Select signal                                     |

| 18      | /SHDN (N.C.)  | MPU          | Active LOW Shutdown control pin for boost converter               |

|         |               |              | (pulled HIGH via on-board 15kΩ resistor)                          |

|         |               |              | Can be made a No Connect by removing resistor R1.                 |

| 19      | BS1           | MPU          | MPU Interface select signal                                       |

| 20      | BS0           | MPU          | MPU Interface select signal                                       |

### **Interface Selection**

#### **MPU Interface Pin Selections**

| Pin<br>Name | 6800 Parallel<br>8-bit interface | 8080 Parallel<br>8-bit interface | 3-wire<br>Serial<br>Interface | 4-wire<br>Serial<br>Interface |  |

|-------------|----------------------------------|----------------------------------|-------------------------------|-------------------------------|--|

| BS1         | 1                                | 1                                | 0                             | 0                             |  |

| BS0         | 1                                | 0                                | 1                             | 0                             |  |

**MPU Interface Pin Assignment Summery**

| Bus        |                      | Data/Command Interface |    |    |    |      |    |      |     |     | Control Signals |         |      |  |  |  |  |

|------------|----------------------|------------------------|----|----|----|------|----|------|-----|-----|-----------------|---------|------|--|--|--|--|

| Interface  | D7                   | D6                     | D5 | D4 | D3 | D2   | D0 | E    | R/W | /cs | D/C             | /RES    |      |  |  |  |  |

| 8-bit 6800 |                      |                        |    |    | D[ | 7:0] |    |      | Е   | R/W | /CS             | D/C     | /RES |  |  |  |  |

| 8-bit 8080 |                      |                        |    |    | D[ | 7:0] |    |      | /RD | /WR | /CS             | D/C     | /RES |  |  |  |  |

| 3-wire SPI |                      | Tie LOW NC SDIN SCLK   |    |    |    |      |    |      |     | LOW | /CS             | Tie LOW | /RES |  |  |  |  |

| 4-wire SPI | Tie LOW NC SDIN SCLK |                        |    |    |    |      |    | SCLK | Tie | LOW | /CS             | D/C     | /RES |  |  |  |  |

## **On-Board Jumper Options**

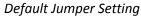

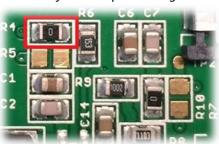

**Default Jumper Setting**

| R4    | R5   | R5 R7 Description |                                                                                                                                                                     |  |  |  |  |  |  |

|-------|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Close | Open | Open              | (default) OLED controller and boost converter + OLED panel are powered from VDD (pin #2). This allows the full module to be powered by a single low-voltage supply. |  |  |  |  |  |  |

**Jumper Option #1 - Independent Supply Voltage for Boost Converter** (BC\_VDD)

| R4   | R5    | R7   | Description                                                                                                                                                                                                                                                 |

|------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open | Close | Open | Boost converter + OLED panel are powered from BC_VDD (pin #3). OLED controller is still powered from VDD (pin #2). This allows for increased efficiency through the boost converter, by allowing a supply voltage up to +12V at its input, BC_VDD (pin #3). |

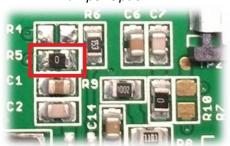

Jumper Option #2 - External Supply Voltage for OLED Panel (VCC)

| R4   | R5   | R7    | Description                                                                                                                                                                                                               |

|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Open | Open | Close | OLED panel is powered from VCC (pin #15) – boost converter is not used. OLED controller is still powered from VDD (pin #2). This allows for maximum module efficiency, and drastically reduced total current consumption. |

Jumper Option #1

Jumper Option #2

For detailed electrical information on each jumper option, please see the Electrical Characteristics table below.

### **Electrical Characteristics**

Values for Current shown below are based on the recommended initialization provided on page 12.

| Item                               | Symbol               | Condition             | Min.    | Тур. | Max.    | Unit |  |  |  |  |

|------------------------------------|----------------------|-----------------------|---------|------|---------|------|--|--|--|--|

| Operating Temperature Range        | Top                  | Absolute Max          | -40     | -    | +85     | °C   |  |  |  |  |

| Storage Temperature Range          | $T_{st}$             | Absolute Max          | -40     | -    | +85     | °C   |  |  |  |  |

| Default Jumper Setting             |                      |                       |         |      |         |      |  |  |  |  |

| Supply Voltage for Module          | VDD                  | -                     | 2.8     | 3.3  | 3.5     | V    |  |  |  |  |

| Supply Current for Module          | IDD                  | VDD=3.3V, 50% ON      | -       | 215  | 235     | mA   |  |  |  |  |

| Supply Culterit for Module         | טטו                  | VDD=3.3V, 100% ON     | -       | 345  | 375     | mA   |  |  |  |  |

|                                    |                      | Jumper Option #1      |         |      |         |      |  |  |  |  |

| Supply Voltage for Module          | VDD                  | -                     | 2.8     | 3.3  | 3.5     | V    |  |  |  |  |

| Supply Voltage for Boost Converter | BC_VDD               | -                     | 2.8     | -    | 12      | V    |  |  |  |  |

| Supply Current for Module          | IDD                  | VDD=3.3V              | -       | 190  | 305     | μΑ   |  |  |  |  |

|                                    |                      | BC_VDD=5.0V, 50% ON   | -       | 135  | 150     | mA   |  |  |  |  |

| Supply Current for Doost Convertor | IDD <sub>BC</sub>    | BC_VDD=5.0V, 100% ON  | -       | 200  | 215     | mA   |  |  |  |  |

| Supply Current for Boost Converter | IDDBC                | BC_VDD=12.0V, 50% ON  | -       | 60   | 70      | mA   |  |  |  |  |

|                                    |                      | BC_VDD=12.0V, 100% ON | -       | 80   | 90      | mA   |  |  |  |  |

|                                    |                      | Jumper Option #2      |         |      |         |      |  |  |  |  |

| Supply Voltage for Module          | VDD                  | -                     | 2.8     | 3.3  | 3.5     | V    |  |  |  |  |

| Supply Voltage for OLED Panel      | VCC                  | -                     | 14.5    | 15   | 15.5    | V    |  |  |  |  |

| Supply Current for Module          | IDD                  | VDD=3.3V              | -       | 180  | 300     | μΑ   |  |  |  |  |

| Cumply Current for OLED Danel      | ICC                  | VCC=15V, 50% ON       | -       | 45   | 50      | mA   |  |  |  |  |

| Supply Current for OLED Panel      | ICC                  | VCC=15V, 100% ON      | -       | 60   | 70      | mA   |  |  |  |  |

|                                    |                      |                       |         | 2=   | 100     |      |  |  |  |  |

| Sleep Mode Current                 | IDD <sub>SLEEP</sub> | -                     | -       | 25   | 120     | μΑ   |  |  |  |  |

| "H" Level input                    | $V_{ih}$             | -                     | 0.8*VDD | -    | VDD     | V    |  |  |  |  |

| "L" Level input                    | V <sub>il</sub>      | -                     | VSS     | -    | 0.2*VDD | V    |  |  |  |  |

| "H" Level output                   | $V_{oh}$             | -                     | 0.9*VDD | -    | VDD     | V    |  |  |  |  |

| "L" Level output                   | Vol                  | -                     | VSS     | -    | 0.1*VDD | V    |  |  |  |  |

**Note:** The electrical characteristics shown above for Jumper Option #1 and Jumper Option #2 apply only when the on-board jumpers are configured accordingly. By default, only Default Jumper Setting supply voltage and current (in bold) need to be considered. For details, see On-Board Jumper Options section on previous page.

## **Optical Characteristics**

Values for Brightness shown below are based on the recommended initialization provided on page 12.

|                              | Ite  | em              | Symbol                                                     | Condition                                                  | Min.   | Тур. | Max.              | Unit |

|------------------------------|------|-----------------|------------------------------------------------------------|------------------------------------------------------------|--------|------|-------------------|------|

| Outined                      | Top  | )               | φΥ+                                                        |                                                            | -      | 85   | -                 | 0    |

| Optimal<br>Viewing<br>Angles | Bot  | ttom            | φΥ-                                                        |                                                            | -      | 85   | -                 | 0    |

|                              | Lef  | t               | θХ-                                                        | -                                                          | -      | 85   | -                 | 0    |

|                              | Rig  | ht              | θX+                                                        |                                                            | -      | 85   | -                 | 0    |

| Contrast Rat                 | io   |                 | Cr                                                         | Cr - >10,000:1                                             |        |      |                   | -    |

| Dospopso Tiv                 | ~~ ~ | Rise            | Tr                                                         | -                                                          | -      | 15   | -                 | ns   |

| Response Tir                 | ne   | Fall            | T <sub>f</sub>                                             | -                                                          | -      | 15   | -                 | ns   |

| Brightness                   |      | L <sub>br</sub> | 50% ON (checkerboard)                                      | 60                                                         | 60 80  |      | cd/m <sup>2</sup> |      |

| Lifetime                     |      | -               | T <sub>a</sub> =25°C, L <sub>br</sub> =80cd/m <sup>2</sup> | 30,000                                                     | -      | -    | hrs               |      |

| Lifetime                     |      |                 | -                                                          | T <sub>a</sub> =25°C, L <sub>br</sub> =60cd/m <sup>2</sup> | 50,000 | -    | -                 | hrs  |

**Note**: Lifetime at typical temperature is based on accelerated high-temperature operation. Lifetime is tested at average 50% pixels on and is rated as Hours until **Half-Brightness**. To extend the life of the display, lower values may be used for the contrast setting registers – see below table of commands for details.

### **Controller Information**

Built-in SSD1322 controller.

For details, view full datasheet at <a href="http://www.newhavendisplay.com/app">http://www.newhavendisplay.com/app</a> notes/SSD1322.pdf

## **Table of Commands**

|                      |     |        |     |     | Cod | e   |     |     |     |     | Do- minking                                                                  |

|----------------------|-----|--------|-----|-----|-----|-----|-----|-----|-----|-----|------------------------------------------------------------------------------|

| Instruction          | D/C | HEX    | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Description                                                                  |

| Enable Grayscale     | 0   | 00     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Enable the Grayscale table settings. (see con                                |

| Table                |     |        |     |     |     |     |     |     |     |     |                                                                              |

| Set Column           | 0   | 15     | 0   | 0   | 0   | 1   | 0   | 1   | 0   | 1   | Set column start and end address                                             |

| Address              | 1   | A[6:0] | *   | A6  | A5  | A4  | А3  | A2  | A1  | A0  | A[6:0]: Column start address. Range: 0-119d                                  |

|                      | 1   | B[6:0] | *   | В6  | В5  | В4  | В3  | B2  | B1  | В0  | B[6:0]: Column end address. Range: 0-119d                                    |

| Write RAM            | 0   | 5C     | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 0   | Enable MCU to write Data into RAM                                            |

| Command              |     |        |     |     |     |     |     |     |     |     |                                                                              |

| Read RAM             | 0   | 5D     | 0   | 1   | 0   | 1   | 1   | 1   | 0   | 1   | Enable MCU to read Data from RAM                                             |

| Command              |     |        |     |     |     |     |     |     |     |     |                                                                              |

| Set Row Address      | 0   | 75     | 0   | 1   | 1   | 1   | 0   | 1   | 0   | 1   | Set row start and end address                                                |

|                      | 1   | A[6:0] | *   | A6  | A5  | A4  | А3  | A2  | A1  | A0  | A[6:0]: Row start address. Range: 0-127d                                     |

|                      | 1   | B[6:0] | *   | В6  | В5  | В4  | В3  | В2  | B1  | В0  | B[6:0]: Row end address. Range: 0-127d                                       |

| Set Re-map           | 0   | Α0     | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | A[0] = 0; Horizontal Address Increment                                       |

| ·                    | 1   | A[5:0] | 0   | 0   | A5  | A4  | 0   | A2  | A1  | A0  | A[0] = 1; Vertical Address Increment                                         |

|                      | 1   | B[4]   | *   | *   | 0   | В4  | 0   | 0   | 0   | 1   | A[1] = 0; Disable Column Address remap                                       |

|                      |     |        |     |     |     |     |     |     |     |     | A[1] = 1; Enable Column Address remap                                        |

|                      |     |        |     |     |     |     |     |     |     |     | A[2] = 0; Disable Nibble remap                                               |

|                      |     |        |     |     |     |     |     |     |     |     | A[2] = 1; Enable Nibble remap<br>A[4] = 0; Scan from COM0 to COM[N-1]        |

|                      |     |        |     |     |     |     |     |     |     |     | A[4] = 0; Scan from COM0 to COM[N-1]<br>A[4] = 1; Scan from COM[N-1] to COM0 |

|                      |     |        |     |     |     |     |     |     |     |     | A[5] = 0; Disable COM split Odd/Even                                         |

|                      |     |        |     |     |     |     |     |     |     |     | A[5] = 1; Enable COM split Odd/Even                                          |

|                      |     |        |     |     |     |     |     |     |     |     | B[4] = 0; Disable Dual COM mode                                              |

|                      |     |        |     |     |     |     |     |     |     |     | B[4] = 1; Enable Dual COM mode                                               |

|                      |     |        |     |     |     |     |     |     |     |     | Note: A[5] must be 0 if B[4] is 1.                                           |

| Set Display Start    | 0   | A1     | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 1   | Set display RAM display start line register fro                              |

| Line                 | 1   | A[6:0] | *   | A6  | A5  | A4  | А3  | A2  | A1  | A0  |                                                                              |

| Set Display Offset   | 0   | A2     | 1   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | Set vertical shift by COM from 0~127.                                        |

|                      | 1   | A[6:0] | *   | A6  | A5  | A4  | А3  | A2  | A1  | A0  |                                                                              |

| Display Mode         | 0   | A4~A7  | 1   | 0   | 1   | 0   | 0   | X2  | X1  | X0  | 0xA4 = Entire display OFF                                                    |

|                      |     |        |     |     |     |     |     |     |     |     | 0xA5 = Entire display ON, all pixels Grayscale                               |

|                      |     |        |     |     |     |     |     |     |     |     | 0xA6 = Normal display                                                        |

|                      |     |        |     |     |     |     |     |     |     |     | 0xA7 = Inverse display                                                       |

| Enable Partial       | 0   | A8     | 1   | 0   | 1   | 0   | 1   | 0   | 0   | 0   | Turns ON partial mode.                                                       |

| Display              | 1   | A[6:0] | 0   | A6  | A5  | A4  | А3  | A2  | A1  | A0  | A[6:0] = Address of start row                                                |

|                      | 1   | B[6:0] | 0   | В6  | B5  | В4  | В3  | B2  | B1  | В0  | B[6:0] = Address of end row (B[6:0] > A[6:0])                                |

| Exit Partial Display | 0   | A9     | 1   | 0   | 1   | 0   | 1   | 0   | 0   | 1   | Exit Partial Display mode                                                    |

| Function Selection   | 0   | AB     | 1   | 0   | 1   | 0   | 1   | 0   | 1   | 1   | A[0] = 0; External VDD                                                       |

|                      | 1   | A[0]   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Α0  | A[0] = 1; Internal VDD regulator                                             |

| Set Sleep Mode<br>ON/OFF | 0 | AE~AF    | 1                | 0                      | 1                      | 0                      | 1                      | 1                | 1                      | X0                     | 0xAE = Sleep Mode ON (display OFF) 0xAF = Sleep Mode OFF (display ON)          |

|--------------------------|---|----------|------------------|------------------------|------------------------|------------------------|------------------------|------------------|------------------------|------------------------|--------------------------------------------------------------------------------|

| Set Phase Length         | 0 | B1       | 1                | 0                      | 1                      | 1                      | 0                      | 0                | 0                      | 1                      | A[3:0] = P1. Phase 1 period of 5-31 DCLK clo                                   |

| get i iluse zeligeli     | 1 | A[7:0]   | A7               | A6                     | A5                     | A4                     | А3                     | A2               | A1                     | A0                     | A[7:4] = P2. Phase 2 period of 3-15 DCLK clo                                   |

| Set Display Clock        | 0 | B3       | 1                | 0                      | 1                      | 1                      | 0                      | 0                | 1                      | 1                      | A[3:0] = 0000; divide by 1                                                     |

| Divide Ratio /           | 1 | A[7:0]   | A7               | A6                     | A5                     | Α4                     | А3                     | A2               | A1                     | A0                     | A[3:0] = 0001; divide by 2                                                     |

| Oscillator               |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 0010; divide by 4                                                     |

| Frequency                |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 0011; divide by 8                                                     |

| ,                        |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 0100; divide by 16                                                    |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 0101; divide by 32                                                    |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 0110; divide by 64                                                    |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 0111; divide by 128                                                   |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 1000; divide by 256                                                   |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 1001; divide by 512                                                   |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] = 1010; divide by 1024                                                  |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:0] >= 1011; invalid                                                        |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[7:4] = Set the Oscillator Frequency. Frequency of A[7:4]. Range 0000b~1111b. |

| VSL / Display            | 0 | B4       | 1                | 0                      | 1                      | 1                      | 0                      | 1                | 0                      | 0                      | A[1:0] = 00b; Enable external VSL                                              |

| Enhancement              |   |          | 1                | 0                      | 1                      | 0                      | 0                      | 0                | A1                     | A0                     | A[1:0] = 10b; Internal VSL                                                     |

| Ennancement              | 1 | A[1:0]   |                  |                        |                        |                        |                        |                  |                        |                        | B[7:3] = 11111b; Enhanced low GS display q                                     |

|                          | 1 | B[7:3]   | В7               | В6                     | B5                     | B4                     | В3                     | 1                | 0                      | 1                      | B[7:3] = 10110b; Normal                                                        |

| Set GPIO                 | 0 | B5       | 1                | 0                      | 1                      | 1                      | 0                      | 1                | 0                      | 1                      | A[1:0] = 00; GPIO0 input disabled                                              |

|                          | 1 | A[3:0]   | *                | *                      | *                      | *                      | А3                     | A2               | A1                     | A0                     | A[1:0] = 01; GPIO0 input enabled                                               |

|                          | _ |          |                  |                        |                        |                        |                        |                  |                        |                        | A[1:0] = 10; GPIO0 output LOW                                                  |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[1:0] = 11; GPIO0 output HIGH                                                 |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:2] = 00; GPIO1 input disabled                                              |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:2] = 01; GPIO1 input enabled                                               |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:2] = 10; GPIO1 output LOW                                                  |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | A[3:2] = 11; GPIO1 output HIGH                                                 |

| Set Second Pre-          | 0 | В6       | 1                | 0                      | 1                      | 1                      | 0                      | 1                | 1                      | 0                      | Sets the second precharge period                                               |

| charge Period            | 1 | A[3:0]   | *                | *                      | *                      | *                      | А3                     | A2               | A1                     | A0                     | A[3:0] = DCLKs                                                                 |

| Set Grayscale            | 0 | В8       | 1                | 0                      | 1                      | 1                      | 1                      | 0                | 0                      | 0                      | Sets the gray scale pulse width in units of De                                 |

| Table                    | 1 | A1[7:0]  | A1 <sub>7</sub>  | <b>A1</b> <sub>6</sub> | <b>A1</b> <sub>5</sub> | <b>A1</b> <sub>4</sub> | <b>A1</b> <sub>3</sub> | A1 <sub>2</sub>  | <b>A1</b> <sub>1</sub> | <b>A1</b> <sub>0</sub> | A1[7:0] = Gamma Setting for GS1                                                |

|                          | 1 | A2[7:0]  | A2 <sub>7</sub>  | A2 <sub>6</sub>        | A2 <sub>5</sub>        | A2 <sub>4</sub>        | A2 <sub>3</sub>        | A2 <sub>2</sub>  | A2 <sub>1</sub>        | A2 <sub>0</sub>        | A2[7:0] = Gamma Setting for GS2                                                |

|                          | 1 | •        |                  | .                      |                        |                        |                        | .                |                        |                        |                                                                                |

|                          | 1 | •        |                  | .                      |                        |                        |                        | .                |                        |                        |                                                                                |

|                          | 1 |          |                  |                        |                        |                        |                        |                  |                        |                        |                                                                                |

|                          | 1 | A14[7:0] | A14 <sub>7</sub> | A14 <sub>6</sub>       | A14 <sub>5</sub>       | A14 <sub>4</sub>       | A14 <sub>3</sub>       | A14 <sub>2</sub> | A14 <sub>1</sub>       | A14 <sub>0</sub>       | A14[7:0] = Gamma Setting for GS14                                              |

|                          | 1 | A15[7:0] | A15 <sub>7</sub> | A15 <sub>6</sub>       | A15 <sub>5</sub>       | A15 <sub>4</sub>       | A15 <sub>3</sub>       | A15 <sub>2</sub> | A15 <sub>1</sub>       | A15 <sub>0</sub>       | A15[7:0] = Gamma Setting for GS15                                              |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | Note: 0 < GS1 < GS2 < GS3 < GS14 < GS15                                        |

|                          |   |          |                  |                        |                        |                        |                        |                  |                        |                        | The setting must be followed by command                                        |

| Select Default    | 0 | В9     | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1  | Sets Linear Grayscale table                    |

|-------------------|---|--------|----|----|----|----|----|----|----|----|------------------------------------------------|

| Linear Gray Scale |   |        |    |    |    |    |    |    |    |    | GS0 pulse width = 0                            |

| Table             |   |        |    |    |    |    |    |    |    |    | GS0 pulse width = 0                            |

|                   |   |        |    |    |    |    |    |    |    |    | GS0 pulse width = 8                            |

|                   |   |        |    |    |    |    |    |    |    |    | GS0 pulse width = 16                           |

|                   |   |        |    |    |    |    |    |    |    |    |                                                |

|                   |   |        |    |    |    |    |    |    |    |    | •                                              |

|                   |   |        |    |    |    |    |    |    |    |    | GS0 pulse width = 104                          |

|                   |   |        |    |    |    |    |    |    |    |    | GSO pulse width = 104<br>GSO pulse width = 112 |

| Set Pre-charge    | 0 | BB     | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 1  | Set precharge voltage level.                   |

| Voltage           | 1 | A[4:0] | *  | *  | *  | A4 | A3 | A2 | A1 | A0 | A[4:0] = 0x00; 0.20*VCC                        |

| VOitage           | 1 | A[4.U] | -  | -  | -  | A4 | AS | AZ | AI | AU |                                                |

|                   |   |        |    |    |    |    |    |    |    |    |                                                |

|                   |   |        |    |    |    |    |    |    |    |    | A[4:0] = 0x3E; 0.60*VCC                        |

| Set VCOMH         | 0 | BE     | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | Sets the VCOMH voltage level                   |

| Voltage           | 1 | A[3:0] | *  | *  | *  | *  | А3 | A2 | A1 | A0 | A[3:0] = 0x00; 0.72*VCC                        |

| •                 |   |        |    |    |    |    |    |    |    |    |                                                |

|                   |   |        |    |    |    |    |    |    |    |    |                                                |

|                   |   |        |    |    |    |    |    |    |    |    | A[3:0] = 0x04; 0.8*VCC                         |

|                   |   |        |    |    |    |    |    |    |    |    | •                                              |

|                   |   |        |    |    |    |    |    |    |    |    | A[3:0] = 0x07; 0.86*VCC                        |

| Set Contrast      | 0 | C1     | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | Double byte command to select 1 out of 256     |

| Control           | 1 | A[7:0] | A7 | A6 | A5 | A4 | A3 | A2 | A1 | Α0 | Contrast increases as the value increases.     |

| Master Contrast   | 0 | C7     | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | A[3:0] = 0x00; Reduce output for all colors to |

| Control           | 1 | A[3:0] | *  | *  | *  | *  | A3 | A2 | A1 | A0 | A[3:0] = 0x01; Reduce output for all colors to |

| Control           | _ | ٦[٥.٥] |    |    |    |    | 73 | 72 |    | ۸٥ |                                                |

|                   |   |        |    |    |    |    |    |    |    |    |                                                |

|                   |   |        |    |    |    |    |    |    |    |    | A[3:0] = 0x0E; Reduce output for all colors to |

|                   |   |        |    |    |    |    |    |    |    |    | A[3:0] = 0x0F; no change                       |

| Set Multiplex     | 0 | CA     | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | Set MUX ratio to N+1 MUX                       |

| Ratio             | 1 | A[6:0] | *  | A6 | A5 | A4 | А3 | A2 | A1 | A0 | N=A[6:0]; from 16MUX to 128MUX (0 to 14        |

| Set Command       | 0 | FD     | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | A[2] = 0; Unlock OLED to enable commands       |

| Lock              | 1 | A[2]   | 0  | 0  | 0  | 1  | 0  | A2 | 1  | 0  | A[2] = 1; Lock OLED from entering command      |

For detailed instruction information, view full SSD1322 datasheet here (pages 32-47):

http://www.newhavendisplay.com/app\_notes/SSD1322.pdf

#### **MPU Interface**

#### **6800-MPU Parallel Interface**

The parallel interface consists of 8 bi-directional data pins, R/W, D/C, E, and /CS.

A LOW on R/W indicates write operation, and HIGH on R/W indicates read operation.

A LOW on D/C indicates "Command" read or write, and HIGH on D/C indicates "Data" read or write.

The E input serves as data latch signal, while /CS is LOW. Data is latched at the falling edge of E signal.

| Function      | E             | R/W | /cs | D/C |

|---------------|---------------|-----|-----|-----|

| Write Command | $\rightarrow$ | 0   | 0   | 0   |

| Read Status   | $\downarrow$  | 1   | 0   | 0   |

| Write Data    | $\downarrow$  | 0   | 0   | 1   |

| Read Data     | $\downarrow$  | 1   | 0   | 1   |

#### 8080-MPU Parallel Interface

The parallel interface consists of 8 bi-directional data pins, /RD, /WR, D/C, and /CS.

A LOW on D/C indicates "Command" read or write, and HIGH on D/C indicates "Data" read or write.

A rising edge of /RS input serves as a data read latch signal while /CS is LOW.

A rising edge of /WR input serves as a data/command write latch signal while /CS is LOW.

| Function      | /RD        | /WR        | /cs | D/C |

|---------------|------------|------------|-----|-----|

| Write Command | 1          | <b></b>    | 0   | 0   |

| Read Status   | $\uparrow$ | 1          | 0   | 0   |

| Write Data    | 1          | $\uparrow$ | 0   | 1   |

| Read Data     | $\uparrow$ | 1          | 0   | 1   |

#### Serial Interface (4-wire)

The 4-wire serial interface consists of Serial Clock (SCLK), Serial Data (SDIN), Data/Command (D/C), and Chip Select (/CS). D0 acts as SCLK and D1 acts as SDIN. D2 must be left as a No Connect D3~D7, E, and R/W should be connected to GND.

| Function      | /RD     | /WR     | /cs | D/C | D0         |

|---------------|---------|---------|-----|-----|------------|

| Write Command | Tie LOW | Tie LOW | 0   | 0   | $\uparrow$ |

| Write Data    | Tie LOW | Tie LOW | 0   | 1   | 1          |

SDIN is shifted into an 8-bit shift register on every rising edge of SCLK in the order of D7, D6,...D0. D/C is sampled on every eighth clock and the data byte in the shift register is written to the GDDRAM or command register in the same clock.

Note: Read functionality is not available in serial mode.

#### Serial Interface (3-wire)

The 3-wire serial interface consists of Serial Clock (SCLK), Serial Data In (SDIN), and Chip Select (/CS). D0 acts as SCLK and D1 acts as SDIN. D2 must be left as a No Connect. D3~D7, E, R/W, and D/C should be connected to Ground.

| Function      | /RD     | /WR     | /cs | D/C     | D0            |

|---------------|---------|---------|-----|---------|---------------|

| Write Command | Tie LOW | Tie LOW | 0   | Tie LOW | $\rightarrow$ |

| Write Data    | Tie LOW | Tie LOW | 0   | Tie LOW | $\uparrow$    |

SDIN is shifted into an 9-bit shift register on every rising edge of SCLK in the order of D/C, D7, D6,...D0. D/C (first bit of the sequential data) will determine if the following data byte is written to the Display Data RAM (D/C = 1) or the command register (D/C = 0).

Note: Read functionality is not available in serial mode.

For detailed timing information for each interface mode, view full SSD1322 datasheet here (pages 50-54): <a href="http://www.newhavendisplay.com/app\_notes/SSD1322.pdf">http://www.newhavendisplay.com/app\_notes/SSD1322.pdf</a>

### **Recommended Initialization**

```

void NHD12864WDY3 Init(void){

digitalWrite(RES, LOW);

//pull /RES (pin #16) low

//keep /RES low for minimum 200µs

delayUS(200);

digitalWrite(RES, HIGH);

//pull /RES high

//wait minimum 200µs before sending commands

delayUS(200);

writeCommand(OxAE);

//display OFF

writeCommand(0xB3);

//set CLK div. & OSC freq.

writeData(0x91);

writeCommand(OxCA);

//set MUX ratio

writeData(0x3F);

writeCommand(0xA2);

//set offset

writeData(0x00);

writeCommand(OxAB);

//function selection

writeData(0x01);

writeCommand(0xA0);

//set re-map

writeData(0x16);

writeData(0x11);

writeCommand(0xC7);

//master contrast current

writeData(OxOF);

//set contrast current

writeCommand(0xC1);

writeData(0x9F);

writeCommand(0xB1);

//set phase length

writeData(0xF2);

//set pre-charge voltage

writeCommand(0xBB);

writeData(Ox1F);

//set VSL

writeCommand(0xB4);

writeData(0xA0);

writeData(OxFD);

writeCommand(0xBE);

//set VCOMH

writeData(0x04);

writeCommand(0xA6);

//set display mode

writeCommand(OxAF);

//display ON

```

### **Example Software Routines**

```

void setColumn(unsigned char xStart, unsigned char xEnd){

//set column (x-axis) start/end address

writeCommand(0x15);

//column start; 28 is left-most column

writeData(xStart);

//column end; 91 is right-most column

writeData(xEnd);

void setRow(unsigned char yStart, unsigned char yEnd){

writeCommand(0x75);

//set row (y-axis) start/end address

//row start; 0 is top row

writeData(yStart);

writeData(yEnd);

//row end; 63 is bottom row

void clearDisplay(void){

unsigned int i;

//set column (x-axis) start/end address

setColumn(28,91);

//set row (y-axis) start/end address

setRow(0,63);

writeRAM();

//single byte command (0x5C) to initiate pixel data write to GDDRAM;

for(i=0;i<4096;i++){}

// ((91-28)+1)*((63-0)+1)

writeData(0x00);

writeData(0x00);

void write2Pixels(unsigned char xPos, unsigned char yPos, unsigned char pixel1, unsigned char pixel2){

if(pixel1>=1) pixel1 = 0xFF;

//set 1st pixel value to ON

else pixel1 = 0x00;

//set 1st pixel value to OFF

if(pixel2>=1) pixel2 = 0xFF;

//set 2nd pixel value to ON

else pixel2 = 0x00;

//set 2nd pixel value to OFF

//boundary check (MIN xPos = 0, MAX xPos = 127)

if(xPos>127) xPos = 127;

xPos = xPos/2;

//account for GDDRAM address mapping

//account for GDDRAM address mapping

xPos+=28;

if(yPos>63) yPos = 63;

//boundary check (MIN yPos = 0, MAX yPos = 63)

setColumn(xPos,xPos);

//set column (x-axis) start/end address

setRow(yPos,yPos);

//set row (y-axis) start/end address

//single byte command (0x5C) to initiate pixel data write to GDDRAM;

writeRAM();

writeData(pixel1);

//write 1st of 2 pixels to the display

//write 2nd of 2 pixels to the display

writeData(pixel2);

void displayArray12864(const unsigned char arr[]){

//display 128x64 monochrome bitmap, horizontal pixel arrangement, 8-pixels per byte

unsigned int i, j;

setColumn(28,91);

//set column (x-axis) start/end address

//set row (y-axis) start/end address

setRow(0,63);

//single byte command (0x5C) to initiate pixel data write to GDDRAM;

writeRAM();

for(i=0;i<1024;i++){

//translate each byte/bit into pixel data

for(j=0;j<8;j++){

if(((arr[i] << j) &0x80) == 0x80){

writeData(OxFF);

else{

writeData(0x00);

```

## **Quality Information**

| Test Item                                | Content of Test                                                                                                                | Test Condition                                                                       | Note |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------|

| High Temperature storage                 | Test the endurance of the display at high storage temperature.                                                                 | +85°C, 240hrs                                                                        | 2    |

| Low Temperature storage                  | Test the endurance of the display at low storage temperature.                                                                  | -40°C, 240hrs                                                                        | 1,2  |

| High Temperature<br>Operation            | Test the endurance of the display by applying electric stress (voltage & current) at high temperature.                         | +85°C, 240hrs                                                                        | 2    |

| Low Temperature<br>Operation             | Test the endurance of the display by applying electric stress (voltage & current) at low temperature.                          | -40°C, 240hrs                                                                        | 1,2  |

| High Temperature /<br>Humidity Operation | Test the endurance of the display by applying electric stress (voltage & current) at high temperature with high humidity.      | +60°C, 90% RH, 240hrs                                                                | 1,2  |

| Thermal Shock resistance                 | Test the endurance of the display by applying electric stress (voltage & current) during a cycle of low and high temperatures. | -40°C, 30min -> +25°C, 5min -><br>+85°C, 30min = 1 cycle<br>100 cycles               |      |

| Vibration test                           | Test the endurance of the display by applying vibration to simulate transportation and use.                                    | 10-22Hz, 15mm amplitude.<br>22-500Hz, 1.5G<br>30min in each of 3 directions<br>X,Y,Z | 3    |

| Atmospheric Pressure test                | Test the endurance of the display by applying atmospheric pressure to simulate transportation by air.                          | 115mbar, 40hrs                                                                       | 3    |

| Static electricity test                  | Test the endurance of the display by applying electric static discharge.                                                       | VS=800V, RS=1.5k $\Omega$ , CS=100pF<br>One time                                     |      |

Note 1: No condensation to be observed.

Note 2: Conducted after 2 hours of storage at 25°C, 0%RH.

**Note 3:** Test performed on product itself, not inside a container.

#### **Evaluation Criteria:**

- 1: Display is fully functional during operational tests and after all tests, at room temperature.

- 2: No observable defects.

- 3: Luminance >50% of initial value.

- 4: Current consumption within 50% of initial value

## Precautions for using OLEDs/LCDs/LCMs

See Precautions at www.newhavendisplay.com/specs/precautions.pdf

## **Warranty Information**

See Terms & Conditions at <a href="http://www.newhavendisplay.com/index.php?main\_page=terms">http://www.newhavendisplay.com/index.php?main\_page=terms</a>

## **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for OLED Displays & Accessories category:

Click to view products by Newhaven Display manufacturer:

Other Similar products are found below:

```

OLED-100H008A-RPP5N00000 OLED-100H016B-RPP5N00000 OLED-200H016A-LPP5N00000 OLED-100H008A-GPP5N00000 OLED-100H008A-LPP5N00000 OLED-100H032A-BPP5N00000 OLED-100H016F-RPP5N00000 OLED-100H016A-BPP5N00000 OLED-100H016A-BPP3N00000 OLED-016N002B-BPP5N00000 OLED-016N002B-BPP5N00000 OLED-016N002B-BPP5N00000 OLED-016N002B-BPP5N00000 OLED-100H016A-BPP5N00000 OLED-100H016B-BPP5N00000 OLED-100H016B-BPP5N00

```