**Data Sheet**

# SiI9292 MHL to HDMI Bridge

ter

Data Sheet

### Document # SiI-DS-1095-B

This document was watermarked on 16-09-2011 at 15:57:22 local time.

March 2011

#### **Copyright Notice**

Copyright © 2010-2011 Silicon Image, Inc. All rights reserved. These materials contain proprietary and confidential information (including trade secrets, copyright and other interests) of Silicon Image, Inc. You may not use these materials except only for your bona fide non-commercial evaluation of your potential purchase of products and/or services from Silicon Image or its affiliates, and/or only in connection with your purchase of products and/or services from Silicon Image or its affiliates, and only in accordance with the terms and conditions herein. You have no right to copy, modify, transfer, sublicense, publicly display, create derivative works of or distribute these materials, or otherwise make these materials available, in whole or in part, to any third party.

#### Patents

The subject matter described herein contains one or more inventions claimed in patents and/or patents pending owned by Silicon Image, Inc., including but not limited to the inventions claimed in US patents #6,914,637, #6,151,334, #6,026,124, #5,974,464 and #5,825,824.

#### **Trademark Acknowledgment**

Silicon Image<sup>TM</sup>, VastLane<sup>TM</sup>, SteelVine<sup>TM</sup>, PinnaClear<sup>TM</sup>, Simplay<sup>TM</sup>, Simplay HD<sup>TM</sup>, Satalink<sup>TM</sup>, InstaPort<sup>TM</sup>, and TMDS<sup>TM</sup> are trademarks or registered trademarks of Silicon Image, Inc. in the United States and other countries. HDMI<sup>®</sup>, the HDMI logo and High-Definition Multimedia Interface<sup>TM</sup> are trademarks or registered trademarks of, and are used under license from, HDMI Licensing, LLC. MHL<sup>TM</sup> is a trademark of, and is under license from, MHL, LLC. x.v.Color<sup>TM</sup> is a trademark of Sony Corporation.

#### **Export Controlled Document**

This document contains information subject to the Export Administration Regulations (EAR) and has a classification of EAR99 or is controlled for Anti-Terrorism (AT) purposes. Transfer of this information by any means to an EAR Country Group E:1 or foreign national thereof (whether in the U.S. or abroad) may require an export license or other approval from the U.S. Department of Commerce. For more information, contact the Silicon Image Director of Global Trade Compliance.

#### **Further Information**

To request other materials, documentation, and information, contact your local Silicon Image, Inc. sales office or visit the Silicon Image, Inc. web site at <u>www.siliconimage.com</u>.

| <b>Revision History</b> |        |                                                 |

|-------------------------|--------|-------------------------------------------------|

| Revision                | Date   | Comment                                         |

| А                       | 2/2011 | Minor content update; first Production release. |

| В                       | 3/2011 | Update description of pin 19.                   |

© 2010-2011 Silicon Image, Inc. All rights reserved.

# **Table of Contents**

| General Description                                                   | 1  |

|-----------------------------------------------------------------------|----|

| Features                                                              |    |

| Pin Mapping                                                           | 2  |

| Functional Description                                                | 3  |

| MHL Receiver Block                                                    | 3  |

| MHL Transcode Engine                                                  | 4  |

| HDMI Transmitter Block                                                | 4  |

| CBUS Interface                                                        | 4  |

| CEC Interface Block                                                   | 4  |

| Downstream Sink Hot Plug                                              |    |

| Downstream Sink DDC Interface                                         | 4  |

| Configuration, Local I <sup>2</sup> C, POR, and Interrupt Logic Block | 4  |

| On-Chip Regulators                                                    | 4  |

| Example System Block Diagram                                          | 5  |

| Electrical Specifications                                             | 6  |

| DC Specifications                                                     | 7  |

| AC Specification                                                      | 8  |

| Timing Diagrams                                                       | 9  |

| Pin Descriptions                                                      | 10 |

| MHL/HDMI Receiver Port Pins                                           |    |

| HDMI Transmitter Port Pins                                            | 10 |

| Control and Configuration Pins                                        | 11 |

| Power and Ground Pins                                                 | 12 |

| Reserved Pins                                                         | 12 |

| System Design Guidelines                                              |    |

| Adapter Application                                                   | 13 |

| Power Supply Decoupling                                               |    |

| High-Speed TMDS Signals                                               | 14 |

| High-Speed TMDS Signals<br>Layout Guidelines                          | 14 |

| Termination Requirement                                               | 15 |

| ESD Protection                                                        | 15 |

| EMI Considerations                                                    | 15 |

| Packaging                                                             | 16 |

| ePad Requirements                                                     | 16 |

| Package Dimensions                                                    |    |

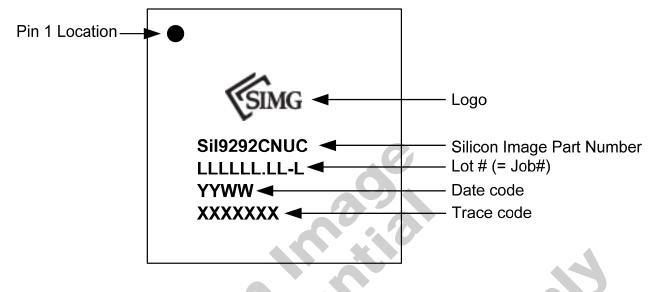

| Marking Specification                                                 | 18 |

| Ordering Information                                                  | 18 |

| References                                                            |    |

| Standards Documents                                                   |    |

| Silicon Image Documents                                               |    |

|                                                                       | -  |

# **List of Figures**

| Figure 1. Typical Application as an MHL-to-HDMI Bridge           | 1  |

|------------------------------------------------------------------|----|

| Figure 2. Pin Mapping                                            |    |

| Figure 3. Functional Block Diagram                               |    |

| Figure 4. MHL to HDMI Bridge Mode                                |    |

| Figure 5. Test Point VDDTP for VDD Noise Tolerance Specification | 6  |

| Figure 6. RESET# Minimum Timing                                  |    |

| Figure 7. Digital Output Transition Times                        | 9  |

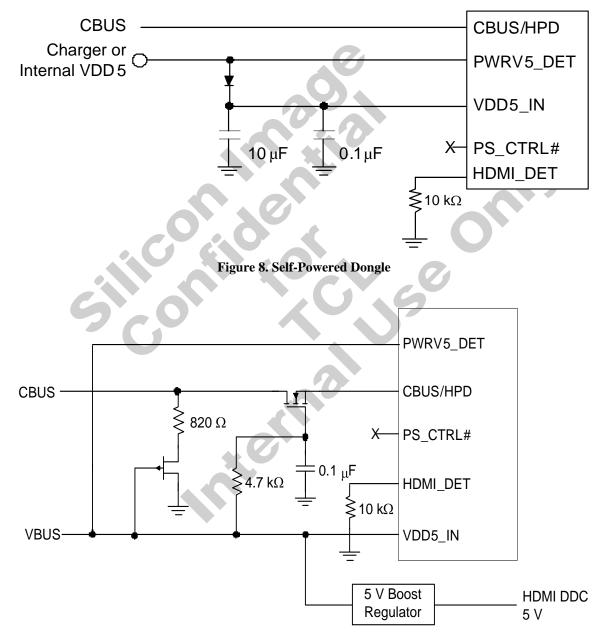

| Figure 8. Self-Powered Dongle                                    | 13 |

| Figure 9. BUS-Powered Dongle with Isolation Circuit              | 13 |

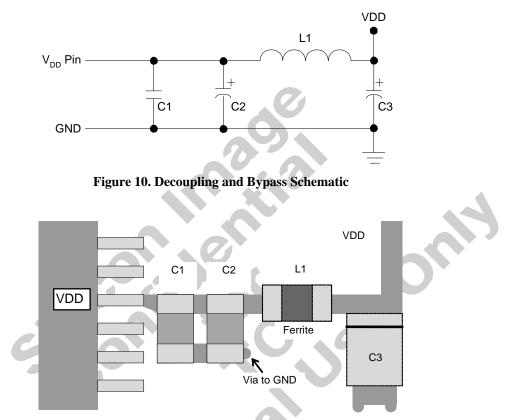

| Figure 10. Decoupling and Bypass Schematic                       | 14 |

| Figure 11. Decoupling and Bypass Capacitor Placement             |    |

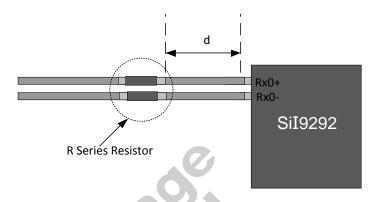

| Figure 12. TMDS Signal Termination                               | 15 |

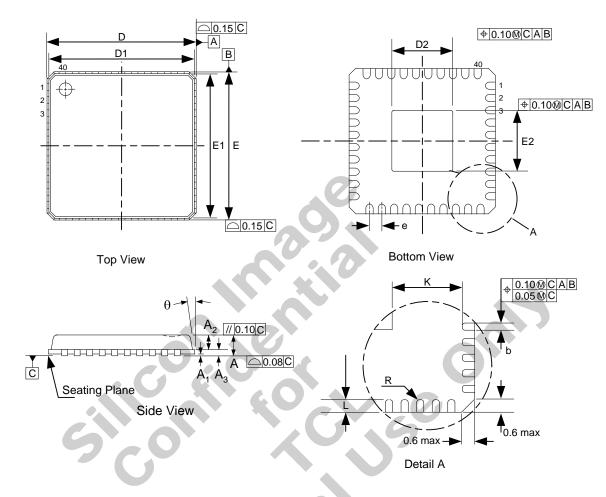

| Figure 13. 40-pin QFN Package Diagram                            | 17 |

| Figure 14. Marking Diagram                                       | 18 |

# List of Tables

| Table 1. Absolute Maximum Conditions                                                                                                                                              | <br>6  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Table 2. Normal Operating Conditions                                                                                                                                              | <br>6  |

| Table 3. DC Power Supply Specifications                                                                                                                                           | <br>7  |

| Table 4. Digital I/O Specifications                                                                                                                                               | <br>7  |

| Table 2. Normal Operating Conditions         Table 3. DC Power Supply Specifications         Table 4. Digital I/O Specifications         Table 5. Digital CBUS I/O Specifications | <br>8  |

| Lable 6 LMUS Input Limings                                                                                                                                                        | X      |

| Table 0. TMDS input Timings         Table 7. TMDS Output Timings         Table 8. Miscellaneous Timings                                                                           | 8      |

| Table 8. Miscellaneous Timings                                                                                                                                                    | <br>8  |

| Table 9. Referenced Documents                                                                                                                                                     |        |

| Table 10. Standards Groups Contact Information         Table 11. Silicon Image Publications                                                                                       | <br>19 |

| Table 11. Silicon Image Publications                                                                                                                                              | <br>19 |

|                                                                                                                                                                                   |        |

# **General Description**

The SiI9292 MHL to HDMI Bridge facilitates the design of low-pin count, low-power mobile-to-standard HDMI<sup>®</sup>-interoperable applications. The Silicon Image Mobile High-definition Link (MHL<sup>TM</sup>) technology carries formatted video and audio from compatible transmitters, using only 3 signal lines, power, and ground (5 pins total) compared to the 19 pins required for the standard High Definition Multimedia Interface (HDMI<sup>®</sup>).

The SiI9292 bridge uses a minimum number of parts to convert MHL source devices, such as adapters, smart cables, and docking stations, to existing HDMI devices.

Silicon Image MHL products use the latest generation of Transition Minimized Differential Signaling (TMDS<sup>™</sup>) core technology. With this solution, HD camcorders, digital still cameras, and personal mobile devices can connect to a large installed base of HDMI TVs.

Together, the SiI923x and SiI9244 MHL transmitters and the SiI9292 bridge enable a fully compliant HDMI link solution and are pre-certified to pass HDMI compliance testing.

# Features

- The MHL receiver part of the bridge receives data over a single differential pair instead of four

- To reduce bridge device cost, a microcontroller is not required if CEC support is not required.

- A single-wire control bus supports all sideband signaling for DDC, Remote Control, and Hot Plug Detect (HPD)

- The bridge converts data received in the MHL format to standard HDMI, and supports all resolutions between 25-75 MHz

- I<sup>2</sup>C interface for configuration by local microcontroller.

- HDMI and DVI 1.0 transmitter compatibility

- Low power 1.2 V core

- 40-pin QFN, 6 mm x 6 mm body size

- Extended commercial temperature range (-20 C to +85 °C).

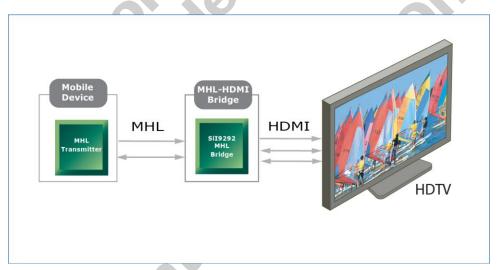

Figure 1. Typical Application as an MHL-to-HDMI Bridge

# **Pin Mapping**

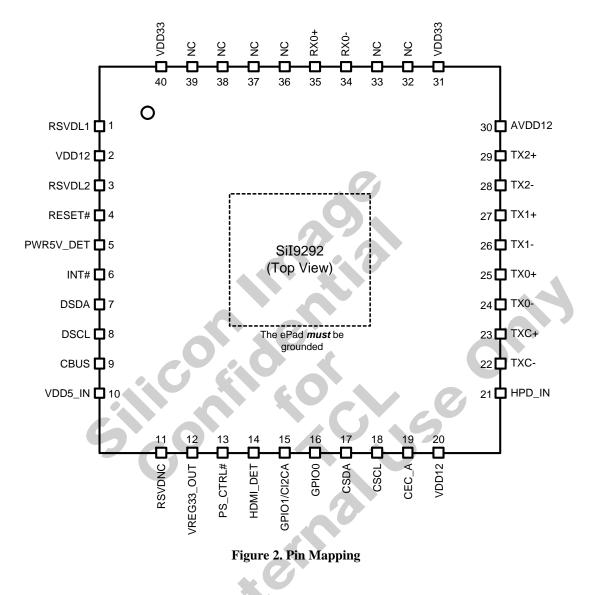

Figure 2 shows the pin diagram for the SiI9292 bridge. A description of the pin functions begins on page 10.

# **Functional Description**

The SiI9292 bridge takes the MHL common mode clock operating at the pixel clock frequency, and the data channel running at 3 times the pixel clock rate, and generates a standard HDMI output.

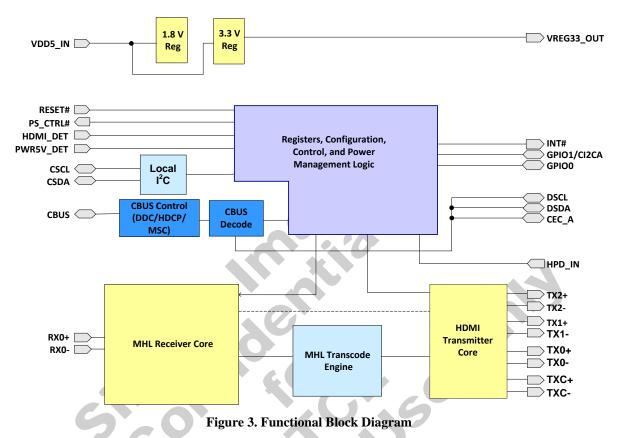

As shown in Figure 3, the bridge consists of these major blocks:

- MHL Receiver with automatic termination and equalization controls

- MHL Transcode Engine

- HDMI Transmitter with internal source termination

- CBUS Interface

- CBUS Decode and HDMI DDC and CEC interface

- Local I<sup>2</sup>C interface

- Configuration registers, control and Interrupt logic block

- On-chip voltage regulators

# **MHL Receiver Block**

The MHL receiver block consists of a single pair MHL standard interface. In MHL mode, the source video and audio is formatted as MHL protocol. The TMDS receiver circuitry recovers the data and passes it on for conversion back to the three-lane HDMI.

### **MHL Transcode Engine**

The MHL Transcode Engine changes the recovered MHL data, which has a single data lane running at 3 times the HDMI rate, into HDMI format. Format conversion repacks this data into the standard 1x video rate, three-lane format associated with standard HDMI.

# **HDMI Transmitter Block**

The transmitter block sends an HDMI stream that is based on the content of the original stream from the source. Internal source termination eliminates the requirement for external RC components for signal shaping.

### **CBUS Interface**

The CBUS signal handles the MHL Control Bus Interface. The MHL transmitter and receiver follow a specific communication and arbitration protocol to exchange EDID, Control, and HDCP information that would normally pass over the DDC clock and data wires. In addition, device remote control commands and hot plug status is also exchanged. All of the communication is managed transparently, so the source and bridge logic operate as if they had discrete DDC, control, and HPD signals.

### **CEC Interface Block**

The Consumer Electronics Control (CEC) Interface, which is part of the CBUS Decode block, sends and receives CECcompliant signals using the CEC\_A signal. A host microcontroller translates RCP (Remote Control Protocol) commands from the host MHL device over the CBUS to CEC commands using the CPI programming interface. The CEC controller in turn sends and receives commands. Using the CEC interface is optional and is used to translate between the RCP and CEC protocols in dongle applications.

### **Downstream Sink Hot Plug**

The HPDIN (Hot Plug) signal is used to detect the connection status of the HDMI sink device. The power management state machine uses this information, and it is also available to the MHL source device over the CBUS.

### **Downstream Sink DDC Interface**

The Downstream DDC Interface is part of the CBUS Decode block and is used to read HDCP and EDID information from the downstream sink device in MHL mode. The DDC interface is encoded and decoded by the Control bus decode block and sent over the CBUS interface to the MHL source device.

# Configuration, Local I<sup>2</sup>C, POR, and Interrupt Logic Block

The Configuration block is used to configure and control the operation of the device, which can operate in either  $I^2C$  mode (*smart* dongle mode with microcontroller) or *standalone* mode (basic bridge or dongle mode). During local register reads only sequential  $I^2C$  read mode is supported by SiI9292 bridge. The Power-On Reset (POR) circuit is also contained in this block. POR provides an on-chip reset function that is primarily to eliminate the need for an external power on reset circuit. The power-on default is the basic dongle mode. Refer to the Programmer's Reference for more information on configuration for smart dongle mode.

# **On-Chip Regulators**

The chip contains two regulators that provide the internal CBUS 1.8 V and external 3.3 V power sources derived from the VDD5\_IN (5 V input) to the chip. The on-chip regulators provide a lower cost system implementation by eliminating the need for external voltage regulator.

# **Example System Block Diagram**

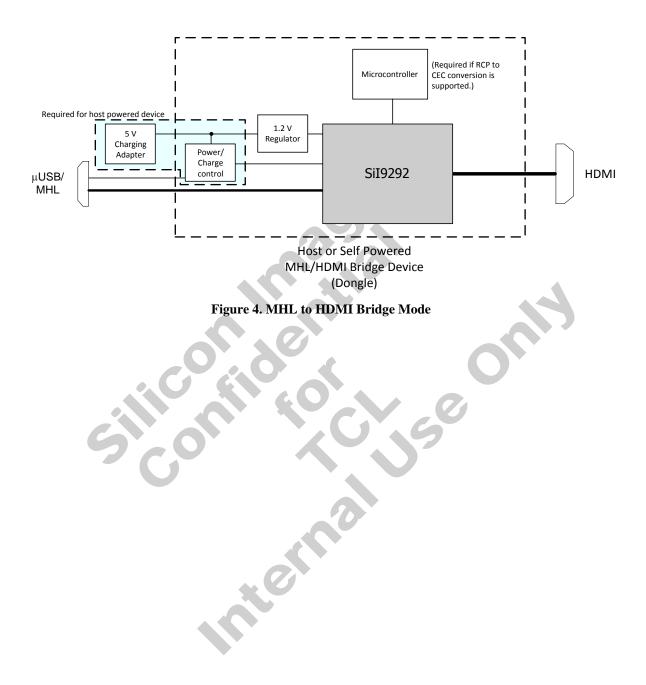

Figure 4 shows an example of a system block diagram with an external 5 V charging adapter and microcontroller option.

# **Electrical Specifications**

| <b>Table 1. Absolute Maximum</b> | Conditions |

|----------------------------------|------------|

|----------------------------------|------------|

| Symbol                   | Parameter                                | Min  | Тур | Max         | Units | Note    |

|--------------------------|------------------------------------------|------|-----|-------------|-------|---------|

| VDD5V_IN                 | Primary on-chip regulator supply voltage | -0.5 | —   | 5.7         | V     | 1, 2, 3 |

| VDD12                    | Core Supply Voltage                      | -0.3 | _   | 2.0         | V     | 1, 2    |

| VDD33                    | TMDS I/O Supply Voltage                  | -0.3 | _   | 4.0         | V     | 1, 2    |

| AVDD12                   | Analog I/O Supply Voltage                | -0.3 | _   | 2.0         | V     | 1, 2    |

| VREG33_OUT               | On-Chip regulator output voltage         | -0.3 | _   | 4.0         | V     | 1, 2    |

| VI                       | Input voltage                            | -0.3 | _   | VDD33 + 0.3 | V     | 1, 2    |

| Vo                       | Output voltage                           | -0.3 | _   | VDD33 + 0.3 | V     | 1, 2    |

| V <sub>5V-Tolerant</sub> | Input voltage on 5 V-tolerant pins       | -0.3 | —   | 5.5         | V     | —       |

| T <sub>J</sub>           | Junction temperature                     | -    | _   | 125         | °C    | _       |

| T <sub>STG</sub>         | Storage temperature                      | -65  | _   | 150         | °C    |         |

Notes:

- 1. Permanent device damage can occur if absolute maximum conditions are exceeded.

- 2. Functional operation should be restricted to the conditions described under Normal Operating Conditions.

- 3. Voltage undershoot or overshoot cannot exceed absolute maximum conditions.

| Table 2. Normal Operating Cond |

|--------------------------------|

|--------------------------------|

| Symbol                 | Parameter                                | Min  | Тур             | Max  | Units             | Note |

|------------------------|------------------------------------------|------|-----------------|------|-------------------|------|

| VDD5V_IN               | Primary on-chip regulator supply voltage | 4.3  | 5.0             | 5.5  | V                 | —    |

| VDD33                  | TMDS I/O supply voltage                  | 3.15 | 3.3             | 3.45 | V                 | 1    |

| VDD12                  | Core supply voltage                      | 1.08 | 1.2             | 1.32 | V                 | _    |

| AVDD12                 | Analog I/O Supply Voltage                | 1.08 | 1.2             | 1.32 | V                 | _    |

| VREG33_OUT             | On-Chip regulator output voltage         | 3.15 | 3.3             | 3.45 | V                 | _    |

| V <sub>DDN</sub>       | Supply voltage noise                     |      | $\rightarrow -$ | 100  | mV <sub>P-P</sub> | 2    |

| T <sub>A</sub>         | Ambient temperature (with power applied) | -20  | +25             | +85  | °C                | _    |

| $\Theta_{\mathrm{ja}}$ | Ambient thermal resistance (Theta JA)    |      |                 | 32   | °C/W              | 3    |

| $\Theta_{\rm jc}$      | Junction to case resistance (Theta JC)   | -    |                 | 24   | °C/W              | 3    |

Notes:

1. The HDMI Specification requires termination voltage (VDD33) to be controlled to  $3.3 \text{ V} \pm 5\%$ .

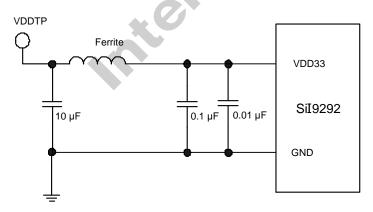

- 2. The supply voltage noise is measured at test point VDDTP as shown in Figure 5. The ferrite bead provides filtering of power supply noise.

- 3. Airflow at 0 m/s, 4-layer PCB.

See the Power Supply Decoupling section on page 14 for the recommended decoupling for power supplies.

Figure 5. Test Point VDDTP for VDD Noise Tolerance Specification

# **DC Specifications**

|                                                   |                     | HDMI                | VDD33    | Тур     |       |                 |         | Max   |                 |       |

|---------------------------------------------------|---------------------|---------------------|----------|---------|-------|-----------------|---------|-------|-----------------|-------|

| Symbol                                            | Parameter           | Output<br>Frequency |          | VDD5_IN | VDD33 | VDD12<br>AVDD12 | VDD5_IN | VDD33 | VDD12<br>AVDD12 | Units |

| I <sub>DDSB</sub>                                 | Standby current     | _                   | External | 2       | 0.5   | 2               | 3       | 3     | 14              | mA    |

|                                                   | MHL Input           |                     |          |         |       |                 |         |       |                 |       |

|                                                   | <b>F</b> U <i>d</i> | 25 MHz              | External | 2.2     | 32    | 80              | 3.7     | 36    | 96              | mA    |

| I <sub>DDFP</sub> Full operation<br>state current | 75 MHz              | External            | 2.2      | 32      | 153   | 3.7             | 36      | 165   | mA              |       |

|                                                   | state current       |                     | Internal | 37      |       | 153             | 40      | _     | 165             | mA    |

\*Note: For VDD Internal Source, connect VREG33\_OUT to VDD33. For VDD External source, connect an external 3.3 V source to VDD33. ,71

#### Table 4. Digital I/O Specifications

| Symbol                | Parameter                                            | Pin Type <sup>3</sup>               | Conditions <sup>2</sup>              | Min  | Тур          | Max  | Units | Note    |

|-----------------------|------------------------------------------------------|-------------------------------------|--------------------------------------|------|--------------|------|-------|---------|

| V <sub>TH+DDC</sub>   | LOW to HIGH threshold                                | Schmitt<br>trigger <sub>DDC</sub>   | 2-                                   | 3.0  |              | _    | V     | 8       |

| V <sub>TH-DDC</sub>   | HIGH to LOW threshold                                | Schmitt<br>trigger <sub>DDC</sub>   | -0                                   |      |              | 1.5  | V     | 8       |

| V <sub>TH+CEC_A</sub> | LOW to HIGH threshold,<br>CEC_A pin                  | Schmitt<br>trigger <sub>CEC_A</sub> |                                      | 2.0  | _            | -    | v     |         |

| V <sub>TH-CEC_A</sub> | HIGH to LOW threshold,<br>CEC_A pin                  | Schmitt<br>trigger <sub>CEC_A</sub> | —                                    |      | -            | 0.8  | V     | _       |

| $V_{TH^+}$            | LOW to HIGH threshold                                | Schmitt<br>trigger                  | -                                    | 1.75 | $\mathbf{+}$ |      | V     | 6, 7    |

| V <sub>TH-</sub>      | HIGH to LOW threshold                                | Schmitt<br>trigger                  | 0-                                   |      |              | 1.1  | V     | 6, 7    |

| I <sub>Oz</sub>       | Output leakage current                               | . –                                 | High impedance                       | -10  |              | 10   | μΑ    |         |

| I <sub>IL</sub>       | Input leakage current                                | _                                   |                                      | -10  |              | 10   | μΑ    | _       |

| V <sub>ID</sub>       | Differential input voltage                           |                                     | -                                    | 75   | 250          | 1000 | mV    | 4       |

| V <sub>OD</sub>       | Differential output single-<br>ended swing amplitude | TMDS                                | RLOAD = 50 $\Omega$                  | 400  | 500          | 600  | mV    |         |

| V <sub>DOH</sub>      | Differential HIGH level<br>output voltage            | TMDS                                | -7                                   |      | 3.3          | _    | V     |         |

| I <sub>DOS</sub>      | Differential output short-<br>circuit current        | TMDS                                | VOUT = 0 V                           |      |              | 5    | μΑ    |         |

| I <sub>OD8</sub>      | General digital output drive                         | Output                              | $V_{OH} = 2.4 V$                     | 7.5  |              | _    | mA    | 1, 6, 7 |

| 1OD8                  | General digital output drive                         | Output                              | $V_{OL} = 0.4 V$                     | 7.5  | _            | —    | mA    | 1, 6, 7 |

| I <sub>ODDDC</sub>    | I <sup>2</sup> C digital output drive                | Output                              | $V_{OL} = 0.5 V$                     | 3.0  |              |      | mA    | 1, 6, 8 |

| I <sub>ODCEC_A</sub>  | CEC_A digital output drive                           | Output                              | $V_{OH} = 2.4 V$<br>$V_{OL} = 0.4 V$ | 4.0  |              |      | mA    | 9       |

Notes:

These limits are guaranteed by design. 1.

2. Under normal operating conditions unless otherwise specified, including output pin loading  $C_L = 10 \text{ pF}$ .

Refer to Pin Descriptions section (beginning on page 10) for pin type designations for all package pins. 3.

- Differential input voltage is a single-ended measurement, according to the DVI Specification. 4.

- Only these Schmitt trigger input pin thresholds V<sub>TH+</sub> and V<sub>TH-</sub> correspond to V<sub>IH</sub> and V<sub>IL</sub>, respectively and are 5. guaranteed by design.

- Minimum output drive specified at ambient = 70 °C and VDD33 = 3.0 V. Typical output drive specified at 6. ambient =  $25^{\circ}$ C and VDD33 = 3.3 V. Maximum output drive specified at ambient =  $-20^{\circ}$ C and VDD33 = 3.6 V.

- I<sub>OD8</sub> Output applies to all pins defined as LVTTL and LVTTL/Schmitt trigger. 7.

- I<sub>ODDDC</sub> Output applies to all pins defined as Schmitt trigger<sub>DDC</sub>. 8.

- 9. I<sub>ODCEC A</sub> Output applies to CEC\_A pin.

### Table 5. Digital CBUS I/O Specifications

| V <sub>IH_CBUS</sub>                | LOW to HIGH threshold,<br>CBUS pin  | CBUS | _                         | 1.0  |      |      | V  | — |

|-------------------------------------|-------------------------------------|------|---------------------------|------|------|------|----|---|

| V <sub>IL_CBUS</sub>                | HIGH to LOW threshold,<br>CBUS pin  | CBUS | _                         | _    |      | 0.6  | V  | — |

| V <sub>OH_CBUS</sub>                | Output HIGH Voltage,<br>CBUS pin    | CBUS | IOVCC18 = 1.8 V,<br>85 °C | 1.5  | _    | 1.9  | V  | — |

| V <sub>OL_CBUS</sub>                | Output LOW Voltage,<br>CBUS pin     | CBUS | IOVCC18 = 1.8 V,<br>85 °C | _    | _    | 0.2  | V  | — |

| I <sub>OH_CBUS</sub>                | HIGH output drive current           | CBUS | VOH = 1.5 V               | 2    | _    | _    | mA | _ |

| I <sub>OL_CBUS</sub>                | LOW output drive current            | CBUS | VOL = 0.2 V               | 300  | _    | _    | μΑ | _ |

| I <sub>IL/IIH</sub>                 | Input Leakage Current               | CBUS | High impedance            | -1.0 | _    | 1.0  | μΑ | _ |

| Z <sub>CBUS_SINK_</sub><br>DISCOVER | Pull down resistance -<br>discovery | CBUS | _                         | 800  | 1000 | 1200 | Ω  | — |

| Z <sub>CBUS_SINK_</sub>             | Pull down resistance - ON           | CBUS | - 0                       | 90   | 100  | 110  | kΩ |   |

# **AC Specification**

### **Table 6. TMDS Input Timings**

| Table 0. 1        | wilds input Timings               |                         |       |     |     |       |       |

|-------------------|-----------------------------------|-------------------------|-------|-----|-----|-------|-------|

| Symbol            | Parameter                         | Conditions <sup>1</sup> | Min   | Тур | Max | Units | Notes |

| F <sub>RXC2</sub> | Common-mode input clock frequency | MHL Mode                | 25    | —   | 75  | MHz   | 2     |

| T <sub>RXC2</sub> | Common-mode input clock period    | MHL Mode                | 13.33 |     | 40  | ns    | _     |

|                   |                                   |                         |       |     |     |       |       |

Notes:

1. Under normal operating conditions unless otherwise specified, including output pin loading of  $C_L = 10 \text{ pF}$ . 2. MHL Mode, 1X clock 3X data rate.

### **Table 7. TMDS Output Timings**

| Symbol                      | Parameter                                      | Conditions | Min   | Тур | Max | Units | Notes |

|-----------------------------|------------------------------------------------|------------|-------|-----|-----|-------|-------|

| F <sub>CYC</sub>            | Clock frequency                                | MHL Input  | 25    | P   | 75  | MHz   | _     |

| T <sub>CYC</sub>            | Clock period                                   | MHL Input  | 13.33 |     | 40  | ns    | _     |

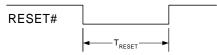

| $\mathbf{S}_{\mathrm{LHT}}$ | Differential swing LOW-to-HIGH transition time |            | 75    |     | 490 | ps    |       |

| S <sub>HLT</sub>            | Differential swing HIGH-to-LOW transition time |            | 75    | _   | 490 | ps    |       |

#### **Table 8. Miscellaneous Timings**

| Symbol              | Parameter                                                         | Conditions <sup>1</sup>      | Min | Тур | Max | Units | Figure   | Notes |

|---------------------|-------------------------------------------------------------------|------------------------------|-----|-----|-----|-------|----------|-------|

| T <sub>I2CDVD</sub> | Delay from falling edge of $I^2C$ clock that $I^2C$ data is valid | $C_{L} = 400 \text{ pF}$     | _   | _   | 700 | ns    | _        | _     |

| F <sub>DDC</sub>    | Speed on HDMI DDC port                                            | $C_{\rm L} = 400 \ {\rm pF}$ |     |     | 100 | kHz   |          | 2     |

| F <sub>I2C</sub>    | Speed on local I <sup>2</sup> C port                              | $C_L = 400 \text{ pF}$       | _   |     | 400 | kHz   | _        | 3     |

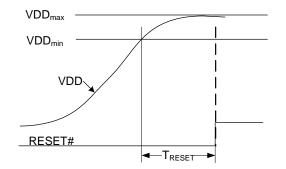

| T <sub>RESET</sub>  | RESET# signal LOW time for valid reset                            |                              | 10  |     |     | ms    | Figure 6 | _     |

Notes:

1. Under normal operating conditions unless otherwise specified, including output pin loading of  $C_L = 10 \text{ pF}$ .

2. DDC port is limited to 100 kHz by the HDMI Specification, and meets  $I^2C$  Standard mode timings.

3. Local I<sup>2</sup>C port (CSCL/CSDA) meets Standard mode I<sup>2</sup>C timing requirements to 400 kHz.

# **Timing Diagrams**

Power sequencing is not required for the SiI9292 device. However to ensure a proper RESET, the rules mentioned under the diagrams in Figure 6 must be followed.

VDD must be stable between its limits for Normal Operating Conditions for  $T_{RESET}$  before RESET# is HIGH.

When using the external reset function, RESET# must be pulled LOW for  $T_{RESET}$  before accessing registers. This can be done by holding RESET# LOW until  $T_{RESET}$  after stable power (as shown at left); or by pulling RESET# LOW from a HIGH state (as shown above) for at least T<sub>RESET</sub>.

# **Pin Descriptions**

# **MHL/HDMI Receiver Port Pins**

| Pin Name | Pin | Туре                                      | Dir              | Description                                                                                                                                               |

|----------|-----|-------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RX0+     | 35  | TMDS                                      | Input            | MHL Input Port Data pair.                                                                                                                                 |

| RX0-     | 34  | TMDS                                      | Input            | Series termination resistors are required for each pin. See the High-Speed TMDS Signals section on page 14 for details.                                   |

| CBUS     | 9   | Custom<br>CBUS<br>Schmitt<br>5-V tolerant | Input/<br>Output | In MHL mode this pin is the Control Bus signal. The CBUS signal is for communication between the MHL transmitter and receiver using a 1.8 V signal level. |

# **HDMI Transmitter Port Pins**

| IDMI Tran | smitter | Port Pin                  | S        |                                                                                                                                 |

|-----------|---------|---------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| Pin Name  | Pin     | Туре                      | Dir      | Description                                                                                                                     |

| TX0+      | 25      | TMDS                      | Output   | TMDS data pair 0.                                                                                                               |

| TX0-      | 24      | TMDS                      | Output   |                                                                                                                                 |

| TX1+      | 27      | TMDS                      | Output   | TMDS data pair 1.                                                                                                               |

| TX1-      | 26      | TMDS                      | Output   |                                                                                                                                 |

| TX2+      | 29      | TMDS                      | Output   | TMDS data pair 2.                                                                                                               |

| TX2-      | 28      | TMDS                      | Output   |                                                                                                                                 |

| TXC+      | 23      | TMDS                      | Output   | TMDS clock pair.                                                                                                                |

| TXC-      | 22      | TMDS                      | Output   |                                                                                                                                 |

| HPD_IN    | 21      | Schmitt                   | Input    | TX Hot Plug Detection input.                                                                                                    |

|           |         | 5 V tolerant              |          | An external 10 k $\Omega$ pulldown resistor is required on this pin.                                                            |

| CEC_A     | 19      | CEC                       | Input/   | Interface to CEC devices.                                                                                                       |

|           |         | compliant                 | Output   | Interface to CEC devices. CEC electrical spec compliant signal.                                                                 |

|           |         |                           |          | Powered by VDD33. Only use this pin with a microcontroller.                                                                     |

|           |         |                           |          | When used in standalone mode or dongle configuration, this                                                                      |

|           |         |                           |          | pin must be left unconnected. This pin has an internal pullup;<br>therefore an external 27 k $\Omega$ resistor is not required. |

| DSCL      | 8       | I <sup>2</sup> C          | Input/   | DDC Clock and Data for transmitter ( $I^2C$ Master).                                                                            |

| DOCL      | Ũ       | compliant                 | Output   | These pins implement true open-drain circuits; external pullup                                                                  |

|           |         | Open drain                | <b>F</b> | (1.8 k $\Omega$ ±10% typical) resistors to DDC 5 V are required.                                                                |

|           |         | 5 V tolerant              |          | These are 5 V tolerant pins.                                                                                                    |

| DSDA      | 7       | I <sup>2</sup> C          | Input/   |                                                                                                                                 |

|           |         | compliant,<br>Open drain, | Output   |                                                                                                                                 |

|           |         | 5 V tolerant              |          |                                                                                                                                 |

|           |         |                           |          | F                                                                                                                               |

# **Control and Configuration Pins**

| Pin Name       | Pin | Туре                                           | Dir              | Description                                                                                                                                                                                                                                                                             |

|----------------|-----|------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET#         | 4   | LVTTL<br>Schmitt<br>5 V tolerant               | Input            | External Reset pin. (Active low).<br>This pin has an Internal pullup; it can be left open when external<br>reset is not required.                                                                                                                                                       |

| CSCL           | 18  | LVTTL<br>Schmitt<br>Open drain<br>5 V tolerant | Input/<br>Output | Local I <sup>2</sup> C Clock.<br>This pin is true open drain, so it does not pull to ground if power is<br>not applied. An external pullup resistor to 3.3 V is required.                                                                                                               |

| CSDA           | 17  | LVTTL<br>Schmitt<br>Open drain<br>5 V tolerant | Input/<br>Output | Local I <sup>2</sup> C Data.<br>This pin is true open drain, so it does not pull to ground if power is<br>not applied. An external pullup resistor to 3.3 V is required                                                                                                                 |

| PS_CTRL#       | 13  | LVTTL/<br>Open Drain<br>5 V tolerant           | Output           | Power Supply Control Output.<br>Active LOW output used to control an external MOSFET power<br>switch to enable VBUS back to the host after MHL discovery has<br>been completed.                                                                                                         |

| INT#           | 6   | LVTTL<br>Open drain<br>5 V tolerant            | Output           | Active LOW interrupt output to host controller.<br>This is an open drain output and requires an external pullup resistor.                                                                                                                                                               |

| GPIO0          | 16  | LVTTL<br>Schmitt<br>5 V tolerant               | Input/<br>Output | General Purpose Input/Output 0.<br>See the Programmer's Reference for more details.                                                                                                                                                                                                     |

| GPIO1<br>CI2CA | 15  | LVTTL<br>Schmitt<br>5 V tolerant               | Input/<br>Output | General Purpose Input/Output 1/CI2CA.<br>This pin defaults to an input and is sampled once at reset to select<br>the local I <sup>2</sup> C target address ranges, as follows:<br>LOW = 0xD0, 0xC0, 0xC8<br>HIGH = 0xD4, 0xC4, 0xCC<br>See the Programmer's Reference for more details. |

| HDMI_DET       | 14  | LVTTL<br>Schmitt<br>5 V tolerant               | Input            | Pull this pin LOW through a 10 k $\Omega$ resistor to ground.                                                                                                                                                                                                                           |

| PWR5V_DET      | 5   | LVTTL<br>Schmitt<br>5 V tolerant               | Input            | Senses External 5 V charger input to change power provisioning.<br>Connect this pin to the local 5 V power supply when using self-<br>powered dongle configurations.                                                                                                                    |

|                |     |                                                | n <sup>e</sup>   |                                                                                                                                                                                                                                                                                         |

### **Power and Ground Pins**

| Pin Name   | Pin    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                   |

|------------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND        | ePad   | Ground | Ground.<br>All ground connections to the device are through the ePad;<br>therefore it <i>must</i> be soldered to the board and the pad must have a<br>low resistance connection to the board ground plane.                                                                                                                                                                    |

| VDD12      | 2, 20  | Power  | Digital Core VDD from external regulator.                                                                                                                                                                                                                                                                                                                                     |

| AVDD12     | 30     | Power  | Analog Core VDD from external regulator.                                                                                                                                                                                                                                                                                                                                      |

| VDD33      | 31, 40 | Power  | Receiver termination 3.3 V analog supply input.<br>Connect to an external 3.3 V regulator or to VREG33_OUT as<br>described below.                                                                                                                                                                                                                                             |

| VDD5V_IN   | 10     | Power  | Connect this pin to the HDMI +5 V input or VBUS +5 V input from a MHL Source.                                                                                                                                                                                                                                                                                                 |

| VREG33_OUT | 12     | Power  | Internal 3.3 V regulator output.<br>When this on-chip regulator is used, it should be externally<br>connected to VDD33 (pins 31 and 40). Additional decoupling<br>capacitors are required; see the Power Supply Decoupling section<br>on page 14 for an example circuit. When an external 3.3 V<br>regulator is used to supply power to VDD33, this pin must be left<br>open. |

### **Reserved Pins**

| iteber veu |     |          |                                                        |  |  |

|------------|-----|----------|--------------------------------------------------------|--|--|

| Name       | Pin | Туре     | Description                                            |  |  |

| RSVDL1     | 1   | Reserved | This pin must be connected to GND in normal operation. |  |  |

| RSVDL2     | 3   | Reserved | This pin must be connected to GND in normal operation. |  |  |

| RSVDNC     | 11  | Reserved | This pin must be left unconnected in normal operation. |  |  |

|            | 56  |          |                                                        |  |  |

# System Design Guidelines

The tolerance of all resistors shown in this section is  $\pm 5\%$  unless otherwise noted.

# **Adapter Application**

In the adapter application, there are two modes, bus-powered and self-powered. In the self-powered mode, the external power supply control circuitry is shown in Figure 8. In the VBUS powered mode, external CBUS circuitry is required to isolate the unpowered device loading and also to provide the 1 k $\Omega$  detection resistance to the source device as shown in Figure 9.

Figure 9. BUS-Powered Dongle with Isolation Circuit

# **Power Supply Decoupling**

Silicon Image recommends that designers include decoupling and bypass capacitors at each power pin in the layout. These are shown schematically in Figure 10. Place these components as close as possible to the SiI9292 device pins and avoid routing traces through vias, if possible. An example of this layout configuration is shown in Figure 11. Pins in each of the VDD12 and VDD33 groups can share C2, C3, and L1, with each pin having a separate C1 placed as close as possible to the pin. Suggested values for C1, C2 and C3 are 0.01  $\mu$ F, 0.1  $\mu$ F, and 10  $\mu$ F, respectively. The recommended impedance of the ferrite is 10  $\Omega$  or more in the frequency range of 1–2 MHz for all power supplies.

Figure 11. Decoupling and Bypass Capacitor Placement

# **High-Speed TMDS Signals**

### **Layout Guidelines**

The layout guidelines below help to ensure signal integrity, and Silicon Image strongly encourages the board designer to follow the guidelines below.

- Place the input and output connectors that carry the TMDS signals as close as possible to the chip.

- Place a 5.1  $\Omega \pm 5\%$  or better series resistor as close as possible to each TMDS receiver pin (see the Termination Requirement section on page 15 for details).

- Route the differential lines as directly as possible from the connector to the device when using industry-standard HDMI connectors.

- Route the two traces of each differential pair together.

- Minimize the number of vias through which the signal lines are routed.

- Lay out the MHL input pin traces with a controlled differential impedance of 100  $\Omega$  and a common mode impedance of 30  $\Omega$ . The differential impedance of the HDMI output pins must be designed within ±15% of 100  $\Omega$ .

- Serpentine traces are not recommended to compensate for inter-pair trace skew.

### **Termination Requirement**

A 5.1  $\Omega$  resistor, shown as *R* in Figure 12, must be placed in series with the SiI9292 Rx0± pins. In addition, the distance from the resistor to the MHL receiver pins, designated as *d* in the figure, must be within 1 cm or 393 mils, to ensure the impedance does not deviate from the limits allowed by the MHL 1.0 Specification.

**Figure 12. TMDS Signal Termination**

### **ESD** Protection

The SiI9292 bridge can withstand electrostatic discharges due to handling during manufacture. In applications where higher protection levels are required, ESD-limiting components can be placed on the differential lines of the chip. These components typically have a capacitive effect that reduces the signal quality at higher clock frequencies. Use the lowest capacitance devices possible. ESD components must be placed after the series termination resistors and as close as possible to the input or output connector. In no case can the capacitance value of these components exceed 1 pF.

#### **EMI Considerations**

Electromagnetic interference is a function of board layout, shielding, receiver component operating voltage, frequency of operation, and other factors. When attempting to control emissions, it is important not to place any passive components on the differential signal lines, except the common-mode chokes and ESD protection described earlier. The differential signaling used in HDMI is inherently low in EMI if the routing recommendations noted in the Layout Guidelines section are followed.

The PCB ground plane should extend unbroken under as much of the bridge chip and associated circuitry as possible, with all ground pins of the chip using a common ground.

re

# Packaging

### ePad Requirements

The SiI9292 chip is packaged in a 40-pin QFN package with an Exposed Pad<sup>TM</sup> (ePad<sup>TM</sup>), used both for electrical connectivity and for improved thermal transfer characteristics. The ePad dimensions are shown on the following page. Soldering of the ePad is *required* to meet package power dissipation requirements at full speed operation, and to correctly connect the chip circuitry to electrical ground.

**Note: The ePad must be soldered to the PCB ground**. Provide a landing area on the PCB with dimensions and location corresponding to the ePad within the footprint of the package. The size of this landing area can be larger than the ePad on the package but should be at least the same as the maximum size of exposed pad of the package (2.50 mm x 2.50 mm). If any circuit traces are within the area of the maximum size of the ePad, the trace may short to the pad if the package has a pad with the maximum dimensions.

The thermal land area on the PCB can use thermal vias to improve heat removal from the package. These thermal vias can double as ground connections, attaching internally in the PCB to the ground plane. An array of vias should be designed into the PCB beneath the package. For optimum thermal performance, Silicon Image recommends that the via diameter be 12 mils to 13 mils (0.30 mm to 0.33 mm) and the via barrel be plated with 1-ounce copper to plug the via. This is desirable to avoid any solder wicking inside the via during the soldering process, which may result in voids in solder between the exposed pad and the thermal land. If the copper plating does not plug the vias, the thermal vias can be tented with solder mask on the top surface of the PCB to avoid solder wicking inside the via during assembly. The solder mask diameter should be at least 4 mils (0.1 mm) larger than the via diameter.

Package stand-off is also a consideration. For a nominal stand-off of approximately 0.1 mm (see dimension A1), the stencil thickness of 5 mils to 8 mils provide a good solder joint between the ePad and the thermal land.

nterr

Silicon Image, Inc.

# **Package Dimensions**

Package drawings are not to scale.

| Item                  | Description    | Min      | Тур      | Max  | Item                   | Description       | Min      | Тур  | Max  |

|-----------------------|----------------|----------|----------|------|------------------------|-------------------|----------|------|------|

| А                     | Thickness      | 0.80     | 0.85     | 0.90 | D <sub>2</sub>         | ePad size         | 2.35     | 2.50 | 2.65 |

| A <sub>1</sub>        | Stand-off      | 0.00     | 0.02     | 0.05 | E <sub>2</sub>         | ePad size         | 2.35     | 2.50 | 2.65 |

| A <sub>2</sub>        | Body thickness | 0.60     | 0.65     | 0.70 | b                      | Plated lead width | 0.18     | 0.23 | 0.30 |

| A <sub>3</sub>        | Base thickness |          | 0.20 REF |      | e                      | Lead pitch        | 0.50 BSC |      |      |

| D                     | Body size      | 5.90     | 6.00     | 6.10 | L                      | Lead foot length  | 0.30     | 0.40 | 0.50 |

| Е                     | Body size      | 5.90     | 6.00     | 6.10 | θ                      | Mold angle        | 0°       | _    | 12°  |

| <b>D</b> <sub>1</sub> | Footprint      | 5.75 BSC |          | R    | Lead tip radius        | 0.09              | _        | _    |      |

| E <sub>1</sub>        | Footprint      | 5.75 BSC |          | K    | Lead to ePad clearance | 0.20              | _        | _    |      |

Figure 13. 40-pin QFN Package Diagram

# **Marking Specification**

Marking drawing is not to scale.

Figure 14. Marking Diagram

nema

### **Ordering Information**

| or doring mor mation                                                       |               |  |  |  |  |  |

|----------------------------------------------------------------------------|---------------|--|--|--|--|--|

| Production Device Type                                                     | Device Number |  |  |  |  |  |

| Universal                                                                  | SiI9292CNUC   |  |  |  |  |  |

| The universal package can be used in lead-free and ordinary process lines. |               |  |  |  |  |  |

|                                                                            |               |  |  |  |  |  |

# References

### **Standards Documents**

Table 9 lists the abbreviations used in this document. Contact the responsible standards groups listed in Table 10 for more information on these specifications.

| Abbreviation     | Standards publication, organization, and date                                                     |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|

| HDMI             | II High Definition Multimedia Interface, Revision 1.4a, HDMI Consortium, March 2010               |  |  |  |  |

| HCTS             | CTS HDMI Compliance Test Specification, Revision 1.4a, HDMI Consortium, March 2010                |  |  |  |  |

| DVI              | DVI Digital Visual Interface, Revision 1.0, Digital Display Working Group, April 1999             |  |  |  |  |

| E-EDID           | DID Enhanced Extended Display Identification Data Standard, Release A Revision 1, VESA, Feb. 2000 |  |  |  |  |

| E-DID IG         | VESA EDID Implementation Guide, VESA, March 2001                                                  |  |  |  |  |

| CEA-861-D        | A DTV Profile for Uncompressed High Speed Digital Interfaces, Draft 020328, EIA/CEA, July 2006    |  |  |  |  |

| EDDC             | Enhanced Display Data Channel Standard, Version 1.1, VESA, March 2004                             |  |  |  |  |

| I <sup>2</sup> C | The l <sup>2</sup> C Bus Specification, Version 2.1, Philips Semiconductors, January 2000         |  |  |  |  |

| MHL              | MHL (Mobile High-definition Link) Specification, Version 1.0, MHL, LLC, June 2010                 |  |  |  |  |

#### **Table 9. Referenced Documents**

### Table 10. Standards Groups Contact Information

| Standards Group  | Web URL                      | e-mail                            | Phone        |

|------------------|------------------------------|-----------------------------------|--------------|

| ANSI/EIA/CEA     | http://global.ihs.com        | global@ihs.com                    | 800-854-7179 |

| VESA             | http://www.vesa.org          | _                                 | 408-957-9270 |

| DVI              | http://www.ddwg.org          | ddwg.if@intel.com                 | —            |

| I <sup>2</sup> C | http://www.nxp.com           |                                   | —            |

| HDMI             | http://www.hdmi.org          | admin@hdmi.org                    | _            |

| MHL              | http://www.mhlconsortium.org | Customerservice@mhlconsortium.org | 408-962-4269 |

### **Silicon Image Documents**

Table 11 lists Silicon Image documents that are available from your Silicon Image sales representative.

### Table 11. Silicon Image Publications

| Document    | Title                                       |

|-------------|---------------------------------------------|

| SiI-PR-1049 | SiI1292 and SiI9292 MHL/HDMI-to-HDMI Bridge |

|             |                                             |

#### Disclaimers

These materials are provided on an "AS IS" basis. Silicon Image, Inc. and its affiliates disclaim all representations and warranties (express, implied, statutory or otherwise), including but not limited to: (i) all implied warranties of merchantability, fitness for a particular purpose, and/or non-infringement of third party rights; (ii) all warranties arising out of course-of-dealing, usage, and/or trade; and (iii) all warranties that the information or results provided in, or that may be obtained from use of, the materials are accurate, reliable, complete, up-to-date, or produce specific outcomes. Silicon Image, Inc. and its affiliates assume no liability or responsibility for any errors or omissions in these materials, makes no commitment or warranty to correct any such errors or omissions or update or keep current the information contained in these materials, and expressly disclaims all direct, indirect, special, incidental, consequential, reliance and punitive damages, including WITHOUT LIMITATION any loss of profits arising out of your access to, use or interpretation of, or actions taken or not taken based on the content of these materials.

Silicon Image, Inc. and its affiliates reserve the right, without notice, to periodically modify the information in these materials, and to add to, delete, and/or change any of this information.

Notwithstanding the foregoing, these materials shall not, in the absence of authorization under U.S. and local law and regulations, as required, be used by or exported or re-exported to (i) any U.S. sanctioned or embargoed country, or to nationals or residents of such countries; or (ii) any person, entity, organization or other party identified on the U.S. Department of Commerce's Denied Persons or Entity List, the U.S. Department of Treasury's Specially Designated Nationals or Blocked Persons List, or the Department of State's Debarred Parties List, as published and revised from time to time; (iii) any party engaged in nuclear, chemical/biological weapons or missile proliferation activities; or (iv) any party for use in the design, development, or production of rocket systems or unmanned air vehicles.

#### **Products and Services**

The products and services described in these materials, and any other information, services, designs, know-how and/or products provided by Silicon Image, Inc. and/or its affiliates are provided on as "AS IS" basis, except to the extent that Silicon Image, Inc. and/or its affiliates provides an applicable written limited warranty in its standard form license agreements, standard Terms and Conditions of Sale and Service or its other applicable standard form agreements, in which case such limited warranty shall apply and shall govern in lieu of all other warranties (express, statutory, or implied). EXCEPT FOR SUCH LIMITED WARRANTY, SILICON IMAGE, INC. AND ITS AFFILIATES DISCLAIM ALL REPRESENTATIONS AND WARRANTIES (EXPRESS, IMPLIED, STATUTORY OR OTHERWISE), REGARDING THE INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS PROVIDED BY SILICON IMAGE, INC. AND/OR ITS AFFILIATES, INCLUDING BUT NOT LIMITED TO, ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND/OR NON-INFRINGEMENT OF THIRD PARTY RIGHTS. YOU ACKNOWLEDGE AND AGREE THAT SUCH INFORMATION, SERVICES, DESIGNS, KNOW-HOW AND PRODUCTS HAVE NOT BEEN DESIGNED, TESTED, OR MANUFACTURED FOR USE OR RESALE IN SYSTEMS WHERE THE FAILURE, MALFUNCTION, OR ANY INACCURACY OF THESE ITEMS CARRIES A RISK OF DEATH OR SERIOUS BODILY INJURY, INCLUDING, BUT NOT LIMITED TO, USE IN NUCLEAR FACILITIES, AIRCRAFT NAVIGATION OR COMMUNICATION, EMERGENCY SYSTEMS, OR OTHER SYSTEMS WITH A SIMILAR DEGREE OF POTENTIAL HAZARD. NO PERSON IS AUTHORIZED TO MAKE ANY OTHER WARRANTY OR REPRESENTATION CONCERNING THE PERFORMANCE OF THE INFORMATION, PRODUCTS, KNOW-HOW, DESIGNS OR SERVICES OTHER THAN AS PROVIDED IN THESE TERMS AND CONDITIONS.

1060 E. Arques Avenue Sunnyvale, CA 94085 T 408.616.4000 F 408.830.9530 www.siliconimage.com

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Audio DSPs category:

Click to view products by Lattice manufacturer:

Other Similar products are found below :

E-TDA7377A TDA7716N BR281W31A101V1G LC823425-12G1-LR-H TDA7419N R3910-CFAB-E1B HMC474MP86ETR AMIS30660CANH6G B300W35A102XYG MAX9892ERT+T MAX9892ELTT SB3229-E1 NJW1157BFC2 ZL38060LDG1 SB3231-E1 HMC1022-SX SA3229-E1-T LC75056PE-H TDA7729 NJW1195AV WM5102ECS/R CI1103 WM5102ECS/R 100-CG1820 CS48L10-CNZ CS48L10-CNZR CS47024C-CQZ CS48L10-CWZR CS48L11-CNZ HMC618LP3ETR HMC604LP3ETR HMC5622LS7TR HMC288MS8ETR HMC240A STA323W13TR BU9408KS2 DSPB56725AF TAS3204PAGR ADAU1467WBCPZ300 ADAU1463WBCPZ300 BD37514FS-E2 ADAU1463WBCPZ150 ADAU1466WBCPZ300 NJM2294V-TE1 LC823450TA-2H NJM2537V-TE1 TWL1103TPBSQ1 LC823450XDTBG HMC-AUH312-SX ADAV4622BSTZ