# BF909; BF909R

### N-channel dual gate MOS-FETs

Rev. 02 — 19 November 2007

**Product data sheet**

### **IMPORTANT NOTICE**

Dear customer,

As from October 1st, 2006 Philips Semiconductors has a new trade name

- NXP Semiconductors, which will be used in future data sheets together with new contact details.

In data sheets where the previous Philips references remain, please use the new links as shown below.

http://www.philips.semiconductors.com use http://www.nxp.com

http://www.semiconductors.philips.com use http://www.nxp.com (Internet)

$sales. addresses @www.semiconductors.philips.com\ use\ sales addresses @nxp.com\ (email)$

The copyright notice at the bottom of each page (or elsewhere in the document, depending on the version)

- © Koninklijke Philips Electronics N.V. (year). All rights reserved is replaced with:

- © NXP B.V. (year). All rights reserved. -

If you have any questions related to the data sheet, please contact our nearest sales office via e-mail or phone (details via salesaddresses@nxp.com). Thank you for your cooperation and understanding,

**NXP Semiconductors**

### N-channel dual gate MOS-FETs

BF909; BF909R

#### **FEATURES**

- Specially designed for use at 5 V supply voltage

- · High forward transfer admittance

- Short channel transistor with high forward transfer admittance to input capacitance ratio

- Low noise gain controlled amplifier up to 1 GHz

- Superior cross-modulation performance during AGC.

### **APPLICATIONS**

VHF and UHF applications with 3 to 7 V supply voltage such as television tuners and professional communications equipment.

### **DESCRIPTION**

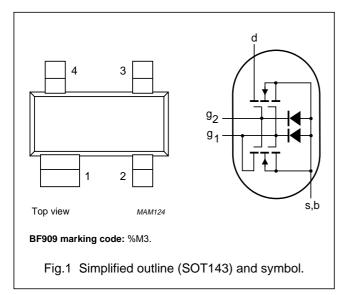

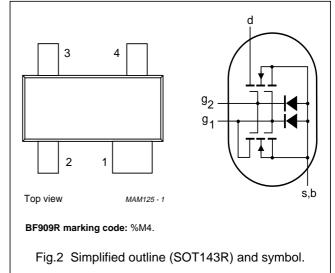

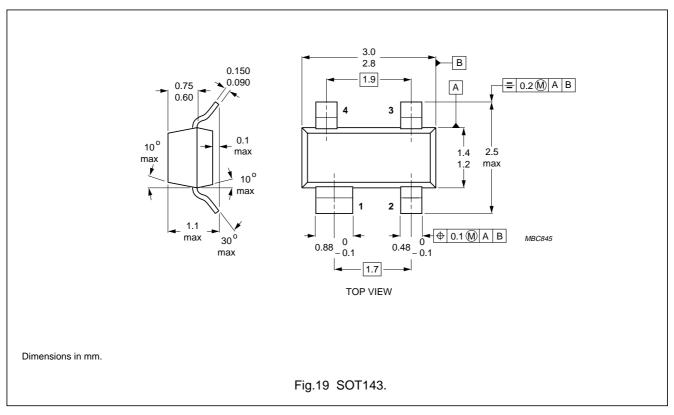

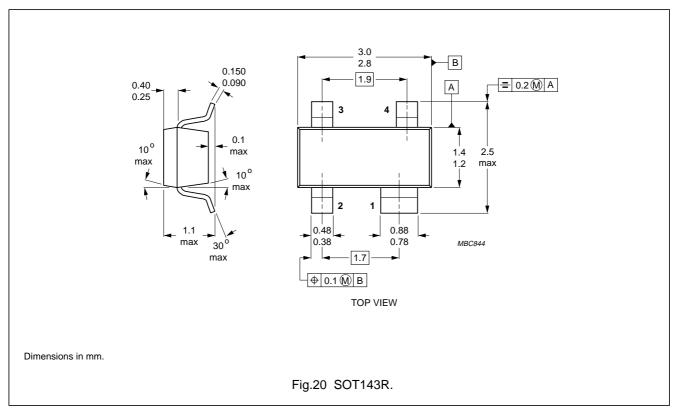

Enhancement type field-effect transistor in a plastic microminiature SOT143 or SOT143R package. The

transistor consists of an amplifier MOS-FET with source and substrate interconnected and an internal bias circuit to ensure good cross-modulation performance during AGC.

#### **CAUTION**

The device is supplied in an antistatic package. The gate-source input must be protected against static discharge during transport or handling.

#### **PINNING**

| PIN | SYMBOL                | DESCRIPTION |

|-----|-----------------------|-------------|

| 1   | s, b                  | source      |

| 2   | d                     | drain       |

| 3   | <b>g</b> <sub>2</sub> | gate 2      |

| 4   | <b>9</b> 1            | gate 1      |

### **QUICK REFERENCE DATA**

| SYMBOL             | PARAMETER                      | CONDITIONS  | MIN. | TYP. | MAX. | UNIT |

|--------------------|--------------------------------|-------------|------|------|------|------|

| V <sub>DS</sub>    | drain-source voltage           |             | _    | _    | 7    | V    |

| I <sub>D</sub>     | drain current                  |             | _    | _    | 40   | mA   |

| P <sub>tot</sub>   | total power dissipation        |             | _    | _    | 200  | mW   |

| T <sub>j</sub>     | operating junction temperature |             | _    | _    | 150  | °C   |

| y <sub>fs</sub>    | forward transfer admittance    |             | 36   | 43   | 50   | mS   |

| C <sub>ig1-s</sub> | input capacitance at gate 1    |             | _    | 3.6  | 4.3  | pF   |

| C <sub>rs</sub>    | reverse transfer capacitance   | f = 1 MHz   | _    | 35   | 50   | fF   |

| F                  | noise figure                   | f = 800 MHz | _    | 2    | 2.8  | dB   |

# N-channel dual gate MOS-FETs

BF909; BF909R

### **LIMITING VALUES**

In accordance with the Absolute Maximum Rating System (IEC 134).

| SYMBOL           | PARAMETER                      | CONDITIONS                              | MIN. | MAX. | UNIT |

|------------------|--------------------------------|-----------------------------------------|------|------|------|

| V <sub>DS</sub>  | drain-source voltage           |                                         | _    | 7    | V    |

| I <sub>D</sub>   | drain current                  |                                         | _    | 40   | mA   |

| I <sub>G1</sub>  | gate 1 current                 |                                         | _    | ±10  | mA   |

| I <sub>G2</sub>  | gate 2 current                 |                                         | _    | ±10  | mA   |

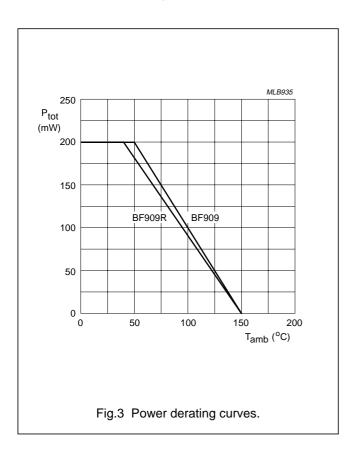

| P <sub>tot</sub> | total power dissipation        | see Fig.3                               |      |      |      |

|                  | BF909                          | up to $T_{amb} = 50 ^{\circ}C$ ; note 1 | _    | 200  | mW   |

|                  | BF909R                         | up to $T_{amb} = 40 ^{\circ}C$ ; note 1 | _    | 200  | mW   |

| T <sub>stg</sub> | storage temperature            |                                         | -65  | +150 | °C   |

| Tj               | operating junction temperature |                                         | _    | 150  | °C   |

### Note

1. Device mounted on a printed-circuit board.

### N-channel dual gate MOS-FETs

BF909; BF909R

### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                           | CONDITIONS             | VALUE | UNIT |

|---------------------|-----------------------------------------------------|------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient         | note 1                 |       |      |

|                     | BF909                                               |                        | 500   | K/W  |

|                     | BF909R                                              |                        | 550   | K/W  |

| R <sub>th j-s</sub> | thermal resistance from junction to soldering point | note 2                 |       |      |

|                     | BF909                                               | T <sub>s</sub> = 92 °C | 290   | K/W  |

|                     | BF909R                                              | T <sub>s</sub> = 78 °C | 360   | K/W  |

#### **Notes**

- 1. Device mounted on a printed-circuit board.

- 2.  $T_s$  is the temperature at the soldering point of the source lead.

### STATIC CHARACTERISTICS

$T_i$  = 25 °C; unless otherwise specified.

| SYMBOL                 | PARAMETER                       | CONDITIONS                                                                                        | MIN. | MAX. | UNIT |

|------------------------|---------------------------------|---------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>(BR)G1-SS</sub> | gate 1-source breakdown voltage | $V_{G2-S} = V_{DS} = 0$ ; $I_{G1-S} = 10 \text{ mA}$                                              | 6    | 15   | V    |

| V <sub>(BR)G2-SS</sub> | gate 2-source breakdown voltage | $V_{G1-S} = V_{DS} = 0$ ; $I_{G2-S} = 10 \text{ mA}$                                              | 6    | 15   | V    |

| V <sub>(F)S-G1</sub>   | forward source-gate 1 voltage   | $V_{G2-S} = V_{DS} = 0$ ; $I_{S-G1} = 10 \text{ mA}$                                              | 0.5  | 1.5  | V    |

| V <sub>(F)S-G2</sub>   | forward source-gate 2 voltage   | $V_{G1-S} = V_{DS} = 0$ ; $I_{S-G2} = 10 \text{ mA}$                                              | 0.5  | 1.5  | V    |

| V <sub>G1-S(th)</sub>  | gate 1-source threshold voltage | $V_{G2-S} = 4 \text{ V}; V_{DS} = 5 \text{ V};$<br>$I_D = 20 \mu A$                               | 0.3  | 1    | V    |

| V <sub>G2-S(th)</sub>  | gate 2-source threshold voltage | $V_{G1-S} = V_{DS} = 5 \text{ V}; I_D = 20 \mu\text{A}$                                           | 0.3  | 1.2  | V    |

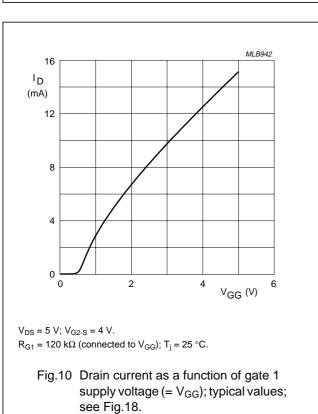

| I <sub>DSX</sub>       | drain-source current            | $V_{G2-S} = 4 \text{ V}; V_{DS} = 5 \text{ V};$<br>$R_{G1} = 120 \text{ k}\Omega; \text{ note 1}$ | 12   | 20   | mA   |

| I <sub>G1-SS</sub>     | gate 1 cut-off current          | $V_{G1-S} = 5 \text{ V}; V_{G2-S} = V_{DS} = 0$                                                   | _    | 50   | nA   |

| I <sub>G2-SS</sub>     | gate 2 cut-off current          | $V_{G2-S} = 5 \text{ V}; V_{G1-S} = V_{DS} = 0$                                                   | _    | 50   | nA   |

### Note

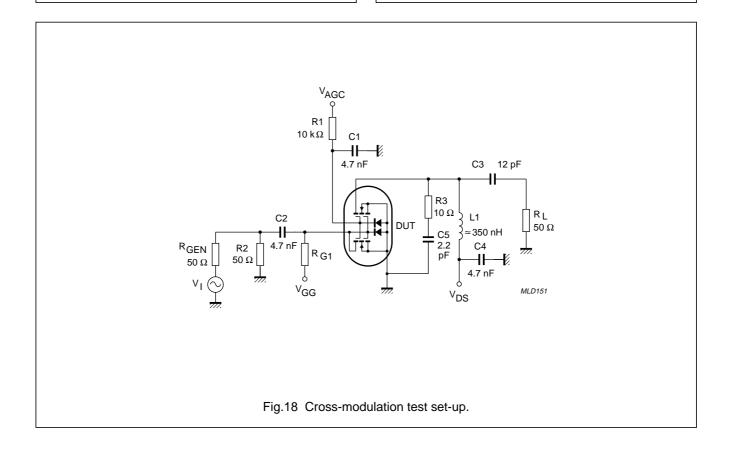

1.  $R_{G1}$  connects gate 1 to  $V_{GG}$  = 5 V; see Fig.18.

### **DYNAMIC CHARACTERISTICS**

Common source;  $T_{amb}$  = 25 °C;  $V_{DS}$  = 5 V;  $V_{G2-S}$  = 4 V;  $I_D$  = 15 mA; unless otherwise specified.

| SYMBOL             | PARAMETER                    | CONDITIONS                                            | MIN. | TYP. | MAX. | UNIT |

|--------------------|------------------------------|-------------------------------------------------------|------|------|------|------|

| y <sub>fs</sub>    | forward transfer admittance  | pulsed; T <sub>j</sub> = 25 °C                        | 36   | 43   | 50   | mS   |

| C <sub>ig1-s</sub> | input capacitance at gate 1  | f = 1 MHz                                             | _    | 3.6  | 4.3  | pF   |

| C <sub>ig2-s</sub> | input capacitance at gate 2  | f = 1 MHz                                             | _    | 2.3  | 3    | pF   |

| Cos                | drain-source capacitance     | f = 1 MHz                                             | _    | 2.3  | 3    | pF   |

| C <sub>rs</sub>    | reverse transfer capacitance | f = 1 MHz                                             | _    | 35   | 50   | fF   |

| F                  | noise figure                 | $f = 800 \text{ MHz}; G_S = G_{Sopt}; B_S = B_{Sopt}$ | _    | 2    | 2.8  | dB   |

# N-channel dual gate MOS-FETs

BF909; BF909R

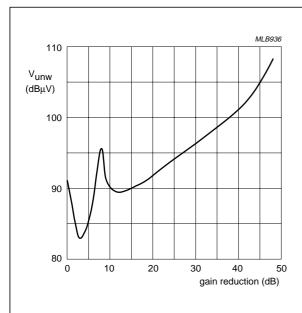

$V_{DS} = 5 \text{ V}; \ V_{GG} = 5 \text{ V}; \ f_w = 50 \text{ MHz}.$   $f_{unw} = 60 \text{ MHz}; \ T_{amb} = 25 \text{ °C}; \ R_{G1} = 120 \text{ k}\Omega.$

Fig.4 Unwanted voltage for 1% cross-modulation as a function of gain reduction; typical values; see Fig.18.

# N-channel dual gate MOS-FETs

# N-channel dual gate MOS-FETs

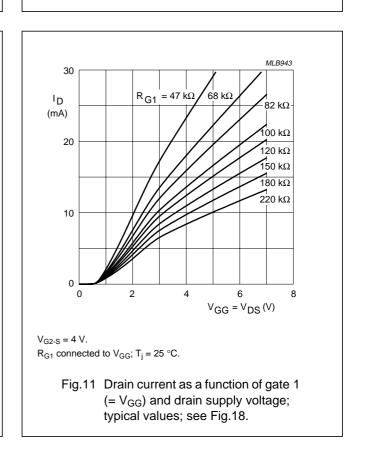

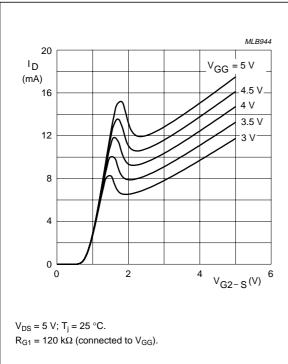

Fig.12 Drain current as a function of gate 2 voltage; typical values; see Fig.18.

### N-channel dual gate MOS-FETs

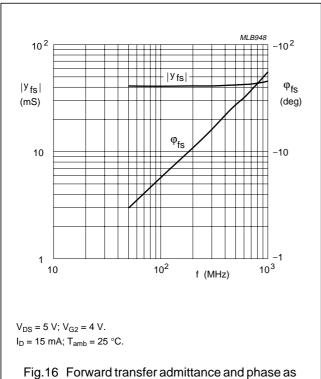

Fig.16 Forward transfer admittance and phase as a function of frequency; typical values.

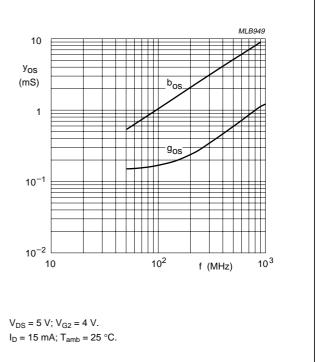

Fig.17 Output admittance as a function of frequency; typical values.

# N-channel dual gate MOS-FETs

**Table 1** Scattering parameters:  $T_{amb} = 25 \, ^{\circ}C$ ;  $V_{DS} = 5 \, V$ ;  $V_{G2-S} = 4 \, V$ ;  $I_D = 15 \, mA$

|       | S <sub>11</sub>   |                | S <sub>21</sub>   |                | S <sub>12</sub>   |                | S <sub>22</sub>   |                |

|-------|-------------------|----------------|-------------------|----------------|-------------------|----------------|-------------------|----------------|

| (MHz) | MAGNITUDE (ratio) | ANGLE<br>(deg) |

| 50    | 0.985             | -6.4           | 4.064             | 172.3          | 0.001             | 86.9           | 0.985             | -3.2           |

| 100   | 0.978             | -12.6          | 3.997             | 164.9          | 0.002             | 82.7           | 0.982             | -6.4           |

| 200   | 0.957             | -25.0          | 3.886             | 150.8          | 0.005             | 74.3           | 0.973             | -12.6          |

| 300   | 0.931             | -36.5          | 3.682             | 137.3          | 0.006             | 68.9           | 0.960             | -18.6          |

| 400   | 0.899             | -47.6          | 3.484             | 123.8          | 0.007             | 59.6           | 0.947             | -24.2          |

| 500   | 0.868             | -57.4          | 3.260             | 111.7          | 0.007             | 57.9           | 0.936             | -29.6          |

| 600   | 0.848             | -66.6          | 3.053             | 101.0          | 0.006             | 58.5           | 0.927             | -34.8          |

| 700   | 0.816             | -74.6          | 2.829             | 90.3           | 0.005             | 65.5           | 0.919             | -39.8          |

| 800   | 0.792             | -82.2          | 2.652             | 79.9           | 0.005             | 83.3           | 0.913             | -44.6          |

| 900   | 0.772             | -89.3          | 2.470             | 69.5           | 0.005             | 114.9          | 0.910             | -49.5          |

| 1000  | 0.754             | -95.6          | 2.328             | 59.5           | 0.006             | 138.7          | 0.909             | -54.6          |

**Table 2** Noise data:  $T_{amb}$  = 25 °C;  $V_{DS}$  = 5 V;  $V_{G2-S}$  = 4 V;  $I_D$  = 15 mA

| f     | F <sub>min</sub> | $\Gamma_{f opt}$ |       | •     |

|-------|------------------|------------------|-------|-------|

| (MHz) | (dB)             | (ratio)          | (deg) | 'n    |

| 800   | 2.00             | 0.603            | 67.71 | 0.581 |

# N-channel dual gate MOS-FETs

BF909; BF909R

### **PACKAGE OUTLINES**

N-channel dual gate MOS-FETs

### **Legal information**

### **Data sheet status**

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### **Definitions**

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### **Disclaimers**

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### **Trademarks**

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### **Contact information**

For additional information, please visit: http://www.nxp.com

For sales office addresses, send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

N-channel dual gate MOS-FETs

# **Revision history**

### **Revision history**

| Document ID    | Release date                       | Data sheet status             | Change notice | Supersedes |

|----------------|------------------------------------|-------------------------------|---------------|------------|

| BF909_N_2      | 20071119                           | Product data sheet            | -             | BF909_1    |

| Modifications: | <ul> <li>Fig.1 and 2 or</li> </ul> | on page 2; Figure note change | d             |            |

| BF909_1        | 19950425                           | Product specification         | -             | -          |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for MOSFET category:

Click to view products by NXP manufacturer:

Other Similar products are found below:

614233C 648584F MCH3443-TL-E MCH6422-TL-E FDPF9N50NZ FW231A-TL-E APT5010JVR NTNS3A92PZT5G IRF100S201

JANTX2N5237 2SK2464-TL-E 2SK3818-DL-E FCA20N60\_F109 FDZ595PZ STD6600NT4G FSS804-TL-E 2SJ277-DL-E 2SK1691-DLE 2SK2545(Q,T) D2294UK 405094E 423220D MCH6646-TL-E TPCC8103,L1Q(CM 367-8430-0972-503 VN1206L 424134F 026935X 051075F SBVS138LT1G 614234A 715780A NTNS3166NZT5G 751625C 873612G IRF7380TRHR IPS70R2K0CEAKMA1

RJK60S3DPP-E0#T2 RJK60S5DPK-M0#T0 APT5010JVFR APT12031JFLL APT12040JVR DMN3404LQ-7 NTE6400 JANTX2N6796U JANTX2N6784U JANTXV2N5416U4 SQM110N05-06L-GE3 SIHF35N60E-GE3 2SK2614(TE16L1,Q)