# MB86R03 'Jade-L' LSI Product Specifications

November, 2009 The 1.2 edition

# **Preface**

# **Objectives and Intended Reader**

Thank you very much for your continued special support for Fujitsu Microelectronics semiconductor products.

MB86R03 is LSI product for the graphics applications.

This manual describes functions and operations of MB86R03 for engineers who design products using MB86R03. Read through this manual before use.

## **Trademarks**

ARM is a registered trademark of ARM Limited in UK, USA and Taiwan.

ARM is a trademark of ARM Limited in Japan and Korea.

ARM Powered logo is a registered trademark of ARM Limited in Japan, UK, USA, and Taiwan.

ARM Powered logo is a trademark of ARM Limited in Korea.

ARM926EJ-S and ETM9 are trademarks of ARM Limited.

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

## **Hardware Related Manuals**

MB86R03 hardware related manuals are shown below. Refer them as the situation demands.

- MB86R03 'Jade-L' LSI product specifications graphics display controller (GDC)

- MB86R03 'Jade-L' LSI product specifications SD memory controller (Note)

- MB86R03 'Jade-L' Data sheet

Note) This specification document is for SD card licensee.

- The contents of this document are subject to change without notice. Customers are advised to consult with sales representatives before ordering.

- The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

- Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- · Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

- The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

All rights reserved, Copyright FUJITSU MICROELECTRONICS LIMITED 2009

# **Revision History**

| Date       | Ver. | Contents                                                                           |

|------------|------|------------------------------------------------------------------------------------|

| 2009/09/18 | 1.0  | Newly issued                                                                       |

| 2009/10/07 | 1.1  | Whole contents                                                                     |

|            |      | Added model number (MB86R03)                                                       |

|            |      | 1.6.23. Unused pin                                                                 |

|            |      | • Table 1-31                                                                       |

|            |      | Revised description of P2, P5, R1, R2, R3, R5, T1, T2, and U3                      |

|            |      | Added description of *1) and *2)                                                   |

| 2009/11/24 | 1.2  | 1.6.23. Unused pin                                                                 |

|            |      | • Revised table 1-31                                                               |

|            |      | [Pin No.] [JEDEC] [Pin name] [Pin name]                                            |

|            |      | 112 N2 VINFID0, GI1[3], MLB_CLK -> VINFID0, GI1[3]                                 |

|            |      | 202 M3 VINVSYNC0, GI1[5], MLB_DATA -> VINVSYNC0, GI1[5]                            |

|            |      | 203 N3 VINHSYNCO, GI1[4], MLB_SIG -> VINHSYNCO, GI1[4]                             |

|            |      | 3.3. Register map                                                                  |

|            |      | • Revised table 3-2                                                                |

|            |      | [Address] [Register name][Explanation] [Register name][Explanation]                |

|            |      | FFF4_2038 <sub>H</sub> CMLB MediaLB setting register -> Reserved Access prohibited |

|            |      | FFF4_2040 <sub>H</sub> CUSB USB setting register -> Reserved Access prohibited     |

# **Contents**

| 1. O  | utline                                                          | 1-1  |

|-------|-----------------------------------------------------------------|------|

| 1.1.  | Feature                                                         | 1-1  |

| 1.2.  | Block diagram                                                   |      |

| 1.3.  | Function list                                                   |      |

| 1.4.  | Package dimension                                               |      |

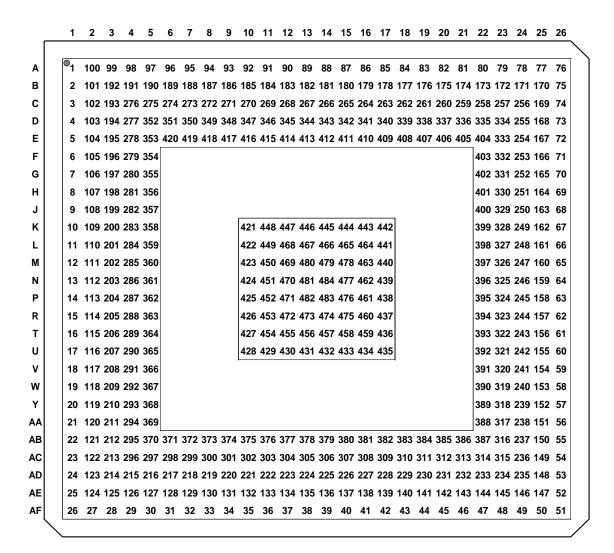

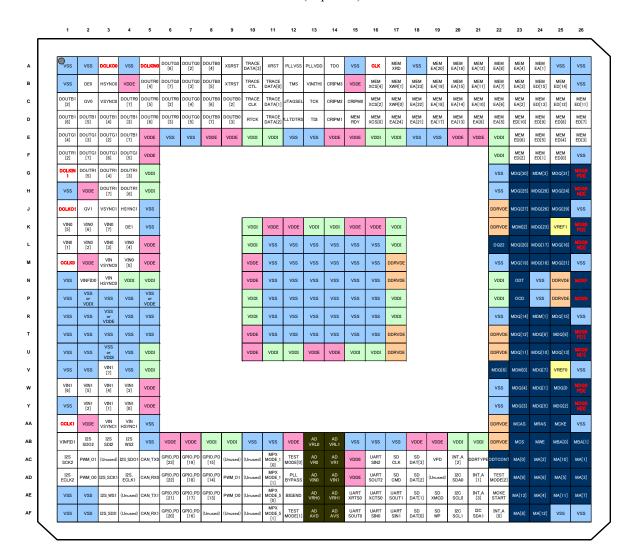

| 1.5.  | Pin assignment                                                  | 1-8  |

| 1.6.  | Pin function                                                    | 1-11 |

| 1.6   | 5.1. Pin Multiplex                                              | 1-11 |

| 1.6   | 5.2. Pin function                                               | 1-16 |

| 1.6   | 5.3. External bus interface related pin                         | 1-17 |

| 1.6   | 5.4. SD memory controller related pin                           | 1-17 |

| 1.6   | 6.5. External interrupt controller related pin                  | 1-17 |

| 1.6   | 5.6. UART related pin                                           | 1-18 |

| 1.6   | 5.7. CAN related pin                                            | 1-18 |

| 1.6   | 5.8. I2S related pin                                            | 1-19 |

| 1.6   | 5.9. I <sup>2</sup> C related pin                               | 1-19 |

| 1.6   | 5.10. SPI related pin                                           | 1-19 |

| 1.6   | 5.11. PWM related pin                                           | 1-20 |

| 1.6   | 5.12. A/D converter related pin                                 | 1-20 |

| 1.6   | 5.13. DDR2 related pin                                          | 1-21 |

| 1.6   | 5.14. DISPLAY related pin                                       | 1-22 |

| 1.6   | 5.15. Video capture related pin                                 | 1-23 |

| 1.6   | 5.16. System related pin                                        | 1-23 |

| 1.6   | 5.17. JTAG related pin                                          | 1-24 |

| 1.6   | 5.18. ICE related pin                                           | 1-24 |

| 1.6   | 5.19. Multiplex setting related pin                             | 1-24 |

| 1.6   | 5.20. ETM related pin                                           | 1-25 |

| 1.6   | 5.21. Power supply related pin                                  | 1-25 |

| 1.6   | 5.22. GPIO related pin                                          | 1-25 |

| 1.6   | 5.23. Unused pin                                                |      |

| 1.6   | 6.24. Unused pin in the duplex case with pin multiplex function | 1-34 |

| 2. Sy | ystem configuration                                             | 2-1  |

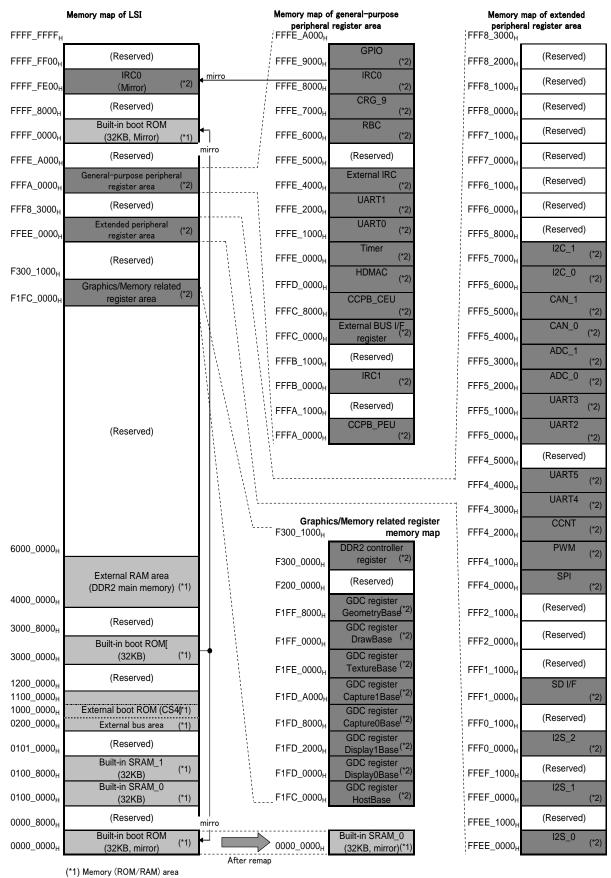

| 3. M  | emory map                                                       | 3-1  |

| 3.1.  | Memory map of LSI                                               | 3-1  |

| 3.2.  | Register access                                                 |      |

| 3.3.  | Register map                                                    |      |

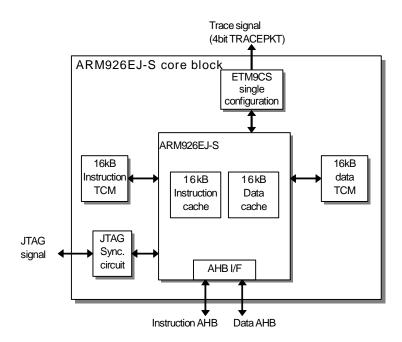

| 4. CF | PU (ARM926EJ-S core part)                                       | 4-1  |

| 4.1.  | Outline                                                         | 4-1  |

| 4.2.  | Feature                                                         |      |

| 4.3.  | Block diagram                                                   |      |

| 44    | ARM926EI-S and ETM setting                                      |      |

| 5. C                                    | IOCK         | reset generator (CRG)                                                    | 5-1  |

|-----------------------------------------|--------------|--------------------------------------------------------------------------|------|

| 5.1.                                    | Ou           | ıtline                                                                   | 5-1  |

| 5.2.                                    | Fea          | ature                                                                    | 5-1  |

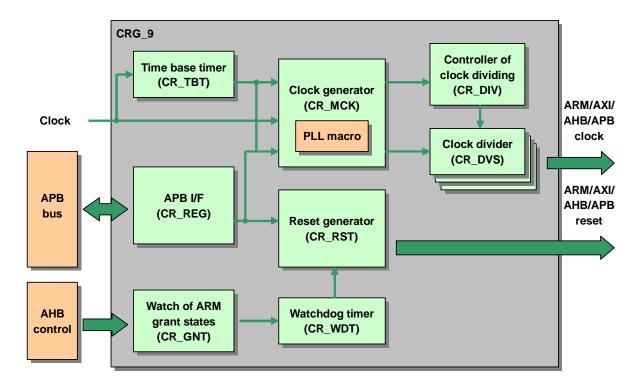

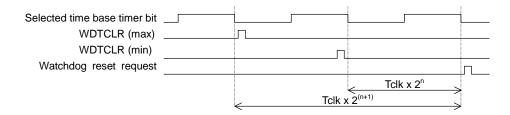

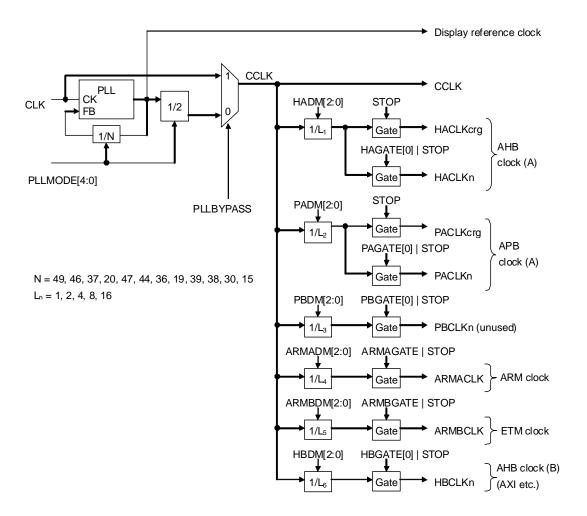

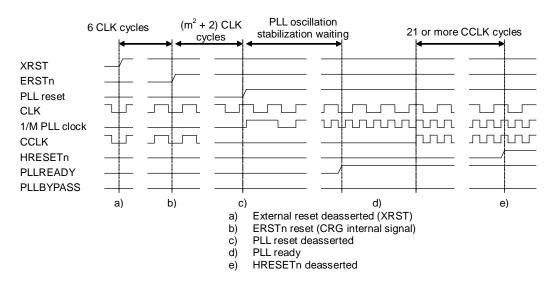

| 5.3.                                    | Blo          | ock diagram                                                              | 5-2  |

| 5.4.                                    | Re           | gister                                                                   | 5-3  |

| 5.4                                     | 4.1.         | Register list                                                            |      |

| 5.4                                     | 4.2.         | PLL control register (CRPR)                                              |      |

| 5.4                                     | 4.3.         | Watchdog timer control register (CRWR)                                   |      |

| 5.4                                     | 4.4.         | Reset/Standby control register (CRSR)                                    |      |

| 5.4                                     | 4.5.         | Clock divider control register A (CRDA)                                  |      |

| 5.4                                     | 4.6.         | Clock divider control register B (CRDB)                                  |      |

| 5.4                                     | 4.7.         | AHB (A) bus clock gate control register (CRHA)                           |      |

| 5.4                                     | 4.8.         | APB (A) bus clock gate control register (CRPA)                           |      |

| 5.4                                     | 4.9.         | APB (B) bus clock gate control register (CRPB)                           |      |

|                                         | 4.10.        | AHB (B) bus clock gate control register (CRHB)                           |      |

|                                         | 4.11.        | ARM core clock gate control register (CRAM)                              |      |

| 5.5.                                    |              | peration                                                                 |      |

|                                         | 5.1.         | Generation of reset                                                      |      |

|                                         | 5.2.         | Clock generation                                                         |      |

| ٥.,                                     | J.2.         | Clock generation                                                         |      |

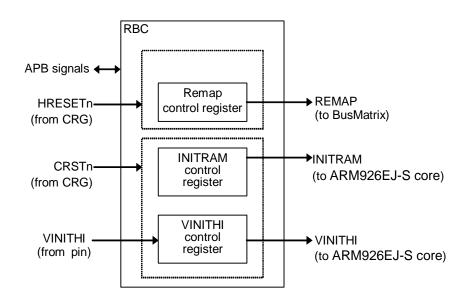

| 6. R                                    | ema          | p boot controller (RBC)                                                  | 6-1  |

| •                                       |              |                                                                          |      |

| 6.1.                                    | Ou           | ıtline                                                                   | 6-1  |

| 6.2.                                    |              | ature                                                                    |      |

| 6.3.                                    |              | ock diagram                                                              |      |

| 6.4.                                    |              | pply clock                                                               |      |

| 6.5.                                    |              | gister                                                                   |      |

|                                         | 5.1.         | Register list                                                            |      |

|                                         | 5.2.         | Remap control register (RBREMAP)                                         |      |

| 6                                       | 5.3.         | VINITHI control register A (RBVIHA)                                      |      |

|                                         | 5.4.         | INITRAM control register A (RBITRA)                                      |      |

| 6.6.                                    |              | peration                                                                 |      |

|                                         | -            | RBC reset                                                                |      |

|                                         | 6.2.         | Remap control                                                            |      |

|                                         | 6.3.         | VINITHI control                                                          |      |

|                                         | 6.4.         | INITRAM control                                                          |      |

| 0.                                      | 0. 1.        | 1 VIIV IVI COMOI                                                         |      |

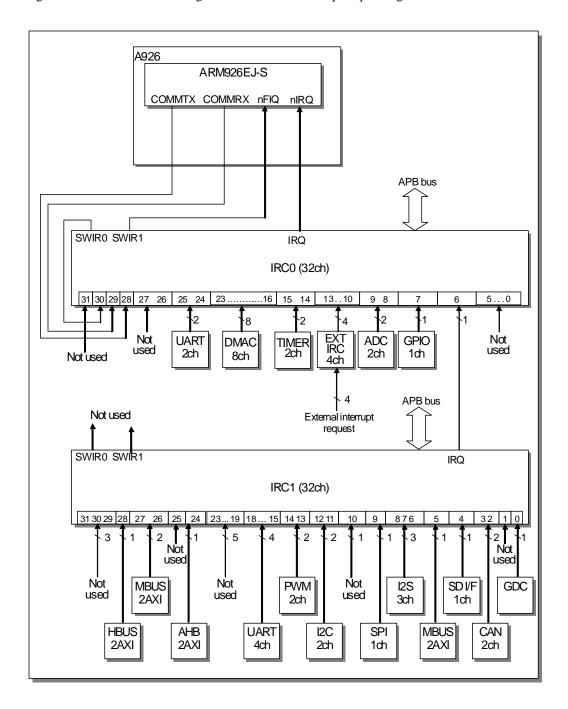

| 7 In                                    | ıtarr        | upt controller (IRC)                                                     | 7-1  |

| • • • • • • • • • • • • • • • • • • • • |              |                                                                          |      |

| 7.1.                                    | Ou           | ıtline                                                                   | 7-1  |

| 7.2.                                    |              | ature                                                                    |      |

| 7.3.                                    |              | ock diagram                                                              |      |

| 7.3.<br>7.4.                            |              | pply clock                                                               |      |

| 7.5.                                    |              | errupt map                                                               |      |

|                                         | 5.1.         | Exception vector to ARM926EJ-S core                                      |      |

|                                         | 5.1.<br>5.2. | Extension IRQ interrupt vector of IRC0/IRC1IRC0/IRC1                     |      |

| 7<br>7.6.                               |              | gistergister                                                             |      |

|                                         | ке<br>6.1.   | Register list                                                            |      |

|                                         | 6.1.<br>6.2. |                                                                          |      |

|                                         | 6.2.<br>6.3. | IRQ flag register (IR0IRQF/ IR1IRQF)IRO mask register (IR0IROM/IR1IROM). |      |

| , ,                                     |              | TING THAN TERINET CHNUTNOWI/TIN LINGUIVI                                 | /-11 |

| 7.6.4.           | Interrupt level mask register (IR0ILM/IR1ILM)    | 7-12 |

|------------------|--------------------------------------------------|------|

| 7.6.5.           | ICR monitoring register (IR0ICRMN/IR1ICRMN)      | 7-13 |

| 7.6.6.           | Delay interrupt control register 0 (IR0DICR0)    | 7-14 |

| 7.6.7.           | Delay interrupt control register 1 (IR0DICR1)    | 7-15 |

| 7.6.8.           | Table base register (IR0TBR/IR1TBR)              | 7-16 |

| 7.6.9.           | Interrupt vector register (IR0VCT/IR1VCT)        | 7-17 |

| 7.6.10.          | 1 0 1                                            |      |

| 7.7. $O_1$       | peration                                         | 7-19 |

| 7.7.1.           | Outline                                          | 7-19 |

| 7.7.2.           | Initialization                                   |      |

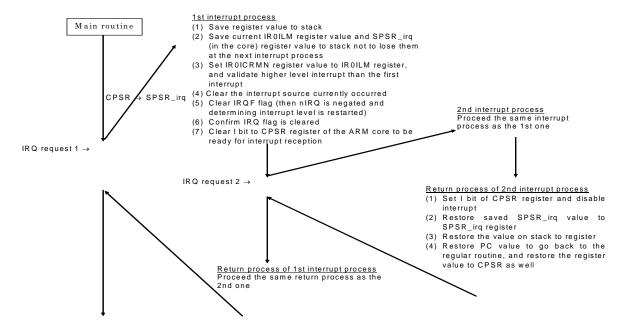

| 7.7.3.           | Multiple interrupt process                       |      |

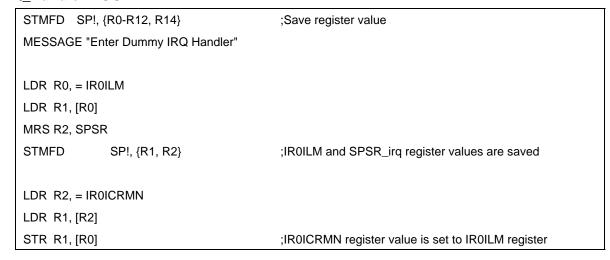

| 7.7.4.           | Example of IRQ interrupt handler                 | 7-20 |

| 7.7.5.           | Resume from Stop and standby modes               |      |

| 7.7.6.           | Notice for using IRC                             | 7-22 |

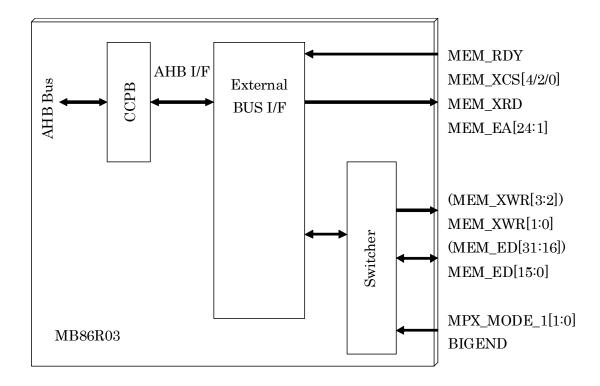

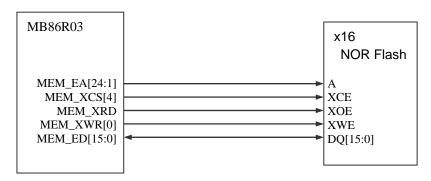

| 8. Exter         | nal bus interface                                | 8-1  |

|                  | utline                                           |      |

|                  | pec limitation                                   |      |

|                  | eature                                           |      |

|                  | ock diagram                                      |      |

|                  | elated pin                                       |      |

|                  | ıpply clock                                      |      |

|                  | egister                                          |      |

| 8.7.1.           | SRAM/Flash mode register 0-7 (MCFMODE0-7)        |      |

| 8.7.2.           | SRAM/Flash timing register 0-7 (MCFTIM0-7)       |      |

| 8.7.3.           | SRAM/Flash area register 0-7 (MCFAREA0-7)        |      |

| 8.7.4.           | Memory controller error register (MCERR)         |      |

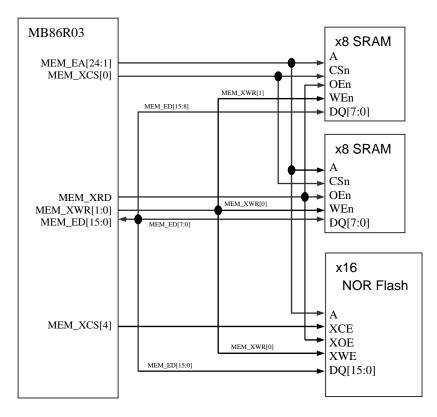

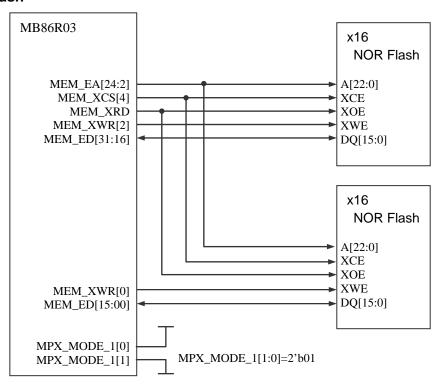

|                  | onnection example                                |      |

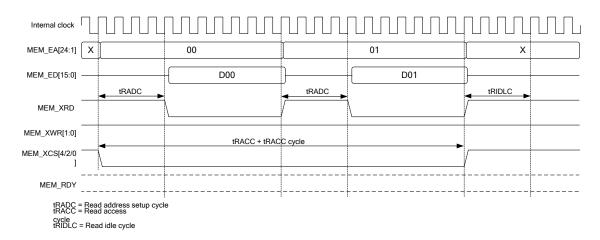

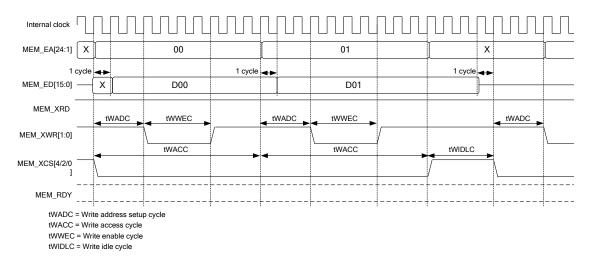

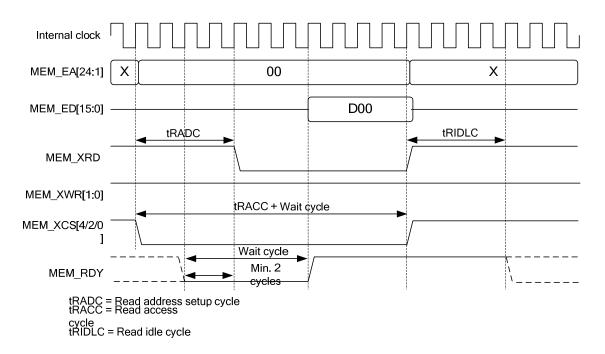

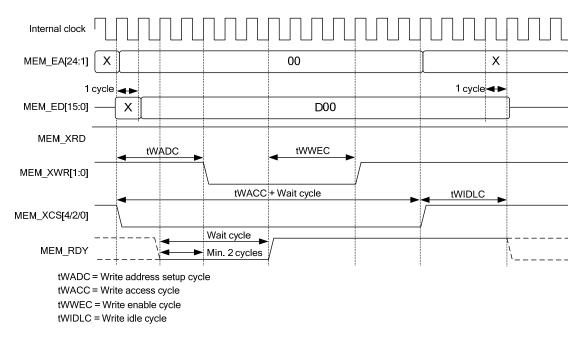

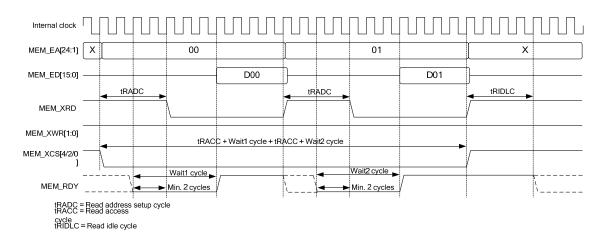

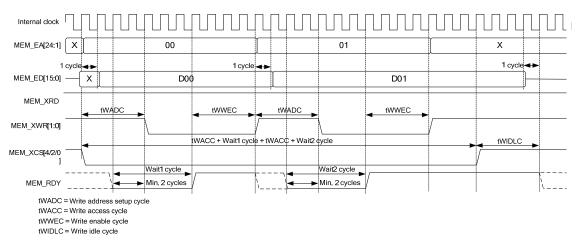

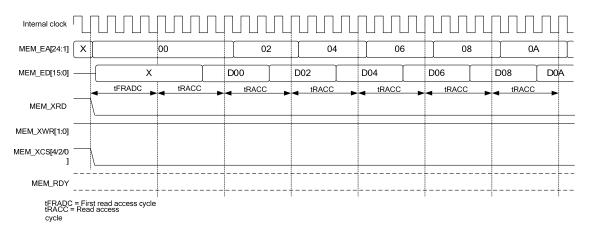

|                  | xample of access waveform                        |      |

|                  | peration                                         |      |

| 8.10.1.          |                                                  |      |

| 8.10.2.          | 1                                                |      |

| 8.10.3.          | Endian and byte lane to each access              | 8-19 |

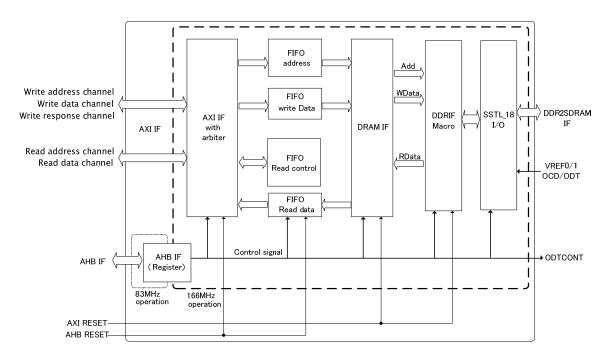

| 9. DDR2          | 2 controller                                     | 9-1  |

|                  | utlineeature                                     |      |

|                  | ock diagram                                      |      |

|                  | ipply clock                                      |      |

|                  | egister                                          |      |

| 9.5.1.           | Register list                                    |      |

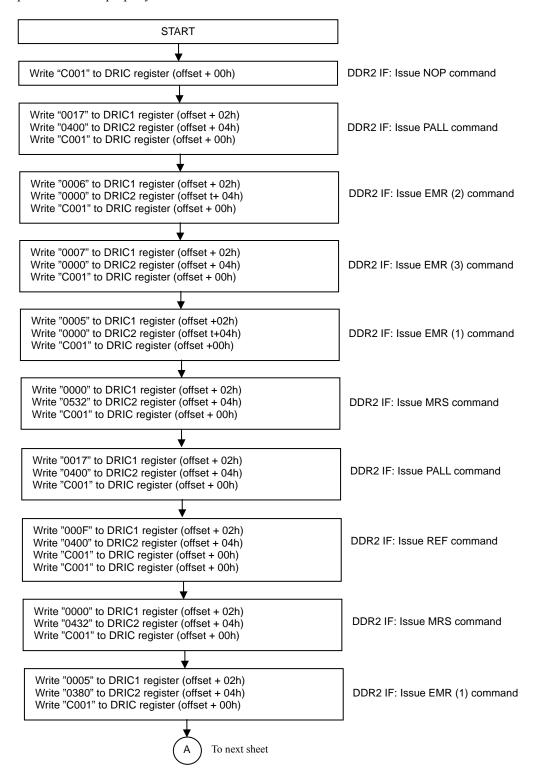

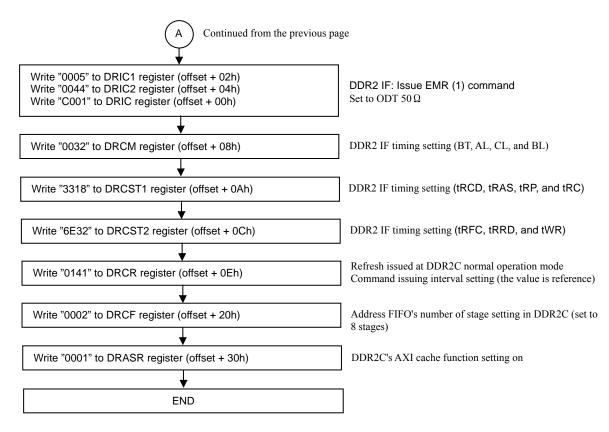

| 9.5.2.           | DRAM initialization control register (DRIC)      |      |

| 9.5.3.           | DRAM initialization command register [1] (DRIC1) |      |

| 9.5.4.           | DRAM initialization command register [1] (DRIC1) |      |

| 9.5.5.           | DRAM CTRL ADD register (DRCA)                    |      |

| 9.5.6.           | DRAM control mode register (DRCM)                |      |

| 9.5.0.<br>9.5.7. | DRAM CTRL SET TIME1 Register (DRCST1)            |      |

| 9.5.8.           | DRAM CTRL SET TIME1 register (DRCST1)            |      |

| 9.5.9.           | DRAM CTRL REFRESH register (DRCR)                |      |

| 9.5.10.          |                                                  |      |

| /                |                                                  | 1    |

| 9.5.12. DRAM IF MACRO SETTING DLL register (DF                                                                                                                                                                                                                                                                                                                             | 9-16                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                            | RIMSD)9-17                                                                                                                                                                                                       |

| 9.5.13. DRAM ODT SETTING register (DROS)                                                                                                                                                                                                                                                                                                                                   | 9-18                                                                                                                                                                                                             |

| 9.5.14. IO buffer setting ODT1 (DRIBSODT1)                                                                                                                                                                                                                                                                                                                                 | 9-19                                                                                                                                                                                                             |

| 9.5.15. IO buffer setting OCD (DRIBSOCD)                                                                                                                                                                                                                                                                                                                                   | 9-20                                                                                                                                                                                                             |

| 9.5.16. IO buffer setting OCD2 (DRIBSOCD2)                                                                                                                                                                                                                                                                                                                                 | 9-21                                                                                                                                                                                                             |

| 9.5.17. ODT auto bias adjust register (DROABA)                                                                                                                                                                                                                                                                                                                             | 9-22                                                                                                                                                                                                             |

| 9.5.18. ODT bias select register (DROBS)                                                                                                                                                                                                                                                                                                                                   | 9-23                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | 9-24                                                                                                                                                                                                             |

| 9.5.20. IO monitor register 2 (DRIMR2)                                                                                                                                                                                                                                                                                                                                     | 9-24                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | 9-25                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | 9-25                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | 9-26                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | 9-26                                                                                                                                                                                                             |

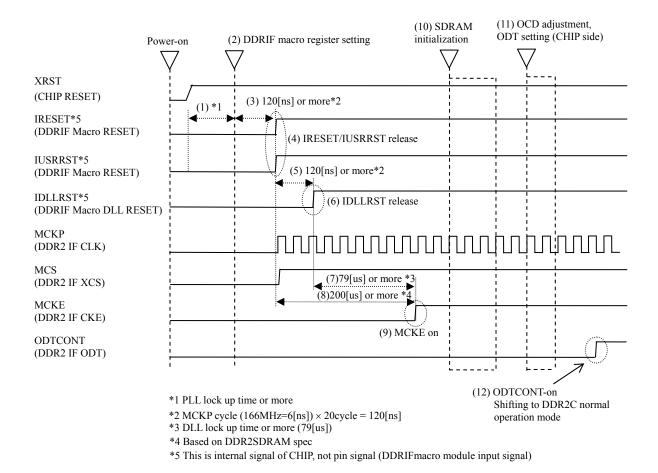

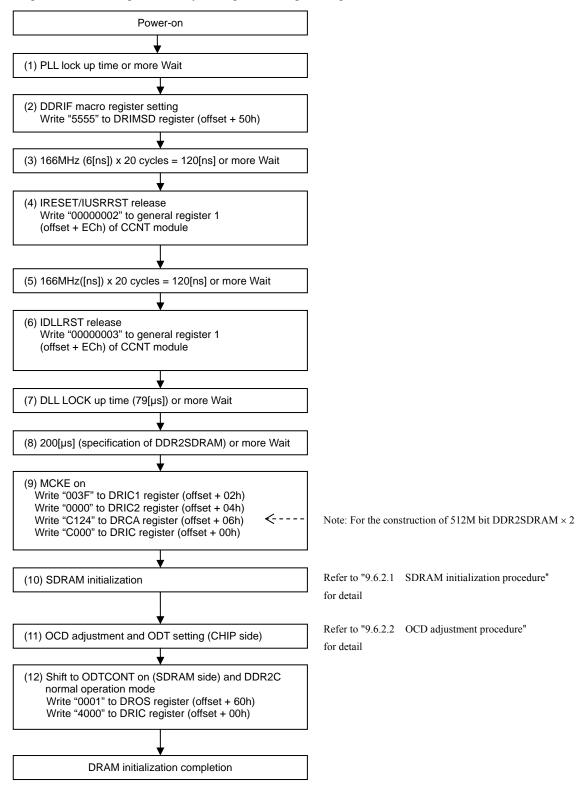

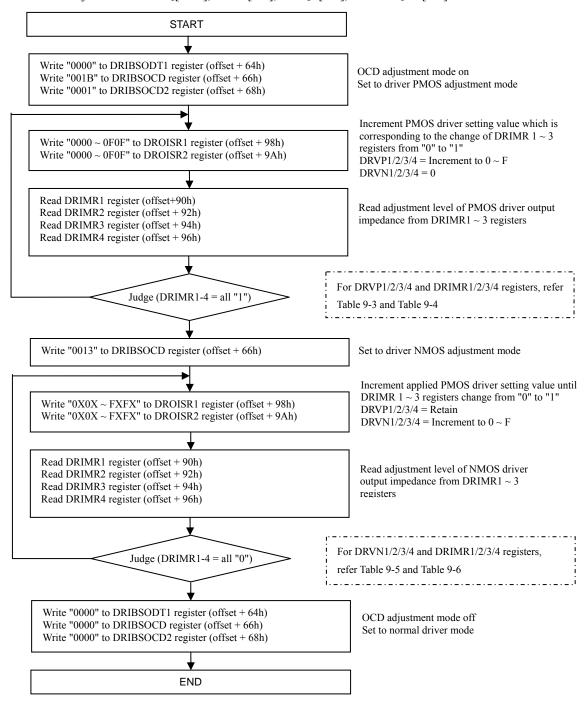

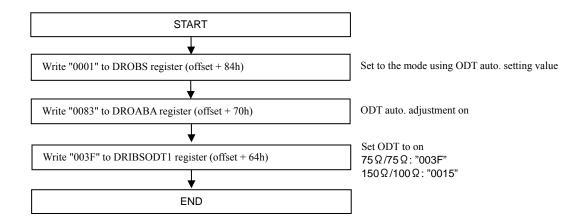

| 9.6. Operation                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                  |

| ÷                                                                                                                                                                                                                                                                                                                                                                          | 9-27                                                                                                                                                                                                             |

| •                                                                                                                                                                                                                                                                                                                                                                          | 9-28                                                                                                                                                                                                             |

| <u> •</u>                                                                                                                                                                                                                                                                                                                                                                  | 9-29                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | 9-31                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | 9-33                                                                                                                                                                                                             |

| 81                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                  |

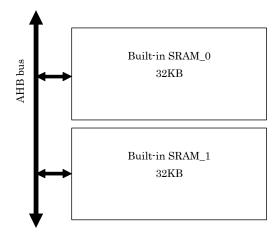

| 10. Built-in SRAM                                                                                                                                                                                                                                                                                                                                                          | 10-1                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                                                |

| 10.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 10-1                                                                                                                                                                                                             |

| 10.2. Feature                                                                                                                                                                                                                                                                                                                                                              | 10-1                                                                                                                                                                                                             |

| 10.3. Block diagram                                                                                                                                                                                                                                                                                                                                                        | 10-1                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                  |

| 10.4. Supply clock                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                  |

| 10.4. Supply clock                                                                                                                                                                                                                                                                                                                                                         | 10-1                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                  |

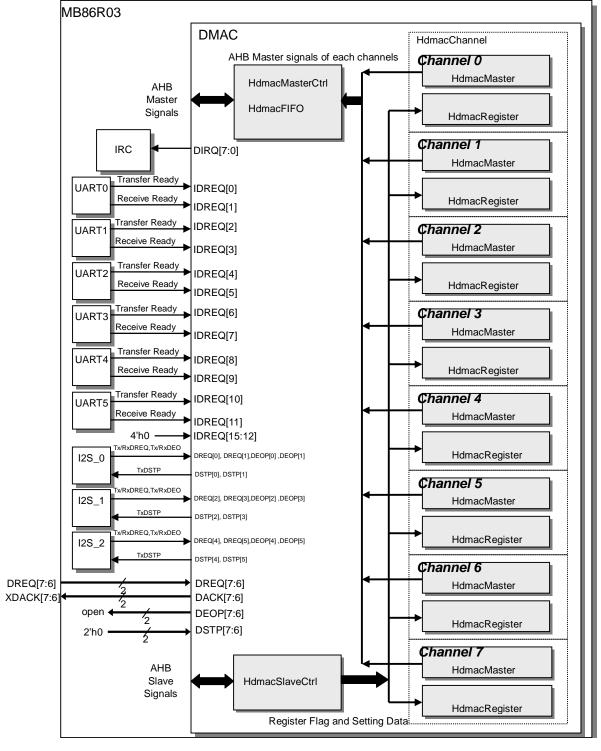

| 11. DMA controller (DMAC)                                                                                                                                                                                                                                                                                                                                                  | 11-1                                                                                                                                                                                                             |

| 11. DMA controller (DMAC)                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                  |

| 11. DMA controller (DMAC)         11.1. Outline         11.2. Feature         11.3. Block diagram                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                  |

| 11. DMA controller (DMAC)         11.1. Outline         11.2. Feature         11.3. Block diagram         11.4. Related pin                                                                                                                                                                                                                                                |                                                                                                                                                                                                                  |

| 11. DMA controller (DMAC)         11.1. Outline         11.2. Feature         11.3. Block diagram         11.4. Related pin         11.5. Supply clock         11.6. Register                                                                                                                                                                                              |                                                                                                                                                                                                                  |

| 11. DMA controller (DMAC)         11.1. Outline         11.2. Feature         11.3. Block diagram         11.4. Related pin         11.5. Supply clock         11.6. Register         11.6.1. Register list                                                                                                                                                                |                                                                                                                                                                                                                  |

| 11. DMA controller (DMAC)         11.1. Outline         11.2. Feature         11.3. Block diagram         11.4. Related pin         11.5. Supply clock         11.6. Register         11.6.1. Register list         11.6.2. DMA configuration register (DMACR)                                                                                                             |                                                                                                                                                                                                                  |

| 11. DMA controller (DMAC)         11.1. Outline         11.2. Feature         11.3. Block diagram         11.4. Related pin         11.5. Supply clock         11.6. Register         11.6.1. Register list         11.6.2. DMA configuration register (DMACR)         11.6.3. DMA configuration A register (DMACAx)                                                       |                                                                                                                                                                                                                  |

| 11. DMA controller (DMAC)         11.1. Outline         11.2. Feature         11.3. Block diagram         11.4. Related pin         11.5. Supply clock         11.6. Register         11.6.1. Register list         11.6.2. DMA configuration register (DMACR)         11.6.3. DMA configuration A register (DMACAx)         11.6.4. DMA configuration B register (DMACBx) |                                                                                                                                                                                                                  |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1  11-1  11-1  11-2  11-3  11-4  11-6  11-8  11-11                                                                                                                                                            |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-4         11-8         11-11         11-14         11-15                                                                                     |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-4         11-8         11-11         11-14         11-15                                                                                     |

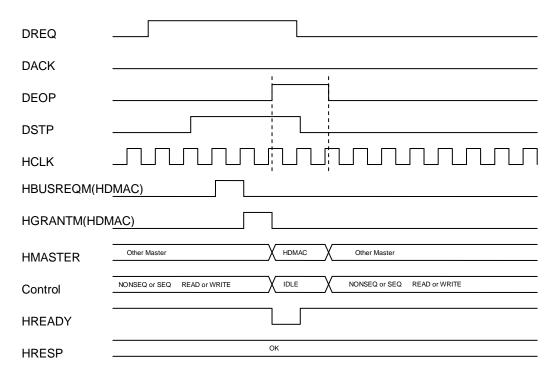

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-3         11-4         11-6         11-18         11-11         11-15         11-16                                                                       |

| 11. DMA controller (DMAC)                                                                                                                                                                                                                                                                                                                                                  | 11-1         11-1         11-2         11-3         11-3         11-4         11-6         11-11         11-14         11-15         11-16         11-16                                                         |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-4         11-6         11-18         11-14         11-15         11-16         11-16         11-16                                           |

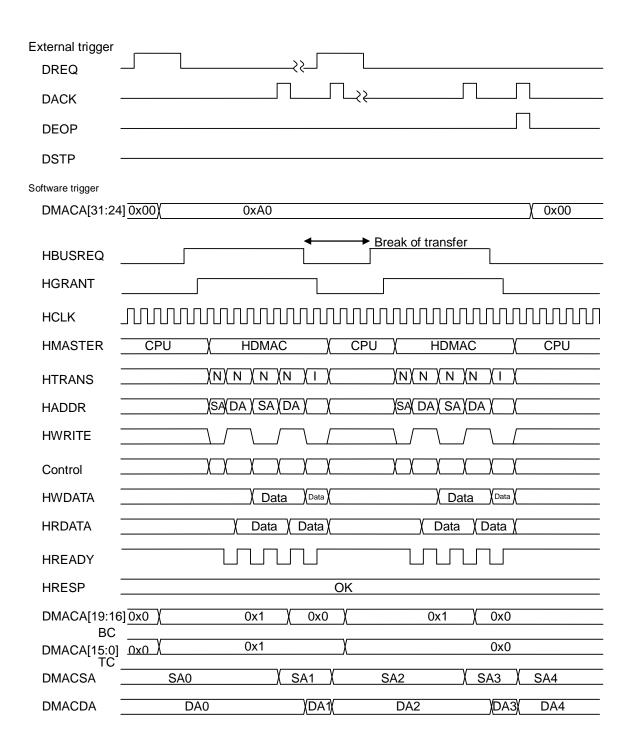

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-6         11-11         11-15         11-16         11-16         11-16         11-20         11-24                                          |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-6         11-11         11-15         11-16         11-16         11-16         11-20         11-24                                          |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-4         11-8         11-11         11-15         11-16         11-16         11-16         11-24         11-24         11-28               |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-4         11-6         11-11         11-15         11-16         11-16         11-16         11-20         11-24         11-28         11-29 |

| 11.1. Outline                                                                                                                                                                                                                                                                                                                                                              | 11-1         11-1         11-2         11-3         11-4         11-4         11-6         11-11         11-15         11-16         11-16         11-16         11-20         11-24         11-28         11-29 |

| 11.7.3.2. Rotate priority                                   | 11-31 |

|-------------------------------------------------------------|-------|

| 11.7.4. Retry, split, and error                             | 11-32 |

| 11.7.4.1. Retry and split                                   | 11-32 |

| 11.7.4.2. Error                                             | 11-33 |

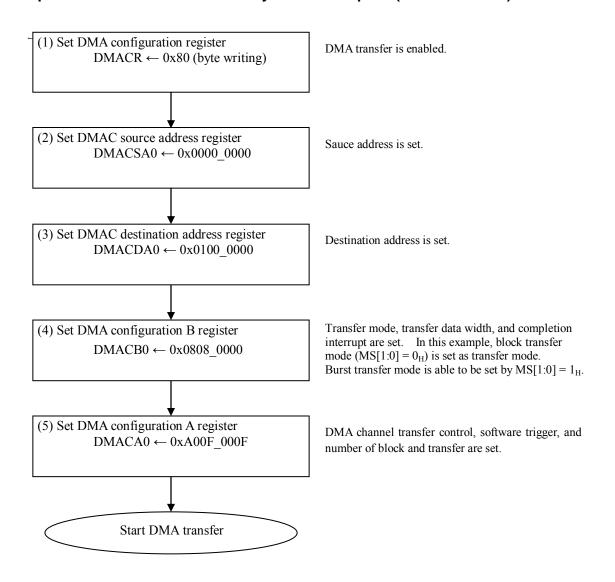

| 11.8. Example of DMAC setting                               | 11-34 |

| 11.8.1. DMA start in Single channel                         | 11-34 |

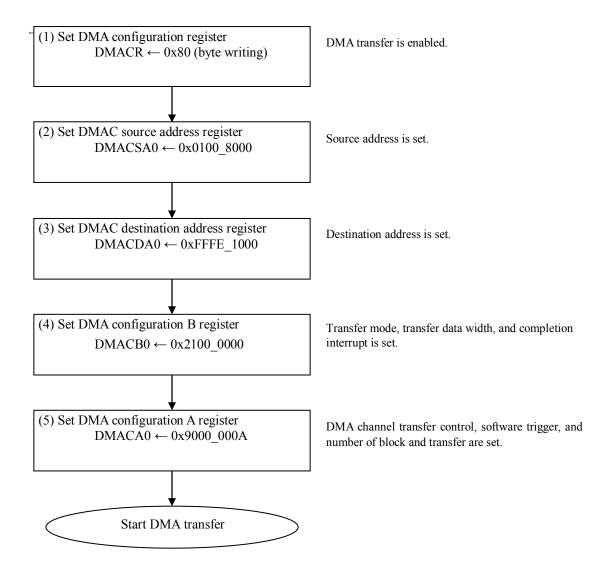

| 11.8.2. DMA start in all channels (in demand transfer mode) |       |

|                                                             |       |

| 12. Timer (TIMER)                                           | 12-1  |

| 12.1. Outline                                               | 12-1  |

| 12.2. Feature                                               | 12-1  |

| 12.3. Supply clock                                          | 12-1  |

| 12.4. Specification                                         | 12-1  |

|                                                             |       |

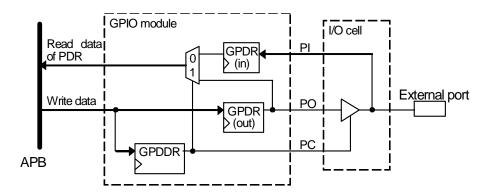

| 13. General-purpose input/output port (GPIO)                | 13-1  |

| 13.1. Outline                                               | 13-1  |

| 13.2. Feature                                               | 13-1  |

| 13.3. Block diagram                                         |       |

| 13.4. Supply clock                                          |       |

| 13.5. Register                                              | 13-2  |

| 13.5.1. Register list                                       |       |

| 13.5.2. Port data register 0-2 (GPDR0-2)                    |       |

| 13.5.3. Data direction register 0-2 (GPDDR2-0)              |       |

| 13.6. Operation                                             |       |

| 13.6.1. Direction control                                   |       |

| 13.6.2. Data transfer                                       |       |

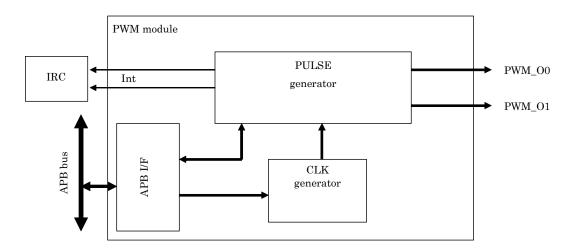

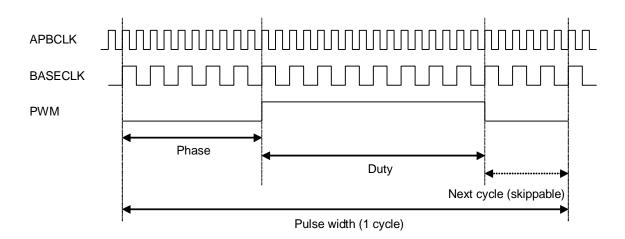

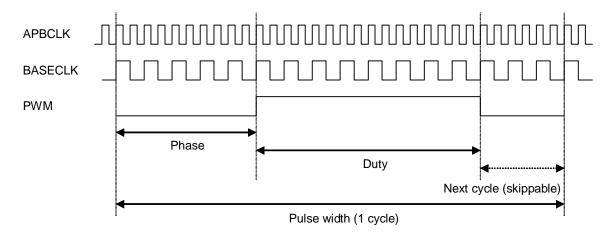

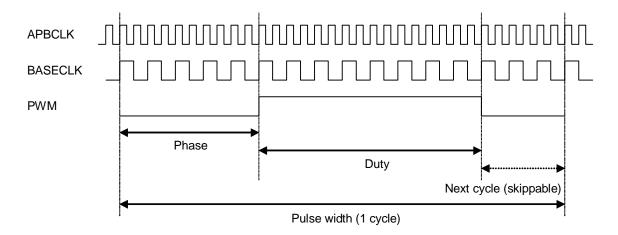

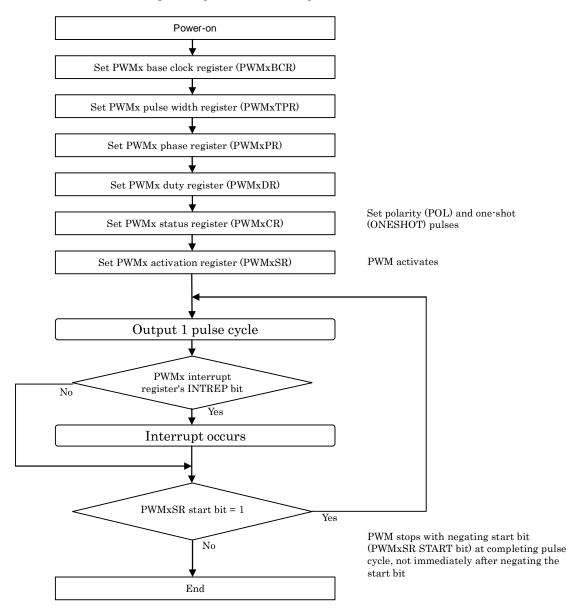

| 14. PWM                                                     | 14-1  |

| 17.1                                                        |       |

| 14.1. Outline                                               |       |

| 14.2. Feature                                               | 14-1  |

| 14.3. Block diagram                                         |       |

| 14.4. Related pin                                           |       |

| 14.5. Supply clock                                          |       |

| 14.6. Interrupt                                             |       |

| 14.7. Register                                              |       |

| 14.7.1. Register list                                       |       |

| 14.7.2. PWMx base clock register (PWMxBCR)                  |       |

| 14.7.3. PWMx pulse width register (PWMxTPR)                 |       |

| 14.7.4. PWMx phase register (PWMxPR)                        |       |

| 14.7.5. PWMx duty register (PWMxDR)                         |       |

| 14.7.6. PWMx status register (PWMxCR)                       |       |

| 14.7.7. PWMx start register (PWMxSR)                        |       |

| 14.7.8. PWMx current count register (PWMxCCR)               |       |

| 14.7.9. PWMx interrupt register (PWMxIR)                    |       |

| 14.8. Example of setting register                           | 14-13 |

| 15. A/D converter                                           | 15-1  |

|                                                             |       |

| 15.1 Outline                                                | 15 1  |

| 15.2. Feature                                      | 15-1  |

|----------------------------------------------------|-------|

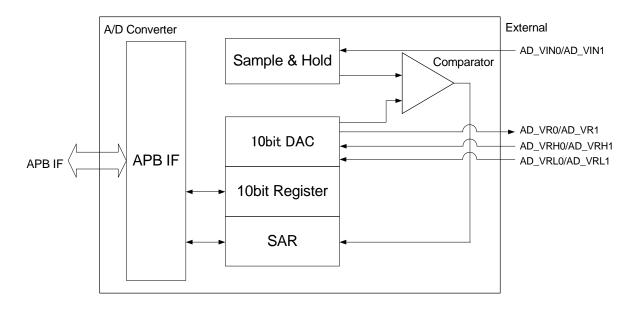

| 15.3. Block diagram                                | 15-2  |

| 15.4. Related pin                                  | 15-2  |

| 15.5. Supply clock                                 | 15-2  |

| 15.6. Output truth value list                      | 15-3  |

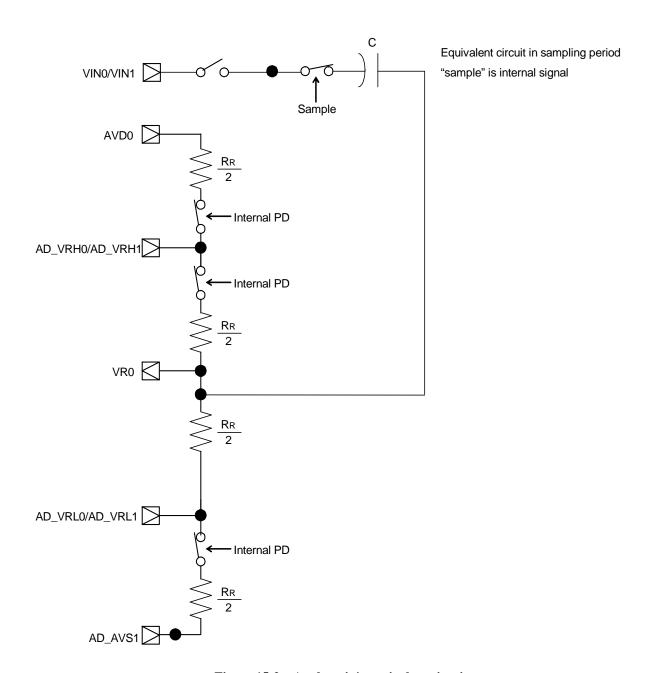

| 15.7. Analog pin equivalent circuit                |       |

| 15.8. Register                                     | 15-5  |

| 15.8.1. Register list                              | 15-5  |

| 15.8.2. ADCx data register (ADCxDATA)              | 15-7  |

| 15.8.3. ADCx power down control register (ADCxXPD) | 15-7  |

| 15.8.4. ADCx clock selection register (ADCxCKSEL)  | 15-8  |

| 15.8.5. ADCx status register (ADCxSTATUS)          | 15-9  |

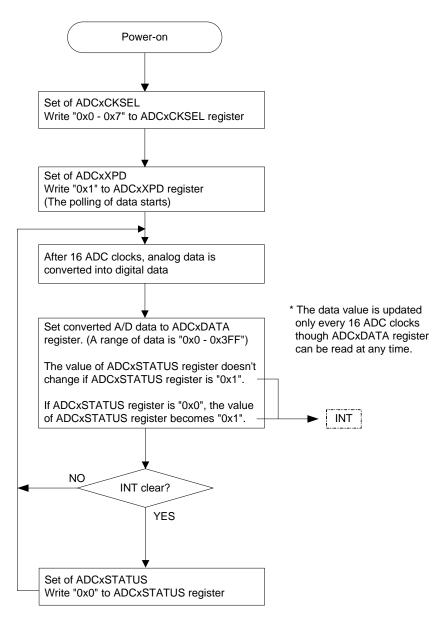

| 15.9. Basic operation flow                         |       |

| 16. Graphics display controller (GDC)              |       |

| 17.1. Outline                                      | 17-1  |

| 17.2. Feature                                      | 17-1  |

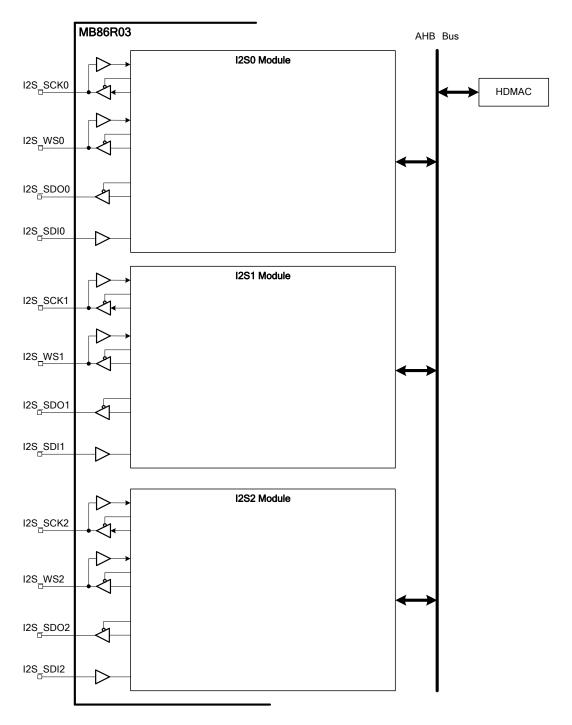

| 17.3. Block diagram                                | 17-2  |

| 17.4. Related pin                                  | 17-3  |

| 17.5. Supply clock                                 | 17-3  |

| 17.6. Register                                     | 17-4  |

| 17.6.1. Register list                              | 17-4  |

| 17.6.2. I2SxRXFDAT register                        | 17-6  |

| 17.6.3. I2SxTXFDAT register                        | 17-7  |

| 17.6.4. I2SxCNTREG register                        | 17-8  |

| 17.6.5. I2SxMCR0REG register                       | 17-11 |

| 17.6.6. I2SxMCR1REG register                       | 17-12 |

| 17.6.7. I2SxMCR2REG register                       | 17-13 |

| 17.6.8. I2SxOPRREG register                        | 17-14 |

| 17.6.9. I2SxSRST register                          |       |

| 17.6.10. I2SxINTCNT register                       | 17-16 |

| 17.6.11. I2SxSTATUS register                       | 17-19 |

| 17.6.12. I2SxDMAACT register                       |       |

| 17.7. Operation                                    | 17-22 |

| 17.7.1. Outline                                    | 17-22 |

| 17.7.2. Transfer start, stop, and malfunction      |       |

| 17.7.3. Frame construction                         | 17-28 |

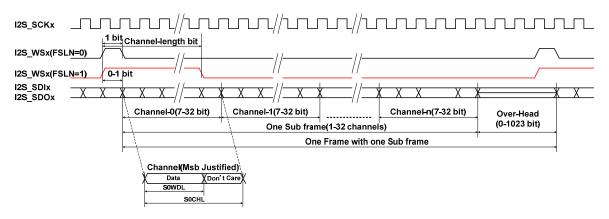

| 17.7.3.1. 1 sub frame construction                 | 17-28 |

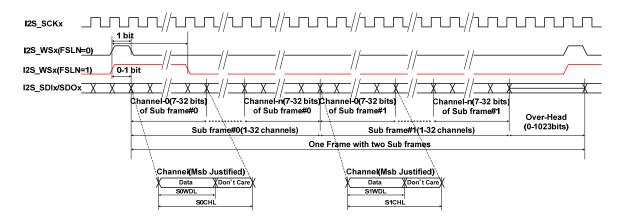

| 17.7.3.2. 2 sub frame construction                 | 17-29 |

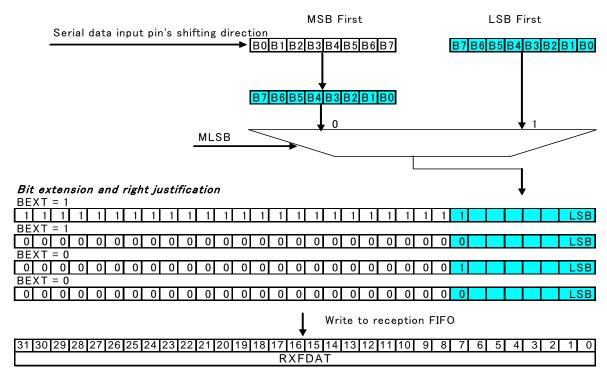

| 17.7.3.3. Bit alignment                            | 17-30 |

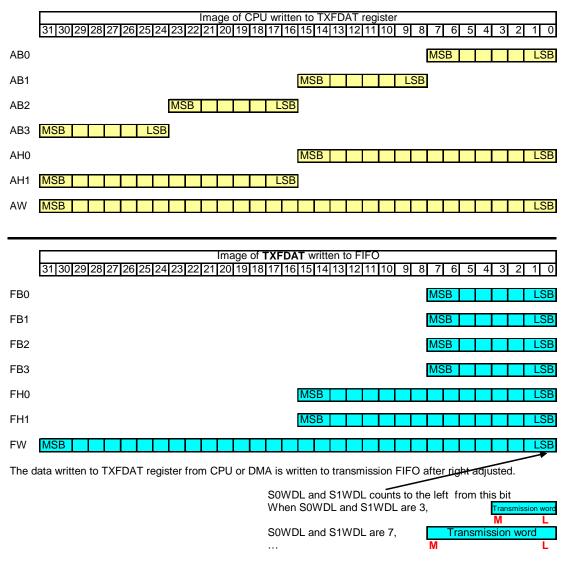

| 17.7.4. FIFO construction and description          |       |

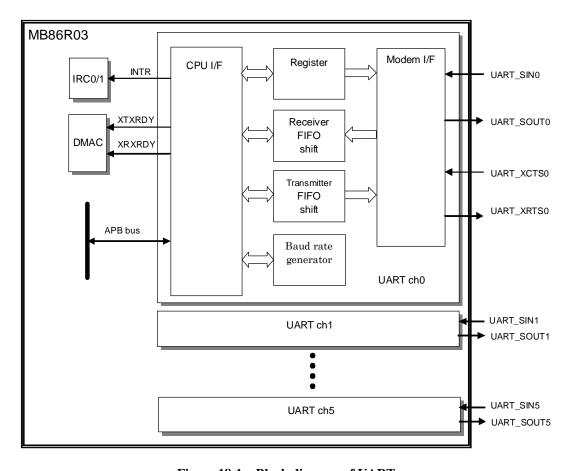

| 18. UART interface                                 | 18-1  |

| 18.1. Outline                                      |       |

| 18.2. Feature                                      |       |

| 18.3. Block diagram                                |       |

| 18.4. Related pin                                  | 18-2  |

| 18.5. Sup              | pply clock                                                    | 18-2  |

|------------------------|---------------------------------------------------------------|-------|

| 18.6. Reg              | gister                                                        | 18-3  |

| 18.6.1.                | Register list                                                 |       |

| 18.6.2.                | Reception FIFO register (URTxRFR)                             | 18-6  |

| 18.6.3.                | Transmission FIFO register (URTxTFR)                          | 18-6  |

| 18.6.4.                | Interrupt enable register (URTxIER)                           | 18-7  |

| 18.6.5.                | Interrupt ID register (URTxIIR)                               | 18-8  |

| 18.6.6.                | FIFO control register (URTxFCR)                               |       |

| 18.6.7.                | Line control register (URTxLCR)                               |       |

| 18.6.8.                | Modem control register (URTxMCR)                              |       |

| 18.6.9.                | Line status register (URTxLSR)                                |       |

| 18.6.10.               | Modem status register (URTxMSR)                               |       |

|                        | Divider latch register (URTxDLL&URTxDLM)                      |       |

|                        | RT operation                                                  |       |

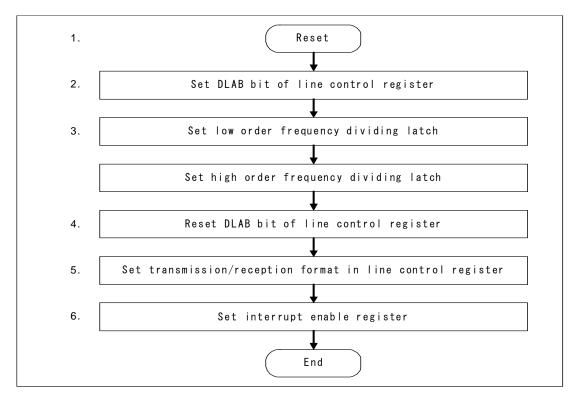

| 18.7.1.                | Example of initial setting                                    |       |

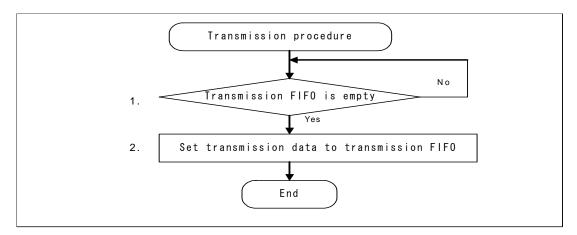

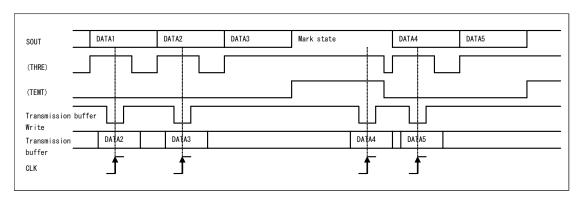

| 18.7.2.                | Example of transfer procedure                                 |       |

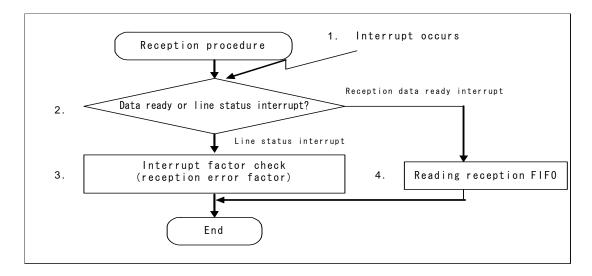

| 18.7.3.                | Example of reception procedure                                |       |

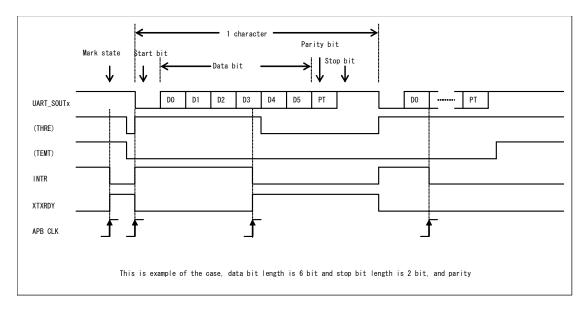

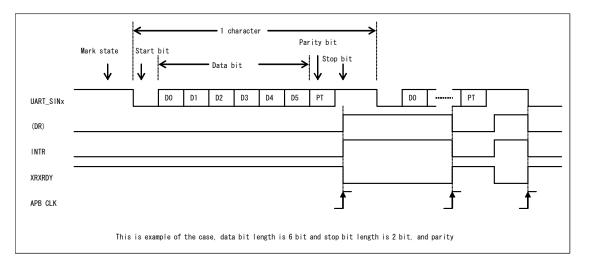

| 18.7.4.                | Basic transmission operation.                                 |       |

| 18.7.5.                | Basic reception operation                                     |       |

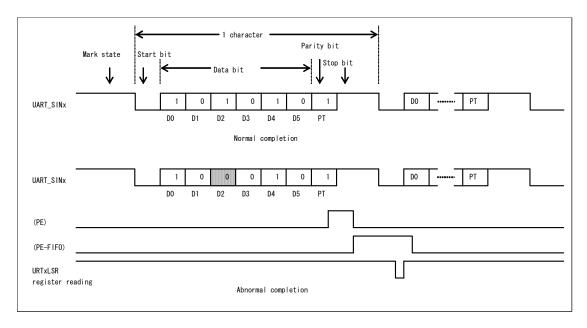

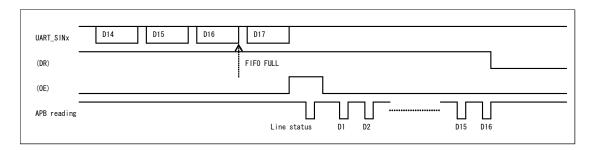

| 18.7.6.                | Line status                                                   |       |

| 18.7.7.                | Character time-out interrupt                                  |       |

| 10.7.7.                | Character time out interrupt                                  | 10 23 |

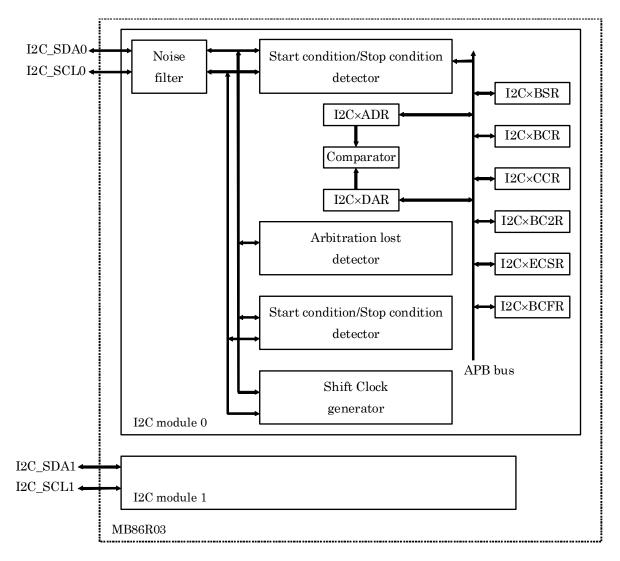

| 19 I <sup>2</sup> C hu | s interface                                                   | 19-1  |

| 10.1 0 84              |                                                               |       |

| 19.1. Out              | tline                                                         | 19-1  |

|                        | uture                                                         |       |

|                        | ock diagram                                                   |       |

|                        | ated pin                                                      |       |

|                        | pply clock                                                    |       |

| _                      | gister                                                        |       |

| 19.6.1.                | Register list                                                 |       |

| 19.6.2.                | Bus status register (I2CxBSR)                                 |       |

| 19.6.3.                | Bus control register (I2CxBCR)                                |       |

| 19.6.4.                | Clock control register (I2CxCCR)                              |       |

| 19.6.5.                | Address register (I2CxADR)                                    |       |

| 19.6.6.                | Data register (I2CxDAR)                                       |       |

| 19.6.7.                | Two bus control registers (I2CxBC2R)                          |       |

| 19.6.8.                | Expansion CS register (I2CxECSR)                              |       |

| 19.6.9.                | Bus clock frequency register (I2CxBCFR)                       |       |

|                        | eration                                                       |       |

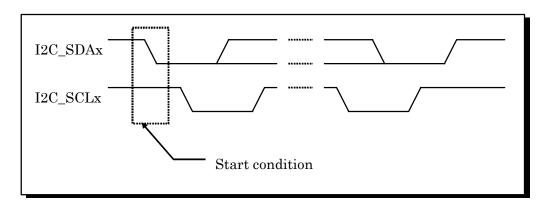

| 19.7.1.                | Start condition                                               |       |

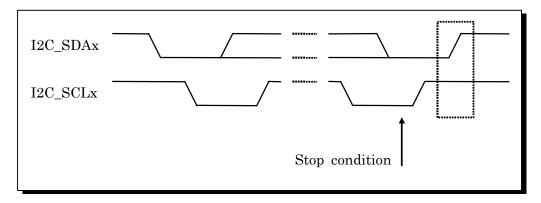

| 19.7.1.                | Stop condition                                                |       |

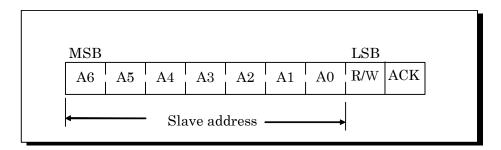

| 19.7.2.                | Addressing                                                    |       |

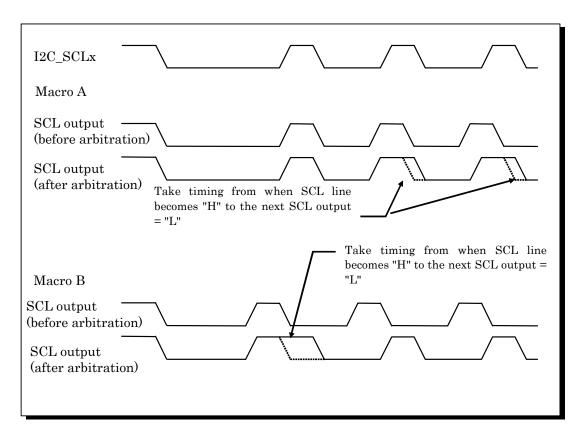

| 19.7.3.                | Synchronous arbitration of SCL                                |       |

|                        | •                                                             |       |

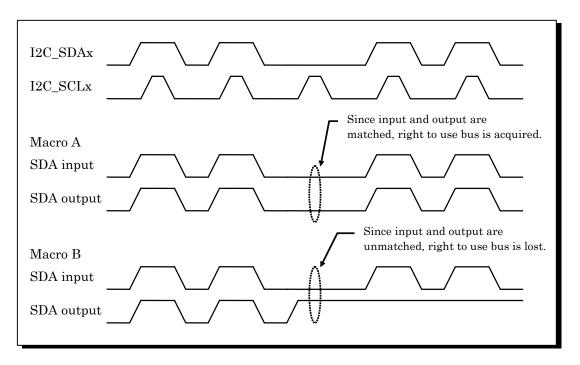

| 19.7.5.                | Arbitration                                                   |       |

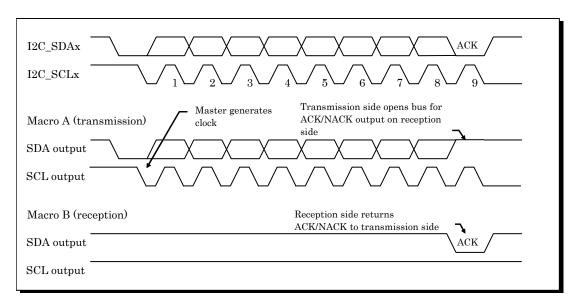

| 19.7.6.                | Acknowledge/Negative acknowledge                              |       |

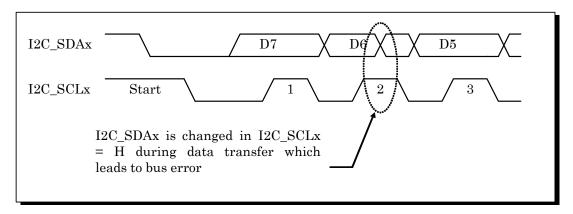

| 19.7.7.                | Bus error                                                     |       |

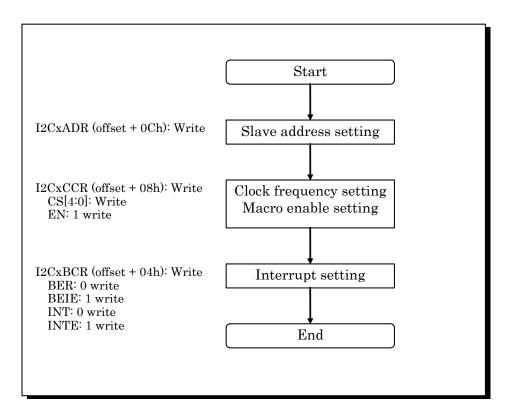

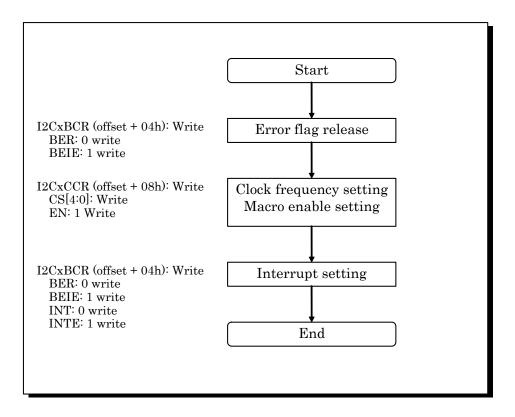

| 19.7.8.                | Initialization                                                |       |

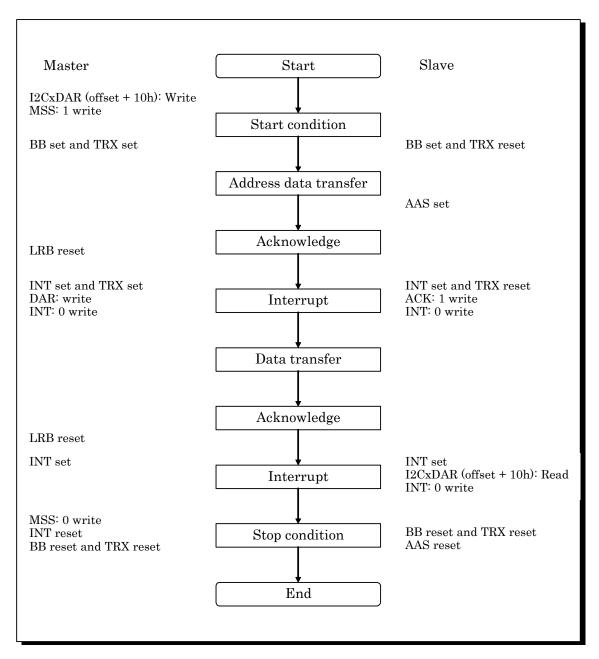

| 19.7.9.                | One byte transfer from master to slave                        |       |

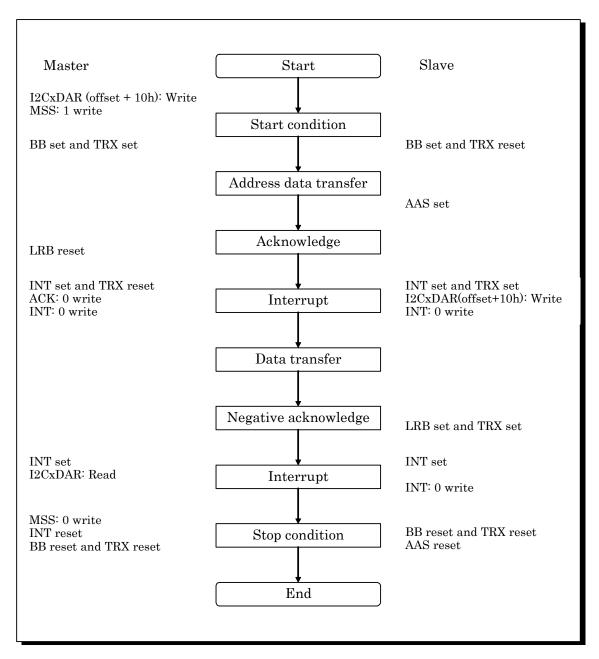

| 19.7.10.               | •                                                             |       |

|                        | Recover from bus error                                        |       |

| 19.7.12.               | Interrupt process and wait request operation to master device | 19-32 |

| 19.8.  | Notice                                                    | 19-32 |

|--------|-----------------------------------------------------------|-------|

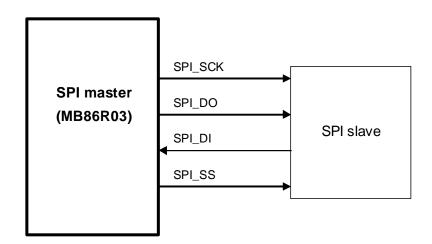

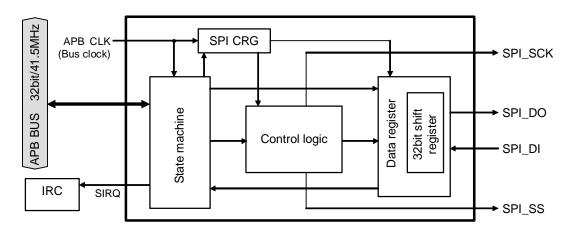

| 20. Se | erial peripheral interface (SPI)                          | 20-1  |

| 20.1.  | Outline                                                   | 20-1  |

| 20.2.  |                                                           |       |

| 20.3.  | Block diagram                                             | 20-2  |

| 20.4.  |                                                           |       |

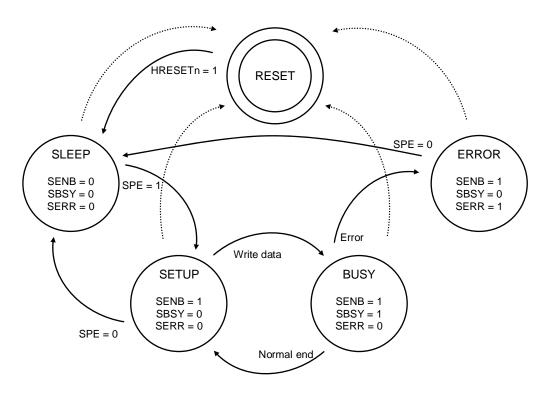

| 20.5.  | Transition state                                          | 20-3  |

| 20.6.  | Register                                                  | 20-4  |

| 20.    | .6.1. Register list                                       |       |

| 20.    | .6.2. SPI control register (SPICR)                        |       |

| 20.    | .6.3. SPI slave control register (SPISCR)                 |       |

| 20.    | .6.4. SPI data register (SPIDR)                           |       |

| 20.    | .6.5. SPI status register (SPISR)                         |       |

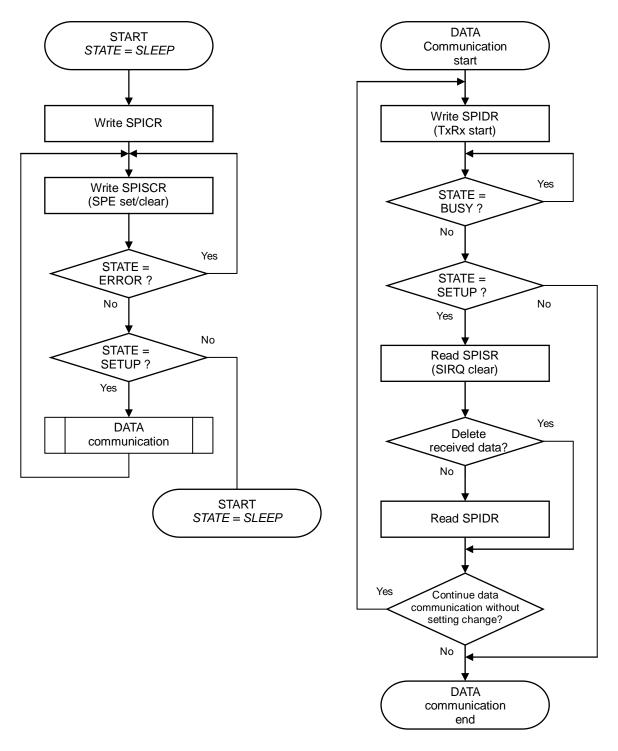

| 20.7.  | Setup procedure flow                                      |       |

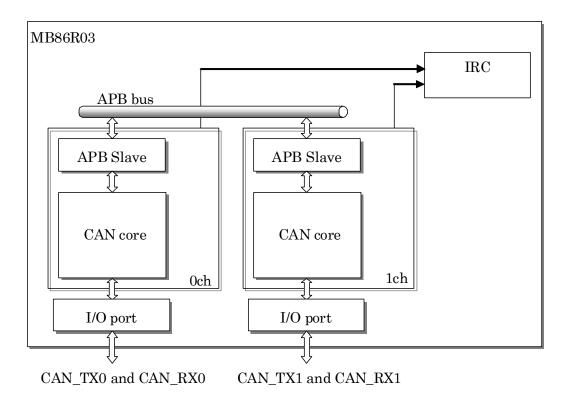

| 21. C  | AN interface (CAN)                                        | 21-1  |

| 21.1.  | Outline                                                   | 21-1  |

| 21.2.  |                                                           |       |

| 21.3.  | •                                                         |       |

| 21.4.  |                                                           |       |

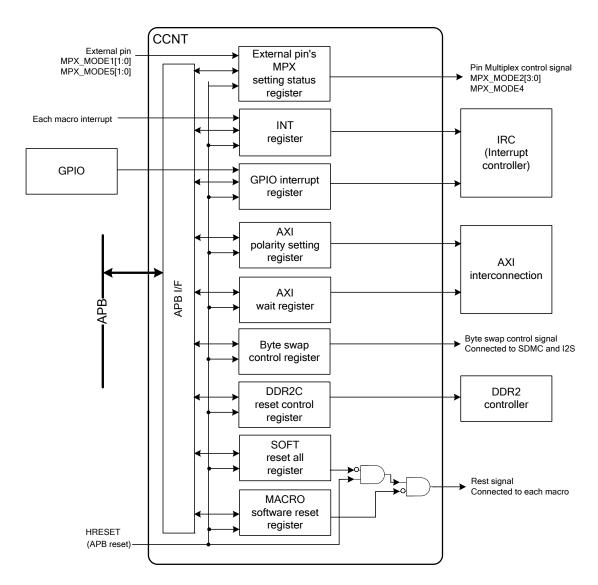

| 22. Cł | hip Control Module (CCNT)                                 | 22-1  |

| 22.1.  | Outline                                                   | 22-1  |

| 22.2.  |                                                           |       |

| 22.3.  |                                                           |       |

| 22.4.  | •                                                         |       |

| 22.5.  |                                                           |       |

| 22.    | .5.1. Register list                                       |       |

| 22.    | .5.2. CHIP ID register (CCID)                             |       |

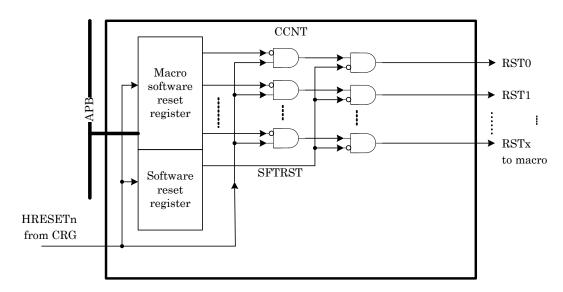

| 22.    | .5.3. Software reset register (CSRST)                     |       |

|        | .5.4. Interrupt status register (CIST)                    |       |

| 22.    | .5.5. Interrupt status mask register (CISTM)              |       |

| 22.    | .5.6. GPIO interrupt status register (CGPIO_IST)          |       |

| 22.    | .5.7. GPIO interrupt status mask register (CGPIO_ISTM)    |       |

| 22.    | .5.8. GPIO interrupt polarity setting register (CGPIO_IP) |       |

| 22.    | .5.9. GPIO interrupt mode setting register (CGPIO_IM)     |       |

| 22.    | .5.10. AXI bus wait cycle setting register (CAXI_BW)      |       |

|        | .5.11. AXI polarity setting register (CAXI_PS)            |       |

|        | .5.12. Multiplex mode setting register (CMUX_MD)          |       |

|        | .5.13. External pin status register (CEX_PIN_ST)          |       |

|        | .5.14. Byte swap switching register (CBSC)                |       |

|        | .5.15. DDR2 controller reset control register (CDCRC)     |       |

|        | .5.16. Software reset register 0 for macro (CMSR0)        |       |

|        | .5.17. Software reset register 1 for macro (CMSR1)        |       |

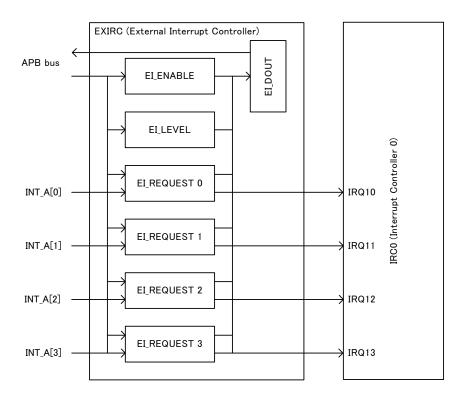

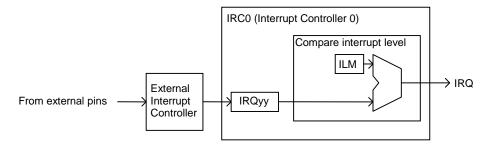

| 23. Ex | xternal interrupt controller (EXIRC)                      | 23-1  |

| 23.1   | Outline                                                   | 23-1  |

| 24. SD ı | memory controller (SDMC)                       | 24-1 |

|----------|------------------------------------------------|------|

| 23.8. I  | Instruction for use                            | 23-8 |

|          | Operation procedure                            |      |

| 23.6.    | Operation                                      | 23-8 |

| 23.5.4   | 4. External interrupt level register (EILVL)   | 23-7 |

| 23.5.3   | 3. External interrupt request register (EIREQ) | 23-6 |

| 23.5.2   | 2. External interrupt enable register (EIENB)  | 23-5 |

| 23.5.1   | 1. Register list                               | 23-3 |

| 23.5. I  | Register                                       | 23-3 |

| 23.4.    | Supply clock                                   | 23-2 |

| 23.3. I  | Block diagram                                  | 23-2 |

| 23.2. I  | Feature                                        | 23-1 |

## 1. Outline

This chapter describes feature, block diagram, and function of MB86R03.

## 1.1. Feature

MB86R03 is LSI product for the graphics applications with ARM Limited's CPU ARM926EJ-S and Fujitsu's GDC MB86296 as its core. This product contains peripheral I/O resources, such as in-vehicle LAN; therefore only a single chip of MB86R03 controls main graphics application system which usually requires 2 chips (CPU and GDC.)

#### MB86R03 has following features:

- CMOS 90nm technology

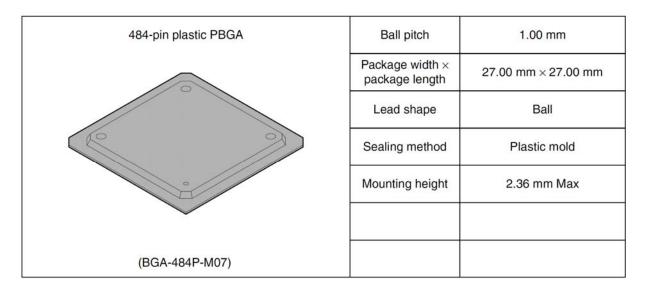

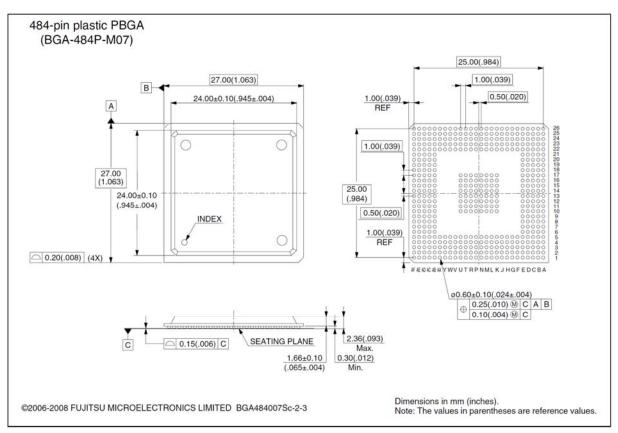

- Package: PBGA484

- Power-supply voltage: (IO:  $3.3 \pm 0.3$ V, core:  $1.2 \pm 0.1$ V, DDR2:  $1.8 \pm 0.1$ V)

- Operation frequency: 333MHz (CPU), 83MHz (AHB), 41.5MHz (APB)

- CPU core

- ARM926EJ-S

- 16KB instruction cache/16KB data cache

- 16KB ITCM/16KB DTCM

- ETM9CS Single and JTAG ICE interface

- Java acceleration (Jazelle technology)

- Bus architecture

- Multi-layer AHB bus architecture

- Interrupt

- Built-in SRAM

- Clock/Reset control function

- Remap/Boot control function

- 16 bit external bus interface with decoding engine

- 32 bit DDR2 memory interface (target: 166MHz: 333Mbps)

- Graphics display controller

- 2D/3D rendering engine of Fujitsu MB86296

- RGB66 video output × 1ch (extensible to RGB888 with using option I/O)

- ITU RBT-656 video capture × 1ch (extensible to RGB666 with using option I/O)

- SD memory controller (SDIO/CPRM: unsupported) × 1ch

- 10 bit A/D converter (1MS/s) × 2ch

- $I^2C$  (I/O voltage: 3.3V) × 2ch

- UART × 3ch (extensible up to 6ch with using option I/O)

- 32/16 bit timer  $\times$  2ch

- DMAC × 8ch

## **Option I/O (with pin multiplex)**

- RGB666 video output is extensible to 2ch

- Video capture is extensible to 2ch

- CAN (I/O voltage: 3.3V) × 2ch is addable

- GPIO is addable up to 24

- SPI × 1ch is addable

- PWM × 2ch is addable

- I2S is addable up to 3ch

- The number of UART channel is extensible up to 6ch

- The data width in the external bus interface is extensible to 32 bit

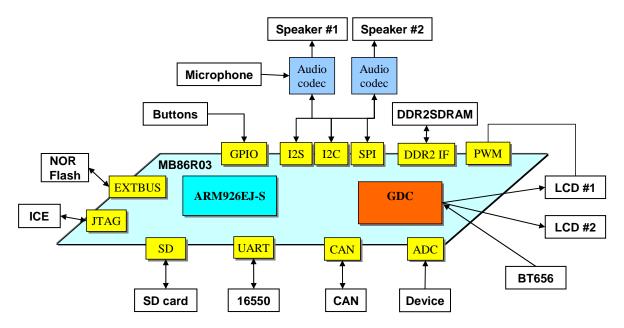

## 1.2. Block diagram

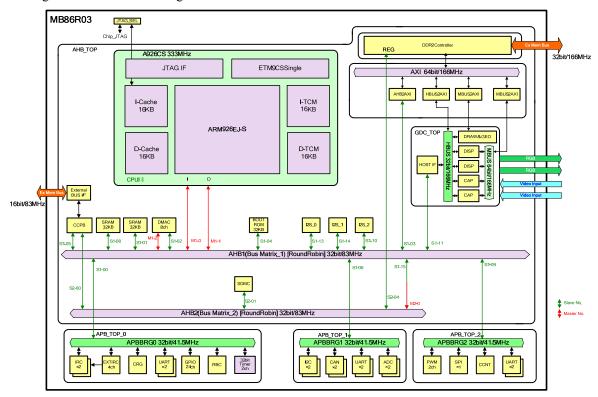

Figure 1-1 shows block diagram of MB86R03.

Figure 1-1 Block diagram of MB86R03

#### **CPU** core

CPU core block of ARM926EJ-S is connected to each I/O through AHB bus in LSI. Instruction (I)/Data (D) function as a separate bus master for Harvard architecture.

### GDC\_TOP

MB86296 compatible GDC has 2 functions: AHB slave function which writes required display list for drawing to GDC with having CPU or DMA controller as master, and AXI master function which reads display list arranged in DDR2 memory with having GDC as master.

#### **AXI** bus

This bus bridges main memory and internal resource. Following 4 bus masters are connected.

- AHB1: Each bus master of AHB bus such as CPU and DMA controller

- HBUS: HOST IF on GDC

- DRAW & GEO: Draw (2D/3D drawing) and GEO (geometry engine) on GDC

- MBUS: DISP (display controller) and CAP (video capture) on GDC

#### AHB1 bus

Following resources are connected.

- CPU core: Bus masters of instruction (I)/data (D)

- GDC: GDC register part

- AHB2AXI: AXI port for main memory access

- CCPB: Encrypted ROM decoding block

- External BUS I/F: External bus interface (connected through CCPB)

- SRAM: General purpose internal SRAM 32KB × 2

- DMAC: General purpose DMA × 8ch It operates as bus master at data transfer

- Boot ROM: Built-in boot ROM

- I2S 0/1/2: Serial audio controller × 3ch

- AHB2

- APBBRG0/1/2: AHB-APB bridge circuit × 3ch

#### AHB2 bus

- CCPB: Encrypted ROM decoding block

- SDMC: SD memory controller

- DDR2 controller: DDR2 controller's register part

#### APB TOP 0

This block bridges between APBBRG0 bus and the AHB1 bus, and following low-speed peripheral resources are connected.

- Interrupt controller (IRC) × 2ch

- External interrupt controller (EXTIRC)

- Clock reset generator (CRG)

- UART (ch0 and ch1) × 2ch

- Remap boot controller (RBC)

- 32 bit general-purpose timer (32 bit timer) × 2ch

### APB TOP 1

This block bridges between APBBRG1 bus and AHB1 bus, and following low-speed peripheral resources are connected.

- $I^2C$  controller × 2ch

- CAN controller × 2ch

- UART (ch2 and ch3) × 2ch

- A/D converter (ADC) × 2ch

### APB\_TOP\_2

This block bridges between APBBRG2 bus and AHB1 bus, and following low-speed peripheral resources are connected.

- PWM controller (PWM)

- SPI controller (SPI)

- Chip control module (CCNT)

- UART (ch4 and ch5) × 2ch

# 1.3. Function list

Function list of MB86R03 is shown below.

Table 1-1 MB86R03 function list

| Function               | Outline                                                                                                                                                                |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU core               |                                                                                                                                                                        |

| CPO core               | ARM926EJ-S <sup>TM</sup> processor core     Grand and the formula (222) MII                                                                                            |

|                        | <ul> <li>Core operation frequency: 333MHz</li> <li>16KB instruction cache</li> </ul>                                                                                   |

|                        | 16KB instruction cache     16KB data cache                                                                                                                             |

|                        | <ul> <li>Tightly-Coupled memory for 16KB instruction (ITCM)</li> </ul>                                                                                                 |

|                        | Tightly-Coupled memory for 16KB data (DTCM)      Tightly-Coupled memory for 16KB data (DTCM)                                                                           |

|                        | ETM9CS Single and JTAG ICE debugging interface                                                                                                                         |

|                        | Java acceleration (Jazelle technology)                                                                                                                                 |

| Bus architecture       | Multilayer AHB bus architecture                                                                                                                                        |

|                        | Speeding up data transfer between main memory and each bus master with 64 bit AXI bus                                                                                  |

|                        |                                                                                                                                                                        |

| Interrupt              | High-speed interrupt × 1ch (software interrupt)                                                                                                                        |

|                        | <ul> <li>Normal interrupt × 64ch (external interrupt × 4ch + built-in internal interrupt × 60ch)</li> <li>Up to 16 interrupt levels are settable by channel</li> </ul> |

| Clock                  | ● PLL multiplication: selectable from ×15 ~ 49                                                                                                                         |

|                        | • Operation frequency: 333MHz (CPU), 83MHz (AHB), 41.5MHz (APB)                                                                                                        |

|                        | Low power consumption mode (clock to ARM and module is stoppable)                                                                                                      |

| Reset                  | Hardware reset, software reset, and watchdog reset                                                                                                                     |

| Remap                  | ROM area is able to be mapping to built-in SRAM area                                                                                                                   |

| External bus interface | Three chip select signals                                                                                                                                              |

|                        | Provided 32M byte address space in each chip select                                                                                                                    |

|                        | Supported 16/32 bit width SRAM/Flash ROM connection                                                                                                                    |

|                        | Programmable weight controller                                                                                                                                         |

|                        | Encrypted ROM compound engine                                                                                                                                          |

| DDR2 controller        | Supported DDR2SDRAM (DDR2-400)                                                                                                                                         |

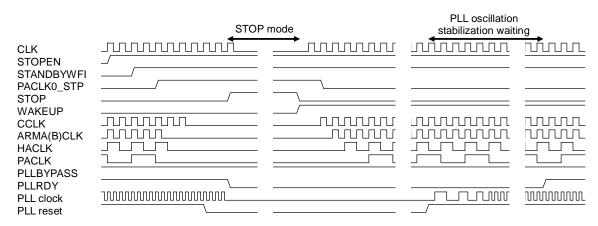

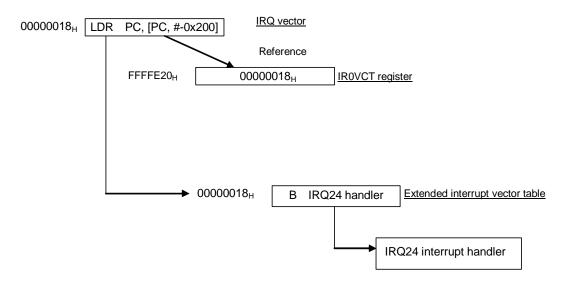

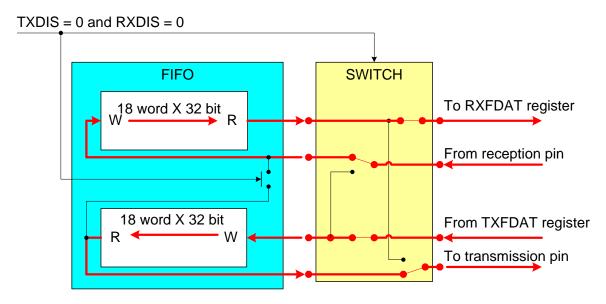

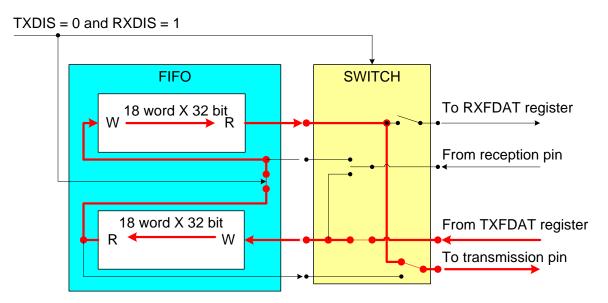

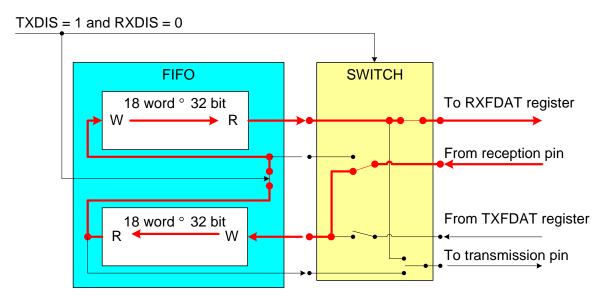

|                        | ● Connectable capacity: 256 ~ 512M bit × 2 or 256 ~ 512M bit × 1                                                                                                       |