scale Semiconductor Advance Information

Document Number: MC34709 Rev. 4.0, 11/2013

# **Power Management Integrated** Circuit (PMIC) for i.MX50/53 **Families**

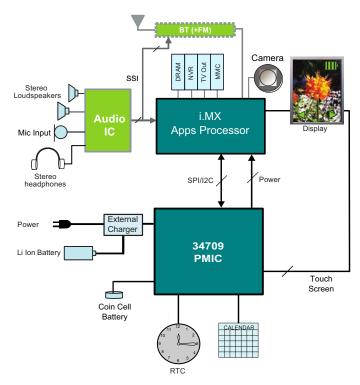

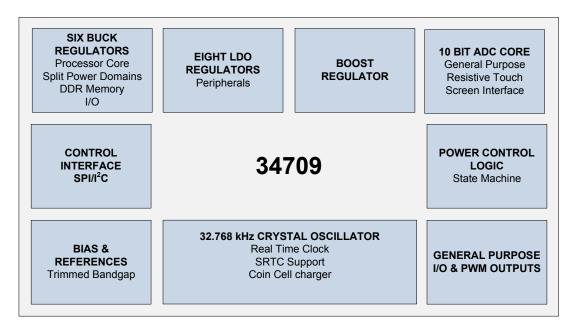

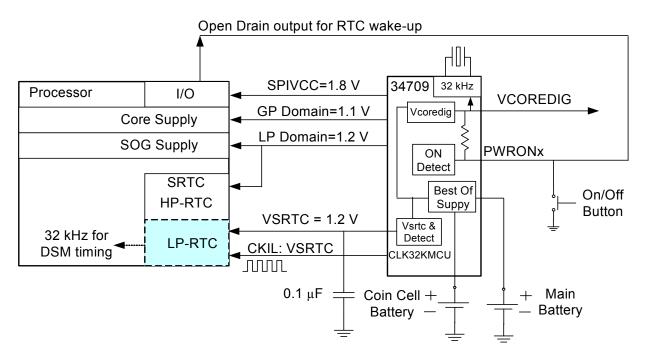

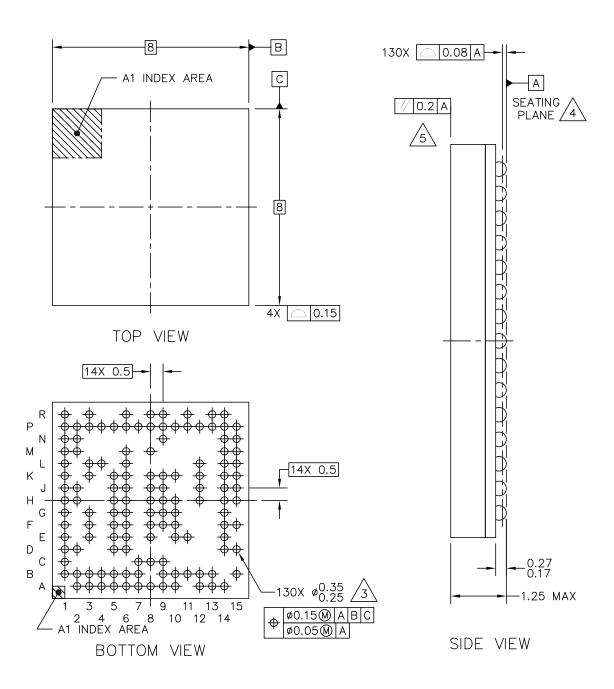

The 34709 is the Power Management Integrated Circuit (PMIC) designed primarily for use with the Freescale i.MX50 and i.MX53 families. It offers a low cost solution targeting embedded applications that do not require a battery charger. However, it can be easily combined with an external charger, allowing flexibility for either single or multi-cell Li-lon battery configurations. It supports both consumer and industrial applications with a single 130-pin 8x8 MAPBGA 0.5 mm pitch package that is easily routable in low cost board designs.

#### **Features**

- · Six multi-mode buck regulators for direct supply of the processor core, memory, and peripherals.

- · Boost regulator for USB PHY domain on i.MX processors.

- Eight LDO regulators with internal and external pass devices for thermal budget optimization and DDR memory voltage reference

- 10-bit ADC for monitoring battery and other inputs

- Real time clock and crystal oscillator circuitry with a coin cell backup/charger

- SPI/I<sup>2</sup>C bus for control and register interface

- Four general purpose low-voltage I/Os with interrupt capability

- Two PWM outputs

## 34709

#### **POWER MANAGEMENT**

VK SUFFIX (PB-FREE) 98ASA00333D 130 MAPBGA 8.0 X 8.0 (0.5 MM PITCH)

| Applications                   |  |  |  |  |  |

|--------------------------------|--|--|--|--|--|

| Tablets                        |  |  |  |  |  |

| Smart Mobile Devices           |  |  |  |  |  |

| Patient Monitors               |  |  |  |  |  |

| Digital Signage                |  |  |  |  |  |

| Human Machine Interfaces (HMI) |  |  |  |  |  |

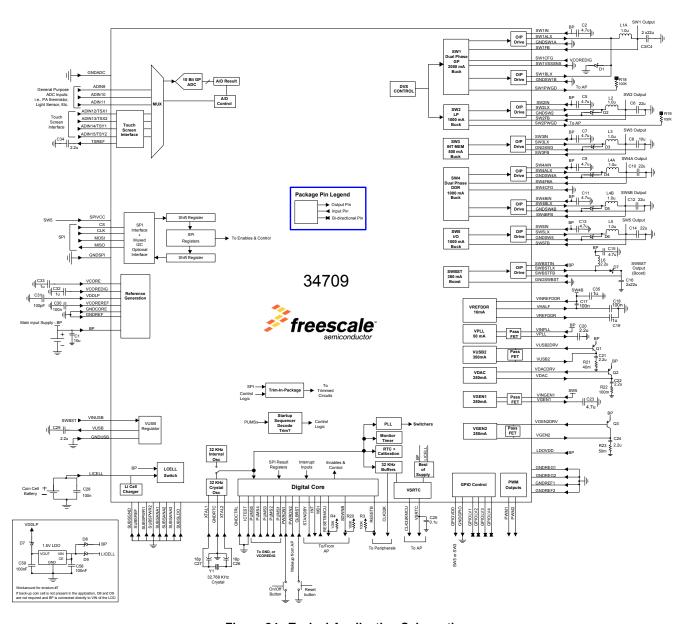

Figure 1. Simplified Application Diagram

<sup>\*</sup> This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

# **Table of Contents**

| 1 | 1 Orderable Parts 4 |             |                             |     |  |  |  |  |  |

|---|---------------------|-------------|-----------------------------|-----|--|--|--|--|--|

| 2 | Part                | Identificat | tion                        | 5   |  |  |  |  |  |

|   | 2.1                 | Descript    | tion                        | 5   |  |  |  |  |  |

|   | 2.2                 | Format      | and Examples                | 5   |  |  |  |  |  |

|   | 2.3                 | Fields .    |                             | . 5 |  |  |  |  |  |

| 3 | Inter               | nal Block   | Diagram                     | 6   |  |  |  |  |  |

|   | 3                   | Internal    | Block Diagram               | 6   |  |  |  |  |  |

| 4 | Pin C               | Connectio   | ns                          | 7   |  |  |  |  |  |

|   | 4.1                 | Ballmap     | )                           | 7   |  |  |  |  |  |

|   | 4.2                 | Pin Defi    | initions                    | 8   |  |  |  |  |  |

| 5 | Gene                | eral Produ  | uct Characteristics         | 12  |  |  |  |  |  |

|   | 5.1                 |             | m Ratings                   |     |  |  |  |  |  |

|   | 5.2                 | Therma      | I Characteristics           | 13  |  |  |  |  |  |

|   |                     | 5.2.2       | Power Dissipation           |     |  |  |  |  |  |

|   | 5.3                 |             | al Characteristics          |     |  |  |  |  |  |

|   |                     | 5.3.2       | General PMIC Specifications |     |  |  |  |  |  |

|   |                     | 5.3.3       | Current Consumption         |     |  |  |  |  |  |

| 6 | Gene                |             | ription                     |     |  |  |  |  |  |

| • | 6.1                 |             | 8                           |     |  |  |  |  |  |

|   | 6.2                 |             | iagram                      |     |  |  |  |  |  |

|   | 7                   |             | nal Block Description       |     |  |  |  |  |  |

| 7 |                     |             | ock Description             |     |  |  |  |  |  |

| ' | 7.1                 |             | Requirements                |     |  |  |  |  |  |

|   | 7.1                 |             | d References Block          |     |  |  |  |  |  |

|   | 7.3                 |             | g and Oscillators           |     |  |  |  |  |  |

|   | 1.3                 | 7.3.1       | Clock Generation            |     |  |  |  |  |  |

|   |                     | 7.3.1       | SRTC Support                |     |  |  |  |  |  |

|   |                     | 7.3.2       | Coin Cell Battery Backup    |     |  |  |  |  |  |

|   | 7.4                 |             |                             |     |  |  |  |  |  |

|   | 7.4                 |             | t Management                |     |  |  |  |  |  |

|   |                     | 7.4.1       |                             |     |  |  |  |  |  |

|   | <b>7</b> F          | 7.4.2       | Interrupt Bit Summary       |     |  |  |  |  |  |

|   | 7.5                 |             |                             |     |  |  |  |  |  |

|   |                     | 7.5.1       | Power Tree                  |     |  |  |  |  |  |

|   |                     | 7.5.2       | Modes of Operation          |     |  |  |  |  |  |

|   |                     | 7.5.3       | Power Control Logic         |     |  |  |  |  |  |

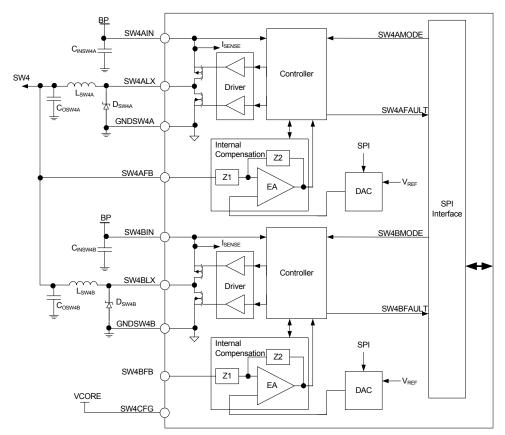

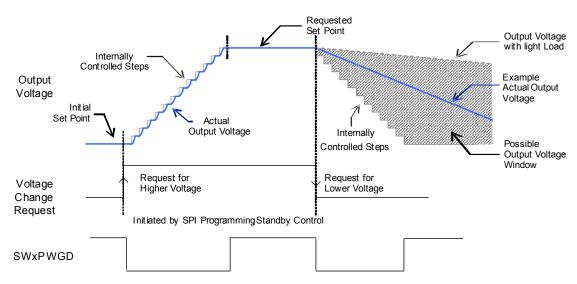

|   |                     | 7.5.4       | Buck Switching Regulators   |     |  |  |  |  |  |

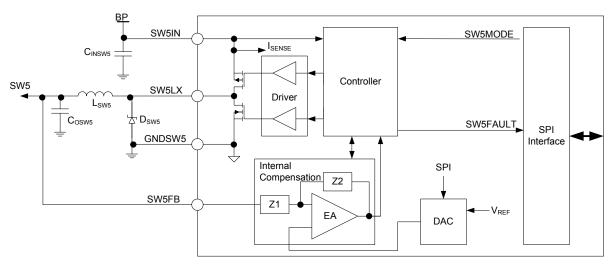

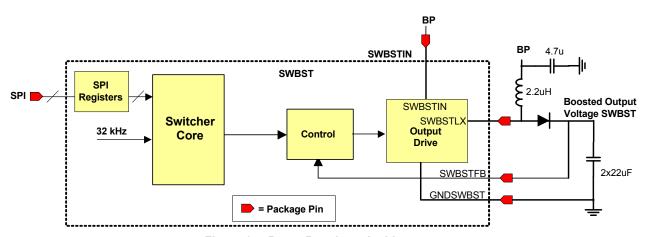

|   |                     | 7.5.5       | Boost Switching Regulator   |     |  |  |  |  |  |

|   | 7.0                 | 7.5.6       | Linear Regulators (LDOs)    |     |  |  |  |  |  |

|   | 7.6                 |             | to Digital Converter        |     |  |  |  |  |  |

|   |                     | 7.6.1       | Input Selector              |     |  |  |  |  |  |

|   |                     | 7.6.2       | Control                     |     |  |  |  |  |  |

|   |                     | 7.6.3       | Dedicated Readings          |     |  |  |  |  |  |

|   |                     | 7.6.4       | Touch Screen Interface      |     |  |  |  |  |  |

|   |                     | 7.6.5       | ADC Specifications          |     |  |  |  |  |  |

|   | 7.7                 | •           | y Circuits                  |     |  |  |  |  |  |

|   |                     | 7.7.1       | General Purpose I/Os        |     |  |  |  |  |  |

|   |                     | 7.7.2       | PWM Outputs                 |     |  |  |  |  |  |

|   | 7.8                 |             | nterfaces                   |     |  |  |  |  |  |

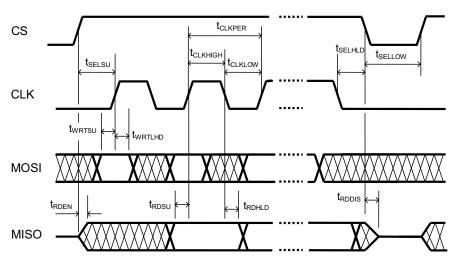

|   |                     | 7.8.1       | SPI Interface               |     |  |  |  |  |  |

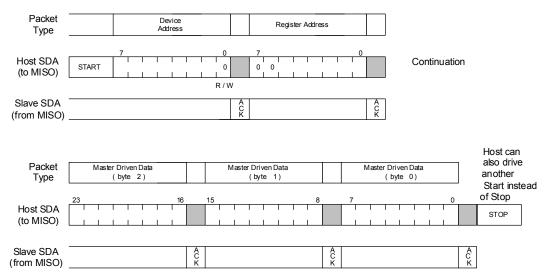

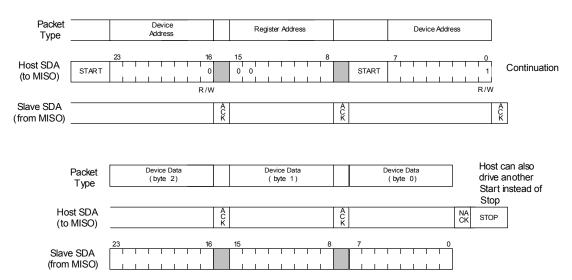

|   |                     | 7.8.2       | I2C Interface               |     |  |  |  |  |  |

|   |                     | 7.8.3       | SPI/I2C Specification       | 87  |  |  |  |  |  |

|    | 7.9  | Configu    | ıration Registers                          | . 88 |

|----|------|------------|--------------------------------------------|------|

|    |      | 7.9.1      | Register Set structure                     | . 88 |

|    |      | 7.9.2      | Specific Registers                         | . 89 |

|    |      | 7.9.3      | SPI/I2C Register Map                       | . 90 |

|    |      | 7.9.4      | SPI Register's Bit Description             | . 96 |

| 8  | Typi | cal Applic | cations                                    | 128  |

|    | 8.1  |            | tion Diagram                               |      |

|    | 8.2  | Bill of N  | Naterial                                   | 129  |

|    | 8.3  | 34709      | Layout Guidelines                          | 132  |

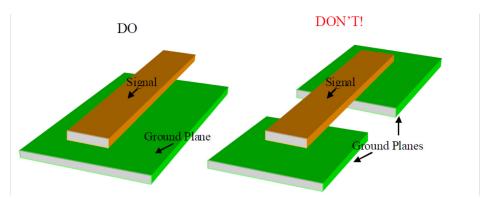

|    |      | 8.3.1      | General board recommendations              | 132  |

|    |      | 8.3.2      | General Routing Requirements               | 132  |

|    |      | 8.3.3      | Parallel Routing Requirements              | 132  |

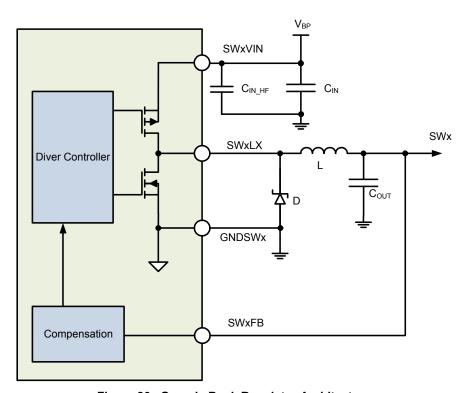

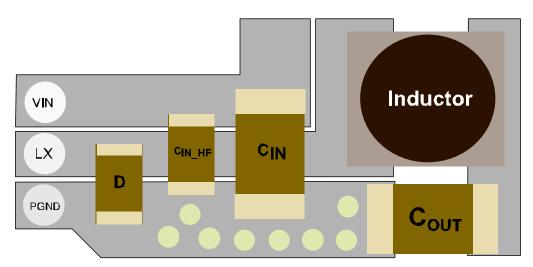

|    |      | 8.3.4      | Switching Regulator Layout Recommendations | 133  |

| 9  | Pack | caging .   |                                            | 135  |

| 10 | Refe | rence Se   | ection                                     | 138  |

| 11 | Povi | eion Hiet  | DDV                                        | 130  |

# 1 Orderable Parts

This section describes the part numbers available to be purchased, along with their differences. Valid orderable part numbers are provided on the web. To determine the orderable part numbers for this device, go to <a href="http://www.freescale.com">http://www.freescale.com</a> and perform a part number search for the following device numbers.

**Table 1. Orderable Part Variations**

| Part Number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package                                  |

|----------------------------|-------------------------------|------------------------------------------|

| MC34709VK                  | -40 to 85 °C                  | 130 MAPBGA - 8.0 x 8.0 mm - 0.5 mm Pitch |

#### Notes

1. To Order parts in Tape & Reel, add the R2 suffix to the part number.

# 2 Part Identification

This section provides an explanation of the part numbers and their alpha numeric breakdown.

# 2.1 Description

Part numbers for the chips have fields that identify the specific part configuration. You can use the values of these fields to determine the specific part you have received.

# 2.2 Format and Examples

Part numbers for a given device have the following format, followed by a device example:

Table 2 - Part Numbering - Analog:

MC tt xxx r v PP RR - MC34709VKR2

## 2.3 Fields

These tables list the possible values for each field in the part number (not all combinations are valid).

**Table 2: Part Numbering - Analog**

| FIELD | DESCRIPTION             | VALUES                                                                              |

|-------|-------------------------|-------------------------------------------------------------------------------------|

| МС    | Product Category        | MC- Qualified Standard     PC- Prototype Device                                     |

| tt    | Temperature Range       | • 33 = -40 °C to > 105 °C<br>• 34 = -40 °C to ≤ 105 °C<br>• 35 = -55 °C to ≥ 125 °C |

| xxx   | Product Number          | Assigned by Marketing                                                               |

| r     | Revision                | (default blank)                                                                     |

| v     | Variation               | (default blank)                                                                     |

| PP    | Package Identifier      | Varies by package                                                                   |

| RR    | Tape and Reel Indicator | • R2 = 13 inch reel hub size                                                        |

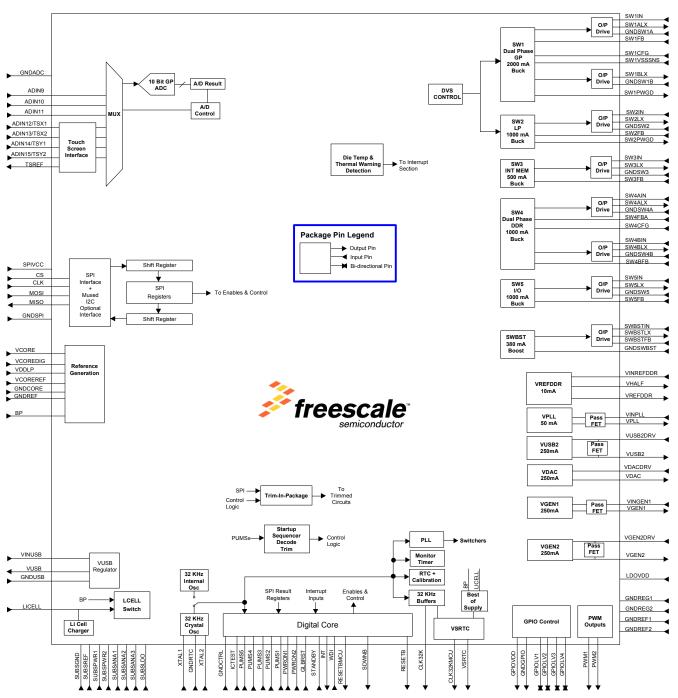

# 3 Internal Block Diagram

Figure 2. Simplified Internal Block Diagram

# 4 Pin Connections

# 4.1 Ballmap

|   | 1        | 2      | 3         | 4      | 5         | 6       | 7       | 8        | 9        | 10       | 11       | 12       | 13        | 14        | 15      |

|---|----------|--------|-----------|--------|-----------|---------|---------|----------|----------|----------|----------|----------|-----------|-----------|---------|

| Α |          | MISO   | GNDSPI    | SPIVCC | GLBRST    | PWRON1  | PWM2    | PWM1     | ICTEST   | SW2LX    |          | SW2FB    | SW2PWGD   | NC_2      |         |

| В | CLK      | CS     | MOSI      | INT    | RESETB    | GNDCTRL | GPIOLV1 |          | GPIOLV2  | GNDSW2   | SW2IN    | GNDREF2  | SW3FB     |           | NC_3    |

| С | GNDUSB   |        |           |        |           |         | GPIOLV0 | GPIOVDD  | GNDGPIO  |          |          |          |           |           |         |

| D | VINUSB   | VUSB   |           |        | RESETBMCU | SDWNB   |         |          |          |          |          |          |           | GNDSW3    | SW3LX   |

| E | XTAL1    |        | CLK32K    |        | PWRON2    | PUMS5   |         | SUBSPWR1 |          | GPIOLV3  | SUBSPWR2 |          |           | SW3IN     |         |

| F | GNDRTC   |        | CLK32KVCC |        | PUMS4     | PUMS3   |         | SUBSPWR1 | SUBSPWR1 | SUBSANA2 |          |          |           | GNDSWBST  | SWBSTIN |

| G | XTAL2    |        | CLK32KMCU |        | PUMS2     | PUMS1   |         | SUBSPWR1 | SUBSPWR1 | SUBSPWR3 |          |          |           | SWBSTLX   |         |

| н | GNDCORE  | VSRTC  |           |        | GNDADC    | ADIN9   |         | SUBSPWR1 | SUBSPWR1 | SUBSLDO  |          | VGEN1    |           | VINGEN1   | SWBSTFB |

| J | VCOREDIG | VCORE  |           |        | ADIN10    | ADIN11  |         | SUBSGND  | SUBSPWR1 |          |          | GNDREG2  |           | VINREFDDR | VHALF   |

| К | VCOREREF |        | WDI       |        | TSX1      | TSREF   |         | SUBSREF  | SUBSPWR  | SW1PWGD  |          | SUBSANA1 |           | VPLL      | VREFDDR |

| L | VDDLP    |        | TSY2      | TSX2   |           | TSY1    |         |          |          |          |          | SW1CFG   |           | VGEN2DRV  | VINPLL  |

| М | GNDREF   | LICELL |           |        |           | SW4CFG  |         | SW5FB    |          |          |          |          |           | GNDREG1   | VGEN2   |

| N | BP       | SW4AFB |           |        |           |         |         |          | GNDREF1  |          |          |          |           | VDACDRV   | LDOVDD  |

| Р | STANDBY  | SW4BFB | GNDSW4A   | SW4AIN | SW4BIN    | GNDSW4B | SW5IN   | GNDSW5   | GNDSW1A  | SW1IN    | SW1IN    | GNDSW1B  | SW1FB     | VUSB2DRV  | VDAC    |

| R | NC_1     |        | SW4ALX    |        |           | SW4BLX  |         | SW5LX    | SW1ALX   |          | SW1BLX   |          | SW1VSSSNS | VUSB2     |         |

Figure 3. Top View Ballmap

# 4.2 Pin Definitions

**Table 3. Pin Definitions**

| Pin Number      | Pin Name  | Pin Function | Definition                                                         |

|-----------------|-----------|--------------|--------------------------------------------------------------------|

| Supply          |           | •            |                                                                    |

| N1              | BP        | I            | Application supply point     Input supply to the IC core circuitry |

| D6              | SDWNB     | 0            | Indication of imminent system shutdown                             |

| IC Core         |           |              |                                                                    |

| J2              | VCORE     | 0            | Regulated supply for the IC analog core circuitry                  |

| J1              | VCOREDIG  | 0            | Regulated supply for the IC digital core circuitry                 |

| K1              | VCOREREF  | 0            | Main bandgap reference                                             |

| L1              | VDDLP     | 0            | VDDLP reference                                                    |

| H1              | GNDCORE   | GND          | Ground for the IC core circuitry                                   |

| M1              | GNDREF    | GND          | Ground reference for IC core circuitry                             |

| Switching Regul | ators     | •            |                                                                    |

| P10<br>P11      | SW1IN     | I            | Regulator 1 input <sup>(2)</sup>                                   |

| R9              | SW1ALX    | 0            | Regulator 1A switch node connection (2)                            |

| P13             | SW1FB     | I            | Regulator 1 feedback <sup>(2)</sup>                                |

| P9              | GNDSW1A   | GND          | Ground for Regulator 1A                                            |

| R13             | SW1VSSSNS | GND          | Regulator 1 sense                                                  |

| K10             | SW1PWGD   | 0            | Power good signal for SW1 <sup>(2)</sup>                           |

| R11             | SW1BLX    | 0            | Regulator 1B switch node connection (2)                            |

| P12             | GNDSW1B   | GND          | Ground for Regulator 1B                                            |

| L12             | SW1CFG    | ı            | Regulator 1A/B mode configuration (2)                              |

| B11             | SW2IN     | ı            | Regulator 2 input (2)                                              |

| A10             | SW2LX     | 0            | Regulator 2 switch node connection (2)                             |

| A12             | SW2FB     | I            | Regulator 2 feedback <sup>(2)</sup>                                |

| B10             | GNDSW2    | GND          | Ground for Regulator 2                                             |

| A13             | SW2PWGD   | 0            | Power good signal for SW2 <sup>(2)</sup>                           |

| E14             | SW3IN     | ı            | Regulator 3 input (2)                                              |

| D15             | SW3LX     | 0            | Regulator 3 switch node connection (2)                             |

| B13             | SW3FB     | ı            | Regulator 3 feedback <sup>(2)</sup>                                |

| D14             | GNDSW3    | GND          | Ground for Regulator 3                                             |

| B12             | GNDREF2   | GND          | Ground reference for Regulators                                    |

| P4              | SW4AIN    | ı            | Regulator 4A input (2)                                             |

| R3              | SW4ALX    | 0            | Regulator 4A switch node connection (2)                            |

| N2              | SW4AFB    | I            | Regulator 4A feedback <sup>(2)</sup>                               |

| P3              | GNDSW4A   | GND          | Ground for Regulator 4A                                            |

Table 3. Pin Definitions (continued)

| Pin Number | Pin Name | Pin Function | Definition                              |

|------------|----------|--------------|-----------------------------------------|

| P5         | SW4BIN   | I            | Regulator 4B input (2)                  |

| R6         | SW4BLX   | 0            | Regulator 4B switch node connection (2) |

| P2         | SW4BFB   | I            | Regulator 4B feedback <sup>(2)</sup>    |

| P6         | GNDSW4B  | GND          | Ground for Regulator 4B                 |

| M6         | SW4CFG   | I            | Regulator 4A/B mode configuration (2)   |

| P7         | SW5IN    | I            | Regulator 5 input (2)                   |

| R8         | SW5LX    | 0            | Regulator 5 output <sup>(2)</sup>       |

| M8         | SW5FB    | I            | Regulator 5 feedback <sup>(2)</sup>     |

| P8         | GNDSW5   | GND          | Ground for Regulator 5                  |

| N9         | GNDREF1  | GND          | Ground reference for regulators         |

| F15        | SWBSTIN  | I            | Boost Regulator BP supply (2)           |

| G14        | SWBSTLX  | 0            | SWBST switch node connection (2)        |

| H15        | SWBSTFB  | I            | Boost Regulator feedback (2)            |

| F14        | GNDSWBST | GND          | Ground for regulator boost              |

### **LDO Regulators**

| J14  | VINREFDDR | ı   | VREFDDR input supply                                                                                                                                                                              |

|------|-----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| K15  | VREFDDR   | 0   | VREFDDR regulator output                                                                                                                                                                          |

| J15  | VHALF     | 0   | Half supply reference for VREFDDR                                                                                                                                                                 |

| L15  | VINPLL    | 1   | VPLL input supply                                                                                                                                                                                 |

| K14  | VPLL      | 0   | VPLL regulator output                                                                                                                                                                             |

| N14  | VDACDRV   | 0   | Drive output for VDAC regulator using an external PNP device                                                                                                                                      |

| P15  | VDAC      | 0   | VDAC regulator output                                                                                                                                                                             |

| N15  | LDOVDD    | I   | Supply pin for VUSB2, VDAC, and VGEN2 Must be always connected to the same supply as the PNP emitter. Recommended to use BP as the LDOVDD supply. See Figure 24 for a typical connection diagram. |

| D2   | VUSB      | 0   | USB transceiver regulator output                                                                                                                                                                  |

| D1   | VINUSB    | 1   | VUSB input supply                                                                                                                                                                                 |

| C1   | GNDUSB    | GND | Ground for VUSB LDO                                                                                                                                                                               |

| P14  | VUSB2DRV  | I   | VUSB2 input using internal PMOS FET                                                                                                                                                               |

| F14  | VUSBZDKV  | 0   | Drive output for VUSB2 regulator using an external PNP device                                                                                                                                     |

| R14  | VUSB2     | 0   | VUSB2 regulator output                                                                                                                                                                            |

| H14  | VINGEN1   | I   | VGEN1 input supply                                                                                                                                                                                |

| H12  | VGEN1     | 0   | VGEN1 regulator output                                                                                                                                                                            |

| L14  | VGEN2DRV  | 1   | VGEN2 input using internal PMOS FET                                                                                                                                                               |

| L 14 | VGLINZDRV | 0   | Drive output for VGEN2 regulator using an external PNP device                                                                                                                                     |

| M15  | VGEN2     | 0   | VGEN2 regulator output                                                                                                                                                                            |

| H2   | VSRTC     | 0   | Output regulator for SRTC module on processor                                                                                                                                                     |

| M14  | GNDREG1   | GND | Ground for Regulator 1                                                                                                                                                                            |

| J12  | GNDREG2   | GND | Ground for Regulator 2                                                                                                                                                                            |

|      |           |     |                                                                                                                                                                                                   |

#### 34709

Table 3. Pin Definitions (continued)

| Pin Number | Pin Name | Pin Function | Definition                     |

|------------|----------|--------------|--------------------------------|

| C8         | GPIOVDD  | I            | Supply for GPIOLV pins         |

| C7         | GPIOLV0  | I/O          | General purpose input/output 1 |

| В7         | GPIOLV1  | I/O          | General purpose input/output 2 |

| В9         | GPIOLV2  | I/O          | General purpose input/output 3 |

| E10        | GPIOLV3  | I/O          | General purpose input/output 4 |

| A8         | PWM1     | 0            | PWM output 1                   |

| A7         | PWM2     | 0            | PWM output 2                   |

| C9         | GNDGPIO  | GND          | GPIO ground                    |

#### Clock/RTC/Coin Cell

| M2   | LICELL    | I   | 1. Coin cell supply input                  |

|------|-----------|-----|--------------------------------------------|

| IVIZ |           | 0   | 2. Coin cell charger output                |

| E1   | XTAL1     | I   | 32.768 kHz Oscillator crystal connection 1 |

| G1   | XTAL2     | I   | 32.768 kHz Oscillator crystal connection 2 |

| F1   | GNDRTC    | GND | Ground for the RTC block                   |

| F3   | CLK32KVCC | I   | Supply voltage for 32 k buffer             |

| E3   | CLK32K    | 0   | 32 kHz Clock output for peripherals        |

| G3   | CLK32KMCU | 0   | 32 kHz Clock output for processor          |

### **Control Logic**

| =  |           |     |                                     |

|----|-----------|-----|-------------------------------------|

| B5 | RESETB    | 0   | Reset output for peripherals        |

| D5 | RESETBMCU | 0   | Reset output for processor          |

| К3 | WDI       | I   | Watchdog input                      |

| P1 | STANDBY   | I   | Standby input signal from processor |

| B4 | INT       | 0   | Interrupt to processor              |

| A6 | PWRON1    | I   | Power on/off button connection 1    |

| E5 | PWRON2    | ļ   | Power on/off button connection 2    |

| A5 | GLBRST    | I   | Global Reset                        |

| G6 | PUMS1     | ļ   | Power up mode supply setting 1      |

| G5 | PUMS2     | ļ   | Power up mode supply setting 2      |

| F6 | PUMS3     | I   | Power up mode supply setting 3      |

| F5 | PUMS4     | I   | Power up mode supply setting 4      |

| E6 | PUMS5     | ļ   | Power up mode supply setting 5      |

| A9 | ICTEST    | I   | Connect to GND for normal operation |

| В6 | GNDCTRL   | GND | Ground for control logic            |

| A4 | SPIVCC    | I   | Supply for SPI bus                  |

| B2 | CS        | I   | Primary SPI select input            |

| B1 | CLK       | I   | Primary SPI clock input             |

| В3 | MOSI      | I   | Primary SPI write input             |

| A2 | MISO      | 0   | Primary SPI read output             |

|    |           |     |                                     |

Table 3. Pin Definitions (continued)

| Pin Number       | Pin Name | Pin Function | Definition                  |

|------------------|----------|--------------|-----------------------------|

| А3               | GNDSPI   | GND          | Ground for SPI interface    |

| A to D Converter | r        |              |                             |

| 110              | ADINIO   |              | ADC generic input channel 0 |

| H6 ADIN9 I ADC generic input channel 9  J5 ADIN10 I ADC generic input channel 10  J6 ADIN11 I ADC generic input channel 11  K5 TSX1 I Touch Screen Interface X1 or ADC generic input channel 12  L4 TSX2 I Touch Screen Interface X2 or ADC generic input channel 13  L6 TSY1 I Touch Screen Interface Y1 or ADC generic input channel 14  L3 TSY2 I Touch Screen Interface Y2 or ADC generic input channel 15  K6 TSREF O Touch screen reference  H5 GNDADC GND Ground for A to D circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |        |     |                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------|-----|-----------------------------------------------------------|

| J6 ADIN11 I ADC generic input channel 11  K5 TSX1 I Touch Screen Interface X1 or ADC generic input channel 12  L4 TSX2 I Touch Screen Interface X2 or ADC generic input channel 13  L6 TSY1 I Touch Screen Interface Y1 or ADC generic input channel 14  L3 TSY2 I Touch Screen Interface Y2 or ADC generic input channel 15  K6 TSREF O Touch screen reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | H6 | ADIN9  | I   | ADC generic input channel 9                               |

| K5 TSX1 I Touch Screen Interface X1 or ADC generic input channel 12  L4 TSX2 I Touch Screen Interface X2 or ADC generic input channel 13  L6 TSY1 I Touch Screen Interface Y1 or ADC generic input channel 14  L3 TSY2 I Touch Screen Interface Y2 or ADC generic input channel 15  K6 TSREF O Touch screen reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | J5 | ADIN10 | I   | ADC generic input channel 10                              |

| L4 TSX2 I Touch Screen Interface X2 or ADC generic input channel 13  L6 TSY1 I Touch Screen Interface Y1 or ADC generic input channel 14  L3 TSY2 I Touch Screen Interface Y2 or ADC generic input channel 15  K6 TSREF O Touch screen reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | J6 | ADIN11 | I   | ADC generic input channel 11                              |

| L6 TSY1 I Touch Screen Interface Y1 or ADC generic input channel 14 L3 TSY2 I Touch Screen Interface Y2 or ADC generic input channel 15 K6 TSREF O Touch screen reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | K5 | TSX1   | I   | Touch Screen Interface X1 or ADC generic input channel 12 |

| L3 TSY2 I Touch Screen Interface Y2 or ADC generic input channel 15  K6 TSREF O Touch screen reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | L4 | TSX2   | I   | Touch Screen Interface X2 or ADC generic input channel 13 |

| K6 TSREF O Touch screen reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | L6 | TSY1   | I   | Touch Screen Interface Y1 or ADC generic input channel 14 |

| No lence o len | L3 | TSY2   | I   | Touch Screen Interface Y2 or ADC generic input channel 15 |

| H5 GNDADC GND Ground for A to D circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | K6 | TSREF  | 0   | Touch screen reference                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | H5 | GNDADC | GND | Ground for A to D circuitry                               |

#### **Substrate Grounds**

| K8  | SUBSREF   | GND | Substrate ground connection |

|-----|-----------|-----|-----------------------------|

| K9  | SUBSPWR   | GND | Substrate ground connection |

| E8  |           |     |                             |

| F8  |           |     |                             |

| F9  |           |     |                             |

| G8  | SUBSPWR1  | GND | Substrate ground connection |

| G9  | SUBSEVIKI | GND | Substrate ground connection |

| H8  |           |     |                             |

| H9  |           |     |                             |

| J9  |           |     |                             |

| E11 | SUBSPWR2  | GND | Substrate ground connection |

| G10 | SUBSPWR3  | GND | Substrate ground connection |

| H10 | SUBSLDO   | GND | Substrate ground connection |

| K12 | SUBSANA1  | GND | Substrate ground connection |

| F10 | SUBSANA2  | GND | Substrate ground connection |

| J8  | SUBSGND   | GND | Substrate ground connection |

### No connects

| A14 |    |   |                |

|-----|----|---|----------------|

| B15 | NC | - | Do not connect |

| R1  |    |   |                |

#### Notes

2. If a switching regulator is not used, connect the regulator pins as follows: SWxVIN = BP, SWxLX = NC, SWxFB = GND, SWxPWGD = NC, SWxCFG = GND

# 5 General Product Characteristics

# 5.1 Maximum Ratings

### **Table 4. Maximum Ratings**

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol       | Description (Rating)                                                                                                | Min. | Max.  | Unit | Notes   |

|--------------|---------------------------------------------------------------------------------------------------------------------|------|-------|------|---------|

| LECTRICAL    | RATINGS                                                                                                             |      | II.   | •    | · I     |

|              | Input Supply Pins                                                                                                   |      |       |      |         |

| $V_{BP}$     | • BP                                                                                                                | -    | 4.8   | V    |         |

| $V_{LICELL}$ | • LICELL                                                                                                            | -    | 4.8   |      |         |

|              | IC Core Reference                                                                                                   |      |       |      |         |

|              | • VCOREREF                                                                                                          | -    | 1.5   | .,   |         |

|              | VCOREDIG, VDDLP                                                                                                     | -    | 1.6   | V    |         |

|              | • VCORE                                                                                                             | -    | 3.6   |      |         |

|              | Switching Regulators Pins                                                                                           |      |       |      |         |

|              | SWxIN, SWxLX, SWBSTFB                                                                                               | -    | 5.5   | .,   |         |

|              | SWxFB, SWxPWGD, SWxCFG                                                                                              | -    | 3.6   | V    |         |

|              | • SWBSTLX                                                                                                           | -    | 7.5   |      |         |

|              | LDO Regulator Pins                                                                                                  |      |       |      |         |

|              | VREFDDR, VHALF                                                                                                      | -    | 1.5   |      |         |

|              | VPLL, VGEN1, VINGEN1, VSRTC                                                                                         | -    | 2.5   | .,   |         |

|              | <ul> <li>VINREFDDR, VDAC, VUSB2, VGEN2, VUSB</li> </ul>                                                             | -    | 3.6   | V    |         |

|              | <ul> <li>VINPLL, VDACDRV, VUSB2DRV, VGEN2DRV</li> </ul>                                                             | -    | 4.8   |      |         |

|              | • LDOVDD, VINUSB                                                                                                    | -    | 5.5   |      |         |

|              | GPIO Pins                                                                                                           |      |       |      |         |

|              | GPIOVDD, GPIOLVx, PWMx                                                                                              | -    | 2.5   | V    |         |

|              | Control Logic Pins                                                                                                  |      |       |      |         |

|              | • ICTEST                                                                                                            | -    | 1.8   |      |         |

|              | • XTAL1, XTAL2                                                                                                      | -    | 2.5   | V    |         |

|              | • CLK32KVCC, CLK32K, CLK32KMCU, WDI, STANDBY,INT, PWRON1, PWRON2, GLBRST, PUMSx, SPIVCC, CS, CLK, MOSI, MISO, SDWNB | -    | 3.6   |      |         |

|              | ADC Interface Pins                                                                                                  |      |       |      |         |

|              | ADINx, TSX1/ADIN12, TSX2/ADIN13, TSY1/ADIN14, TSY2/ADIN15, TSREF                                                    | -    | 4.8   | V    | (4), (5 |

|              | ESD Ratings                                                                                                         |      |       |      |         |

| $V_{ESD}$    | Human Body Model All pins                                                                                           | -    | ±2000 | V    | (3)     |

| 200          | Charge Device Model All pins                                                                                        | -    | ±500  |      | (3)     |

#### Notes

- 3. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), and the Charge Device Model (CDM), Robotic ( $C_{ZAP}$  = 4.0 pF).

- 4. ADINx must not exceed BP.

- 5. TSXx and TSYx must not exceed BP or VCORE.

## 5.2 Thermal Characteristics

The thermal rating data of the packages has been simulated with the results listed in Table 5.

Table 5. Thermal Ratings

| Symbol            | Description (Rating)                                             | Min.     | Max.   | Unit | Notes     |

|-------------------|------------------------------------------------------------------|----------|--------|------|-----------|

| IERMAL RA         | ATINGS                                                           | <b>-</b> | 1      | I .  | L         |

| T <sub>A</sub>    | Ambient Operating Temperature Range                              | -40      | 85     | °C   |           |

| TJ                | Operating Junction Temperature Range                             | -40      | 125    | °C   |           |

| T <sub>ST</sub>   | Storage Temperature Range                                        | -65      | 150    | °C   |           |

| T <sub>PPRT</sub> | Peak Package Reflow Temperature During Reflow                    | -        | Note 6 | °C   | (6), (7)  |

| IERMAL RE         | ESISTANCE AND PACKAGE DISSIPATION RATINGS                        |          | •      |      |           |

| $R_{\theta JA}$   | Junction to Ambient Natural Convection • Single layer board (1s) | -        | 93     | °C/W | (8), (9)  |

| $R_{\theta JMA}$  | Junction to Ambient Natural Convection Four layer board (2s2p)   | -        | 53     | °C/W | (8), (10) |

| $R_{\theta JMA}$  | Junction to Ambient (@200 ft/min.)  • Single layer board (1s)    | -        | 80     | °C/W | (8), (10) |

| $R_{\theta JMA}$  | Junction to Ambient (@200 ft/min.)  • Four layer board (2s2p)    | -        | 49     | °C/W | (8), (10) |

| $R_{\theta JB}$   | Junction to Board                                                | -        | 34     | °C/W | (11)      |

|                   | Junction to Case                                                 |          | 25     | °C/W | (12)      |

| ΨJT | Junction to Package Top  • Natural Convection | - | 6.0 | °C/W | (13) |  |

|-----|-----------------------------------------------|---|-----|------|------|--|

|-----|-----------------------------------------------|---|-----|------|------|--|

#### Notes

- 6. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause a malfunction or permanent damage to the device.

- Freescale's Package Reflow capability meets the Pb-free requirements for JEDEC standard J-STD-020C, for Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL).

- 8. Junction temperature is a function of on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 9. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 10. Per JEDEC JESD51-6 with the board horizontal.

- 11. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 12. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 13. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Junction to Ambient Thermal Resistance Nomenclature: the JEDEC specification reserves the symbol  $R_{\theta JA}$  or  $\theta JA$  (Theta-JA) strictly for junction-to-ambient thermal resistance on a 1s test board in natural convection environment.  $R_{\theta JMA}$  or  $\theta JMA$  (Theta-JMA) will be used for both junction-to-ambient on a 2s2p test board in natural convection and for junction-to-ambient with forced convection on both 1s and 2s2p test boards. It is anticipated that the generic name, Theta-JA, will continue to be commonly used

The JEDEC standards can be consulted at <a href="http://www.jedec.org/">http://www.jedec.org/</a>

## 5.2.1 Estimation of Junction Temperature

An estimation of the chip junction temperature TJ can be obtained from the equation

•

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

#### where

- T<sub>A</sub> = Ambient temperature for the package in °C

- R<sub>θ,IA</sub> = Junction to ambient thermal resistance in °C/W

- P<sub>D</sub> = Power dissipation in the package in W

The junction to ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board  $R_{\theta JMA}$ . Actual application PCBs show a performance close to the simulated four layer board value although this may be somewhat degraded in case of significant power dissipated by other components placed close to the device.

At a known board temperature, the junction temperature T<sub>I</sub> is estimated using the following equation

•

$$T_J = T_B + (R_{\theta JB} \times P_D)$$

#### where

- T<sub>B</sub> = Board temperature at the package perimeter in °C

- R<sub>θJB</sub> = Junction to board thermal resistance in °C/W

- P<sub>D</sub> = Power dissipation in the package in W

When the heat loss from the package case to the air can be ignored, acceptable predictions of junction temperature can be made.

## 5.2.2 Power Dissipation

During operation, the temperature of the die should not exceed the maximum junction temperature. To optimize thermal management and avoid overheating, the 34709 PMIC provides a thermal management system. The thermal protection is based on a circuit with a voltage output that is proportional to the absolute temperature. This voltage can be read via the ADC for specific temperature readouts, see Analog to Digital Converter.

This voltage is monitored by an integrated comparator. Interrupts THERM110, THERM120, THERM125, and THERM130 will be generated when crossing in either direction of the thresholds specified in <u>Table 6</u>. The temperature range can be determined by reading the THERMxxxS bits.

Thermal protection is integrated to power off the 34709 PMIC, in case of over dissipation. This thermal protection will act above the maximum junction temperature to avoid any unwanted power downs. The protection is debounced for 8.0 ms in order to suppress any thermal noise. This protection should be considered as a fail-safe mechanism and therefore the application should be designed such that this protection is not tripped under normal conditions. The temperature thresholds and the sense bit assignment are listed in Table 6.

**Table 6. Thermal Protection Thresholds**

| Parameter                           | Min | Тур | Max | Units | Notes |

|-------------------------------------|-----|-----|-----|-------|-------|

| Thermal 110 °C threshold (THERM110) | 105 | 110 | 115 | °C    |       |

| Thermal 120 °C threshold (THERM120) | 115 | 120 | 125 | °C    |       |

| Thermal 125 °C threshold (THERM125) | 120 | 125 | 130 | °C    |       |

| Thermal 130 °C threshold (THERM130) | 125 | 130 | 135 | °C    |       |

| Thermal warning hysteresis          | 2.0 | -   | 4.0 | °C    | (14)  |

| Thermal protection threshold        | 130 | 140 | 150 | °C    |       |

#### Notes

14. Equivalent to approx. 30 mW min, 60 mW max

## 5.3 Electrical Characteristics

# **5.3.1** Recommended Operating Conditions

**Table 7. Recommended Operating Conditions**

| Symbol              | Description (Rating)  | Min. | Max. | Unit | Notes |

|---------------------|-----------------------|------|------|------|-------|

| V <sub>BP</sub>     | Main Input Supply     | 3.0  | 4.5  | V    |       |

| V <sub>LICELL</sub> | LICELL Backup Battery | 1.8  | 3.6  | V    |       |

| T <sub>A</sub>      | Ambient Temperature   | -40  | 85   | °C   |       |

# 5.3.2 General PMIC Specifications

Table 8. Pin Logic Thresholds

| Pin Name                                 | Internal<br>Termination <sup>(19)</sup> | Parameter     | Load Condition | Min             | Max <sup>(22)</sup> | Unit                                  | Notes      |

|------------------------------------------|-----------------------------------------|---------------|----------------|-----------------|---------------------|---------------------------------------|------------|

| PWRON1, PWRON2,                          | Pull up                                 | Input Low     | 47 kOhm        | 0.0             | 0.3                 | V                                     | (16)       |

| GLBRST                                   | r ull-up                                | Input High    | 1.0 MOhm       | 1.0             | VCOREDIG            | V V V V V V V V V V V V V V V V V V V | (16)       |

| STANDBY, WDI                             | Wook Bull down                          | Input Low     | -              | 0.0             | 0.3                 | ٧                                     | (21)       |

| STANDBT, WDI                             | Weak Full-down                          | Input High    | -              | 0.9             | 3.6                 | ٧                                     | (21)       |

| CLK32K                                   | CMOS                                    | Output Low    | -100 μΑ        | 0.0             | 0.2                 | ٧                                     |            |

| CLN32N                                   | CIVIOS                                  | Output High   | 100 μΑ         | CLK32KVCC - 0.2 | CLK32KVCC           | ٧                                     |            |

| CLK32KMCU                                | CMOS                                    | Output Low    | -100 μΑ        | 0.0             | 0.2                 | ٧                                     |            |

| CERSZRIVICO                              | CIVIOS                                  | Output High   | 100 μΑ         | VSRTC - 0.2     | VSRTC               | ٧                                     |            |

| RESETB,                                  | Open-drain                              | Output Low    | -2.0 mA        | 0.0             | 0.4                 | ٧                                     | (20)       |

| RESETBMCU,<br>SDWNB, SW1PWGD,<br>SW2PWGD | MCU,<br>SW1PWGD,                        | Output High   | Open-drain     | -               | 3.6                 | V                                     | (20)       |

| GPIOLV1,2,3,4                            | CMOS                                    | Input Low     | -              | 0.0             | 0.3 * GPIOVDD       | ٧                                     |            |

|                                          |                                         | Input High    | -              | 0.7 * GPIOVDD   | GPIOVDD + 0.3       | V                                     |            |

|                                          |                                         | Output Low    | -              | 0.0             | 0.2                 | V                                     |            |

|                                          |                                         | Output High   | -              | GPIOVDD - 0.2   | GPIOVDD             | V                                     |            |

|                                          | Open drain                              | Output Low    | -2.0 mA        | 0.0             | 0.4                 | ٧                                     |            |

|                                          | Pull-up                                 | GPIOVDD + 0.3 | V              |                 |                     |                                       |            |

| PWM1, PWM2                               | CMOS                                    | Output Low    | -              | 0.0             | 0.2                 | V                                     |            |

| I VVIVII, I VVIVIZ                       | CIVIOS                                  | Output High   | -              | GPIOVDD - 0.2   | GPIOVDD             | V                                     |            |

| CLK, MOSI                                |                                         | Input Low     | -              | 0.0             | 0.3 * SPIVCC        | V                                     | (15)       |

| CER, MOSI                                |                                         | Input High    | -              | 0.7 * SPIVCC    | SPIVCC + 0.3        | V                                     | (15)       |

| cs                                       | Weak Pull-down                          | Input Low     | -              | 0.0             | 0.4                 | V                                     | (15)       |

|                                          | Weak Full-dowll                         | Input High    | -              | 1.1             | SPIVCC + 0.3        | V                                     | (15)       |

| CS, MOSI (at Booting                     | Weak Pull-down                          | Input Low     | -              | 0.0             | 0.3 * VCOREDIG      | V                                     | (15), (23) |

| for SPI / I <sup>2</sup> C decoding)     | on CS                                   | Input High    | -              | 0.7 * VCOREDIG  | VCOREDIG            | V                                     | (15), (23) |

Table 8. Pin Logic Thresholds

| Pin Name                | Internal<br>Termination <sup>(19)</sup> | Parameter                | Load Condition | Min          | Max <sup>(22)</sup> | Unit                           | Notes             |

|-------------------------|-----------------------------------------|--------------------------|----------------|--------------|---------------------|--------------------------------|-------------------|

| MISO, INT PUMS1,2,3,4,5 | CMOS                                    | Output Low               | -100 μΑ        | 0.0          | 0.2                 | V                              | MISO<br>(15) (24) |

|                         | GMIGG                                   | Output High              | 100 μΑ         | SPIVCC - 0.2 | SPIVCC              | V                              | MISO<br>(15) (24) |

| DLIMS1 2 3 4 5          |                                         | Input Low<br>PUMSxS = 0  | -              | 0.0          | 0.3                 | V                              | (17)              |

| F UNIS 1,2,5,4,5        |                                         | Input High<br>PUMSxS = 1 | -              | 1.0          | VCOREDIG            | V                              | (17)              |

| ICTEST                  |                                         | Input Low                | -              | 0.0          | 0.3                 | V                              | (18)              |

| ICILSI                  |                                         | Input High               | -              | 1.1          | 1.7                 | V MI (15) V (15) V (17) V (18) | (18)              |

|                         |                                         | Input Low                | -              | 0.0          | 0.3                 | V                              |                   |

| SW1CFG, SW4CFG          |                                         | Input Mid                | -              | 1.3          | 2.0                 | V                              |                   |

|                         |                                         | Input High               | -              | 2.5          | 3.1                 | V                              |                   |

#### Notes

- 15. SPIVCC is typically connected to the output of buck regulator SW5 and set to 1.800 V

- 16. Input has internal pull-up to VCOREDIG equivalent to 200 kOhm

- 17. Input state is latched in first phase of cold start, refer to Serial Interfaces for a description of the PUMS configuration

- 18. Input state is not latched

- 19. A weak pull-down represents a nominal internal pull-down of 100 nA, unless otherwise noted

- 20. RESETB, RESETBMCU, SDWNB, SW1PWGD, SW2PWGD have open-drain outputs, external pull-ups are required

- 21. SPIVCC needs to remain enabled for proper detection of WDI High to avoid involuntary shutdown

- 22. The maximum should never exceed the maximum rating of the pin as given in Pin Connections

- 23. The weak pull-down on CS is disabled if a VIH is detected at start-up to avoid extra consumption in I2C mode

- 24. The output drive strength is programmable

# 5.3.3 Current Consumption

<u>Table 9</u> provides the current consumption for standard use cases.

## Table 9. Current Consumption Summary (27)

Characteristics noted under conditions BP = 3.6 V, -40  $^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85  $^{\circ}$ C, unless otherwise noted. Typical values at BP = 3.6 V and T<sub>A</sub> = 25  $^{\circ}$ C under nominal conditions, unless otherwise noted.

| Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                     | Тур                                                           | Max      | Unit            | Notes |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------|-----------------|-------|

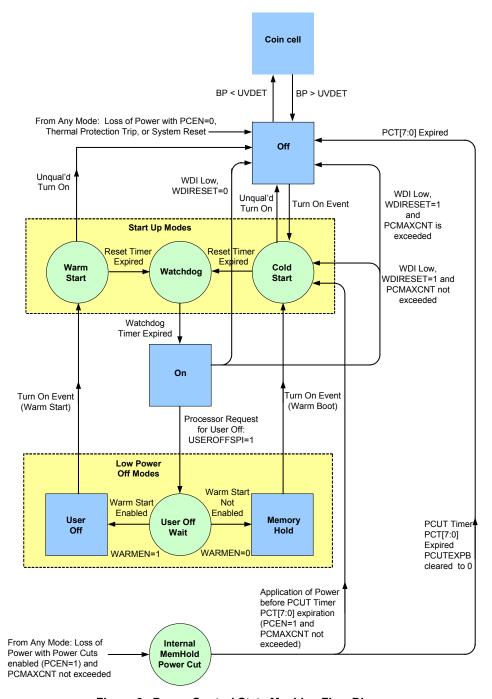

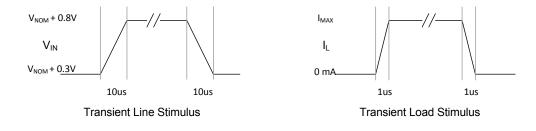

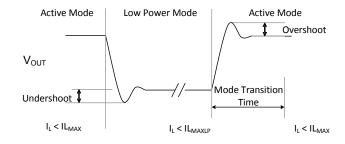

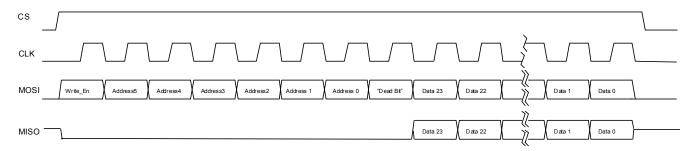

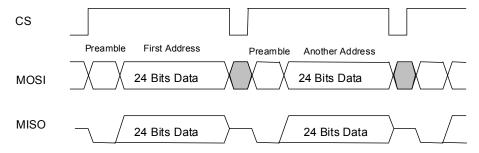

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | All blocks disabled, BP=0, coin cell is attached to LICELL (at 25 °C only)                                                                                                                                                                                                                                                                                                      |                                                               |          |                 |       |