# RICHTEK

# Low Profile 500mA LDO with Enable and Power Good/Reset

#### **General Description**

The RT9186 is a low-dropout linear regulator providing up to 500mA load current with 160mV dropout. It is especially designed for the application of portable and smart handheld device.

The RT9186 operates from 2.5V to 5.5V supply. The internal P-MOSFET pass transistor allows the regulator to work with 190µA low quiescent current. Its preset output voltage version covers the most frequently used values, including 1.8V/2.5V/3.3V. Output voltage can also be adjusted via the ADJ pin for those other than the preset values.

With only 0.1µA required in the shut down mode, one enable pin is able to control output on/off. RT9186A contains PGOOD function. On the other hand, RT9186B contains RST function with 6ms (typ.) time delay.

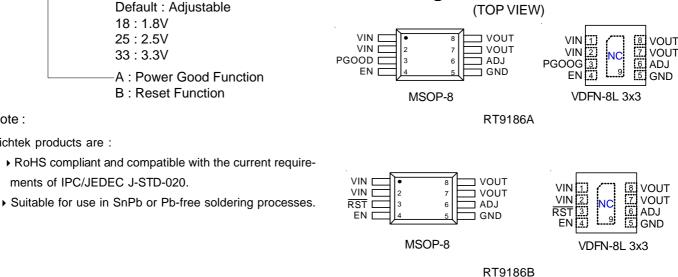

Package Type

QV: VDFN-8L 3x3 (V-Type)

G : Green (Halogen Free and Pb Free)

Lead Plating System

A : Power Good Function

**B** : Reset Function

F: MSOP-8

P: Pb Free

18:1.8V 25:2.5V

33:3.3V

Output Voltage Default : Adjustable

## **Ordering Information**

RT9186A/B-000

Note :

Richtek products are :

## Features

- 2.5V to 5.5V Wide Input Range

- Guaranteed 500mA Output Current

- Low 160mV Dropout at 500mA

- 1.8V/2.5V/3.3V Preset Output Voltage Version with Adjustable Range from 0.8V to 4.5V.

- Reset Output with 6ms (typ.) Delay Time

- Power Good Output

- Low 190µA Ground Pin Current

- 0.1µA Shutdown Current

- Thermal and Over Current Protection

- RoHS Compliant and 100% Lead (Pb)-Free

#### Applications

- Notebook Computer

- PDAs/SHDs

- PCMCIA/Cardbus Card Product

- Mobile Phone

#### Marking Information

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

## Pin Configurations

Copyright @2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

ments of IPC/JEDEC J-STD-020.

## **Pin Description**

| Pin Number |             | Pin Name           | Din Eurotion                                                                                                                                           |  |

|------------|-------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MSOP-8     | VDFN-8L 3x3 |                    | Pin Function                                                                                                                                           |  |

| 1, 2       | 1,2         | VIN                | Power Input Voltage.                                                                                                                                   |  |

| 3          | 3           | PGOOD<br>(RT9186A) | Power Good Indicator. (RT9186A).                                                                                                                       |  |

| 3          | 3           | RST<br>(RT9186B)   | Open-Drain Active-Low Reset Output. Connect a $100k\Omega$ to VOUT to obtain output voltage.<br>In shutdown the $\overline{\text{RST}}$ output is low. |  |

| 4          | 4           | EN                 | Enable Control Input (Active-High). There should be a pull low resistor $100k\Omega$ connected to GND when the control signal is floating.             |  |

| 5          | 5           | GND                | Ground.                                                                                                                                                |  |

| 6          | 6           | ADJ                | Output Voltage Setting. Connect to GND for Fixed output voltage model.                                                                                 |  |

| 7, 8       | 7,8         | VOUT               | Output Voltage.                                                                                                                                        |  |

| 9          | 9           | NC                 | No Internal Connection.                                                                                                                                |  |

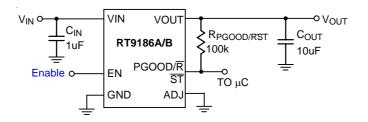

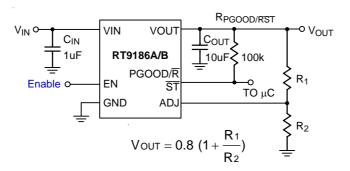

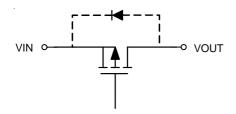

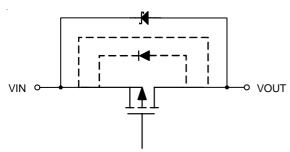

## **Typical Application Circuit**

Figure 1. Fixed Voltage Regulator

Figure 2. Adjustable Voltage Regulator

Note1 : R2 should be less than 80k to ensure regulation. Note2 : X5R or X7R input capacitor  $i\hat{U}1\mu F$  is recommended for output stability.

| Copyright ©2013 Richtek Technology Corporation. All rights reserved. | <b>RICHTEK</b> is a registered trademark of Richtek Technology Corporation. |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

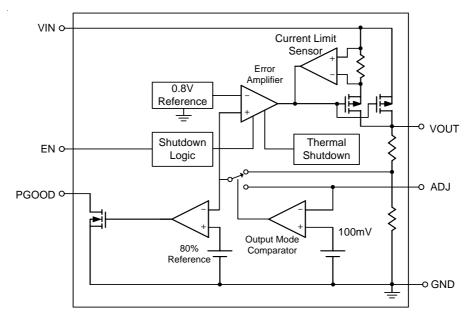

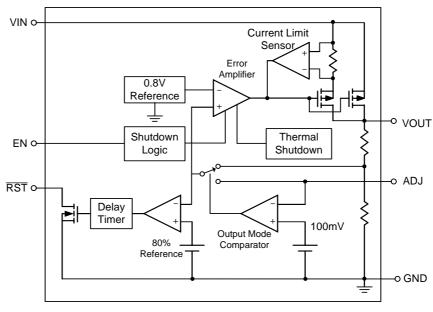

## **Function Block Diagram**

-RT9186A-

-RT9186B-

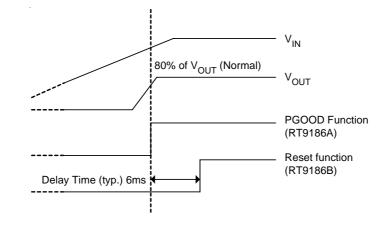

## **Timing Diagram**

## Absolute Maximum Ratings (Note 1)

| Input Voltage                                                  | 7V             |

|----------------------------------------------------------------|----------------|

| Storage Temperature Range                                      | –65°C to 150°C |

| Lead Temperature (Soldering, 10 sec.)                          | 260°C          |

| <ul> <li>Power Dissipation, PD @ T<sub>A</sub>=25°C</li> </ul> |                |

| MSOP-8                                                         | 0.625W         |

| VDFN-8L 3x3                                                    | 0.952W         |

| Package Thermal Resistance (Note 2)                            |                |

| MSOP-8, θ <sub>JA</sub>                                        | 160°C/W        |

| VDFN-8L 3x3, $\theta_{JA}$                                     | 105°C/W        |

| Junction Temperature                                           | 150°C          |

| ESD Susceptibility (Note 3)                                    |                |

| HBM (Human Body Model)                                         | 2kV            |

## Recommended Operating Conditions (Note 4)

| • | Input Voltage              | 2.5V to 5.5V   |

|---|----------------------------|----------------|

| • | Junction Temperature Range | –40°C to 125°C |

| • | Ambient Temperature Range  | –40°C to 85°C  |

#### **Electrical Characteristics**

$(V_{IN} = V_{OUT(NOM)} + 500mV \text{ or } V_{IN} = +2.5V \text{ (whichever is greater), } T_A = 25^{\circ}C, \text{ unless otherwise specified)}$

| Parameter                                |                             | Symbol             | Test Conditions                                                            | Min   | Тур  | Мах   | Unit |

|------------------------------------------|-----------------------------|--------------------|----------------------------------------------------------------------------|-------|------|-------|------|

| General Specifi                          | cation                      |                    |                                                                            |       |      |       |      |

| Input Under Voltage Lock-Out             |                             | V <sub>UVLO</sub>  |                                                                            | 2.0   | 2.3  | 2.4   | V    |

| Output Voltage Accuracy<br>(Preset Mode) |                             | ΔV <sub>OUT</sub>  | I <sub>OUT</sub> = 1mA to 500mA                                            | -3    | 0    | 3     | %    |

| Adjustable Outp                          | ut Voltage Range            | Vout_adj           |                                                                            | 0.8   |      | 4.5   | V    |

| ADJ Pin Voltage                          |                             | V <sub>ADJ</sub>   |                                                                            | 0.784 | 0.8  | 0.816 | V    |

| ADJ Input Bias (                         | Current                     | I <sub>ADJ</sub>   | V <sub>ADJ</sub> = +0.8V                                                   |       | 10   | 100   | nA   |

| Short Circuit Cur                        | rrent Limit                 | ILIM               | V <sub>OUT</sub> = 0V                                                      | 0.9   | 1.4  | 2.0   | А    |

| Quiescent Curre                          | nt (Note 5)                 | lq                 | I <sub>OUT</sub> = 0mA                                                     |       | 190  | 250   | μA   |

| Dropout Voltage                          | (Note 6)                    | V <sub>DROP</sub>  | I <sub>OUT</sub> = 500mA                                                   |       | 200  | 330   | mV   |

|                                          | (                           | BILOI              | V <sub>OUT</sub> = 3.3V                                                    |       | 160  | 220   |      |

| Line Regulation                          |                             | $\Delta V_{LINE}$  | V <sub>OUT</sub> + 0.1V < V <sub>IN</sub> < 5.5V<br>I <sub>OUT</sub> = 5mA |       | 0.02 | 0.125 | %/V  |

| Load Regulation (Note 7)                 |                             | $\Delta V_{LOAD}$  | I <sub>OUT</sub> = 1mA to 500mA                                            |       | 21   | 40    | mV   |

| Chip Enable                              |                             |                    |                                                                            |       |      |       |      |

| Standby Current                          |                             | I <sub>STBY</sub>  | V <sub>IN</sub> = 5.5V                                                     |       | 0.1  | 2     | μA   |

| EN Threshold                             | Logic-Low Voltage           | V <sub>ENL</sub>   | V <sub>IN</sub> = 2.5V                                                     |       |      | 0.7   | V    |

|                                          | Logic-High Voltage          | V <sub>ENH</sub>   | V <sub>IN</sub> = 5.5V                                                     | 1.6   |      |       | v    |

| EN Input Bias Current                    |                             | I <sub>EN</sub>    | V <sub>CE</sub> = 5.5V                                                     |       | 20   | 100   | nA   |

| Reset                                    |                             |                    |                                                                            |       |      |       |      |

| Reset Output Low Voltage                 |                             | V <sub>OL</sub>    | Reset Output Sinking 2mA                                                   |       | 50   | 100   | mV   |

| Output High Leal                         | kage Current                |                    | V <sub>RST</sub> = 5V                                                      |       |      | 100   | nA   |

| Threshold to Out                         | put Voltage                 |                    | Rising edge, referred to $V_{OUT}$                                         | 77    | 80   | 83    | %    |

| Reset Delay Tim                          | e                           | T <sub>DELAY</sub> | Rising edge of $V_{OUT}$ to $V_{\overline{RST}}$                           | 0.7   | 6    | 8     | ms   |

| Power Good                               |                             |                    |                                                                            |       |      |       |      |

| PGOOD Output Low Voltage                 |                             |                    | PGOOD Output sinking 2mA                                                   |       | 50   | 100   | mV   |

| Output High Leakage Current              |                             |                    | V <sub>PGOOD</sub> = 5V                                                    |       |      | 100   | nA   |

| Threshold to Output Voltage              |                             |                    | Rising edge, referred to $V_{\mbox{OUT}}$                                  | 77    | 80   | 83    | %    |

| Thermal Protection                       |                             |                    |                                                                            |       |      |       |      |

| Thermal Shutdov                          | wn Temperature              | T <sub>SD</sub>    |                                                                            |       | 160  |       | °C   |

|                                          | Thermal Shutdown Hysteresis |                    |                                                                            |       | 30   |       | °C   |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a single-layer and four-layer test board of JEDEC 51. The measurement case position of  $\theta_{JC}$  is on the lead of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is highly recommended.

- Note 4. The operating conditions beyond the recommended range is not guaranteed.

- Note 5. Quiescent, or ground current, is the difference between input and output currents. It is defined by  $I_Q = I_{IN} I_{OUT}$  under no load condition ( $I_{OUT} = 0$ mA). The total current drawn from the supply is the sum of the load current plus the ground pin current.

- Note 6. The dropout voltage is defined as  $V_{IN}$  - $V_{OUT}$ , which is measured when  $V_{OUT}$  is  $V_{OUT(NORMAL)}$  100mV.

- **Note 7.** Regulation is measured at constant junction temperature by using a 20ms current pulse. Devices are tested for load regulation in the load range from 1mA to 300mA and 500mA respectively.

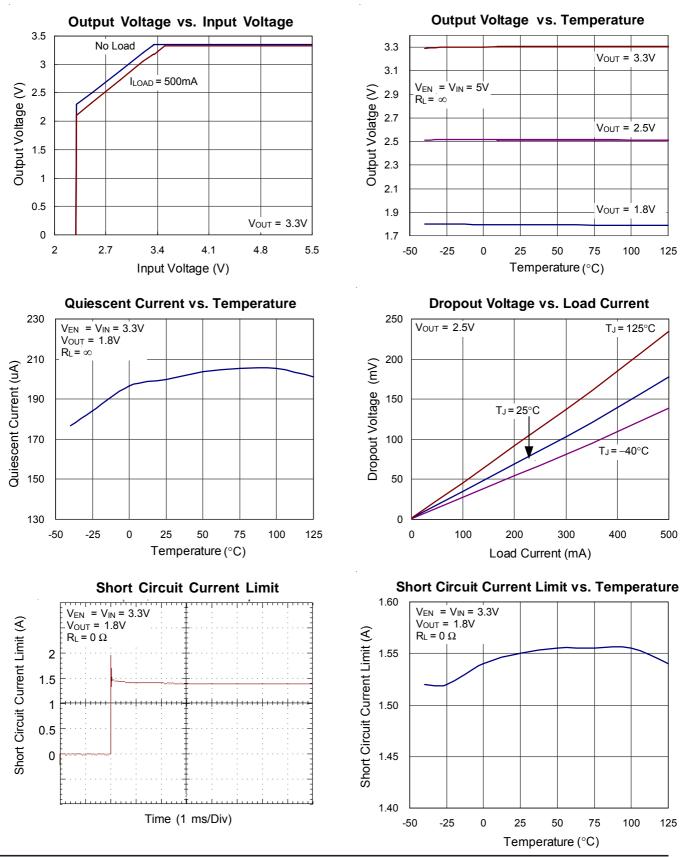

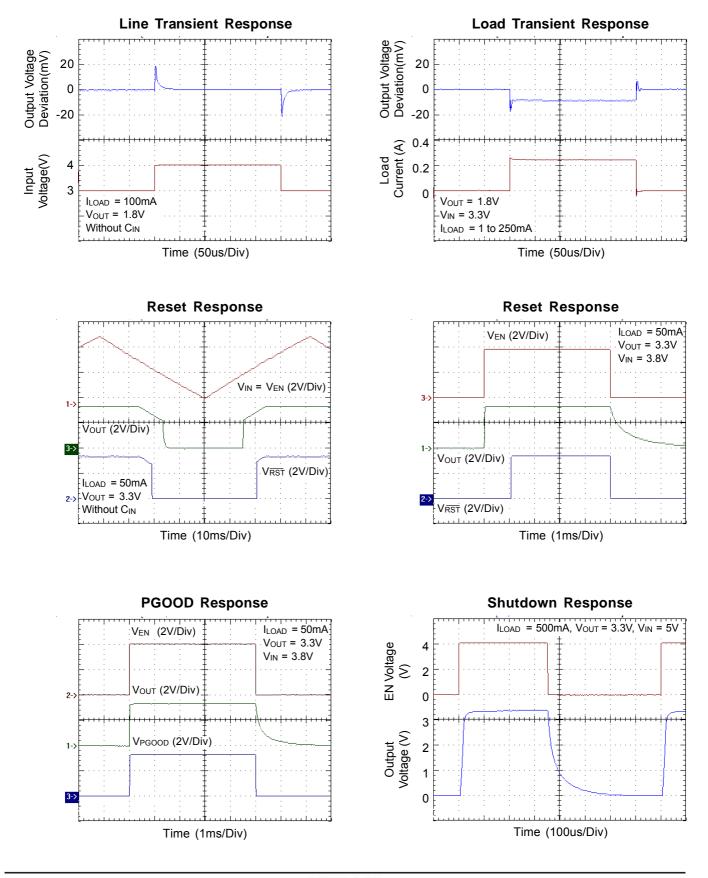

**Typical Operating Characteristics**  $C_{IN} = 1\mu F(X7R \text{ Ceramic}), C_{OUT} = 10\mu F(Y5V \text{ Ceramic}), T_A = 25^{\circ}C$ , unless otherwise specified.

## **Application Information**

#### Capacitor Selection and Regulator Stability

Careful selection of the external capacitors for RT9186 is highly recommended in order to remain high stability and performance.

Regarding the Input capacitor, connecting an X7R or X5R ceramic capacitor which is  $i\dot{U}1\mu$ F between input and ground is a must. Distance less than 1 cm between input pin and ground of RT9186 is recommended to avoid any unstability. With larger value of capacitor adding on lower ESR could result in better performance for both PSRR and line transient response.

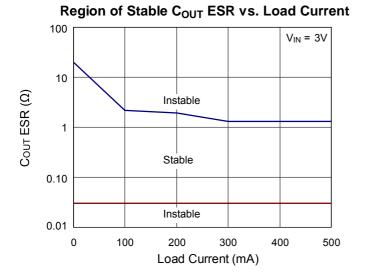

Regarding the output capacitor, connecting  $a10\mu$ F capacitor between output and ground is a must. Any capacitor is acceptable only with a highlight of relation between ESR region and Load current, shown in below. Output capacitor with larger capacitance can reduce noise and improve load transient response, stability, and PSRR. The same as Input capacitor, distance less than 1 cm between output pin and ground of RT9186 is recommended to avoid any unstability.

#### Input-Output (Dropout) Voltage

A regulator' s minimum input-to-output voltage differential (dropout voltage) determines the lowest usable supply voltage. In battery-powered systems, this determines the useful end-of-life battery voltage. Because the device uses a P-MOSFET, its dropout voltage is a function of drain-to-source on-resistance, R<sub>DS(ON)</sub>, multiplied by the load current:

$V_{DROPOUT} = V_{IN} - V_{OUT} = R_{DS(ON)} I_{OUT}$

#### **Over-Current and Short-Circuit Protection**

The RT9186 continuously monitors output current to provide maximum safety. In the event of output over current or short-circuit, over-current protection function will activate and override the voltage regulation function to limit output current at 1.4A typically. Large power dissipation at this condition may cause chip temperature to raise and trigger the over temperature protection if over-current or shortcircuit is not removed in a short time

#### Power Good and Reset

The power good and the reset output is an open-drain output. Connect an  $100k\Omega$  pull up resistor to V<sub>OUT</sub> to obtain an output voltage. The power good will output high immediately after the output voltage arrives 80% of normal output voltage. In the same situation, the reset will output high with 6ms delay time. See Timing Diagram and Typical Operating Characteristics.

#### **Adjustable Operation**

The output voltage of RT9186 is adjustable from 0.8V to 4.5V by an external voltage divider as shown in Typical Application Circuit Figure 2. The value of R2 should be less than  $80k\Omega$  to ensure regulation.

#### **Chip Enable Operation**

Pull the EN pin low to drive the device into shutdown mode. At the same time, pin 3 (PGOOD/RST) is pulled low. During shutdown mode, the standby current drops to  $0.1\mu A$  (typ). The output voltage decay rate is determined by the external capacitor and load current. Drive the EN pin high to turn on the device again.

# RICHTEK

#### **Reverse Current Path**

The P-MOSFET pass element of RT9186 has an inherendiode connected between the regulator input and output as shown in Figure 3. The inherent diode will be forward biased and conduct an unlimited current if  $V_{OUT}$  is sufficiently higher than  $V_{IN}$  a Schottky diode is recommended connecting parallel with the inherent diode in the application where output voltage may be higher than input voltage as shown in Figure 4. This Schottkly will clamp the forward bias voltage to 0.3V and conduct the possible current to protect the RT9186 from damage by unlimited current.

Figure 3. Inherent Diode of P-MOSFET Pass Transistor

Figure 4. Schottkly Diode Parallel with The Ingerent Diode

#### **Thermal Considerations**

Thermal protection limits power dissipation in RT9186A/B. When the operation junction temperature exceeds 160°C, the OTP circuit starts the thermal shutdown function and turns the pass element off. The pass element turn on again after the junction temperature cools by 30°C.

For continuous operation, do not exceed absolute maximum operation junction temperature 125°C. The power dissipation definition in device is :

$$P_{D} = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{Q}$$

The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by following formula :

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = \left(\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}\right) / \, \theta_{\mathsf{JA}}$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature 125°C,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

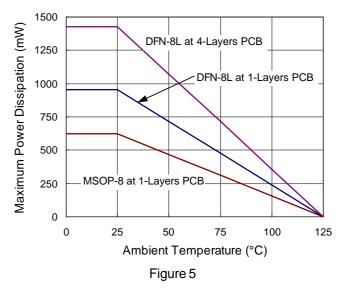

For recommended operating conditions specification of RT9186A/B, where  $T_{J(MAX)}$  is the maximum junction temperature of the die (125°C) and  $T_A$  is the maximum ambient temperature. The junction to ambient thermal resistance  $\theta_{JA}$  is layout dependent. For VDFN-8L 3x3 package, the thermal resistance  $\theta_{JA}$  is 105°C/W on the standard JEDEC 51-3 single-layer 1S thermal test board and 70°C/W on the standard JEDEC 51-7 4-layers 2S2P thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by following formula :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / 105 = 0.952W \text{ for single-layer}$  1S board

$\mathsf{P}_{\mathsf{D}(\mathsf{MAX})}$  = (125°C - 25°C) / 70 = 1.428W for 4-layers 2S2P board

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ . The Figure 5 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power allowed.

# RICHTEK

#### Layout Consideration

Good board layout practices must be used or instability can be induced because of ground loops and voltage drops. The input and output capacitors **MUST** be directly connected to the input, output, and ground pins of the device using traces which have no other currents flowing through them.

The best way to do this is to layout  $C_{IN}$  and  $C_{OUT}$  near the device with short traces to the  $V_{IN}$ ,  $V_{OUT}$ , and ground pins. The regulator ground pin should be connected to the external circuit ground so that the regulator and its capacitors have a "single point ground".

It should be noted that stability problems have been seen in applications where "vias" to an internal ground plane were used at the ground points of the device and the input and output capacitors. This was caused by varying ground potentials at these nodes resulting from current flowing through the ground plane. Using a single point ground technique for the regulator and it's capacitors fixed the problem. Since high current flows through the traces going into V<sub>IN</sub> and coming from V<sub>OUT</sub>, Kelvin connect the capacitor leads to these pins so there is no voltage drop in series with the input and output capacitors.

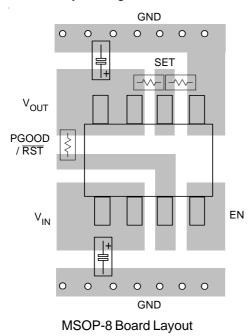

Optimum performance can only be achieved when the device is mounted on a PC board according to the MSOP-8 Board Layout diagram.

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

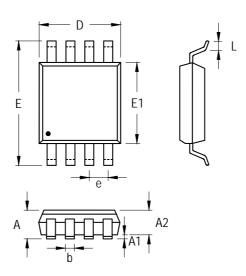

# **Outline Dimension**

| C. maked | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|----------|------------|----------------|----------------------|-------|--|

| Symbol   | Min        | Max            | Min                  | Max   |  |

| А        | 0.810      | 1.100          | 0.032                | 0.043 |  |

| A1       | 0.000      | 0.150          | 0.000                | 0.006 |  |

| A2       | 0.750      | 0.950          | 0.030                | 0.037 |  |

| b        | 0.220      | 0.380          | 0.009                | 0.015 |  |

| D        | 2.900      | 3.100          | 0.114                | 0.122 |  |

| е        | 0.650      |                | 0.0                  | 26    |  |

| E        | 4.800      | 5.000          | 0.189                | 0.197 |  |

| E1       | 2.900      | 3.100          | 0.114                | 0.122 |  |

| L        | 0.400      | 0.800          | 0.016                | 0.031 |  |

8-Lead MSOP Plastic Package

Copyright 2013 Richtek Technology Corporation. All rights reserved.

# RICHTEK

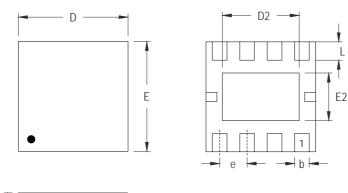

| Cumhal | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| А      | 0.800        | 1.000         | 0.031                | 0.039 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175        | 0.228         | 0.007                | 0.009 |  |

| b      | 0.200        | 0.300         | 0.008                | 0.012 |  |

| D      | 2.950        | 3.050         | 0.116                | 0.120 |  |

| D2     | 2.250        | 2.350         | 0.089                | 0.093 |  |

| E      | 2.950        | 3.050         | 0.116                | 0.120 |  |

| E2     | 1.450        | 1.550         | 0.057                | 0.061 |  |

| е      | 0.650        |               | 0.026                |       |  |

| L      | 0.425        | 0.525         | 0.017                | 0.021 |  |

V-Type 8L DFN 3x3 Package

#### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

# **X-ON Electronics**

Largest Supplier of Electrical and Electronic Components

Click to view similar products for Richtek manufacturer:

Other Similar products are found below :

EVB\_RT5047GSP\_EVB\_RT7275GQW\_EVB\_RT7297CHZSP\_RT9080N-08GJ5\_EVB\_RT5047AGSP\_EVB\_RT7243GQW EVB\_RT7272BGSP\_RT8097AHGE\_EVB\_RT7247CHGSP\_EVB\_RT7276GQW\_EVB\_RT8293AHZSP\_EVB\_RT6200GE EVB\_RT7235GQW\_EVB\_RT7237AHGSP\_EVB\_RT7251AZQW\_RT5047AGSP\_EVB\_RT7272AGSP\_EVB\_RT7237CHGSP EVB\_RT7247AHGSP\_EVB\_RT7252BZSP\_EVB\_RT7280GQW\_EVB\_RT8292AHZSP\_EVB\_RT8297BZQW\_EVB\_RT7231GQW EVB\_RT7232GQW\_EVB\_RT7236GQW\_EVB\_RT7250BZSP\_EVB\_RT7251BZQW\_EVB\_RT7279GQW\_EVB\_RT8008GB\_RT8207MZQW RT8296AHZSP\_RT9011-JGPJ6\_RT8258GE\_RT5711AHGQW\_RT9081AGQZA(2)\_RT6154BGQW\_RT7238BGQUF\_RT5788AGJ8F RT8812AGQW\_RT6278BHGQUF\_RT7270HZSP\_RD0004\_RT5789AGQUF\_RT9076-18GVN\_RT9193-15GU5\_RT3602AJGQW RT8296BHZSP\_RT6214AHGJ6F\_RT9276GQW(Z00)